© SUMMIT MICROELECTRONICS, Inc. 2000 ∑ 300 Orchard City Drive, Suite 131 ∑ Campbell, CA 95008 ∑ Phone 408-378-6461 ∑ Fax 408-378-6586 ∑ www.summitmicro.com

1

Characteristics subject to change without notice

2038 2.0 6/8/00

SUMMIT

MICROELECTRONICS, Inc.

SMS1242

FEATURES

∑ Supply voltage monitor

- Nominal V

RST

of 2.45V, 2.65V, 2.95V, 4.45V,

4.55V or 4.65V

- RESET# Outputs Guaranteed true at V

CC

= 1V

- 150ms Reset Delay Time

∑ Second voltage monitor

- V

SENSE

Input

- 1.25V threshold ±1%

∑ Manual Reset Input

∑ Includes 16k-bits nonvolatile memory

- Industry standard 2-wire serial interface

2.5V, 3V, 3.3V & 5V Dual Voltage, Dual Reset

Microprocessor Supervisory Circuits

OVERVIEW

The SMS1242 microprocessor supervisory circuit re-

duces the complexity and number of components required

to monitor the supply voltage in +5V, +3V and +2.5V

systems. The SMS1242 will significantly improve system

reliability and accuracy when compared to implementing

the same functions with discrete components.

The SMS1242 provides reset output during power-up,

power-down, and brown-out conditions. It has a 1.25V

threshold input detector for power-fail warning, low battery

detection, or monitoring a secondary power supply. The

part also integrates a separate active low manual reset

input.

It also has 16k-bits of nonvolatile memory accessible over

an industry standard 2-wire serial interface.

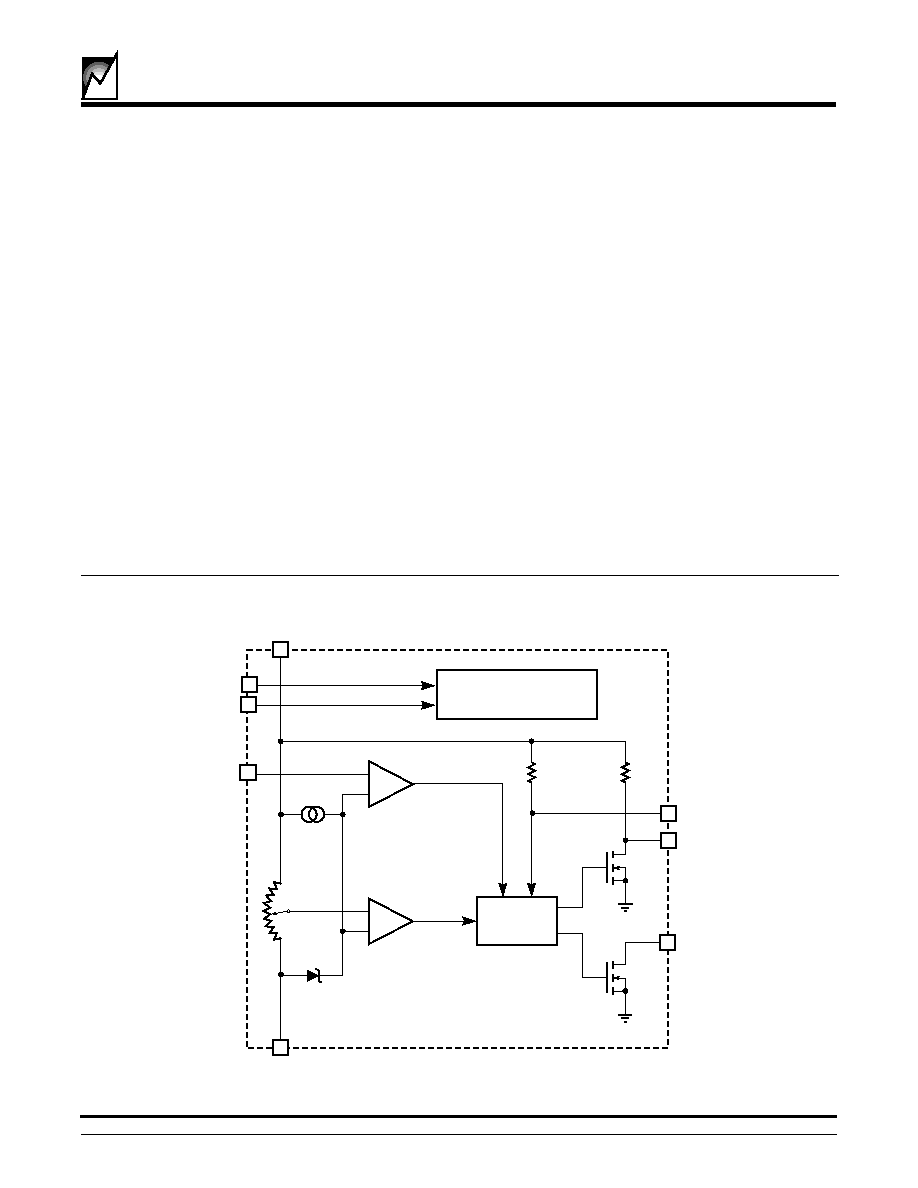

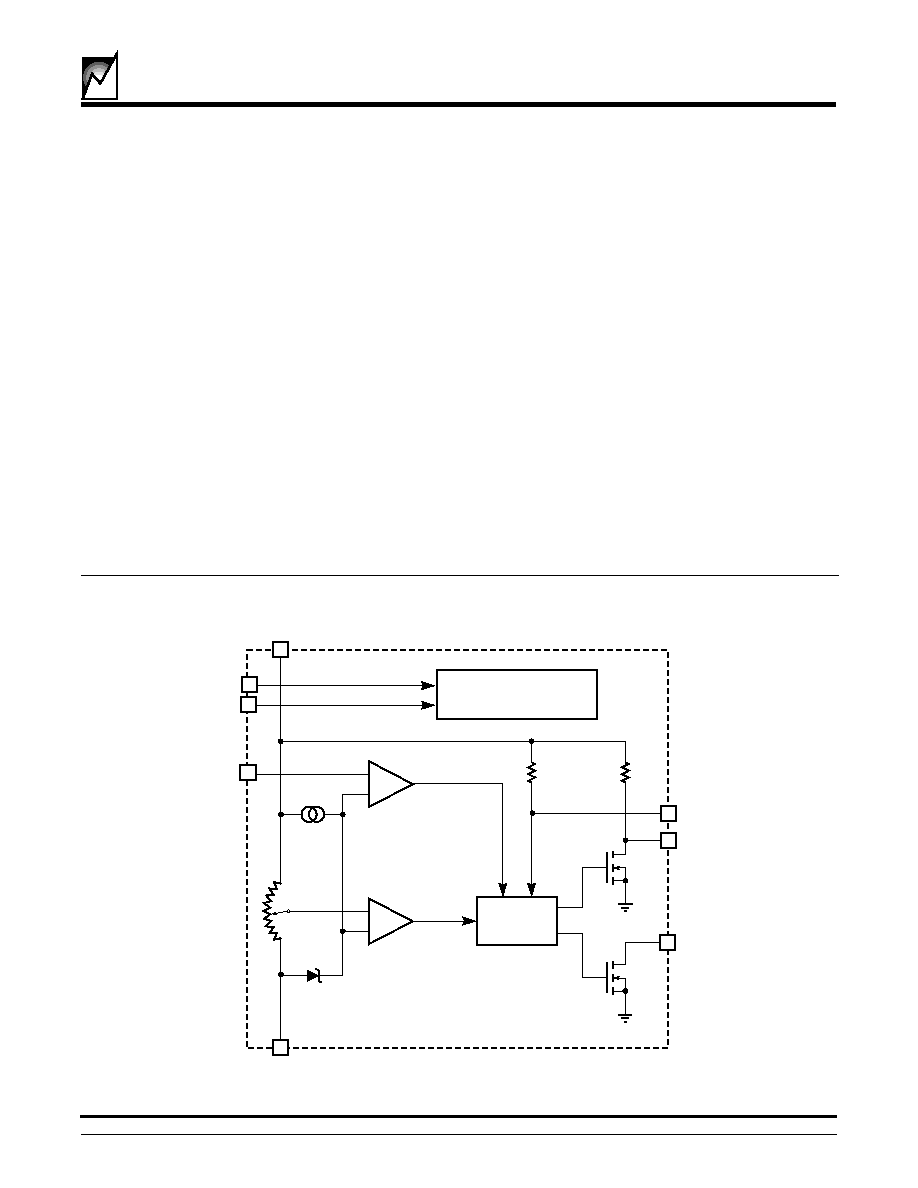

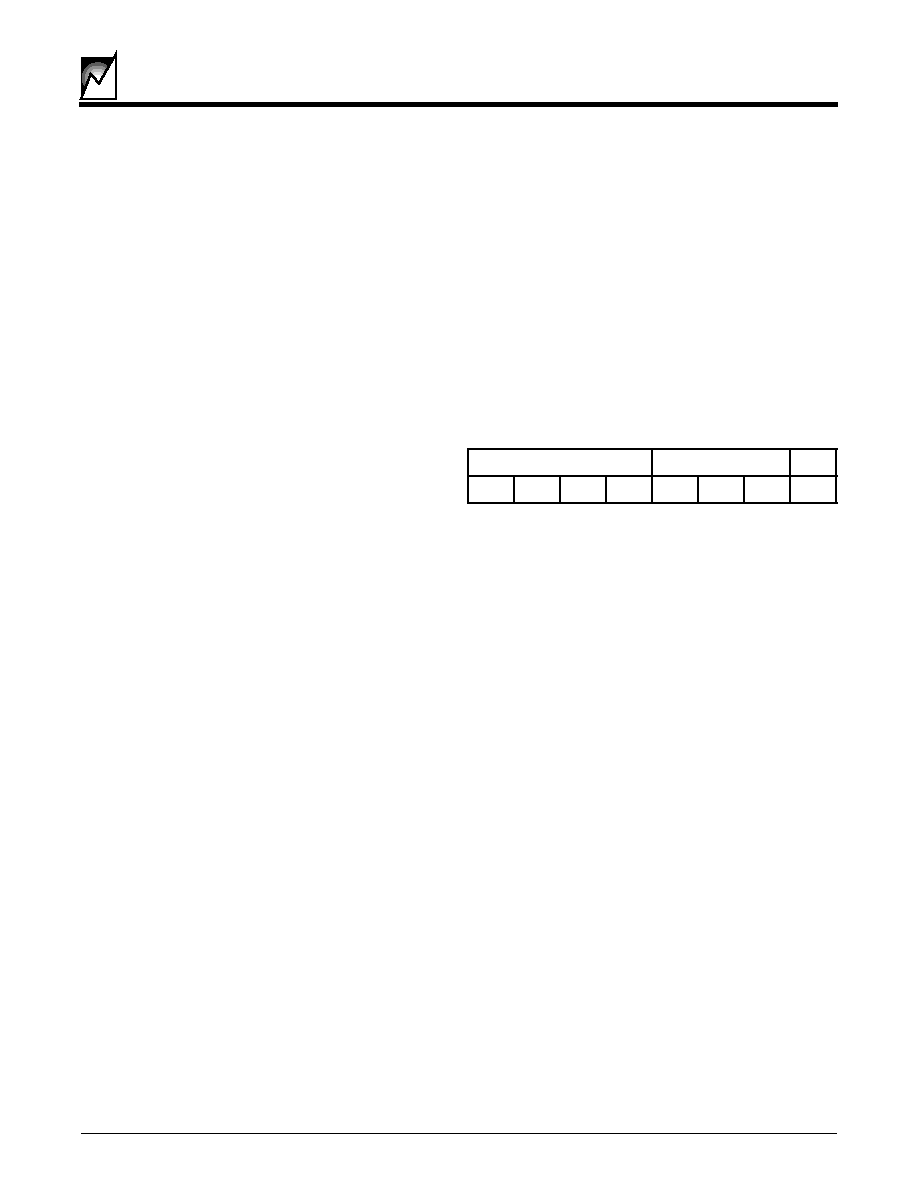

FUNCTIONAL BLOCK DIAGRAM

+

≠

GND

VCC

8

4

RESET1#

2

VTRIP

RESET

GENERATOR

7

1.25V

SCL

6

SDA

5

2038 BD 2.0

NONVOLATILE

MEMORY

ARRAY

VSENSE 3

MR#

1

+

≠

RESET2#

2

SMS1242

2038 2.0 6/8/00

SUMMIT MICROELECTRONICS, Inc.

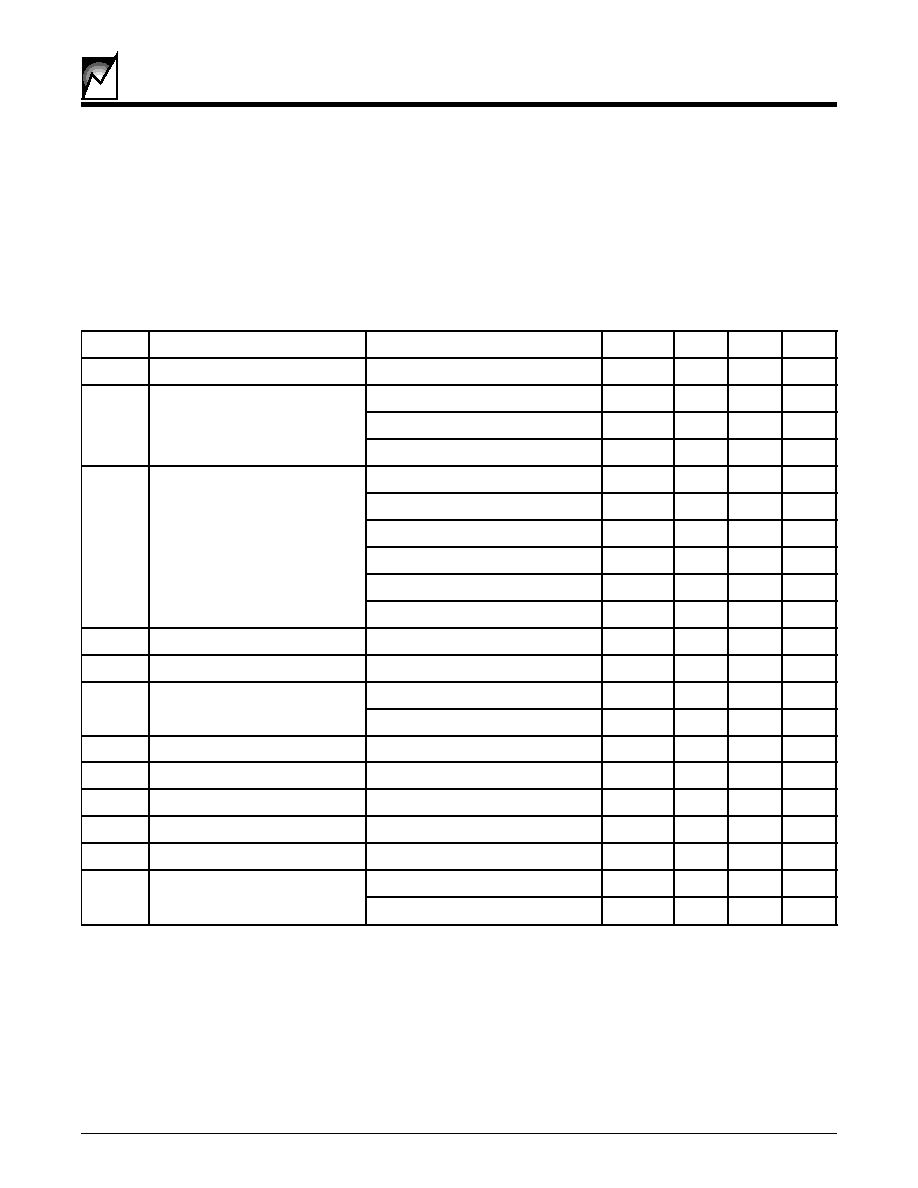

ABSOLUTE MAXIMUM RATINGS*

Temperature Under Bias

≠55∞C to 125∞C

Storage Temperature

≠65∞C to 150∞C

Terminal Voltage (With Respect to Ground)≠0.3V to 6V

Lead Solder Temperature (10 secs)

300∞C

*COMMENT

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or

any other conditions outside those listed in the operation sec-

tions of this specification is not implied. Exposure to any abso-

lute maximum rating for extended periods may affect device

performance and reliability.

2038 Elect Table 2.0

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

.

n

i

M

.

p

y

T

.

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

v

y

l

p

p

u

s

g

n

i

t

a

r

e

p

O

1

5

.

5

V

I

C

C

t

n

e

r

r

u

c

y

l

p

p

u

S

<

V

6

.

3

V

C

C

5

.

5

<

V

5

2

0

5

A

µ

>

V

6

.

3

V

C

C

5

2

0

5

A

µ

)

y

l

n

o

3

4

2

1

S

M

S

(

s

s

e

c

c

a

y

r

o

m

e

M

3

A

m

V

T

S

R

d

l

o

h

s

e

r

h

t

t

e

s

e

R

A

n

o

i

t

p

o

e

c

i

v

e

D

5

7

3

.

4

5

2

4

.

4

5

7

4

.

4

V

B

n

o

i

t

p

o

e

c

i

v

e

D

5

2

6

.

4

5

7

6

.

4

5

2

7

.

4

V

C

n

o

i

t

p

o

e

c

i

v

e

D

5

2

4

.

4

5

7

4

.

4

5

2

5

.

4

V

D

n

o

i

t

p

o

e

c

i

v

e

D

5

2

4

.

2

0

5

4

.

2

5

7

4

.

2

V

E

n

o

i

t

p

o

e

c

i

v

e

D

5

2

6

.

2

0

5

6

.

2

5

7

6

.

2

V

F

n

o

i

t

p

o

e

c

i

v

e

D

5

2

9

.

2

0

5

9

.

2

5

7

9

.

2

V

V

T

S

Y

H

V

T

S

R

s

i

s

i

r

e

t

s

y

H

0

5

V

m

t

T

S

R

h

t

d

i

w

e

s

l

u

p

t

e

s

e

R

0

0

1

0

5

1

0

0

2

s

m

V

L

O

e

g

a

t

l

o

v

w

o

l

t

u

p

t

u

o

#

1

T

E

S

E

R

I

K

N

I

S

V

,

A

m

2

.

1

=

C

C

V

=

T

S

R

.

n

i

m

3

.

0

V

I

K

N

I

S

V

,

A

µ

0

0

2

=

C

C

V

2

.

1

=

3

.

0

V

I

R

M

t

n

e

r

r

u

c

p

u

ll

u

p

#

R

M

0

0

1

A

µ

t

R

M

h

t

d

i

w

e

s

l

u

p

#

R

M

0

5

s

n

V

L

I

d

l

o

h

s

e

r

h

t

t

u

p

n

i

#

R

M

6

.

0

V

V

H

I

d

l

o

h

s

e

r

h

t

t

u

p

n

i

#

R

M

7

.

0

◊

V

C

C

V

V

S

N

S

V

E

S

N

E

S

d

l

o

h

s

e

r

h

t

t

u

p

n

i

V

C

C

= V

T

S

R

V

,

.

n

i

m

E

S

N

E

S

g

n

il

l

a

f

0

2

.

1

5

2

.

1

0

3

.

1

V

V

C

C

e

g

a

t

l

o

v

w

o

l

t

u

p

t

u

o

#

2

T

E

S

E

R

I

K

N

I

S

V

,

A

m

2

.

1

=

C

C

V

=

T

S

R

.

n

i

m

3

.

0

V

I

K

N

I

S

V

,

A

µ

0

0

2

=

C

C

V

2

.

1

=

4

.

0

V

3

2038 2.0 6/8/00

SMS1242

SUMMIT MICROELECTRONICS, Inc.

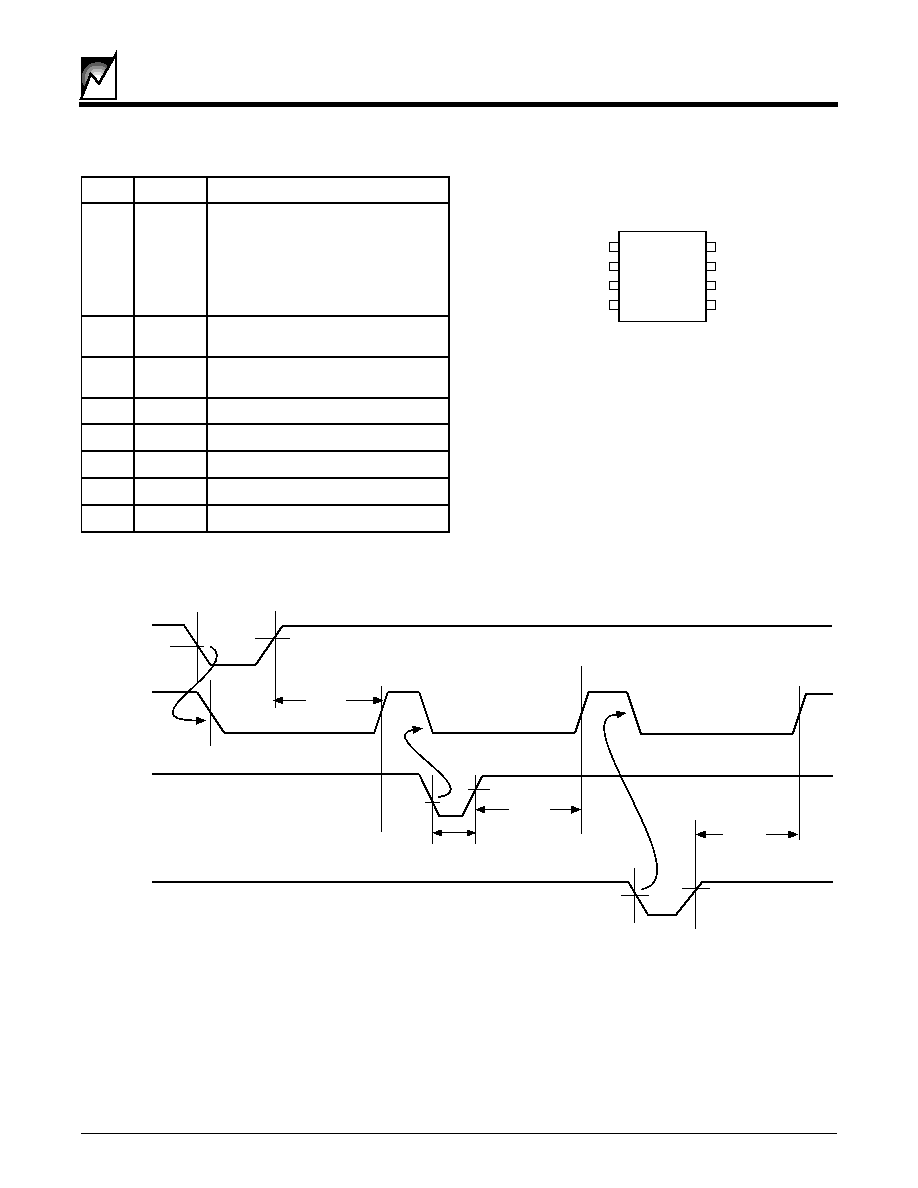

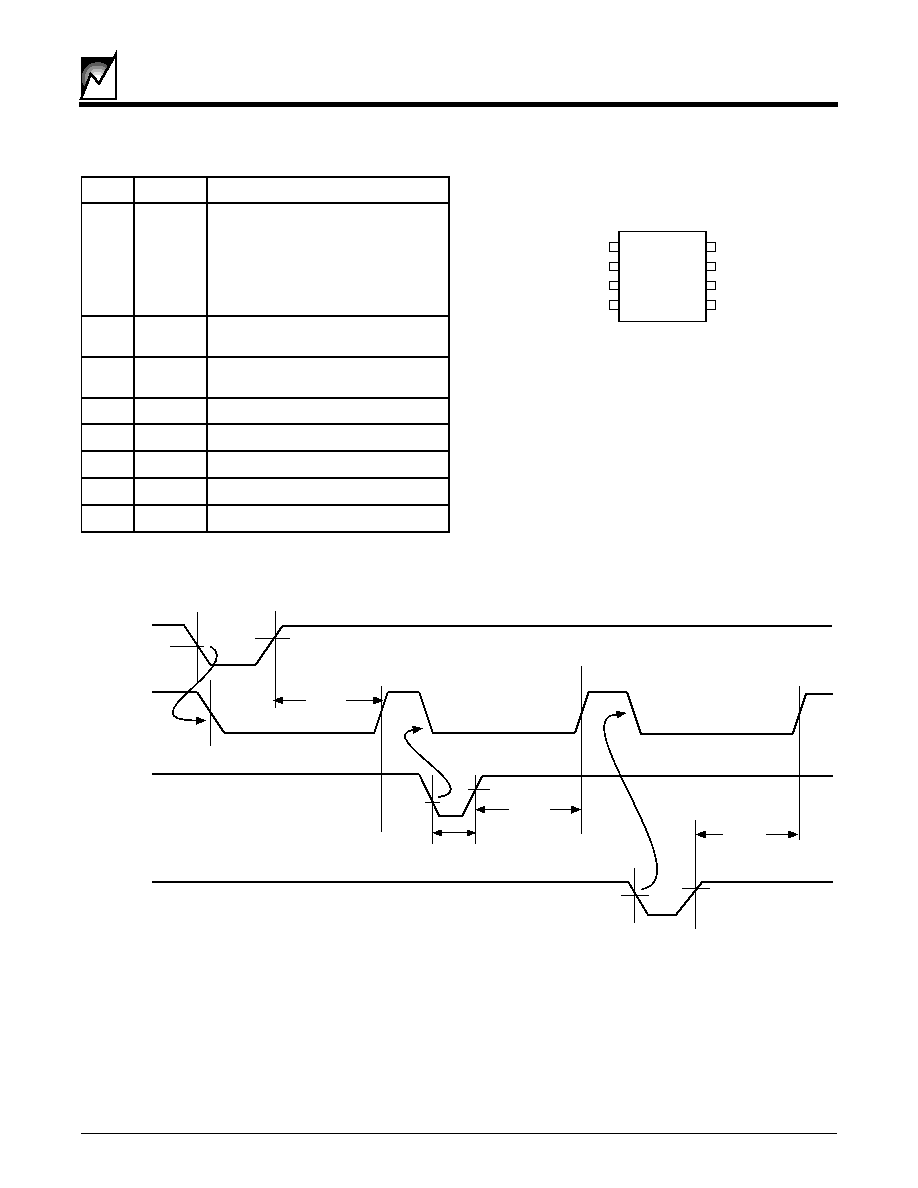

PIN CONFIGURATION

PIN NAMES

2038 Pin Table 2.0

RESET1#

RESET2#

V

SENSE

GND

V

CC

MR#

SCL

SDA

1

2

3

4

8

7

6

5

8-Pin SOIC

2038 T PCon 2.0

Figure 1. Reset Waveforms

n

i

P

l

a

n

g

i

S

n

o

i

t

c

n

u

F

1

#

1

T

E

S

E

R

.

p

u

ll

u

p

k

a

e

w

h

t

i

w

t

u

p

t

u

o

w

o

l

e

v

i

t

c

A

:

y

b

w

o

l

n

e

v

i

r

D

V

E

S

N

E

S

-

h

s

e

r

h

t

w

o

l

e

b

r

o

;

d

l

o

V

C

C

e

li

h

w

d

l

o

h

s

e

r

h

t

w

o

l

e

b

s

n

i

a

m

e

R

.

d

l

o

h

s

e

r

h

t

w

o

l

e

b

s

i

#

R

M

r

e

t

f

a

s

m

0

5

1

r

o

f

w

o

l

V

E

S

N

E

S

r

o

,

V

C

C

.

d

l

o

h

s

e

r

h

t

e

v

o

b

a

s

i

,

#

R

M

d

n

a

2

#

2

T

E

S

E

R

n

e

p

o

t

p

e

c

x

e

,

#

1

t

e

s

e

R

s

a

e

m

a

S

n

o

i

t

c

e

n

n

o

c

n

i

a

r

d

3

V

E

S

N

E

S

e

h

t

r

o

f

t

u

p

n

i

r

o

t

c

e

t

e

d

d

l

o

h

s

e

r

h

T

s

t

e

s

e

R

4

D

N

G

d

n

u

o

r

G

5

D

N

G

/

A

D

S

d

n

u

o

r

g

r

o

,

O

/

I

a

t

a

D

3

4

2

1

S

M

S

6

D

N

G

/

L

C

S

d

n

u

o

r

g

r

o

,

k

c

o

l

C

a

t

a

D

3

4

2

1

S

M

S

7

#

R

M

s

t

e

s

e

R

r

o

f

t

u

p

n

i

l

a

u

n

a

M

8

V

C

C

e

g

a

t

l

o

v

y

l

p

p

u

S

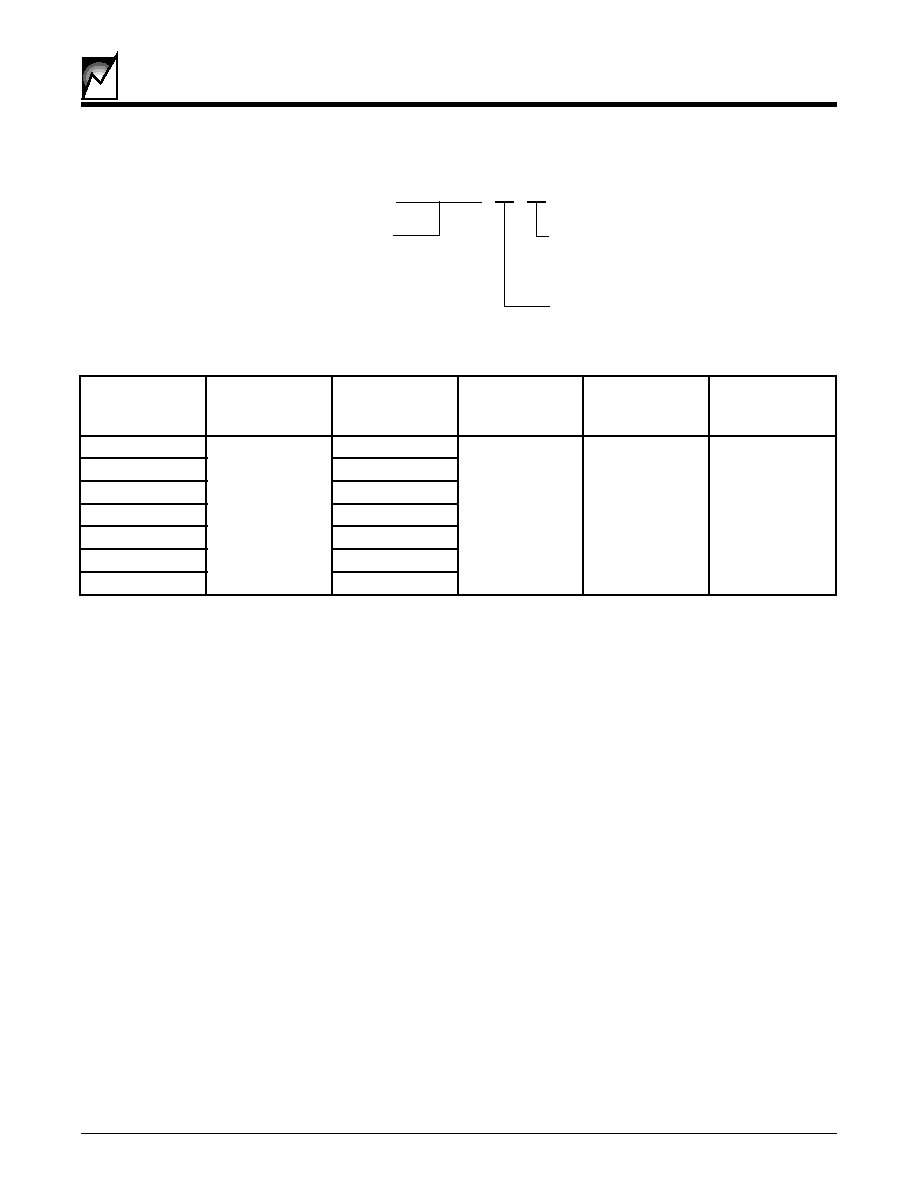

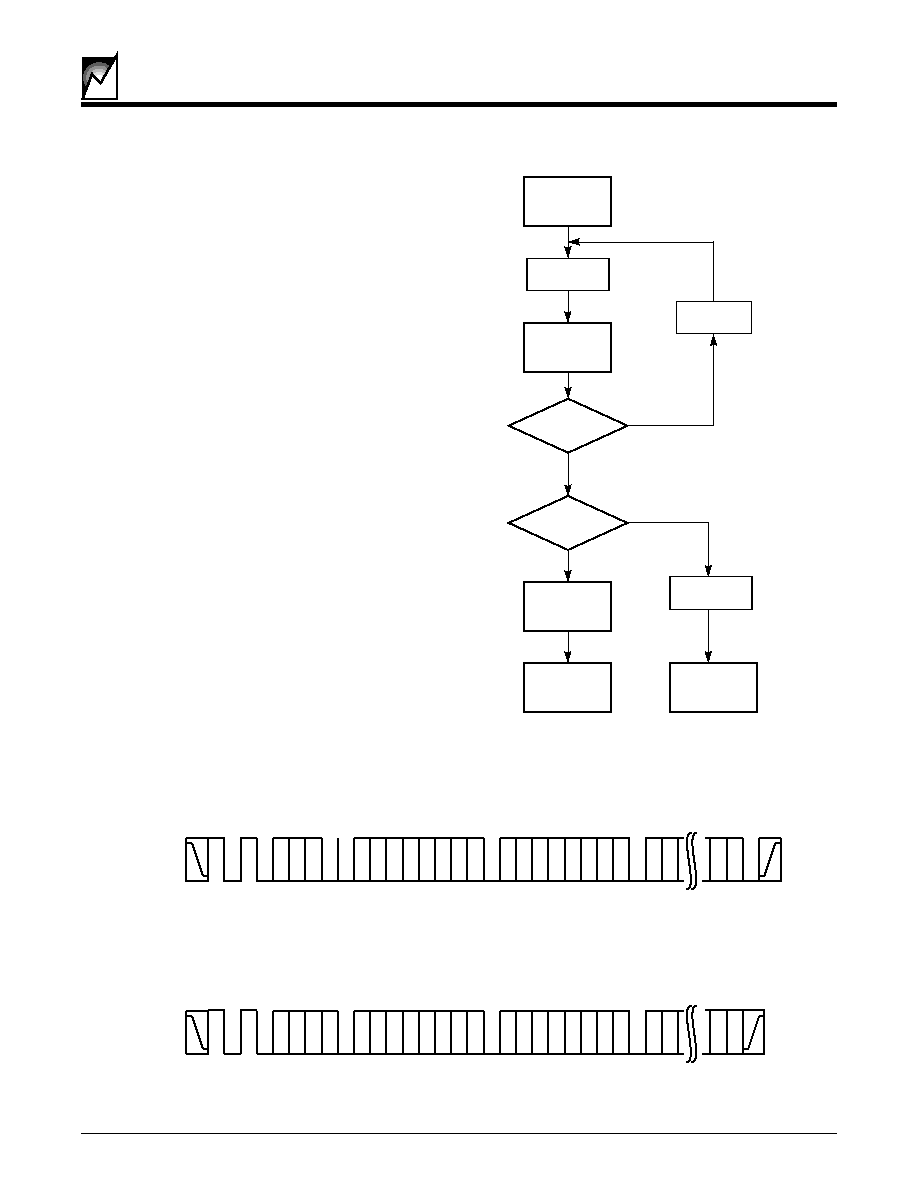

V

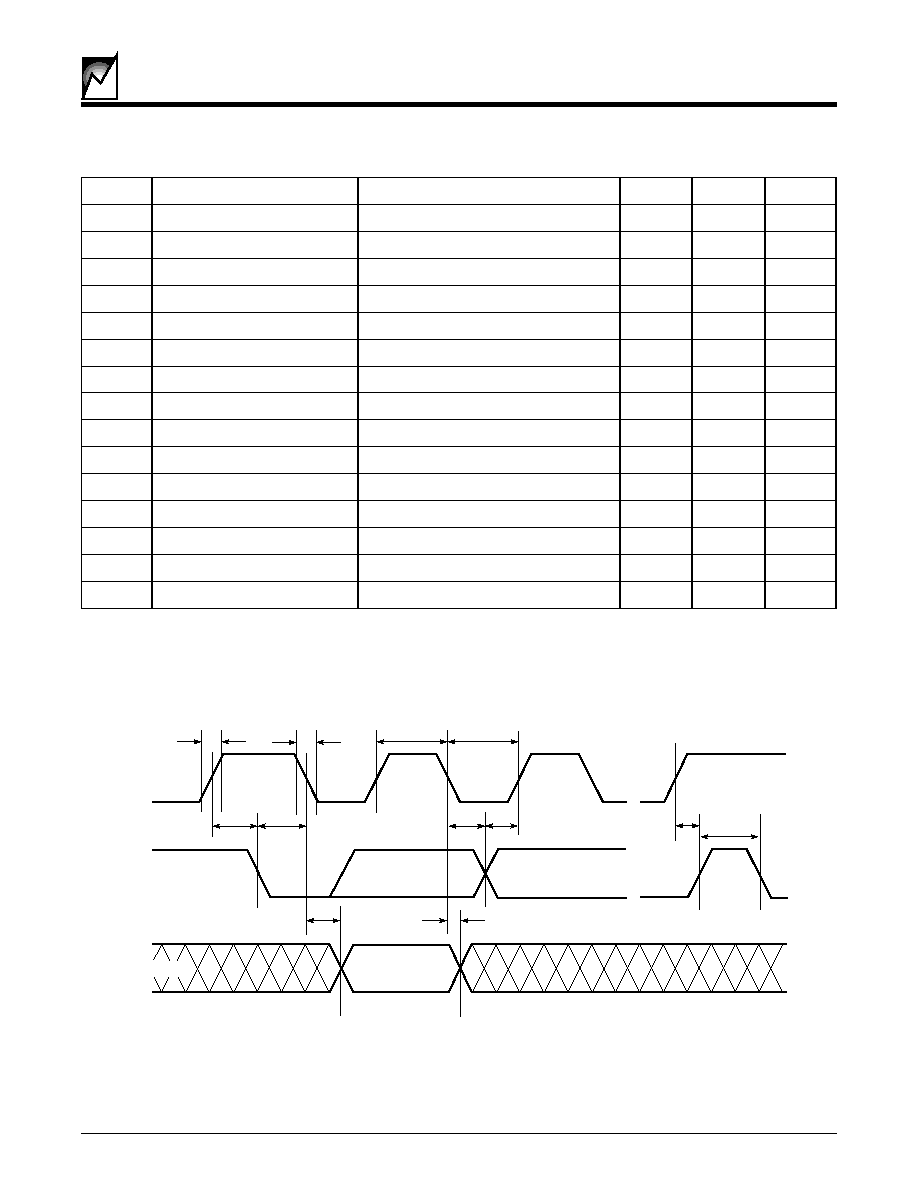

CC

RESET#

MR#

V

SENSE

V

RST

V

RST

t

RST

t

RST

t

RST

V

SNS

V

IL

V

IH

t

MR

2038 T Fig01 2.0

4

SMS1242

2038 2.0 6/8/00

SUMMIT MICROELECTRONICS, Inc.

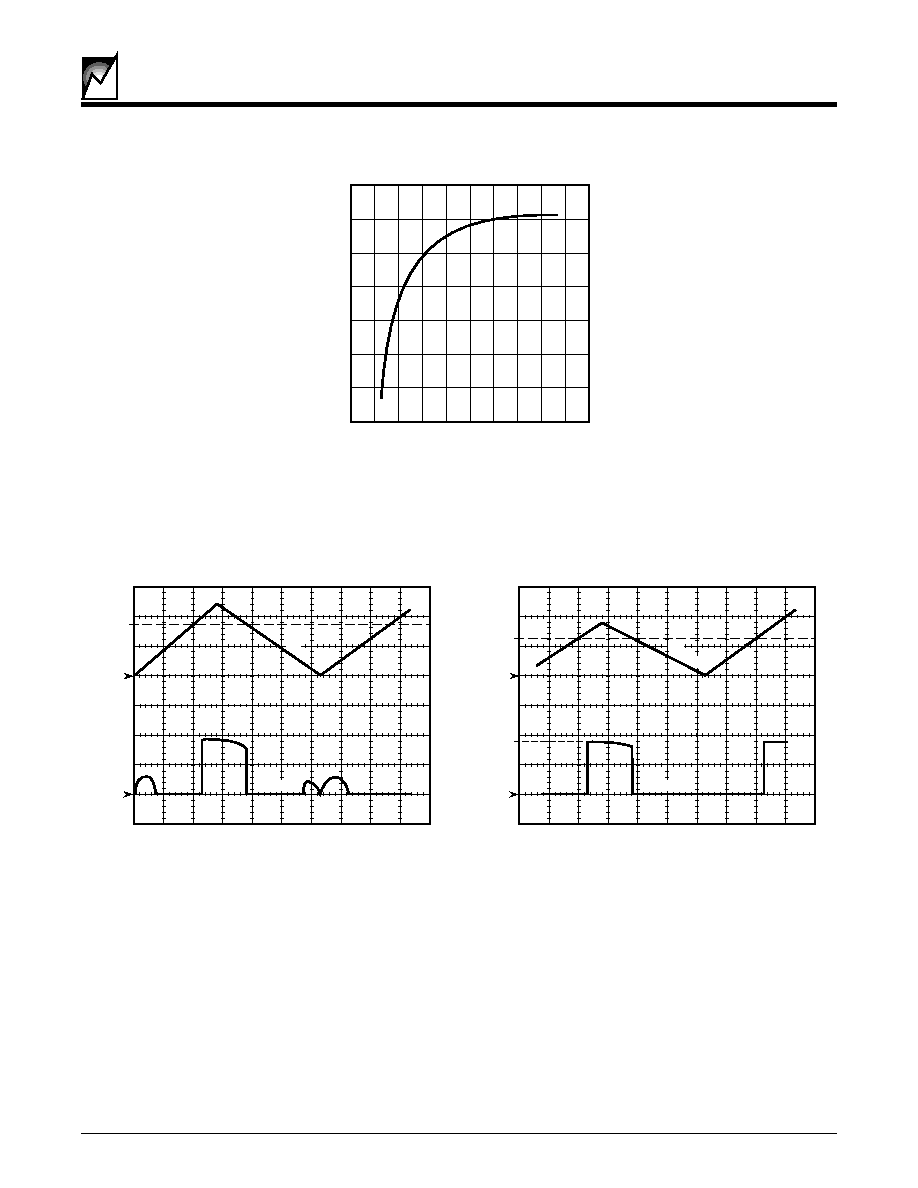

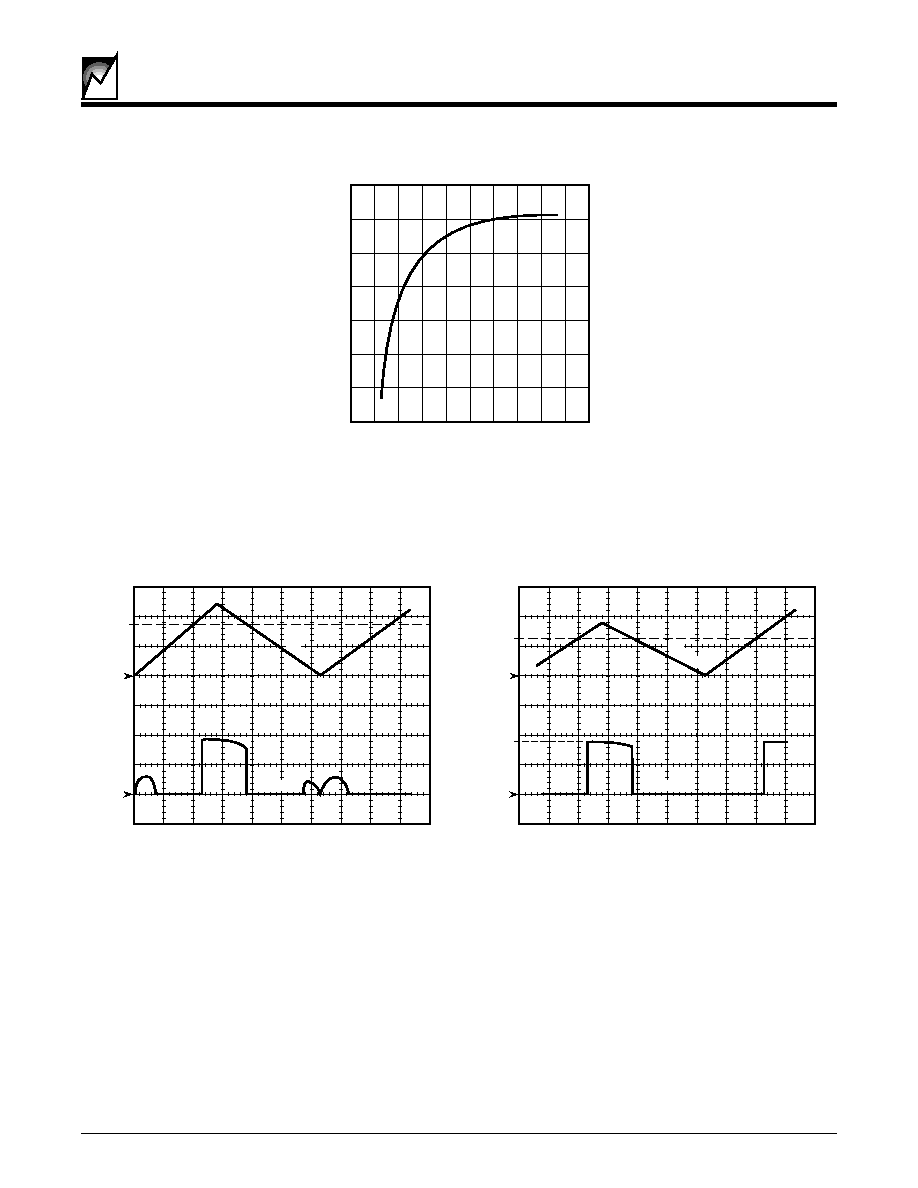

Figure 4. RESET Output vs. V

SENSE

Figure 3. RESET Output vs. Supply

Figure 2. Supply Voltage Noise Rejection, V

RST

=4.55V, T

A

= 25∫C

0

2

6

10

8

4

3

1

7

5

9

GLITCH AMPLITUDE (V)

PULSE WIDTH (ms)

4.5

4.4

4.3

4.2

4.1

4.0

3.9

3.8

2038 Fig02 2.0

V

RST

0V

0V

RESET#

V

CC

500ms/Div.

1.25V

0V

2V

0V

RESET#

V

SENSE

V

CC

5

2038 2.0 6/8/00

SMS1242

SUMMIT MICROELECTRONICS, Inc.

DEVICE OPERATION

The SMS1242 provides a precision reset function for a

microcontroller or microprocessor during power-up,

power-down and brown-out conditions. The device will

monitor two independent voltage supplies and will gener-

ate a reset condition when either supply is invalid. It is

configured with two outputs, both driven by the same

conditions. They are open drain and will track each other

but the outputs are not internally tied together.

Because RESET1# and RESET2# are essentially open

drain outputs (RESET1# has a weak internal pullup,

RESET2# does not) they can be independently driven low

by external signals. This can be very useful in a dual

processor system or in a combined processor/ASIC sys-

tem where, either for system operation or system test, the

processors or ASICs must be independently held in reset

without resetting the other portion of the system.

SUPPLY MONITOR

(Assume V

SENSE

> V

SNS

) During power-up the SMS1242

monitors the supply voltage. The RESET1# and RE-

SET2# outputs are guaranteed to be driven low once V

CC

reaches 1V. As V

CC

rises RESET1# and RESET2#

remain asserted until V

CC

reaches the V

RST

threshold. As

V

CC

passes through V

RST

an internal timer is started to

continue driving the outputs for an additional 150ms

(nominal).

If a power-fail or brown-out condition occurs (V

CC

< V

RST

)

RESET1# and RESET2# will be asserted. They will

remain active so long as V

CC

is below V

RST

. Because the

internal timer will be continuously reset so long as V

CC

is

below V

RST

, a brownout condition that interrupts a previ-

ously initiated reset pulse causes an additional reset delay

from the time the V

CC

passes back through V

RST

.

During power down conditions, once V

CC

drops below

V

RST

, RESET1# and RESET2# are guaranteed to be

asserted for V

CC

1V.

V

SENSE

MONITOR

(Assume V

CC

is >V

RST

) The SMS1242 continuously

monitors the VSENSE input. The RESET1# and RE-

SET2# outputs will be driven low so long as V

SENSE

is <

VSNS. As V

SENSE

passes through V

SNS

an internal timer

is started to continue driving the outputs for an additional

150ms (nom.).

If a power-fail condition occurs (V

SENSE

falls below V

SNS

)

RESET1# and RESET2# will be asserted. They will re-

main active so long as V

SENSE

is below V

SNS

. Because

the internal timer will be continuously reset so long as

V

SENSE

is below V

SNS

, a brownout condition that inter-

rupts a previously initiated reset pulse causes an addi-

tional reset delay from the time V

SENSE

becomes greater

than V

SNS

.

MANUAL RESET

The manual reset input allows RESET1# and RESET2# to

be activated by a pushbutton switch. The switch is

effectively debounced by the 100ms minimum t

RST

(RE-

SET pulse width). MR# can also be driven by an external

logic input that meets the 50ns minimum pulse width

required.

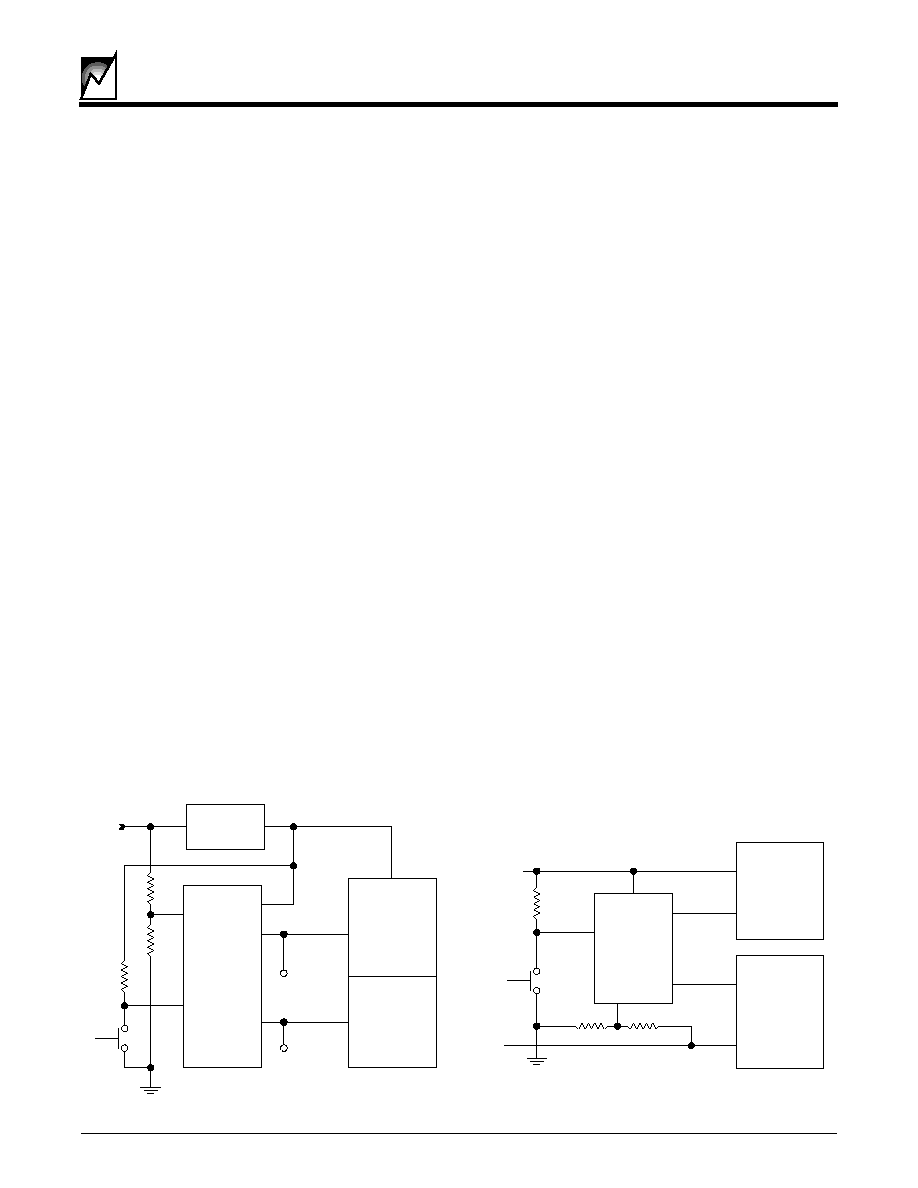

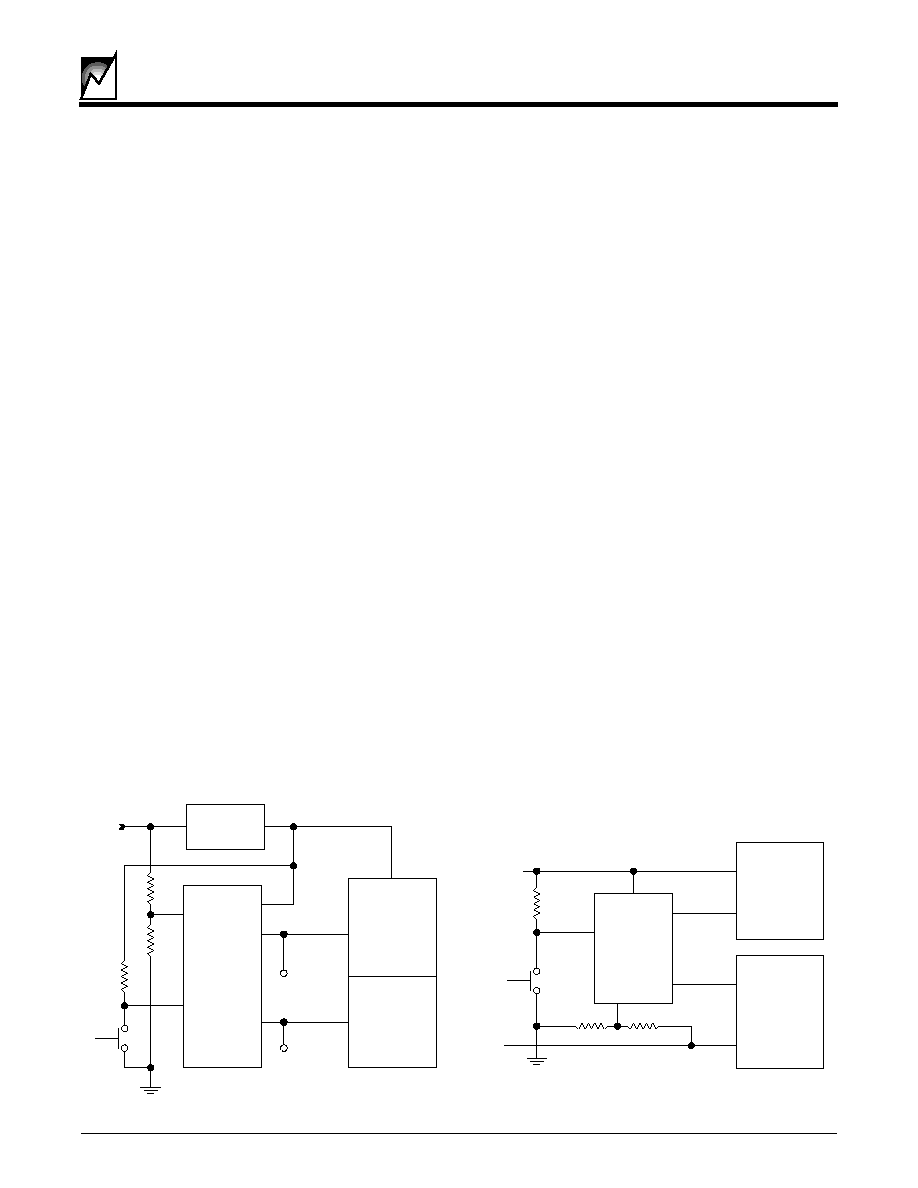

MCU #1

ASIC or MCU #2

RESET2#

RESET1#

VCC

Unregulated

+12V DC

DC to DC

Converter

3.3V Out

VSENSE

MR#

Test Point #1

Test Point #2

SMS1242

2038 ILL7.0

MCU

Low Voltage

High Speed

ASIC

RESET2#

RESET1#

VCC

3.3V

VSENSE

MR#

SMS1242

1.8V

2038 ILL8.0

Figure 5. Typical Multi-MCU Implementation

Figure 6. Typical Dual Voltage Implementation

6

SMS1242

2038 2.0 6/8/00

SUMMIT MICROELECTRONICS, Inc.

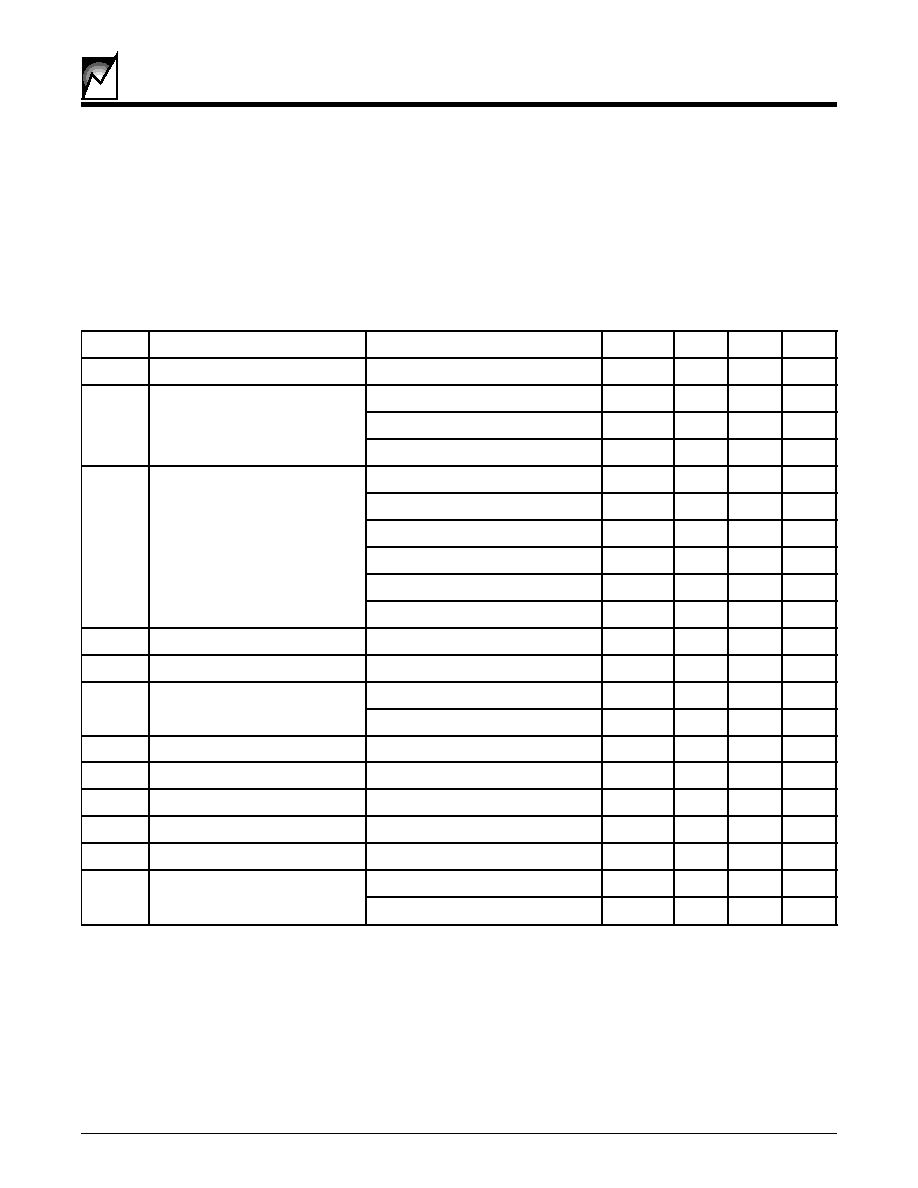

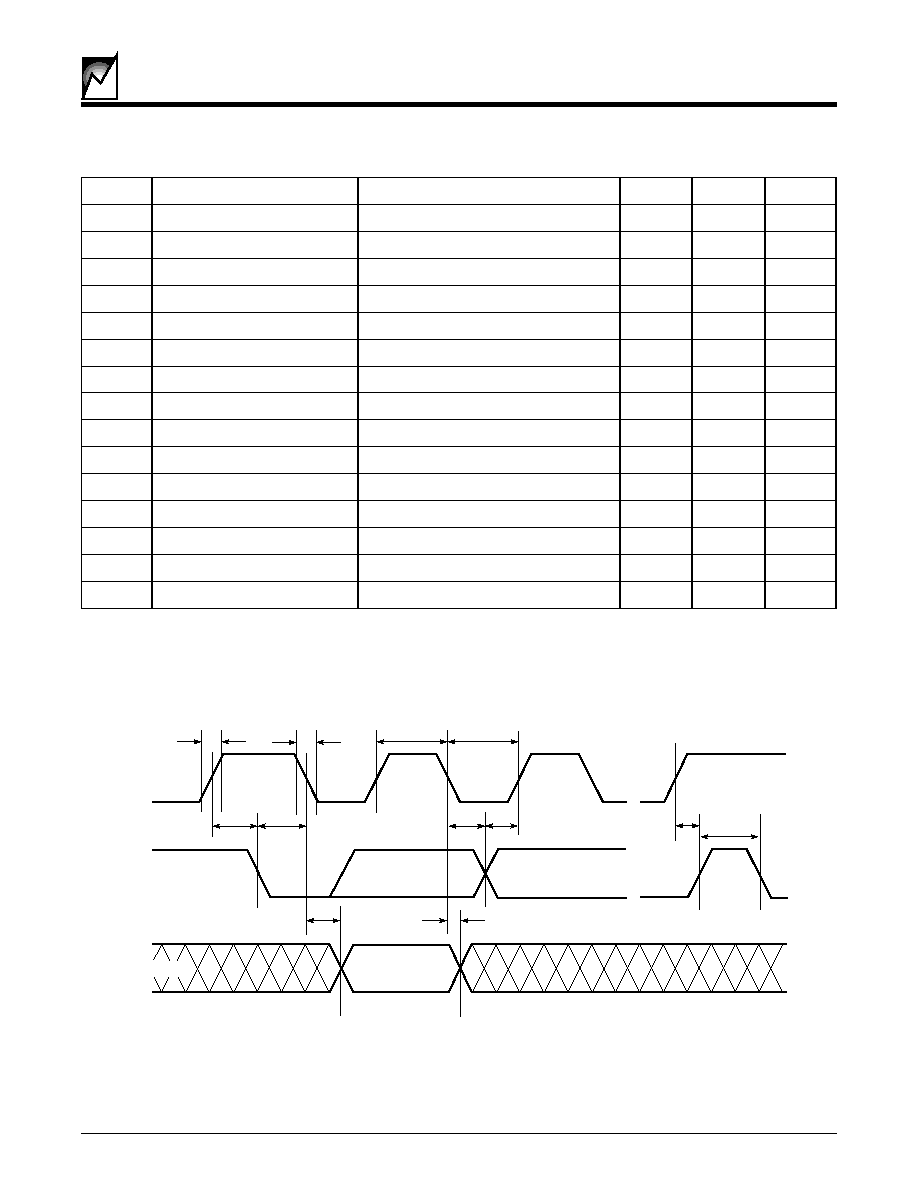

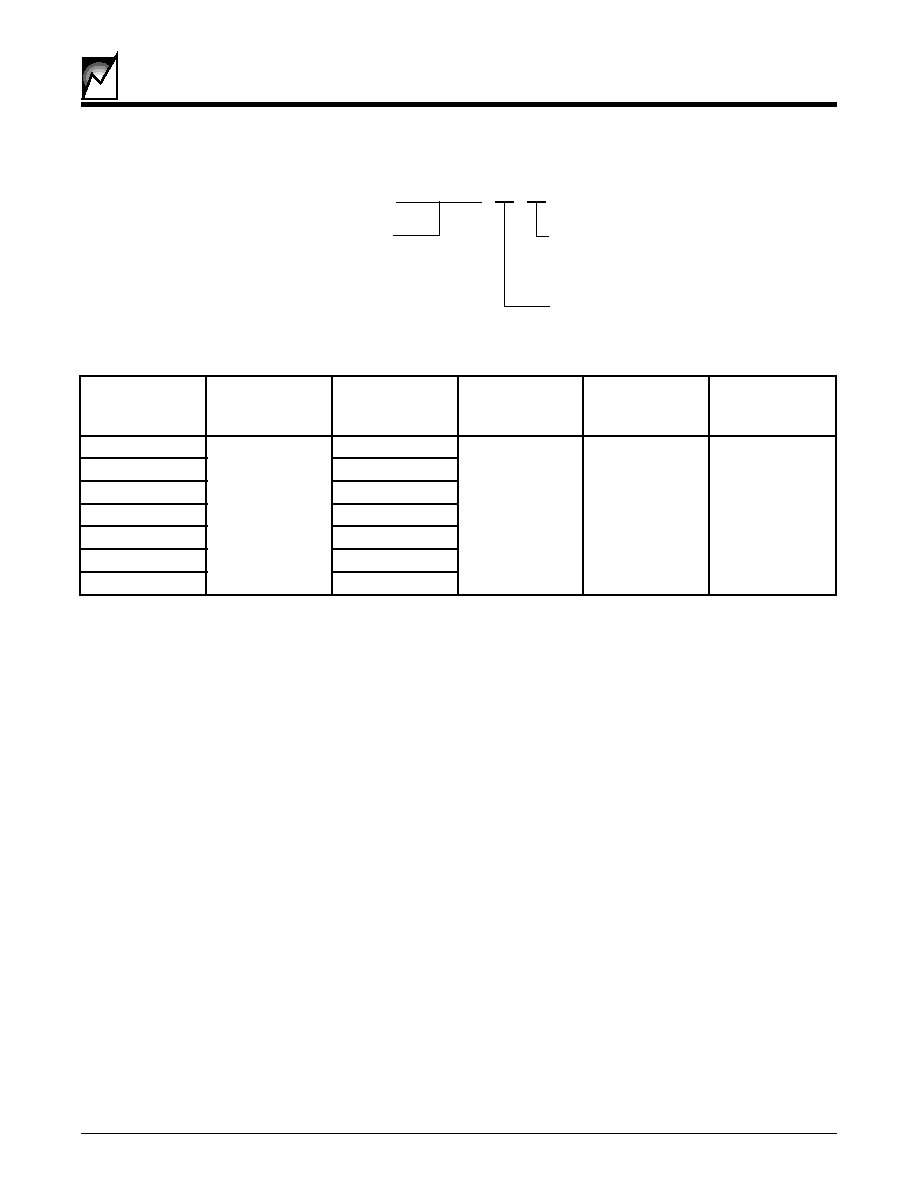

2038 Table01 2.0

Figure 7. Memory Timing

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

.

n

i

M

.

x

a

M

s

t

i

n

U

f

L

C

S

y

c

n

e

u

q

e

r

f

k

c

o

l

c

L

C

S

0

0

0

1

z

H

k

t

W

O

L

d

o

i

r

e

p

w

o

l

k

c

o

l

C

7

.

4

s

µ

t

H

G

I

H

d

o

i

r

e

p

h

g

i

h

k

c

o

l

C

0

.

4

s

µ

t

F

U

B

e

m

i

t

e

e

r

f

s

u

B

n

o

i

s

s

i

m

s

n

a

r

t

w

e

n

e

r

o

f

e

B

7

.

4

s

µ

t

A

T

S

:

U

S

e

m

i

t

p

u

t

e

s

n

o

i

t

i

d

n

o

c

t

r

a

t

S

7

.

4

s

µ

t

A

T

S

:

D

H

e

m

i

t

d

l

o

h

n

o

i

t

i

d

n

o

c

t

r

a

t

S

0

.

4

s

µ

t

O

T

S

:

U

S

e

m

i

t

p

u

t

e

s

n

o

i

t

i

d

n

o

c

p

o

t

S

7

.

4

s

µ

t

A

A

t

u

p

t

u

o

d

il

a

v

o

t

e

g

d

e

k

c

o

l

C

)

n

e

l

c

y

c

(

A

D

S

d

il

a

v

o

t

w

o

l

L

C

S

3

.

0

5

.

3

s

µ

t

H

D

e

m

i

t

d

l

o

h

t

u

O

a

t

a

D

e

g

n

a

h

c

A

D

S

o

t

)

1

+

n

e

l

c

y

c

(

w

o

l

L

C

S

3

.

0

s

µ

t

R

e

m

i

t

e

s

i

r

A

D

S

d

n

a

L

C

S

0

0

0

1

s

n

t

F

e

m

i

t

ll

a

f

A

D

S

d

n

a

L

C

S

0

0

3

s

n

t

T

A

D

:

U

S

e

m

i

t

p

u

t

e

s

n

I

a

t

a

D

0

5

2

s

n

t

T

A

D

:

D

H

e

m

i

t

d

l

o

h

n

I

a

t

a

D

0

s

n

I

T

A

D

S

d

n

a

L

C

S

r

e

t

li

f

e

s

i

o

N

n

o

i

s

e

r

p

p

u

s

e

s

i

o

N

0

0

1

s

n

t

R

W

e

m

i

t

e

l

c

y

c

e

t

i

r

W

5

s

m

tF

tR

tLOW

tHIGH

tHD:SDA

tSU:SDA

tBUF

tDH

tHD:DAT

tSU:DAT

tSU:STO

SCL

SDA In

SDA Out

tAA

2038 Fig07 2.0

7

2038 2.0 6/8/00

SMS1242

SUMMIT MICROELECTRONICS, Inc.

MEMORY OPERATION

The SMS1242 memory is configured as a 2k

◊

8 array.

Data is read and written via an industry standard two-wire

interface. The bus was designed for two-way, two-line

serial communication between different integrated cir-

cuits. The two lines are a serial data line (SDA) and a serial

clock line (SCL). The SDA line must be connected to a

positive supply by a pull-up resistor located somewhere on

the bus

Input Data Protocol

The protocol defines any device that sends data onto the

bus as a "transmitter" and any device that receives data as

a "receiver." The device controlling data transmission is

called the "master" and the controlled device is called the

"slave." In all cases the SMS1242 will be a "slave" device

since it never initiates a data transfer.

One data bit is transferred during each clock pulse. The

data on the SDA line must remain stable during clock high

time, because changes on the data line while SCL is high

will be interpreted as start or stop condition.

START and STOP Conditions

When both the data and clock lines are high the bus is said

to be not busy. A high-to-low transition on the data line

while the clock is high is defined as the "START" condition.

A low-to-high transition on the data line while the clock is

high is defined as the "STOP" condition.

Acknowledge (ACK)

Acknowledge is a software convention used to indicate

successful data transfers. The transmitting device, either

the master or the slave, will release the bus after transmit-

ting eight bits. During the ninth clock cycle the receiver will

pull the SDA line low to ACKnowledge that it received the

eight bits of data.

The SMS1242 will respond with an ACKnowledge after

recognition of a START condition and its slave address

byte. If both the device and a write operation are selected,

the SMS1242 will respond with an ACKnowledge after the

receipt of each subsequent 8-bit word. In the READ mode

the SMS1242 transmits eight bits of data, then releases

the SDA line, and monitors the line for an ACKnowledge

signal. If an ACKnowledge is detected and no STOP

condition is generated by the master, the SMS1242 will

continue to transmit data. If an ACKnowledge is not

detected the SMS1242 will terminate further data trans-

missions and await a STOP condition before returning to

the standby power mode.

Device Addressing

Following a start condition the master must output the

address of the slave it is accessing. The most significant

four bits of the slave address are the device type identifier.

For the SMS1242 this is fixed as 1010

BIN

. The next three

bits are the Most Significant Bits of the data address. They

are supplied for write operations, and are "don't care" for

read operations.

Read/Write Bit

The last bit of the data stream defines the operation to be

performed. A "1" indicates a read operation; and a "0," a

write operation.

2038 Table02 2.0

r

e

i

f

i

t

n

e

d

I

e

c

i

v

e

D

s

t

i

B

s

s

e

r

d

d

A

S

M

W

/

R

1

0

1

0

0

1

A

9

A

8

A

0

/

1

WRITE OPERATIONS

The SMS1242 allows two types of write operations: byte

write and page write. A byte write operation writes a single

byte during the nonvolatile write period (tWR). The page

write operation allows up to 16 bytes in the same page to

be written during t

WR

.

Byte Write

Upon receipt of the word address the SMS1242 responds

with an ACKnowledge. After receiving the next byte of

data it responds with another ACKnowledge. The master

then terminates the transfer by generating a STOP condi-

tion, at which time the SMS1242 begins the internal write

cycle. While the internal write cycle is in progress the

SMS1242 inputs are disabled and the device will not

respond to any requests from the master.

Page Write

The SMS1242 is capable of a 16-byte page write opera-

tion. It is initiated in the same manner as the byte-write

operation, but instead of terminating the write cycle after

the first data word the master can transmit up to 15 more

bytes of data. After the receipt of each byte the SMS1242

will respond with an ACKnowledge.

The SMS1242 automatically increments the address for

subsequent data words. After the receipt of each word, the

low order address bits are internally incremented by one.

The high order bits of the address byte remain constant.

8

SMS1242

2038 2.0 6/8/00

SUMMIT MICROELECTRONICS, Inc.

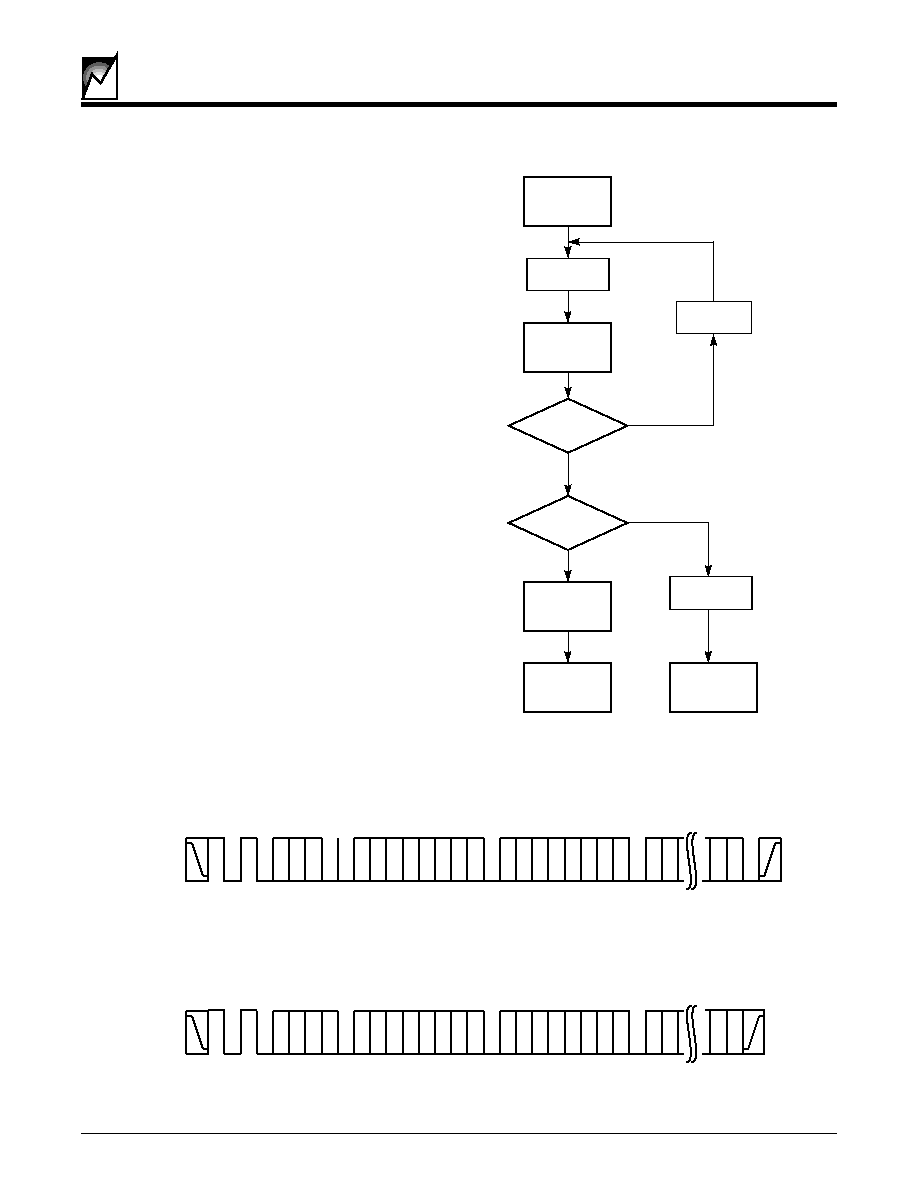

Next

Operation

a Write?

ACK

Returned

Issue

Address

Proceed

With

Write

Await

Next

Command

Issue Stop

Issue Slave

Address and

R/W = 0

Issue Stop

Write Cycle

In Progress

Yes

No

Issue Start

2038 Flow01 2.0

Yes

No

Should the master transmit more than 16 bytes, prior to

generating the STOP condition, the address counter will

"roll over" and the previously written data will be overwrit-

ten. As with the byte-write operation, all inputs are

disabled during the internal write cycle. Refer to Figure 8

for the address, ACKnowledge and data transfer se-

quence.

Acknowledge Polling

When the SMS1242 is performing an internal WRITE

operation it will ignore any new START conditions. Since

the device will only return an acknowledge after it accepts

the START, the part can be continuously queried until an

acknowledge is issued, indicating that the internal WRITE

cycle is complete. See the flow diagram for the proper

sequence of operations for polling.

READ OPERATIONS

Read operations are initiated with the R/W bit of the

identification field set to "1." There are two different read

options:

1. Current Address Byte Read

2. Random Address Byte Read

Current Address Read

The SMS1242 contains an internal address counter which

maintains the address of the last word accessed, incre-

mented by one. If the last address accessed (either a read

Figure 8. Memory Operation

A

C

K

X

X

X

R

/

W

A

C

K

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

A

C

K

D

7

D

6

D

1

D

0

S

T

O

P

S

T

A

R

T

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

S

T

A

R

T

A

C

K

R

/

W

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

A

C

K

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

A

C

K

D

7

D

6

D

1

D

0

A

C

K

S

T

O

P

Typical Write Operation

Typical Read Operation

Master

SDA

Slave

Master

SDA

Slave

2038 T Fig08 2.0

A

1

0

A

9

A

8

MEMORY OPERATION

(Continued)

9

2038 2.0 6/8/00

SMS1242

SUMMIT MICROELECTRONICS, Inc.

or write) was to address location n, the next read operation

would access data from address location n+1 and incre-

ment the current address pointer. When the SMS1242

receives the slave address field with the R/W bit set to "1"

it issues an acknowledge and transmits the 8-bit word

stored at address location n+1. The current address byte

read operation only accesses a single byte of data. The

master does not acknowledge the transfer, but does

generate a stop condition. At this point, the SMS1242

discontinues data transmission.

Random Address Read

Random address read operations allow the master to

access any memory location in a random fashion. This

operation involves a two-step process. First, the master

issues a write command which includes the start condition

and the slave address field (with the R/W bit set to WRITE),

followed by the address of the word it is to read. This

procedure sets the internal address counter of the

SMS1242 to the desired address. After the word address

acknowledge is received by the master it immediately

reissues a start condition followed by another slave ad-

dress field with the R/W bit set to READ. The SMS1242

will respond with an acknowledge and then transmit the 8-

data bits stored at the addressed location. At this point, the

master does not acknowledge the transmission but does

generate the stop condition. The SMS1242 discontinues

data transmission and reverts to its standby power mode.

Sequential READ

Sequential reads can be initiated as either a current

address READ or a random access READ. The first word

is transmitted as with the other byte read modes (current

address byte READ or random address byte READ);

however, the master now responds with an ACKnowl-

edge, indicating that it requires additional data from the

SMS1242. The SMS1242 continues to output data for

each ACKnowledge received. The master terminates the

sequential READ operation by not responding with an

ACKnowledge, and issues a STOP condition. During a

sequential read operation, the internal address counter is

automatically incremented with each ACKnowledge sig-

nal. For read operations, all address bits are incremented,

allowing the entire array to be read using a single read

command. After a count of the last memory address, the

address counter will roll-over, and the memory will con-

tinue to output data.

10

SMS1242

2038 2.0 6/8/00

SUMMIT MICROELECTRONICS, Inc.

ORDERING INFORMATION

SMS1242

S

A

Base Part Number

Option

See Option Table

Package

S = SOIC

2038 Option Table 2.0

Table 3. Order Options

r

e

b

m

u

N

t

r

a

P

g

n

i

t

a

r

e

p

O

e

g

a

t

l

o

V

V

T

S

R

V

S

N

S

g

n

i

t

a

r

e

p

O

e

r

u

t

a

r

e

p

m

e

T

e

g

n

a

R

&

t

n

u

o

C

d

a

e

L

e

l

y

t

S

e

g

a

k

c

a

P

A

-

S

2

4

2

1

S

M

S

V

5

.

5

o

t

V

1

5

2

4

.

4

V

5

2

.

1

C

∫

5

8

o

t

C

∫

0

4

≠

C

I

O

S

n

i

P

8

B

-

S

2

4

2

1

S

M

S

5

7

4

.

4

C

-

S

2

4

2

1

S

M

S

6

7

6

.

4

D

-

S

2

4

2

1

S

M

S

0

5

4

.

4

E

-

S

2

4

2

1

S

M

S

0

5

6

.

2

F

-

S

2

4

2

1

S

M

S

0

5

9

.

2

*

-

S

2

4

2

1

S

M

S

*

G

O

R

P

11

2038 2.0 6/8/00

SMS1242

SUMMIT MICROELECTRONICS, Inc.

NOTICE

SUMMIT Microelectronics, Inc. reserves the right to make changes to the products contained in this publication in order to improve

design, performance or reliability. SUMMIT Microelectronics, Inc. assumes no responsibility for the use of any circuits described

herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent

infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon

a user's specific application. While the information in this publication has been carefully checked, SUMMIT Microelectronics, Inc.

shall not be liable for any damages arising as a result of any error or omission.

SUMMIT Microelectronics, Inc. does not recommend the use of any of its products in life support applications where the failure or

malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety

or effectiveness. Products are not authorized for use in such applications unless SUMMIT Microelectronics, Inc. receives written

assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and

(c) potential liability of SUMMIT Microelectronics, Inc. is adequately protected under the circumstances.

© Copyright 2000 SUMMIT Microelectronics, Inc.

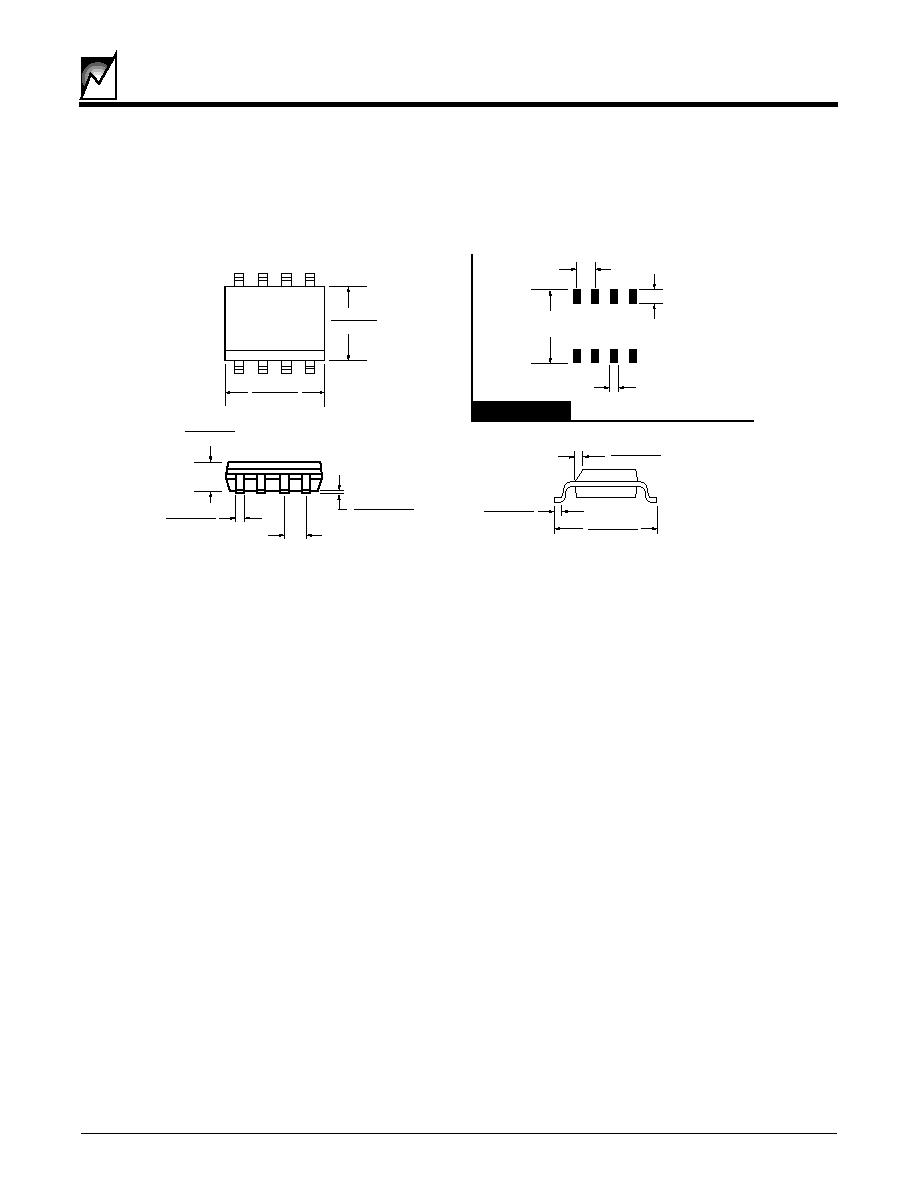

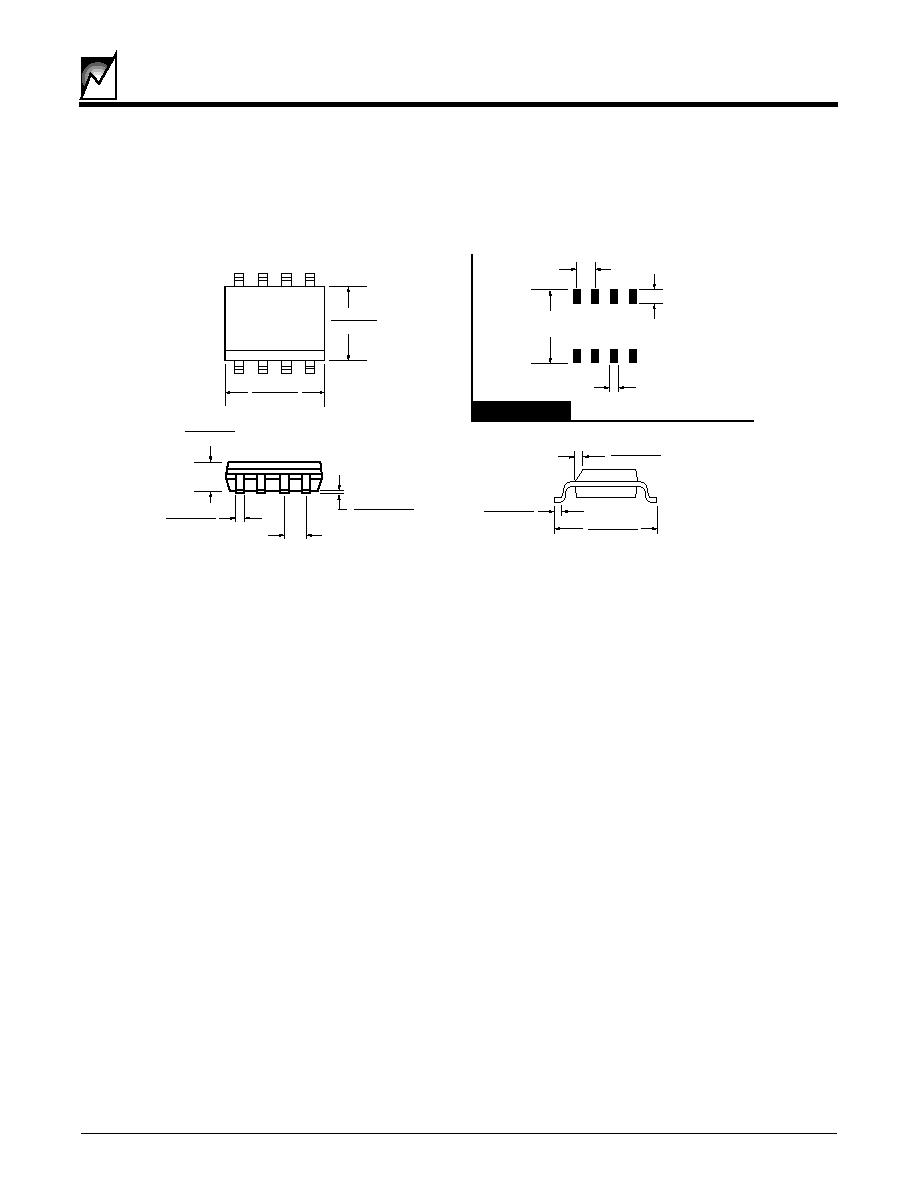

.228 (5.80)

.244 (6.20)

.016 (.40)

.035 (.90)

.020 (.50)

.010 (.25)

x45

∞

.0192 (.49)

.0138 (.35)

.061 (1.75)

.053 (1.35)

.0098 (.25)

.004 (.127)

.05 (1.27) TYP.

.275 (6.99) TYP.

.030 (.762) TYP.

8 Places

.050 (1.27) TYP.

.050 (1.270) TYP.

8 Places

.157 (4.00)

.150 (3.80)

.196 (5.00)

1

.189 (4.80)

FOOTPRINT

8pn JEDEC SOIC ILL.2

8 Pin SOIC (Type S) Package JEDEC (150 mil body width)

PACKAGE