| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HV2201 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Supertex inc.

Supertex inc.

∑

1235 Bordeaux Drive, Sunnyvale, CA 94089

∑

Tel: (408) 222-8888

∑

FAX: (408) 222-4895

∑

www.supertex.com

1

NR032106

HV2201

Initial Release

Low Charge Injection 8-Channel

Enhanced High Voltage Analog Switch

Features

HVCMOS technology for high performance

8 Channels of high voltage analog switch

3.3V or 5V CMOS input logic level

20MHz data shift clock frequency

Very low quiescent power dissipation-10µA

Low parasitic capacitance

DC to 10MHz analog signal frequency

-60dB typical off-isolation at 5MHz

CMOS logic circuitry for low power

Excellent noise immunity

Cascadable serial data register with latches

Flexible operating supply voltages

Applications

Medical ultrasound imaging

NDT metal fl aw detection

Piezoelectric transducer drivers

Inkjet printer heads

Optical MEMS modules

General Description

The Supertex HV2201 is a low charge injection, 8-channel,

high voltage analog switch integrated circuit (IC). The

device can be used in applications requiring high voltage

switching controlled by low voltage control signals, such as

medical ultrasound imaging, piezoelectric transducer drivers,

and printers. The HV2201 is an enhanced version of the

HV20220.

Input data is shifted into an 8-bit shift register that can then

be retained in an 8-bit latch. To reduce any possible clock

feed- through noise, the latch enable bar should be left high

until all bits are clocked in. Data is clocked in during the rising

edge of the clock. Using HVCMOS technology, this device

combines high voltage bilateral DMOS switches and low

power CMOS logic to provide effi cient control of high voltage

analog signals.

The device is suitable for various combinations of high

voltage supplies, e.g., V

PP

/V

NN

: +40V/-160V, +100V/-100V,

and +160V/-40V.

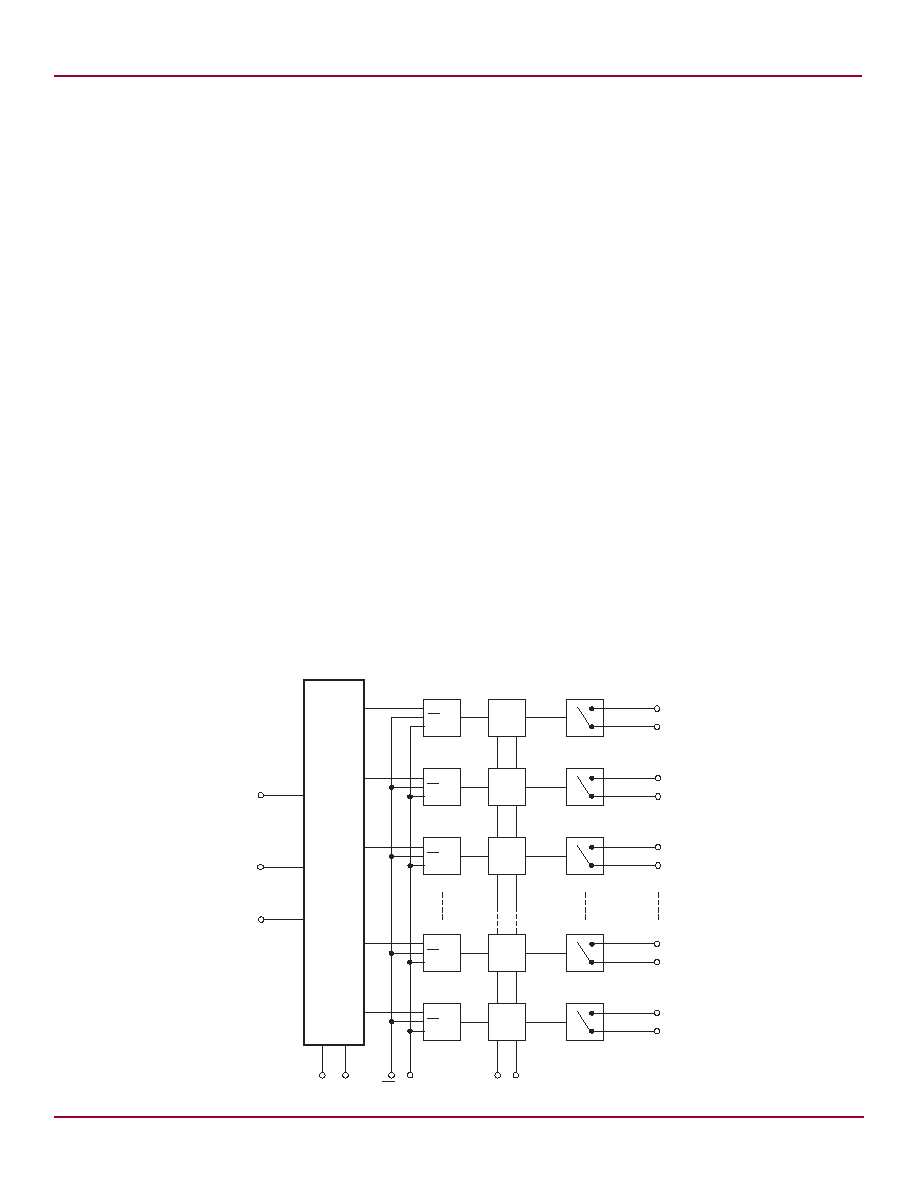

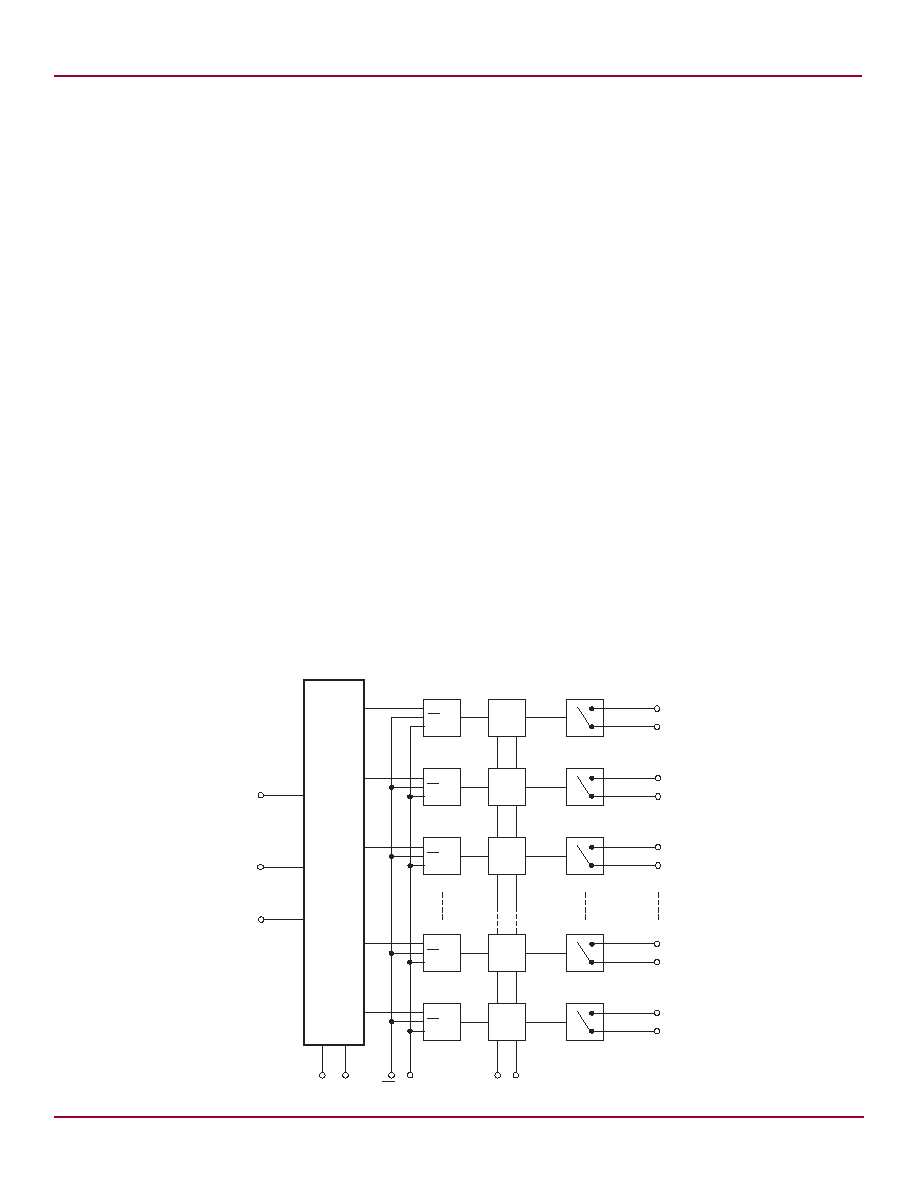

Block Diagram

D

LE

CL

SW0

D

LE

CL

SW1

D

LE

CL

SW2

D

LE

CL

SW6

D

LE

CL

SW7

CLK

8-BIT

SHIFT

REGISTER

D

IN

D

OUT

LATCHES

LEVEL

SHIFTERS

OUTPUT

SWITCHES

V

NN

LE CLR

V

DD

GND

V

PP

2

NR032106

HV2201

Ordering Information

Device

Package Options

48-Lead TQFP

28-Lead PLCC

32-Lead BCC

HV2201

HV2201FG-G

HV2201PJ-G

HV2201B1-G

-G indicates package is RoHS compliant (`Green')

Absolute Maximum Ratings

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation

under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect

device reliability. All voltages are referenced to device ground.

Parameter

Value

V

DD

logic supply

-0.5V to +7V

V

PP

-V

NN

differential supply

220V

V

PP

positive supply

-0.5V to V

NN

+200V

V

NN

negative supply

+0.5V to -200V

Logic input voltage

-0.5V to V

DD

+0.3V

Analog signal range

V

NN

to V

PP

Peak analog signal current/channel

3.0A

Storage temperature

-65∞C to 150∞C

Power dissipation:

48-Lead TQFP

28-Lead PLCC

32-Lead BCC

1.0W

1.2W

1.0W

Operating Conditions

Symbol

Parameter

Value

V

DD

Logic power supply voltage

3.0V to 5.5V

V

PP

positive high voltage supply

40V to V

NN

+200V

V

NN

negative high voltage supply

-40V to -160V

V

IH

High level input voltage

0.9V to V

DD

V

IL

Low-level input voltage

0V to 0.1V

V

SIG

Analog signal voltage peak-to-peak

V

NN

+10V to V

PP

-10V

T

A

Operating free air temperature

0

O

C to 70

O

C

Notes:

1. Power up/down sequence is arbtrary except GND must be powered -up fi rst and powered down last.

2. V

SIG

must be V

NN

V

SIG

V

PP

or fl oating during power up/down transition.

3. Rise and fall times of power supplies V

DD

, V

PP

, and V

NN

should not be less than 1.0msec.

3

NR032106

HV2201

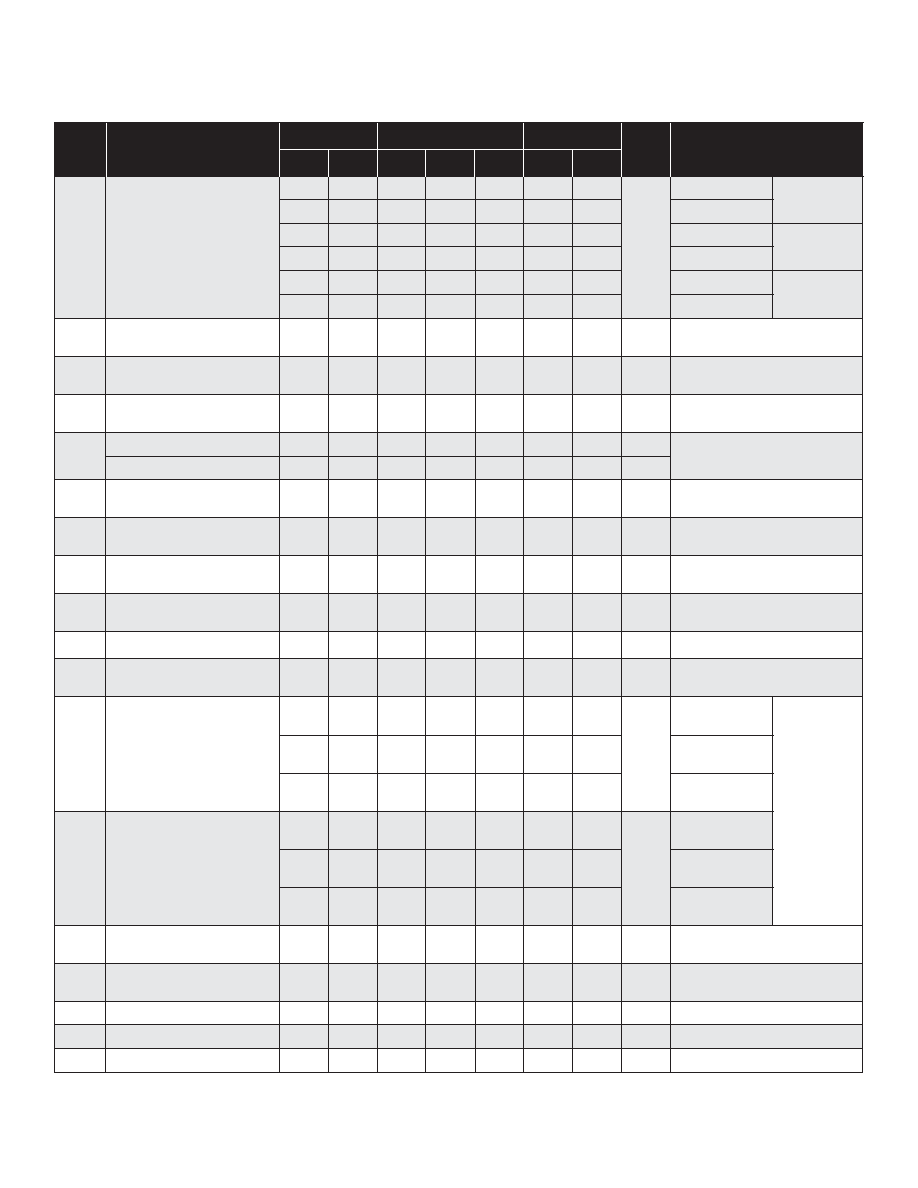

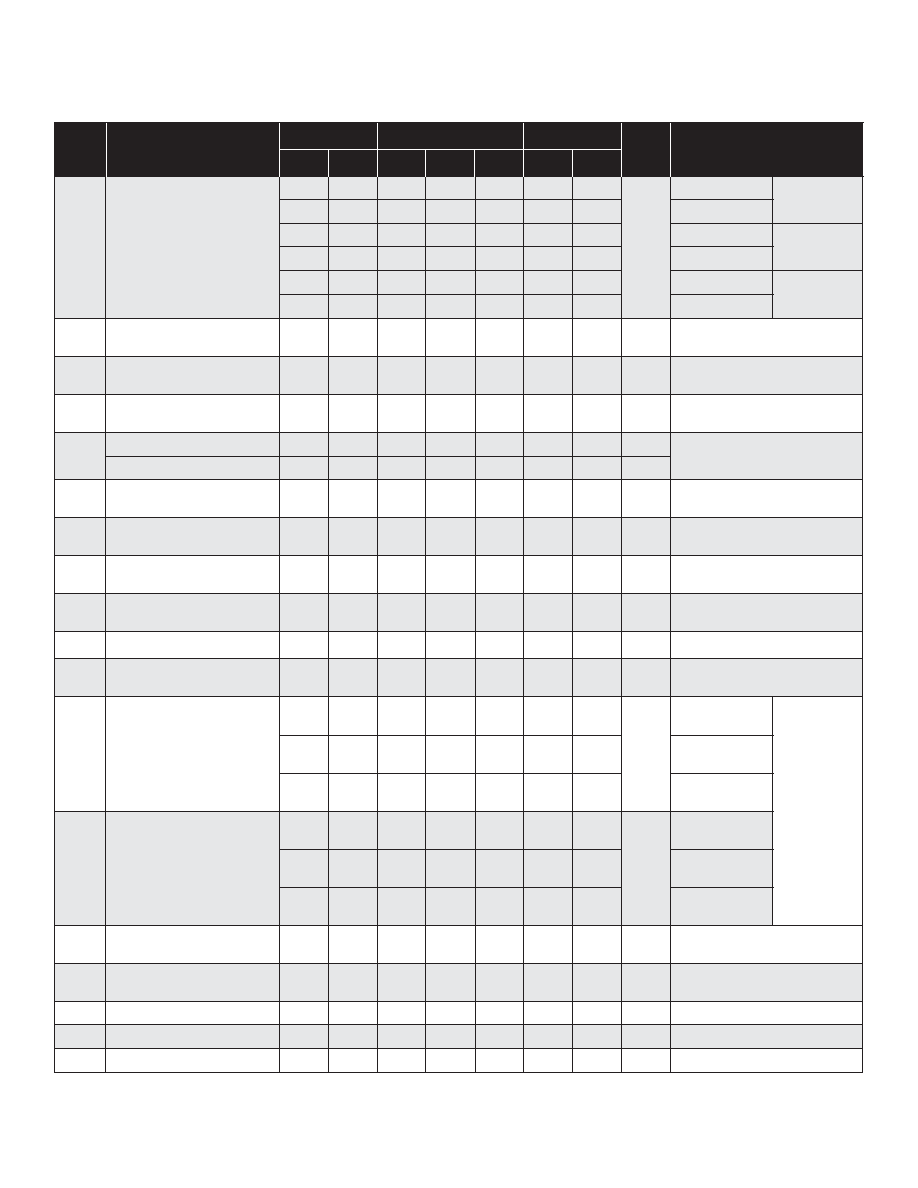

DC Electrical Characteristics

(Over operating conditions unless otherwise specifi ed )

R

ONS

Small signal switch

on-resistance

-

30

-

26

38

-

48

I

SIG

= 5mA

V

PP

= +40V

V

NN

= -160V

-

25

-

22

27

-

32

I

SIG

= 200mA

-

25

-

22

27

-

30

I

SIG

= 5mA

V

PP

= +100V

V

NN

= -100V

-

18

-

18

24

-

27

I

SIG

= 200mA

-

23

-

20

25

-

30

I

SIG

= 5mA

V

PP

= +160V

V

NN

= -40V

-

22

-

16

25

-

27

I

SIG

= 200mA

R

ONS

Small signal switch

on-resistance matching

-

20

-

5.0

20

-

20

%

I

SIG

= 5mA, V

PP

= +100V,

V

NN

= - 100V

R

ONL

Large signal switch

on-resistance

-

-

-

15

-

-

-

V

SIG

= V

PP

-10V, I

SIG

= 1A

I

SOL

Switch off leakage per

switch

-

5.0

-

1.0

10

-

15

A

V

SIG

= V

PP

-10V, V

NN

+10V

V

OS

DC offset switch off

-

300

-

100

300

-

300

mV

100k load

DC offset switch on

-

500

-

100

500

-

500

mV

I

PPQ

Quiescent V

PP

supply

current

-

-

-

10

50

-

-

A

All switches off

I

NNQ

Quiescent V

NN

supply

current

-

-

-

-10

-50

-

-

A

All switches off

I

PPQ

Quiescent V

PP

supply

current

-

-

-

10

50

-

-

A

All switches on, I

SW

= 5mA

I

NNQ

Quiescent V

NN

supply

current

-

-

-

-10

-50

-

-

A

All switches on, I

SW

= 5mA

I

SW

Switch output peak current

-

3.0

-

3.0

2.0

-

2.0

A

V

SIG

duty cycly < 0.1%

f

SW

Output switching

frequency

-

-

-

-

50

-

-

kHz

Duty cycle = 50%

I

PP

Average V

PP

supply current

-

4.0

-

-

5.0

-

5.5

mA

V

PP

= +40V

V

NN

= -160V

All output

switches are

turning On

and Off at

50kHz with

no load

-

3.5

-

-

3.5

-

3.5

V

PP

= +100V

V

NN

= -100V

-

3.5

-

-

3.5

-

4.0

V

PP

= +160V

V

NN

= -40V

I

NN

Average V

NN

supply curent

-

4.5

-

-

5.0

-

5.5

mA

V

PP

= +40V

V

NN

= -160V

-

3.5

-

-

3.5

-

3.5

V

PP

= +100V

V

NN

= -100V

-

3.5

-

-

3.5

-

4.0

V

PP

= +160V

V

NN

= -40V

I

DD

Average V

DD

supply cur-

rent

-

4.0

-

-

4.0

-

4.0

mA

f

CLK

= 5MHz, V

DD

= 5.0V

I

DDQ

Quiescent V

DD

supply

current

-

10

-

-

10

-

10

A

All logic inputs are static

I

SOR

Data out source current

0.45

-

0.45

0.70

-

0.40

-

mA

V

OUT

= V

DD

-0.7V

I

SINK

Data out sink current

0.45

-

0.45

0.70

-

0.40

-

mA

V

OUT

= 0.7V

C

IN

Logic input capacitance

-

10

-

-

10

-

10

pF

---

Sym

Parameter

0

O

C

+25

O

C

+70

O

C

Units

Conditions

Min

Max

Min

Typ

Max

Min

Max

4

NR032106

HV2201

Sym

Parameter

0

O

C

+25

O

C

+70

O

C

Units

Conditions

Min

Max

Min

Typ

Max

Min

Max

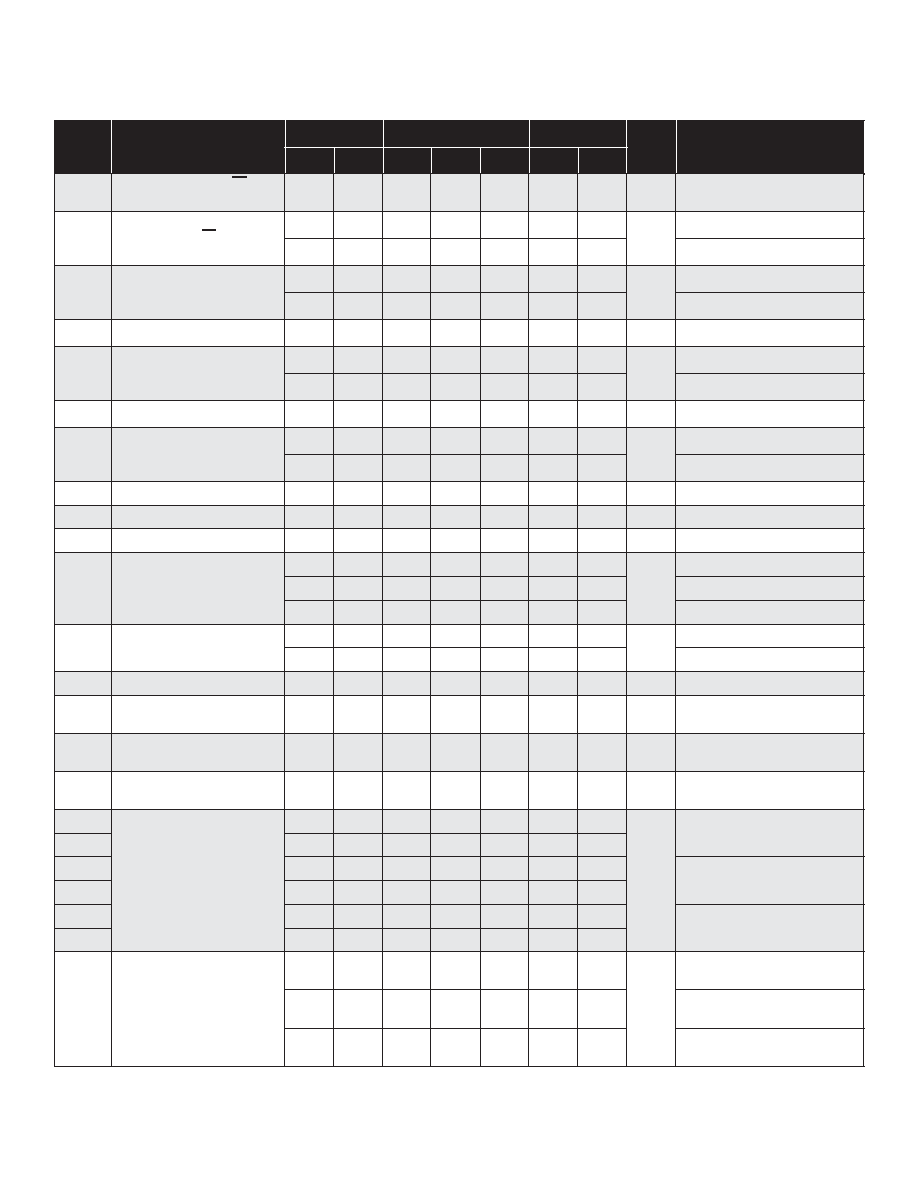

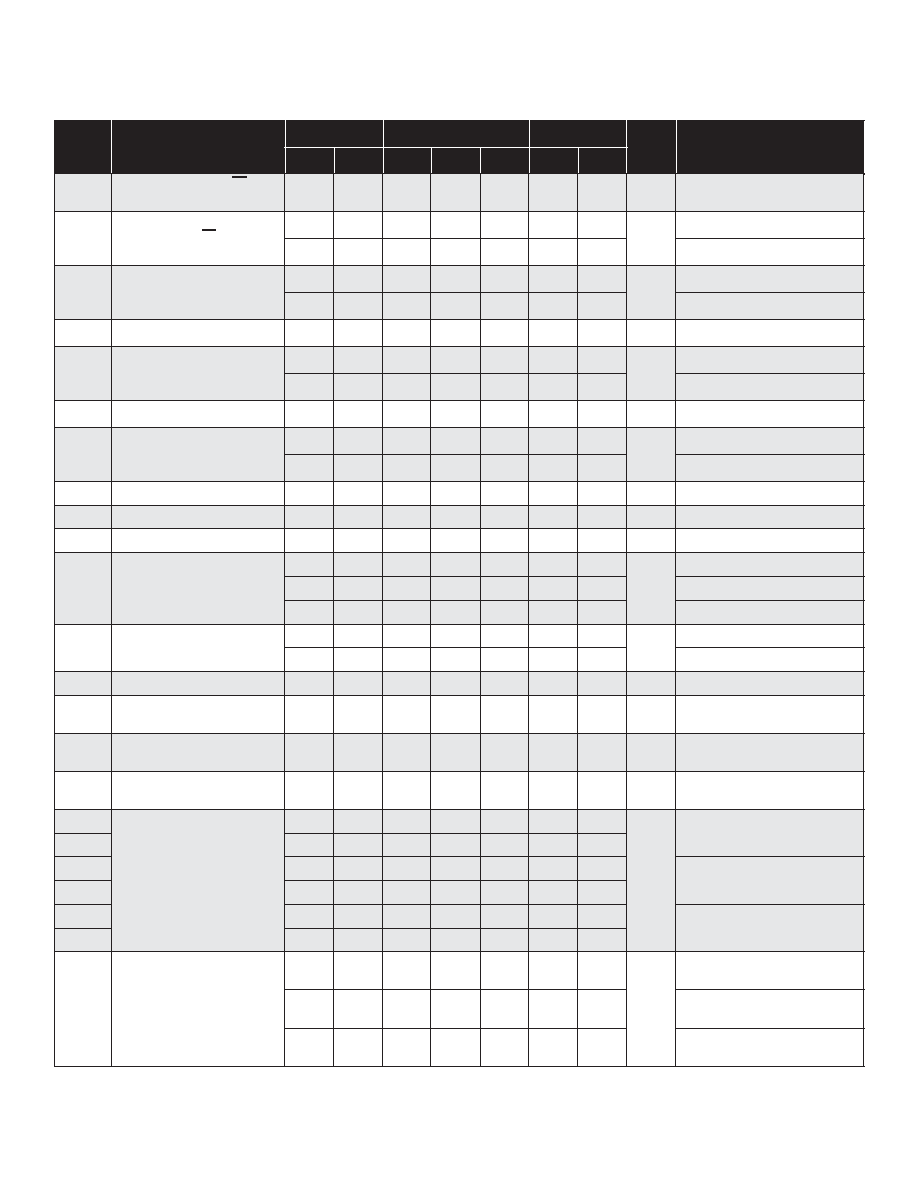

AC Electrical Characteristics

(Over recommended operating conditions: V

DD

= 5.0V, t

R

= t

F

5ns, 50% duty cycle, C

LOAD

= 20pF, unless otherwise specifi ed)

t

SD

Set up time before LE

rises

25

-

25

-

-

25

-

ns

---

t

WLE

Time width of LE

56

-

-

56

-

56

-

ns

V

DD

= 3.0V

12

-

-

12

-

12

-

V

DD

= 5.0V

t

DO

Clock delay time to data

out

-

120

-

95

140

-

167

ns

V

DD

= 3.0V

-

58

-

40

69

-

85

V

DD

= 5.0V

t

WCL

Time width of CL

55

-

55

-

-

55

-

ns

---

t

SU

Set up time data to clock

39

-

47

30

-

58

-

ns

V

DD

= 3.0V

16

-

21

10

-

26

-

V

DD

= 5.0V

t

H

Hold time data from clock

2

-

2

-

-

2

-

ns

V

DD

= 3.0 or 5.0V

f

CLK

Clock frequency

-

-

-

8

-

-

-

MHz

V

DD

= 3.0V

-

-

-

20

-

-

-

V

DD

= 5.0V

t

R

, t

F

Clock rise and fall times

-

50

-

50

-

50

ns

---

t

ON

Turn on time

-

5.0

-

-

5.0

-

5.0

s

V

SIG

= V

PP

-10V, R

LOAD

= 10k

t

OFF

Turn off time

-

5.0

-

-

5.0

-

5.0

s

V

SIG

= V

PP

-10V, R

LOAD

= 10k

dv/dt

Maximun V

SIG

slew rate

-

20

-

-

20

-

20

V/ns

V

PP

= +40V, V

NN

= -160V

-

20

-

-

20

-

20

V

PP

= +100V, V

NN

= -100V

-

20

-

-

20

-

20

V

PP

= +160V, V

NN

= -40V

K

O

Off isolation

-30

-

-30

-33

-

-30

-

dB

f = 5.0MHz, 1k/15pF load

-58

-

-58

-

-

-58

-

f = 5.0MHz, 50 load

K

CR

Switch crosstalk

-60

-

-60

-70

-

-60

-

dB

f = 5.0MHz, 50 load

I

ID

Output switch isolation

diode current

-

300

-

-

300

-

300

mA

300ns pulse width,

2.0% duty cycle

C

SG(OFF)

Off capacitance SW to

GND

5.0

17

5.0

12

17

5.0

17

pF

0V, f = 1.0MHz

C

SG(ON)

On capacitance SW to

GND

25

50

25

38

50

25

50

pF

0V, f = 1.0MHz

+V

SPK

Output voltage spike

-

-

-

-

150

-

-

mV

V

PP

= +40V, V

NN

= -160V,

R

LOAD

= 50

-V

SPK

-

-

-

-

150

-

-

+V

SPK

-

-

-

-

150

-

-

V

PP

= +100V, V

NN

= -100V,

R

LOAD

= 50

-V

SPK

-

-

-

-

150

-

-

+V

SPK

-

-

-

-

150

-

-

V

PP

= +160V, V

NN

= -40V,

R

LOAD

= 50

-V

SPK

-

-

-

-

150

-

-

QC

Charge injection

-

-

-

820

-

-

-

pC

V

PP

= +40V, V

NN

= -160V,

V

SIG

= 0V

-

-

-

600

-

-

-

V

PP

= +100V, V

NN

= -100V,

V

SIG

= 0V

-

-

-

350

-

-

-

V

PP

= +160V, V

NN

= -40V,

V

SIG

= 0V

5

NR032106

HV2201

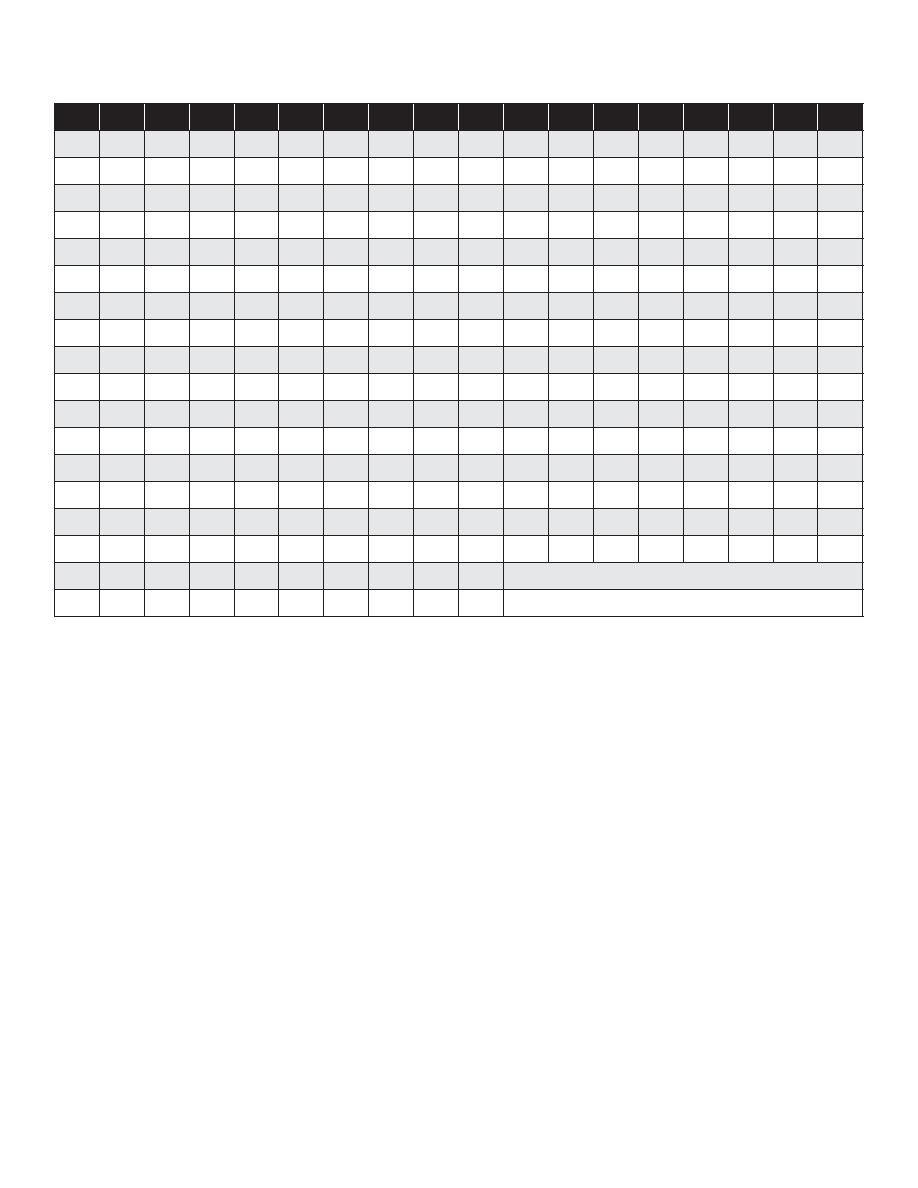

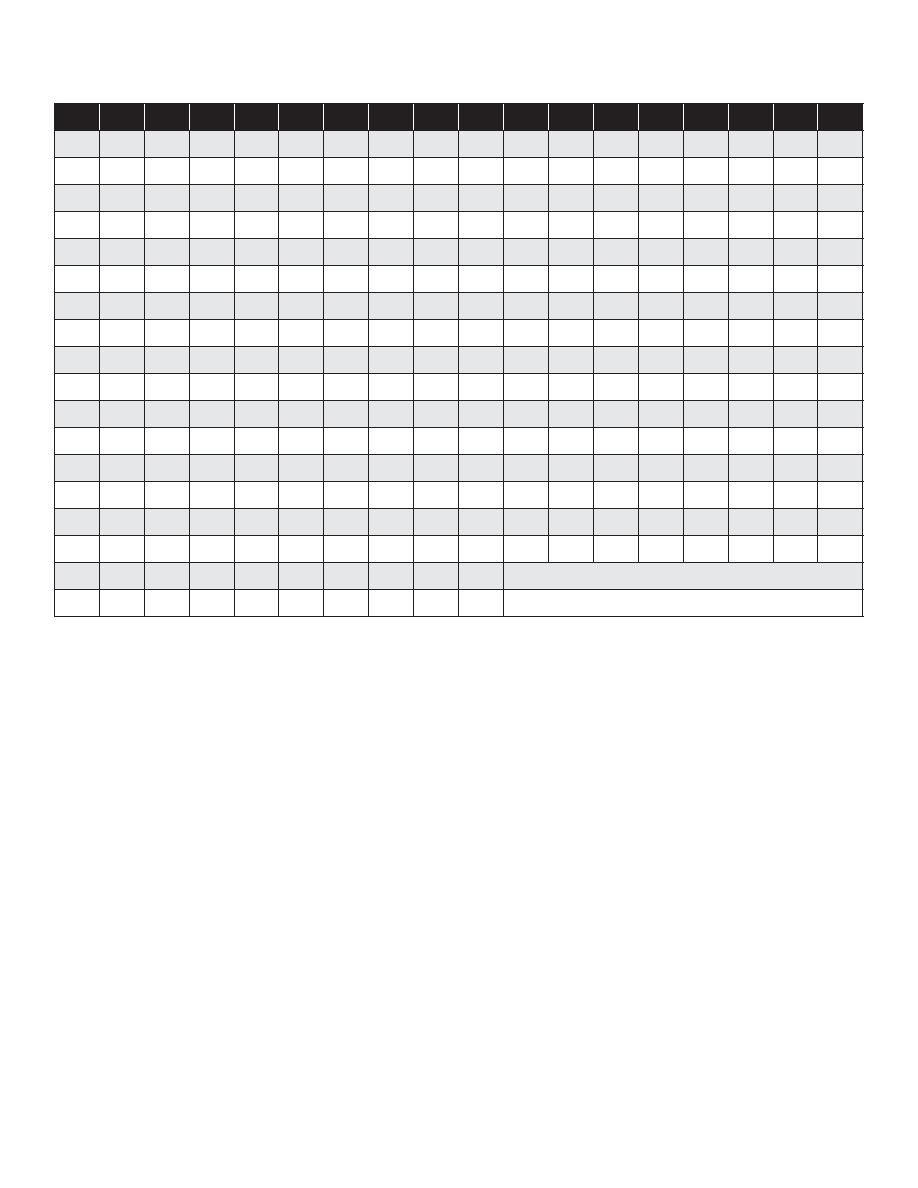

Truth Table

D0

D1

D2

D3

D4

D5

D6

D7

LE

CLR

SW0

SW1

SW2

SW3

SW4

SW5

SW6

SW7

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

L

L

L

Off

H

L

L

On

X

X

X

X

X

X

X

X

H

L

Hold Previous State

X

X

X

X

X

X

X

X

X

H

All Switches Off

Notes:

1. The eight switches operate independently.

2. Serial data is clocked in on the L to H transition of the CLK.

3. The switches go to a state retaining their present condition at the rising edge of LE. When LE is low the shift register data fl ow through the latch.

4. D

OUT

is high when data in the register 7 is high.

5. Shift register clocking has no effect on the switch states if LE is high.

6. The CLR clear input overrides all other inputs.