73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

April 2000

DESCRIPTION

The 73K324L is a highly integrated single-chip

modem IC which provides the functions needed to

design a Quad-mode CCITT and Bell 212A

compatible modem capable of operation over dial-up

lines. The 73K324L adds V.23 capability to the

CCITT modes of TDK Semiconductor Corporation's

73K224 one-chip modem, allowing a one-chip

implementation in designs intended for European

markets which require this added Modulation mode.

The 73K324L offers excellent performance and a

high level of functional integration in a single IC. The

device supports V.22bis, V.22, Bell 212A, V.21, and

V.23 operating modes, allowing both synchronous

and asynchronous operation as defined by the

appropriate standard.

The 73K324L is designed to appear to the Systems

Engineer as a microprocessor peripheral, and will

easily interface with popular one-chip

microcontrollers (80C51 typical) for control of

modem functions through its 8-bit multiplexed

address/data bus. A serial control bus is available

for applications not requiring a parallel interface. An

optional package with only the serial control bus is

also available. Data communications occurs through

a separate serial port.

(continued)

FEATURES

∑

One chip Multi-mode CCITT V.22bis, V.22, V.21,

V.23 and Bell 212A compatible modem data pump

∑

FSK (75, 300, 1200 bit/s), DPSK (600, 1200 bit/s),

or QAM (2400 bit/s) encoding

∑

Pin and software compatible with other

TDK Semiconductor Corporation K-Series family

one-chip modems

∑

Interfaces directly with standard

microprocessors (8048, 80C51 typical)

∑

Serial and parallel microprocessor bus for

control

∑

Selectable asynch/synch with internal

buffer/debuffer and scrambler/descrambler

functions

∑

All synchronous (internal, external, slave) and

Asynchronous Operating modes

∑

Adaptive equalization for optimum performance

over all lines

∑

Programmable transmit attenuation (16 dB, 1 dB

steps), and selectable receive boost (+18 dB)

∑

Call progress, carrier, answer tone, unscrambled

mark, S1, and signal quality monitors

∑

DTMF, answer, calling, SCT and guard tone

generators

∑

Test modes available: ALB, DL, RDL; Mark, Space

and Alternating bit pattern generators

∑

CMOS technology for low power consumption

(100 MW @ 5 V) with power-down mode

(15 mW @ 5V)

∑

4-wire full duplex operation in all modes

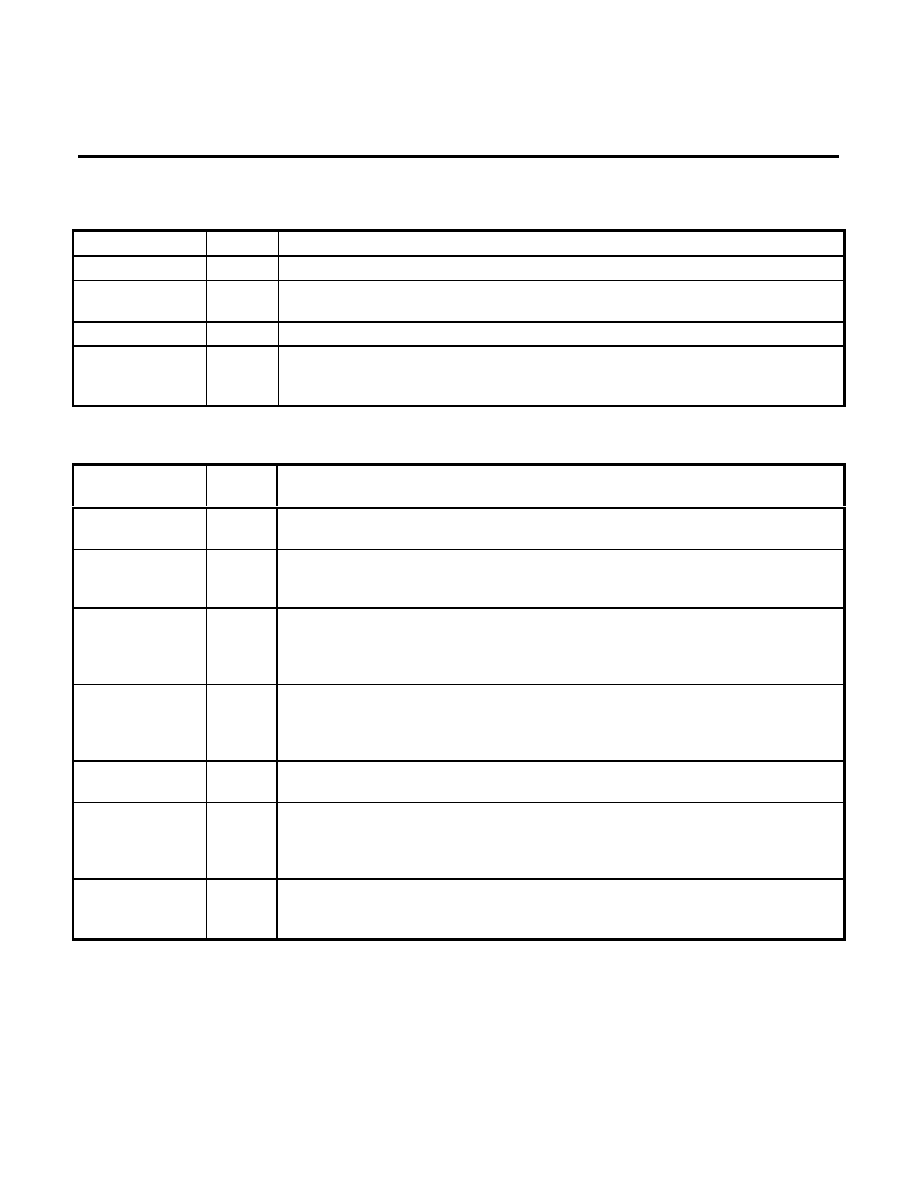

BLOCK DIAGRAM

SERIAL

I/F

FSK

MODULATOR

DIBIT/

QUADBIT

ENCODER

FILTER

DEBUFFER

DIBIT/

QUADBIT

DECODER

DE-

SCRAMBLER

FILTER

FIR

PULSE

SHAPER

QAM/

DPSK

MODULATOR

EQUALIZER

FILTER

TXA

DIGITAL

SIGNAL

PROCESSOR

RECEIVE

FUNCTIONS

A/D

EQUALIZER

FILTER

RXA

GAIN BOOST

TONE DETECTION

FIXED

DEMOD

FILTER

TXD

RXD

ATTEN

I/F

+

+

BUFFER

SCRAMBLER

DTMF,

ANSWER,

GUARD &

CALLING

TONE

GENERATOR

8 - BIT

P

BUS

m

AGC

6 dB

6 dB

GAIN

BOOST

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

2

DESCRIPTION

(continued)

The 73K324L offers full hardware and software

compatibility with other products in TDK

Semiconductor's K-Series family of single-chip

modems, allowing system upgrades with a single

component change. The 73K324L is ideal for use in

free-standing or integral system modem products

where full-duplex 2400 bit/s operation with Alternate

mode capability is required. Its high functionality, low

power consumption, and efficient packaging simplify

design requirements and increase system reliability.

A complete modem requires only the addition of the

phone line interface, a control microprocessor, and

RS-232 level converters for a typical system.

The 73K324L is designed to provide a complete

V.22bis, V.22, Bell 212A, V.21, and V.23 compatible

modem on a chip. Many functions were included to

simplify implementation in typical modem designs. In

addition to the basic 2400 bit/s QAM, 1200/600 bit/s

DPSK and 1200/300/75 bit/s FSK

modulator/demodulator sections, the device also

includes synch/asynch buffering, DTMF, answer,

soft carrier, guard, and calling tone generator

capabilities. Handshake pattern detectors simplify

control of connect sequences, and precise tone

detectors allow accurate detection of call progress,

answer, calling, and soft carrier turn off tones. All

Operating modes defined by the incorporated

standards are included, and Test modes are

provided. Most functions are selectable as options,

and logical defaults are provided. The device can be

directly interfaced to a microprocessor via its 8-bit

multiplexed address/data bus for control and status

monitoring. Data communications takes place

through a separate serial port. Data may also be

sent and received through the control registers. This

simplifies designs requiring speed buffering, error

control and compression.

FUNCTIONAL DESCRIPTION

QAM MODULATOR/DEMODULATOR

The 73K324L encodes incoming data into quad-bits

represented by 16 possible signal points with

specific phase and amplitude levels. The baseband

signal is then filtered to reduce intersymbol

interference on the bandlimited telephone network.

The modulator transmits this encoded data using

either a 1200 Hz (Originate mode) or 2400 Hz

(Answer mode) carrier. The demodulator, although

more complex, essentially reverses this procedure

while also recovering the data clock from the

incoming signal. Adaptive equalization corrects for

varying line conditions by automatically changing

filter parameters to compensate for line

characteristics.

DPSK MODULATOR/DEMODULATOR

The 73K324L modulates a serial bit stream into

di-bit pairs that are represented by four possible

phase shifts as prescribed by the Bell 212A/V.22

standards. The baseband signal is then filtered to

reduce intersymbol interference on the bandlimited

2-wire PSTN line. Transmission occurs on either a

1200 Hz (Originate mode) or 2400 Hz carrier

(Answer mode). Demodulation is the reverse of the

modulation process, with the incoming analog signal

eventually decoded into di-bits and converted back

to a serial bit stream. The demodulator also recovers

the clock, which was encoded into the analog signal

during modulation. Demodulation occurs using either

a 1200 Hz carrier (Answer mode or ALB Originate

mode) or a 2400 Hz carrier (Originate mode or ALB

Answer mode). The 73K324L use a phase locked

loop coherent demodulation technique that offers

excellent performance. Adaptive equalization is also

used in DPSK modes for optimum operation with

varying lines.

FSK MODULATOR/DEMODULATOR

The FSK modulator/demodulator produces a

frequency modulated analog output signal using two

discrete frequencies to represent the binary data.

V.21 frequencies of 980 and 1180 Hz (originate

mark and space), or 1650 and 1850 Hz (answer

mark and space) are used in V.21 mode. V.23 mode

uses 1300 and 2100 Hz for the main channel or 390

and 450 Hz for the back channel. Demodulation

involves detecting the received frequencies and

decoding them into the appropriate binary value.

The rate converter and scrambler/descrambler are

automatically bypassed in the FSK modes.

PASSBAND FILTERS AND EQUALIZERS

High and low band filters are included to shape the

amplitude and phase response of the transmit and

receive signals and to provide compromise delay

equalization as well as rejection of out-of-band

signals. The transmit signal filtering corresponds to a

&%

% raised cosine frequency response

characteristic.

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

3

ASYNCHRONOUS MODE

The Asynchronous mode is used for communication

with asynchronous terminals which may transfer

data at 600, 1200, or 2400 bit/s +1%, -2.5% even

though the modem's output is limited to the nominal

bit rate ±0.01% in DPSK and QAM modes. When

transmitting in this mode the serial data on the TXD

input is passed through a rate converter which

inserts or deletes stop bits in the serial bit stream in

order to output a signal that is the nominal bit rate

±0.01%. This signal is then routed to a data

scrambler and into the analog modulator where di-bit

or quad-bit encoding results in the output signal.

Both the rate converter and scrambler can be

bypassed for handshaking and synchronous

operation as selected. Received data is processed

in a similar fashion except that the rate converter

now acts to reinsert any deleted stop bits and output

data to the terminal at no greater than the bit rate

plus 1%. An incoming break signal (low through two

characters) will be recognized and passed through

without incorrectly inserting a stop bit.

The SYNC/ASYNC converter has an extended

Overspeed mode which allows selection of an output

speed range of either +1% or +2.3%. In the

extended Overspeed mode, some stop bits are

output at 7/8 the normal width.

Both the SYNC/ASYNC rate converter and the data

descrambler are automatically bypassed in the FSK

modes.

SYNCHRONOUS MODE

Synchronous operation is possible only in the QAM

or DPSK modes. Operation is similar to that of the

Asynchronous mode except that data must be

synchronized to a clock and no variation in data

transfer rate is allowable. Serial input data appearing

at TXD must be valid on the rising edge of TXCLK.

TXCLK is an internally derived 1200 or 2400 Hz

signal in Internal mode and is connected internally to

the RXCLK pin in Slave mode. Receive data at the

RXD pin is clocked out on the falling edge of

RXCLK. The asynch/synch converter is bypassed

when Synchronous mode is selected and data is

transmitted out at essentially the same rate as it is

input.

PARALLEL CONTROL INTERFACE

Eight 8-bit registers are provided for control, option

select, and status monitoring. These registers are

addressed with the AD0, AD1, and AD2 multiplexed

address lines (latched by ALE) and appear to a

control microprocessor as seven consecutive

memory locations. Six control registers are

read/write. The detect and ID registers are read only

and cannot be modified except by modem response

to monitored parameters.

SERIAL CONTROL INTERFACE

The Serial Command mode allows access to the

73K324L control and status registers via a serial

control port. In this mode the A0, A1, and A2 lines

provide register addresses for data passed through

the DATA pin under control of the

RD

and

WR

lines.

A read operation is initiated when the

RD

line is

taken low. The next eight cycles of EXCLK will then

transfer out eight bits of the selected addresss

location LSB first. A write takes place by shifting in

eight bits of data LSB first for eight consectuive

cycles of EXCLK.

WR

is then pulsed low and data

transfer into the selected register occurs on the

rising edge of

WR

.

TONE GENERATOR

The DTMF generator controls the sending of the

sixteen standard DTMF tone pairs. The tone pair

sent is determined by selecting TRANSMIT DTMF

(bit D4) and the 4 DTMF bits (D0-D3) of the TONE

register. Transmission of DTMF tones from TXA is

gated by the TRANSMIT ENABLE bit of CR0 (bit D1)

as with all other analog signals.

FULL DUPLEX OPERATION

Four-wire full duplex operation is allowed in all

modes. This feature allows transmission and

reception in the same band for four wire applications

only.

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

4

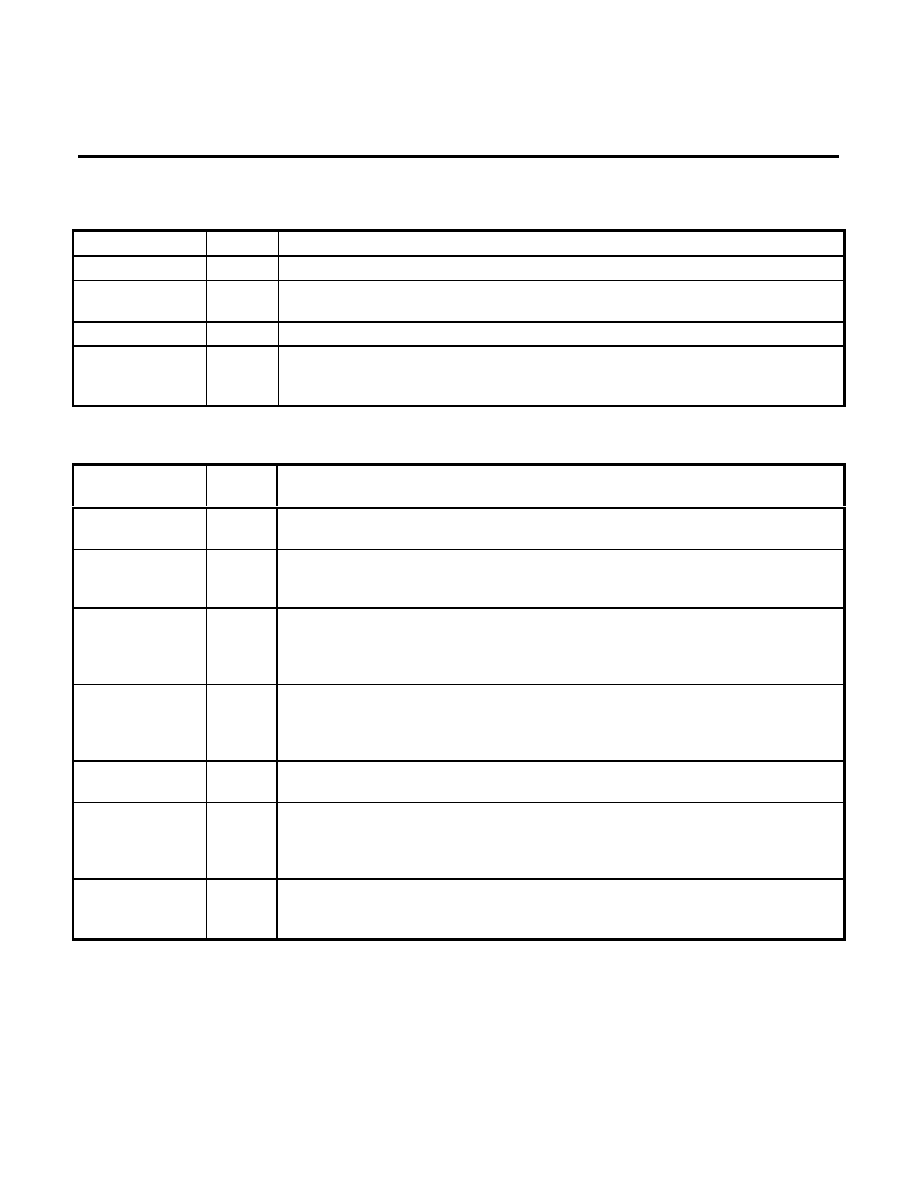

PIN DESCRIPTION

POWER

NAME

TYPE

DESCRIPTION

GND

I

System Ground.

VDD

I

Power supply input, 5V -5% +10%. Bypass with 0.22 µF and 22 µF capacitors to

GND.

VREF

O

An internally generated reference voltage. Bypass with 0.22 µF capacitor to GND.

ISET

I

Chip current reference. Sets bias current for op-amps. The chip current is set by

connecting this pin to VDD through a 2 M

resistor. Iset should be bypassed to

GND with a 0.22 µF capacitor.

PARALLEL MICROPROCESSOR INTERFACE

ALE

I

Address latch enable. The falling edge of ALE latches the address on AD0-AD2

and the chip select on

CS

.

AD0- AD7

I/O /

Tristate

Address/data bus. These bidirectional tri-state multi-plexed lines carry information

to and from the internal registers.

CS

I

Chip select. A low on this pin allows a read cycle or a write cycle to occur. AD0-

AD7 will not be driven and no registers will be written if

CS

(latched) is not active.

CS

is latched on the falling edge of ALE.

CLK

O

Output clock. This pin is selectable under processor control to be either the crystal

frequency (for use as a processor clock) or 16 x the data rate for use as a baud

rate clock in QAM/DPSK modes only. The pin defaults to the crystal frequency on

reset.

INT

O

Interrupt. This open drain weak pullup, output signal is used to inform the

processor that a detect flag has occurred. The processor must then read the detect

register to determine which detect triggered the interrupt.

INT

will stay active until

the processor reads the detect register or does a full reset.

RD

I

Read. A low requests a read of the 73K324L internal registers. Data cannot be

output unless both

RD

and the latched

CS

are active or low.

RESET

I

Reset. An active high signal on this pin will put the chip into an inactive state. All

control register bits (CR0, CR1, CR2, CR3, Tone) will be reset. The output of the

CLK pin will be set to the crystal frequency. An internal pull down resistor permits

power on reset using a capacitor to VDD.

WR

I

Write. A low on this informs the 73K324L that data is available on AD0-AD7 for

writing into an internal register. Data is latched on the rising edge of

WR

. No data

is written unless both

WR

and the latched

CS

are low.

NOTE:

The Serial Control mode is provided by tying ALE high and

CS

low. In this configuration AD7 becomes

DATA and AD0, AD1 and AD2 become the address only. See the serial time diagrams on page 23.

73K324L

CCITT V.22bis, V.22, V.21, V.23, Bell 212A

Single-Chip Modem

5

RS-232 INTERFACE

NAME

TYPE

DESCRIPTION

EXCLK

I

External Clock. This signal is used in synchronous transmission when the external

timing option has been selected. In the External Timing mode the rising edge of

EXCLK is used to strobe synchronous transmit data available on the TXD pin. Also

used for serial control interface.

RXCLK

O/Tristate Receive Clock Tri-statable. The falling edge of this clock output is coincident with

the transitions in the serial received DPSK/QAM data output. The rising edge of

RXCLK can be used to latch the valid output data. RXCLK will be valid as long as

a carrier is present. In V.23 or V.21 mode a clock which is 16 x 1200/75 or 16 x

300 Hz data rate is output, respectively.

RXD

O/

Weak

Pull-up

Received Data Output. Serial receive data is available on this pin. The data is

always valid on the rising edge of RXCLK when in Synchronous mode. RXD will

output constant marks if no carrier is detected.

TXCLK

O/Tristate Transmit Clock Tri-statable. This signal is used in synchronous DPSK/QAM

transmission to latch serial input data on the TXD pin. Data must be provided so

that valid data is available on the rising edge of the TXCLK. The transmit clock is

derived from different sources depending upon the Synchronization mode

selection. In Internal Mode the clock is generated internally (2400 Hz for QAM,

1200 Hz for DPSK or 600 Hz for half-speed DPSK). In External Mode TXCLK is

phase locked to the EXCLK pin. In Slave Mode TXCLK is phase locked to the

RXCLK pin. TXCLK is always active. In V.23 or V.21 mode the output is a 16 x

1200/75 or 16 x 300 Hz clock, respectively.

TXD

I

Transmit Data Input. Serial data for transmission is input on this pin. In

Synchronous modes, the data must be valid on the rising edge of the TXCLK

clock. In Asynchronous modes (2400/1200/600 bit/s, or 75/300 baud) no clocking

is necessary. DPSK/QAM data must be +1%, -2.5% or +2.3%, -2.5 % in Extended

Overspeed mode.

ANALOG INTERFACE

RXA

I

Received modulated analog signal input from the phone line.

TXA

O

Transmit analog output to the phone line.

XTL1

I

XTL2

I/O

These pins are for the internal crystal oscillator requiring a 11.0592 MHz Parallel

mode crystal. Two capacitors from these pins to ground are also required for

proper crystal operation. Consult crystal manufacturer for proper values. XTL2 can

also be driven from an external clock.