U4083B

Preliminary Information

TELEFUNKEN Semiconductors

Rev. A2, 07-Apr-97

1 (11)

Low-Power Audio Amplifier for Telephone Applications

Description

The integrated circuit, U4083B, is a low power audio

amplifier for a telephone loudspeaker. It has differential

speaker outputs to maximize the output swing at low

supply voltages. There is no need for coupler capacitors.

The U4083B has an open loop gain of 80 dB whereas the

closed loop gain is adjusted with two external resistors. A

chip disable pin permits powering down and/or muting

the input signal.

Features

D Wide operating voltage range: 2 to 16 V

D Battery powered application due to low quiescent

supply current: 2.7 mA typical

D Chip disable input to power down the integrated

circuit

D Low power down quiescent current

D Drives a wide range of speaker loads

D Output Power, P

o

= 250 mW @ R

L

= 32

W (speaker)

D Low harmonic distortion (0.5% typical)

D Wide range gain adjustable: 0 dB to 46 dB

Benefits

D Low number of external components

D Low current consumption

Block Diagram / Application Circuit

0.1 F

�

+

�

+

4 k

4 k

125 k

50 k

50 k

Amp.1

Amp.2

Bias

circuit

V

S

6

5

8

VO1

VO2

1

CD

GND

7

4

Vi

3

2

Rf

75 k

Ri

3 k

C

i

Input

C2

5 F

C1

1 F

93 7781 e

W

W

W

W

W

W

W

m

m

m

FC1

FC2

Figure 1.

Order Information

Extended Type Number

Package

Remarks

U4083B-AFP

SO8

U4083B-AFPG3

SO8

Taped and reeled

U4083B

TELEFUNKEN Semiconductors

Rev. A2, 07-Apr-97

Preliminary Information

2 (11)

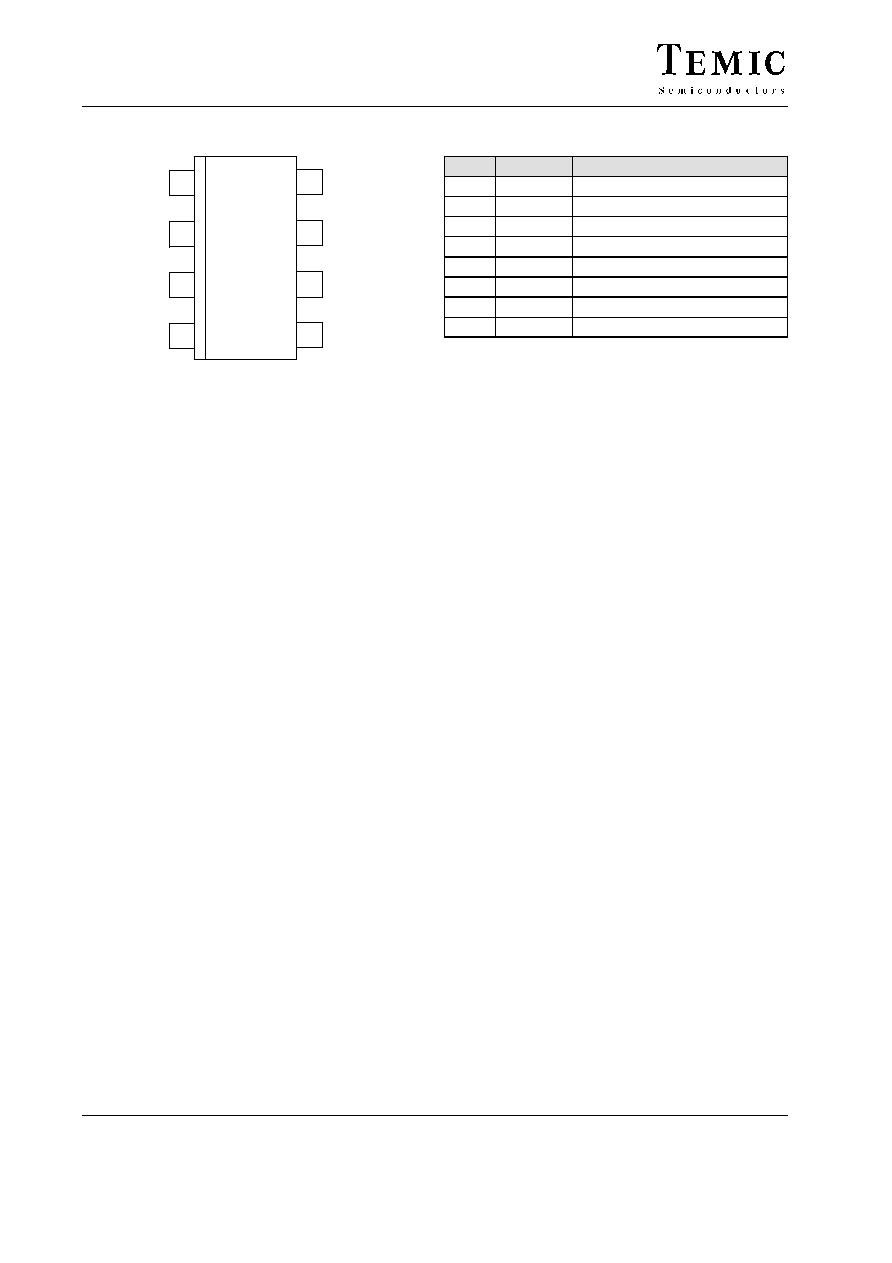

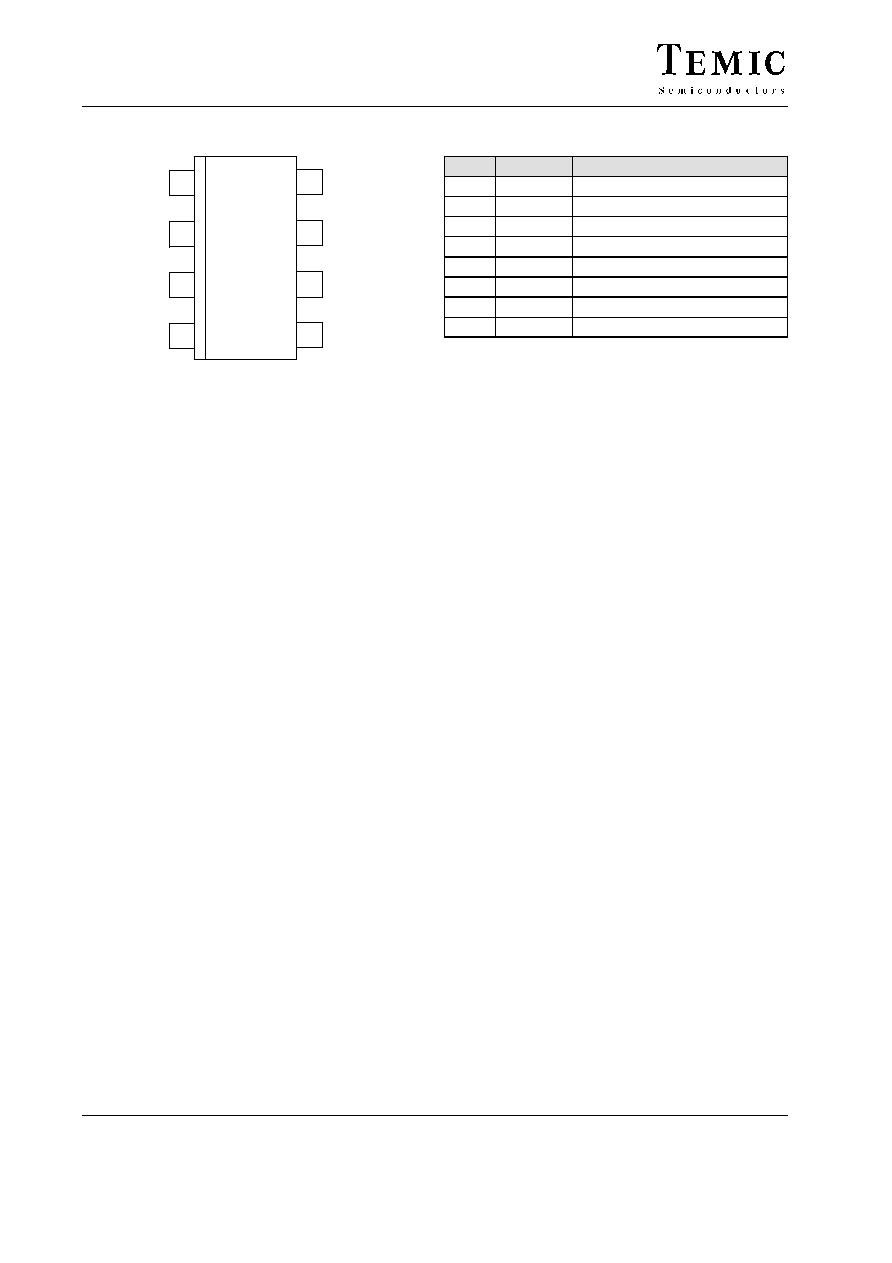

Pin Description

1

2

3

4

8

7

6

5

94 8022

V i

FC1

FC2

GND

CD

VO1

VO2

V S

Figure 2. Pinning

Pin

Symbol

Function

1

CD

Chip disable

2

FC2

Filtering, power supply rejection

3

FC1

Filtering, power supply rejection

4

V

i

Amplifier input

5

VO1

Amplifier output 1

6

V

S

Voltage supply

7

GND

Ground

8

VO2

Amplifier output 2

Functional Description

Including External Circuitry

Pin 1: Chip disable

* digital input (CD)

Pin 1 (chip disable) is used to power down the IC to con-

serve power or muting or both.

Input impedance at pin 1 is typically 90 k

W.

Logic 0 < 0.8 V

IC enabled (normal operation)

Logic 1 > 2 V

IC disabled

Figure 15 shows power supply current diagram. The

change in differential gain from normal operation to

muted operation (muting) is more than 70 dB.

Switching characteristics are as follows:

turn-on time

t

on

= 12 to 15 ms

turn-off time

t

off

v 2 ms

They are independent of C

1

, C

2

and V

S

.

Voltages at Pins 2 and 3 are supplied from V

S

and there-

fore do not change when the U4083B is disabled.

Outputs� V

O1

(Pin 5) and V

O2

(Pin 8) �turn to a high im-

pedance condition by removing the signal from the

speaker.

When signals are applied from an external source to the

outputs (disabled), they must not exceed the range be-

tween the supply voltage, V

s

, and Ground.

Pins 2 and 3: Filtering, power supply rejection

Power supply rejection is provided by capacitors C

1

and

C

2

at Pin 3 and Pin 2, respectively. C

1

is dominant at high

frequencies whereas C

2

is dominant at low frequencies

(figures 4 to 7). Values of C

1

and C

2

depend on the

conditions of each application. For example, a line

powered speakerphone (telephone amplifier) will require

more filtering than a system powered by regulated power

supply.

The amount of rejection is a function of the capacitors and

the equivalent impedance looking into Pin 3 and Pin 2

(see electrical characteristic equivalent resistance, R).

Apart from filtering, capacitors C

1

and C

2

also influence

the turn-on time of the circuit at power-up since capaci-

tors are charged up through the internal resistors (50 k

W

and 125 k

W) as shown in the block diagram.

Figure 1 shows turn-on time versus C

2

at V

S

= 6 V, for two

different C

1

values.

Turn-on time is 60% longer when V

S

= 3 V and 20%

shorter when V

S

= 9 V.

Turn-off time is less than 10

ms

Pin 4: Amplifier input

V

i

Pin 5: Amplifier output 1 V

O1

Pin 8: Amplifier output 2 V

O2

There are two identical operational amplifiers. Amp.1 has

an open loop gain

w 80 dB at 100 Hz (figure 2), whereas

the closed loop gain is set by external resistors, Rf and Ri

(figure 3). The amplifier is unity gain stable, and has a

unity gain frequency of approximately 1.5 MHz. A closed

loop gain of 46 dB is recommended for a frequency range

of 300 to 3400 Hz (voice band). Amp.2 is internally set

to a gain of �1.0 (0 dB). The outputs of both amplifiers are

capable of sourcing and sinking a peak current of 200 mA.

Output voltage swing is between 0.4 V and V

s

� 1.3 V at

maximum current (figures 18 and 19).

The output dc offset voltage between Pins 5 and 8 (V

O1

� V

O2

) is mainly a function of the feedback resistor, R

f

,

because the input offset voltage of the two amplifiers

generally neutralize each other.

Bias current of Amp. 1 which is constant with respect to

V

s

, however flows out of Pin 4 (V

i

) and through R

f

,

forcing V

01

to shift negative by an amount equal to R

f

I

IB

and V

O2

positive to an equal amount.

The output offset voltage specified in the electrical char-

acteristics is measured with the feedback resistor

(R

f

= 75 k

W) shown in typical application circuit. It takes

into account bias current as well as internal offset voltages

of the amplifiers.

U4083B

Preliminary Information

TELEFUNKEN Semiconductors

Rev. A2, 07-Apr-97

3 (11)

Pin 6: Supply and power dissipation

Power dissipation is shown in figures 8 to 10 for different

loads. Distortion characteristics are given in figures 11 to

13.

P

totmax

+

T

jmax

� T

amb

R

thJA

where

T

jmax

= Junction temperature = 140

�

C

T

amb

= Ambient temperature

R

thJA

= Thermal resistance, junction-ambient

Power dissipated within the IC in a given application is

found from the following equation:

P

tot

= (V

S

@ I

S

) + (I

RMS

@ V

S

) � (R

L

@ I

RMS

2

)

I

S

is obtained from figures 15

I

RMS

is the RMS current at the load R

L.

Operating range of the integrated circuit is defined with

a peak operating load current of

"200 mA (figures 8 to

13). It is further specified with respect to different loads

in figure 14. The left (ascending) portion of each of the

three curves is defined by the power level at which 10%

distortion occurs. The center flat portion of each curve is

defined by the maximum output current capability of the

integrated circuit. The right (descending) portion of each

curve is defined by the maximum internal power dissipa-

tion of the IC at 25

�

C. At higher ambient temperatures,

the maximum load power must be reduced according to

the above mentioned equation.

Layout Considerations

Normally a snubber is not needed at the output of the IC,

unlike many other audio amplifiers. However, the PC

board layout, stray capacitances, and the manner in which

the speaker wires are configured, may dictate otherwise.

Generally the speaker wires should be twisted tightly, and

be not more than a few cm (or inches) in length.

Absolute Maximum Ratings

Reference point Pin 7, T

amb

= 25

�

C unless otherwise specified.

Parameters

Symbol

Value

Unit

Supply voltage

Pin 6

V

S

�1.0 to +18

V

Voltages

Pins 1, 2, 3 and 4

Disabled

Pins 5 and 8

�1.0 to (VS +1.0)

�1.0 to (VS +1.0)

V

V

Output current

Pins 5 and 8

"250

mA

Junction temperature

T

j

+140

�

C

Storage temperature range

T

stg

�55 to +150

�

C

Ambient temperature range

T

amb

�20 to +70

�

C

Power dissipation: T

amb

= 60

�

C

SO8

P

tot

440

mW

Thermal Resistance

Parameters

Symbol

Value

Unit

Junction ambient

SO8

R

thJA

180

K/W

Operation Recommendation

Parameters

Symbol

Value

Unit

Supply voltage

Pin 6

V

S

2 to 16

V

Load impedance

Pins 5 to 8

R

L

8.0 to 100

W

Load current

I

L

"200

mA

Differential gain (5.0 kHz bandwidth)

DG

0 to 46

dB

Voltage @ CD Pin 1

V

CD

VS

V

Ambient temperature range

T

amb

�20 to +70

�

C

U4083B

TELEFUNKEN Semiconductors

Rev. A2, 07-Apr-97

Preliminary Information

4 (11)

Electrical Characteristics

T

amb

= +25

�

C, reference point Pin 7, unless otherwise specified

Parameters

Test Conditions / Pins

Symbol

Min.

Typ.

Max.

Unit

Amplifiers (AC Characteristics)

Open gain loop

(Amp. 1, f < 100 Hz)

G

VOL1

80

dB

Closed gain loop (Amp. 2)

V

S

= 6.0 V, f = 1.0 kHz, R

L

= 32

W

G

V2

�0.35

0

+0.35

dB

Gain bandwidth product

G

BW

1.5

MHz

Output power

V

S

= 3.0 V, R

L

= 16

W, d < 10%

V

S

= 6.0 V, R

L

= 32

W, d < 10%

V

S

= 12 V, R

L

= 100

W, d < 10%

Po

Po

Po

55

250

400

mW

Total harmonic distortion

(f = 1.0 kHz)

V

S

= 6.0 V, R

L

= 32

W,

P

o

= 125 mW

V

S

> 3.0 V, R

L

= 8

W,

P

o

= 20 mW

V

S

> 12 V, R

L

= 32

W,

P

o

= 200 mW

d

d

d

0.5

0.5

0.6

1.0

%

Power supply rejection ra-

tio

V

S

= 6.0 V,

DV

S

= 3.0 V

C

1

=

T, C

2

= 0.01

mF

C

1

= 0.1

mF, C

2

= 0, f = 1.0 kHz

C

1

= 1.0

mF, C

2

= 5.0

mF,

f = 1.0 kHz

PSRR

PSRR

PSRR

50

12

52

dB

Muting

V

S

= 6.0 V, 1.0 kHz < f < 20 kHz,

CD = 2.0 V

G

MUTE

>70

dB

Amplifiers (DC Characteristics)

Output dc level at V

O1

,

V

O2

R

f

= 75 kW

V

S

= 3.0 V, R

L

= 16

W

V

S

= 6.0 V

V

S

= 12 V

V

O

V

O

V

O

1.0

1.15

2.65

5.65

1.25

V

Output high level

I

O

= � 75 mA,

2.0 V < V

S

< 16 V

V

OH

V

S

�1

V

Output low level

I

O

= 75 mA,

2.0 V < V

S

< 16 V

V

OL

0.16

V

Output dc offset voltage

(V

O1

� V

O2

)

V

S

= 6.0 V, R

f

= 75 k

W,

R

L

= 32

W

DV

O

�30

0

+30

mV

Input bias current at V

i

V

S

= 6.0 V

�I

IB

100

200

nA

Equivalent resistance at

Pin 3

V

S

= 6.0 V

R

100

150

220

k

W

Equivalent resistance at

Pin 2

V

S

= 6.0 V

R

18

25

40

k

W

Chip disable Pin 1

Input voltage

* low

Input voltage

* high

Input resistance

V

S

= V

CD

= 16 V

V

IL

V

IH

R

CD

2.0

50

90

0.8

175

V

V

kW

Power supply current

V

S

= 3.0 V, R

L

=

T, CD = 0.8 V

V

S

= 16 V, R

L

=

T, CD = 0.8 V

V

S

= 3.0 V, R

L

=

T, CD = 2.0 V

I

S

I

S

I

S

65

4.0

5.0

100

mA

mA

mA

U4083B

Preliminary Information

TELEFUNKEN Semiconductors

Rev. A2, 07-Apr-97

5 (11)

Typical Temperature Performance

T

amb

= �20 to +70

�

C

Function

Typical Change

Units

Input bias current at V

i

"40

pA/

�

C

Total harmonic distortion

V

S

= 6.0 V, R

L

= 32

W, P

o

= 125 mW,

f = 1.0 kHz

+ 0.003

%/

�

C

Power supply current

V

S

= 3.0 V, R

L

=

T, CD = 0 V

V

S

= 3.0 V, R

L

=

T, CD = 2.0 V

� 2.5

� 0.03

mA/

�

C

mA/

�

C

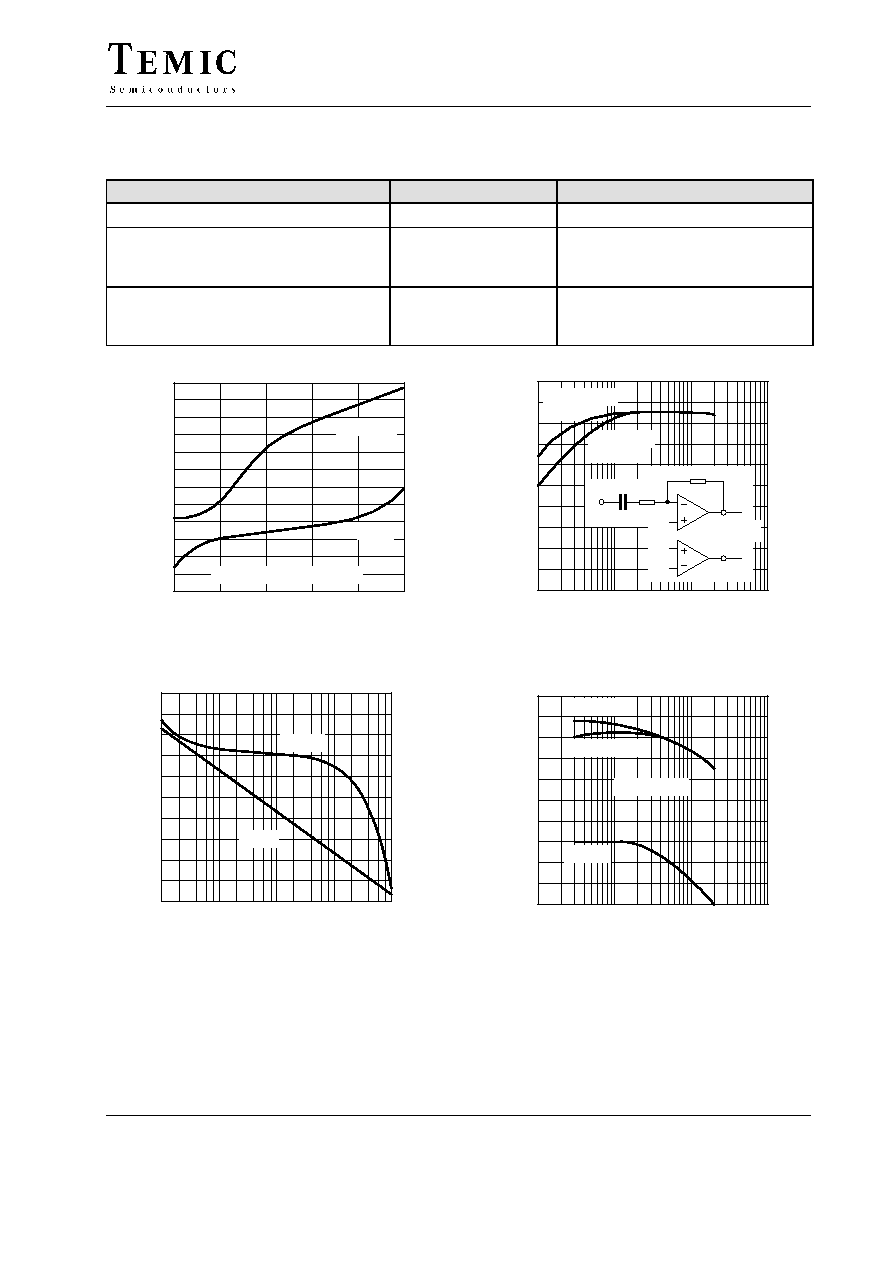

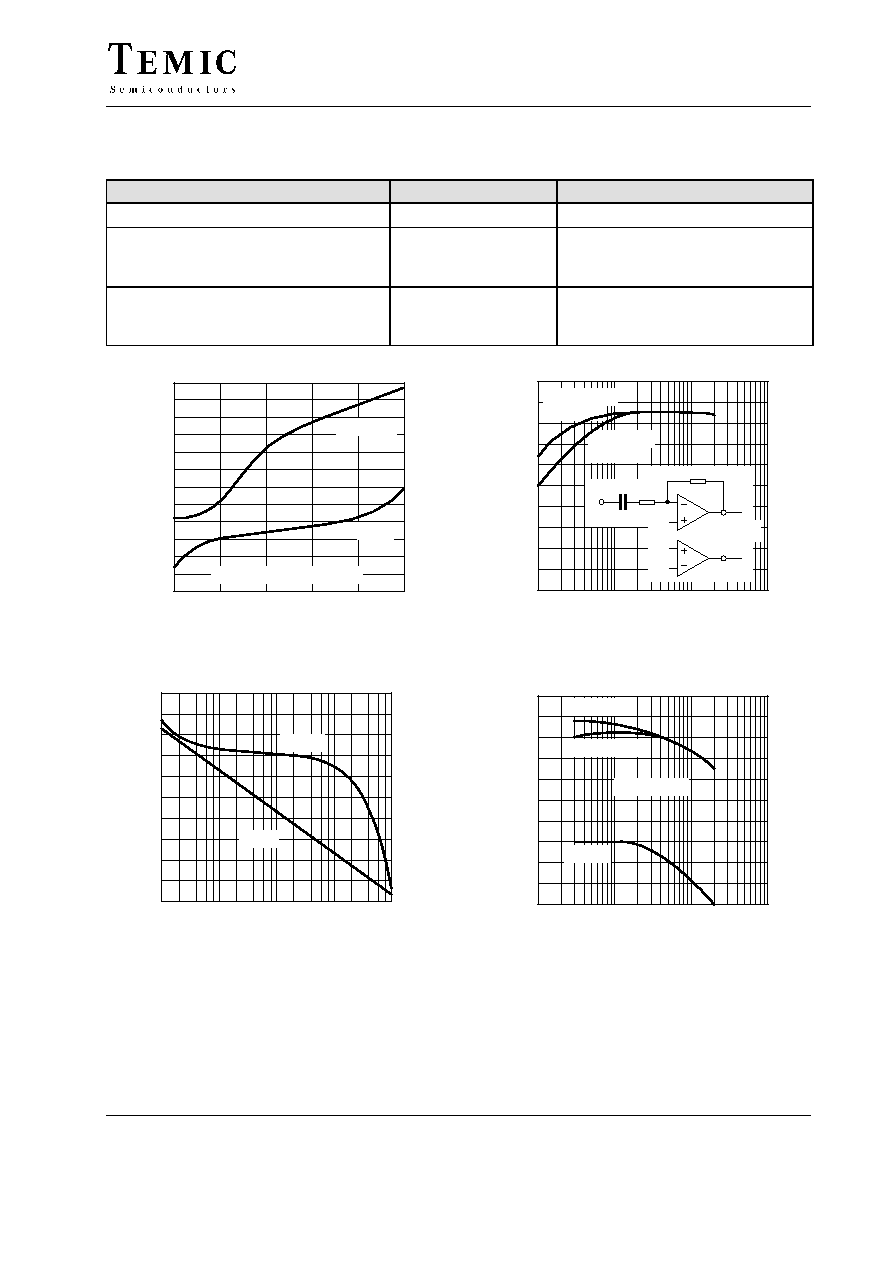

0

2

4

6

8

0

60

120

180

240

300

t ( ms )

on

C

2

(

mF )

10

360

C

1

= 5

mF

V

S

switching from 0 to + 6 V

1

mF

94 7838 e

Figure 1.

0.1

1

10

100

0

20

40

60

80

100

G (dB )

f ( kH )

1000

72.67

79.33

86.00

92.67

99.33

66.00

Phase ( Degrees )

Phase

Gain

94 7839 e

Figure 2.

Input

C

i

R

i

R

f

V

O1

V

O2

Outputs

Amp 1

Amp 2

0.1

mF

0

1

10

0

8

16

24

32

40

100

R

f

= 150 k

W

R

f

= 75 k

W

R

i

= 3 k

W

93 7797 e

R

i

= 6 k

W

Figure 3.

0.1

1

10

10

20

30

40

50

60

PSSR ( dB )

f ( kHz )

100

C

1

w1 mF

C

1

= 0.1

mF

C

2

= 10

mF

C

1

= 0

93 7798 e

Figure 4.