SN74LVC1G3157 Q1

SINGLE POLE, DOUBLE THROW ANALOG SWITCH

SCES463A - JUNE 2003 - REVISED OCTOBER 2003

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Qualification in Accordance With

AEC-Q100

D

Qualified for Automotive Applications

D

Customer-Specific Configuration Control

Can Be Supported Along With

Major-Change Approval

D

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D

1.65-V to 5.5-V V

CC

Operation

D

Useful for Both Analog and Digital

Applications

D

Specified Break-Before-Make Switching

Contact factory for details. Q100 qualification data available on

request.

D

Rail-to-Rail Signal Handling

D

High Degree of Linearity

D

High Speed, Typically 0.5 ns

(V

CC

= 3 V, C

L

= 50 pF)

D

Low On-State Resistance, Typically

6

(V

CC

= 4.5 V)

D

Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II

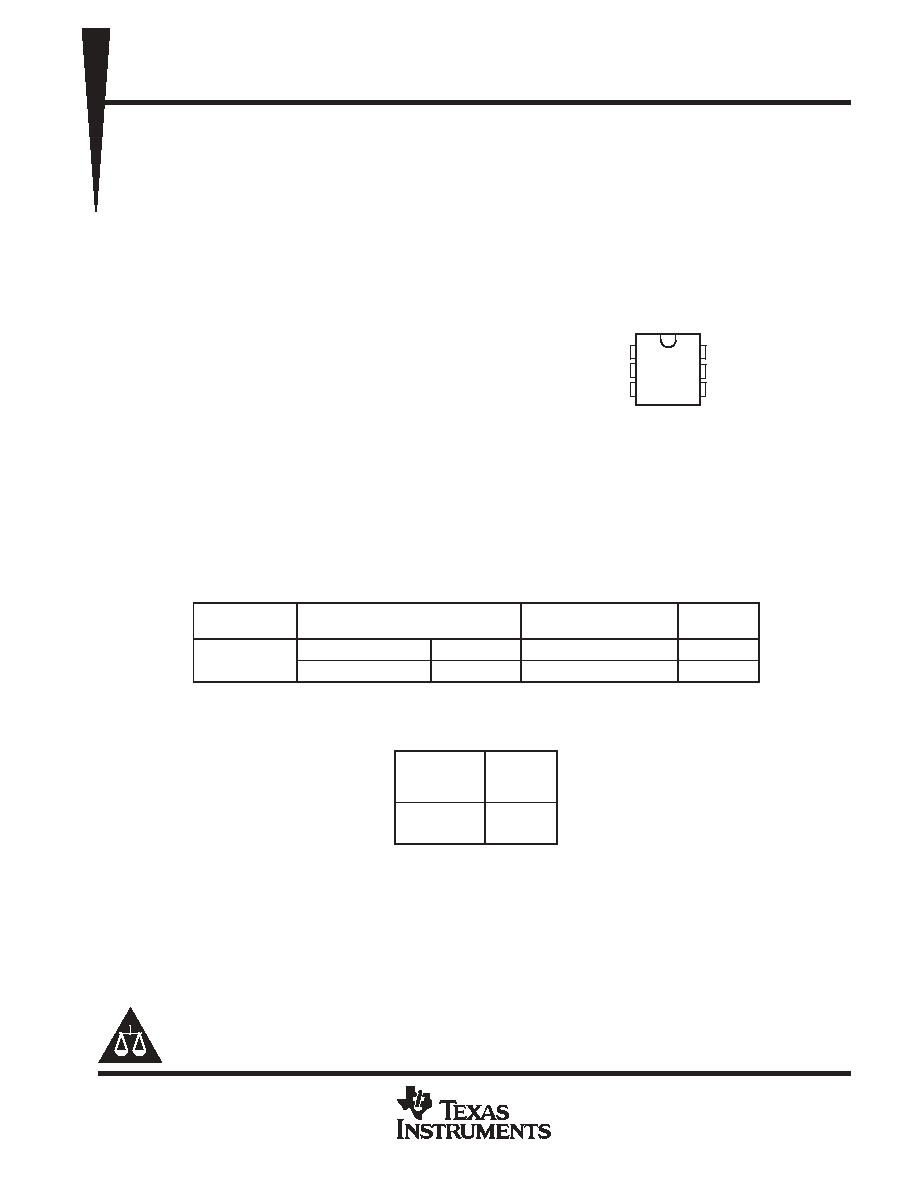

description/ordering information

This single-pole, double-throw (SPDT) analog switch is designed for 1.65-V to 5.5-V V

CC

operation.

The SN74LVC1G3157 can handle both analog and digital signals. The device permits signals with amplitudes

of up to V

CC

(peak) to be transmitted in either direction.

Applications include signal gating, chopping, modulation or demodulation (modem), and signal multiplexing for

analog-to-digital and digital-to-analog conversion systems.

ORDERING INFORMATION

TA

PACKAGE

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

-40

∞

C to 125

∞

C

SOT (SOT-23) - DBV

Tape and reel

1P1G3157QDBVRQ1

CC5R

-40

∞

C to 125

∞

C

SOT (SC-70) - DCK

Tape and reel

1P1G3157QDCKRQ1

C5R

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines

are available at www.ti.com/sc/package.

FUNCTION TABLE

CONTROL

INPUT

ON

INPUT

S

ON

CHANNEL

L

B1

H

B2

Copyright

2003, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DBV OR DCK PACKAGE

(TOP VIEW)

1

2

3

6

5

4

B2

GND

B1

S

V

CC

A

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN74LVC1G3157 Q1

SINGLE POLE, DOUBLE THROW ANALOG SWITCH

SCES463A - JUNE 2003 - REVISED OCTOBER 2003

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

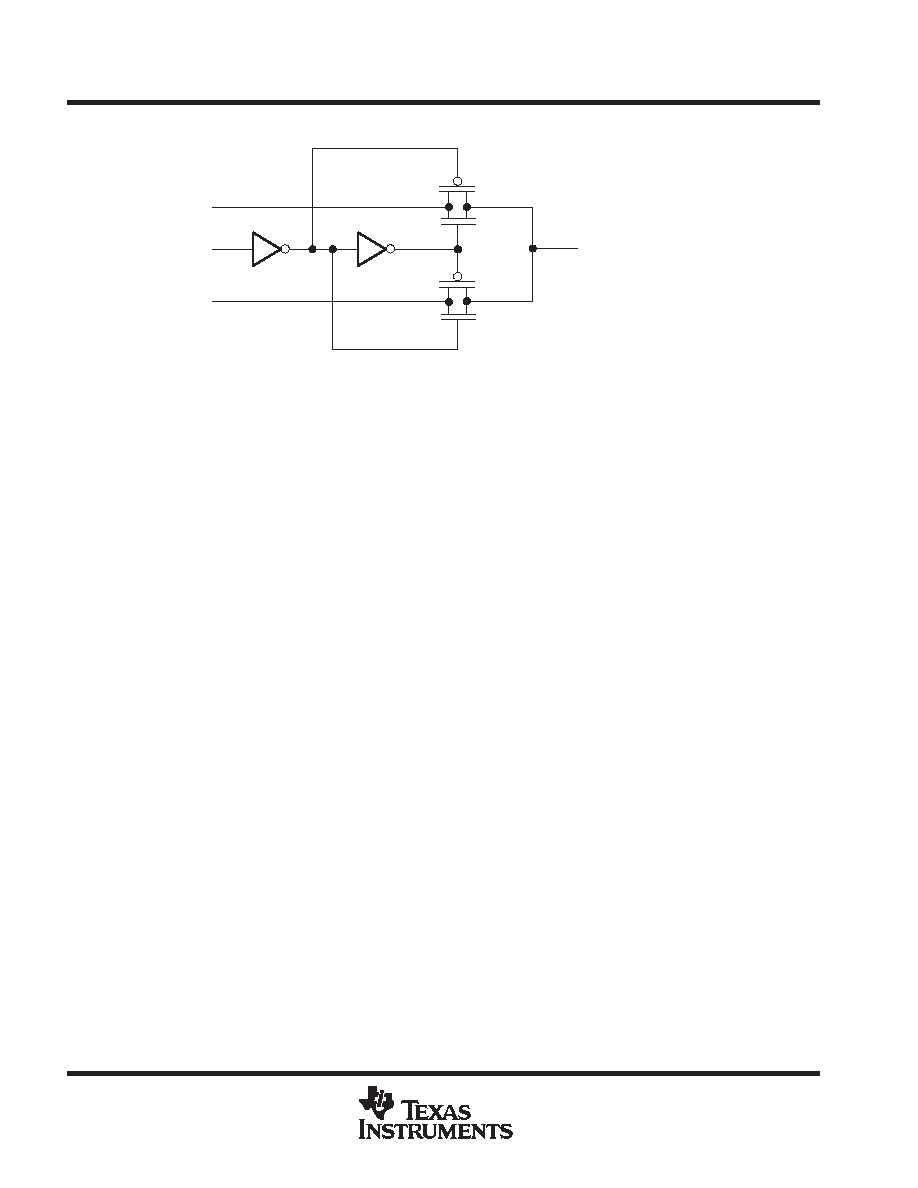

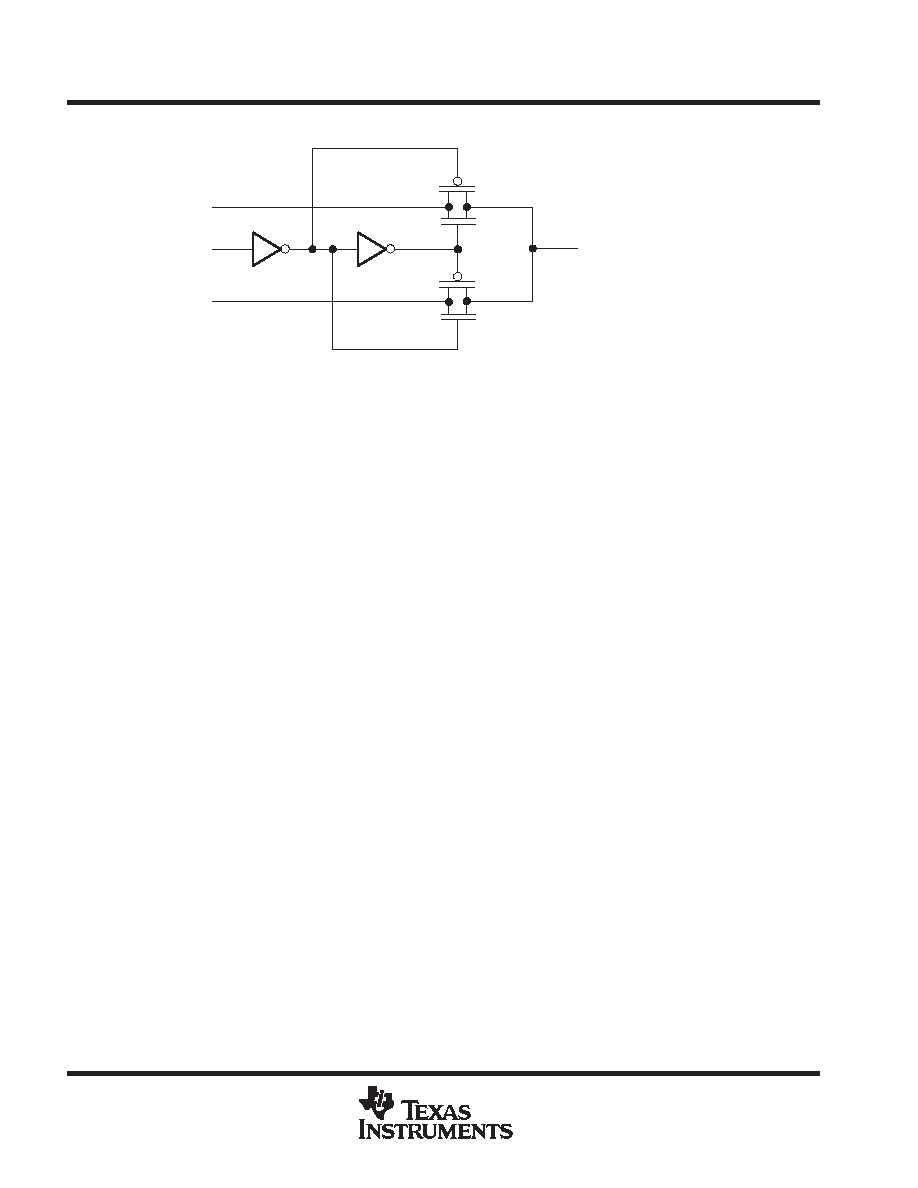

logic diagram (positive logic)

A

B2

B1

1

3

4

S

6

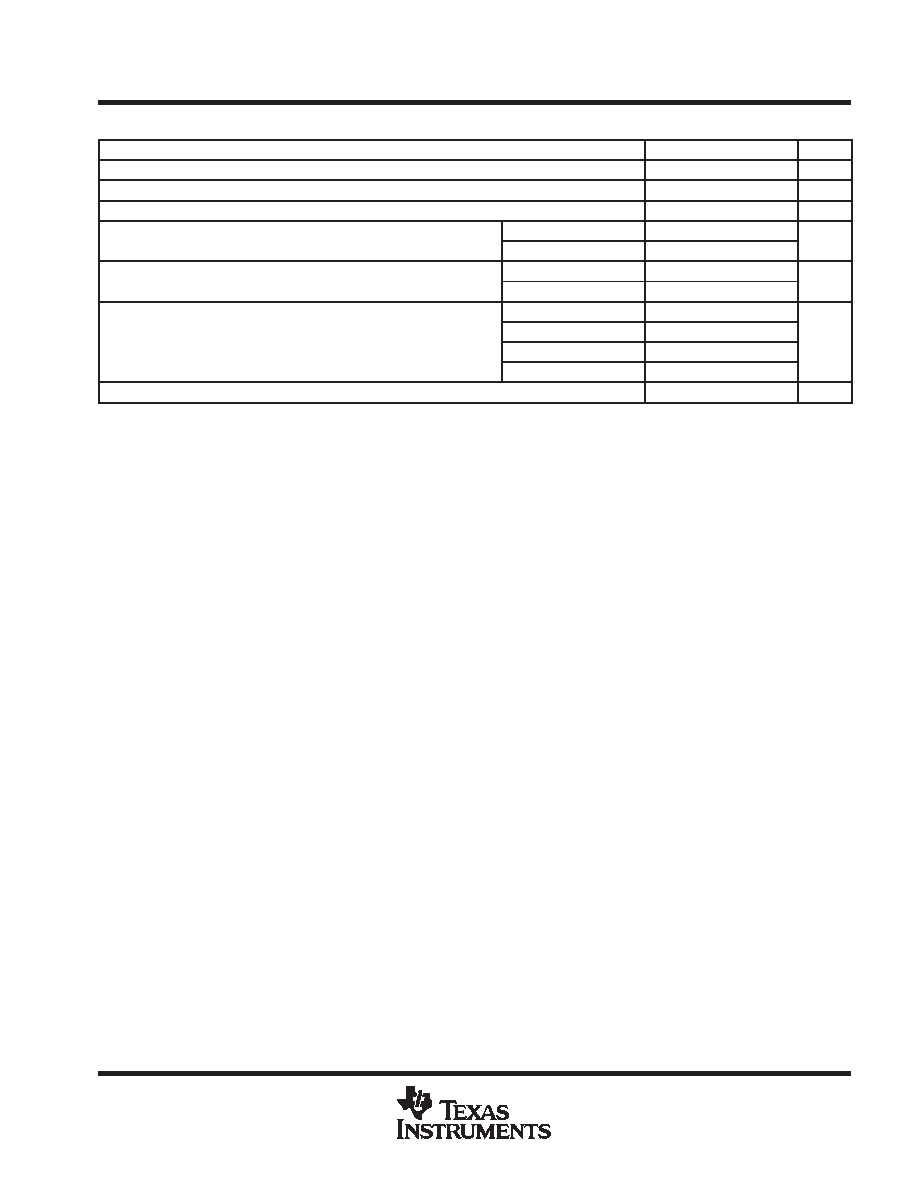

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

CC

(see Note 1)

-0.5 V to 6.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control input voltage range, V

IN

(see Notes 1 and 2)

-0.5 V to 6.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Switch I/O voltage range, V

I/O

(see Notes 1, 2, 3, and 4)

-0.5 V to V

CC

+ 0.5 V

. . . . . . . . . . . . . . . . . . . . . . . . .

Control input clamp current, I

IK

(V

IN

< 0)

-50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I/O port diode current, I

IOK

(V

I/O

< 0 or V

I/O

> V

CC

)

±

50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

On-state switch current, I

I/O

(V

I/O

= 0 to V

CC

) (see Note 5)

±

128 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through V

CC

or GND

±

100 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

JA

(see Note 6): DBV package

165

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DCK package

258

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

-65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. All voltages are with respect to ground unless otherwise specified.

2. The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

3. This value is limited to 5.5 V maximum.

4. VI, VO, VA, and VBn are used to denote specific conditions for VI/O.

5. II, IO, IA, and IBn are used to denote specific conditions for II/O.

6. The package thermal impedance is calculated in accordance with JESD 51-7.

SN74LVC1G3157 Q1

SINGLE POLE, DOUBLE THROW ANALOG SWITCH

SCES463A - JUNE 2003 - REVISED OCTOBER 2003

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

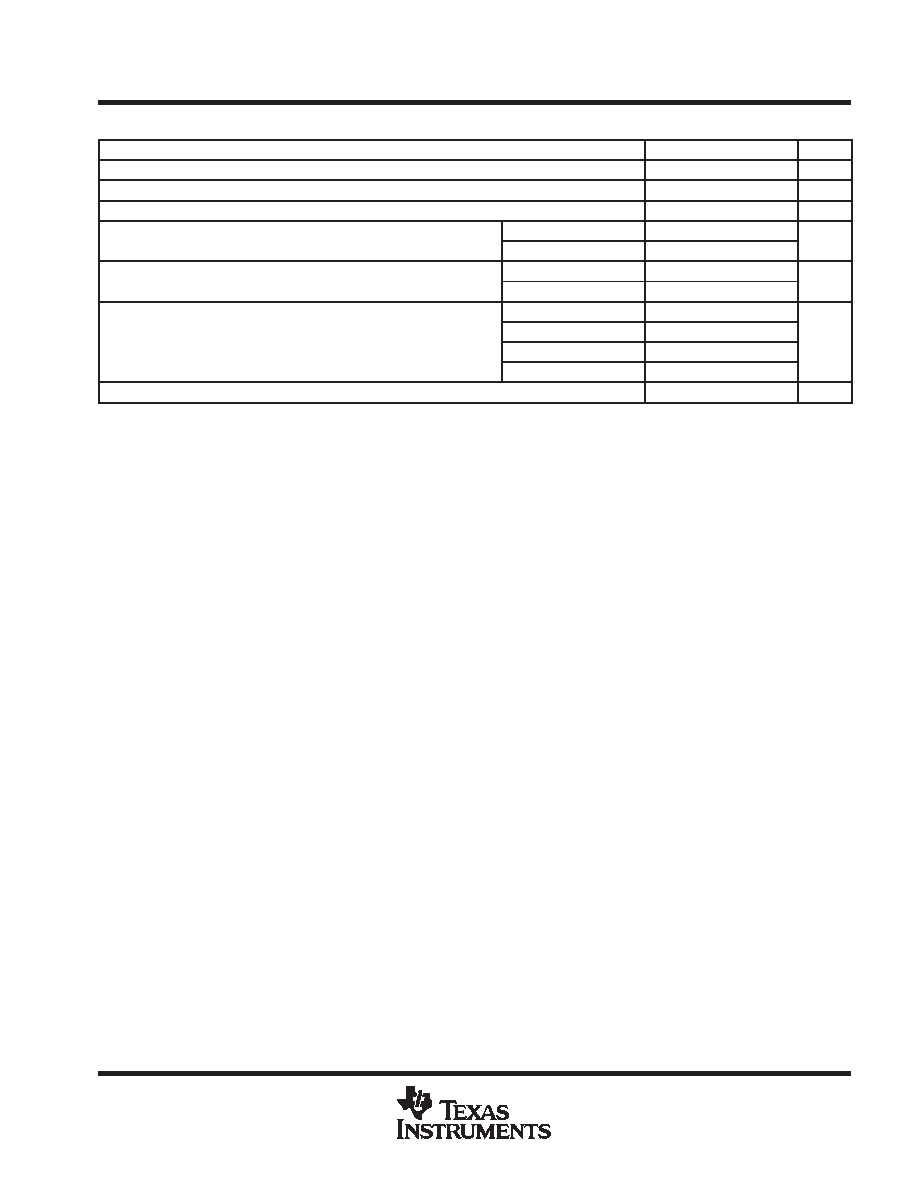

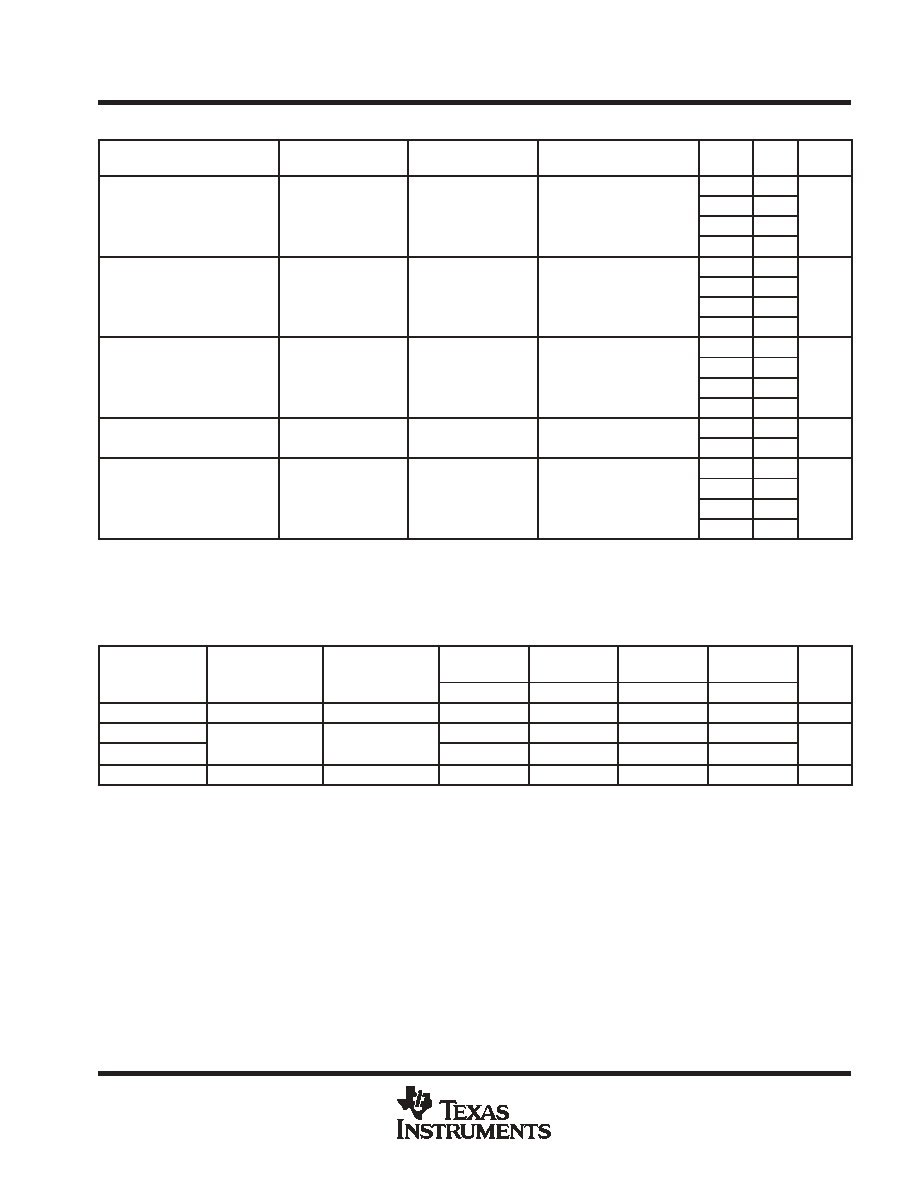

recommended operating conditions (see Note 7)

MIN

MAX

UNIT

VCC

1.65

5.5

V

VI/O

0

VCC

V

VIN

0

5.5

V

VIH

High-level input voltage, control input

VCC = 1.65 V to 1.95 V

VCC

◊

0.75

V

VIH

High-level input voltage, control input

VCC = 2.3 V to 5.5 V

VCC

◊

0.7

V

VIL

Low-level input voltage, control input

VCC = 1.65 V to 1.95 V

VCC

◊

0.25

V

VIL

Low-level input voltage, control input

VCC = 2.3 V to 5.5 V

VCC

◊

0.3

V

VCC = 1.65 V to 1.95 V

20

t/

v

Input transition rise/fall time

VCC = 2.3 V to 2.7 V

20

ns/V

t/

v

Input transition rise/fall time

VCC = 3 V to 3.6 V

10

ns/V

VCC = 4.5 V to 5.5 V

10

TA

-40

125

∞

C

NOTE 7: All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

SN74LVC1G3157 Q1

SINGLE POLE, DOUBLE THROW ANALOG SWITCH

SCES463A - JUNE 2003 - REVISED OCTOBER 2003

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

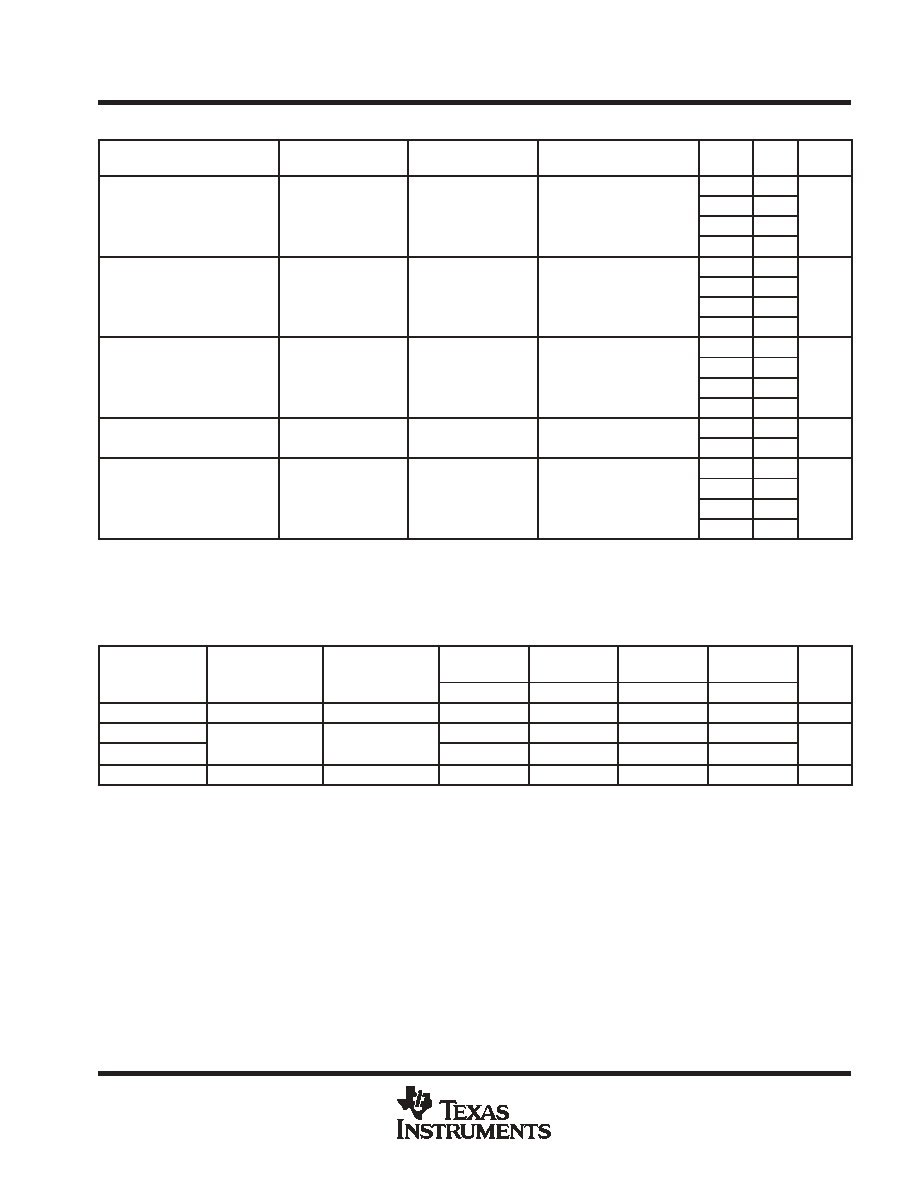

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

VCC

MIN

TYP

MAX

UNIT

VI = 0 V

IO = 4 mA

1.65 V

11

20

VI = 1.65 V

IO = -4 mA

1.65 V

15

50

VI = 0 V

IO = 8 mA

2.3 V

8

12

See

VI = 2.3 V

IO = -8 mA

2.3 V

11

30

ron

On-state switch resistance

See

Figures 1 and 2

VI = 0 V

IO = 24 mA

3 V

7

9.5

ron

On-state switch resistance

Figures 1 and 2

VI = 3 V

IO = -24 mA

3 V

9

20

VI = 0 V

IO = 30 mA

6

7.5

VI = 2.4 V

IO = -30 mA

4.5 V

7

12

VI = 4.5 V

IO = -30 mA

4.5 V

7

15

IA = -4 mA

1.65 V

140

rrange

On-state switch resistance

ß

0

VBn

VCC

IA = -8 mA

2.3 V

45

rrange

On-state switch resistance

over signal rangeß

0

VBn

VCC

(see Figures 1 and 2)

IA = -24 mA

3 V

18

over signal range

(see Figures 1 and 2)

IA = -30 mA

4.5 V

10

VBn = 1.15 V IA = -4 mA

1.65 V

0.5

ron

Difference of on-state

∂#

See Figure 1

VBn = 1.6V

IA = -8 mA

2.3 V

0.1

ron

Difference of on-state

resistance between switches∂#

See Figure 1

VBn = 2.1 V

IA = -24 mA

3 V

0.1

resistance between switches

VBn = 3.15 V IA = -30 mA

4.5 V

0.1

IA = -4 mA

1.65 V

110

ron(flat)

On-state resistance flatness∂||

0

VBn

VCC

IA = -8 mA

2.3 V

26

ron(flat)

On-state resistance flatness∂||

0

VBn

VCC

IA = -24 mA

3 V

9

IA = -30 mA

4.5 V

4

Ioff

k

Off-state switch leakage current

0

VI, VO

VCC, (see Figure 3)

1.65 V

±

1

A

Ioff

k

Off-state switch leakage current

0

VI, VO

VCC, (see Figure 3)

1.65 V

to 5.5 V

±

0.05

±

1

µ

A

IS(on)

On-state switch leakage current

VI = VCC or GND, VO = Open (see Figure 4)

5.5 V

±

1

A

IS(on)

On-state switch leakage current

VI = VCC or GND, VO = Open (see Figure 4)

5.5 V

±

0.1

µ

A

IIN

Control input current

0

VIN

VCC

0 V to

±

1

A

IIN

Control input current

0

VIN

VCC

0 V to

5.5 V

±

0.05

±

1

µ

A

ICC

Supply current

VIN = VCC or GND

5.5 V

1

10

µ

A

ICC

Supply-current change

VIN = VCC - 0.6 V

5.5 V

500

µ

A

Cin

Control input

capacitance

S

5 V

2.7

pF

Cio(off)

Switch input/output

capacitance

Bn

5 V

5.2

pF

Cio(on)

Switch input/output

Bn

5 V

17.3

pF

Cio(on)

Switch input/output

capacitance

A

5 V

17.3

pF

TA = 25

∞

C

Measured by the voltage drop between I/O pins at the indicated current through the switch. On-state resistance is determined by the lower of

the voltages on the two (A or B) ports.

ß Specified by design

∂

ron = ron(max) - ron(min) measured at identical VCC, temperature, and voltage levels.

# This parameter is characterized, but not tested in production.

|| Flatness is defined as the difference between the maximum and minimum values of on-state resistance over the specified range of conditions.

k

Ioff is the same as IS(off) (off-state switch leakage current).

SN74LVC1G3157 Q1

SINGLE POLE, DOUBLE THROW ANALOG SWITCH

SCES463A - JUNE 2003 - REVISED OCTOBER 2003

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

analog switch characteristics, T

A

= 25

∞

C

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

TEST CONDITIONS

VCC

TYP

UNIT

1.65 V

300

Frequency response

A or Bn

Bn or A

RL = 50

,

fin = sine wave

2.3 V

300

MHz

Frequency response

(switch on)

A or Bn

Bn or A

L

fin = sine wave

(see Figure 6)

3 V

300

MHz

(switch on)

(see Figure 6)

4.5 V

300

1.65 V

-54

Crosstalk

B1 or B2

B2

or B1

RL = 50

,

fin = 10 MHz (sine wave)

2.3 V

-54

dB

Crosstalk

(between switches)

B1 or B2

B2

or B1

L

fin = 10 MHz (sine wave)

(see Figure 7)

3 V

-54

dB

(between switches)

(see Figure 7)

4.5 V

-54

1.65 V

-57

Feed-through attenuation

A or Bn

Bn or A

CL = 5 pF, RL = 50

,

fin = 10 MHz (sine wave)

2.3 V

-57

dB

Feed-through attenuation

(switch off)

A or Bn

Bn or A

L

L

fin = 10 MHz (sine wave)

(see Figure 8)

3 V

-57

dB

(switch off)

(see Figure 8)

4.5 V

-57

Charge injectionß

S

A

CL = 0.1 nF, RL = 1 M

,

3.3 V

3

pC

Charge injectionß

S

A

CL = 0.1 nF, RL = 1 M

,

(see Figure 9)

5 V

7

pC

VI = 0.5 V p-p, RL = 600

,

1.65 V

0.1

Total harmonic distortion

A or Bn

Bn or A

VI = 0.5 V p-p, RL = 600

,

fin = 600 Hz to 20 kHz

2.3 V

0.025

%

Total harmonic distortion

A or Bn

Bn or A

fin = 600 Hz to 20 kHz

(sine wave)

(see Figure 10)

3 V

0.015

%

(sine wave)

(see Figure 10)

4.5 V

0.01

Adjust fin voltage to obtain 0 dBm at output. Increase fin frequency until dB meter reads -3 dB.

Adjust fin voltage to obtain 0 dBm at input.

ß Specified by design

switching characteristics over recommended operating free-air temperature range (unless

otherwise noted) (see Figures 5 and 11)

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

VCC = 1.8 V

±

0.15 V

VCC = 2.5 V

±

0.2 V

VCC = 3.3 V

±

0.3 V

VCC = 5 V

±

0.5 V

UNIT

PARAMETER

(INPUT)

(OUTPUT)

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

tpd∂

A or Bn

Bn or A

2

1.2

0.8

0.3

ns

ten#

S

Bn

7

24

3.5

14

2.5

7.6

1.7

5.7

ns

tdis||

S

Bn

3

13

2

7.5

1.5

5.3

0.8

3.8

ns

tB-M

k

0.5

0.5

0.5

0.5

ns

∂ tpd is the slower of tPLH or tPHL. The propagation delay is calculated RC time constant of the typical on-state resistance of the switch and the

specified load capacitance when driven by an ideal voltage source (zero output impedance).

# ten is the slower of tPZL or tPZH.

|| tdis is the slower of tPLZ or tPHZ.

k

Specified by design