TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052E ≠ MARCH 1992 ≠ OCTOBER 1998

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

10-Bit Resolution A/D Converter

D

11 Analog Input Channels

D

Three Built-In Self-Test Modes

D

Inherent Sample-and-Hold Function

D

Total Unadjusted Error . . .

±

1 LSB Max

D

On-Chip System Clock

D

End-of-Conversion (EOC) Output

D

Terminal Compatible With TLC542

D

CMOS Technology

description

The TLC1542C, TLC1542I, TLC1542M, TLC1542Q,

TLC1543C, TLC1543I, and TLC1543Q are CMOS

10-bit switched-capacitor successive-approximation

analog-to-digital converters. These devices have three

inputs and a 3-state output [chip select (CS),

input-output clock (I/O CLOCK), address input

(ADDRESS), and data output (DATA OUT)] that

provide a direct 4-wire interface to the serial port of a

host processor. These devices allow high-speed data

transfers from the host.

In addition to a high-speed A /D converter and versatile

control capability, these devices have an on-chip

14-channel multiplexer that can select any one of 11

analog inputs or any one of three internal self-test

voltages. The sample-and-hold function is automatic.

At the end of A /D conversion, the end-of-conversion

(EOC) output goes high to indicate that conversion is

complete. The converter incorporated in the devices

features differential high-impedance reference inputs

that facilitate ratiometric conversion, scaling, and

isolation of analog circuitry from logic and supply noise.

A switched-capacitor design allows low-error conver-

sion over the full operating free-air temperature range.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright

©

1998, Texas Instruments Incorporated

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

A0

A1

A2

A3

A4

A5

A6

A7

A8

GND

V

CC

EOC

I/O CLOCK

ADDRESS

DATA OUT

CS

REF +

REF ≠

A10

A9

DB, DW, J, OR N PACKAGE

(TOP VIEW)

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

I/O CLOCK

ADDRESS

DATA OUT

CS

REF +

A3

A4

A5

A6

A7

FK OR FN PACKAGE

(TOP VIEW)

A2

A1

A0

A10

REF ≠

EOC

A8

GND

A9

V

CC

TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052E ≠ MARCH 1992 ≠ OCTOBER 1998

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

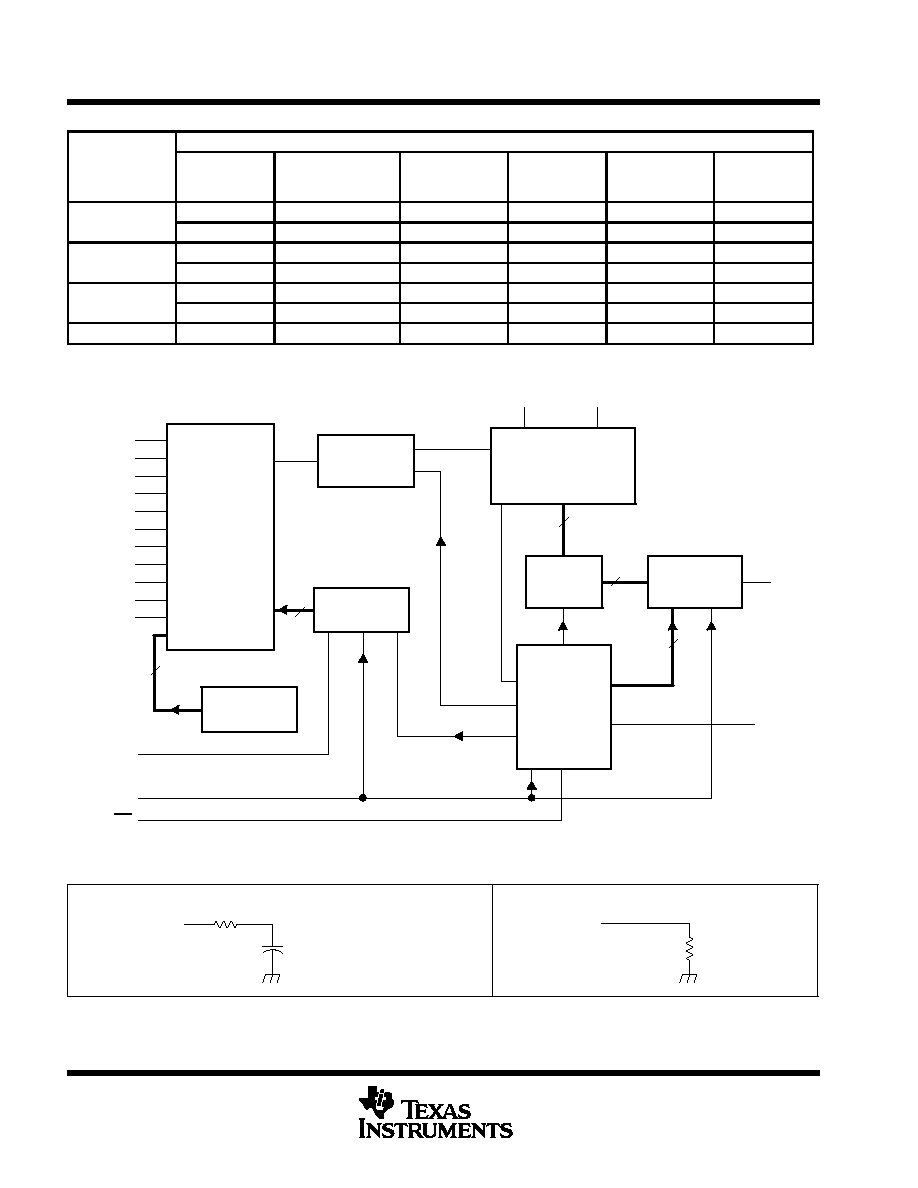

AVAILABLE OPTIONS

PACKAGE

TA

SMALL

OUTLINE

(DB)

SMALL OUTLINE

(DW)

CHIP CARRIER

(FN)

PLASTIC DIP

(N)

CHIP CARRIER

(FK)

CERAMIC DIP

(J)

0

∞

C to 70

∞

C

TLC1542CDW

TLC1542CFN

TLC1542CN

0

∞

C to 70

∞

C

TLC1543CDB

TLC1543CDW

TLC1543CFN

TLC1543CN

40

∞

C to 85

∞

C

TLC1542IDW

TLC1542IFN

TLC1542IN

≠ 40

∞

C to 85

∞

C

TLC1543IDB

TLC1543IDW

TLC1543IFN

TLC1543IN

40

∞

C to 125

∞

C

TLC1542QDB

TLC1542QDW

TLC1542QFN

TLC1542QN

≠ 40

∞

C to 125

∞

C

TLC1543QDB

TLC1543QDW

TLC1543QFN

TLC1543QN

≠ 55

∞

C to 125

∞

C

TLC1542MFK

TLC1542MJ

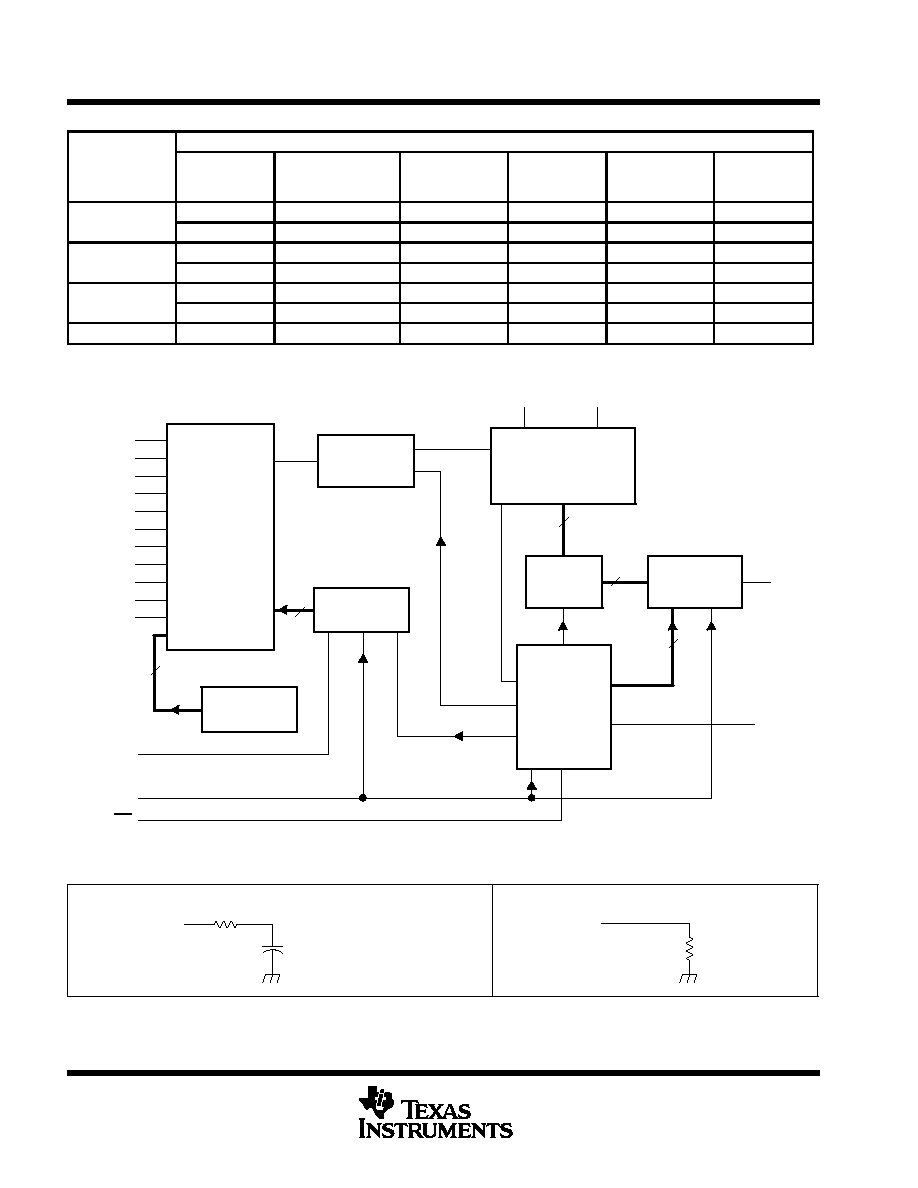

functional block diagram

14-Channel

Analog

Multiplexer

4

10

10

4

REF+

REF ≠

DATA

OUT

ADDRESS

I/O CLOCK

CS

3

EOC

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

1

2

3

4

5

6

7

8

9

11

12

18

15

17

19

16

14

13

10-Bit

Analog-to-Digital

Converter

(switched capacitors)

Sample and

Hold

Input Address

Register

Self-Test

Reference

Output

Data

Register

System

Clock,

Control Logic,

and I/O

Counters

10-to-1 Data

Selector and

Driver

typical equivalent inputs

INPUT CIRCUIT IMPEDANCE DURING SAMPLING MODE

INPUT CIRCUIT IMPEDANCE DURING HOLD MODE

1 k

TYP

Ci = 60 pF TYP

(equivalent input

capacitance)

5 M

TYP

A0 ≠ A10

A0 ≠ A10

TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052E ≠ MARCH 1992 ≠ OCTOBER 1998

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

ADDRESS

17

I

Serial address input. A 4-bit serial address selects the desired analog input or test voltage that is to

be converted next. The address data is presented with the MSB first and shifts in on the first four rising

edges of I/O CLOCK. After the four address bits have been read into the address register, this input

is ignored for the remainder of the current conversion period.

A0 ≠ A10

1 ≠ 9, 11, 12

I

Analog signal inputs. The 11 analog inputs are applied to these terminals and are internally multiplexed.

The driving source impedance should be less than or equal to 1 k

.

CS

15

I

Chip select. A high-to-low transition on this input resets the internal counters and controls and enables

DATA OUT, ADDRESS, and I/O CLOCK within a maximum of a setup time plus two falling edges of

the internal system clock. A low-to-high transition disables ADDRESS and I/O CLOCK within a setup

time plus two falling edges of the internal system clock.

DATA OUT

16

O

The 3-state serial output for the A/D conversion result. This output is in the high-impedance state when

CS is high and active when CS is low. With a valid chip select, DATA OUT is removed from the

high-impedance state and is driven to the logic level corresponding to the MSB value of the previous

conversion result. The next falling edge of I/O CLOCK drives this output to the logic level corresponding

to the next most significant bit, and the remaining bits shift out in order with the LSB appearing on the

ninth falling edge of I/O CLOCK. On the tenth falling edge of I/O CLOCK, DATA OUT is driven to a low

logic level so that serial interface data transfers of more than ten clocks produce zeroes as the unused

LSBs.

EOC

19

O

End of conversion. This output goes from a high to a low logic level on the trailing edge of the tenth I/O

CLOCK and remains low until the conversion is complete and data are ready for transfer.

GND

10

I

The ground return terminal for the internal circuitry. Unless otherwise noted, all voltage measurements

are with respect to this terminal.

I/O CLOCK

18

I

Input/output clock. This terminal receives the serial I/O CLOCK input and performs the following four

functions:

1) It clocks the four input address bits into the address register on the first four rising edges of the I/O

CLOCK with the multiplex address available after the fourth rising edge.

2) On the fourth falling edge of I/O CLOCK, the analog input voltage on the selected multiplex input

begins charging the capacitor array and continues to do so until the tenth falling edge of

I/O CLOCK.

3) It shifts the nine remaining bits of the previous conversion data out on DATA OUT.

4) It transfers control of the conversion to the internal state controller on the falling edge of the tenth

clock.

REF +

14

I

The upper reference voltage value (nominally VCC) is applied to this terminal. The maximum input

voltage range is determined by the difference between the voltage applied to this terminal and the

voltage applied to the REF ≠ terminal.

REF ≠

13

I

The lower reference voltage value (nominally ground) is applied to this terminal.

VCC

20

I

Positive supply voltage

detailed description

With chip select (CS) inactive (high), the ADDRESS and I/O CLOCK inputs are initially disabled and DATA OUT

is in the high-impedance state. When the serial interface takes CS active (low), the conversion sequence begins

with the enabling of I/O CLOCK and ADDRESS and the removal of DATA OUT from the high-impedance state.

The serial interface then provides the 4-bit channel address to ADDRESS and the I/O CLOCK sequence to I/O

CLOCK. During this transfer, the serial interface also receives the previous conversion result from DATA OUT.

I/O CLOCK receives an input sequence that is between 10 and 16 clocks long from the host serial interface.

The first four I/O clocks load the address register with the 4-bit address on ADDRESS, selecting the desired

analog channel, and the next six clocks providing the control timing for sampling the analog input.

TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052E ≠ MARCH 1992 ≠ OCTOBER 1998

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

detailed description (continued)

There are six basic serial-interface timing modes that can be used with the device. These modes are determined

by the speed of I/O CLOCK and the operation of CS as shown in Table 1. These modes are (1) a fast mode with

a 10-clock transfer and CS inactive (high) between conversion cycles, (2) a fast mode with a 10-clock transfer

and CS active (low) continuously, (3) a fast mode with an 11- to 16-clock transfer and CS inactive (high) between

conversion cycles, (4) a fast mode with a 16-clock transfer and CS active (low) continuously, (5) a slow mode

with an 11- to 16-clock transfer and CS inactive (high) between conversion cycles, and (6) a slow mode with

a 16-clock transfer and CS active (low) continuously.

The MSB of the previous conversion appears at DATA OUT on the falling edge of CS in mode 1, mode 3, and

mode 5, on the rising edge of EOC in mode 2 and mode 4, and following the sixteenth clock falling edge in

mode 6. The remaining nine bits are shifted out on the next nine falling edges of I/O CLOCK. Ten bits of data

are transmitted to the host-serial interface through DATA OUT. The number of serial clock pulses used also

depends on the mode of operation, but a minimum of ten clock pulses is required for conversion to begin. On

the tenth clock falling edge, the EOC output goes low and returns to the high logic level when conversion is

complete and the result can be read by the host. Also, on the tenth clock falling edge, the internal logic takes

DATA OUT low to ensure that the remaining bit values are zero when the I/O CLOCK transfer is more than ten

clocks long.

Table 1 lists the operational modes with respect to the state of CS, the number of I/O serial transfer clocks that

can be used, and the timing edge on which the MSB of the previous conversion appears at the output.

Table 1. Mode Operation

MODES

CS

NO. OF

I/O CLOCKS

MSB AT DATA OUT

TIMING

DIAGRAM

Mode 1

High between conversion cycles

10

CS falling edge

Figure 9

Fast Modes

Mode 2

Low continuously

10

EOC rising edge

Figure 10

Fast Modes

Mode 3

High between conversion cycles

11 to 16

CS falling edge

Figure 11

Mode 4

Low continuously

16

EOC rising edge

Figure 12

Slow Modes

Mode 5

High between conversion cycles

11 to 16

CS falling edge

Figure 13

Slow Modes

Mode 6

Low continuously

16

16th clock falling edge

Figure 14

These edges also initiate serial-interface communication.

No more than 16 clocks should be used.

fast modes

The device is in a fast mode when the serial I/O CLOCK data transfer is completed before the conversion is

completed. With a 10-clock serial transfer, the device can only run in a fast mode since a conversion does not

begin until the falling edge of the tenth I/O CLOCK.

mode 1: fast mode, CS inactive (high) between conversion cycles, 10-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers and each transfer is ten clocks long. The

falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The rising edge

of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified delay time.

Also, the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time plus two falling

edges of the internal system clock.

mode 2: fast mode, CS active (low) continuously, 10-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer is ten clocks long. After

the initial conversion cycle, CS is held active (low) for subsequent conversions; the rising edge of EOC then

begins each sequence by removing DATA OUT from the low logic level, allowing the MSB of the previous

conversion to appear immediately on this output.

TLC1542C, TLC1542I, TLC1542M, TLC1542Q, TLC1543C, TLC1543I, TLC1543Q

10-BIT ANALOG-TO-DIGITAL CONVERTERS WITH

SERIAL CONTROL AND 11 ANALOG INPUTS

SLAS052E ≠ MARCH 1992 ≠ OCTOBER 1998

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

mode 3: fast mode, CS inactive (high) between conversion cycles, 11- to 16-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers, and each transfer can be 11 to 16 clocks

long. The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The

rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified

delay time. Also, the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time

plus two falling edges of the internal system clock.

mode 4: fast mode, CS active (low) continuously, 16-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer must be exactly 16 clocks

long. After the initial conversion cycle, CS is held active (low) for subsequent conversions; the rising edge of

EOC then begins each sequence by removing DATA OUT from the low logic level, allowing the MSB of the

previous conversion to appear immediately on this output.

slow modes

In a slow mode, the conversion is completed before the serial I/O CLOCK data transfer is completed. A slow

mode requires a minimum 11-clock transfer into I/O CLOCK, and the rising edge of the eleventh clock must

occur before the conversion period is complete; otherwise, the device loses synchronization with the host-serial

interface and CS has to be toggled to initialize the system. The eleventh rising edge of the I/O CLOCK must

occur within 9.5

µ

s after the tenth I/O clock falling edge.

mode 5: slow mode, CS inactive (high) between conversion cycles, 11- to 16-clock transfer

In this mode, CS is inactive (high) between serial I/O CLOCK transfers and each transfer can be 11 to 16 clocks

long. The falling edge of CS begins the sequence by removing DATA OUT from the high-impedance state. The

rising edge of CS ends the sequence by returning DATA OUT to the high-impedance state within the specified

delay time. Also, the rising edge of CS disables the I/O CLOCK and ADDRESS terminals within a setup time

plus two falling edges of the internal system clock.

mode 6: slow mode, CS active (low) continuously, 16-clock transfer

In this mode, CS is active (low) between serial I/O CLOCK transfers and each transfer must be exactly 16 clocks

long. After the initial conversion cycle, CS is held active (low) for subsequent conversions. The falling edge of

the sixteenth I/O CLOCK then begins each sequence by removing DATA OUT from the low state, allowing the

MSB of the previous conversion to appear immediately at DATA OUT. The device is then ready for the next

16-clock transfer initiated by the serial interface.

address bits

The 4-bit analog channel-select address for the next conversion cycle is presented to the ADDRESS terminal

(MSB first) and is clocked into the address register on the first four leading edges of I/O CLOCK. This address

selects one of 14 inputs (11 analog inputs or three internal test inputs).

analog inputs and test modes

The 11 analog inputs and the three internal test inputs are selected by the 14-channel multiplexer according

to the input address as shown in Tables 2 and 3. The input multiplexer is a break-before-make type to reduce

input-to-input noise injection resulting from channel switching.

Sampling of the analog input starts on the falling edge of the fourth I/O CLOCK, and sampling continues for six

I/O CLOCK periods. The sample is held on the falling edge of the tenth I/O CLOCK. The three test inputs are

applied to the multiplexer, sampled, and converted in the same manner as the external analog inputs.