TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Excellent Output Drive Capability

V

O

=

±

2.5 V Min at R

L

= 100

,

V

CC

±

=

±

5 V

V

O

=

±

12.5 V Min at R

L

= 600

,

V

CC

±

=

±

15 V

D

Low Supply Current . . . 280

µ

A Typ

D

Decompensated for High Slew Rate and

Gain-Bandwidth Product

A

VD

= 0.5 Min

Slew Rate = 10 V/

µ

s Typ

Gain-Bandwidth Product = 6.5 MHz Typ

D

Wide Operating Supply Voltage Range

V

CC

±

=

±

3.5 V to

±

18 V

D

High Open-Loop Gain . . . 280 V/mV Typ

D

Low Offset Voltage . . . 500

µ

V Max

D

Low Offset Voltage Drift With Time

0.04

µ

V/Month Typ

D

Low Input Bias Current . . . 5 pA Typ

description

The TLE2161, TLE2161A, and TLE2161B are

JFET-input, low-power, precision operational

amplifiers manufactured using the Texas

Instruments Excalibur process. Decompensated

for stability with a minimum closed-loop gain of 5,

these devices combine outstanding output drive

capability with low power consumption, excellent

dc precision, and high gain-bandwidth product.

In addition to maintaining the traditional JFET

advantages of fast slew rates and low input bias

and offset currents, the Excalibur process offers

outstanding parametric stability over time and

temperature. This results in a device that remains

precise even with changes in temperature and

over years of use.

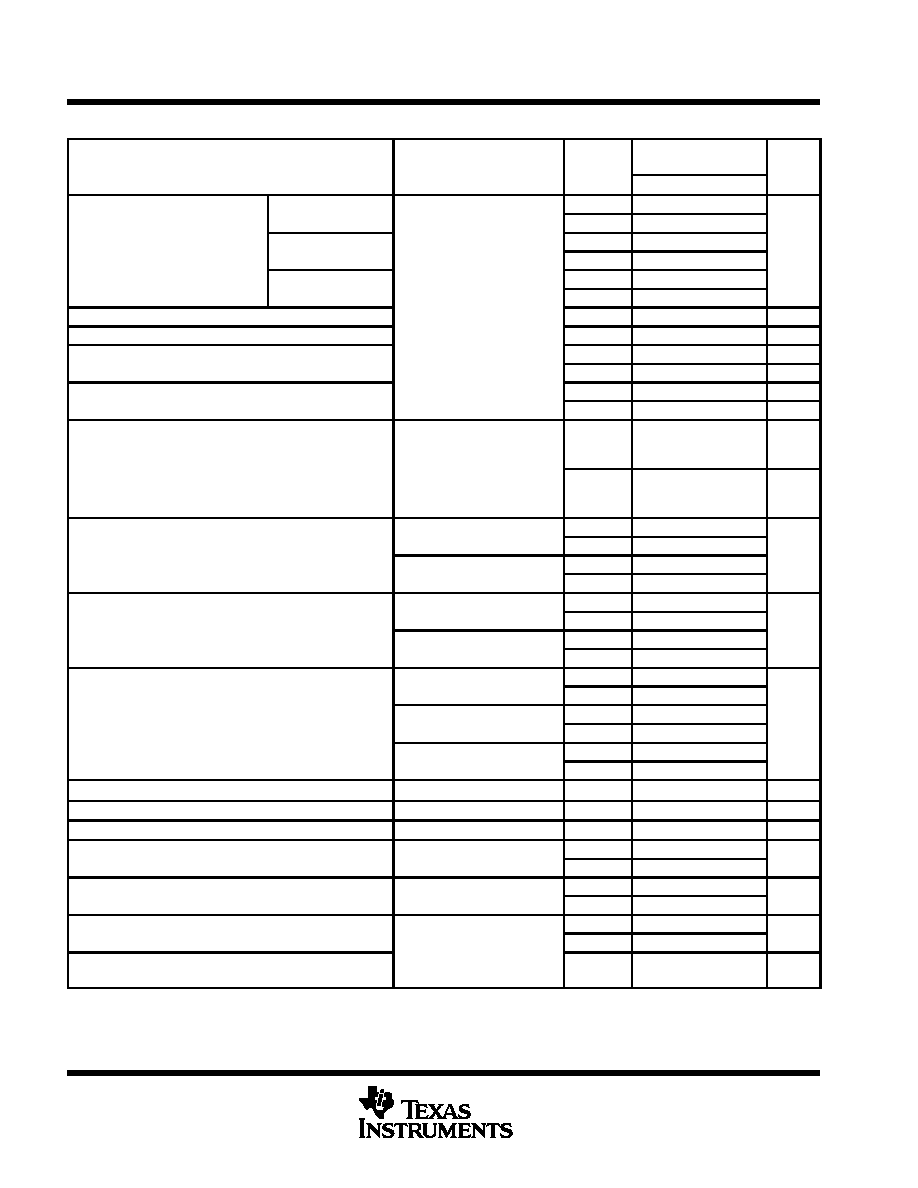

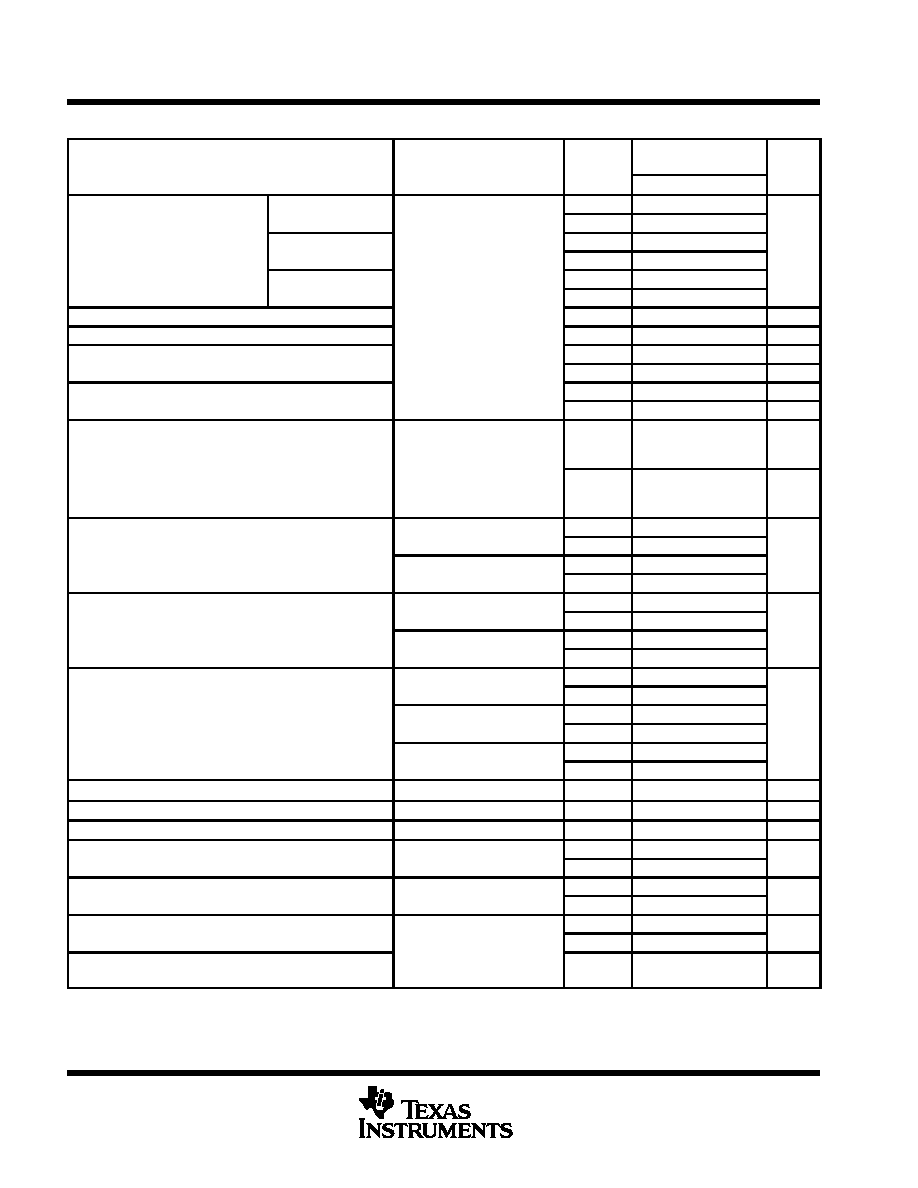

AVAILABLE OPTIONS

PACKAGE

TA

VIOmax

AT 25

∞

C

SMALL

OUTLINE

CHIP

CARRIER

CERAMIC

DIP

PLASTIC

DIP

AT 25 C

OUTLINE

(D)

CARRIER

(FK)

DIP

(JG)

DIP

(P)

0

∞

C

to

500

µ

V

1 5 mV

--

TLE2161ACD

--

--

TLE2161BCP

TLE2161ACP

to

70

∞

C

1.5 mV

3 mV

TLE2161ACD

TLE2161CD

--

--

TLE2161ACP

TLE2161CP

≠ 40

∞

C

to

500

µ

V

1 5 mV

--

TLE2161AID

--

--

TLE2161BIP

TLE2161AIP

to

85

∞

C

1.5 mV

3 mV

TLE2161AID

TLE2161ID

--

--

TLE2161AIP

TLE2161IP

≠ 55

∞

C

to

500

µ

V

1 5 mV

--

TLE2161AMD

--

TLE2161AMFK

TLE2161BMJG

TLE2161AMJG

TLE2161BMP

TLE2161AMP

to

125

∞

C

1.5 mV

3 mV

TLE2161AMD

TLE2161MD

TLE2161AMFK

TLE2161MFK

TLE2161AMJG

TLE2161MJG

TLE2161AMP

TLE2161MP

The D packages are available taped and reeled. Add R suffix to device type (e.g., TLE2161ACDR).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright

©

1996, Texas Instruments Incorporated

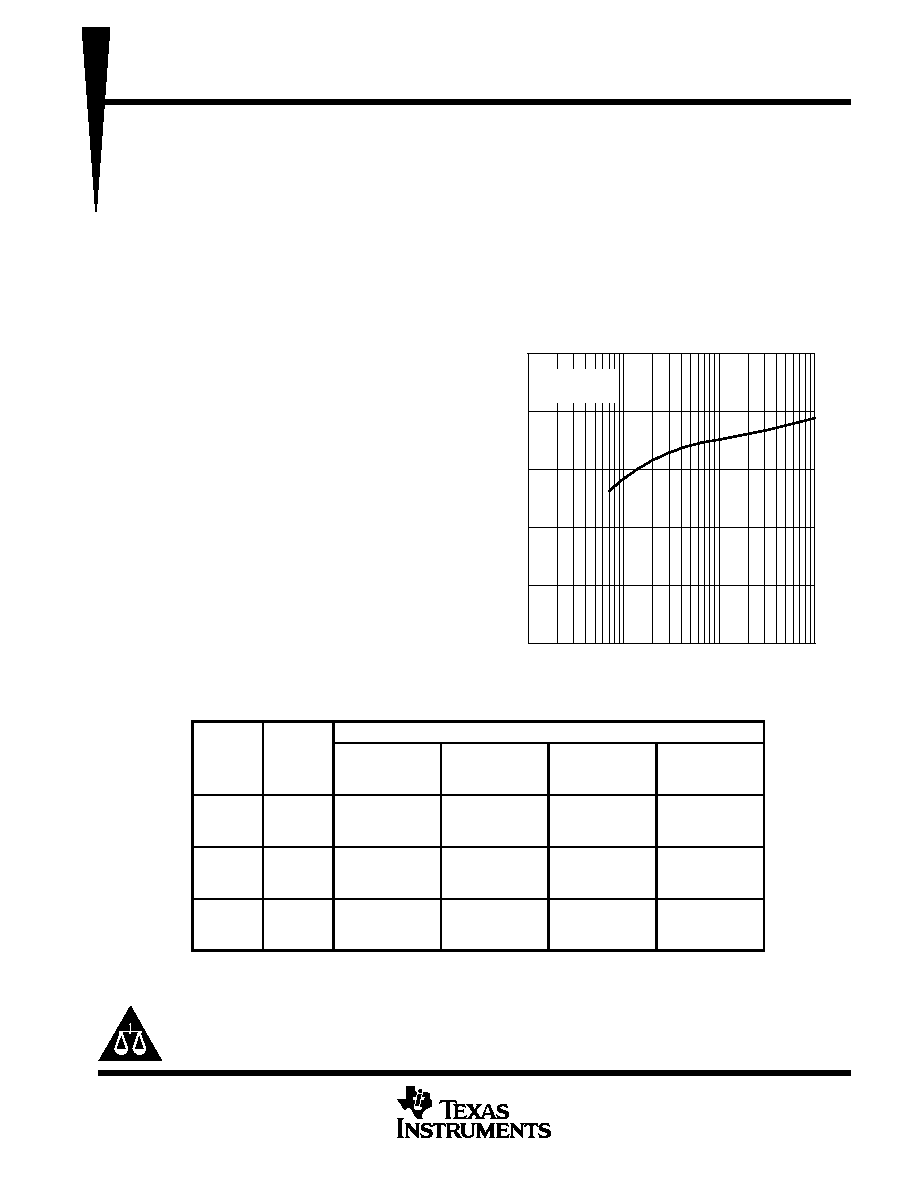

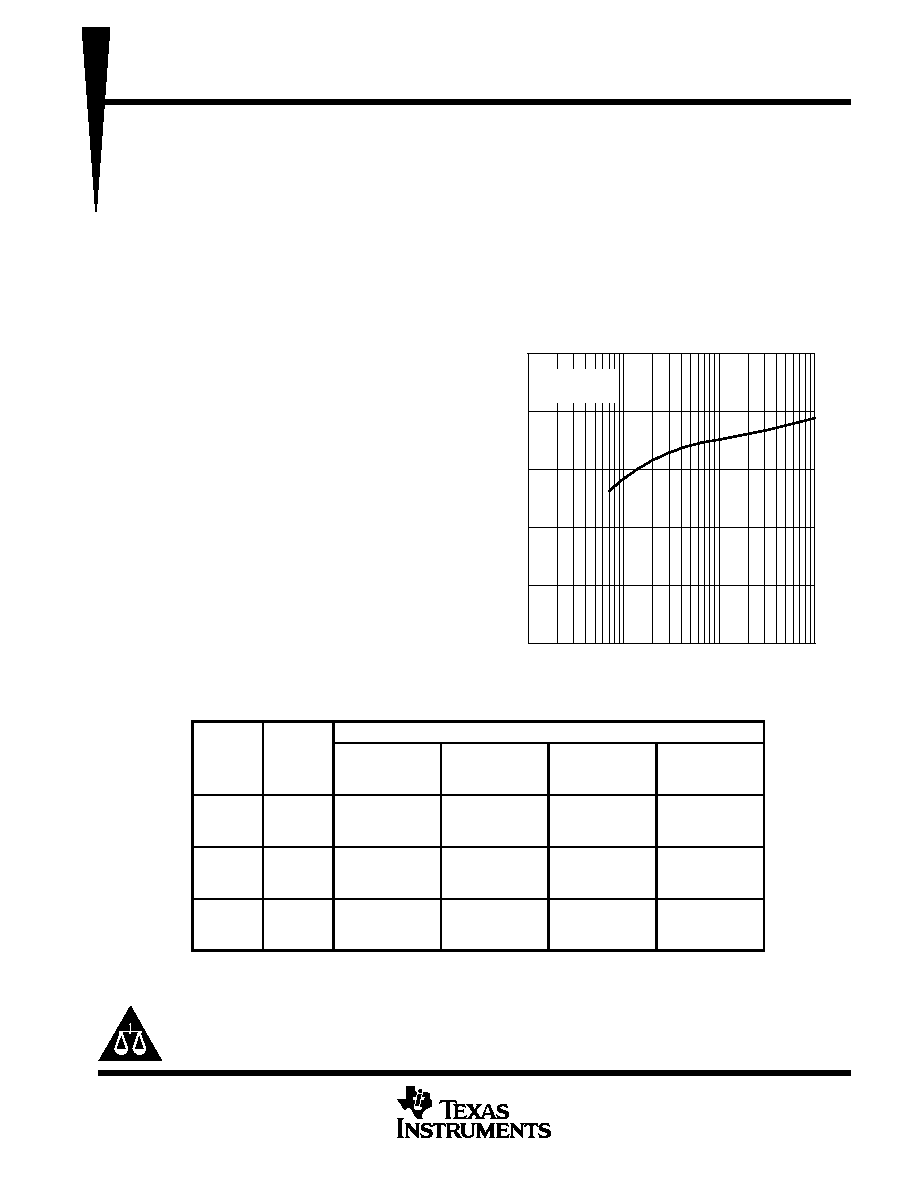

10 k

1 k

100

RL ≠ Load Resistance ≠

10

0

2

4

6

8

10

TA = 25

∞

C

MAXIMUM PEAK-TO-PEAK OUTPUT VOLTAGE

vs

LOAD RESISTANCE

≠ Maximum Peak-to-Peak Output V

oltage ≠ V

V

O(PP)

VCC

±

=

±

5 V

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

description (continued)

A variety of available options includes small-outline packages and chip-carrier versions for high-density system

applications.

The C-suffix devices are characterized for operation from 0

∞

C to 70

∞

C. The I-suffix devices are characterized

for operation from ≠ 40

∞

C to 85

∞

C. The M-suffix devices are characterized for operation over the full military

temperature range of ≠ 55

∞

C to 125

∞

C.

NC

1

2

3

4

8

7

6

5

OFFSET N1

IN ≠

IN +

V

CC ≠

NC

V

CC +

OUT

OFFSET N2

D, JG, OR P PACKAGE

(TOP VIEW)

NC ≠ No internal connection

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

NC

V

CC +

NC

OUT

NC

NC

IN ≠

NC

IN +

NC

FK PACKAGE

(TOP VIEW)

NC

N1

NC

NC

NC

NC

NC

N2

CC

≠

V

equivalent schematic

Q35

Q34

2.7 k

Q10

Q15

VCC ≠

Q2

OFFSET N2

OFFSET N1

1.1 k

R1

15 pF

C1

55 k

1.1 k

R4

R2

Q8

C2 15 pF

Q6

2.4 k

R3

60 k

R5

Q12

Q22

Q21

Q26

Q7

IN ≠

IN +

1.6 pF

C3

Q11

Q20

Q24

Q16

Q17

Q23

R6

Q19

Q18

Q25

Q27

Q28

600

R7

Q31

Q30

Q38

Q39

Q41

Q42

OUT

100

R9

20

R8

Q29

Q43

Q40

Q37

Q36

Q33

Q32

Q5

Q1

Q3

Q14

Q13

Q9

Q4

VCC +

All component values are nominal.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage, V

CC +

(see Note 1)

19 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage, V

CC ≠

≠ 19 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Differential input voltage, V

ID

(see Note 2)

±

38 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

(any input)

V

CC

±

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input current, I

I

(each input)

±

1 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output current, I

O

±

80 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current into V

CC +

80 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current out of V

CC ≠

80 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duration of short-circuit current at (or below) 25

∞

C (see Note 3)

unlimited

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation

See Dissipation Rating Table

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: C suffix

0

∞

C to 70

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

I suffix

≠ 40

∞

C to 85

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

M suffix

≠ 55

∞

C to 125

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

≠ 65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 60 seconds: FK package

260

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D or P package

260

∞

C

. . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 60seconds: JG package

300

∞

C

. . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. All voltage values, except differential voltages, are with respect to the midpoint between VCC +, and VCC ≠.

2. Differential voltages are at IN+ with respect to IN ≠.

3. The output may be shorted to either supply. Temperature and /or supply voltages must be limited to ensure that the maximum

dissipation rating is not exceeded.

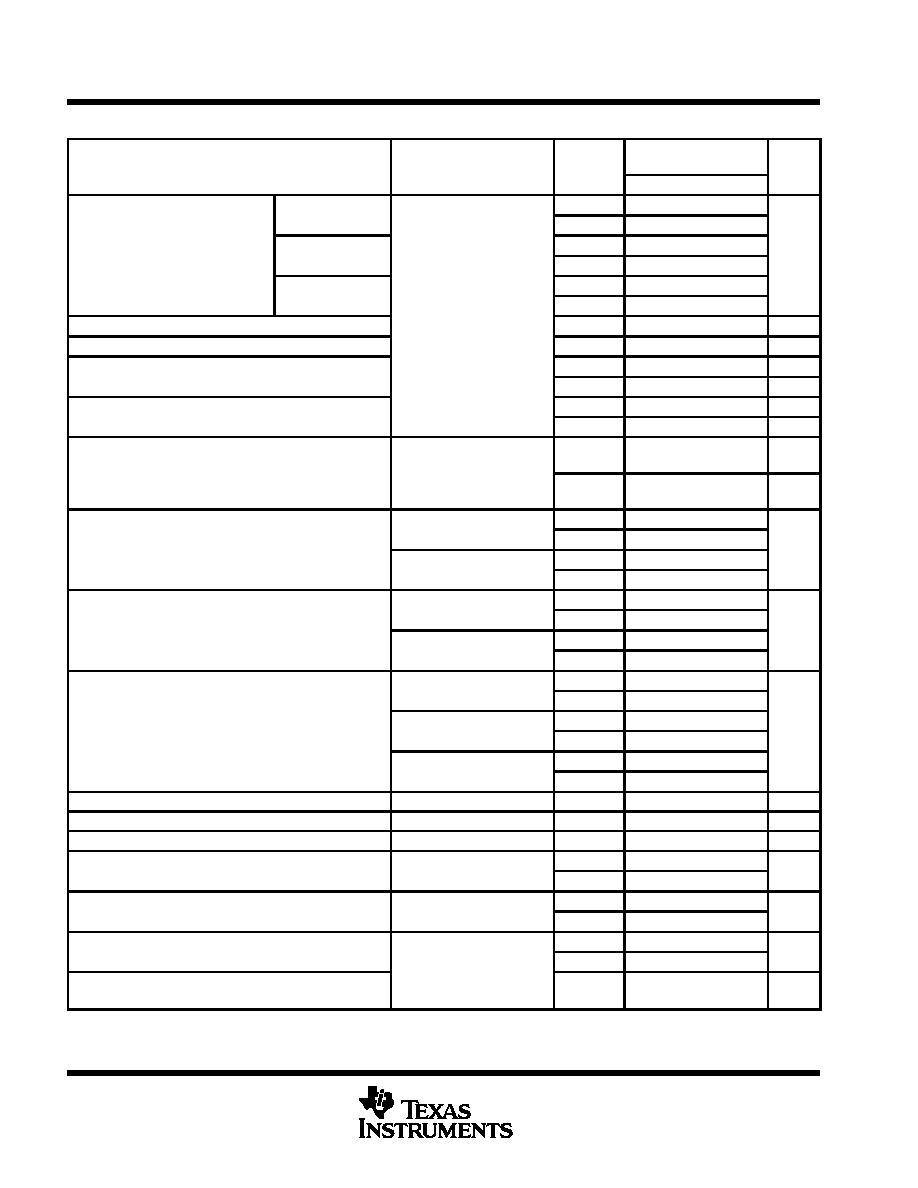

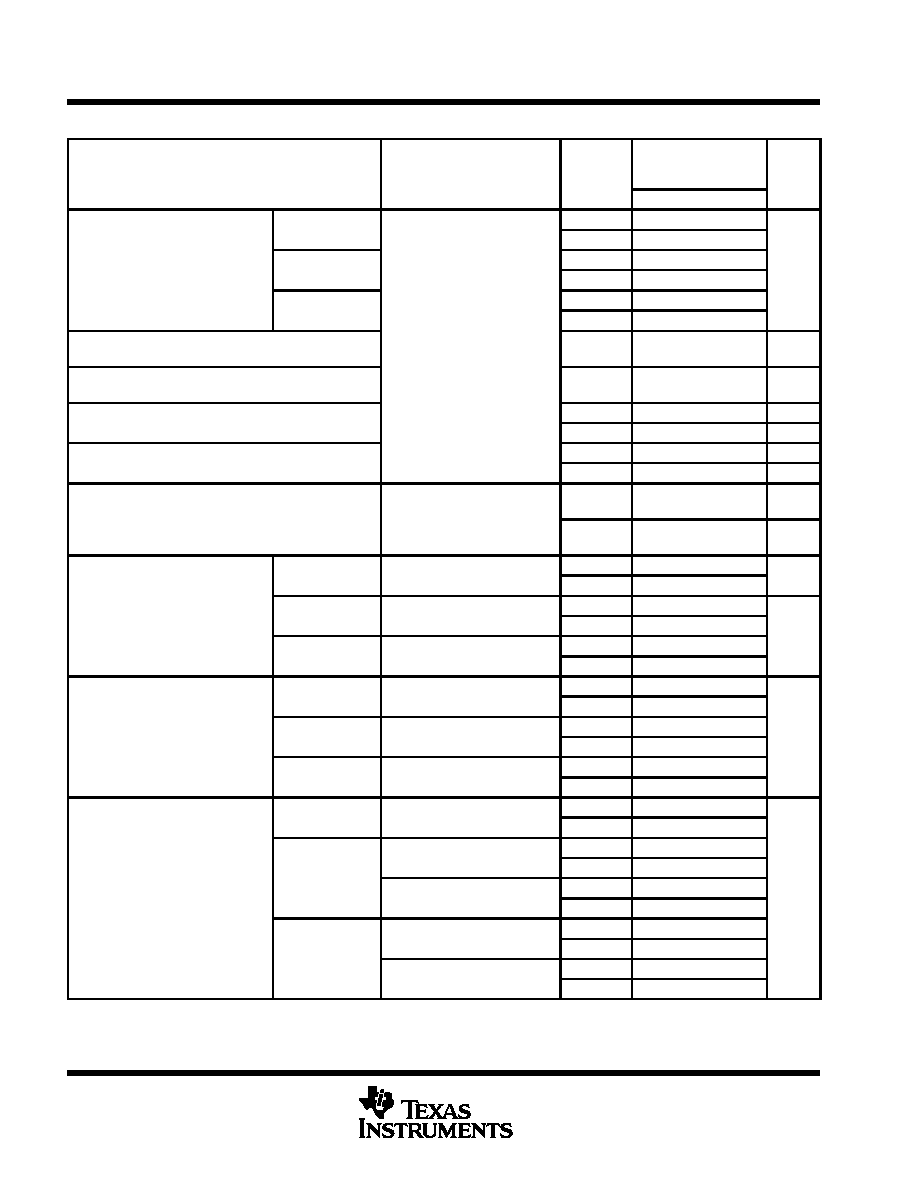

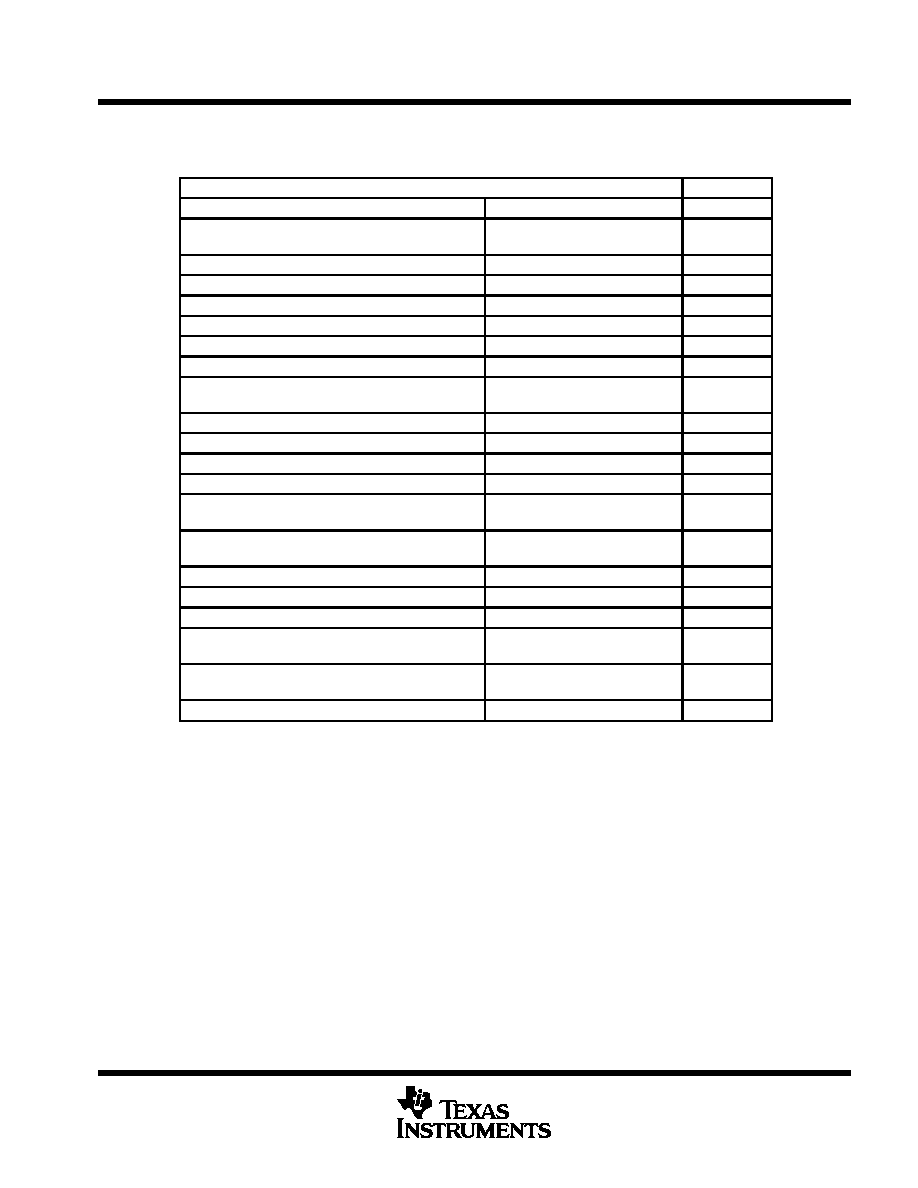

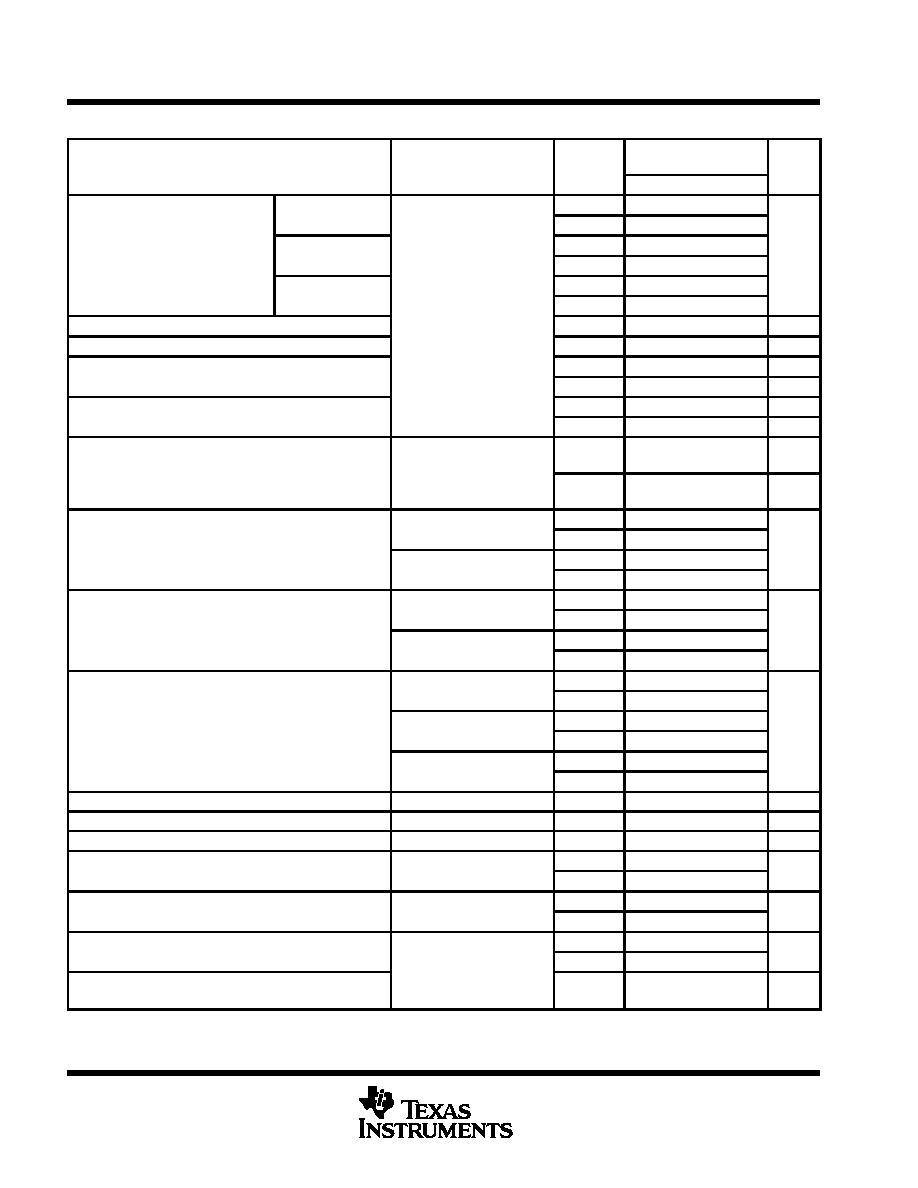

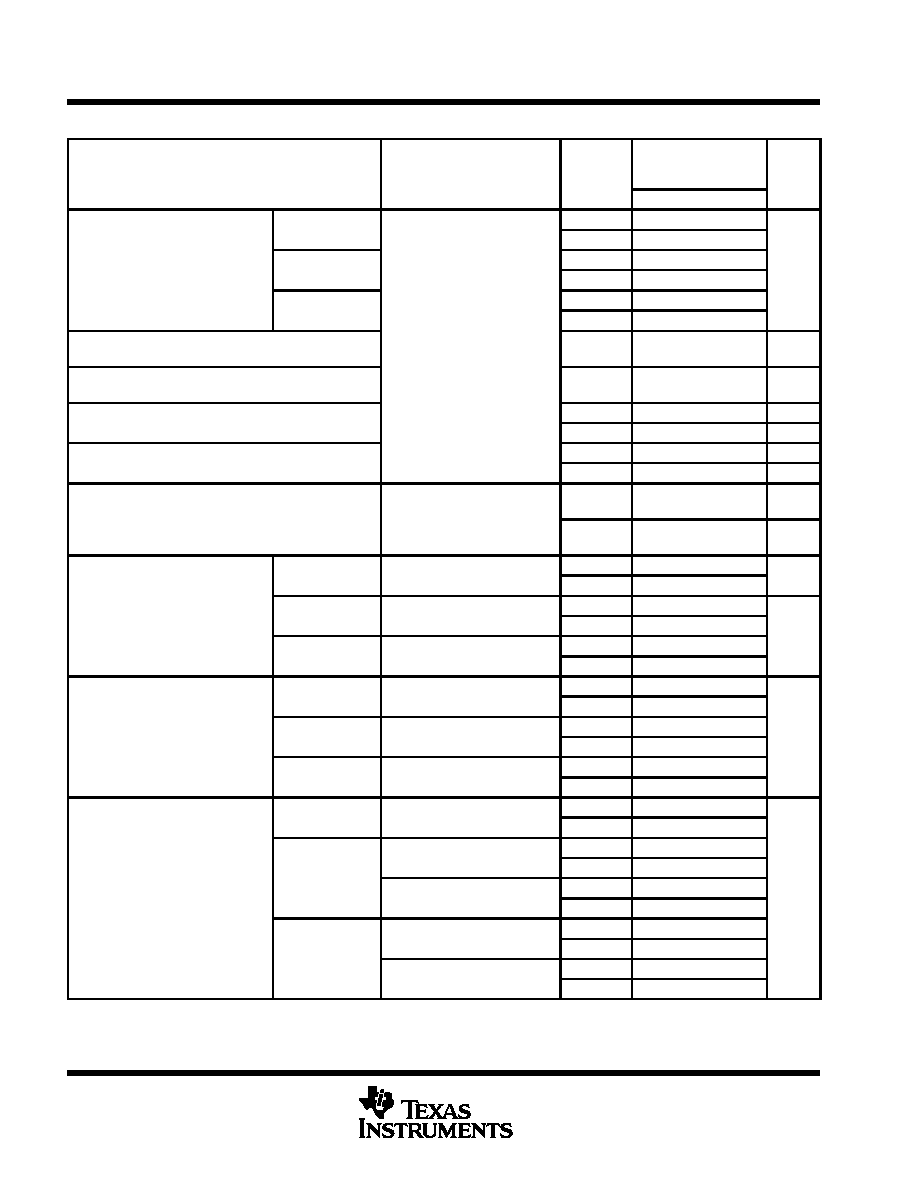

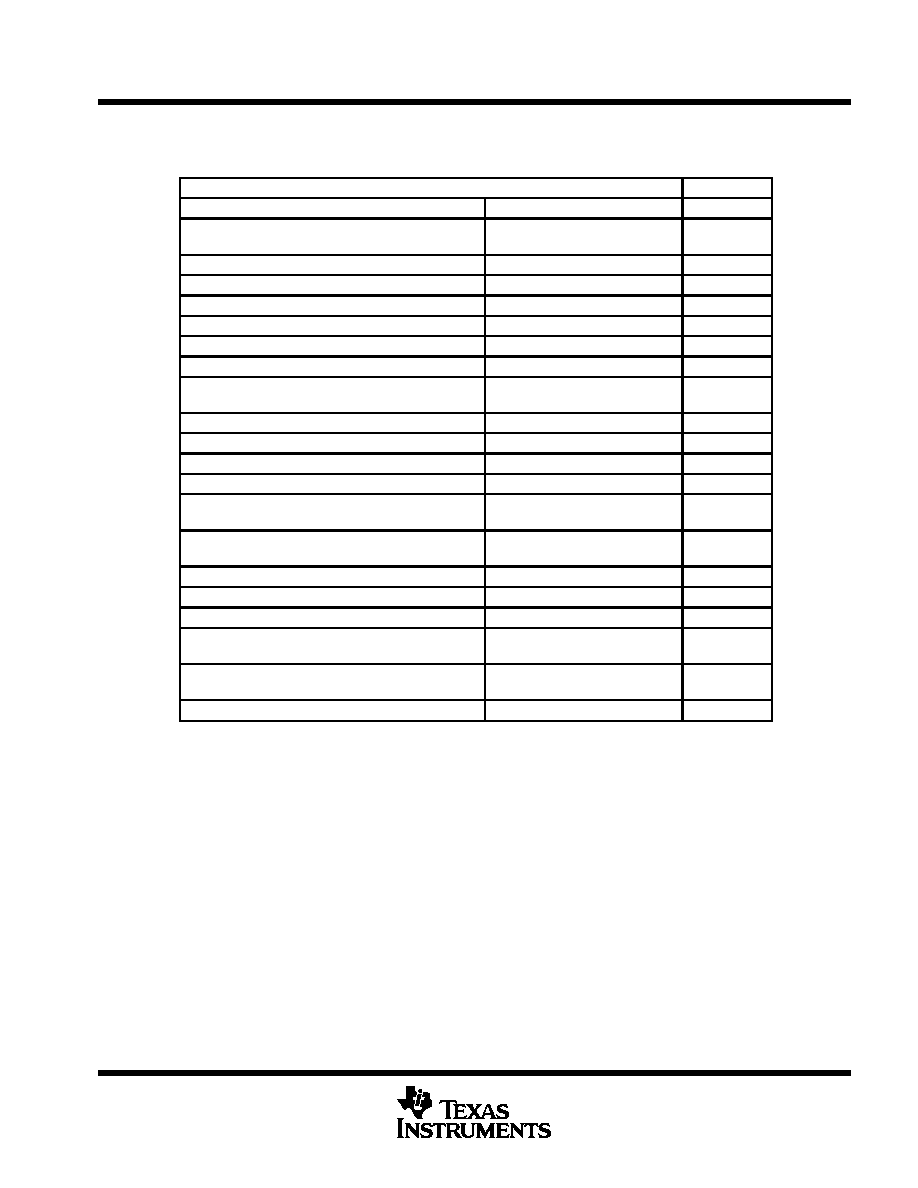

DISSIPATION RATING TABLE

PACKAGE

TA

25

∞

C

POWER RATING

DERATING FACTOR

ABOVE TA = 25

∞

C

TA = 70

∞

C

POWER RATING

TA = 85

∞

C

POWER RATING

TA = 125

∞

C

POWER RATING

D

725 mW

5.8 mW/

∞

C

464 mW

377 mW

145 mW

FK

1375 mW

11.0 mW/

∞

C

880 mW

715 mW

275 mW

JG

1050 mW

8.4 mW/

∞

C

672 mW

546 mW

210 mW

P

1000 mW

8.0 mW/

∞

C

640 mW

520 mW

200 mW

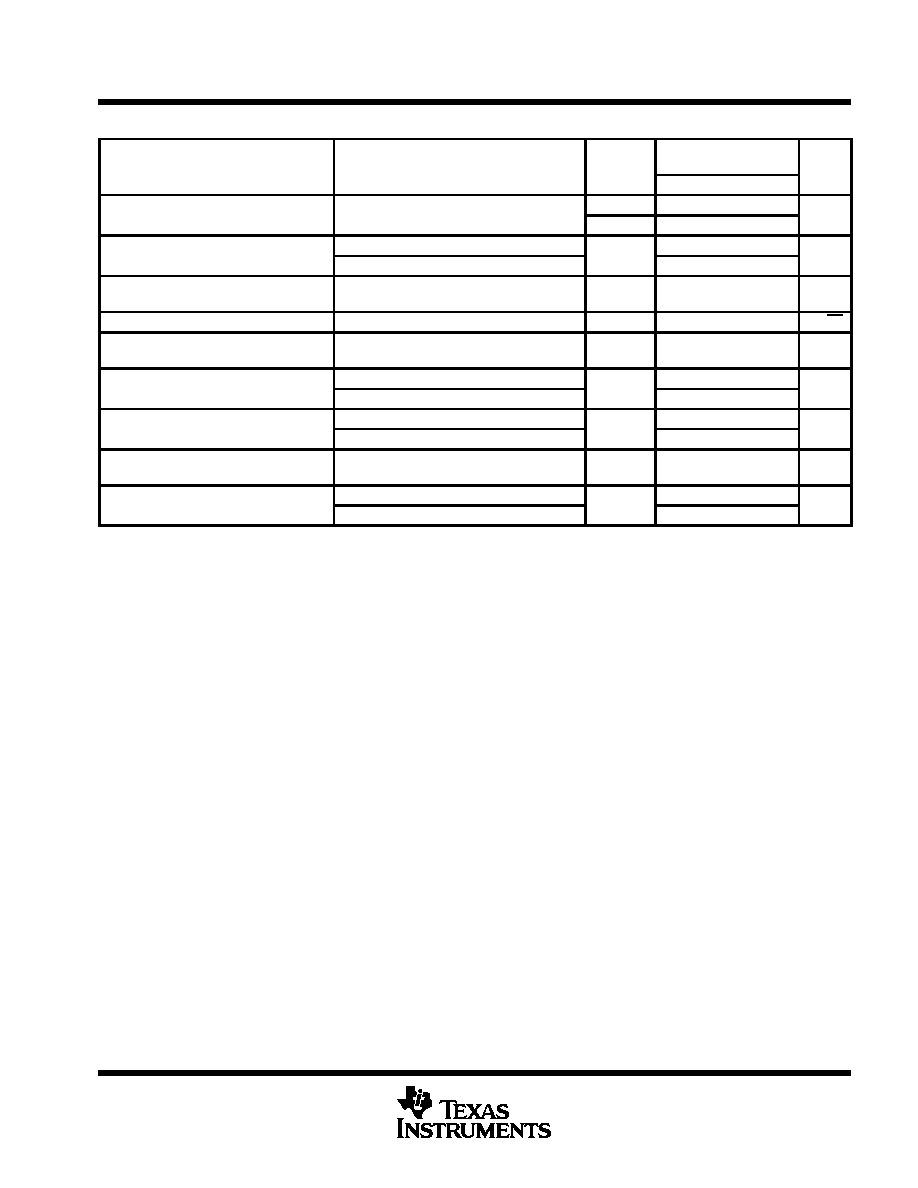

recommended operating conditions

C SUFFIX

I SUFFIX

M SUFFIX

UNIT

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Supply voltage, VCC

±

±

3.5

±

18

±

3.5

±

18

+

3.5

±

18

V

Common mode input voltage VIC

VCC

±

=

±

5 V

≠ 1.6

4

≠ 1.6

4

≠ 1.6

4

V

Common-mode input voltage, VIC

VCC

±

=

±

15 V

≠ 11

13

≠ 11

13

≠ 11

13

V

Operating free-air temperature, TA

0

70

≠ 40

85

≠ 55

125

∞

C

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

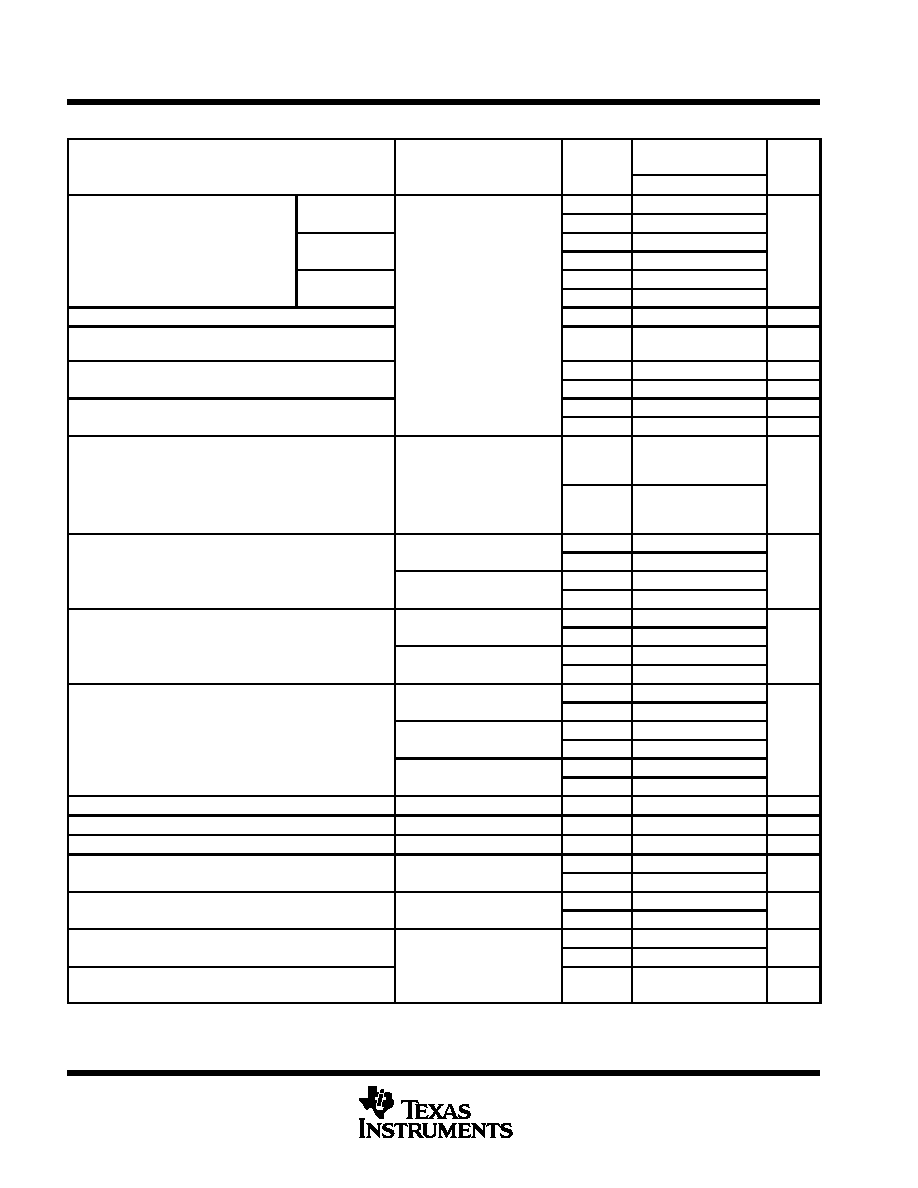

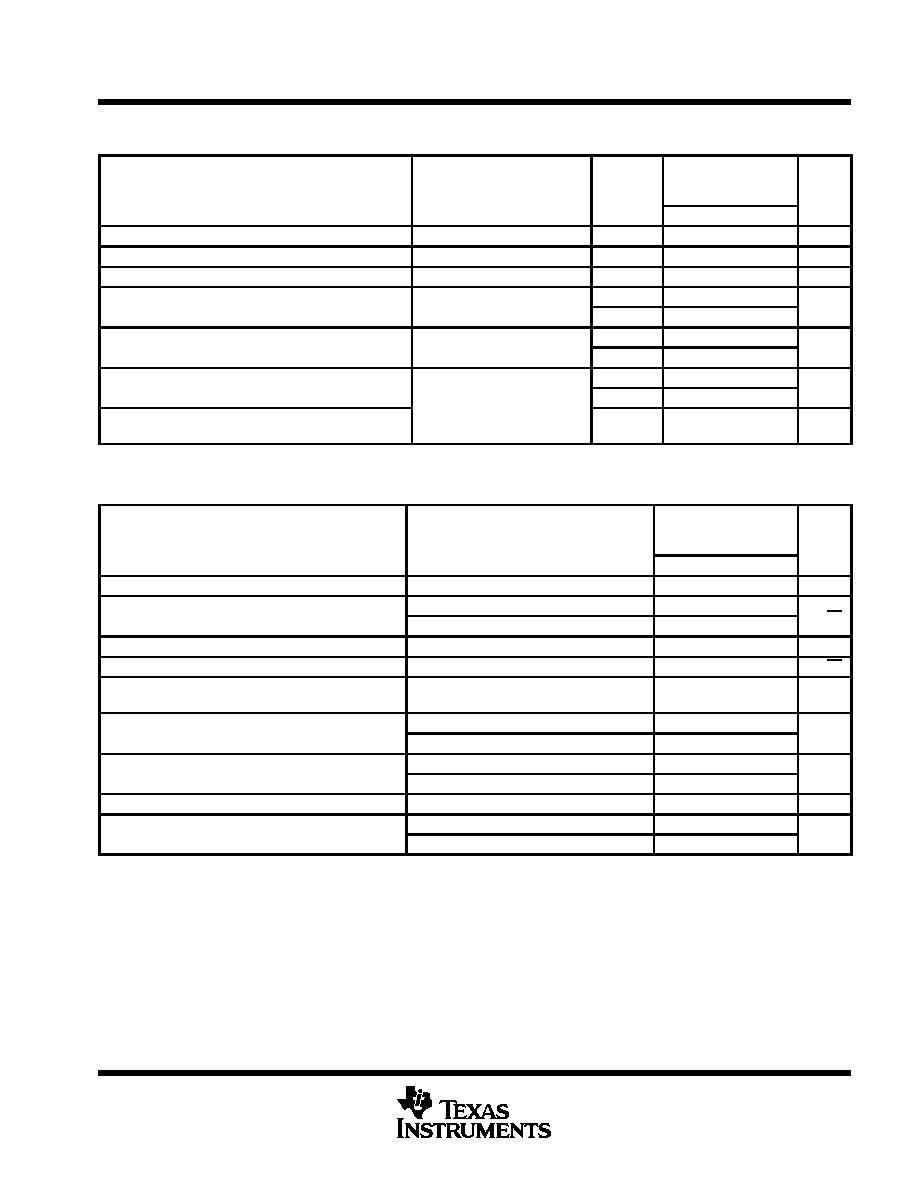

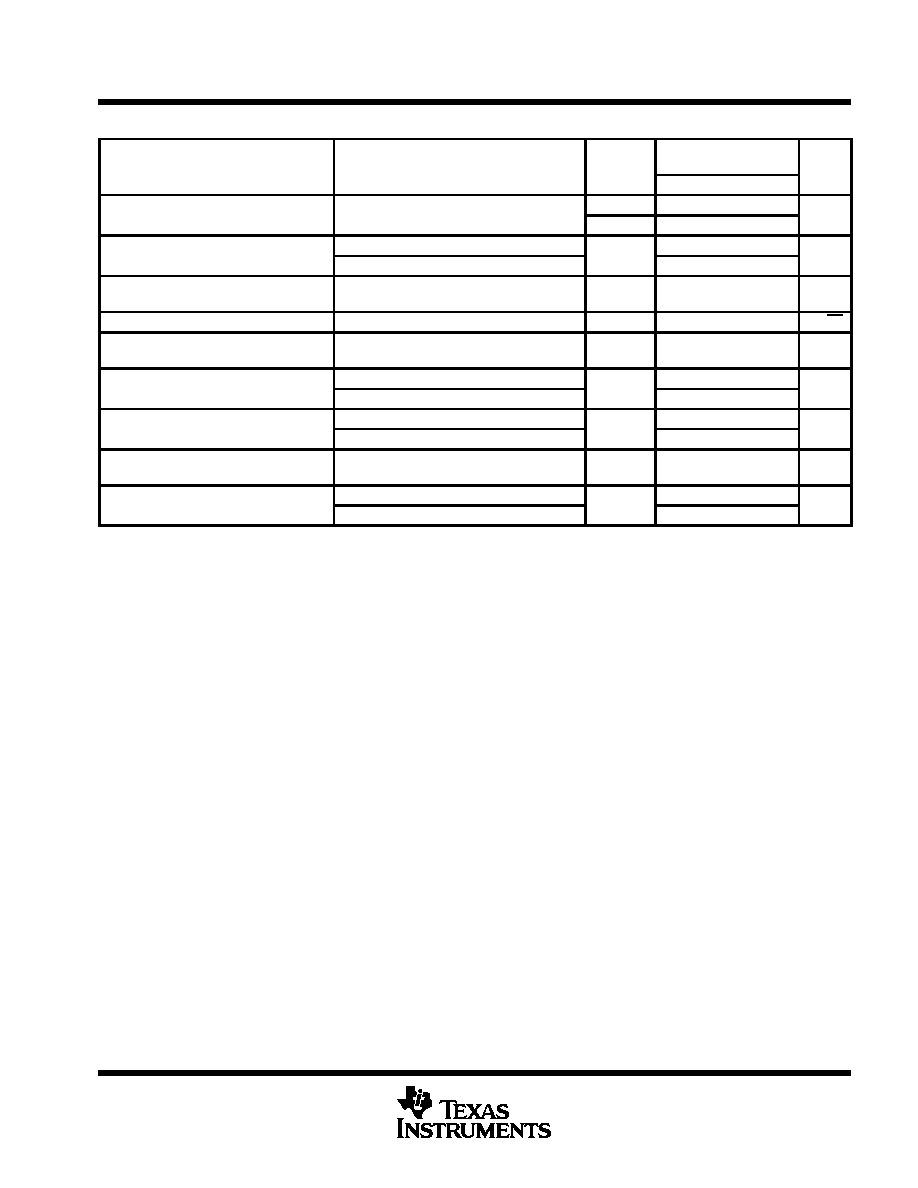

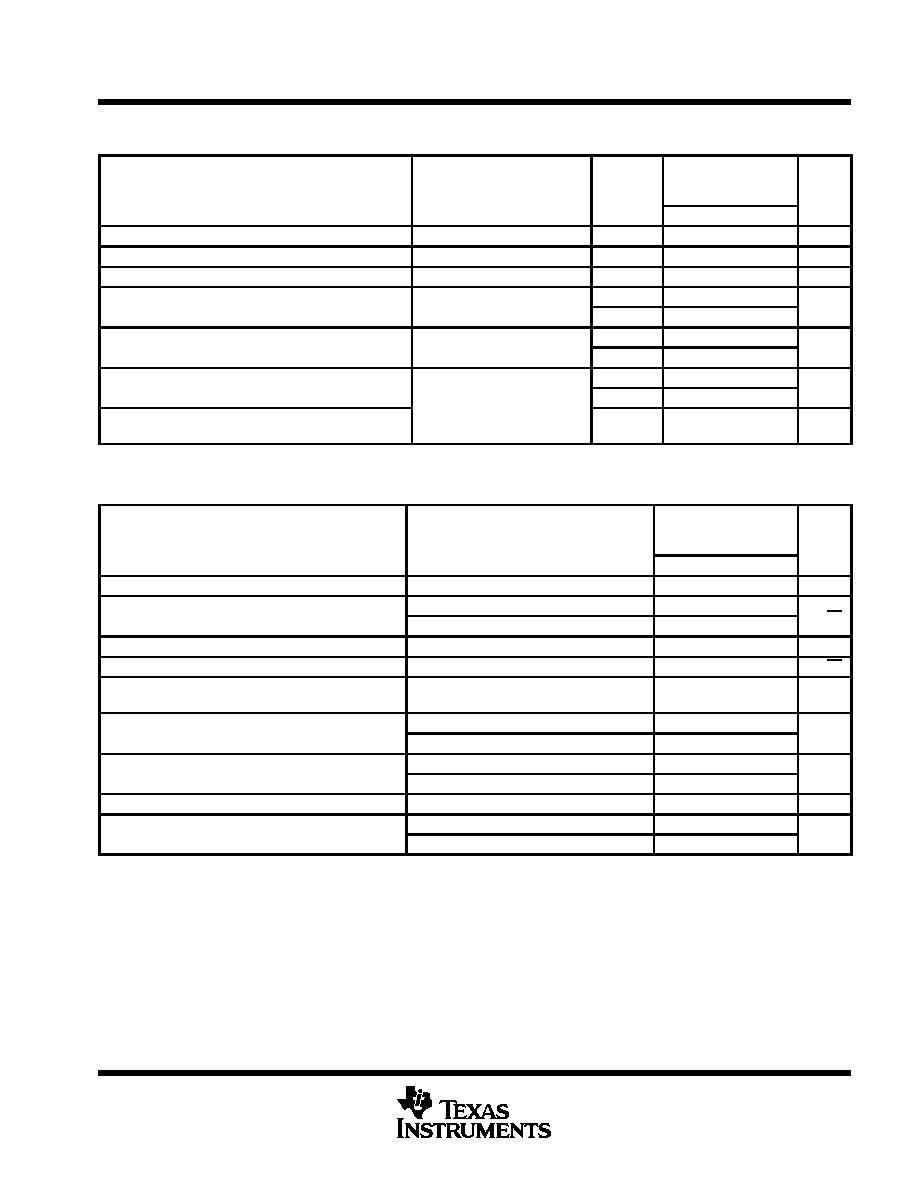

electrical characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161C, TLE2161AC

TLE2161BC

UNIT

A

MIN

TYP

MAX

TLE2161C

25

∞

C

0.8

3.1

TLE2161C

Full range

4

VIO

Input offset voltage

TLE2161AC

25

∞

C

0.6

2.6

mV

VIO

Input offset voltage

TLE2161AC

Full range

3.5

mV

TLE2161BC

25

∞

C

0.5

1.9

TLE2161BC

VIC = 0

RS = 50

Full range

2.4

VIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift (see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

1

pA

IIO

Input offset current

Full range

0.8

nA

IIB

Input bias current

25

∞

C

3

pA

IIB

Input bias current

Full range

2

nA

VICR

Common mode input voltage range

25

∞

C

≠ 1.6

to 4

≠ 2

to 6

V

VICR

Common-mode input voltage range

Full range

≠ 1.6

to 4

V

RL = 10

k

25

∞

C

3.5

3.7

VOM

Maximum positive peak output voltage swing

RL = 10

k

Full range

3.3

V

VOM + Maximum positive peak output voltage swing

RL = 100

25

∞

C

2.5

3.1

V

RL = 100

Full range

2

RL = 10

k

25

∞

C

≠ 3.7

≠ 3.9

VOM

Maximum negative peak output voltage swing

RL = 10

k

Full range

≠ 3.3

V

VOM ≠ Maximum negative peak output voltage swing

RL = 100

25

∞

C

≠ 2.5

≠ 2.7

V

RL = 100

Full range

≠ 2

VO =

±

2 8 V

RL = 10 k

25

∞

C

15

80

VO =

±

2.8 V,

RL = 10 k

Full range

2

AVD

Large signal differential voltage amplification

VO = 0 to 2 V

RL = 100

25

∞

C

0.75

45

V/mV

AVD

Large-signal differential voltage amplification

VO = 0 to 2 V, RL = 100

Full range

0.5

V/mV

VO = 0 to 2 V

RL = 100

25

∞

C

0.5

3

VO = 0 to ≠ 2 V, RL = 100

Full range

0.25

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC=VICRmin

RS = 50

25

∞

C

65

82

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

65

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

±

5 V to

±

15 V,

RS = 50

Full range

75

dB

ICC

Supply current

25

∞

C

280

325

µ

A

ICC

Supply current

VO = 0

No load

Full range

350

µ

A

ICC

Supply-current change over operating

VO = 0,

No load

Full range

29

µ

A

ICC

y

g

g

temperature range

Full range

29

µ

A

Full range is 0

∞

C to 70

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150

∞

C extrapolated

to TA = 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

operating characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161C, TLE2161AC

TLE2161BC

UNIT

A

MIN

TYP

MAX

25

∞

C

7

10

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

Full

range

5

V/

µ

s

V

Equivalent input noise voltage

RS = 20

,

f = 10 Hz

25

∞

C

59

100

nV/

H

Vn

q

g

(see Figure 2)

RS = 20

,

f = 1 kHz

25

∞

C

43

60

nV/

Hz

Vn(PP)

Peak-to-peak equivalent input

noise voltage

f = 0.1 Hz to 10 Hz

25

∞

C

1.1

µ

V

In

Equivalent input noise current

f = 1 kHz

25

∞

C

1

fA/

Hz

THD

Total harmonic distortion

VO(PP) = 2 V,

RL = 10 k

AVD

= 5,

f = 10 kHz,

25

∞

C

0.025%

Gain-bandwidth product

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

25

∞

C

5.8

MHz

(see Figure 3)

f = 100 kHz,

RL

= 100 k

,

CL = 100 pF

25

∞

C

4.3

MHz

t

Settling time

= 0.1%

25

∞

C

5

µ

s

ts

Settling time

= 0.01%

25

∞

C

10

µ

s

BOM

Maximum output-swing

bandwidth

AVD = 5,

RL

= 10 k

25

∞

C

420

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

25

∞

C

70

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 100

,

CL = 100 pF

25

∞

C

84

∞

Full range is 0

∞

C to 70

∞

C.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

6

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

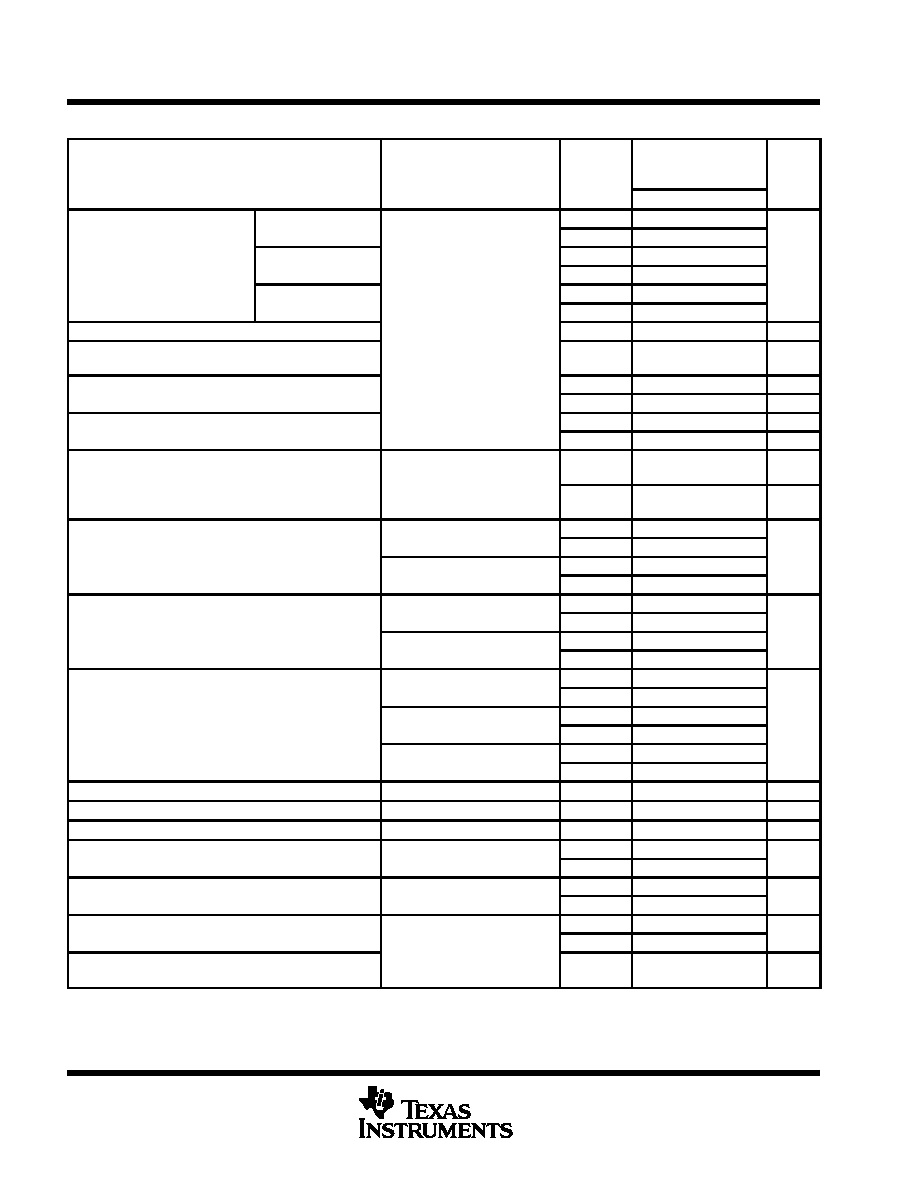

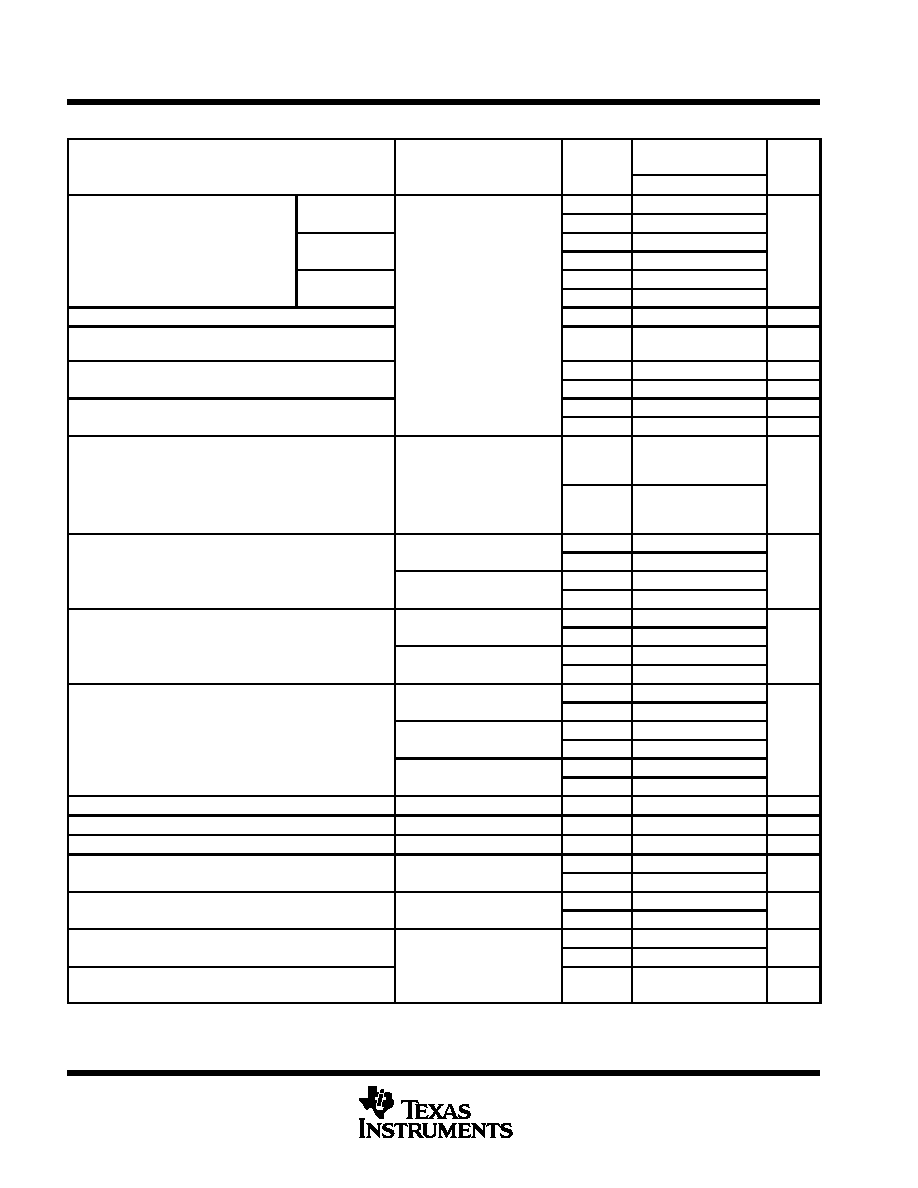

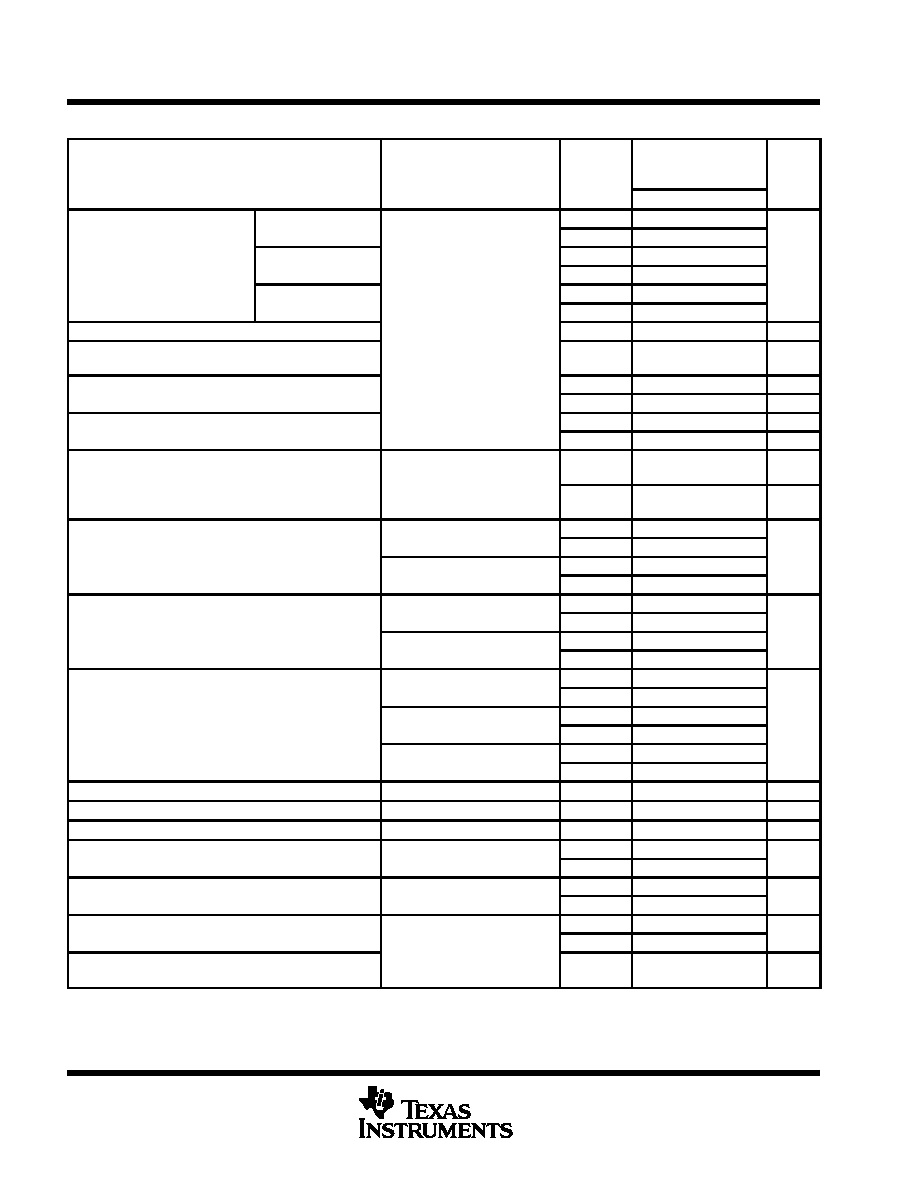

electrical characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161C, TLE2161AC

TLE2161BC

UNIT

A

MIN

TYP

MAX

TLE2161C

25

∞

C

0.6

3

TLE2161C

Full range

3.9

VIO

Input offset voltage

TLE2161AC

25

∞

C

0.5

1.5

mV

VIO

Input offset voltage

TLE2161AC

Full range

2.5

mV

TLE2161BC

25

∞

C

0.3

0.5

TLE2161BC

Full range

1

VIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift

(see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

2

pA

IIO

Input offset current

Full range

1

nA

IIB

Input bias current

25

∞

C

4

pA

IIB

Input bias current

Full range

3

nA

VICR

Common mode input voltage range

25

∞

C

≠ 11

to 13

≠ 12

to 16

V

VICR

Common-mode input voltage range

Full range

≠ 11

to 13

V

RL = 10 k

25

∞

C

13.2

13.7

VOM

Maximum positive peak output voltage swing

RL = 10 k

Full range

13

V

VOM +

Maximum positive peak output voltage swing

RL = 600

25

∞

C

12.5

13.2

V

RL = 600

Full range

12

RL = 10 k

25

∞

C

≠ 13.2

≠ 13.7

VOM

Maximum negative peak output voltage swing

RL = 10 k

Full range

≠ 13

V

VOM ≠

Maximum negative peak output voltage swing

RL = 600

25

∞

C

≠ 12.5

≠ 13

V

RL = 600

Full range

≠ 12

VO =

±

10 V

RL = 10 k

25

∞

C

30

230

VO =

±

10 V,

RL = 10 k

Full range

20

AVD

Large signal differential voltage amplification

VO = 0 to 8 V

RL = 600

25

∞

C

25

100

V/mV

AVD

Large-signal differential voltage amplification

VO = 0 to 8 V,

RL = 600

Full range

10

V/mV

VO = 0 to 8 V

RL = 600

25

∞

C

3

25

VO = 0 to ≠ 8 V,

RL = 600

Full range

1

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC = VICRmin

RS = 50

25

∞

C

72

90

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

70

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

CC

±

,

RS = 50

Full range

75

dB

ICC

Supply current

25

∞

C

290

350

µ

A

ICC

Supply current

VO = 0

No load

Full range

375

µ

A

ICC

Supply-current change over operating

VO = 0,

No load

Full range

34

µ

A

ICC

y

g

g

temperature range

Full range

34

µ

A

Full range is 0

∞

C to 70

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150

∞

C extrapolated

to TA = 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

7

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

operating characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161C, TLE2161AC

TLE2161BC

UNIT

A

MIN

TYP

MAX

SR

Slew rate (see Figure 1)

AVD = 5

RL = 10 k

CL = 100 pF

25

∞

C

7

10

V/

µ

s

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

Full range

5

V/

µ

s

V

Equivalent input noise voltage

RS = 20

,

f = 10 Hz

25

∞

C

70

100

nV/

Hz

Vn

q

g

(see Figure 2)

RS = 20

,

f = 1 kHz

25

∞

C

40

60

nV/

Hz

Vn(PP)

Peak-to-peak equivalent input

noise voltage

f = 0.1 Hz to 10 Hz

25

∞

C

1.1

µ

V

In

Equivalent input noise current

f = 1 kHz

25

∞

C

1.1

fA/

Hz

THD

Total harmonic distortion

VO(PP) = 2 V,

RL = 10 k

AVD

= 5,

f = 10 kHz,

25

∞

C

0.025%

Gain-bandwidth product

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

25

∞

C

6.4

MHz

(see Figure 3)

f = 100 kHz,

RL

= 600

,

CL = 100 pF

25

∞

C

5.6

MHz

t

Settling time

= 0.1%

25

∞

C

5

µ

s

ts

Settling time

= 0.01%

25

∞

C

10

µ

s

BOM

Maximum output-swing

bandwidth

AVD = 5,

RL

= 10 k

25

∞

C

116

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

25

∞

C

72

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 600

,

CL = 100 pF

25

∞

C

78

∞

Full range is 0

∞

C to 70

∞

C.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

8

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161I, TLE2161AI

TLE2161BI

UNIT

A

MIN

TYP

MAX

TLE2161I

25

∞

C

0.8

3.1

TLE2161I

Full range

4.4

VIO

Input offset voltage

TLE2161AI

25

∞

C

0.6

2.6

mV

VIO

Input offset voltage

TLE2161AI

Full range

3.9

mV

TLE2161BI

25

∞

C

0.5

1.9

TLE2161BI

Full range

2.7

VIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift

(see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

1

pA

IIO

Input offset current

Full range

2

nA

IIB

Input bias current

25

∞

C

3

pA

IIB

Input bias current

Full range

4

nA

VICR

Common mode input voltage range

25

∞

C

≠ 1.6

to

4

≠ 2

to

6

V

VICR

Common-mode input voltage range

Full range

≠ 1.6

to

4

V

RL = 10 k

25

∞

C

3.5

3.7

VOM

Maximum positive peak output voltage

RL = 10 k

Full range

3.1

V

VOM +

Maximum positive peak output voltage

RL = 100

25

∞

C

2.5

3.1

V

RL = 100

Full range

2

RL = 10 k

25

∞

C

≠ 3.7

≠ 3.9

VOM

Maximum negative peak output voltage swing

RL = 10 k

Full range

≠ 3.1

V

VOM ≠

Maximum negative peak output voltage swing

RL = 100

25

∞

C

≠ 2.5

≠ 2.7

V

RL = 100

Full range

≠ 2

VO =

±

2 8 V

RL = 10 k

25

∞

C

15

80

VO =

±

2.8 V,

RL = 10 k

Full range

2

AVD

Large signal differential voltage amplification

VO = 0 to 2 V

RL = 100

25

∞

C

0.75

45

V/mV

AVD

Large-signal differential voltage amplification

VO = 0 to 2 V, RL = 100

Full range

0.5

V/mV

VO = 0 to 2 V

RL = 100

25

∞

C

0.5

3

VO = 0 to ≠ 2 V, RL = 100

Full range

0.25

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC=VICRmin

RS = 50

25

∞

C

65

82

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

65

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

CC

±

RS = 50

Full range

65

dB

ICC

Supply current

25

∞

C

280

325

µ

A

ICC

Supply current

VO = 0

No load

Full range

350

µ

A

ICC

Supply-current change over operating

temperature range

VO = 0,

No load

Full range

29

µ

A

Full range is ≠ 40

∞

C to 85

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150

∞

C extrapolated

to TA= 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

9

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

operating characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161I, TLE2161AI

TLE2161BI

UNIT

A

MIN

TYP

MAX

SR

Slew rate (see Figure 1)

AVD = 5

RL = 10 k

CL = 100 pF

25

∞

C

7

10

V/

µ

s

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

Full range

5

V/

µ

s

V

Equivalent input noise

RS = 20

,

f = 10 Hz

25

∞

C

59

100

nV/

Hz

Vn

q

voltage (see Figure 2)

RS = 20

,

f = 1 kHz

25

∞

C

43

60

nV/

Hz

Vn(PP)

Peak-to-peak equivalent

input noise voltage

f = 0.1 Hz to 10 Hz

25

∞

C

1.1

µ

V

In

Equivalent input noise

current

f = 1 kHz

25

∞

C

1

fA/

Hz

THD

Total harmonic distortion

VO(PP) = 2 V,

RL = 10 k

AVD

= 5,

f = 10 kHz,

25

∞

C

0.025%

Gain-bandwidth product

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

25

∞

C

5.8

MHz

(see Figure 3)

f = 100 kHz,

RL

= 100

,

CL = 100 pF

25

∞

C

4.3

MHz

t

Settling time

= 0.1%

25

∞

C

5

µ

s

ts

Settling time

= 0.01%

25

∞

C

10

µ

s

BOM

Maximum output-swing

bandwidth

AVD = 5,

RL

= 10 k

25

∞

C

420

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

25

∞

C

70

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 100

,

CL = 100 pF

25

∞

C

84

∞

Full range is ≠ 40

∞

C to 85

∞

C.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

10

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161I, TLE2161AI

TLE2161BI

UNIT

A

MIN

TYP

MAX

TLE2161I

25

∞

C

0.6

3

TLE2161I

Full range

4.3

VIO

Input offset voltage

TLE2161AI

25

∞

C

0.5

1.5

mV

VIO

Input offset voltage

TLE2161AI

Full range

2.9

mV

TLE2161BI

25

∞

C

0.3

0.5

TLE2161BI

VIC = 0

RS = 50

Full range

1.3

VIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift (see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

2

pA

IIO

Input offset current

Full range

3

nA

IIB

Input bias current

25

∞

C

4

pA

IIB

Input bias current

Full range

5

nA

VICR

Common mode input voltage range

25

∞

C

≠ 11

to

13

≠ 12

to

16

V

VICR

Common-mode input voltage range

Full range

≠ 11

to

13

V

RL = 10 k

25

∞

C

13.2

13.7

VOM

Maximum positive peak output voltage swing

RL = 10 k

Full range

13

V

VOM +

Maximum positive peak output voltage swing

RL = 600

25

∞

C

12.5

13.2

V

RL = 600

Full range

12

RL = 10 k

25

∞

C

≠ 13.2

≠ 13.7

VOM

Maximum negative peak output voltage swing

RL = 10 k

Full range

≠ 13

V

VOM ≠

Maximum negative peak output voltage swing

RL = 600

25

∞

C

≠ 12.5

≠ 13

V

RL = 600

Full range

≠ 12

V0 =

±

10 V

RL = 10 k

25

∞

C

30

230

V0 =

±

10 V,

RL = 10 k

Full range

20

AVD

Large signal differential voltage amplification

V0 = 0 to 8 V

RL = 600

25

∞

C

25

100

V/mV

AVD

Large-signal differential voltage amplification

V0 = 0 to 8 V,

RL = 600

Full range

10

V/mV

V0 = 0 to 8 V

RL = 600

25

∞

C

3

25

V0 = 0 to ≠ 8 V, RL = 600

Full range

1

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC=VICRmin

RS = 50

25

∞

C

72

90

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

65

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

CC

±

RS = 50

Full range

65

dB

ICC

Supply current

25

∞

C

290

350

µ

A

ICC

Supply current

VO = 0

No load

Full range

375

µ

A

ICC

Supply-current change over operating

temperature range

VO = 0,

No load

Full range

34

µ

A

Full range is ≠ 40

∞

C to 85

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA= 150

∞

C extrapolated

to TA = 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

11

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

operating characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161I, TLE2161AI

TLE2161IB

UNIT

A

MIN

TYP

MAX

SR

Slew rate (see Figure 1)

AVD = 5

RL = 10 k

CL = 100 pF

25

∞

C

7

10

V/

µ

s

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

Full range

5

V/

µ

s

V

Equivalent input noise voltage

RS = 20

,

f = 10 Hz

25

∞

C

70

100

nV/

Hz

Vn

q

g

(see Figure 2)

RS = 20

,

f = 1 kHz

25

∞

C

40

60

nV/

Hz

V (PP)

Peak-to-peak equivalent input

f = 0 1 Hz to 10 Hz

25

∞

C

1 1

µ

V

Vn(PP)

q

noise voltage

f = 0.1 Hz to 10 Hz

25

∞

C

1.1

µ

V

In

Equivalent input noise current

f = 1 kHz

25

∞

C

1.1

fA/

Hz

THD

Total harmonic distortion

VO(PP) = 2 V, AVD

= 5,

f = 10 kHz,

25

∞

C

0 025%

THD

Total harmonic distortion

O(PP)

,

RL = 10 k

VD

,

,

25

∞

C

0.025%

Gain-bandwidth product

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

25

∞

C

6.4

MHz

(see Figure 3)

f = 100 kHz,

RL

= 600

,

CL = 100 pF

25

∞

C

5.6

MHz

t

Settling time

= 0.1%

25

∞

C

5

µ

s

ts

Settling time

= 0.01%

25

∞

C

10

µ

s

BOM

Maximum output-swing

AVD = 5

RL = 10 k

25

∞

C

116

kHz

BOM

g

bandwidth

AVD = 5,

RL

= 10 k

25

∞

C

116

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

25

∞

C

72

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 600

,

CL = 100 pF

25

∞

C

78

∞

Full range is ≠ 40

∞

C to 85

∞

C.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

12

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161M

TLE2161AM

TLE2161BM

UNIT

MIN

TYP

MAX

TLE2161M

25

∞

C

0.8

3.1

TLE2161M

Full range

6

VIO

Input offset voltage

TLE2161AM

25

∞

C

0.6

2.6

mV

VIO

Input offset voltage

TLE2161AM

Full range

4.6

mV

TLE2161BM

25

∞

C

0.5

1.9

TLE2161BM

Full range

3.1

VIO

Temperature coefficient of input offset

voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift

(see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

1

pA

IIO

Input offset current

Full range

15

nA

IIB

Input bias current

25

∞

C

3

pA

IIB

Input bias current

Full range

30

nA

VICR

Common mode input voltage range

25

∞

C

≠ 1.6

to 4

≠ 2

to 6

V

VICR

Common-mode input voltage range

Full range

≠ 1.6

to 4

V

All packages

RL = 10 k

25

∞

C

3.5

3.7

V

All packages

RL = 10 k

Full range

3

V

VOM

Maximum positive peak

FK and JG

RL = 600

25

∞

C

2.5

3.6

VOM +

output voltage swing

packages

RL = 600

Full range

2

V

D and P

RL = 100

25

∞

C

2.5

3.1

V

packages

RL = 100

Full range

2

All packages

RL = 10 k

25

∞

C

≠ 3.7

≠ 3.9

All packages

RL = 10 k

Full range

≠ 3

VOM

Maximum negative peak

FK and JG

RL = 600

25

∞

C

≠ 2.5

≠ 3.5

V

VOM ≠

g

output voltage swing

packages

RL = 600

Full range

≠ 2

V

D and P

RL = 100

25

∞

C

≠ 2.5

≠ 2.7

packages

RL = 100

Full range

≠ 2

All packages

V0 =

±

2 8 V

RL = 10 k

25

∞

C

15

80

All packages

V0 =

±

2.8 V,

RL = 10 k

Full range

2

V0 = 0 to 2 5 V

RL = 600

25

∞

C

1

65

FK and JG

V0 = 0 to 2.5 V,

RL = 600

Full range

0.5

AVD

Large-signal differential

packages

V0 = 0 to 2 5 V

RL = 600

25

∞

C

1

16

V/mV

AVD

g

g

voltage amplification

V0 = 0 to ≠ 2.5 V, RL = 600

Full range

0.5

V/mV

V0 = 0 to 2 V

RL = 100

25

∞

C

0.75

45

D and P

V0 = 0 to 2 V,

RL = 100

Full range

0.5

packages

V0 = 0 to 2 V

RL = 100

25

∞

C

0.5

3

V0 = 0 to ≠ 2 V,

RL = 100

Full range

0.25

Full range is ≠ 55

∞

C to 125

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150

∞

C extrapolated

to TA = 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

13

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics at specified free-air temperature, V

CC

±

=

±

5 V (unless otherwise noted

continued)

PARAMETER

TEST CONDITIONS

TA

TLE2161M

TLE2161AM

TLE2161BM

UNIT

MIN

TYP

MAX

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC = VICRmin

RS = 50

25

∞

C

65

82

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

60

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

CC

±

,

RS = 50

Full range

65

dB

ICC

Supply current

25

∞

C

280

325

µ

A

ICC

Supply current

VO = 0

No load

Full range

350

µ

A

ICC

Supply-current change over operating

temperature range

VO = 0,

No load

Full range

39

µ

A

Full range is ≠ 55

∞

C to 125

∞

C.

operating characteristics, V

CC

±

=

±

5 V, T

A

= 25

∞

C

PARAMETER

TEST CONDITIONS

TLE2161M

TLE2161AM

TLE2161BM

UNIT

MIN

TYP

MAX

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

10

V/

µ

s

V

Equivalent input noise voltage (see Figure 2)

RS = 20

,

f = 10 Hz

59

nV/

H

Vn

Equivalent input noise voltage (see Figure 2)

RS = 20

,

f = 1 kHz

43

nV/

Hz

Vn(PP)

Peak-to-peak equivalent input noise voltage

f = 0.1 Hz to 10 Hz

1.1

µ

V

In

Equivalent input noise current

f = 1 kHz

1

fA/

Hz

THD

Total harmonic distortion

AVD

= 5,

RL = 10 k

VO(PP) = 2 V,

f = 10 kHz,

0.025%

Gain bandwidth product (see Figure 3)

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

5.8

MHz

Gain-bandwidth product (see Figure 3)

f = 100 kHz,

RL

= 600 k

,

CL = 100 pF

4.3

MHz

t

Settling time

= 0.1%

5

µ

s

ts

Settling time

= 0.01%

10

µ

s

BOM

Maximum output-swing bandwidth

AVD = 5,

RL

= 10 k

420

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

70

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 600

,

CL = 100 pF

84

∞

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

14

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161M

TLE2161AM

TLE2161BM

UNIT

MIN

TYP

MAX

TLE2161M

25

∞

C

0.6

3

TLE2161M

Full range

6

VIO

Input offset voltage

TLE2161AM

25

∞

C

0.5

1.5

mV

VIO

Input offset voltage

TLE2161AM

Full range

3.6

mV

TLE2161BM

25

∞

C

0.3

0.5

TLE2161BM

Full range

1.7

VIO

Temperature coefficient of input offset voltage

VIC = 0,

RS = 50

Full range

6

µ

V/

∞

C

Input offset voltage long-term drift

(see Note 4)

25

∞

C

0.04

µ

V/mo

IIO

Input offset current

25

∞

C

2

pA

IIO

Input offset current

Full range

20

nA

IIB

Input bias current

25

∞

C

4

pA

IIB

Input bias current

Full range

40

nA

VICR

Common mode input voltage range

25

∞

C

≠ 11

to 13

≠ 12

to 16

V

VICR

Common-mode input voltage range

Full range

≠ 11

to 13

V

RL = 10 k

25

∞

C

13.2

13.7

VOM

Maximum positive peak output voltage swing

RL = 10 k

Full range

12.5

V

VOM +

Maximum positive peak output voltage swing

RL = 600

25

∞

C

12.5

13.2

V

RL = 600

Full range

12

RL = 10 k

25

∞

C

≠ 13.2

≠ 13.7

VOM

Maximum negative peak output voltage swing

RL = 10 k

Full range

≠ 12.5

V

VOM ≠

Maximum negative peak output voltage swing

RL = 600

25

∞

C

≠ 12.5

≠ 13

V

RL = 600

Full range

≠ 12

VO =

±

10 V

RL = 10 k

25

∞

C

30

230

VO =

±

10 V,

RL = 10 k

Full range

20

AVD

Large signal differential voltage amplification

VO = 0 to 8 V

RL = 600

25

∞

C

25

100

V/mV

AVD

Large-signal differential voltage amplification

VO = 0 to 8 V,

RL = 600

Full range

7

V/mV

VO = 0 to 8 V

RL = 600

25

∞

C

3

25

VO = 0 to ≠ 8 V,

RL = 600

Full range

1

ri

Input resistance

25

∞

C

1012

ci

Input capacitance

25

∞

C

4

pF

zo

Open-loop output impedance

IO = 0

25

∞

C

280

CMRR

Common mode rejection ratio

VIC = VICRmin

RS = 50

25

∞

C

72

90

dB

CMRR

Common-mode rejection ratio

VIC = VICRmin, RS = 50

Full range

65

dB

kSVR

Supply voltage rejection ratio (

VCC

±

/

VIO)

VCC

±

=

±

5 V to

±

15 V,

25

∞

C

75

93

dB

kSVR

Supply-voltage rejection ratio (

VCC

±

/

VIO)

CC

±

RS = 50

Full range

65

dB

ICC

Supply current

25

∞

C

290

350

µ

A

ICC

Supply current

VO = 0

No load

Full range

375

µ

A

ICC

Supply-current change over operating

temperature range

VO = 0,

No load

Full range

46

µ

A

Full range is ≠ 55

∞

C to 125

∞

C.

NOTE 4: Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150

∞

C extrapolated

to TA = 25

∞

C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

15

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

operating characteristics at specified free-air temperature, V

CC

±

=

±

15 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

TA

TLE2161M

TLE2161AM

TLE2161BM

UNIT

MIN

TYP

MAX

SR

Slew rate (see Figure 1)

AVD = 5

RL = 10 k

CL = 100 pF

25

∞

C

7

10

V/

µ

s

SR

Slew rate (see Figure 1)

AVD = 5,

RL = 10 k

,

CL = 100 pF

Full range

5

V/

µ

s

V

Equivalent input noise voltage

RS = 20

,

f = 10 Hz

25

∞

C

70

nV/

Hz

Vn

q

g

(see Figure 2)

RS = 20

,

f = 1 kHz

25

∞

C

40

nV/

Hz

VN(PP)

Peak-to-peak equivalent input

noise voltage

f = 0.1 Hz to 10 Hz

25

∞

C

1.1

µ

V

In

Equivalent input noise current

f = 1 Hz

25

∞

C

1.1

fA/

Hz

THD

Total harmonic distortion

VO(PP) = 2 V,

RL = 10 k

AVD

= 5,

f = 10 kHz,

25

∞

C

0.025%

Gain-bandwidth product

f = 100 kHz,

RL = 10 k

,

CL = 100 pF

25

∞

C

6.4

MHz

(see Figure 3)

f = 100 kHz,

RL

= 600

,

CL = 100 pF

25

∞

C

5.6

MHz

t

Settling time

= 0.1%

25

∞

C

5

µ

s

ts

Settling time

= 0.01%

25

∞

C

10

µ

s

BOM

Maximum output-swing

bandwidth

AVD = 5,

RL

= 10 k

25

∞

C

116

kHz

Phase margin (see Figure 3)

AVD = 5,

RL

= 10 k

,

CL = 100 pF

25

∞

C

72

∞

m

Phase margin (see Figure 3)

AVD = 5,

RL

= 600

,

CL = 100 pF

25

∞

C

78

∞

Full range is ≠ 55

∞

C to 125

∞

C.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

16

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

2 k

8 k

(see Note A)

CL

VO

VCC ≠

VI

+

≠

VCC +

NOTE A: CL includes fixture capacitance.

Figure 1. Slew-Rate Test Circuit

VO

RS

RS

2 k

VCC ≠

VCC +

+

≠

Figure 2. Noise-Voltage Test Circuit

VO

RL

CL

(see Note A)

10 k

100

VI

VCC ≠

VCC +

+

≠

NOTE A: CL includes fixture capacitance.

Figure 3. Gain-Bandwidth Product and Phase-Margin Test Circuit

typical values

Typical values presented in this data sheet represent the median (50% point) of device parametric performance.

Input bias and offset current

At the picoampere bias-current level typical of the TLE2161, TLE2161A, and TLE2161B, accurate

measurement of the bias current becomes difficult. Not only does this measurement require a picoammeter,

but test socket leakages can easily exceed the actual device bias currents. To accurately measure these small

currents, Texas Instruments uses a two-step process. The socket leakage is measured using picoammeters

with bias voltages applied but with no device in the socket. The device is then inserted into the socket, and a

second test that measures both the socket leakage and the device input bias current is performed. The two

measurements are then subtracted algebraically to determine the bias current of the device.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

17

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

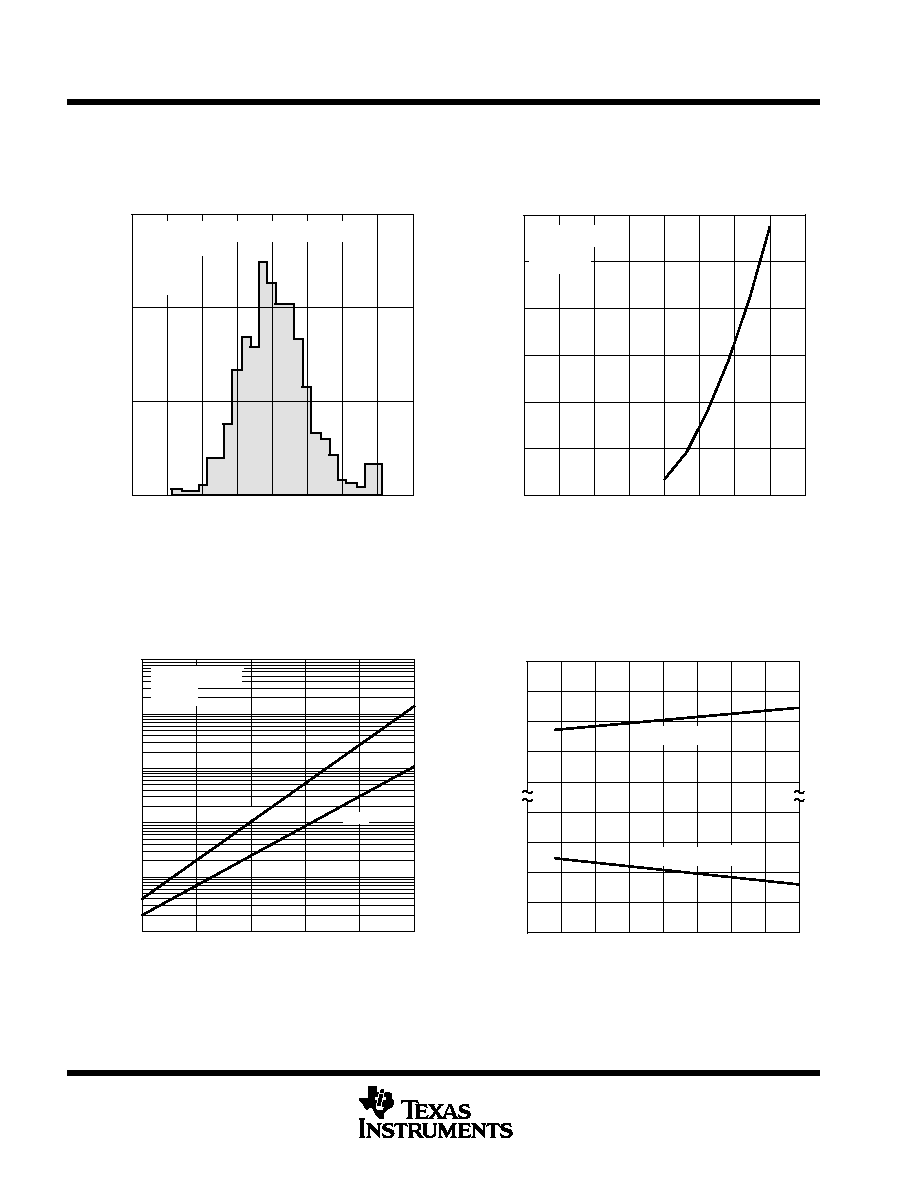

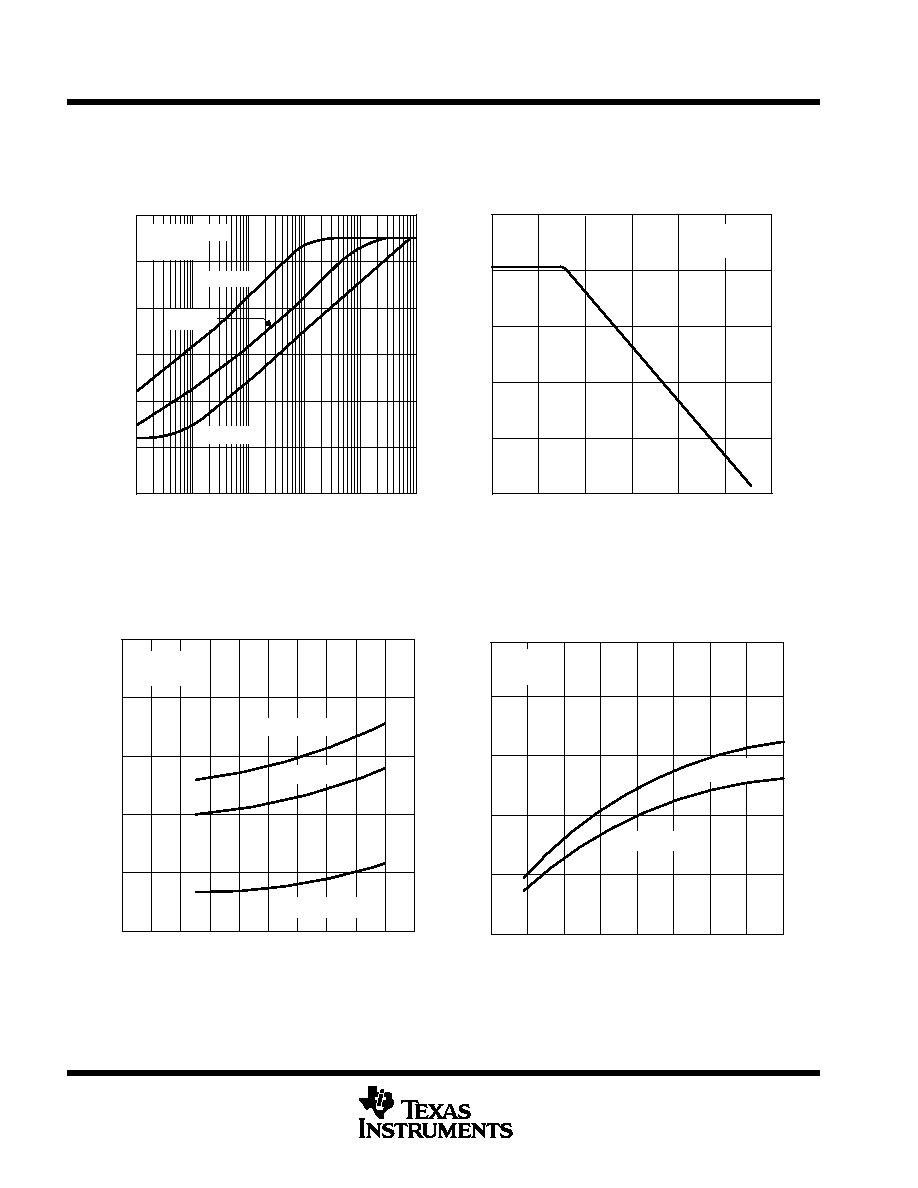

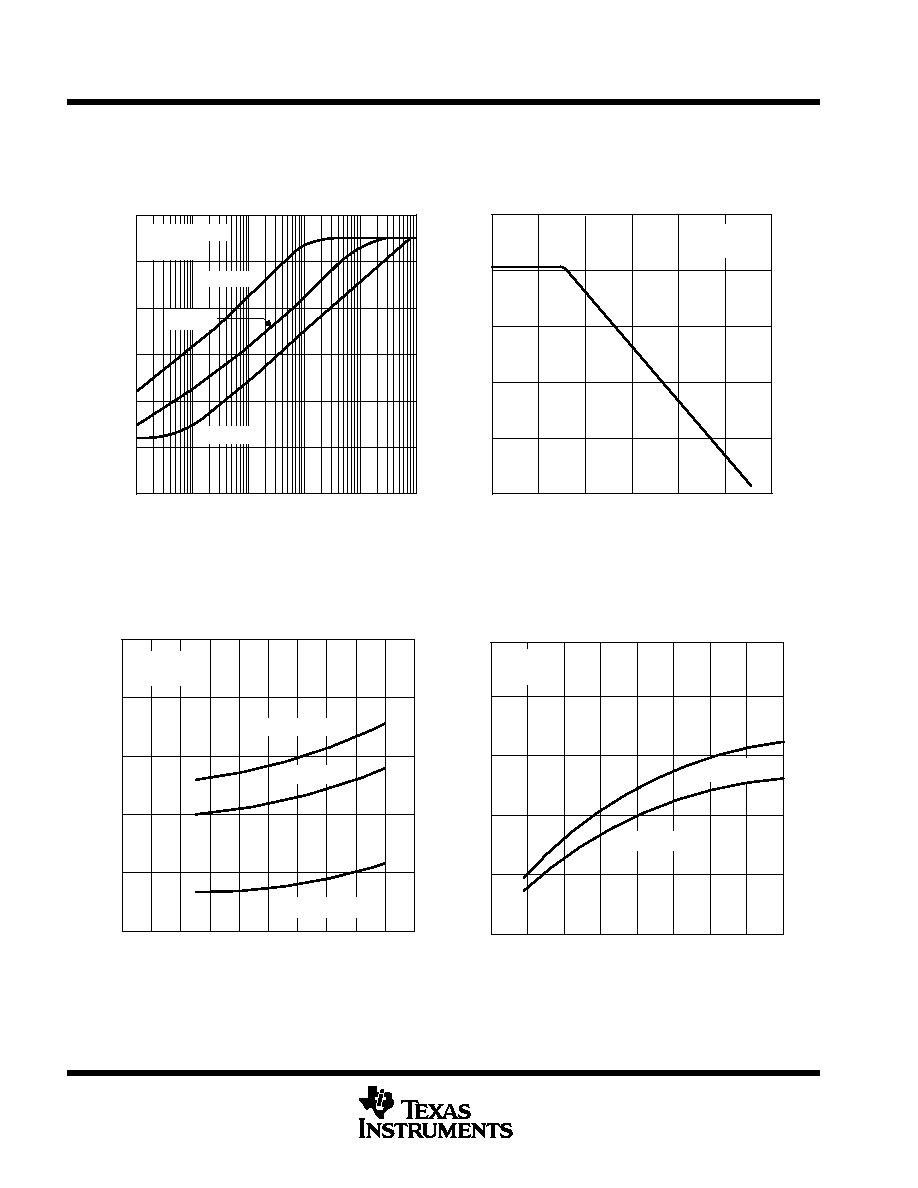

TYPICAL CHARACTERISTICS

Table of Graphs

FIGURE

VIO

Input offset voltage

Distribution

4

IIB

Input bias current

vs Common-mode input voltage

vs Free-air temperature

5

6

IIO

Input offset current

vs Free-air temperature

6

VICR

Common-mode input voltage range limits

vs Free-air temperature

7

VOM

Maximum positive peak output voltage

vs Output current

8

VOM

Maximum negative peak output voltage

vs Output current

9

VOM

Maximum peak output voltage

vs Supply voltage

10, 11, 12

VO(PP) Maximum peak-to-peak output voltage

vs Frequency

13, 14, 15

AVD

Large-signal differential voltage amplification

vs Frequency

vs Free-air temperature

16

17

IOS

Short-circuit output current

vs Elapsed time

18

Large-signal voltage amplification

vs Free-air temperature

19

zo

Output impedance

vs Frequency

20

CMRR

Common-mode rejection ratio

vs Frequency

21

ICC

Supply current

vs Supply voltage

vs Free-air temperature

22

23

Pulse response

Small signal

Large signal

24, 25

26, 27

Noise voltage (referred to input)

0.1 to 10 Hz

28

Vn

Equivalent input noise voltage

vs Frequency

29

THD

Total harmonic distortion

vs Frequency

30, 31

Gain-bandwidth product

vs Supply voltage

vs Free-air temperature

32

33

m

Phase margin

vs Supply voltage

vs Free-air temperature

34

35

Phase shift

vs Frequency

16

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

18

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

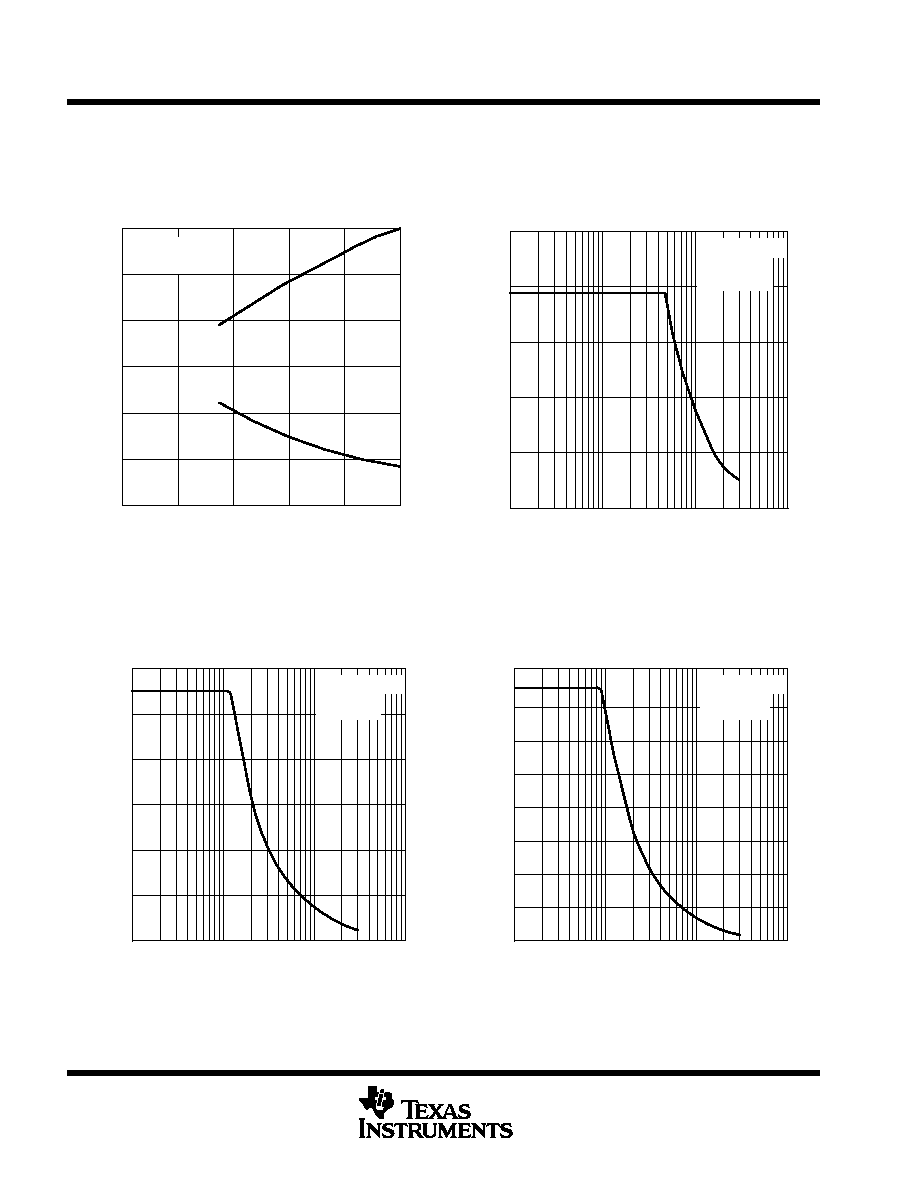

TYPICAL CHARACTERISTICS

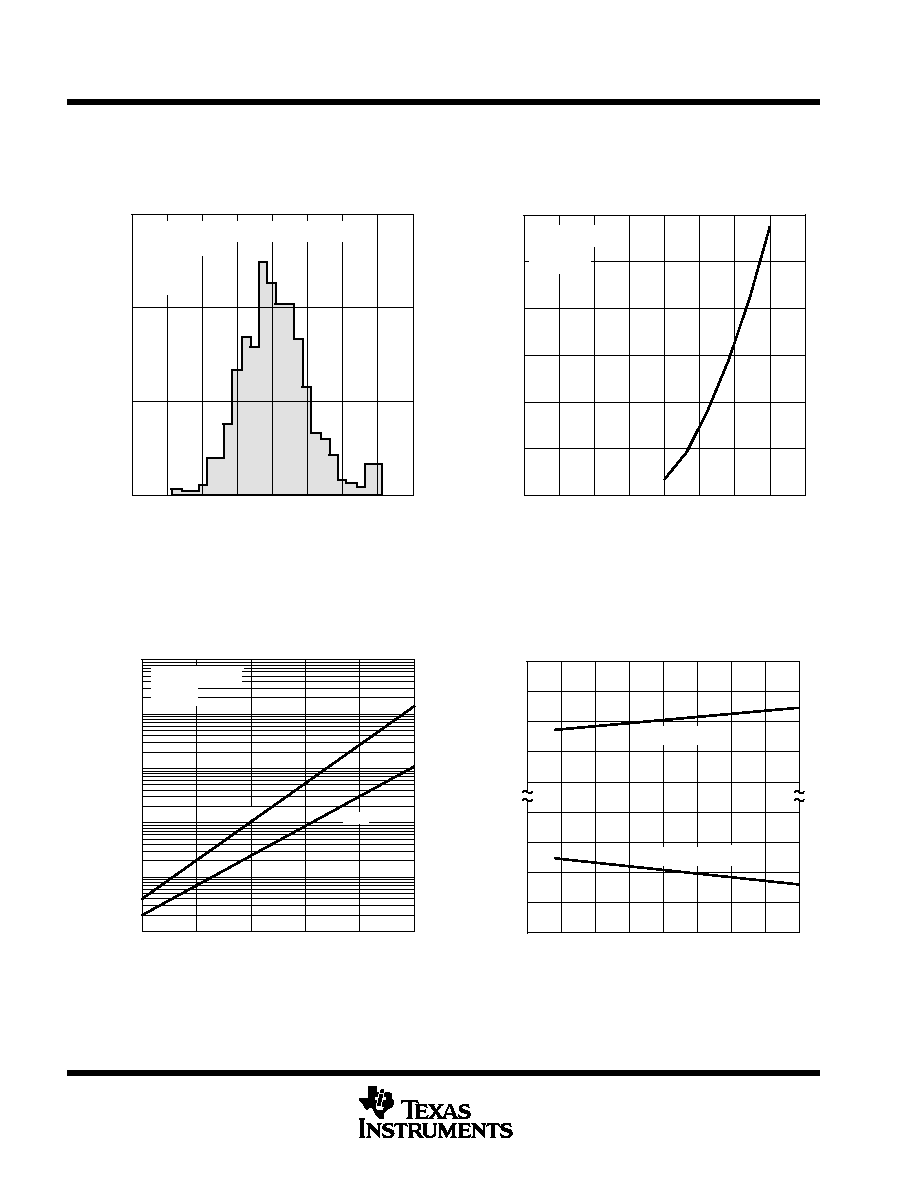

TLE2161

DISTRIBUTION OF

INPUT OFFSET VOLTAGE

P Package

TA = 25

∞

C

VCC

±

=

±

15 V

736 Amplifiers Tested From 3 Wafer Lots

4

3

2

1

0

≠ 1

≠ 2

≠ 3

≠ 4

VIO ≠ Input Offset Voltage ≠ mV

Percentage of

Amplifiers ≠ %

0

5

10

15

Figure 4

TA = 25

∞

C

VID = 0

VIC ≠ Common-Mode Input Voltage ≠ V

≠ 20

≠ 15

≠10

≠ 5

0

5

10

15

20

0

≠ Input Bias Current ≠ pA

INPUT BIAS CURRENT

vs

COMMON-MODE INPUT VOLTAGE

I IB

VCC

±

=

±

15 V

30

60

50

40

20

10

Figure 5

INPUT BIAS CURRENT

AND INPUT OFFSET CURRENT

vs

FREE-AIR TEMPERATURE

TA ≠ Free-Air Temperature ≠

∞

C

105

85

65

45

25

105

104

103

102

101

1

VIC = 0

VCC

±

=

±

15 V

œœ

IIB

≠ Input Bias and Offset Currents ≠ pA

IBI

and

IOI

œœ

IIO

Figure 6

125

≠ Common-Mode Input V

oltage ≠ V

V

IC

COMMON-MODE

INPUT VOLTAGE RANGE LIMITS

vs

FREE-AIR TEMPERATURE

Negative Limit

Positive Limit

125

100

75

50

25

0

≠ 25

≠ 50

≠ 75

TA ≠ Free-Air Temperature ≠

∞

C

VCC +

VCC +

VCC ≠

VCC ≠

VCC ≠ +2

+3

+4

VCC +

+1

+2

Figure 7

Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

19

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

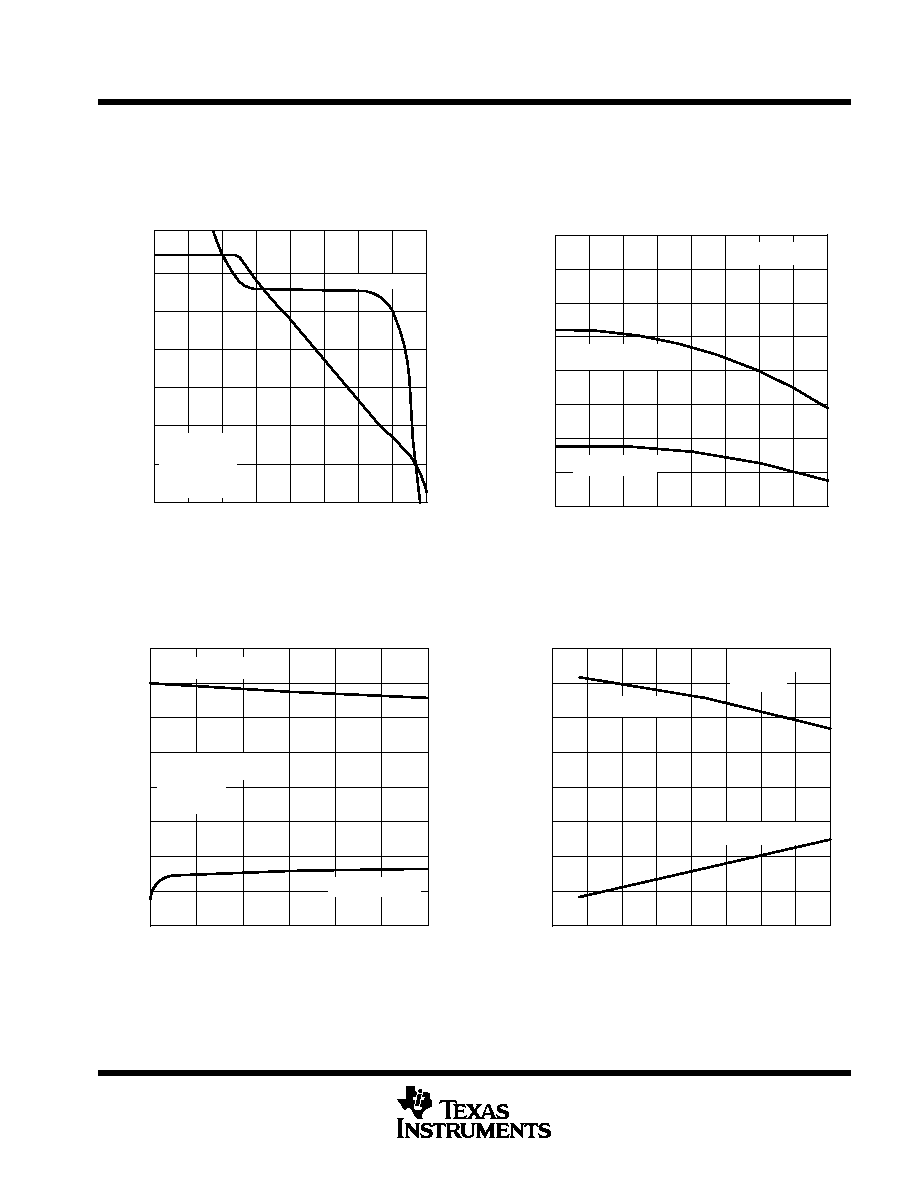

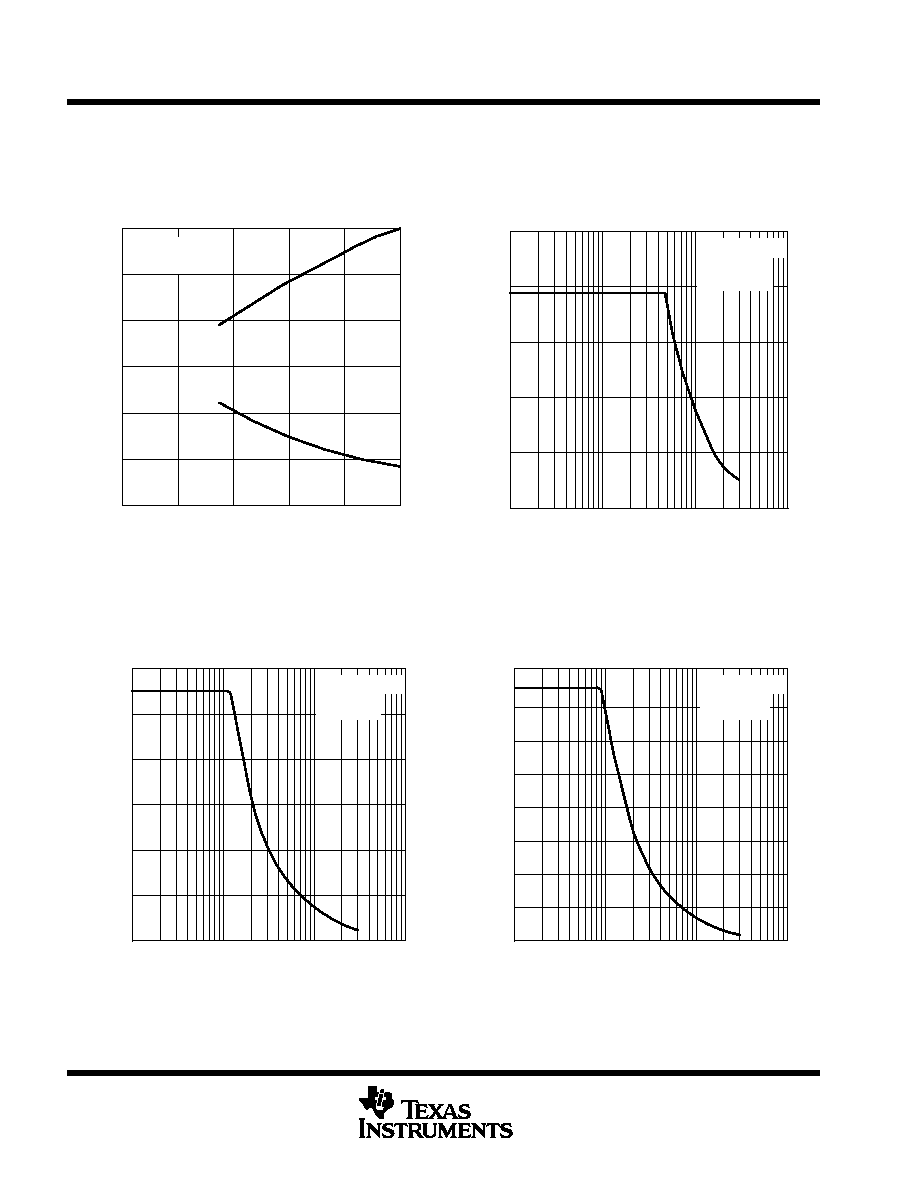

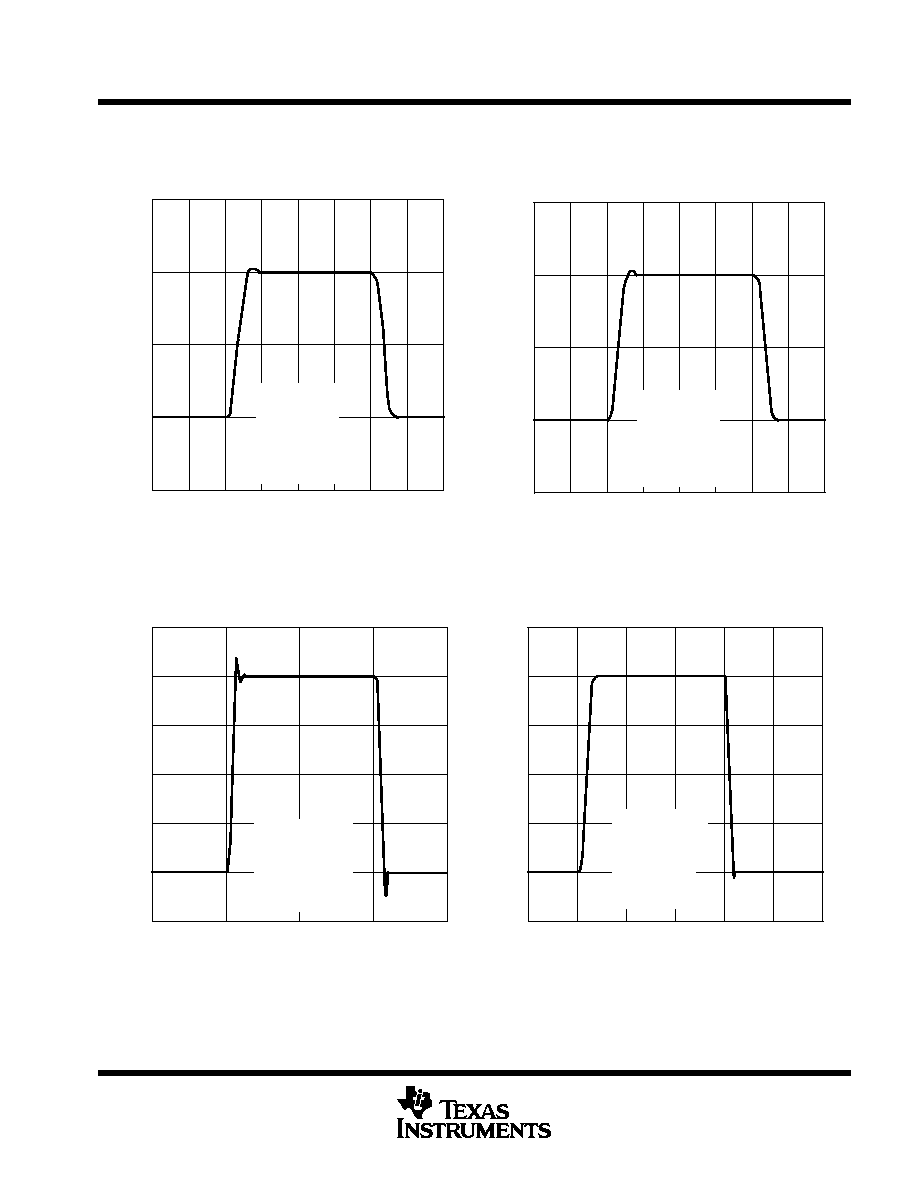

TYPICAL CHARACTERISTICS

Figure 8

≠ Maximum Positive Peak Output V

oltage ≠ V

V

OM+

MAXIMUM POSITIVE PEAK

OUTPUT VOLTAGE

vs

OUTPUT CURRENT

TA = 25

∞

C

≠ 60

≠ 50

≠ 40

≠ 30

≠ 20

≠ 10

0

IO ≠ Output Current ≠ mA

0

2

4

6

8

10

12

14

16

VCC

±

=

±

5 V

VCC

±

=

±

15 V

Figure 9

≠ Maximum Negative Peak Output V

oltage ≠ V

V

OM

≠

MAXIMUM NEGATIVE PEAK

OUTPUT VOLTAGE

vs

OUTPUT CURRENT

30

35

VCC

±

=

±

15 V

VCC

±

=

±

5 V

IO ≠ Output Current ≠ mA

0

5

10

15

20

25

40

≠ 16

≠ 14

≠ 12

≠ 10

≠ 8

≠ 6

≠ 4

≠ 2

0

œœœœ

œœœœ

TA = 25

∞

C

≠ Maximum Peak Output V

oltage ≠ V

V

OM

MAXIMUM PEAK OUTPUT VOLTAGE

vs

SUPPLY VOLTAGE

20

18

16

14

12

10

8

6

4

2

0

| VCC

±

| ≠ Supply Voltage ≠ V

≠ 20

≠ 15

≠ 10

≠ 5

0

5

10

15

20

VOM ≠

VOM +

TA = 25

∞

C

RL = 10 k

Figure 10

≠ Maximum Peak Output V

oltage ≠ V

V

OM

MAXIMUM PEAK OUTPUT VOLTAGE

vs

SUPPLY VOLTAGE

RL = 600

TA = 25

∞

C

VOM +

VOM ≠

20

15

10

5

0

≠ 5

≠ 10

≠ 15

≠ 20

| VCC

±

| ≠ Supply Voltage ≠ V

0

2

4

6

8

10

12

14

16

18

20

Figure 11

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

20

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

Figure 12

≠ Maximum Peak Output V

oltage ≠ V

V

OM

MAXIMUM PEAK OUTPUT VOLTAGE

vs

SUPPLY VOLTAGE

VOM ≠

VOM +

TA = 25

∞

C

RL = 100

10

8

6

4

2

0

|VCC

±

| ≠ Supply Voltage ≠ V

≠ 6

≠ 4

≠ 2

0

2

4

6

Figure 13

≠ Maximum Peak-to-Peak Output V

oltage ≠ V

V

O(PP)

MAXIMUM PEAK-TO-PEAK

OUTPUT VOLTAGE

vs

FREQUENCY

TA = 25

∞

C

RL = 10 k

VCC

±

=

±

5 V

10

8

6

10 k

100 k

1 M

10 M

f ≠ Frequency ≠ Hz

4

2

0

≠ Maximum Peak-to-Peak Output V

oltage ≠ V

V

O(PP)

MAXIMUM PEAK-TO-PEAK

OUTPUT VOLTAGE

vs

FRQUENCY

15

TA = 25

∞

C

RL = 10 k

VCC

±

=

±

15 V

30

25

20

10 k

100 k

1 M

10 M

f ≠ Frequency ≠ Hz

10

5

0

Figure 14

≠ Maximum Peak-to-Peak Output V

oltage ≠ V

V

O(PP)

MAXIMUM PEAK-TO-PEAK

OUTPUT VOLTAGE

vs

FREQUENCY

10

20

30

0

5

15

f ≠ Frequency ≠ Hz

10 M

1 M

100 k

10 k

25

35

40

VCC

±

=

±

5 V

RL = 10 k

TA = 25

∞

C

Figure 15

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

21

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

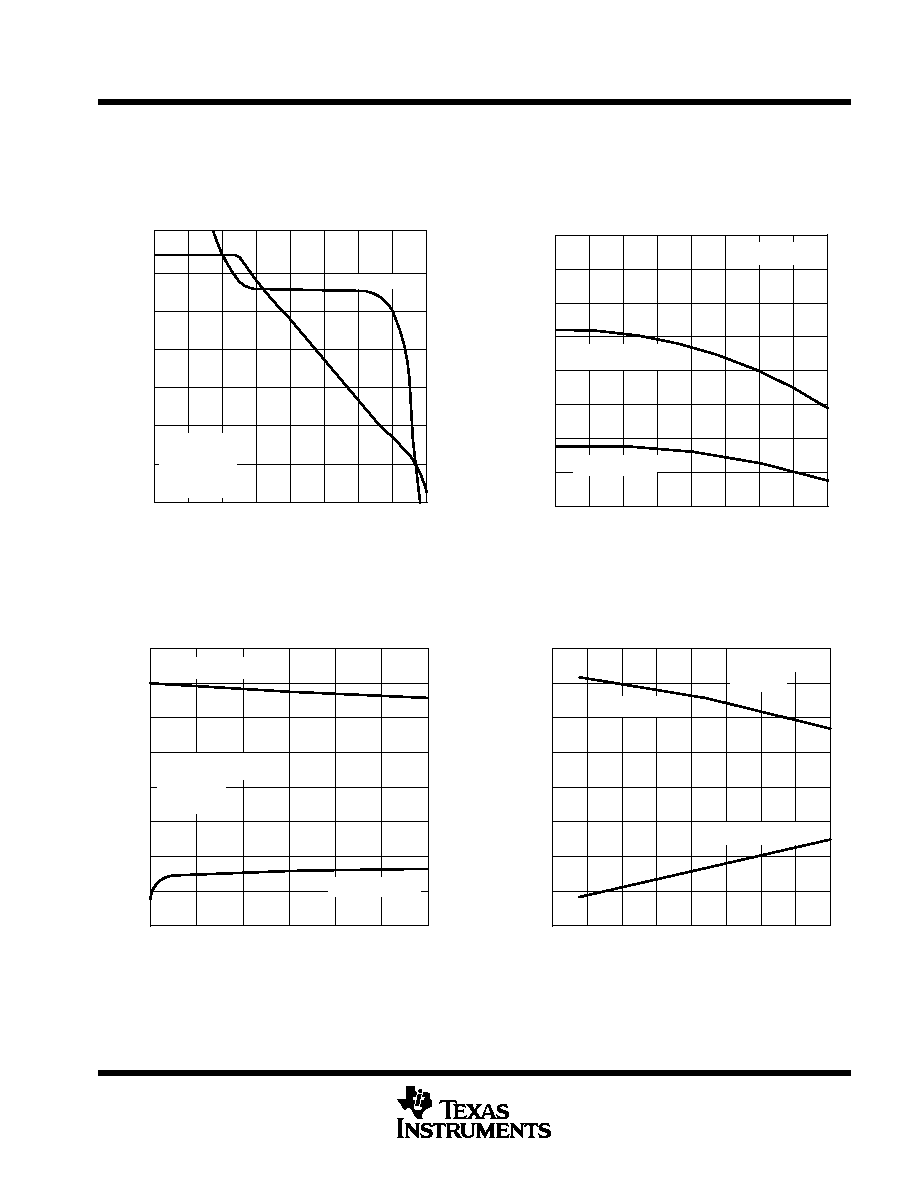

LARGE-SIGNAL DIFFERENTIAL VOLTAGE

AMPLIFICATION AND PHASE SHIFT

vs

FRQUENCY

TA = 25

∞

C

CL = 100 pF

RL = 10 k

VCC

±

=

±

15 V

Phase Shift

AVD

60

∞

80

∞

10 M

1 M

100 k

10 k

1 k

100

10

1

0.1

f ≠ Frequency ≠ Hz

≠ 20

0

20

40

60

80

100

120

A

VD ≠ Large-Signal Differential

¡¡

¡¡

¡¡

A

VD

V

oltage

Amplification ≠ dB

Figure 16

100

∞

120

∞

140

∞

160

∞

180

∞

200

∞

Phase Shift

LARGE-SIGNAL DIFFERENTIAL

VOLTAGE AMPLIFICATION

vs

FREE-AIR TEMPERATURE

RL = 10 k

VCC

±

=

±

5 V

VCC

±

=

±

15 V

TA ≠ Free-Air Temperature ≠

∞

C

125

100

75

50

25

0

≠ 25

≠ 50

≠ 75

350

300

250

200

150

100

50

0

400

A

VD ≠ Large-Signal Differential

¡¡

¡¡

¡¡

A

VD

V

oltage

Amplification ≠ V/mV

Figure 17

≠ Short-Circuit Output Current ≠ mA

I

OS

SHORT-CIRCUIT OUTPUT CURRENT

vs

ELAPSED TIME

VID = 100 mV

VO = 0

TA = 25

∞

C

VCC

±

=

±

15 V

VID = ≠ 100 mV

60

50

40

30

20

10

0

t ≠ Elapsed Time ≠ s

≠ 80

≠ 60

≠ 40

≠ 20

0

20

40

60

80

Figure 18

LARGE-SIGNAL VOLTAGE AMPLIFICATION

vs

FREE-AIR TEMPERATURE

VID = ≠100 mV

VID = 100 mV

VO = 0

VCC

±

=

±

15 V

80

≠ 80

≠ 60

≠ 40

≠ 20

0

20

40

60

≠ 75

≠ 50

≠ 25

0

25

50

75

100

125

TA ≠ Free-Air Temperature ≠

∞

C

≠ Short-Circuit Output Current ≠ mA

I

OS

Figure 19

Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

22

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

≠ Output Impedance ≠

z

o

OUTPUT IMPEDANCE

vs

FREQUENCY

AVD =100

AVD = 1

TA = 25

∞

C

VCC

±

=

±

15 V

AVD = 10

f ≠ Frequency ≠ Hz

1 M

100 k

10 k

1 k

100

10

0.001

0.01

0.1

1

10

100

1000

Figure 20

COMMON-MODE REJECTION RATIO

vs

FREQUENCY

CMRR ≠ Common-Mode Rejection Ratio ≠ dB

10

100

1 k

10 k

100 k

1 M

f ≠ Frequency ≠ Hz

10 M

0

20

40

60

80

100

TA = 25

∞

C

VCC

±

=

±

5 V

Figure 21

≠ Supply Current ≠

A

I

CC

SUPPLY CURRENT

vs

SUPPLY VOLTAGE

No Load

VO = 0

TA = 125

∞

C

TA = 25

∞

C

TA = ≠ 55

∞

C

|VCC

±

| ≠ Supply Voltage ≠ V

20

18

16

14

12

10

8

6

4

2

0

240

260

280

300

320

340

µ

Figure 22

SUPPLY CURRENT

vs

FREE-AIR TEMPERATURE

VCC

±

=

±

5 V

VCC

±

=

±

15 V

VO = 0

No Load

TA ≠ Free-Air Temperature ≠

∞

C

240

260

280

300

320

340

125

100

75

50

25

0

≠ 25

≠ 50

≠75

≠ Supply Current ≠

A

I

CC

µ

Figure 23

Data at high and low temperatures are applicable only within the rated operating free-air temperature ranges of the various devices.

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

23

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

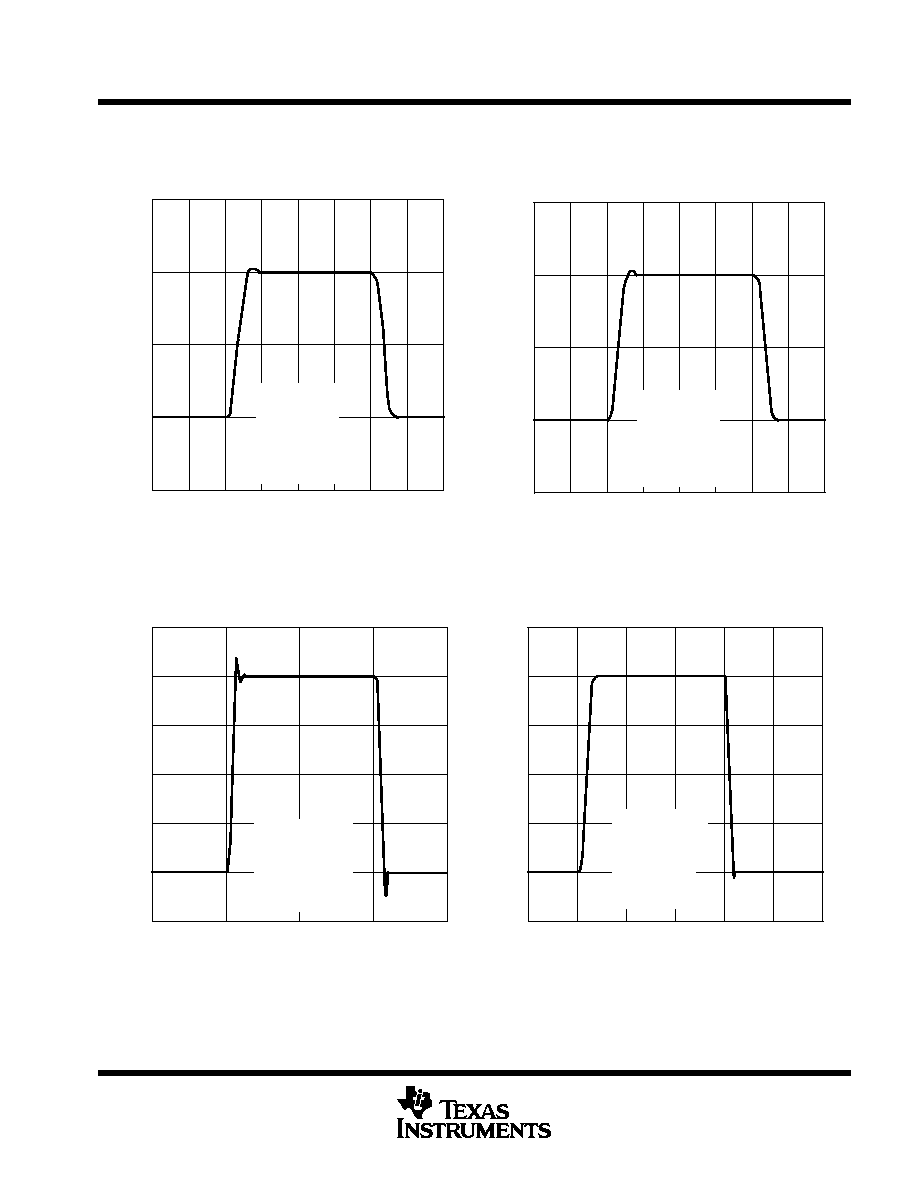

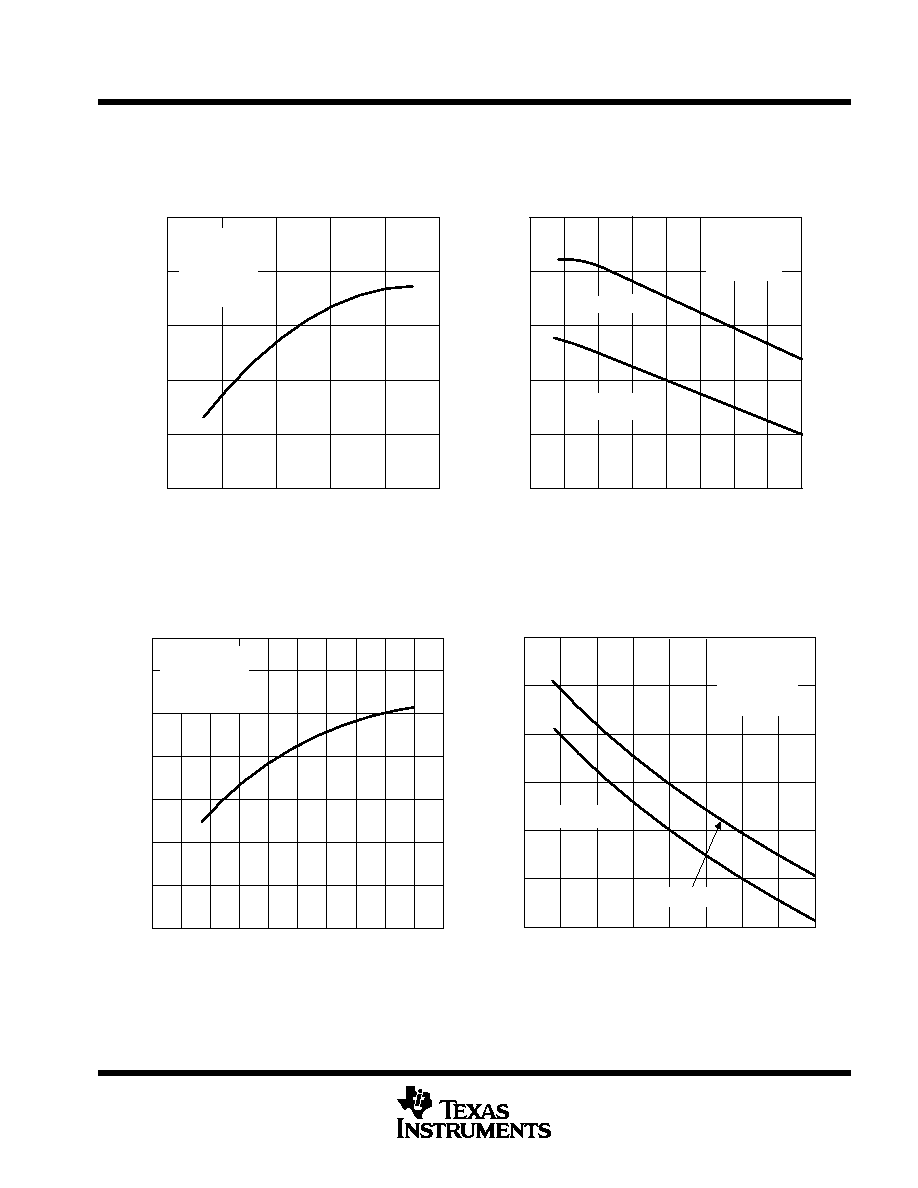

TYPICAL CHARACTERISTICS

≠ Output V

oltage

≠

mV

V

O

SMALL-SIGNAL

PULSE RESPONSE

See Figure 1

t ≠ Time ≠

µ

s

3

2

1

0

≠ 100

≠ 50

0

50

100

TA = 25

∞

C

CL = 100 pF

RL = 10 k

AVD = 5

VCC

±

=

±

5 V

0.5

1.5

2.5

Figure 24

SMALL-SIGNAL

PULSE RESPONSE

VCC

±

=

±

15 V

RL = 10 k

CL = 100 pF

TA = 25

∞

C

See Figure 1

100

50

0

≠ 50

≠ 100

0

1

2

3

t ≠ Time ≠

µ

s

≠ Output V

oltage

≠

mV

V

O

0.5

1.5

2.5

AVD = 5

Figure 25

CL = 100 pF

≠ Output V

oltage ≠ V

V

O

LARGE-SIGNAL

PULSE RESPONSE

RL = 10 k

VCC

±

=

±

5 V

AVD = 5

TA = 25

∞

C

See Figure 1

0

5

10

15

t ≠ Time ≠

µ

s

≠ 2

≠ 1

0

1

2

3

4

Figure 26

LARGE-SIGNAL

PULSE RESPONSE

≠ Output V

oltage ≠ V

V

O

See Figure 1

TA = 25

∞

C

CL = 100 pF

RL = 10 k

AVD = 5

VCC

±

=

±

15 V

t ≠ Time ≠

µ

s

40

30

20

10

0

≠ 15

≠ 10

≠ 5

0

5

10

15

Figure 27

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

24

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

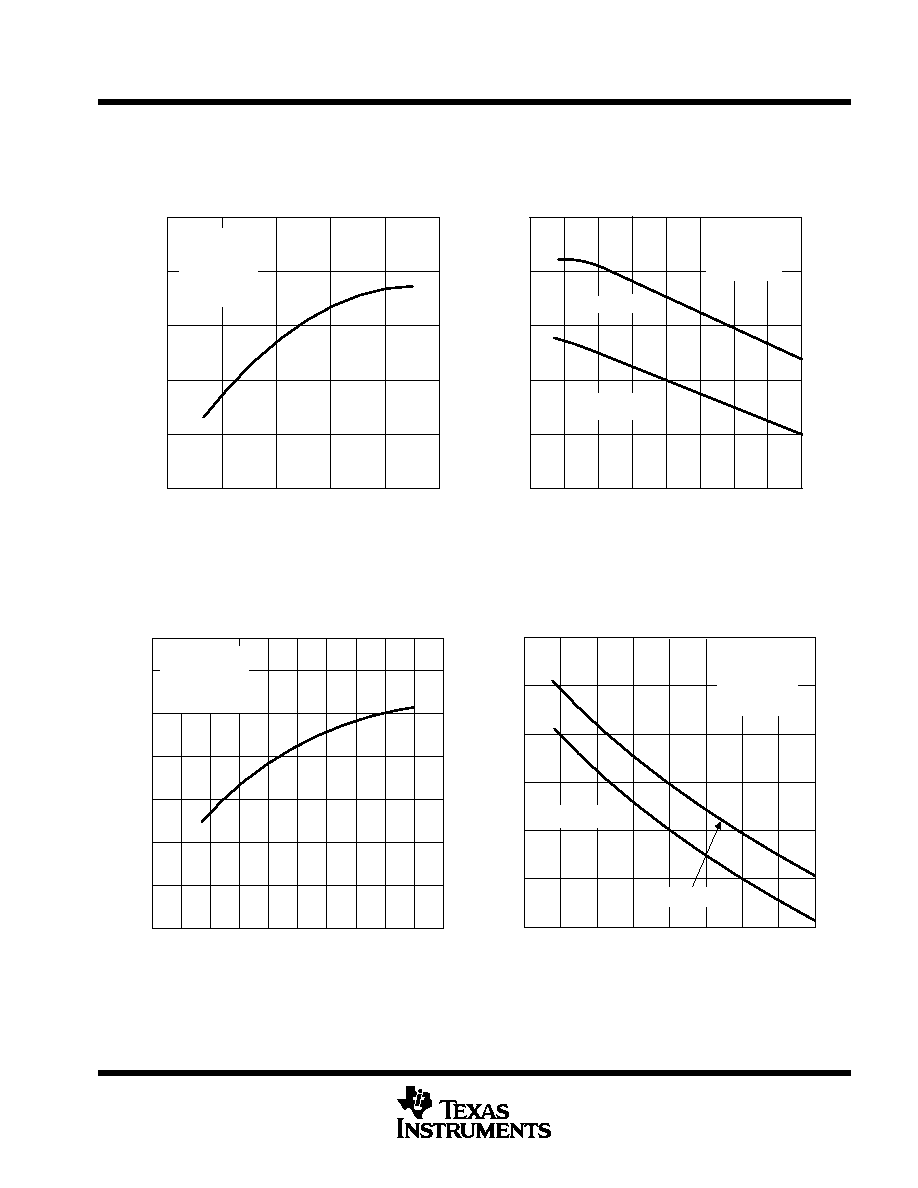

TYPICAL CHARACTERISTICS

NOISE VOLTAGE

(REFERRED TO INPUT)

OVER A 10-SECOND INTERVAL

t ≠ Time ≠ s

10

9

8

7

6

5

4

3

2

1

0

≠ 1

≠ 0.5

0

0.5

1

TA = 25

∞

C

f = 0.1 to 10 Hz

VCC

±

=

±

15 V

≠ Noise V

oltage ≠ uV

V

n

µ

Figure 28

EQUIVALENT INPUT NOISE VOLTAGE

vs

FREQUENCY

≠ Equivalent Input Noise V

oltage ≠

V

n

See Figure 2

TA = 25

∞

C

RS = 20

VCC

±

=

±

5 V

10 k

1 k

100

10

1

f ≠ Frequency ≠ Hz

0

20

40

60

80

100

nV/

Hz

Figure 29

AVD = 2

VO(PP) = 2 V

TA = 25

∞

C

Source Signal

0.2

0.15

100 k

10 k

1 k

100

10

t ≠ Frequency ≠ Hz

THD

≠

T

otal Harmonic Distortion ≠ %

0

0.25

0.1

0.05

TOTAL HARMONIC DISTORTION

vs

FREQUENCY

œœœœœ

VCC

±

=

±

5 V

Figure 30

TOTAL HARMONIC DISTORTION

vs

FREQUENCY

œœœœœœ

VCC

±

=

±

5 V

Source Signal

TA = 25

∞

C

VO(PP) = 2 V

AVD = 10

0.3

0.1

0.5

0.6

0

THD

≠

T

otal Harmonic Distortion ≠ %

f ≠ Frequency ≠ Hz

10

100

1 k

10 k

100 k

0.2

0.4

Figure 31

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

25

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

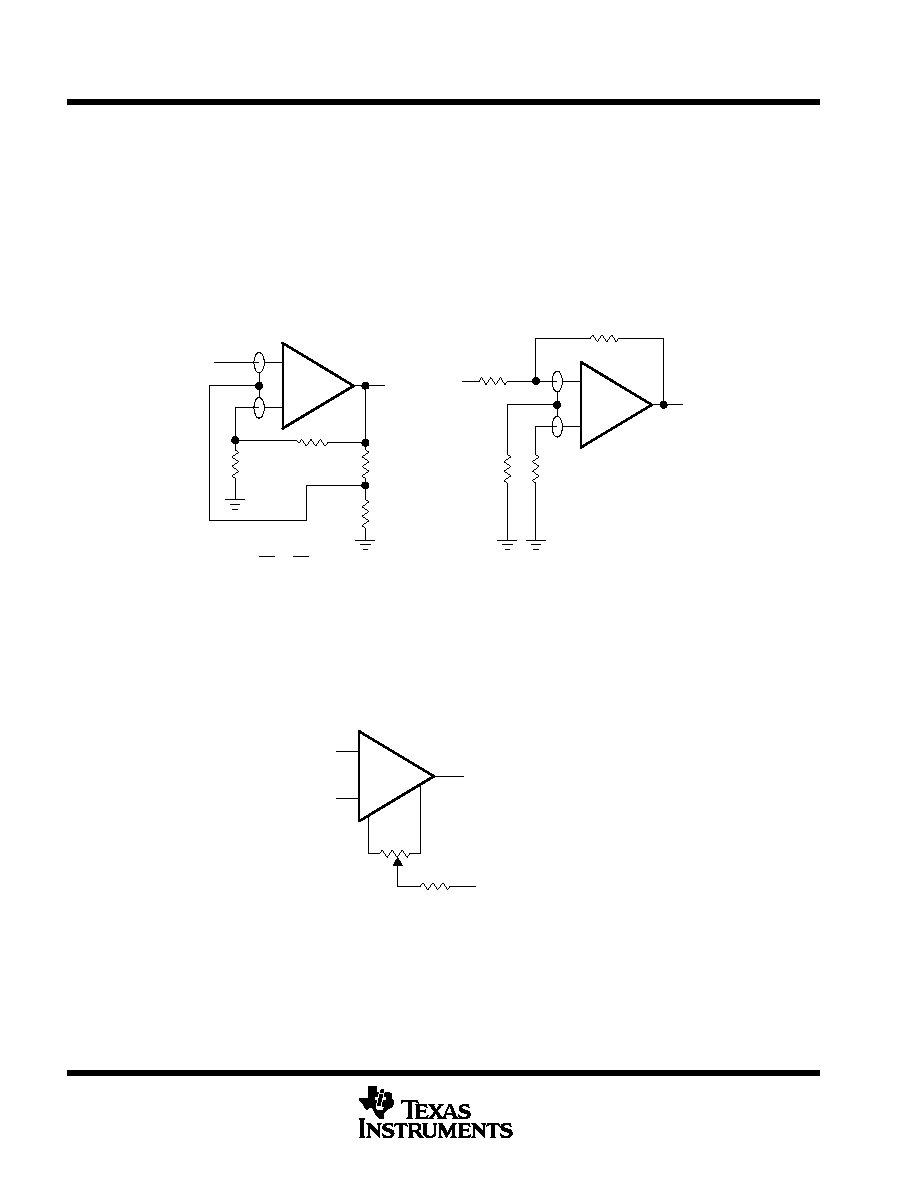

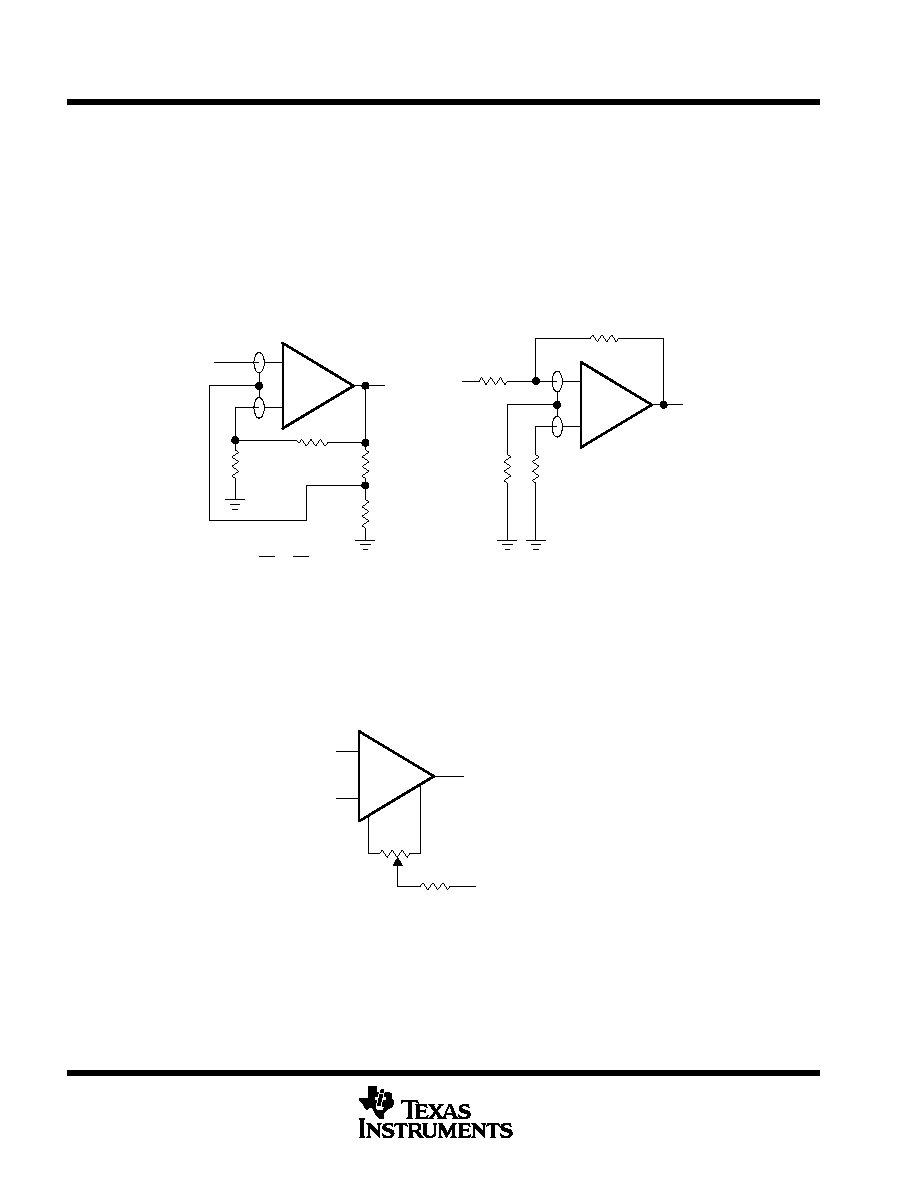

TYPICAL CHARACTERISTICS

GAIN-BANDWIDTH PRODUCT

vs

SUPPLY VOLTAGE

6.6

6.2

5.8

5.4

16

12

8

4

7

20

5

0

f = 100 kHz

See Figure 3

TA = 25

∞

C

CL = 100 pF

RL = 10 k

|VCC

±

| ≠ Supply Voltage ≠ V

Gain-Bandwidth Product ≠ MHz

Figure 32

GAIN-BANDWIDTH PRODUCT

vs

FREE-AIR TEMPERATURE

125

100

75

50

25

0

≠ 25

≠ 50

6.6

6.2

5.8

5.4

7

5

See Figure 3

CL = 100 pF

RL = 10 k

f = 100 kHz

VCC

±

=

±

5 V

VCC

±

=

±

15 V

TA ≠ Free-Air Temperature ≠

∞

C

≠ 75

Gain-Bandwidth Product ≠ MHz

Figure 33

PHASE MARGIN

vs

SUPPLY VOLTAGE

AVD = 5

RL = 10 k

CL = 100 pF

TA = 25

∞

C

See Figure 3

74

∞

73

∞

72

∞

71

∞

70

∞

69

∞

68

∞

0

|VCC

±

| ≠ Supply Voltage ≠ V

2

4

6

8

10

12

14

16

18

20

67

∞

≠ Phase Margin

m

¡¡

¡¡

m

Figure 34

≠ Phase Margin

m

PHASE MARGIN

vs

FREE-AIR TEMPERATURE

VCC

±

=

±

5 V

VCC

±

=

±

15 V

See Figure 3

CL = 100 pF

RL = 10 k

AVD = 5

76

∞

74

∞

72

∞

70

∞

68

∞

100

75

50

25

0

≠ 25

≠ 50

78

∞

125

TA ≠ Free-Air Temperature ≠

∞

C

66

∞

≠ 75

¡¡

¡¡

m

Figure 35

TLE2161, TLE2161A, TLE2161B

EXCALIBUR JFET-INPUT HIGH-OUTPUT-DRIVE

µ

POWER OPERATIONAL AMPLIFIERS

SLOS049D ≠ NOVEMBER 1989 ≠ REVISED MAY 1996

26

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

APPLICATION INFORMATION

macromodel information

Macromodel information provided was derived using Microsim

Parts

TM

, the model generation software used

with Microsim

PSpice

TM

. The Boyle macromodel (see Note 5) and subcircuit in Figure 36 and Figure 37 were

generated using the TLE2161 typical electrical and operating characteristics at 25

∞

C. Using this information,