| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 74148 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

SN54147, SN54148, SN54LS147, SN54LS148

SN74147, SN74148 (TIM9907), SN74LS147, SN74LS148

10 LINE TO 4 LINE AND 8 LINE TO 3 LINE PRIORITY ENCODERS

SDLS053B - OCTOBER 1976 - REVISED MAY 2004

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

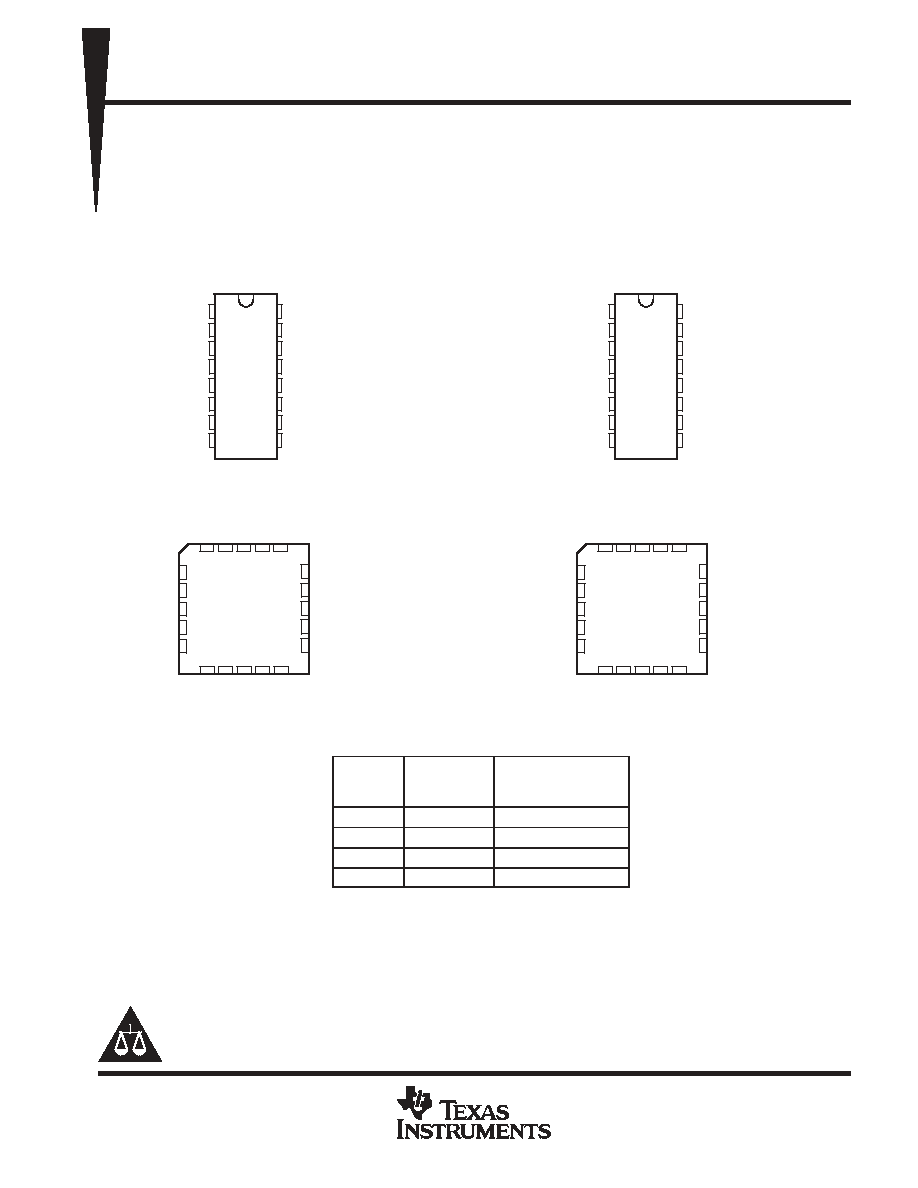

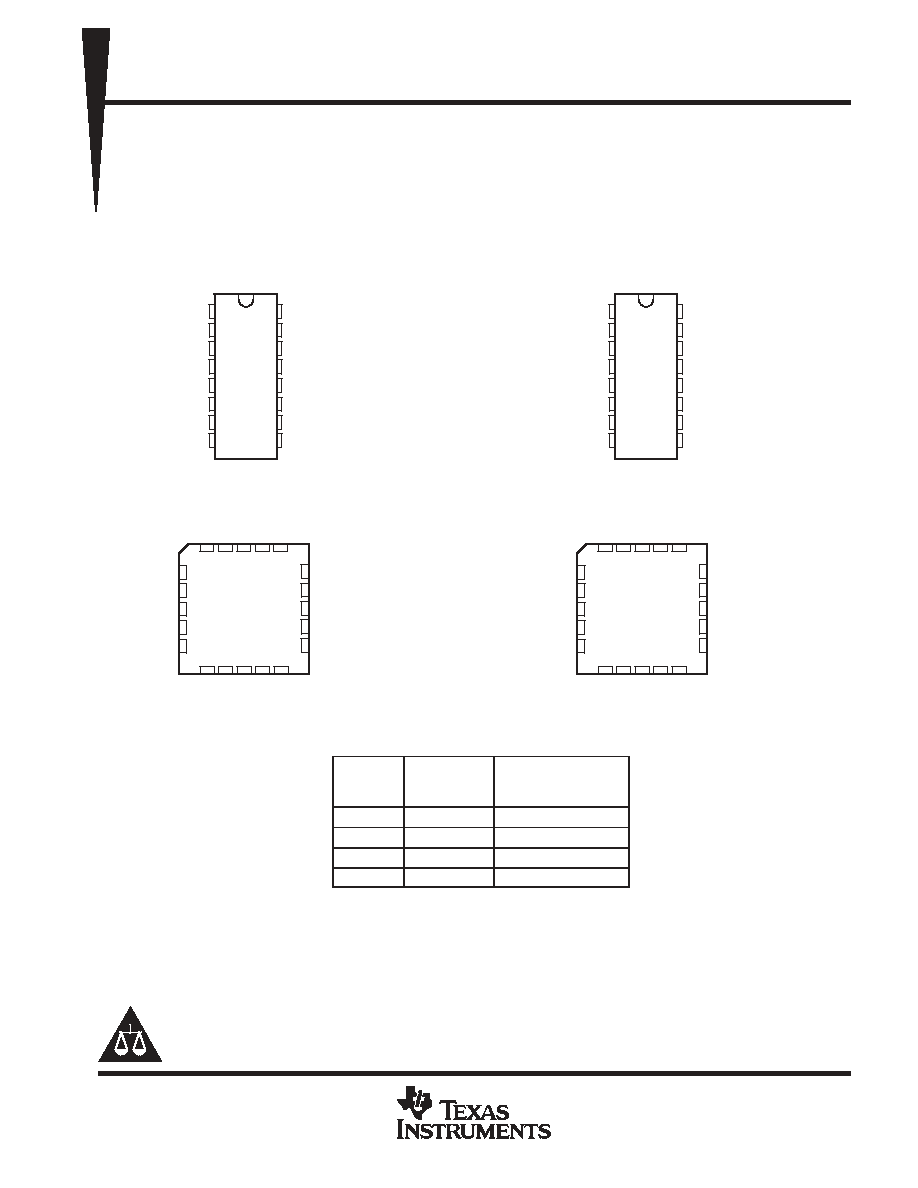

'147, 'LS147

D

Encode 10-Line Decimal to 4-Line BCD

D

Applications Include:

- Keyboard Encoding

- Range Selection

'148, 'LS148

D

Encode 8 Data Lines to 3-Line Binary

(Octal)

D

Applications Include:

- n-Bit Encoding

- Code Converters and Generators

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

D

3

NC

2

1

6

7

NC

8

C

5

4

NC

A

9

V

NC

B

GND

NC

SN54LS147 . . . FK PACKAGE

(TOP VIEW)

CC

NC - No internal connection

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

4

5

6

7

8

C

B

GND

V

CC

NC

D

3

2

1

9

A

SN54147, SN54LS147 . . . J OR W PACKAGE

SN74147, SN74LS147 . . . D OR N PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

4

5

6

7

EI

A2

A1

GND

V

CC

E0

GS

3

2

1

0

A0

SN54148, SN54LS148 . . . J OR W PACKAGE

SN74148, SN74LS148 . . . D, N, OR NS PACKAGE

(TOP VIEW)

3

2

1 20 19

9 10 11 12 13

4

5

6

7

8

18

17

16

15

14

GS

3

NC

2

1

6

7

NC

EI

A2

5

4

NC

A0

0

V

E0

A1

GND

NC

SN54LS148 . . . FK PACKAGE

(TOP VIEW)

CC

TYPE

TYPICAL

DATA

DELAY

TYPICAL

POWER

DISSIPATION

'147

10 ns

225 mW

'148

10 ns

190 mW

'LS147

15 ns

60 mW

'LS148

15 ns

60 mW

NOTE: The SN54147, SN54LS147, SN54148, SN74147, SN74LS147, and SN74148 are obsolete and are no longer supplied.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright

2004, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

On products compliant to MIL PRF 38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SN54147, SN54148, SN54LS147, SN54LS148

SN74147, SN74148 (TIM9907), SN74LS147, SN74LS148

10 LINE TO 4 LINE AND 8 LINE TO 3 LINE PRIORITY ENCODERS

SDLS053B - OCTOBER 1976 - REVISED MAY 2004

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

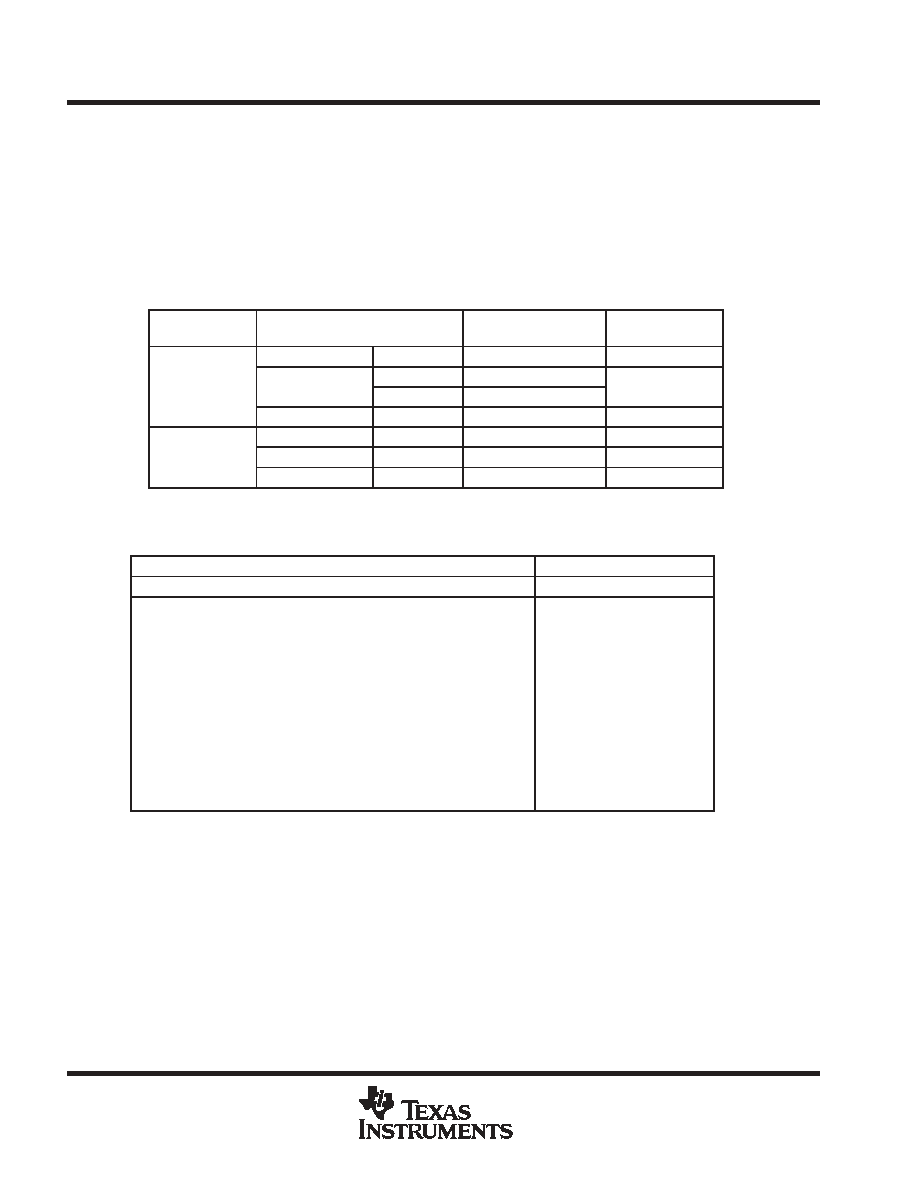

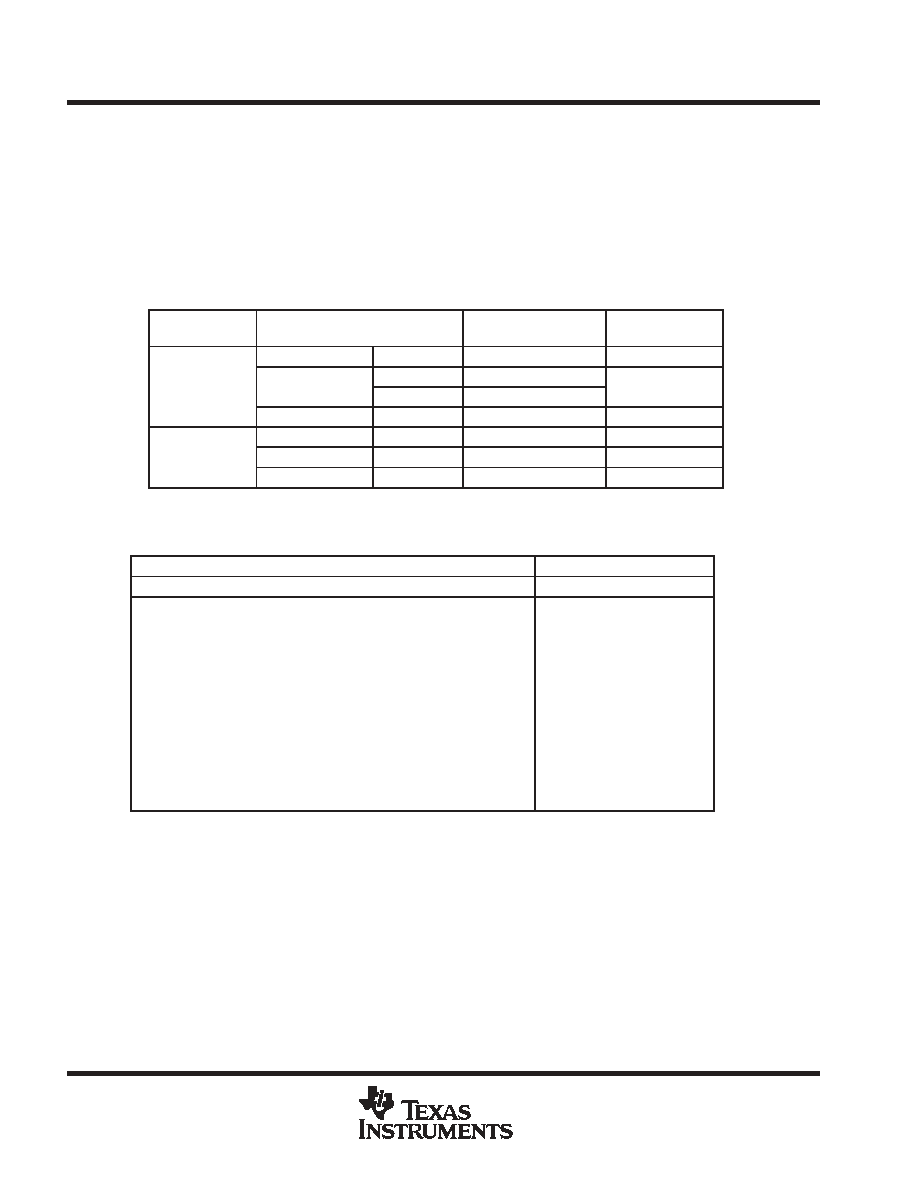

description/ordering information

These TTL encoders feature priority decoding of the inputs to ensure that only the highest-order data line is

encoded. The '147 and 'LS147 devices encode nine data lines to four-line (8-4-2-1) BCD. The implied decimal

zero condition requires no input condition, as zero is encoded when all nine data lines are at a high logic level.

The '148 and 'LS148 devices encode eight data lines to three-line (4-2-1) binary (octal). Cascading circuitry

(enable input EI and enable output EO) has been provided to allow octal expansion without the need for external

circuitry. For all types, data inputs and outputs are active at the low logic level. All inputs are buffered to represent

one normalized Series 54/74 or 54/74LS load, respectively.

ORDERING INFORMATION

TA

PACKAGE

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

PDIP - N

Tube

SN74LS148N

SN74LS148N

0

∞

C to 70

∞

C

SOIC - D

Tube

SN74LS148D

LS148

0

∞

C to 70

∞

C

SOIC - D

Tape and reel

SN74LS148DR

LS148

SOP - NS

Tape and reel

SN74LS148NSR

74LS148

CDIP - J

Tube

SNJ54LS148J

SNJ54LS148J

-55

∞

C to 125

∞

C

CFP - W

Tube

SNJ54LS148W

SNJ54LS148W

-55 C to 125 C

LCCC - FK

Tube

SNJ54LS148FK

SNJ54LS148FK

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are

available at www.ti.com/sc/package.

FUNCTION TABLE - '147, 'LS147

INPUTS

OUTPUTS

1

2

3

4

5

6

7

8

9

D

C

B

A

H

H

H

H

H

H

H

H

H

H

H

H

H

X

X

X

X

X

X

X

X

L

L

H

H

L

X

X

X

X

X

X

X

L

H

L

H

H

H

X

X

X

X

X

X

L

H

H

H

L

L

L

X

X

X

X

X

L

H

H

H

H

L

L

H

X

X

X

X

L

H

H

H

H

H

L

H

L

X

X

X

L

H

H

H

H

H

H

L

H

H

X

X

L

H

H

H

H

H

H

H

H

L

L

X

L

H

H

H

H

H

H

H

H

H

L

H

L

H

H

H

H

H

H

H

H

H

H

H

L

H = high logic level, L = low logic level, X = irrelevant

SN54147, SN54148, SN54LS147, SN54LS148

SN74147, SN74148 (TIM9907), SN74LS147, SN74LS148

10 LINE TO 4 LINE AND 8 LINE TO 3 LINE PRIORITY ENCODERS

SDLS053B - OCTOBER 1976 - REVISED MAY 2004

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

FUNCTION TABLE - '148, 'LS148

INPUTS

OUTPUTS

EI

0

1

2

3

4

5

6

7

A2

A1

A0

GS

EO

H

X

X

X

X

X

X

X

X

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

L

L

X

X

X

X

X

X

X

L

L

L

L

L

H

L

X

X

X

X

X

X

L

H

L

L

H

L

H

L

X

X

X

X

X

L

H

H

L

H

L

L

H

L

X

X

X

X

L

H

H

H

L

H

H

L

H

L

X

X

X

L

H

H

H

H

H

L

L

L

H

L

X

X

L

H

H

H

H

H

H

L

H

L

H

L

X

L

H

H

H

H

H

H

H

H

L

L

H

L

L

H

H

H

H

H

H

H

H

H

H

L

H

H = high logic level, L = low logic level, X = irrelevant

SN54147, SN54148, SN54LS147, SN54LS148

SN74147, SN74148 (TIM9907), SN74LS147, SN74LS148

10 LINE TO 4 LINE AND 8 LINE TO 3 LINE PRIORITY ENCODERS

SDLS053B - OCTOBER 1976 - REVISED MAY 2004

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

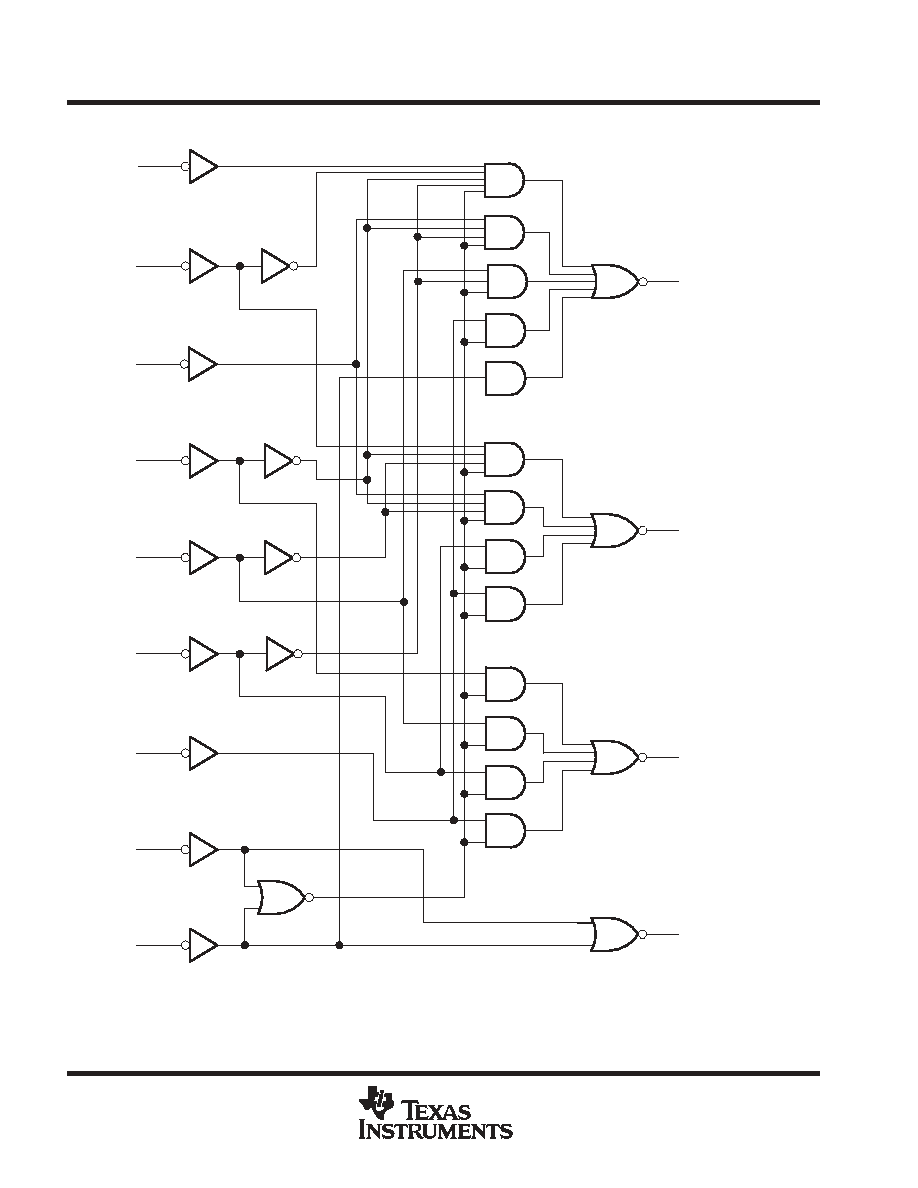

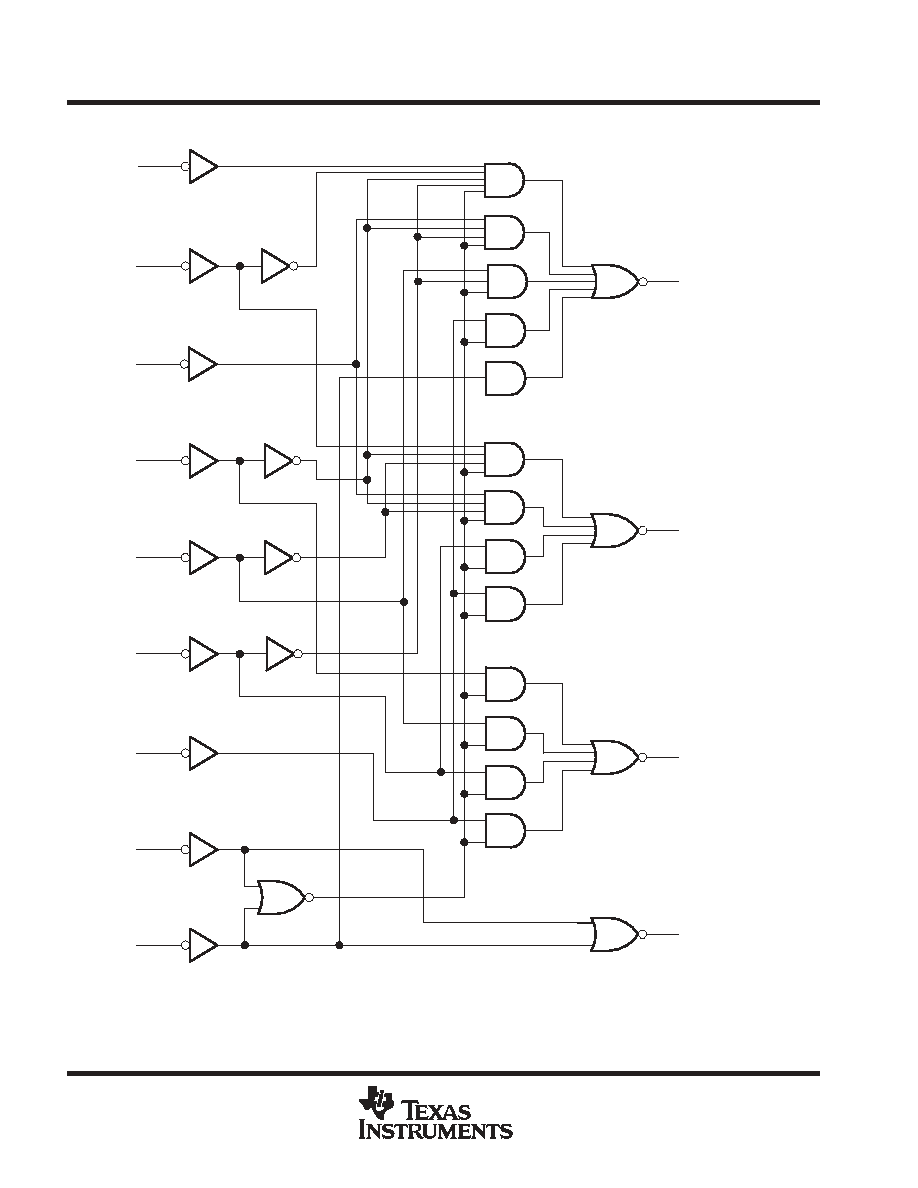

'147, 'LS147 logic diagram (positive logic)

(11)

(12)

(13)

(1)

(2)

(3)

(4)

(5)

(10)

1

2

3

4

5

6

7

8

9

D

B

C

A

(9)

(7)

(6)

(14)

Pin numbers shown are for D, J, N, and W packages.

SN54147, SN54148, SN54LS147, SN54LS148

SN74147, SN74148 (TIM9907), SN74LS147, SN74LS148

10 LINE TO 4 LINE AND 8 LINE TO 3 LINE PRIORITY ENCODERS

SDLS053B - OCTOBER 1976 - REVISED MAY 2004

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

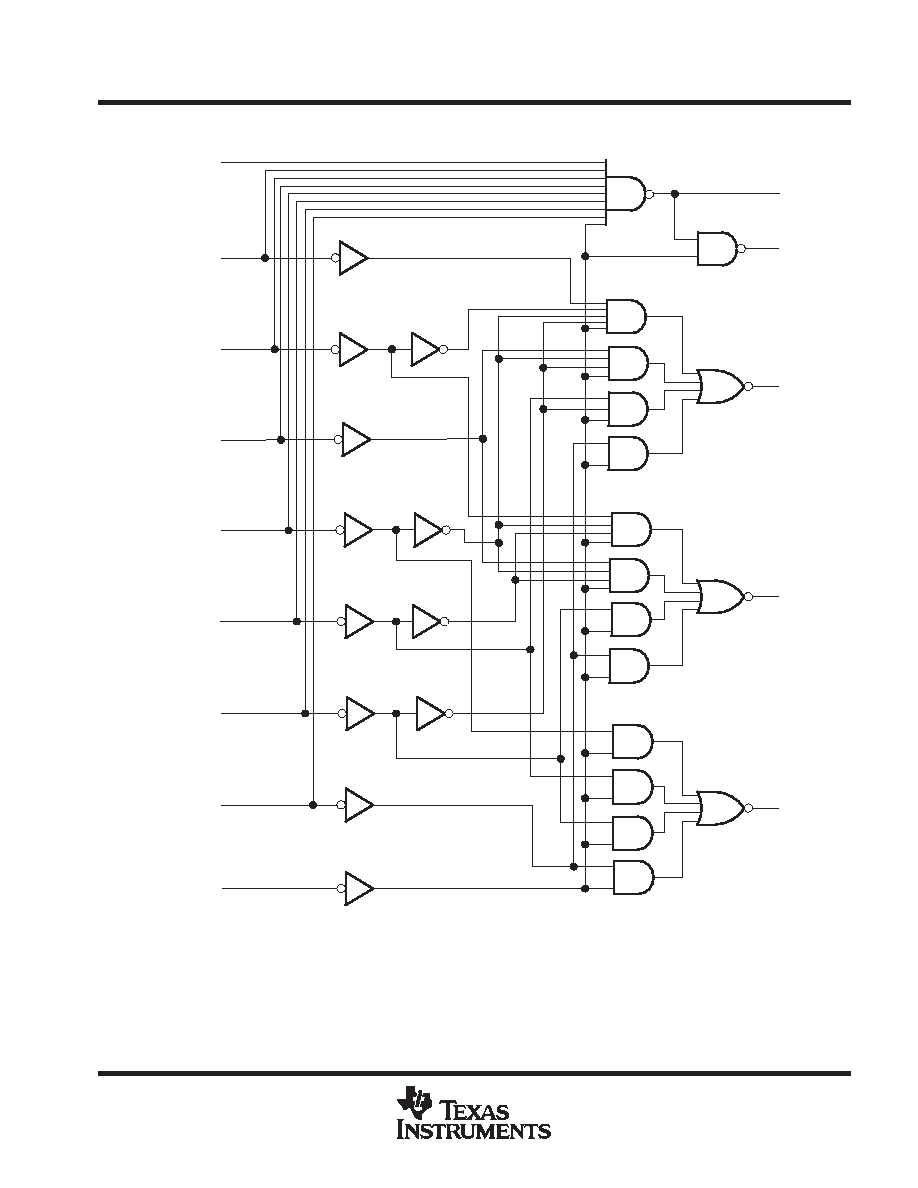

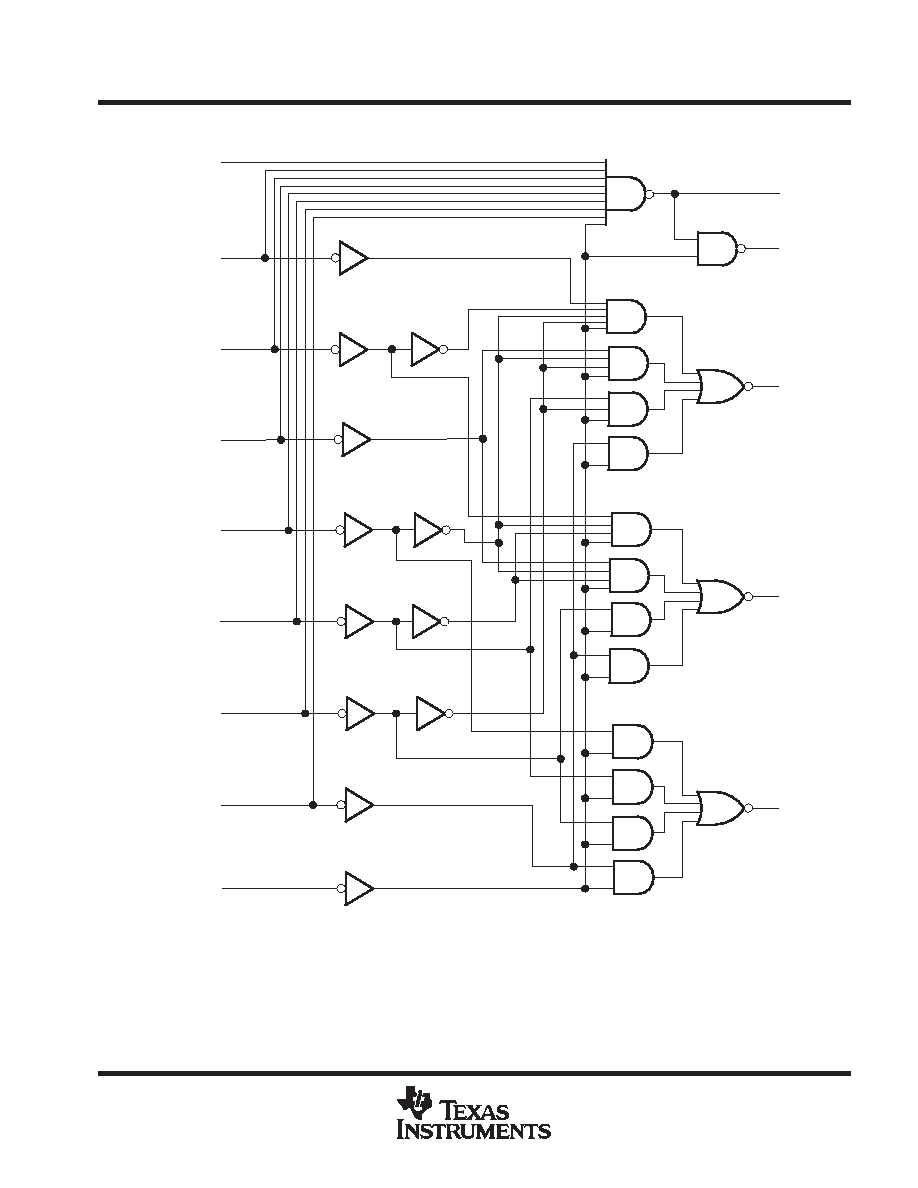

'148, 'LS148 logic diagram (positive logic)

(10)

(11)

(12)

(13)

(1)

(2)

(3)

(4)

1

2

3

4

5

6

7

EI

A1

A2

A0

(5)

0

(14)

EO

G5

(6)

(9)

(7)

(15)

Pin numbers shown are for D, J, N, NS, and W packages.