| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 8406401EA | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

Data sheet acquired from Harris Semiconductor

SCHS149F

Features

∑ Buffered Inputs and Outputs

∑ Typical Propagation Delay: 13ns at V

CC

= 5V,

C

L

= 15pF, T

A

= 25

o

C

∑ Fanout (Over Temperature Range)

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

∑ Wide Operating Temperature Range . . . -55

o

C to 125

o

C

∑ Balanced Propagation Delay and Transition Times

∑ Significant Power Reduction Compared to LSTTL

Logic ICs

∑ HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30% of V

CC

at V

CC

= 5V

∑ HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

1

µ

A at V

OL

, V

OH

Description

The 'HC147 and CD74HCT147 are high speed silicon-gate

CMOS devices and are pin-compatible with low power

Schottky TTL (LSTTL).

The 'HC147 and CD74HCT147 9-input priority encoders

accept data from nine active LOW inputs (l

1

to l

9

) and

provide binary representation on the four active LOW inputs

(Y0 to Y3). A priority is assigned to each input so that when

two or more inputs are simultaneously active, the input with

the highest priority is represented on the output, with input

line l

9

having the highest priority.

These devices provide the 10-line to 4-line priority encoding

function by use of the implied decimal "zero". The "zero" is

encoded when all nine data inputs are HIGH, forcing all four

outputs HIGH.

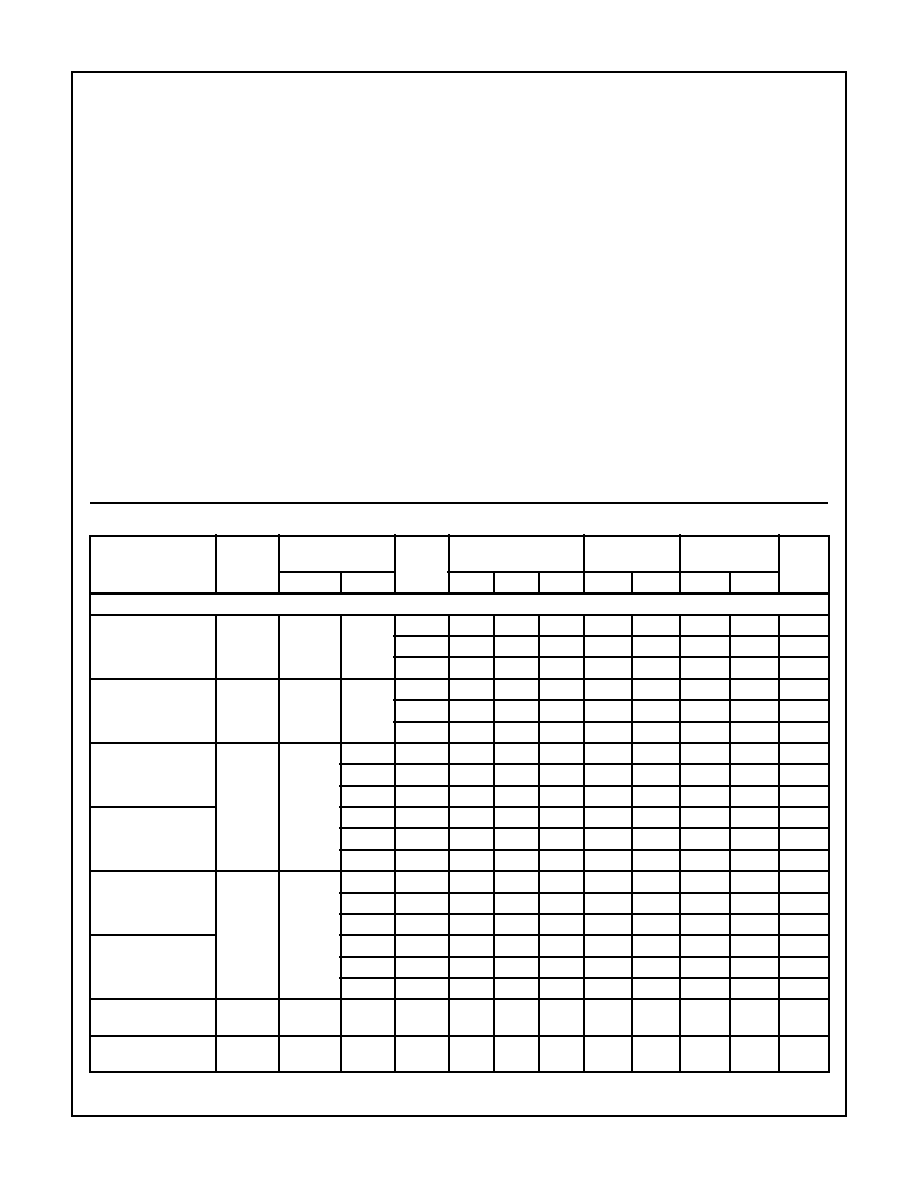

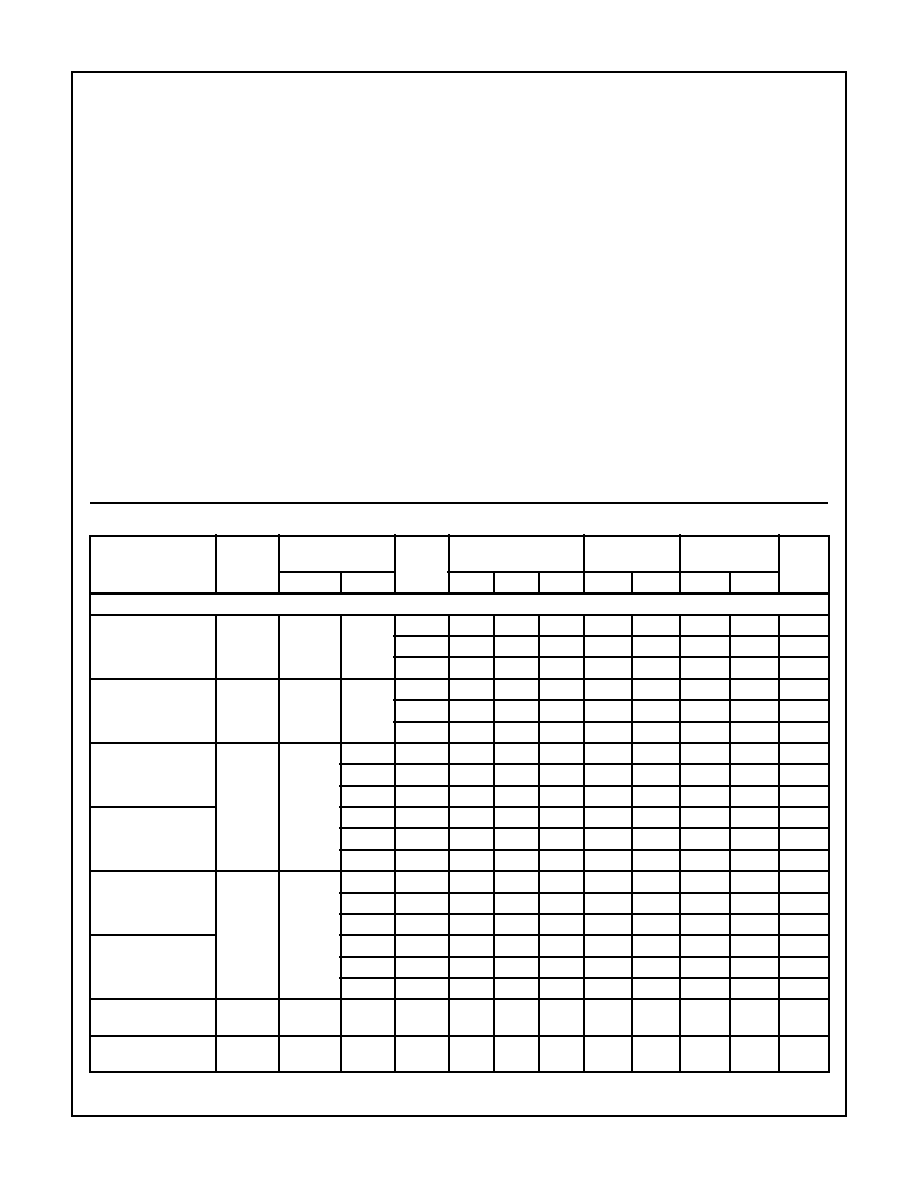

Pinout

CD54HC147 (CERDIP)

CD74HC147 (PDIP, SOIC, SOP, TSSOP)

CD74HCT147 (PDIP, TSSOP)

TOP VIEW

Ordering Information

PART NUMBER

TEMP. RANGE

(

o

C)

PACKAGE

CD54HC147F3A

-55 to 125

16 Ld CERDIP

CD74HC147E

-55 to 125

16 Ld PDIP

CD74HC147M

-55 to 125

16 Ld SOIC

CD74HC147MT

-55 to 125

16 Ld SOIC

CD74HC147M96

-55 to 125

16 Ld SOIC

CD74HC147NSR

-55 to 125

16 Ld SOP

CD74HC147PW

-55 to 125

16 Ld TSSOP

CD74HC147PWR

-55 to 125

16 Ld TSSOP

CD74HC147PWT

-55 to 125

16 Ld TSSOP

CD74HCT147E

-55 to 125

16 Ld PDIP

NOTE: When ordering, use the entire part number. The suffixes

96 and R denote tape and reel. The suffix T denotes a

small-quantity reel of 250.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

I4

I5

I6

I7

I8

Y2

GND

Y1

V

CC

Y3

I3

I2

I1

I9

Y0

NC

September 1997 - Revised November 2003

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

©

2003, Texas Instruments Incorporated

CD54HC147, CD74HC147,

CD74HCT147

High-Speed CMOS Logic

10- to 4-Line Priority Encoder

[ /Title

(CD74

HC147

,

CD74

HCT14

7)

/Sub-

ject

(High

Speed

CMOS

Logic

10-to-4

Line

Prior-

ity

Encode

r)

/Autho

r ()

/Key-

words

(High

Speed

CMOS

Logic

10-to-4

Line

Prior-

ity

Encode

r, High

Speed

CMOS

Logic

10-to-4

Line

Prior-

ity

2

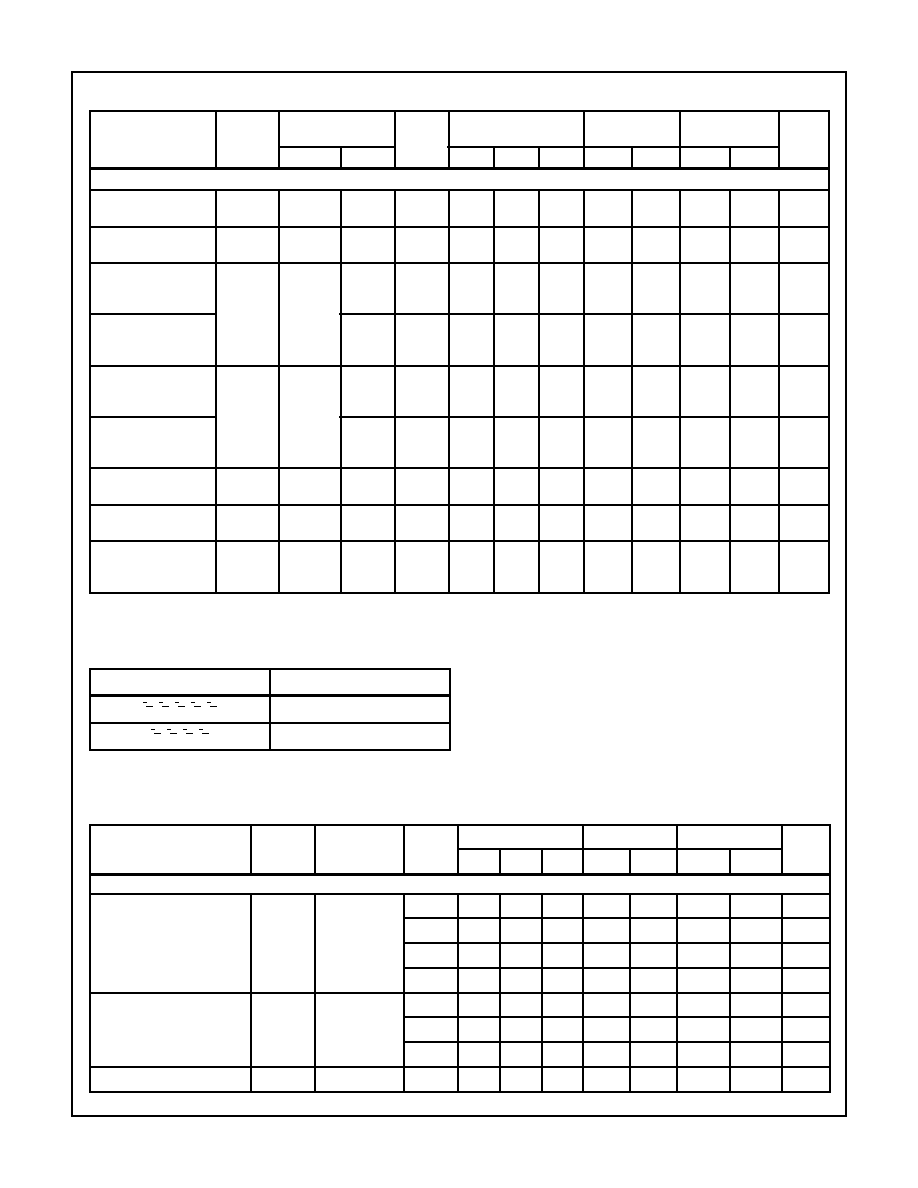

Functional Diagram

TRUTH TABLE

INPUTS

OUTPUTS

I1

I2

I3

I4

I5

I6

I7

I8

I9

Y3

Y2

Y1

Y0

H

H

H

H

H

H

H

H

H

H

H

H

H

X

X

X

X

X

X

X

X

L

L

H

H

L

X

X

X

X

X

X

X

L

H

L

H

H

H

X

X

X

X

X

X

L

H

H

H

L

L

L

X

X

X

X

X

L

H

H

H

H

L

L

H

X

X

X

X

L

H

H

H

H

H

L

H

L

X

X

X

L

H

H

H

H

H

H

L

H

H

X

X

L

H

H

H

H

H

H

H

H

L

L

X

L

H

H

H

H

H

H

H

H

H

L

H

L

H

H

H

H

H

H

H

H

H

H

H

L

H = High Logic Level, L = Low Logic Level, X = Don't Care

9

7

Y0

11

12

13

2

4

3

1

I7

I6

I5

I4

I3

I2

I1

5

I8

10

I9

GND = 8

V

CC

= 16

6

14

Y1

Y2

Y3

CD54HC147, CD74HC147, CD74HCT147

3

Absolute Maximum Ratings

Thermal Information

DC Supply Voltage, V

CC

. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V

DC Input Diode Current, I

IK

For V

I

< -0.5V or V

I

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . . . .±

20mA

DC Output Diode Current, I

OK

For V

O

< -0.5V or V

O

> V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .±

20mA

DC Output Source or Sink Current per Output Pin, I

O

For V

O

> -0.5V or V

O

< V

CC

+ 0.5V

. . . . . . . . . . . . . . . . . . . .±

25mA

DC V

CC

or Ground Current, I

CC or

I

GND

. . . . . . . . . . . . . . . . . .±

50mA

Operating Conditions

Temperature Range (T

A

) . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Supply Voltage Range, V

CC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V

HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, V

I

, V

O

. . . . . . . . . . . . . . . . . 0V to V

CC

Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

Package Thermal Impedance,

JA

(see Note 1):

E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

o

C/W

M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

o

C/W

NS (SOP) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

o

C/W

PW (TSSOP) Package . . . . . . . . . . . . . . . . . . . . . . . . . 108

o

C/W

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

DC Electrical Specifications

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

High Level Input

Voltage

V

IH

-

-

2

1.5

-

-

1.5

-

1.5

-

V

4.5

3.15

-

-

3.15

-

3.15

-

V

6

4.2

-

-

4.2

-

4.2

-

V

Low Level Input

Voltage

V

IL

-

-

2

-

-

0.5

-

0.5

-

0.5

V

4.5

-

-

1.35

-

1.35

-

1.35

V

6

-

-

1.8

-

1.8

-

1.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or V

IL

-0.02

2

1.9

-

-

1.9

-

1.9

-

V

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

-0.02

6

5.9

-

-

5.9

-

5.9

-

V

High Level Output

Voltage

TTL Loads

-

-

-

-

-

-

-

-

-

V

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

-5.2

6

5.48

-

-

5.34

-

5.2

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

2

-

-

0.1

-

0.1

-

0.1

V

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

0.02

6

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

-

-

-

-

-

-

-

-

-

V

4

4.5

-

-

0.26

-

0.33

-

0.4

V

5.2

6

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

or

GND

-

6

-

-

±

0.1

-

±

1

-

±

1

µ

A

Quiescent Device

Current

I

CC

V

CC

or

GND

0

6

-

-

8

-

80

-

160

µ

A

CD54HC147, CD74HC147, CD74HCT147

4

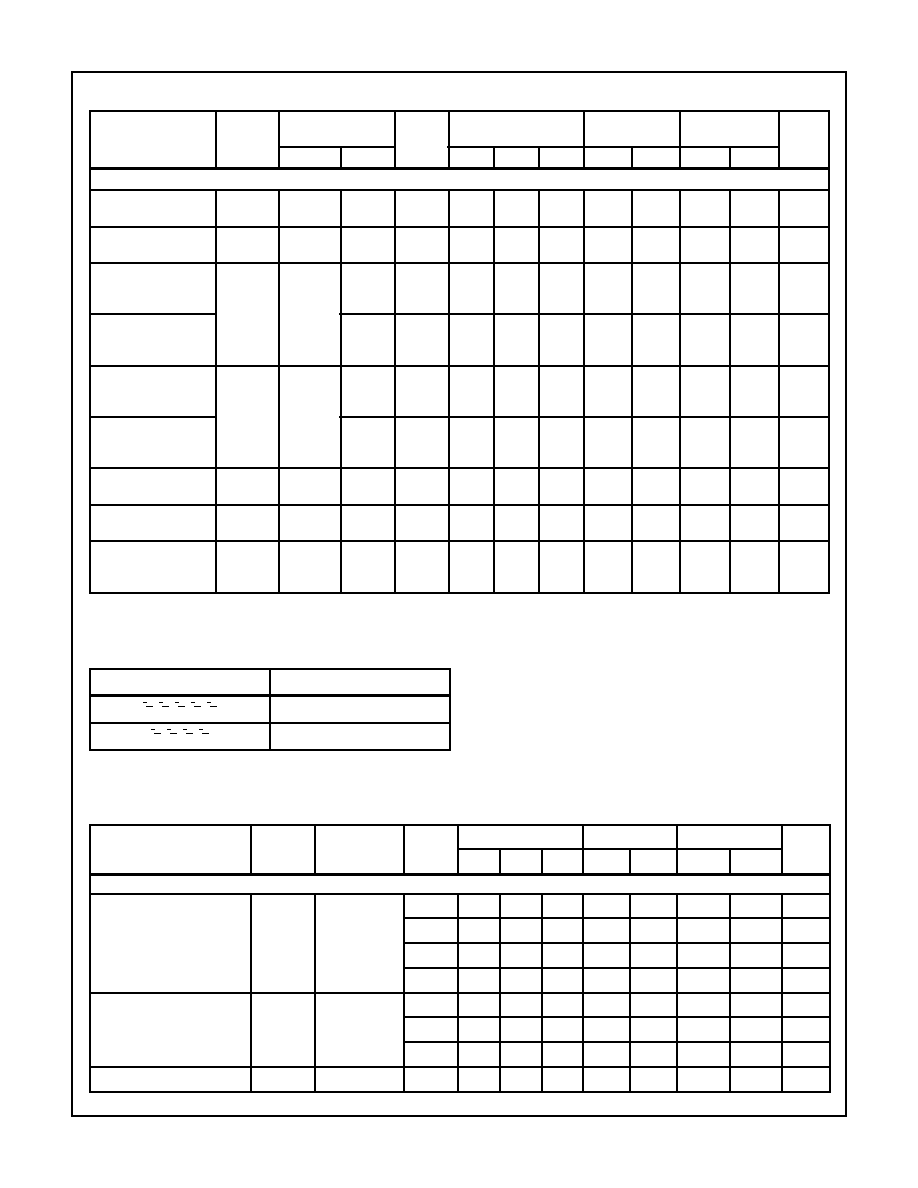

HCT TYPES

High Level Input

Voltage

V

IH

-

-

4.5 to

5.5

2

-

-

2

-

2

-

V

Low Level Input

Voltage

V

IL

-

-

4.5 to

5.5

-

-

0.8

-

0.8

-

0.8

V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or V

IL

-0.02

4.5

4.4

-

-

4.4

-

4.4

-

V

High Level Output

Voltage

TTL Loads

-4

4.5

3.98

-

-

3.84

-

3.7

-

V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or V

IL

0.02

4.5

-

-

0.1

-

0.1

-

0.1

V

Low Level Output

Voltage

TTL Loads

4

4.5

-

-

0.26

-

0.33

-

0.4

V

Input Leakage

Current

I

I

V

CC

and

GND

0

5.5

-

±

0.1

-

±

1

-

±

1

µ

A

Quiescent Device

Current

I

CC

V

CC

or

GND

0

5.5

-

-

8

-

80

-

160

µ

A

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

I

CC

(Note 2)

V

CC

-2.1

-

4.5 to

5.5

-

100

360

-

450

-

490

µ

A

NOTE:

2. For dual-supply systems theoretical worst case (V

I

= 2.4V, V

CC

= 5.5V) specification is 1.8mA.

DC Electrical Specifications

(Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITS

V

I

(V)

I

O

(mA)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HCT Input Loading Table

INPUT

UNIT LOADS

I

1

, I

2

, I

3

, I

6

, I

7

1.1

I

4

, I

5

, I

8

, I

9

1.5

NOTE: Unit Load is

I

CC

limit specified in DC Electrical Table, e.g.,

360

µ

A max at 25

o

C.

Switching Specifications

Input t

r

, t

f

= 6ns

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C

-55

o

C TO 125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

HC TYPES

Propagation Delay,

Input to Output (Figure 1)

t

PLH,

t

PHL

C

L

= 50pF

2

-

-

160

-

200

-

240

ns

4.5

-

-

32

-

40

-

48

ns

5

-

13

-

-

-

-

-

ns

6

-

-

27

-

34

-

41

ns

Transition Times

(Figure 1)

t

TLH

, t

THL

C

L

= 50pF

2

-

-

75

-

95

-

110

ns

4.5

-

-

15

-

19

-

22

ns

6

-

-

13

-

16

-

19

ns

Input Capacitance

C

IN

-

-

-

-

10

-

10

-

10

pF

CD54HC147, CD74HC147, CD74HCT147

5

Power Dissipation Capaci-

tance

(Notes 3, 4)

C

PD

-

5

-

32

-

-

-

-

-

pF

HCT TYPES

Propagation Delay,

Input to Output (Figure 2)

t

PLH

, t

PHL

C

L

= 50pF

4.5

-

-

35

-

44

-

53

ns

5

-

14

-

-

-

-

-

ns

Transition Times (Figure 2)

t

TLH

, t

THL

C

L

= 50pF

4.5

-

-

15

-

19

-

22

ns

Input Capacitance

C

IN

-

-

-

-

10

-

10

-

10

pF

Power Dissipation Capaci-

tance

(Notes 3, 4)

C

PD

-

5

-

42

-

-

-

-

-

pF

NOTES:

3. C

PD

is used to determine the dynamic power consumption, per gate.

4. P

D

= V

CC

2

f

i

(C

PD

+ C

L

) where f

i

= Input Frequency, C

L

= Output Load Capacitance, V

CC

= Supply Voltage.

Switching Specifications

Input t

r

, t

f

= 6ns (Continued)

PARAMETER

SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C

-40

o

C TO 85

o

C

-55

o

C TO 125

o

C

UNITS

MIN

TYP

MAX

MIN

MAX

MIN

MAX

Test Circuits and Waveforms

FIGURE 6. HC AND HCU TRANSITION TIMES AND PROPAGA-

TION DELAY TIMES, COMBINATION LOGIC

FIGURE 7. HCT TRANSITION TIMES AND PROPAGATION

DELAY TIMES, COMBINATION LOGIC

t

PHL

t

PLH

t

THL

t

TLH

90%

50%

10%

50%

10%

INVERTING

OUTPUT

INPUT

GND

V

CC

t

r

= 6ns

t

f

= 6ns

90%

t

PHL

t

PLH

t

THL

t

TLH

2.7V

1.3V

0.3V

1.3V

10%

INVERTING

OUTPUT

INPUT

GND

3V

t

r

= 6ns

t

f

= 6ns

90%

CD54HC147, CD74HC147, CD74HCT147