Adv Multi-Chemistry & Mutli-Cell Sync Switch-Mode Charger & Syst Power Selector (Rev. A)

www.ti.com

FEATURES

APPLICATIONS

DESCRIPTION

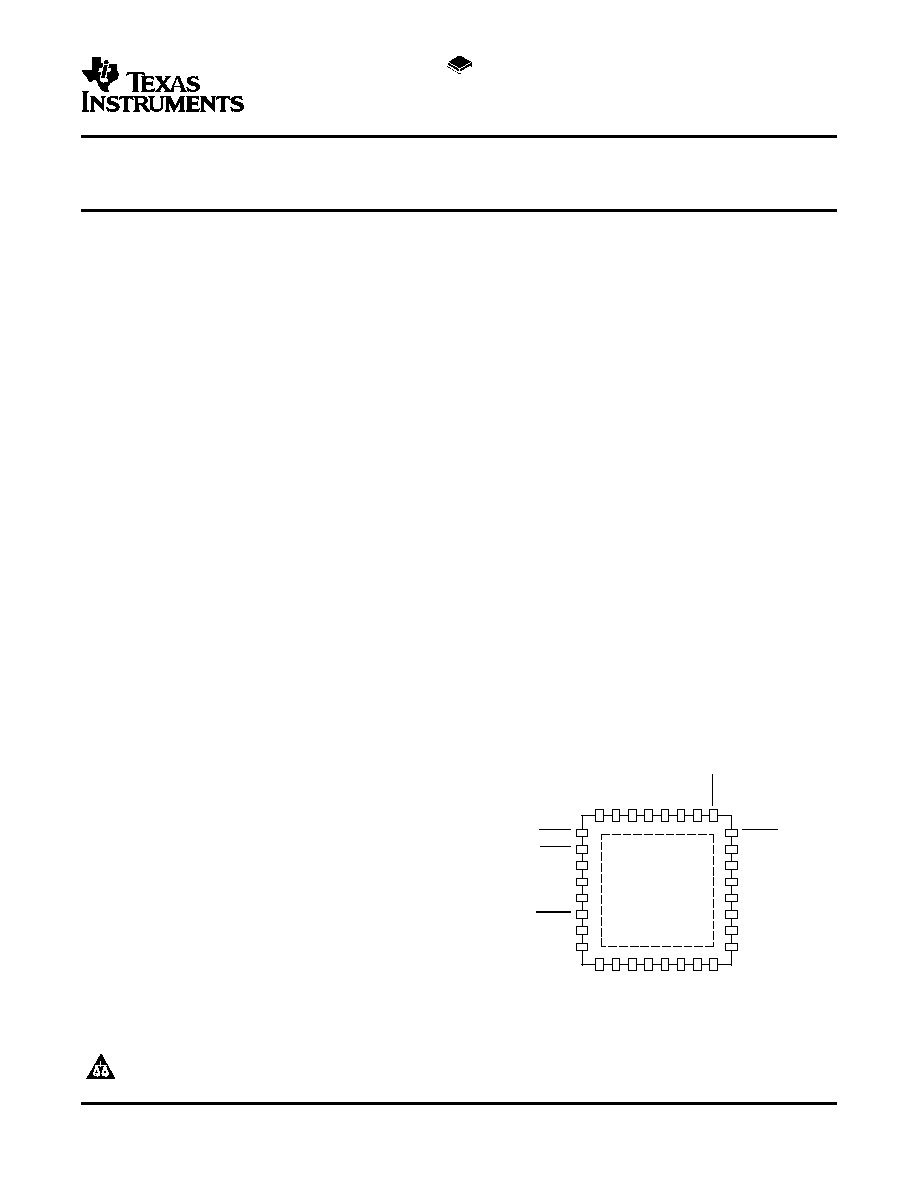

1

2

3

4

5

6

7

8

9

10

1

1

12

13

14

15

16

24

23

22

21

20

19

18

17

25

26

27

28

29

30

31

32

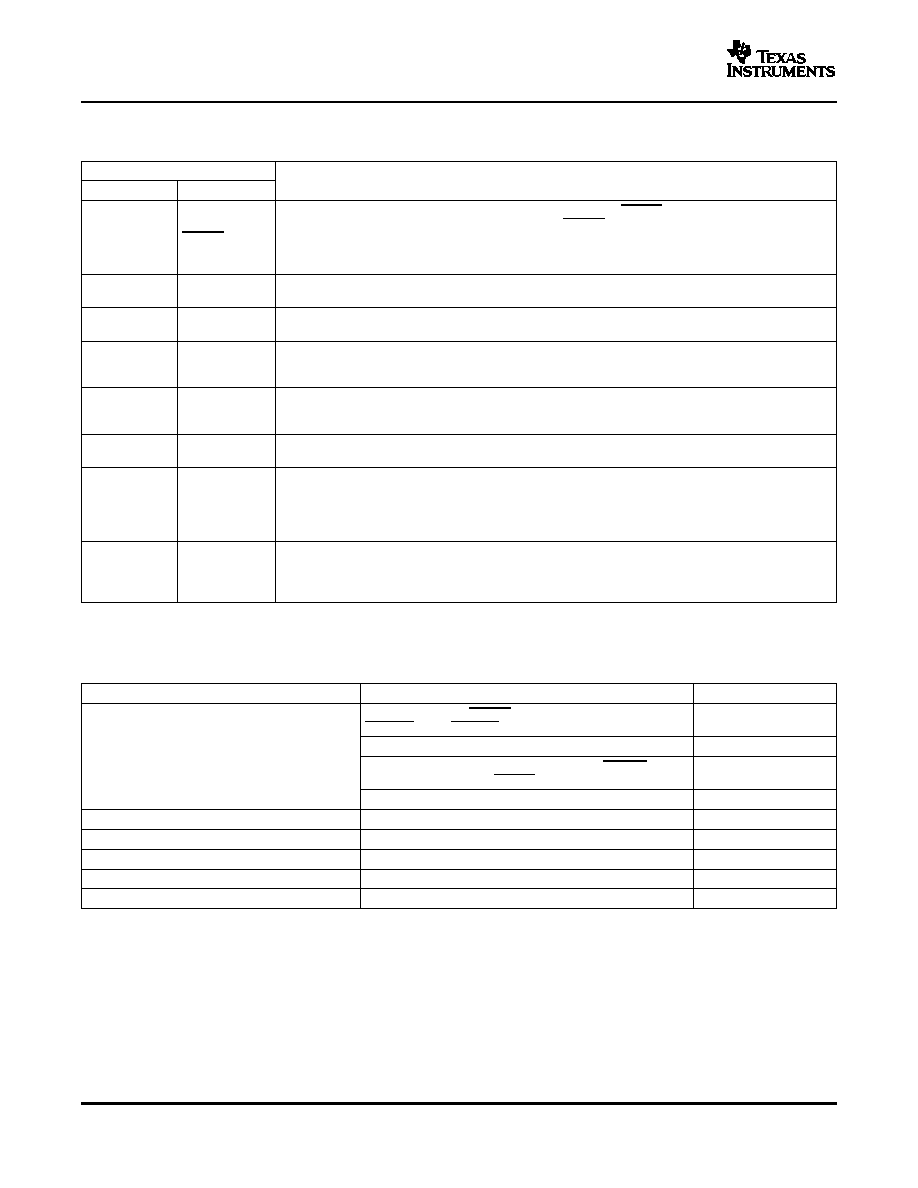

bq24721

CHGEN

ACDRV

ACN

ACP

ACDET

BYPASS

EAO

EAI

FBO

AGND

VREF5

VCC

SDA

SCL

TS

ISYNSET

IOUT

BAT

SRN

SRP

SYNN

SYNP

SYS

BATDRV

PVCC

BTST

HIDR

V

PH

REGN

LODR

V

PGND

ALARM

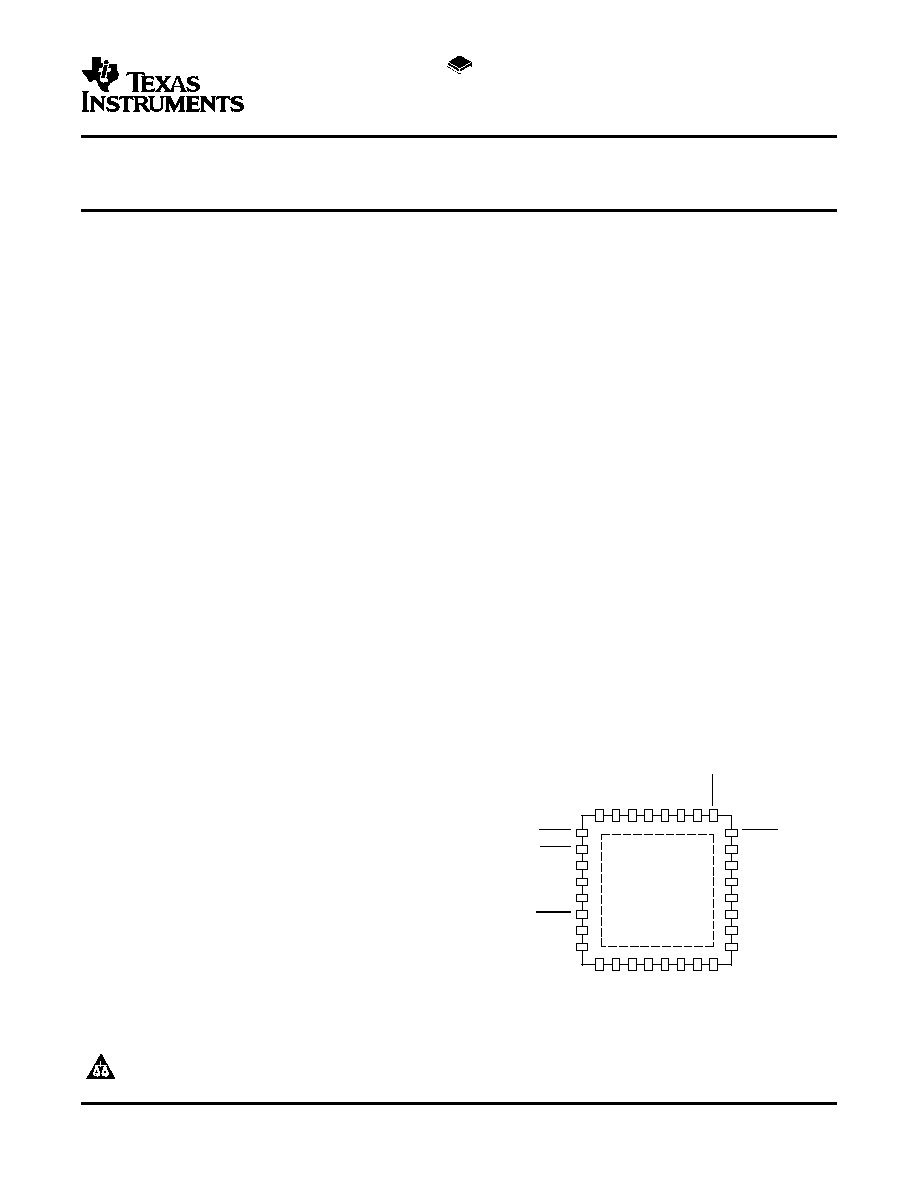

5x5 QFN PACKAGE (TOP VIEW)

bq24721

SLUS683A NOVEMBER 2005 REVISED JANUARY 2006

ADVANCED MULTI-CHEMISTRY AND MULTI-CELL SYNCHRONOUS SWITCH-MODE

CHARGER AND SYSTEM POWER SELECTOR

·

Portable Notebook Computers

·

High Efficiency NMOS-NMOS Synchronous

Buck Converter With User-Selectable 300 kHz

·

Portable DVD Players

or 500 kHz frequency

·

Webpads, PC Tablets

·

SBS-Like

(1)

SMBus Interface for Control and

Status Communications With Host

·

Programmable Battery Voltage, Charge

The bq24721 is a high efficiency synchronous battery

Current, and AC Adapter Current via SBS-Like

pack charger with high level of integration for portable

SMBus Interface

applications.

This

device

implements

a

high

performance analog front-end that interfaces to the

·

0.4% Charge Voltage Regulation Accuracy

system power management micro-controller through

·

3% Charge Current Regulation Accuracy

a simplified SBS-like SMBus interface.

·

3% Adapter Current Regulation Accuracy

The dynamic power management (DPM) function

Dynamic Power Management (DPM)

modifies the charge current depending on system

·

2% Accuracy Integrated Charge and AC

load conditions, avoiding ac adapter overload.

Adapter 20x Current Amplifier Output

High

accuracy

current

sense

amplifiers

enable

·

3-Cell and 4-Cell Li-Ion Voltage Regulation

accurate measurement of either the charge current or

9 V, 12 V14.4 V, 16 V19.2 V

the ac adapter current, allowing termination of

nonsmart packs and monitoring of overall system

·

Battery Pack Voltage Operating Range

power.

0 V19.2 V

·

AC Adapter Operating Range 8 V28 V

The adapter isolation diode can be bypassed or

entirely replaced with an external MOSFET using a

·

99.5% Max Duty Cycle

control signal provided by the bq24721, thus reducing

·

Internal Soft Start

overall power dissipation.

·

Integrated 5% 5-V LDO When AC Adapter

Integrated features such as charger soft start, charge

Applied

overcurrent protection, and IC temperature monitoring

·

6-V Drive Supply Voltage for Increased

provide a second level of protection, in addition to

Efficiency

pack and system protection functions.

·

Reverse Battery to Adapter Discharge

Protection

·

Battery/Adapter to System Power Selector

Function

·

Charge and Adapter Overcurrent Protection

·

Battery Thermistor Sense, TS, Comparators

·

Available in 32-Pin 5 x 5 mm QFN Package

(1)

SBS-Like interface is not 100% SBS compliant. SBS-Like

interface is SMBus1.1 complaint but does not support Packet

Error Correction (PEC). The control and status registers were

changed to simplify and enhance notebook charger control.

An eight bit address (0x12) is used. See

Table 1

for a

comparison between SBS-like vs SBS Specification.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright © 20052006, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

www.ti.com

DEVICE INFORMATION

bq24721

SLUS683A NOVEMBER 2005 REVISED JANUARY 2006

These devices have limited built-in ESD protection. The leads should be shorted together or the device

placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

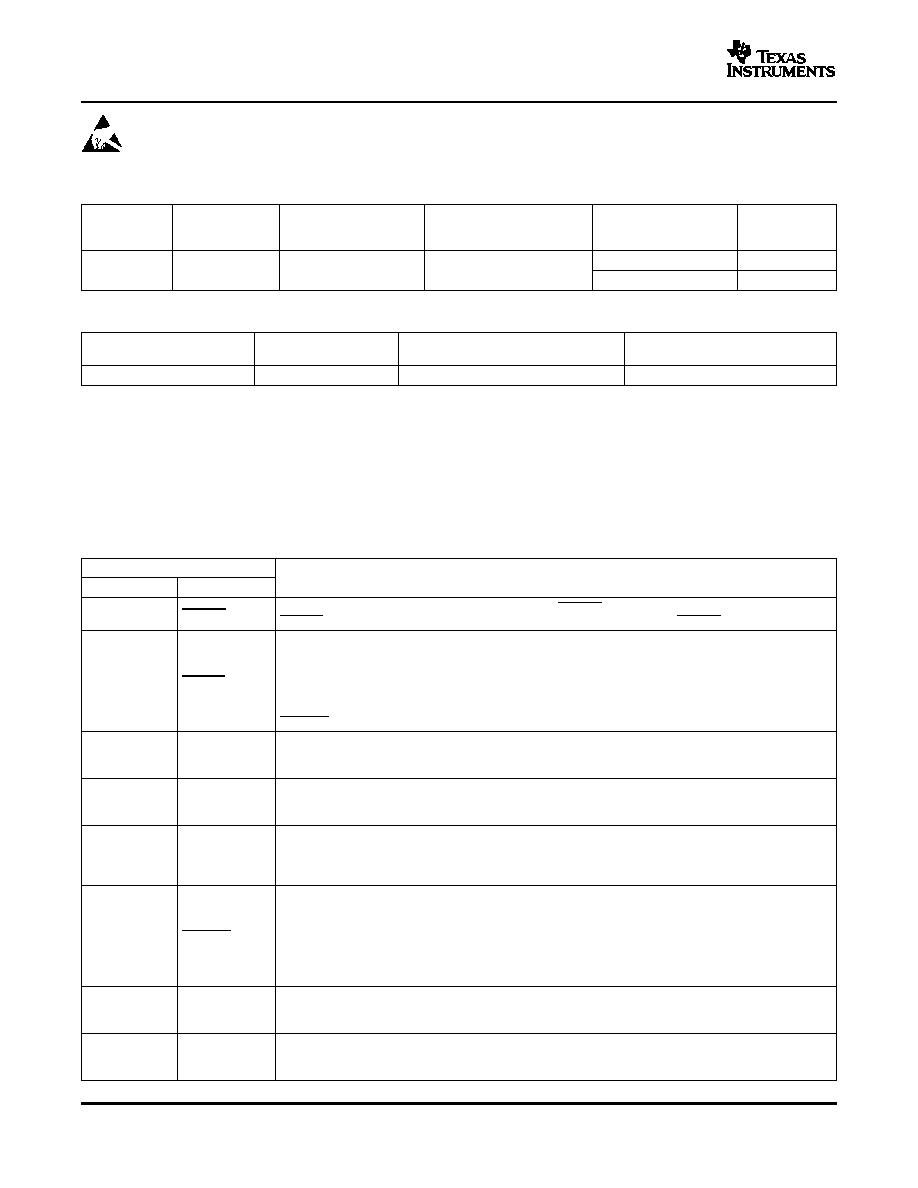

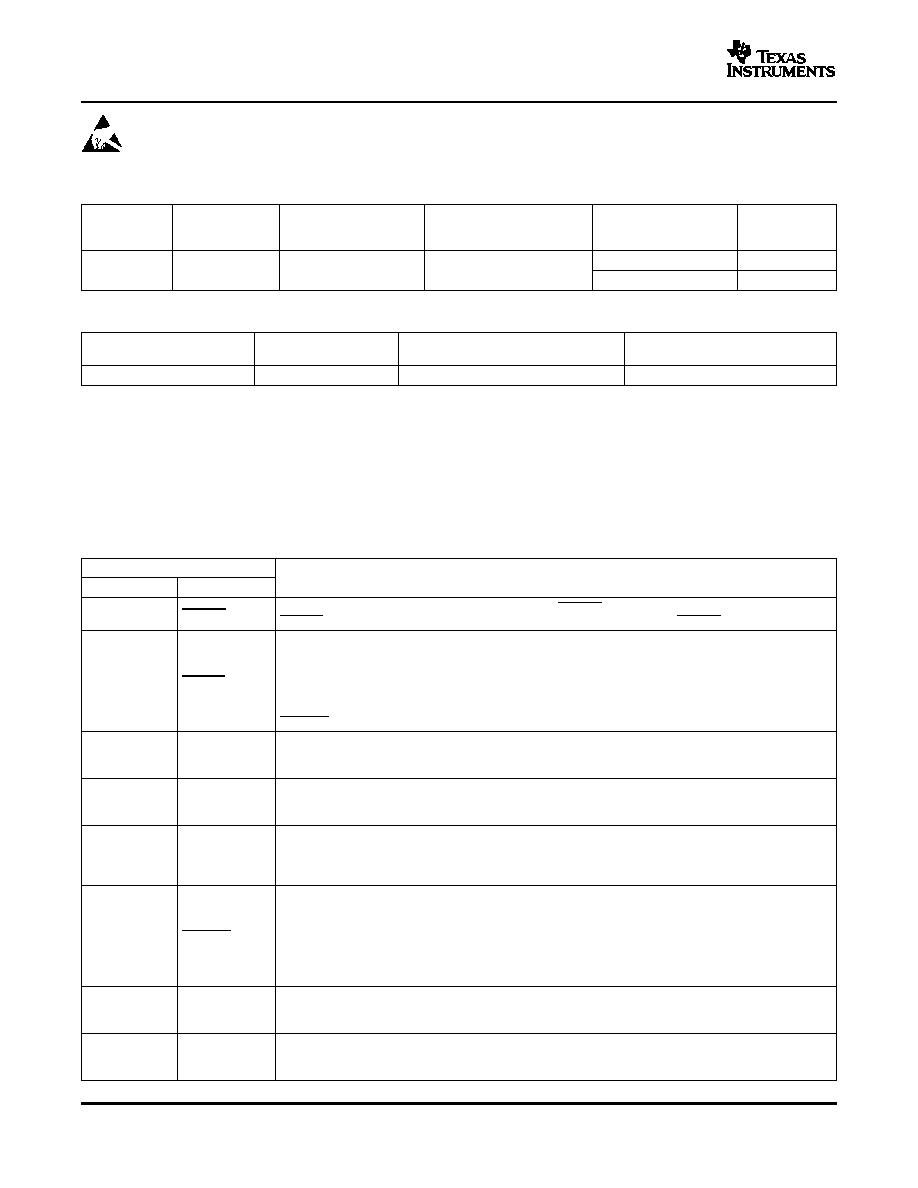

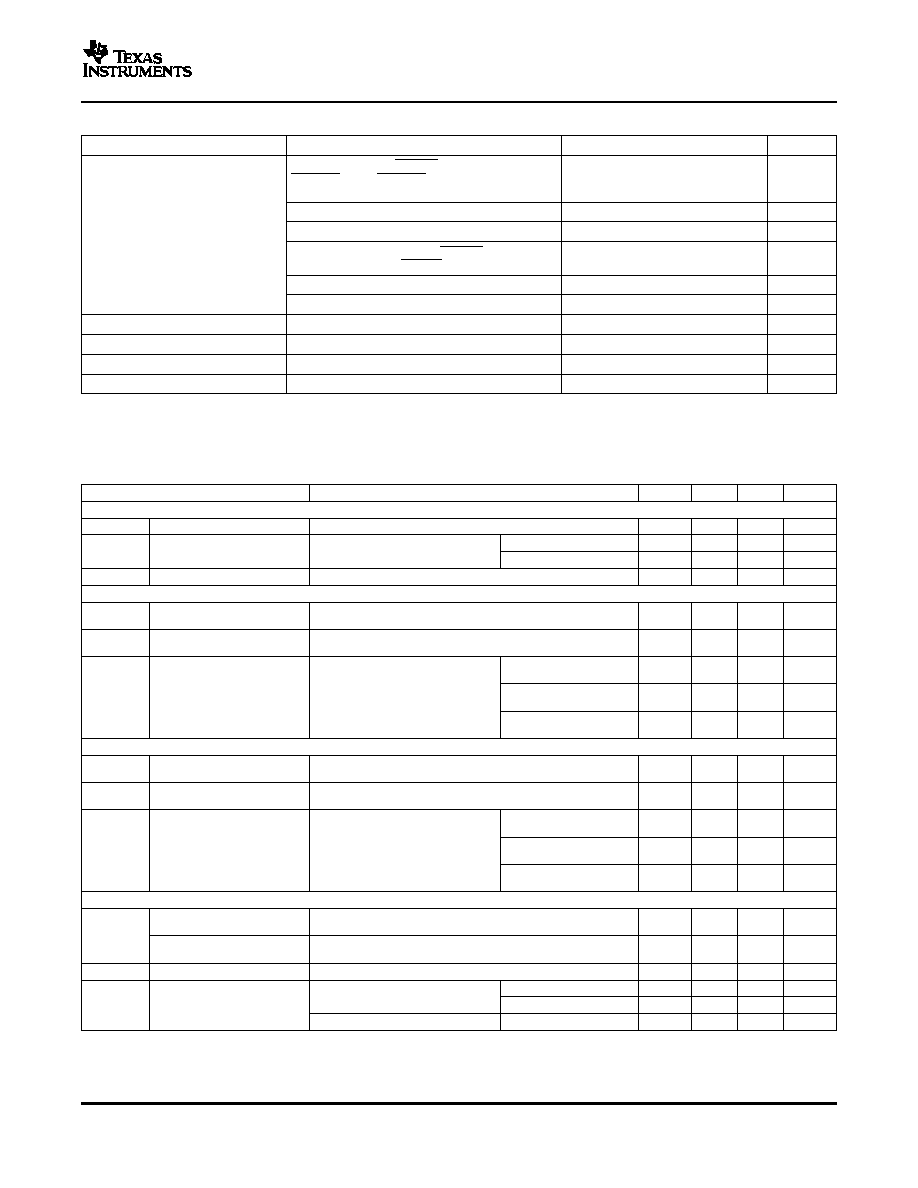

ORDERING INFORMATION

BATTERY SHORTED

THERMISTOR

ORDERING NUMBER

PART NO.

PACKAGE

(VERY LOW BATTERY

QUANTITY

SENSE

(TAPE AND REEL)

VOLTAGE) OPERATION

bq24721RHBR

3000

32 PIN

Charge Current Changes to

bq24721

TS

5x5mm QFN

C/8

bq24721RHBT

250

PACKAGE THERMAL DATA

TA

40

°

C

DERATING FACTOR

PACKAGE

(1)

JA

POWER RATING

ABOVE T

A

= 25

°

C

RHB

(2)

36

°

C/W

2.36 W

0.028 W/

°

C

(1)

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

Web site at

www.ti.com

.

(2)

This data is based on using the JEDEC High-K board and the exposed die pad is connected to a copper pad on the board. This is

connected to the ground plane by a 2

×

3 via matrix.

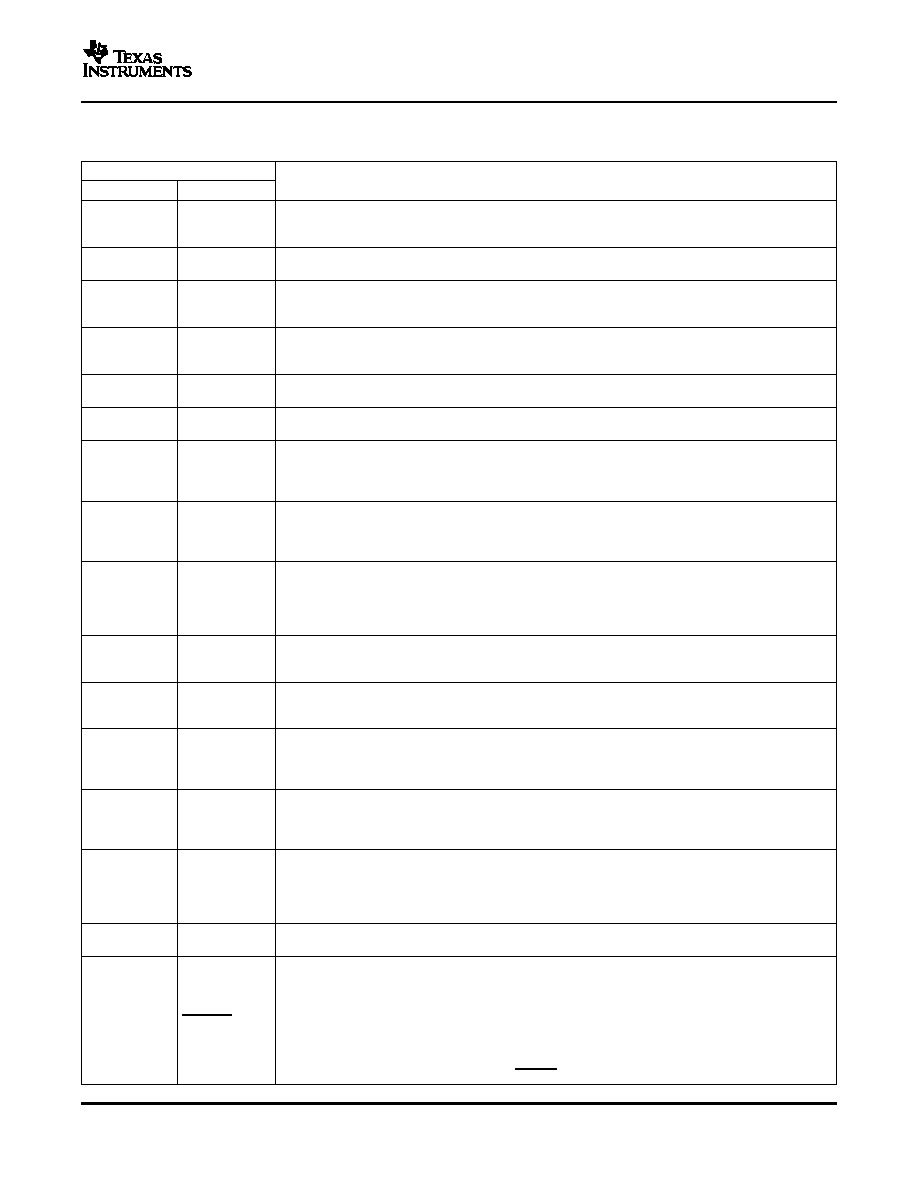

TERMINAL FUNCTIONS

TERMINAL

DESCRIPTION

NO.

NAME

Charge enable logic level low input. Logic HI on the CHGEN pin disables the charger. Logic LO on the

1

CHGEN

CHGEN pin enables the charger. When the SMBus control register = bit0, CHGEN is also LO.

AC adapter to system switch driver output. Connect directly to the gate of the ACFET PMOS power

FET. Connect the FET source to the PVCC node and negative side of the input current-sense resistor.

Connect the FET drain to the system load side. Recommend placing a 10-k

resistor from the gate to

2

ACDRV

the source of the Bypass FET. If needed, an optional capacitor from gate to source of the ACFET is

used to help slow down the ON and OFF times. The internal gate drive is asymmetrical allowing a

quick turn-off and slower turn-off in addition to the internal break-before-make logic with respect to the

BATDRV.

Adapter current sense resistor, negative input. An optional 0.1-

µ

F ceramic capacitor is placed from this

3

ACN

pin to AGND for common-mode filtering. An optional 0.1-

µ

F ceramic capacitor is placed from ACN to

ACP to provide differential-mode filtering.

Adapter current sense resistor, positive input. Place this on the adapter side of the input current sense

4

ACP

resistor. Recommend placing a 0.1-

µ

F ceramic capacitor from ACP to AGND to provide common-mode

filtering.

AC adapter detected sense voltage input. Connect a voltage divider resistor from adapter input (before

Bypass FET) to ACDET, and another resistor from ACDET to AGND, in order to program adapter

5

ACDET

detect threshold of 1.2 V. ACDET threshold should be greater than maximum battery regulation

voltage, and lower than the minimum adapter voltage.

Gate drive for the adapter input BYPASS switch to prevent reverse discharge from the battery to the

input. Connect this pin directly to the gate of the input bypass PMOS power FET. The source of the

FET is connected to the adapter input voltage node. Recommend placing a 10-k

resistor from the

6

BYPASS

gate to the source of the BYPASS FET. The drain of the FET is connected to the positive node of the

input current-sense resistor. An optional capacitor can be placed from the gate to the source to

slow-down the switching times. Adjusting the turn-on and turn-off times is typically not needed for this

FET.

Error amplifier output for compensation. Connect the feedback compensation components from EAO to

7

EAO

EAI. Typically a capacitor in parallel with a series resistor and capacitor. See the compensation

calculation procedures. This node is internally compared to the PWM saw-tooth oscillator.

Error amplifier input for compensation, also connect the feedback compensation components from EAI

8

EAI

to EAO. Connect the input compensation components from FBO to EAI. See the compensation

calculation procedures.

2

www.ti.com

bq24721

SLUS683A NOVEMBER 2005 REVISED JANUARY 2006

DEVICE INFORMATION (continued)

TERMINAL FUNCTIONS (continued)

TERMINAL

DESCRIPTION

NO.

NAME

Feedback output for compensation. Connect the input compensation components from FBO to EAI.

9

FBO

Typically, a resistor in parallel with a series resistor and capacitor. See the compensation calculation

procedures.

Analog ground. Ground connection for low current sensitive analog and digital signals. Only connect to

10

AGND

the PGND node by connecting to the PowerPADTM underneath the IC.

5-V regulated voltage output, used for internal bias and the reference for programming the TS

11

VREF5

thermistor sense network. Used to indicate adapter present status. It is enabled by ac detected.

Connect a 1-

µ

F ceramic capacitor from VREF5 pin to AGND as close to IC as possible.

IC analog positive supply. Connect to adapter input, or diode, or by putting a diode from adapter input

12

VCC

and a diode from battery pack to VCC. Put a 1-

µ

F ceramic capacitor from VCC to AGND, as close to

the IC as possible.

SMBus Data input. Connect to SMBus data line from the host controller. A 10-k

pullup resistor to the

13

SDA

host controller supply rail is needed.

SMBus Clock input. Connect to SMBus clock line from the host controller. A 10-k

pullup resistor to

14

SCL

the host controller supply rail is needed.

Thermistor sense input. Use a voltage divider from VREF5 to TS and AGND. Place a resistor from

VREF to TS, and a resistor from TS to AGND to program the hot and cold battery pack thermistor

15

TS

temperatures. Charge is disabled when outside the hot/cold window. The TS pin is also used to detect

if a battery is connected.

Program current threshold for synchronous to nonsynchronous regulation transition. Place a resistor

from ISYNSET to AGND to program the charge undercurrent threshold to force nonsynchronous

16

ISYNSET

converter operation at low output current and prevent negative inductor current. Threshold should be

set from ½ inductor current ripple to full value of inductor current ripple.

Battery charger or adapter current amplifier output. Current sense amplifier that outputs a voltage 20x

the current sense resistor differential voltage. The output can be selected by SMBus charge control

17

IOUT

register (0x12) bit3 to be the input adapter current (ACP-ACN), or the battery charge current

(SRP-SRN). Place a 0.1-

µ

F capacitor from IOUT to AGND for filtering the output ripple. Optionally, add

an RC filter after the output filter for further filtering.

Battery voltage remote sense. Directly connect a kelvin sense trace from the battery pack positive

18

BAT

terminal to the BAT pin to accurately sense the battery pack voltage. Place a 0.1-

µ

F capacitor from

BAT to AGND close to the IC to filter high frequency noise.

Charge current sense resistor, negative input. Connect to the charge current sense resistor negative

19

SRN

terminal. Optionally, add a 0.1-

µ

F ceramic capacitor from SRN to AGND near the IC for common-mode

filter.

Charge current sense resistor, positive input. Connect to the charge current sense resistor positive

terminal. Recommend placing a 0.1-

µ

F ceramic capacitor from SRP to AGND near the IC for

20

SRP

common-mode filter. Optionally, place a 0.1-

µ

F ceramic capacitor from SRP to SRN near the IC for

differential-mode filter.

Charge overcurrent and charge undercurrent negative sense input. Connect to the charge current

sense resistor negative terminal. If sensing the same sense resistor as SRN, the user can connect

21

SYNN

directly to the SRN pin and no further filter capacitors are needed. To sense a different sense resistor,

add a 0.1-

µ

F ceramic capacitor from SYNN to AGND near the IC for common-mode filter.

Charge overcurrent and charge undercurrent negative sense input. Connect to the charge current

sense resistor positive terminal. If sensing the same sense resistor as SRP, the user can connect

22

SYNP

directly to the SRP pin, and no further filter capacitors are needed. To sense a different sense resistor,

add a 0.1-

µ

F ceramic capacitor from SYNP to AGND near the IC for common-mode filter, and place a

0.1-

µ

F ceramic capacitor from SYNP to SYNN near the IC for differential-mode filter.

System load, voltage sense. Connect directly to the system load node and the drain of the BAT PMOS

23

SYS

power FET.

Battery to system switch driver output. Gate drive for the battery to system load BAT PMOS power FET

to isolate the system from the battery to prevent current flow from the system to the battery, while

allowing a low impedance path from battery to system while discharging the battery pack to the system

load. Connect this pin directly to the gate of the input BAT PMOS power FET. Connect the source of

24

BATDRV

the FET to the system load voltage node. Connect the drain of the FET to the battery pack positive

node. Recommend placing a 10-k

resistor from the gate to the source of the BAT FET. An optional

capacitor is placed from the gate to the source to slow-down the switching times. The internal gate

drive is asymmetrical allowing a quick turn-off and slower turn-off in addition to the internal

break-before-make logic with respect to the ACDRV.

3

www.ti.com

ABSOLUTE MAXIMUM RATINGS

bq24721

SLUS683A NOVEMBER 2005 REVISED JANUARY 2006

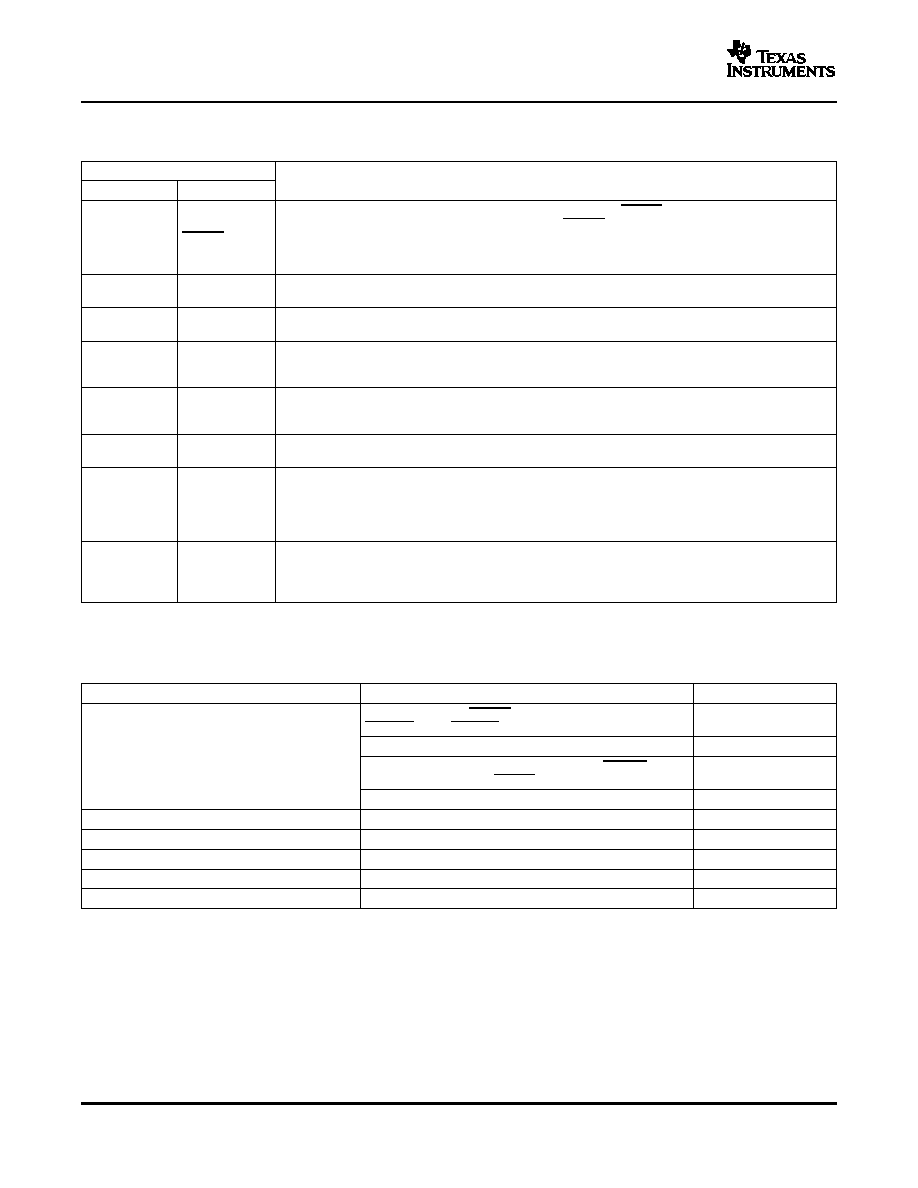

DEVICE INFORMATION (continued)

TERMINAL FUNCTIONS (continued)

TERMINAL

DESCRIPTION

NO.

NAME

Alarm indicating charger status change, open-drain output. The ALARM is pulled low (LO) whenever

the SMBus status register (0x13) has a change. The ALARM output is cleared (HI) when the SMBus

25

ALARM

status (0x13) register is read, or there is a reset. This is used to alert the host and initiate an interrupt

with the host instead of having to continuously poll the charger. A 10-k

pull-up resistor to the host

controller supply rail is needed.

Power ground. Ground connection for the high-current power converter nodes. Only connect to the

26

PGND

AGND node by connecting to the PowerPADTM underneath the IC.

PWM low side driver output. Connect directly to the gate of the low-side NMOS power FET with a short

27

LODRV

trace.

Low-side driver gate voltage regulator and source for high-side driver bootstrap voltage. Add a 1-

µ

F

28

REGN

ceramic capacitor from REGN pin to PGND pin, close to the IC. Place a small signal Schottky diode

from REGN to BTST for bootstrap voltage.

High-side driver negative supply. Connect directly to the source of the high-side NMOS FET with a

29

PH

short trace. This node is the common connection between the high-side FET, low-side FET, and output

inductor. Connect a 0.1-

µ

F boot-strap ceramic capacitor from BTST to PH.

PWM high side driver output. Connect directly to the gate of the high-side NMOS power FET with a

30

HIDRV

short trace.

High-side driver positive supply, connect pos-side of boot-strap capacitor. Connect a 0.1-

µ

F bootstrap

capacitor from the BTST pin to the PH node. Also, connect a bootstrap diode with the anode connected

31

BTST

to the REGN pin and the cathode connected to the BTST pin. An optional 4.7-

- 15-

series resistor

is placed between the BTST pin and the bootstrap-diode/capacitor junction to slow-down the turn-on

time of the high-side FET for reducing ringing due to high dv/dt of the phase node.

IC power positive supply. Connect directly to the drain of the high-side NMOS power FET. Recommend

placing at least a 10-

µ

F ceramic capacitor directly from the drain of the high-side NMOS power FET to

32

PVCC

PGND. Up to 40

µ

F may be needed to prevent resonance filtering inductance. Also, a 0.1-

µ

F

decoupling ceramic capacitor is recommended.

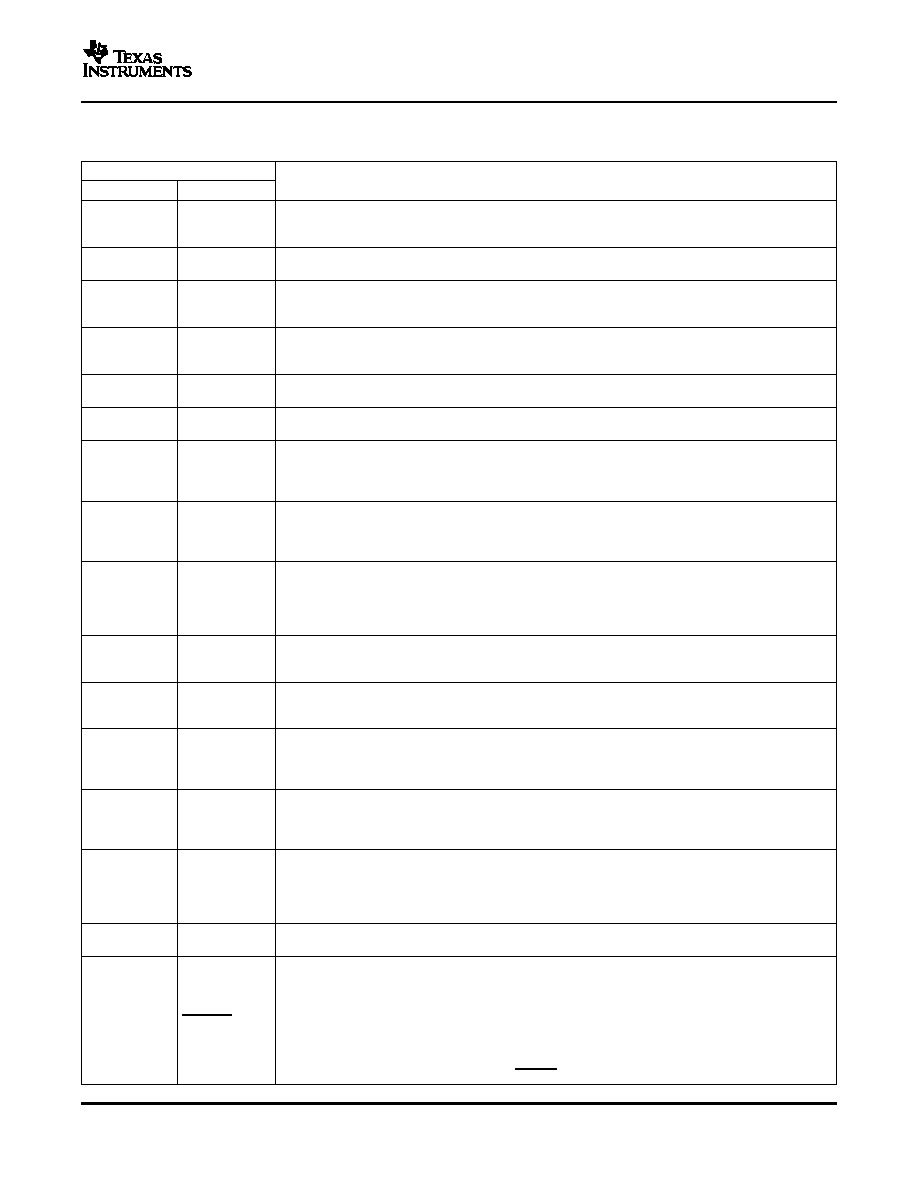

over operating free-air temperature range (unless otherwise noted)

(1) (2)

PARAMETER

PIN

VALUE / UNIT

ACN, ACP, PVCC, ACDRV, SYNN, SYNP, SRP, SRN,

0.3 V to 30 V

BATDRV, BAT, BYPASS, SYS, VCC

PH

1 V to 30 V

Supply voltage range

LODRV, REGN, FBO, EAI, EAO, ISYNSET, CHGEN, TS ,

0.3 V to 7 V

VREF5, ACDET, IOUT, ALARM, SCL, SDA

BTST, HIDRV (with respect to AGND and PGND)

1 V to 36 V

Maximum differential voltage

AGND-PGND

0.3 V to 0.3 V

Maximum difference voltage

ACPACN , SRPSRN, and SYNPSYNN

0.6 V

Operating ambient temperature range (T

A

)

40

°

C to 85

°

C

Maximum junction temperature (T

J_MAX

)

150

°

C

Storage temperature range (T

stg

)

65

°

C to 150

°

C

(1)

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2)

All voltages are with respect to AGND, unless otherwise noted. Currents are positive into, negative out of the specified terminal. Consult

Packaging Section of the Databook for thermal limitations and considerations of packages.

4

www.ti.com

RECOMMENDED OPERATING CONDITIONS

ELECTRICAL CHARACTERISTICS

bq24721

SLUS683A NOVEMBER 2005 REVISED JANUARY 2006

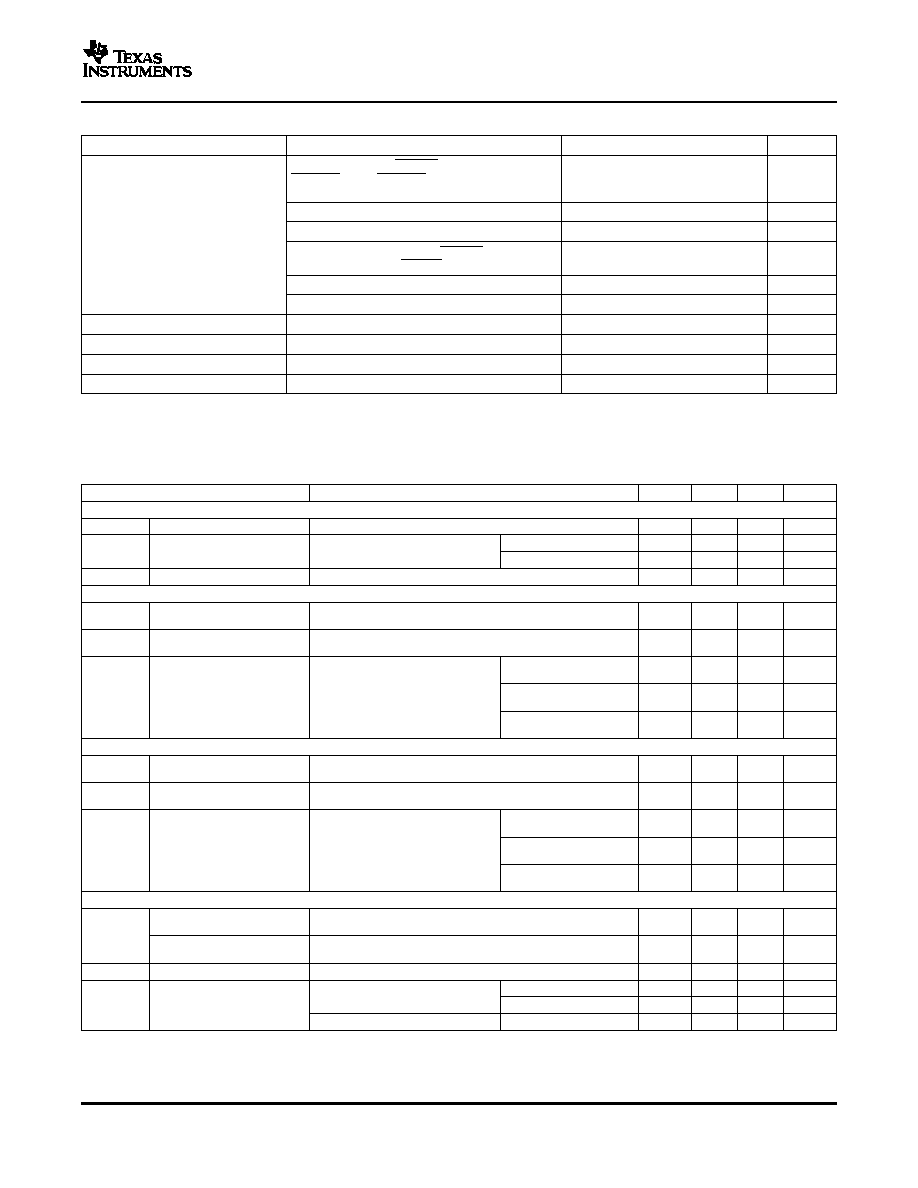

PARAMETER

PIN

MIN

NOM

MAX

UNIT

ACN, ACP, PVCC, ACDRV, SRP, SRN,

BATDRV, BAT, BYPASS, SYS, VCC, SYNN,

0

24

V

SYNP

PH

0.5

30

V

LODRV, REGN, VREF5

0

6.5

V

Supply voltage range

FBO, EAI, EAO, ISYNSET, CHGEN, TS ,

0

5.5

V

ACDET, SCL, SDA, ALARM

IOUT, ACDET

0

5.5

V

BTST, HIDRV

0

30

V

Maximum differential voltage

AGND-PGND

0

V

Maximum difference voltage

ACPACN, SYNNSYNP, SRPSRN

0.5

V

Junction temperature Range (T

J

)

0

125

°

C

Storage temperature Range (T

stg

)

-55

150

°

C

8 Vdc

V

(VCC)

24 Vdc, 0

°

C

T

J

125

°

C, all voltages with respect to AGND (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

BATTERY VOLTAGE REGULATION

V

(BAT_ICR)

VBAT Input voltage range

V

(BAT)

0

PVCC

V

T

J

= 0

°

C 85

°

C

0.4%

0.4%

Full valid voltage DAC range,

Battery Regulation Voltage Accuracy

SMBus DAC register 0

×

15

T

J

= 0

°

C 125

°

C

0.5%

0.5%

V

(VBATREG)

BAT voltage regulation range

9

19.2

V

PWM AC ADAPTER INPUT CURRENT REGULATION, DPM (Dynamic Power Management), I

(REG_DPM)

= V

(IREG_DPM)

/R

(SENSE_DPM)

ACP-ACN differential voltage range

V

(IREG_DPM)

= V

(ACP)

- V

(ACN)

V

(IREG_DPM)

1.28

162.56

mV

for input current regulation

SMBus DAC register 0

×

3F, bits b0b13

Current regulation LSB programming

V

(ACP-ACN)

/ 10m

I

(REG_step_DPM)

128

mA

current step

Using a 10m

sense resistor, R

(SNS)

V

(ACP)

V

(ACN)

> 40.96 mV

3%

3%

(4096 mA with 10 m

)

V

CC

V

CC

(min),

V

CC

V

I(BAT)

+ V

(DO-MAX)

,

(1)

V

(ACP)

V

(ACN)

> 20.48 mV

Current regulation accuracy

Over differential threshold range, V

(IREG)

,

5%

5%

(2048 mA with 10 m

)

Does not include error induced by the

tolerance of the sense resistor, R

(SNS)

V

(ACP)

V

(ACN)

> 5.12 mV

25%

25%

(512 mA with 10 m

)

PWM BATTERY CHARGE CURRENT REGULATION, I

(REG_CHG)

= V

(IREG_CHG)

/ R

(SENSE_CHG)

SRP-SRN differential voltage range

V

(IREG_CHG)

= V

(SRP)

- V

(SRN)

V

(IREG_CHG)

1.28

162.56

mV

for input current regulation

SMBus DAC register 0

×

14, bits b0b13

Current regulation LSB programming

V

(SRP-SRN)

/ 10 m

I

(REG_step_CHG)

128

mA

current step

Using a 10m

sense resistor, R

(SNS)

V

(SRP-SRN)

> 40.96 mV

3%

3%

(4096 mA with 10 m

)

V

CC

V

CC

(min),

V

CC

V

I(BAT)

+ V

(DO-MAX)

,

(1)

V

(SRP-SRN)

>20.48 mV

Current regulation accuracy

Over differential threshold range, V

(IREG)

,

5%

5%

(2048 mA with 10 m

)

Does not include error induced by the

tolerance of the sense resistor, R

(SNS)

V

(SRP-SRN)

> 5.12 mV

25%

25%

(512 mA with 10 m

)

CURRENT SENSE AMPLIFIERS IBAT AMPLIFIER and IADAPT AMPLIFIER

MUX TO IOUT

SRP, SRN common-mode input

2.5

20

V

voltage range

V

(IOUT_IBAT)

IOUT output voltage range with IBAT

V

(IOUT)

= V

(SRP, SRN)

×

A

(IBAT)

0

3.5

V

selected

V

(BAT)

> 2.5 V or V

(BAT)

> V

(IOUT)

+ V

(DO-MAX)

(1)

G

(IBAT)

Voltage gain

A

(IOUT)

= V

(IOUT)

/ V

(SRP, SRN)

20

V/V

V

(SRP, SRN)

= 40 mV and higher

2%

2%

V

(BAT)

> 2.5 V or V

(BAT)

>

V

(IOUT)

+ V

(DO-MAX)

(1)

Charge current amplifier accuracy

V

(SRP, SRN)

= 20 mV and higher

3%

3%

V

(SRP, SRN)

= 5 mV and higher

25%

25%

(1)

V

(DO-max)

is defined as the maximum drop-out voltage. V

(DO-MAX)

= 1 V unless other wise specified. In an actual application, V

(DO - MAX)

= (R

(SNS)

×

I

O

) + V

(DSON_HIGH_SIDE_FET)

+ V

(DSON_BYPASS_FET)

.

5

Document Outline