CD54ACT163, CD74ACT163

4-BIT SYNCHRONOUS BINARY COUNTERS

SCHS300 ≠ APRIL 2000

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Inputs Are TTL-Voltage Compatible

D

Internal Look-Ahead for Fast Counting

D

Carry Output for n-Bit Cascading

D

Synchronous Counting

D

Synchronously Programmable

D

Package Options Include Plastic

Small-Outline (M), Standard Plastic (E) and

Ceramic (F) DIPs

description

The CD54ACT163 and CD74ACT163 devices

are 4-bit binary counters. These synchronous,

presettable counters feature an internal carry

look-ahead for application in high-speed counting

designs. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs

change coincident with each other when instructed by the count-enable (ENP, ENT) inputs and internal gating.

This mode of operation eliminates the output counting spikes normally associated with synchronous

(ripple-clock) counters. A buffered clock (CLK) input triggers the four flip-flops on the rising (positive-going) edge

of the clock waveform.

The counters are fully programmable; that is, they can be preset to any number between 0 and 9 or 15.

Presetting is synchronous; therefore, setting up a low level at the load input disables the counter and causes

the outputs to agree with the setup data after the next clock pulse, regardless of the levels of the enable inputs.

The clear function is synchronous. A low level at the clear (CLR) input sets all four of the flip-flop outputs low

after the next low-to-high transition of CLK, regardless of the levels of the enable inputs. This synchronous clear

allows the count length to be modified easily by decoding the Q outputs for the maximum count desired. The

active-low output of the gate used for decoding is connected to CLR to synchronously clear the counter to 0000

(LLLL).

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without

additional gating. ENP, ENT, and a ripple-carry output (RCO) are instrumental in accomplishing this function.

Both ENP and ENT must be high to count, and ENT is fed forward to enable RCO. Enabling RCO produces a

high-level pulse while the count is maximum (9 or 15 with Q

A

high). This high-level overflow ripple-carry pulse

can be used to enable successive cascaded stages. Transitions at ENP or ENT are allowed, regardless of the

level of CLK.

These devices feature a fully independent clock circuit. Changes at control inputs (ENP, ENT, or LOAD) that

modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of

the counter (whether enabled, disabled, loading, or counting) is dictated solely by the conditions meeting the

stable setup and hold times.

The CD54ACT163 is characterized for operation over the full military temperature range of ≠55

∞

C to 125

∞

C.

The CD74ACT163 is characterized for operation from ≠40

∞

C to 85

∞

C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

CLR

CLK

A

B

C

D

ENP

GND

V

CC

RCO

Q

A

Q

B

Q

C

Q

D

ENT

LOAD

CD54ACT163 . . . F PACKAGE

CD74ACT163 . . . E OR M PACKAGE

(TOP VIEW)

Copyright

©

2000, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

CD54ACT163, CD74ACT163

4-BIT SYNCHRONOUS BINARY COUNTERS

SCHS300 ≠ APRIL 2000

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

FUNCTION TABLE

INPUTS

OUTPUTS

FUNCTION

CLR

CLK

ENP

ENT

LOAD

A,B,C,D

Qn

RCO

FUNCTION

L

X

X

X

X

L

L

Reset (clear)

h

X

X

l

l

L

L

Parallel load

h

X

X

l

h

H

Note 1

Parallel load

h

h

h

h

X

Count

Note 1

Count

h

X

l

X

h

X

qn

Note 1

Inhibit

h

X

X

l

h

X

qn

L

Inhibit

H = high level, L = low level, X = don't care, h = high level one setup time prior to the CLK

low-to-high transition, l = low level one setup time prior to the CLK low-to-high transition, q = the

state of the referenced output prior to the CLK low-to-high transition,

= CLK low-to-high

transition.

NOTE 1: The RCO output is high when ENT is high and the counter is at terminal count (HHHH).

logic symbol

This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

14

13

12

11

CTRDIV16

LOAD

1,5D

3

A

4

B

5

C

6

D

5CT=0

1

M2

M1

9

C5/2,3,4+

G3

10

ENT

RCO

15

3CT=15

QA

QB

QC

QD

G4

7

ENP

2

CLK

CLR

[1]

[2]

[4]

[8]

CD54ACT163, CD74ACT163

4-BIT SYNCHRONOUS BINARY COUNTERS

SCHS300 ≠ APRIL 2000

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

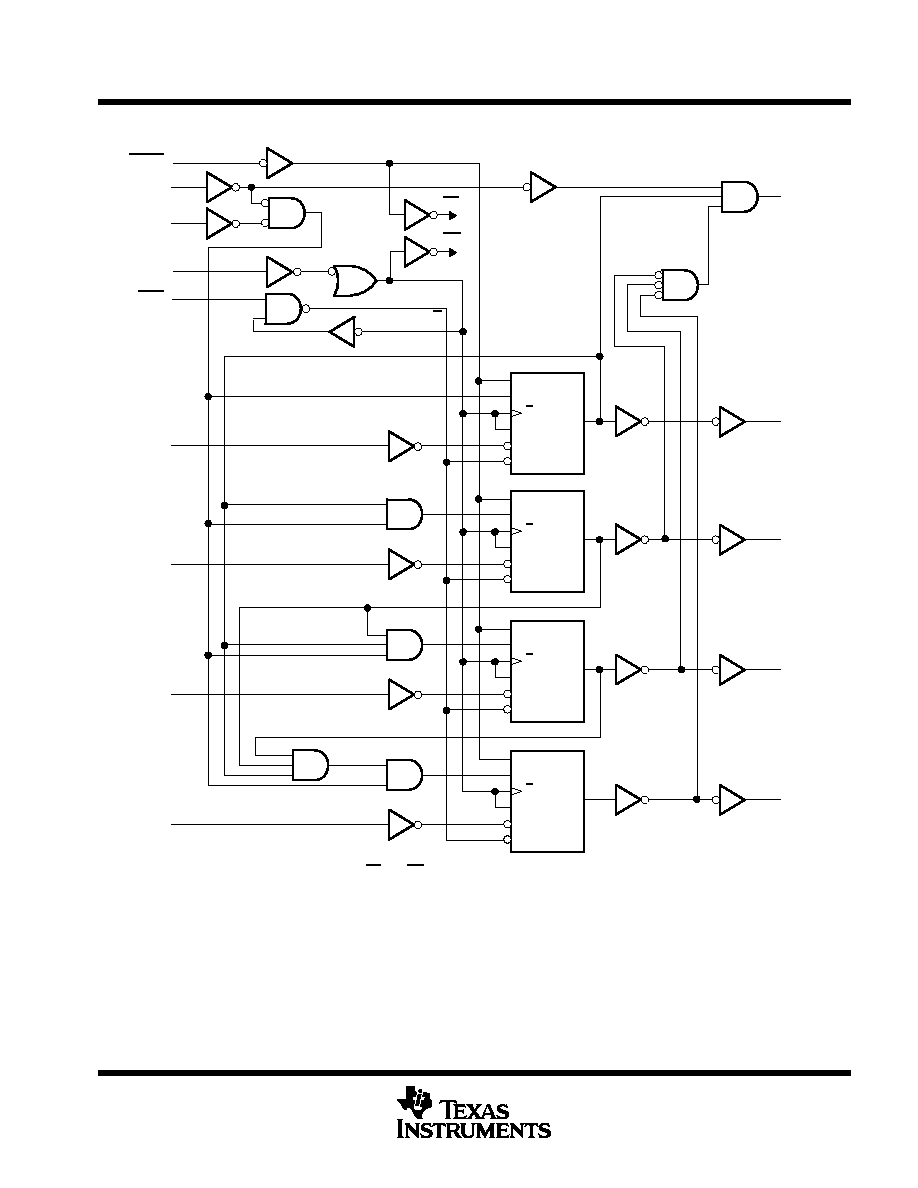

logic symbol, each D/T flip-flop

M1

LD (Load)

Q (Output)

G2

TE (Toggle Enable)

CK (Clock)

G4

3D

4R

1, 2T/1C3

D (Inverted Data)

R (Inverted Reset)

logic diagram, each D/T flip-flop (positive logic)

TG

TG

TG

TG

TG

TG

CK

LD

TE

LD

LD

D

R

CK

CK

CK

CK

Q

The origins of LD and CK are shown in the logic diagram of the overall device.

CD54ACT163, CD74ACT163

4-BIT SYNCHRONOUS BINARY COUNTERS

SCHS300 ≠ APRIL 2000

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

typical clear, preset, count, and inhibit sequence

The following sequence is illustrated below:

1.

Clear outputs to zero (synchronous)

2.

Preset to binary 12

3.

Count to 13, 14, 15, 0, 1, and 2

4.

Inhibit

Data

Inputs

Data

Outputs

CLR

LOAD

A

B

C

D

CLK

ENP

ENT

RCO

QA

QB

QC

QD

Sync

Clear

Preset

Count

Inhibit

12

13

14

15

0

1

2