| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DSD1791DB | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DSD1791

SLES072A - MARCH 2003 - REVISED JANUARY 2004

24 BIT, 192 kHz SAMPLING, ADVANCED SEGMENT,

AUDIO STEREO DIGITAL TO ANALOG CONVERTER

FEATURES

D

Supports both DSD and PCM Formats

D

24-Bit Resolution

D

Analog Performance:

- Dynamic Range: 113 dB

- THD+N: 0.001%

- Full-Scale Output: 2.1 V RMS (at Postamp)

D

Differential Voltage Output: 3.2 Vp-p

D

8

◊

Oversampling Digital Filter:

- Stop-Band Attenuation: ≠82 dB

- Pass-Band Ripple:

±

0.002 dB

D

Sampling Frequency: 10 kHz to 200 kHz

D

System Clock: 128, 192, 256, 384, 512, or

768 f

S

With Autodetect

D

Accepts 16-, 20-, and 24-Bit PCM Audio Data

D

PCM Data Formats: Standard, I

2

S, and

Left-Justified

D

DSD Format Interface Available

D

Optional Interface to External Digital Filter or

DSP Available

D

TDMCA Interface Available

D

User-Programmable Mode Controls:

- Digital Attenuation: 0 dB to ≠120 dB,

0.5 dB/Step

- Digital De-Emphasis

- Digital Filter Rolloff: Sharp or Slow

- Soft Mute

- Zero Flag for Each Output/PCM and DSD

Formats

D

Dual Supply Operation:

- 5-V Analog, 3.3-V Digital

D

5-V Tolerant Digital Inputs

D

Small 28-Lead SSOP Package, Lead-Free

Product

APPLICATIONS

D

A/V Receivers

D

SACD Players

D

DVD Players

D

HDTV Receivers

D

Car Audio Systems

D

Digital Multitrack Recorders

D

Other Applications Requiring 24-Bit Audio

DESCRIPTION

The DSD1791 is a monolithic CMOS integrated circuit that

includes stereo digital-to-analog converters and support

circuitry in a small 28-lead SSOP package. The data

converters use TI's advanced segment DAC architecture

to achieve excellent dynamic performance and improved

tolerance to clock jitter. The DSD1791 provides balanced

voltage outputs, allowing the user to optimize analog

performance externally. The DSD1791 accepts PCM and

DSD audio data formats, providing easy interfacing to

audio DSP and decoder chips. The DSD1791 also accepts

interface to external digital filter devices (DF1704,

DF1706, PMD200). Sampling rates up to 200 kHz are

supported. A full set of user-programmable functions is

accessible through an SPI control port, which supports

register write and readback functions. The DSD1791 also

supports the time-division-multiplexed command and

audio (TDMCA) data format.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate

precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to

damage because very small parametric changes could cause the device not to meet its published specifications.

PRODUCTION DATA information is current as of publication date. Products

conform to specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments

semiconductor products and disclaimers thereto appears at the end of this data sheet.

Burr Brown Products

from Texas Instruments

Copyright

2004, Texas Instruments Incorporated

DSD1791

SLES072A - MARCH 2003 - REVISED JANUARY 2004

www.ti.com

2

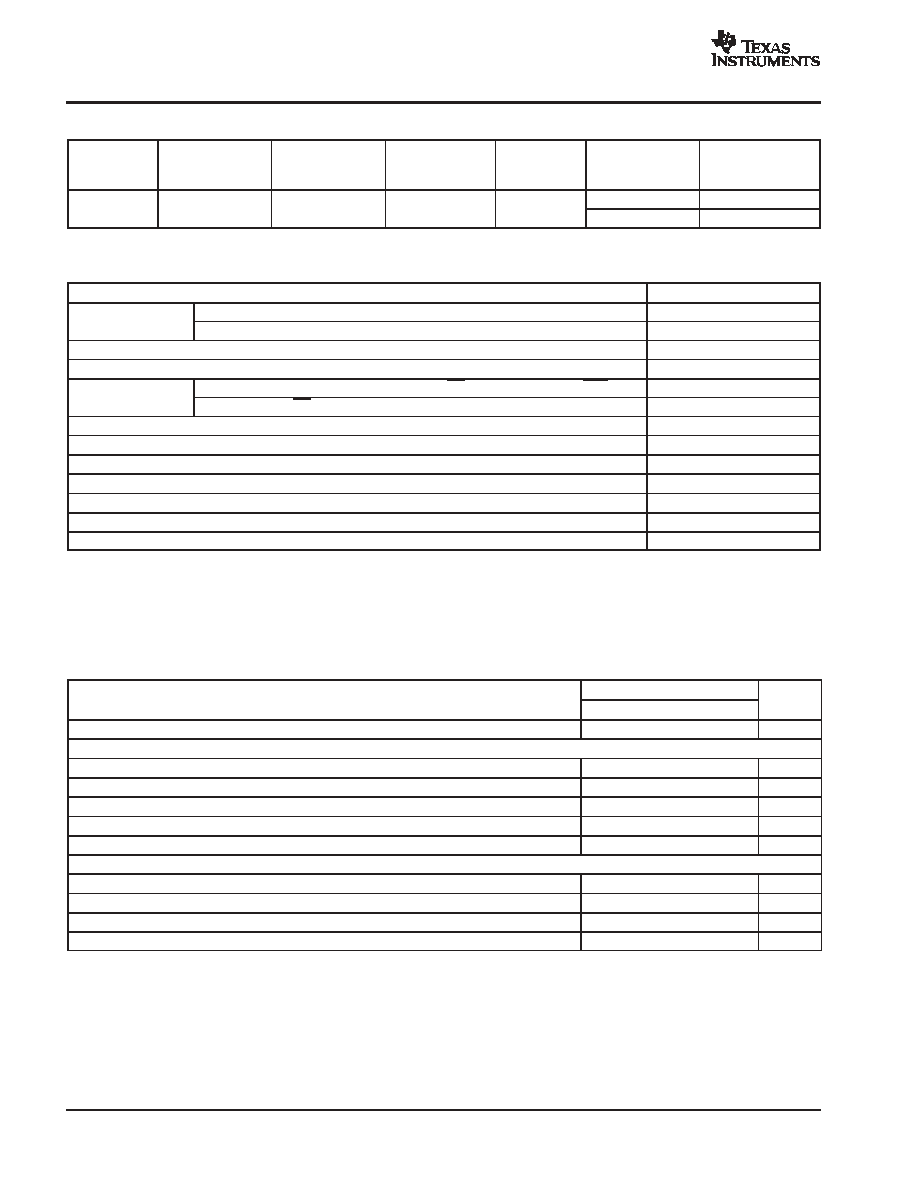

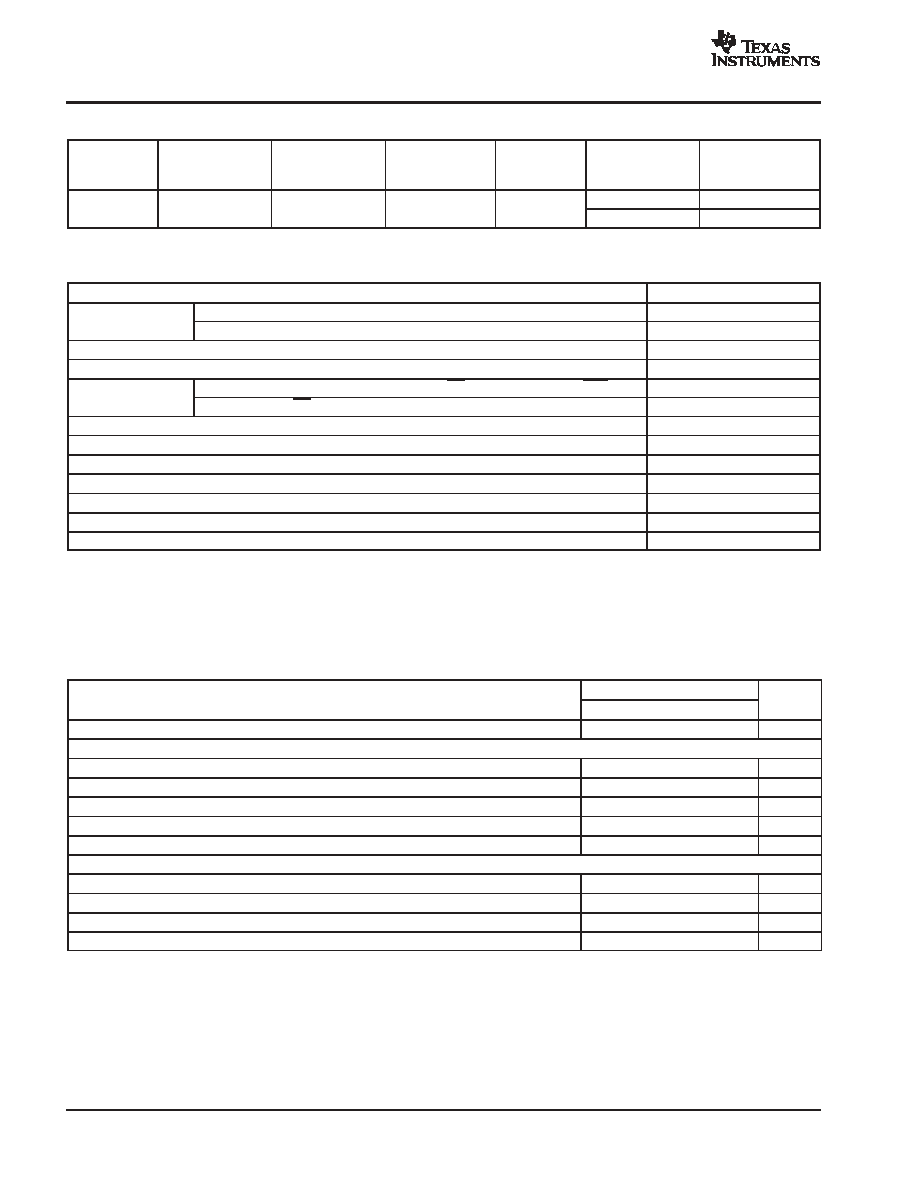

ORDERING INFORMATION

PRODUCT

PACKAGE

PACKAGE CODE

OPERATION

TEMPERATURE

RANGE

PACKAGE

MARKING

ORDERING

NUMBER

TRANSPORT

MEDIA

DSD1791DB

28-lead SSOP

28DB

-25

∞

C to 85

∞

C

DSD1791

DSD1791DB

Tube

DSD1791DB

28-lead SSOP

28DB

-25

∞

C to 85

∞

C

DSD1791

DSD1791DBR

Tape and reel

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range unless otherwise noted(1)

DSD1791

Supply voltage

VCCF, VCCL, VCCC, VCCR

-0.3 V to 6.5 V

Supply voltage

VDD

-0.3 V to 4 V

Supply voltage differences: VCCF, VCCL, VCCC, VCCR

±

0.1 V

Ground voltage differences: AGNDF, AGNDL, AGNDC, AGNDR, DGND

±

0.1 V

Digital input voltage

PLRCK, PDATA, PBCK, DSDL, DSDR, DBCK, MS(2), MDI(2), MC, SCK, RST

≠0.3 V to 6.5 V

Digital input voltage

ZEROL, ZEROR, MS(3), MDI(3)

≠0.3 V to (VDD + 0.3 V) < 4 V

Analog input voltage

≠0.3 V to (VCC + 0.3 V) < 6.5 V

Input current (any pins except supplies)

±

10 mA

Ambient temperature under bias

≠40

∞

C to 125

∞

C

Storage temperature

≠55

∞

C to 150

∞

C

Junction temperature

150

∞

C

Lead temperature (soldering)

260

∞

C, 5 s

Package temperature (IR reflow, peak)

260

∞

C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Input mode

(3) Output mode

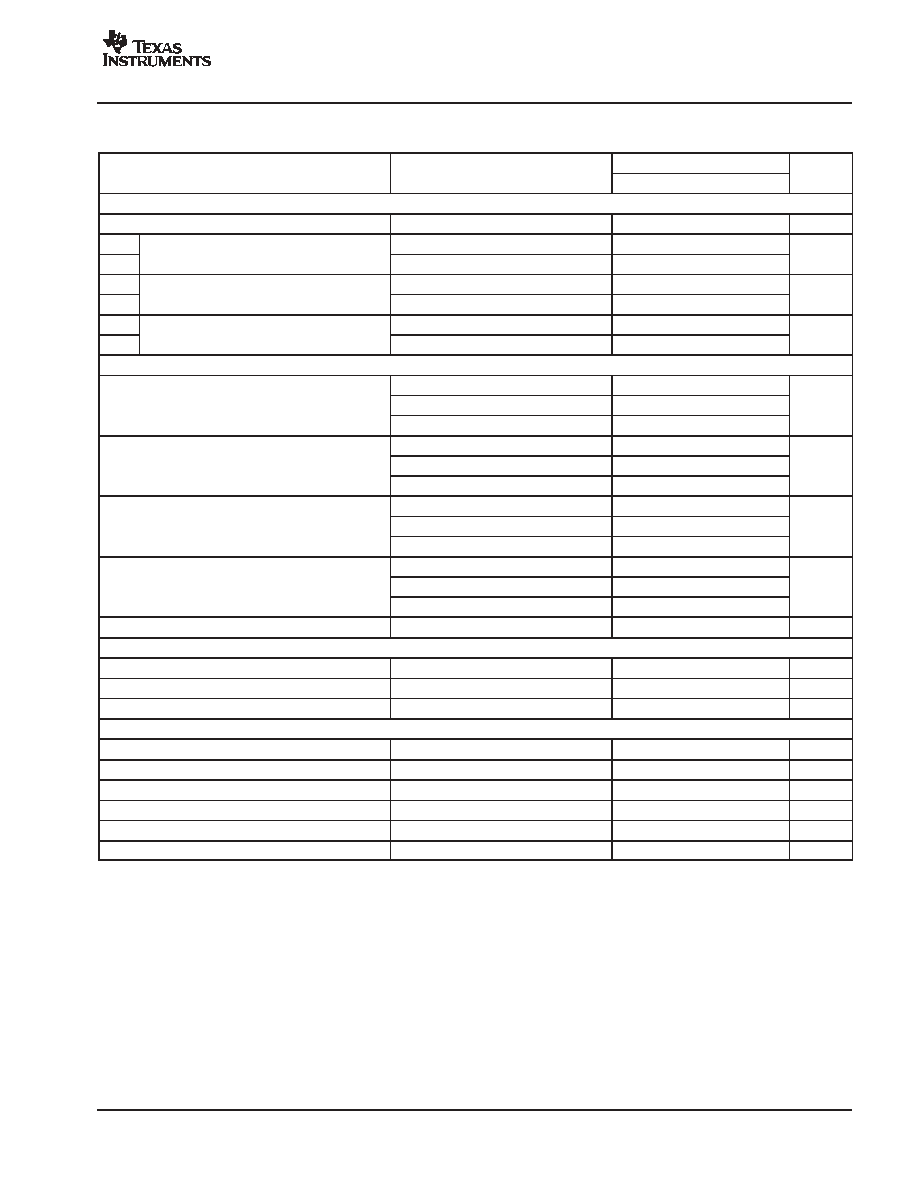

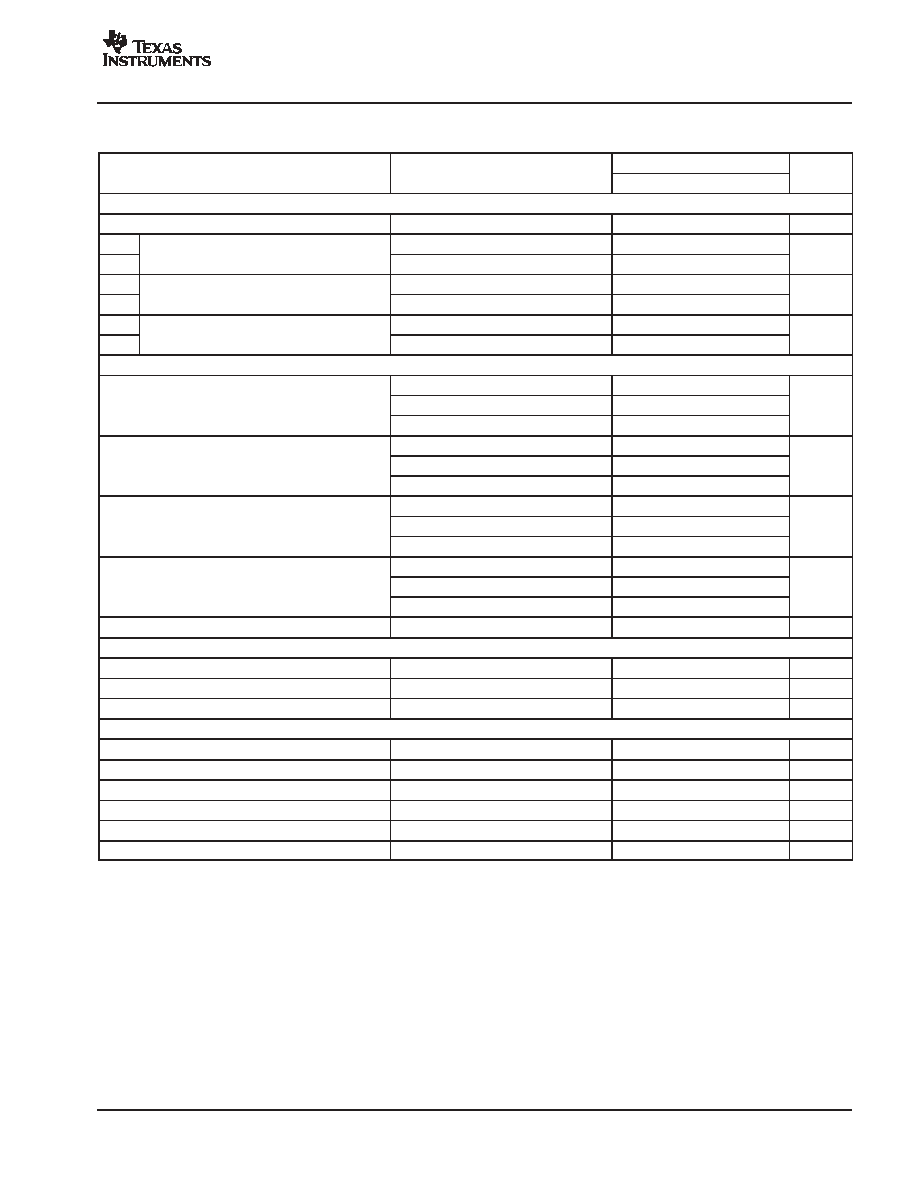

ELECTRICAL CHARACTERISTICS

all specifications at TA = 25

∞

C, VCC = 5 V, VDD = 3.3 V, fS = 44.1 kHz, system clock = 256 fS, and 24-bit data, unless otherwise noted

PARAMETER

DSD1791DB

UNIT

PARAMETER

MIN

TYP

MAX

UNIT

RESOLUTION

24

Bits

DATA FORMAT (PCM Mode)

Audio data interface format

Standard, I2S, left justified

Audio data bit length

16-, 20-, 24-bit selectable

Audio data format

MSB first, 2s complement

fS

Sampling frequency

10

200

kHz

System clock frequency

128, 192, 256, 384, 512, 768 fS

DATA FORMAT (DSD Mode)

Audio data interface format

DSD (direct stream digital)

Audio data bit length

1 Bit

fS

Sampling frequency

2.8224

MHz

System clock frequency

2.8224

11.2896

MHz

DSD1791

SLES072A - MARCH 2003 - REVISED JANUARY 2004

www.ti.com

3

ELECTRICAL CHARACTERISTICS (Continued)

all specifications at TA = 25

∞

C, VCC = 5 V, VDD = 3.3 V, fS = 44.1 kHz, system clock = 256 fS, and 24-bit data, unless otherwise noted

PARAMETER

TEST CONDITIONS

DSD1791DB

UNIT

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

DIGITAL INPUT/OUTPUT

Logic family

TTL compatible

VIH

Input logic level

2

VDC

VIL

Input logic level

0.8

VDC

IIH

Input logic current

VIN = VDD

10

A

IIL

Input logic current

VIN = 0 V

≠10

µ

A

VOH

Output logic level

IOH = ≠2 mA

2.4

VDC

VOL

Output logic level

IOL = 2 mA

0.4

VDC

DYNAMIC PERFORMANCE (PCM MODE) (1)

fS = 44.1 kHz

0.001%

0.002%

THD+N at VOUT = 0 dB

fS = 96 kHz

0.0015%

THD+N at VOUT = 0 dB

fS = 192 kHz

0.003%

EIAJ, A-weighted, fS = 44.1 kHz

110

113

Dynamic range

EIAJ, A-weighted, fS = 96 kHz

113

dB

Dynamic range

EIAJ, A-weighted, fS = 192 kHz

113

dB

EIAJ, A-weighted, fS = 44.1 kHz

110

113

Signal-to-noise ratio

EIAJ, A-weighted, fS = 96 kHz

113

dB

Signal-to-noise ratio

EIAJ, A-weighted, fS = 192 kHz

113

dB

fS = 44.1 kHz

106

110

Channel separation

fS = 96 kHz

110

dB

Channel separation

fS = 192 kHz

109

dB

Level linearity error

VOUT = ≠120 dB

±

1

dB

DYNAMIC PERFORMANCE (DSD MODE) (1) (2)

THD+N at VOUT = 0 dB

2.1 V rms

0.001%

Dynamic range

≠60 dB, EIAJ, A-weighted

113

dB

Signal-to-noise ratio

EIAJ, A-weighted

113

dB

ANALOG OUTPUT

Gain error

≠8

±

3

8

% of FSR

Gain mismatch, channel-to-channel

≠3

±

0.5

3

% of FSR

Bipolar zero error

At BPZ

≠2

±

0.5

2

% of FSR

Differential output voltage (3)

Full scale (0 dB)

3.2

V p-p

Bipolar zero voltage (3)

At BPZ

1.4

V

Load impedance (3)

R1 = R2

1.7

k

(1) Dynamic performance and dc accuracy are specified at the output of the postamplifier as shown in Figure 33. Analog performance specifications

are measured using the System Two

t

Cascade audio measurement system by Audio Precision

t

in the averaging mode. For all

sampling-frequency operations, measurement bandwidth is limited with a 20-kHz AES17 filter.

(2) Analog performance in the DSD mode is specified as the DSD modulation index of 100%. This is equivalent to PCM mode performance at 44.1 kHz

and 64 fS.

(3) These parameters are defined at the DSD1791 output pins. Load impedances, R1 and R2, are input resistors of the postamplifier. They are defined

as dc loads.

Audio Precision and System Two are trademarks of Audio Precision, Inc.

Other trademarks are the property of their respective owners.

DSD1791

SLES072A - MARCH 2003 - REVISED JANUARY 2004

www.ti.com

4

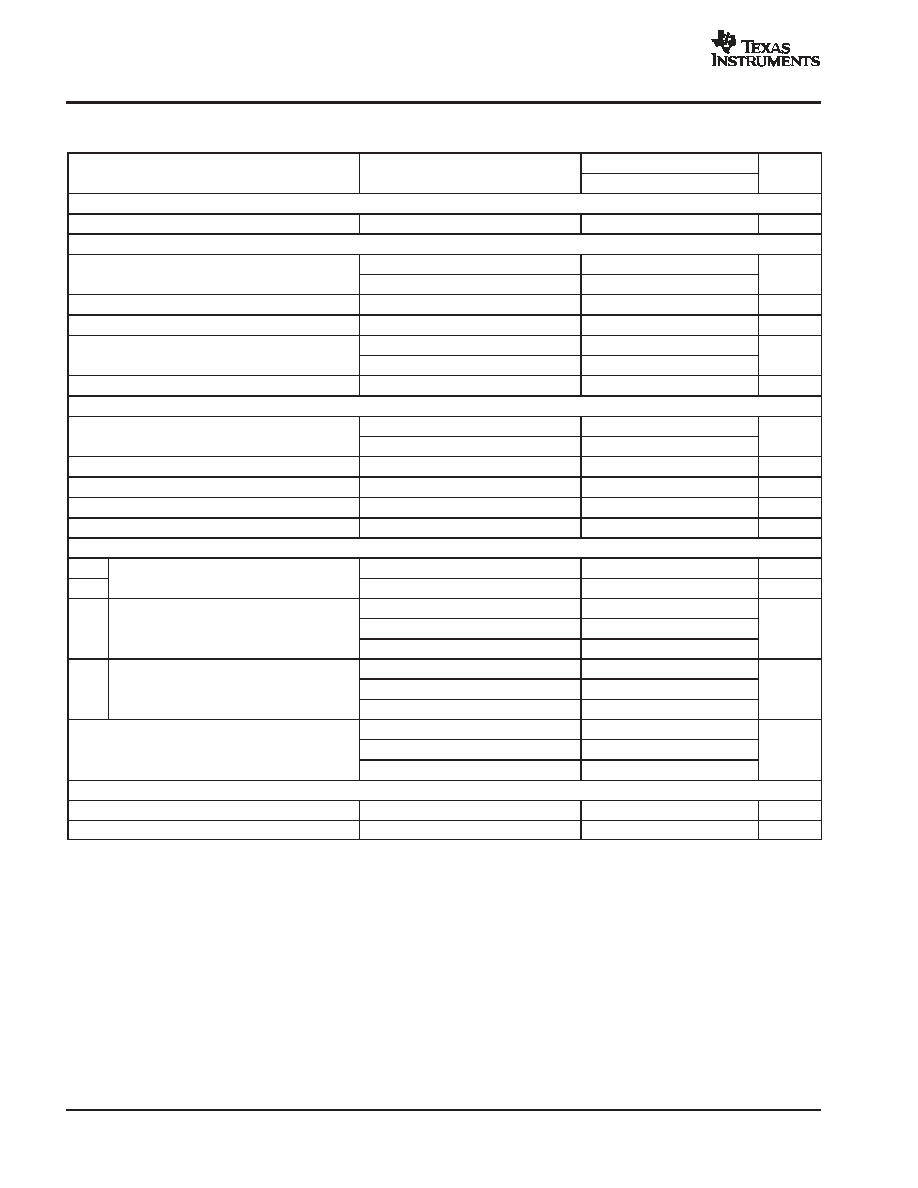

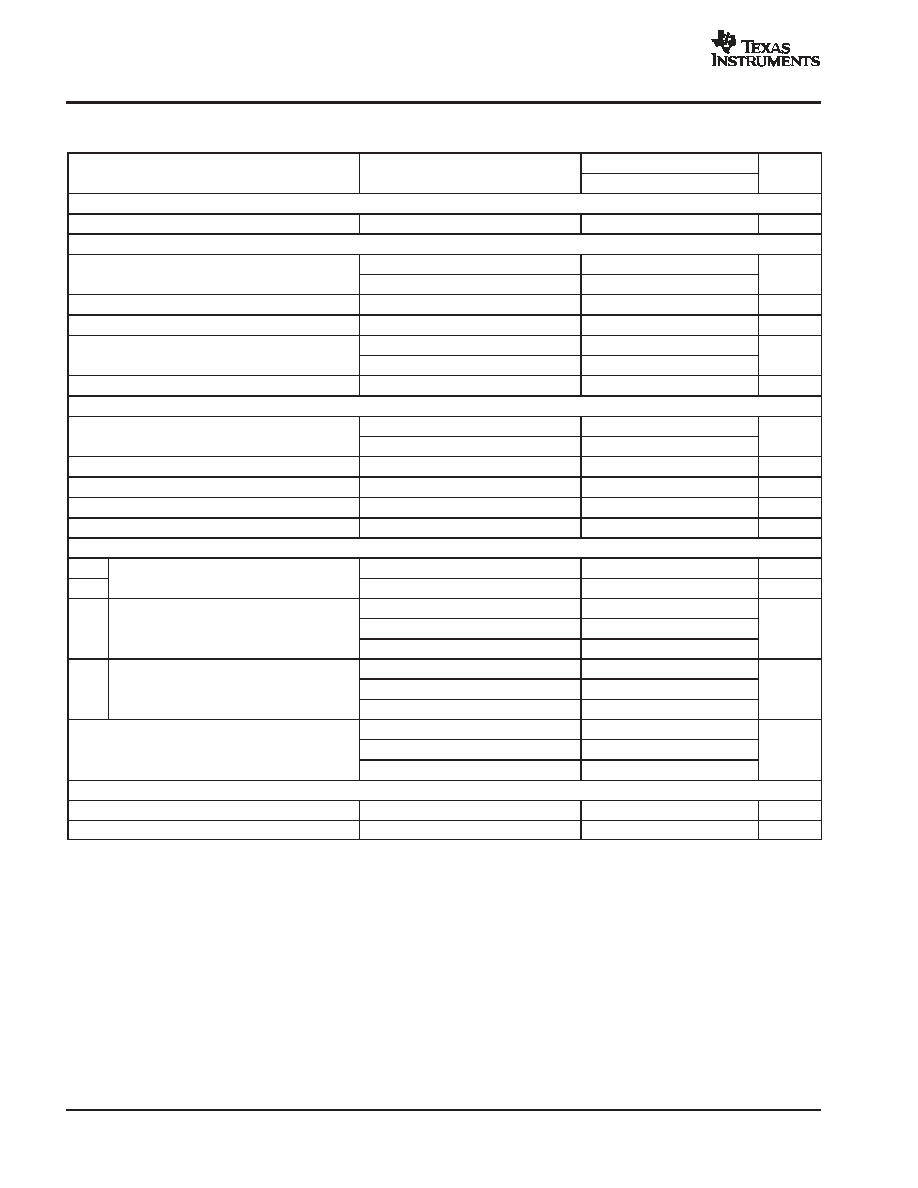

ELECTRICAL CHARACTERISTICS (Continued)

all specifications at TA = 25

∞

C, VCC = 5 V, VDD = 3.3 V, fS = 44.1 kHz, system clock = 256 fS, and 24-bit data, unless otherwise noted

PARAMETER

TEST CONDITIONS

DSD1791DB

UNIT

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

DIGITAL FILTER PERFORMANCE

De-emphasis error

±

0.1

dB

FILTER CHARACTERISTICS-1: SHARP ROLLOFF

Pass band

±

0.002 dB

0.454 fS

Pass band

≠3 dB

0.49 fS

Stop band

0.546 fS

Pass-band ripple

±

0.002

dB

Stop-band attenuation

Stop band = 0.546 fS

≠75

dB

Stop-band attenuation

Stop band = 0.567 fS

-82

dB

Delay time

29/fS

s

FILTER CHARACTERISTICS-2: SLOW ROLLOFF

Pass band

±

0.04 dB

0.274 fS

Pass band

≠3 dB

0.454 fS

Stop band

0.732 fS

Pass-band ripple

±

0.002

dB

Stop-band attenuation

Stop band = 0.732 fS

≠82

dB

Delay time

29/fS

s

POWER SUPPLY REQUIREMENTS

VDD

Voltage range

3

3.3

3.6

VDC

VCC

Voltage range

4.5

5

5.5

VDC

(1)

fS = 44.1 kHz

6.5

8

IDD

Supply current (1)

fS = 96 kHz

13.5

mA

IDD

Supply current (1)

fS = 192 kHz

28

mA

(1)

fS = 44.1 kHz

14

16

ICC

Supply current (1)

fS = 96 kHz

15

mA

ICC

Supply current (1)

fS = 192 kHz

16

mA

(1)

fS = 44.1 kHz

90

110

Power dissipation (1)

fS = 96 kHz

120

mW

Power dissipation (1)

fS = 192 kHz

170

mW

TEMPERATURE RANGE

Operation temperature

≠25

85

∞

C

JA

Thermal resistance

28-pin SSOP

100

∞

C/W

(1) Input is BPZ data.

DSD1791

SLES072A - MARCH 2003 - REVISED JANUARY 2004

www.ti.com

5

PIN ASSIGNMENTS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PLRCK

PBCK

PDATA

DBCK

SCK

RST

V

DD

DGND

AGNDF

V

CC

R

AGNDR

V

OUT

R-

V

OUT

R+

V

COM

MS

MC

MDI

DSDL

DSDR

ZEROL

ZEROR

V

CC

F

V

CC

L

AGNDL

V

OUT

L-

V

OUT

L+

AGNDC

V

CC

C

DSD1791

(TOP VIEW)