OMAP5910

Dual-Core Processor

Data Manual

Literature Number: SPRS197D

August 2002 - Revised August 2004

Literature Number: SPRS197D

August 2002 - Revised August 2004

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI's terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty. Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application

solutions:

Products

Applications

Amplifiers

amplifier.ti.com

Audio

www.ti.com/audio

Data Converters

dataconverter.ti.com

Automotive

www.ti.com/automotive

DSP

dsp.ti.com

Broadband

www.ti.com/broadband

Interface

interface.ti.com

Digital Control

www.ti.com/digitalcontrol

Logic

logic.ti.com

Military

www.ti.com/military

Power Mgmt

power.ti.com

Optical Networking

www.ti.com/opticalnetwork

Microcontrollers

microcontroller.ti.com

Security

www.ti.com/security

Telephony

www.ti.com/telephony

Video & Imaging

www.ti.com/video

Wireless

www.ti.com/wireless

Mailing Address:

Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright

2004, Texas Instruments Incorporated

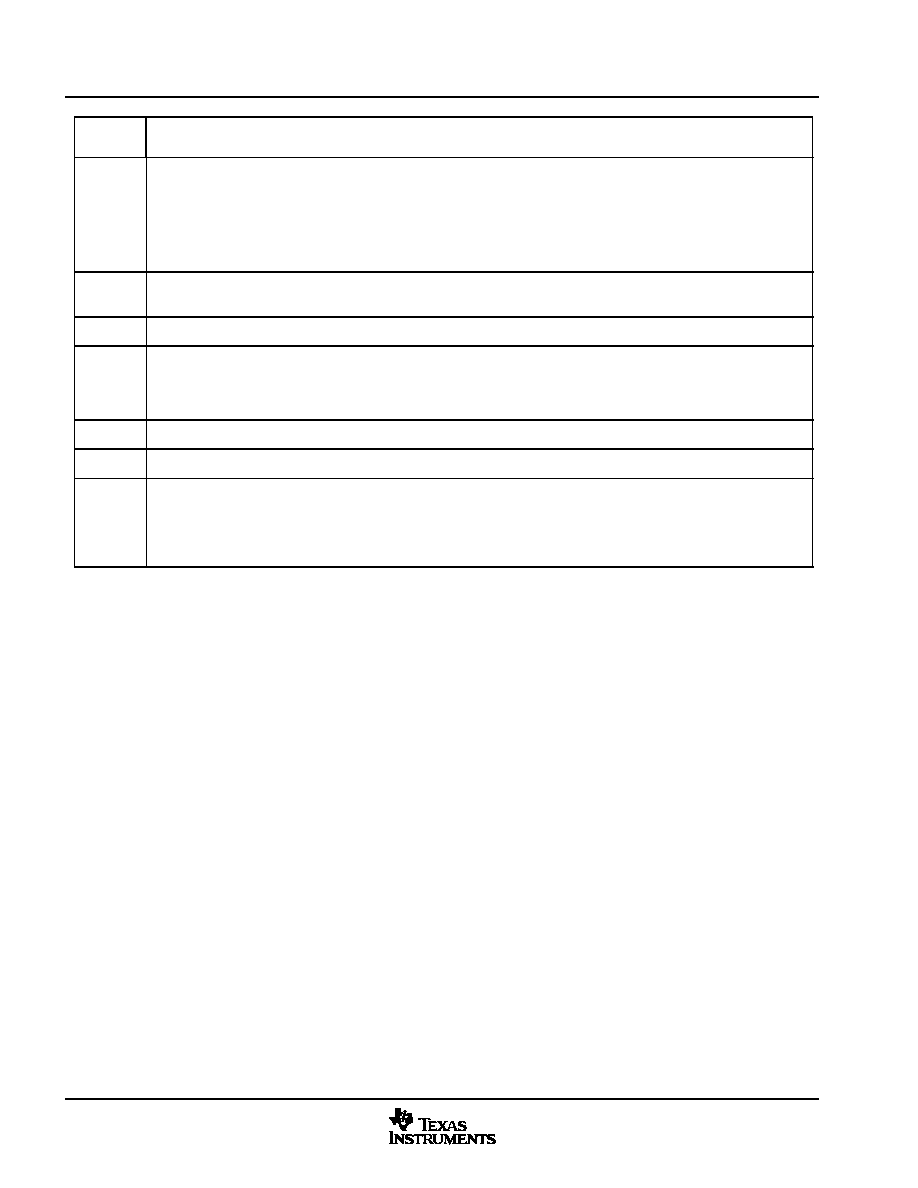

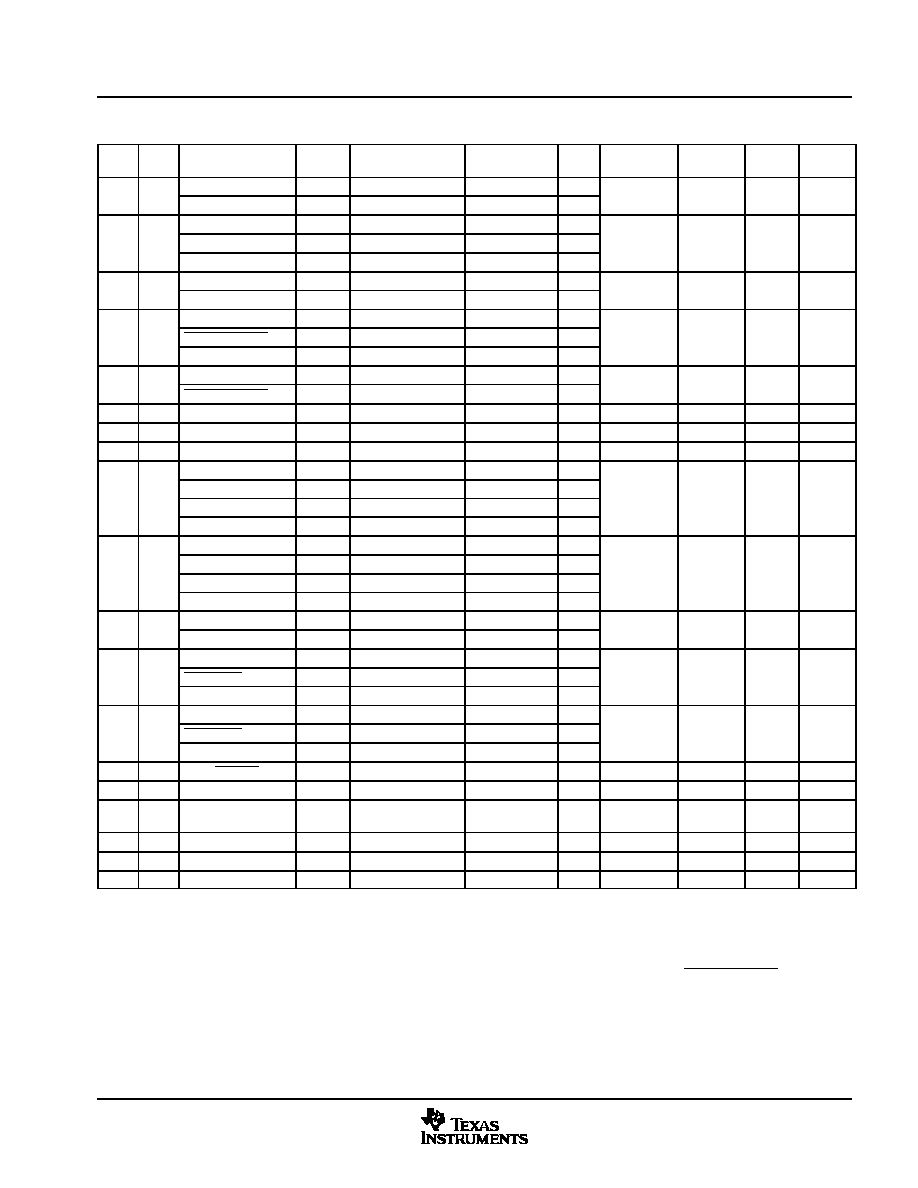

Revision History

3

August 2002 - Revised August 2004

SPRS197D

REVISION HISTORY

This data sheet revision history highlights the technical changes made to the SPRS197C device-specific data

sheet to make it an SPRS197D revision.

Scope: This document has been reviewed for technical accuracy; the technical content is up-to-date as of the

specified release date and includes the following changes.

PAGE(S)

NO.

ADDITIONS/CHANGES/DELETIONS

All

Removed all references to MMC/SD SPI mode that is no longer supported.

18 - 21

In Table 2-1:

Added footnote for GZG pin V12; "See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with

oscillator circuits."

Changed GZG pin P9 from "USB0.DP" to "USB.DP"

22 - 24

In Table 2-2:

Added footnote for GDY pin F6; "See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with

oscillator circuits."

Changed GDY pin P5 from "USB0.DP" to "USB.DP"

34 - 46

In Table 2-4:

Added A11, A13, H9, and G9 to list o f V

SS

Pins

Changed U21 to N16 in the GDY column

Changed USB1.TXEN pin in the GDY column from T6 to P14

Changed LCD.PCLK and LCD.P[15:0] description from "LCD panels" to "LCD panel"

Changed SDRAM.CLK description to include "SDRAM.CLK can also be configured as an input to monitor

skew control."

Changed STAT_VAL/WKUP description to remove "STAT_VAL/WKUP may be configured via software to function as an

external wake-up signal to the OMAP5910 device to request chip wake-up during sleep modes."

48

Changed last bullet in Section 3.1

from:

LCD controller supporting monochrome panels or STN and TFT color panels

to:

LCD controller supporting monochrome panels (STN) and color panels (STN or TFT)

54

In Section 3.3.4, changed the last sentence in the first paragraph

from: Accessing registers with the incorrect access width may result in unexpected results including a TI Peripheral

Bus (TIPB) bus error and associated TIPB interrupt.

to:

Accessing registers with the incorrect access width may cause unexpected results including a TI Peripheral Bus

(TIPB) bus error and associated TIPB interrupt.

64

Combined bullets:

�

Selectable UART/autobauding modes (autobauding on UART1 and UART2)

�

Auto bauding between 1200bits/s and 115.2K bits/s

To read as follows:

�

Selectable UART/autobauding modes (autobauding on UART1 and UART2) with autobauding between

1200 bits/s and 115.2K bits/s

66

Revised Section 3.11 to removed bulleted list and replace with the following: "The EMIFF Interface provides access to

16-bit-wide access to standard SDRAM memories and the IMIF provides access to the 192K bytes of on-chip SRAM."

Revision History

4

August 2002 - Revised August 2004

SPRS197D

PAGE(S)

NO.

ADDITIONS/CHANGES/DELETIONS

68

In Section 3.13, removed the following bulleted items:

�

Quantization /Dequantization (useful for JPEG, MPEG, H.26x Encoding/Decoding)

�

Flexible 1D/2D Wavelet Processing (useful for JPEG2000, MPEG4, and other compression standards)

�

Boundary and Perimeter Computation (useful for Machine Vision applications)

�

Image Threshold and Histogram Computations (useful for various Image Analysis applications)

72

Revised Table 3-17 to change access width from 32 bit to 16 bit. Changed MPU_READ_TIM_WD address to FFFE:C804

and changed MPU_TIMER_MODE_WD address to FFFE:C808.

120

Revised Section 4.1 and added Figure 4-1, OMAP Device Nomenclature

126

Changed Section 5.6.2, first paragraph, third line from "If the internal oscillator is not used (configured in software), an ex-

ternal clock source must be applied to the OSC1_IN pin and the OSC1_OUT pin must be left unconnected." to "If the inter-

nal oscillator is not used (configured in software using FUNC_MUX_CTRL_B register), an external clock source must be

applied to the OSC1_IN pin and the OSC1_OUT pin must be left unconnected."

130

Revised Table 5-10

131

Revised Table 5-11

141 - 142

Changed footnote of Table 5-14 from: "P = 1/(Base frequency) for McBSP1 and 3, or 1/(AMPER_CK clock frequency) in

nanoseconds (ns) for McBSP 2.Base frequency is 12 or 13MHz". to: "Regardless of whether MCBSP.CLKS is internally or

externally clocked, P = 1/(DSPXOR_CK) for McBSP1 and McBSP3, and P = 1/(AMPER_CK) for McBSP2. See the

OMAP5910 Dual-Core Processor Clock Generation and System Reset Management Reference Guide (literature number

SPRU678) for additional details."

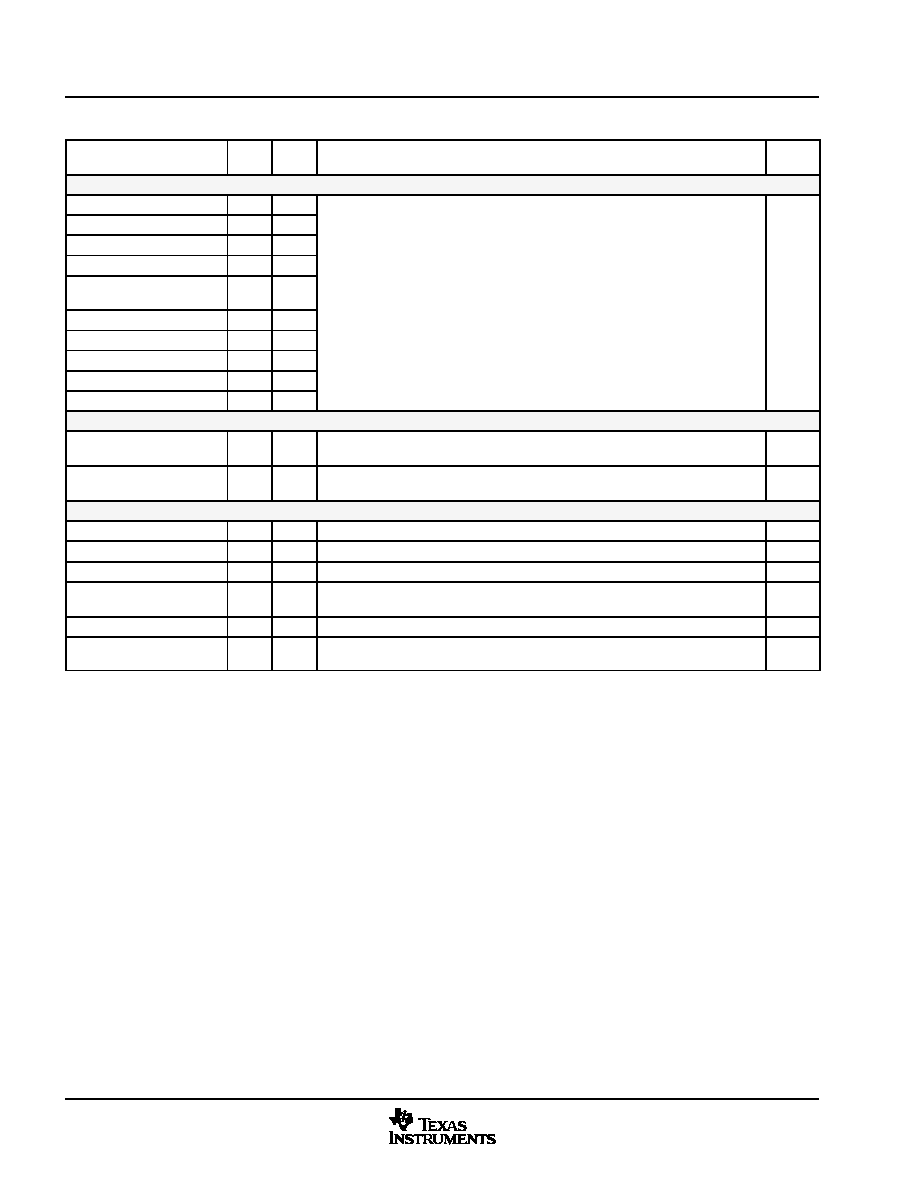

Contents

5

August 2002 - Revised August 2004

SPRS197D

Contents

Section

Page

1

OMAP5910 Features

15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2

Introduction

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1

Description

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1

TMS320C55x DSP Core

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2

TI-Enhanced TI925T RISC Processor

17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2

Terminal Assignments

18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3

Terminal Characteristics and Multiplexing

24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4

Signal Description

34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

Functional Overview

47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

Functional Block Diagram Features

48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2

MPU Memory Maps

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1

MPU Global Memory Map

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2

MPU Subsystem Registers Memory Map

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3

DSP Memory Maps

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1

DSP Global Memory Map

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2

On-Chip Dual-Access RAM (DARAM)

53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.3

On-Chip Single-Access RAM (SARAM)

53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.4

DSP I/O Space Memory Map

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4

DSP External Memory (Managed by MMU)

55

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

MPU and DSP Private Peripherals

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1

Timers

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2

32k Timer (MPU only)

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.3

Watchdog Timer

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.4

Interrupt Handlers

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.5

LCD Controller

57

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6

MPU Public Peripherals

58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.1

USB Host Controller

58

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2

USB Function Peripheral

59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3

Multichannel Buffered Serial Port (McBSP)

59

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.4

I

2

C Master/Slave Interface

60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.5

MICROWIRE Serial Interface

60

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.6

Multimedia Card/Secure Digital (MMC/SD) Interface

60

. . . . . . . . . . . . . . . . . . . . . . . . .

3.6.7

HDQ/1-Wire Interface

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.8

Camera Interface

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.9

MPUIO/Keyboard Interface

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.10

Pulse-Width Light (PWL)

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.11

Pulse-Width Tone (PWT)

61

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.12

LED Pulse Generator

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.13

Real-Time Clock

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.14

Frame Adjustment Counter

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7

DSP Public Peripherals

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1

Multichannel Buffered Serial Port (McBSP)

62

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2

Multichannel Serial Interface (MCSI)

63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

6

August 2002 - Revised August 2004

SPRS197D

Section

Page

3.8

Shared Peripherals

63

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1

Universal Asynchronous Receiver/Transmitter (UART)

63

. . . . . . . . . . . . . . . . . . . . . . .

3.8.2

General-Purpose I/O (GPIO)

64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3

Mailbox Registers

64

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9

System DMA Controller

65

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10

DSP DMA Controller

66

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.11

Traffic Controller (Memory Interfaces)

66

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12

Interprocessor Communication

67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.1

MPU/DSP Mailbox Registers

67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.2

MPU Interface (MPUI)

67

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.12.3

MPU/DSP Shared Memory

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13

DSP Hardware Accelerators

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.1

DCT/iDCT Accelerator

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.2

Motion Estimation Accelerator

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.13.3

Pixel Interpolation Accelerator

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14

Power Supply Connection Examples

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14.1

Core and I/O Voltage Supply Connections

68

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.14.2

Core Voltage Noise Isolation

70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15

MPU Register Descriptions

71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15.1

MPU Private Peripheral Registers

72

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15.2

MPU Public Peripheral Registers

79

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.15.3

MPU Configuration Registers

88

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16

DSP Register Descriptions

95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16.1

DSP Private Peripheral Registers

95

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16.2

DSP Public Peripheral Registers

101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16.3

DSP Configuration Registers

106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.16.4

MPU/DSP Shared Peripheral Register Descriptions

108

. . . . . . . . . . . . . . . . . . . . . . . . . .

3.17

Interrupts

113

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.18

MPU System DMA Request Mapping

117

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.19

DSP DMA Event Mapping

118

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

Documentation Support

119

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1

Device and Development Tool Support Nomenclature

120

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

Electrical Specifications

121

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1

Absolute Maximum Ratings

121

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2

Recommended Operating Conditions

122

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3

Electrical Characteristics Over Recommended Operating Case Temperature

Range (Unless Otherwise Noted)

123

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4

Package Thermal Resistance Characteristics

124

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5

Timing Parameter Symbology

124

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6

Clock Specifications

125

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.1

32-kHz Oscillator and Input Clock

125

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6.2

Base Oscillator (12 MHz or 13 MHz) and Input Clock

126

. . . . . . . . . . . . . . . . . . . . . . . . .

5.6.3

Internal Clock Speed Limitations

127

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7

Reset Timings

128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.1

OMAP5910 Device Reset

128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.2

OMAP5910 MPU Core Reset

129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

7

August 2002 - Revised August 2004

SPRS197D

Section

Page

5.8

External Memory Interface Timing

130

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.1

EMIFS/Flash Interface Timing

130

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8.2

EMIFF/SDRAM Interface Timing

137

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

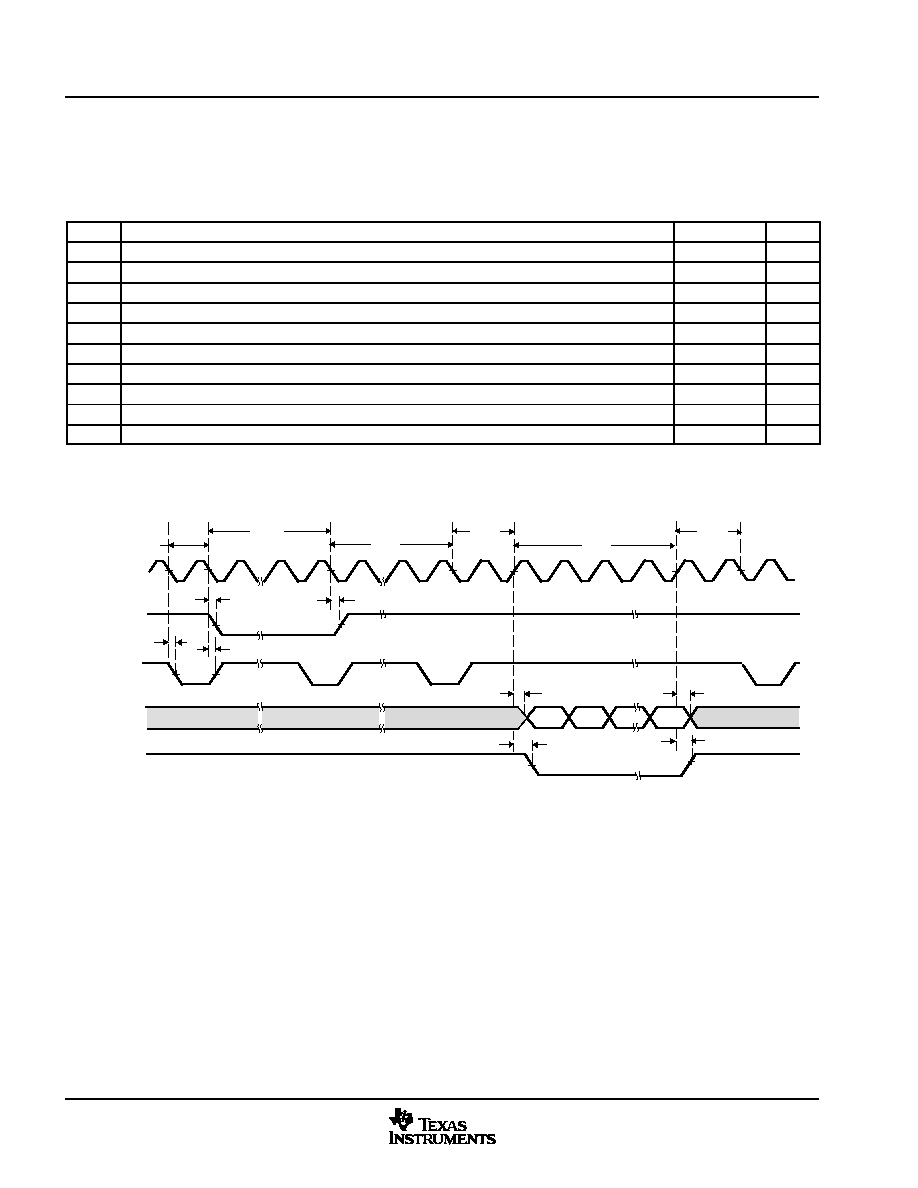

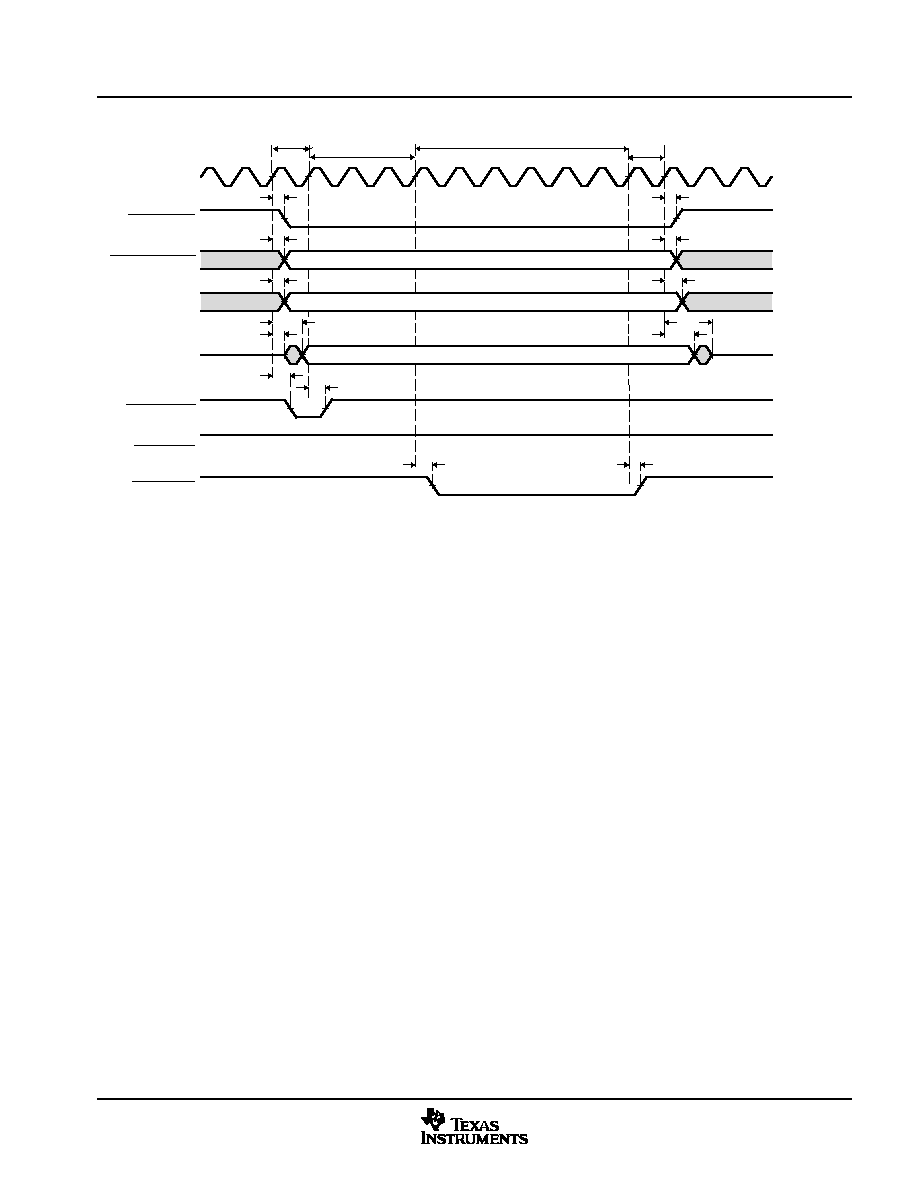

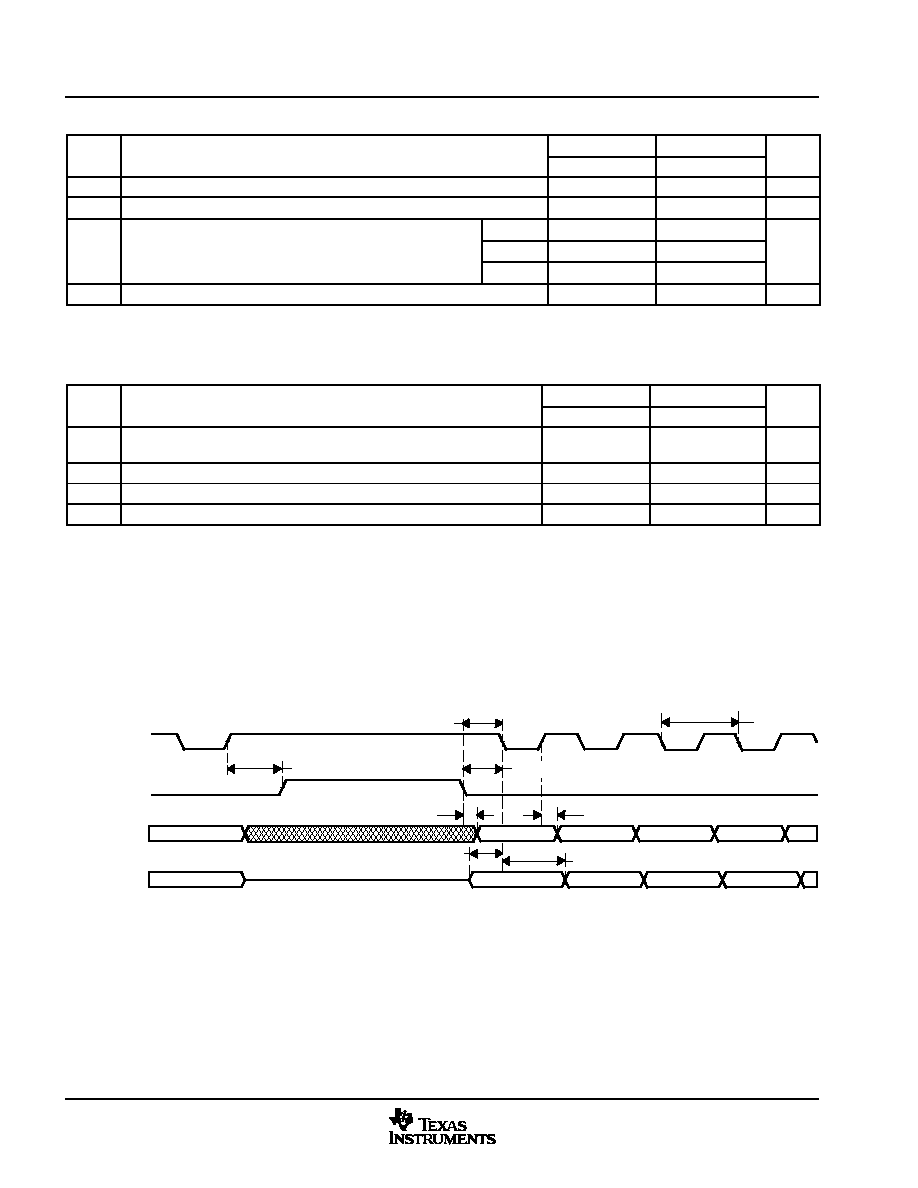

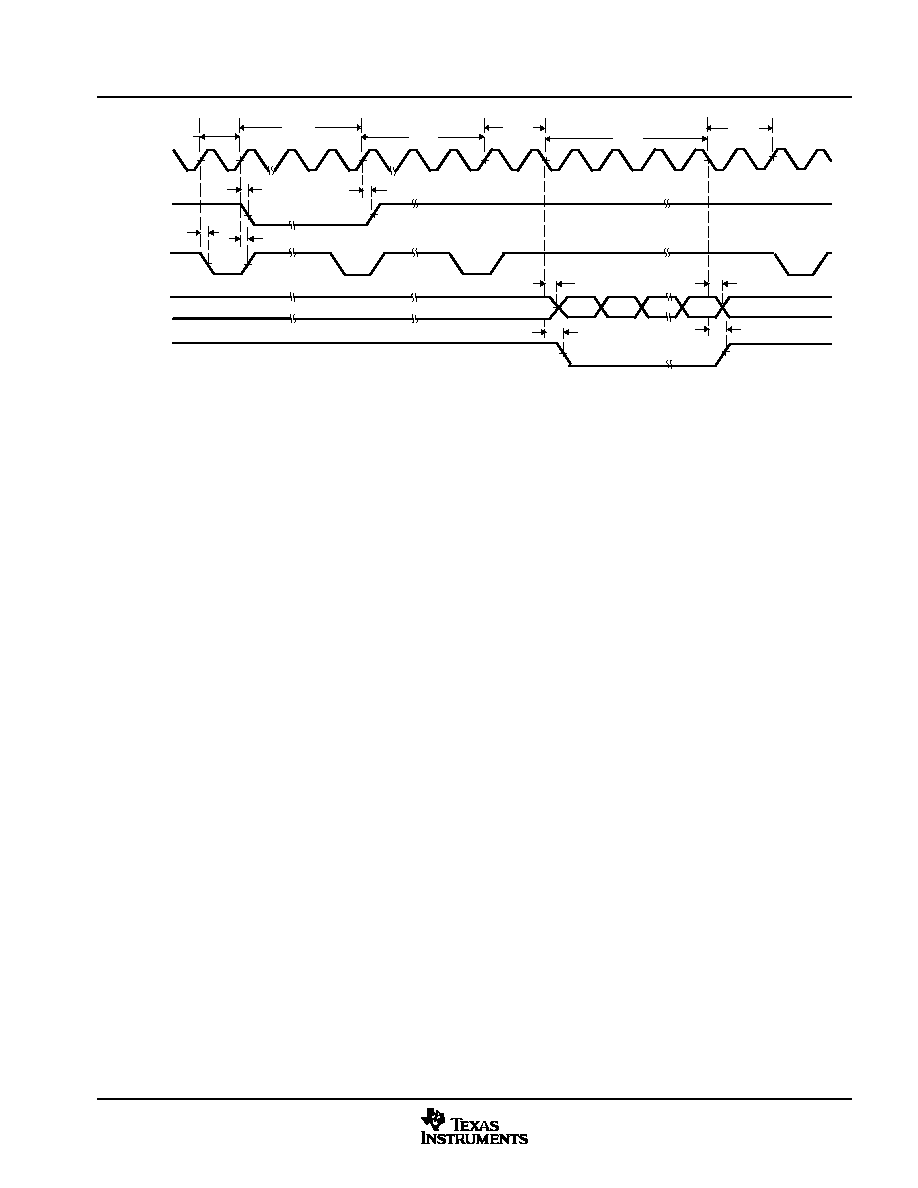

5.9

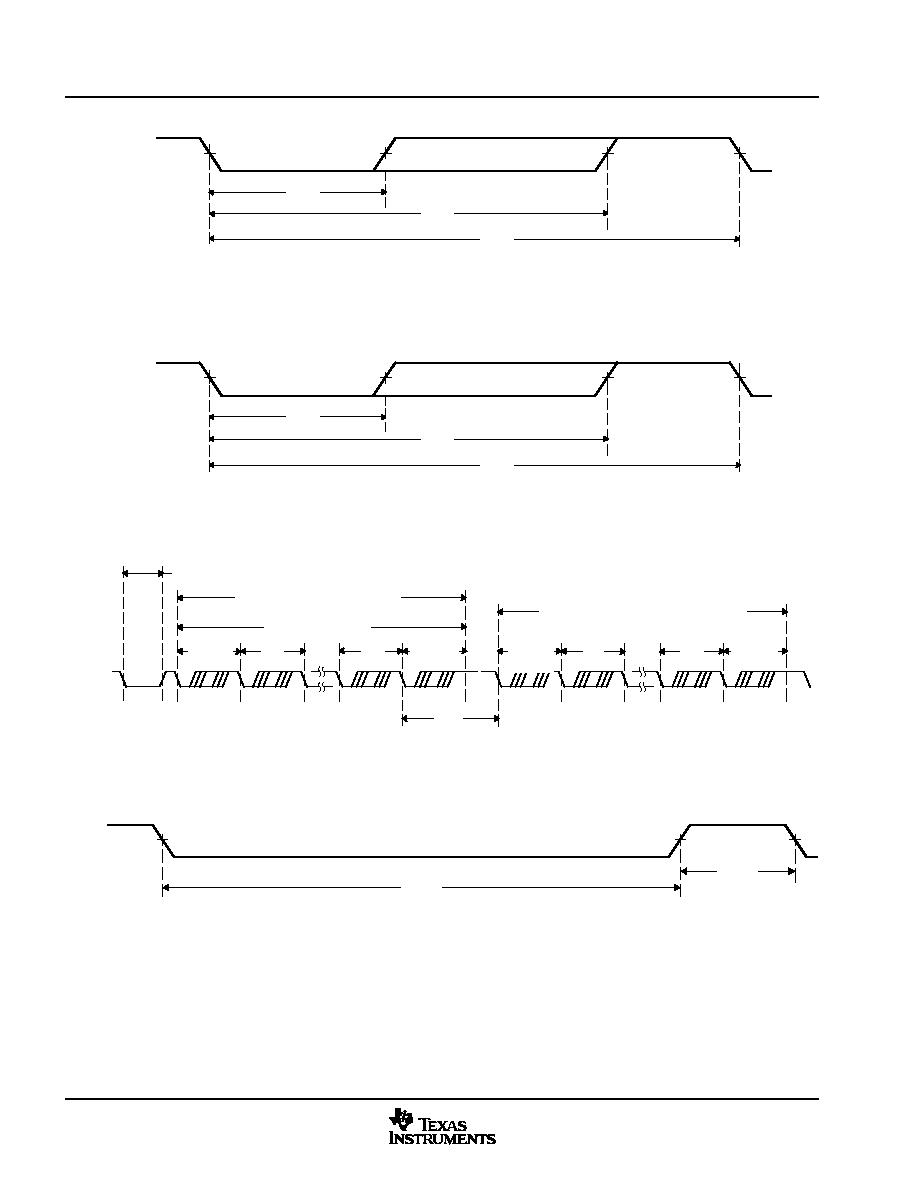

Multichannel Buffered Serial Port (McBSP) Timings

141

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

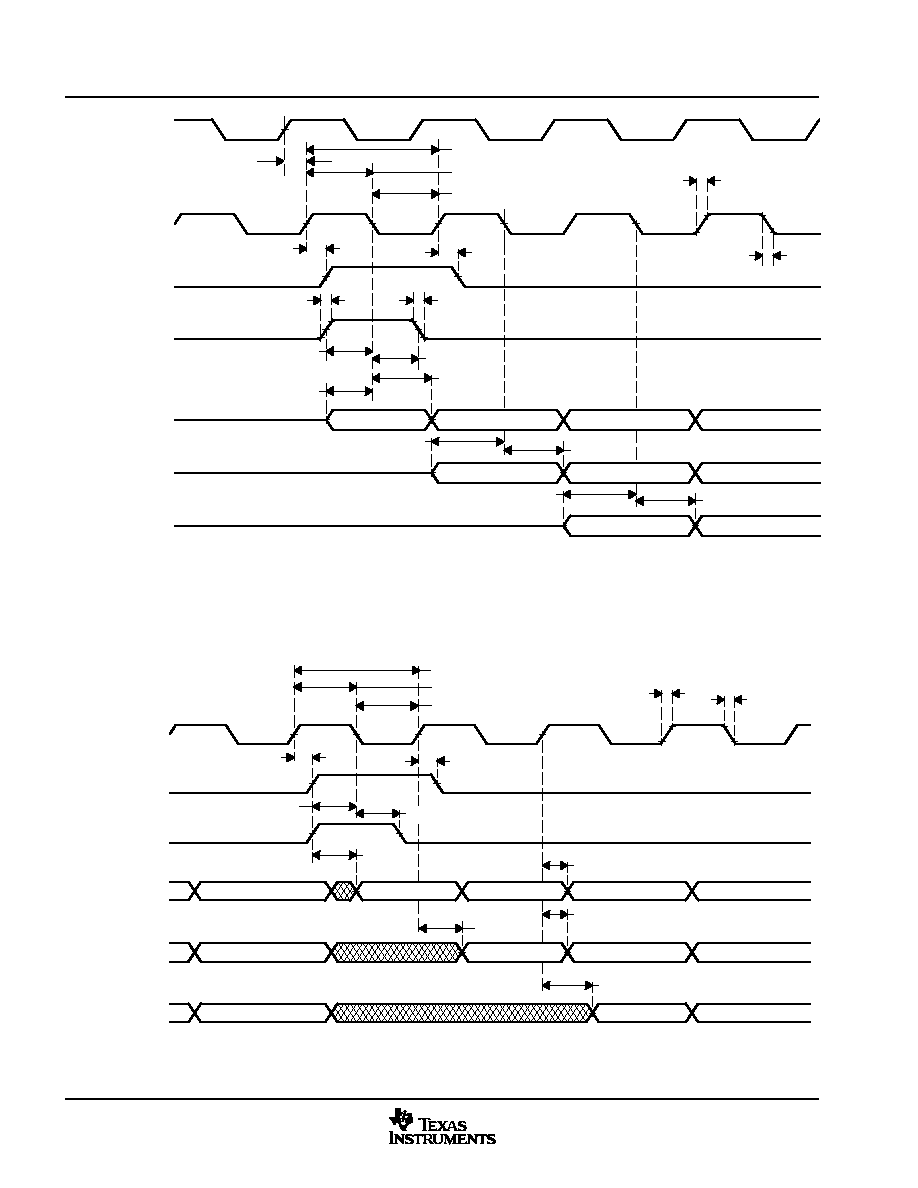

5.9.1

McBSP Transmit and Receive Timings

141

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

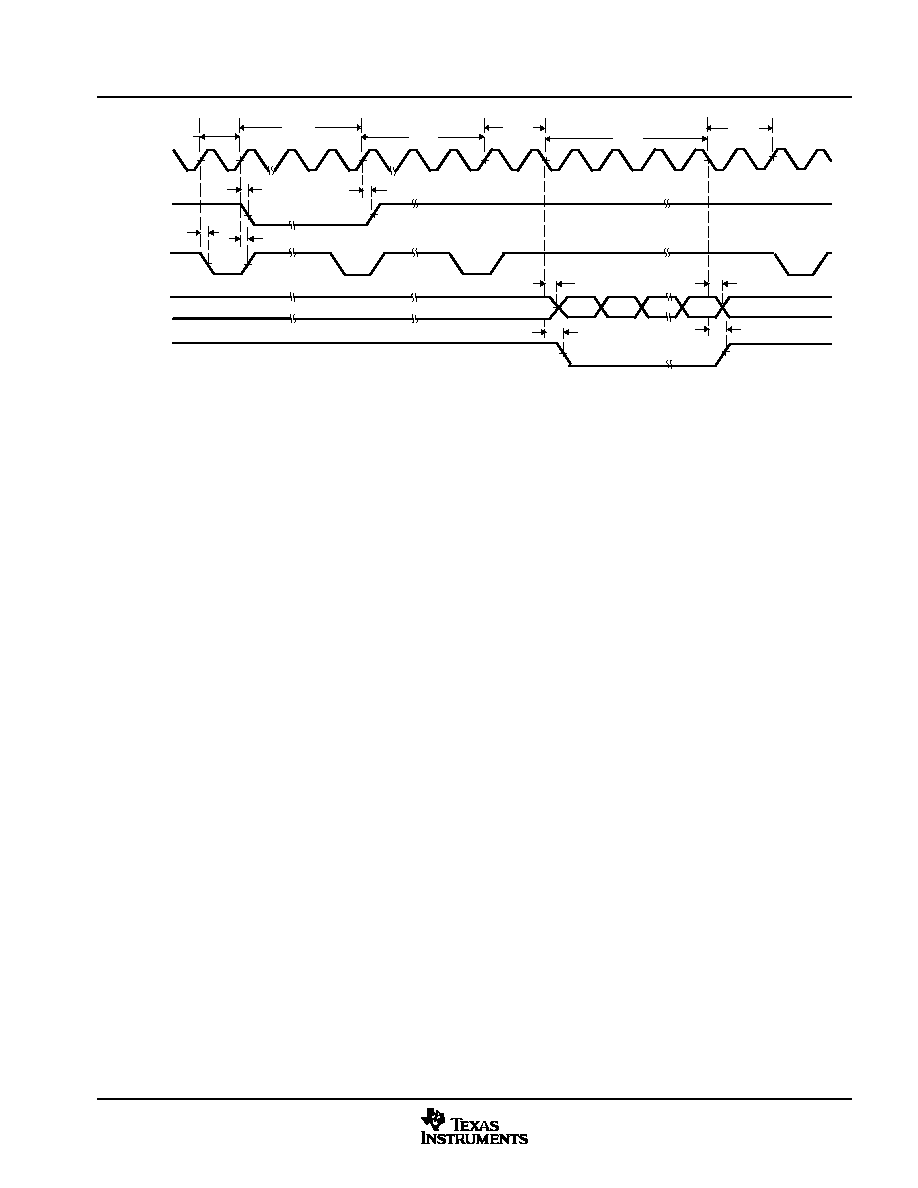

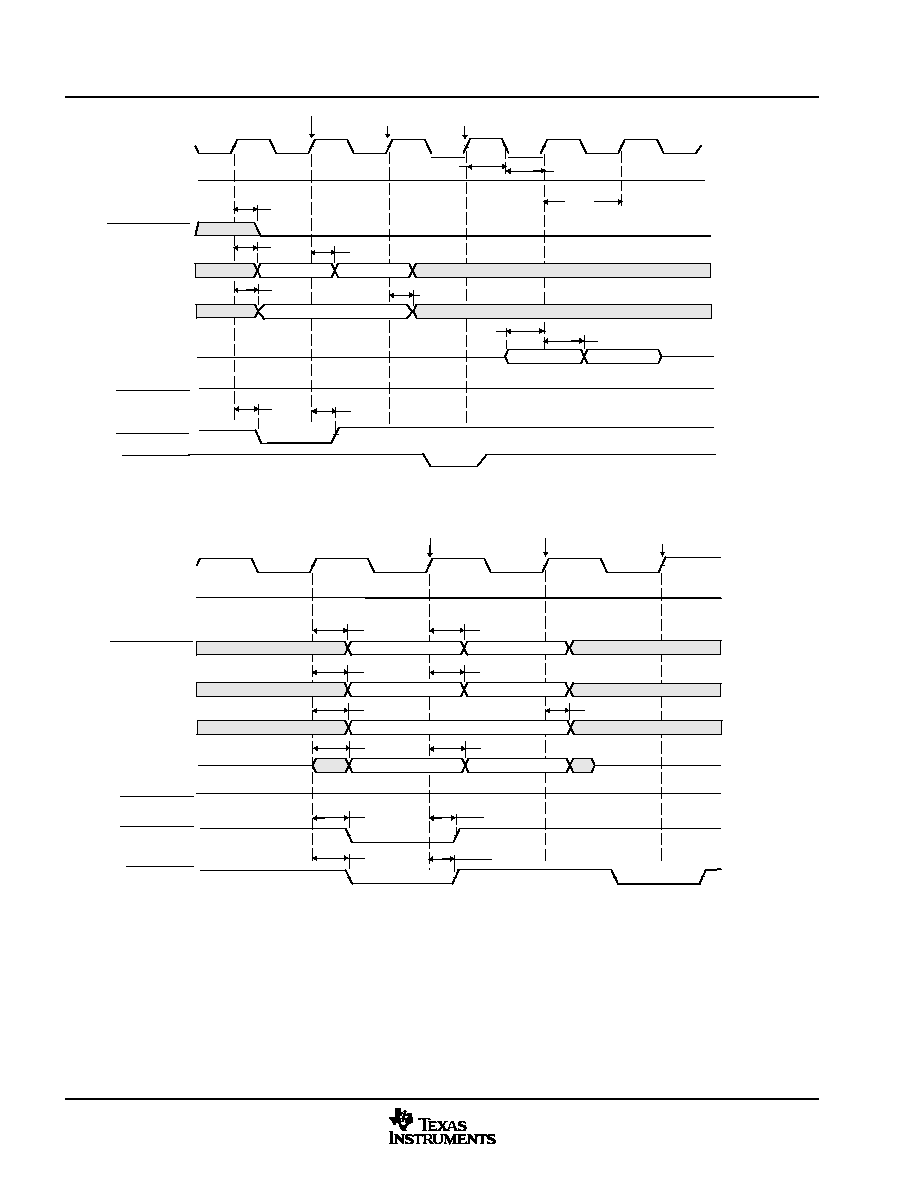

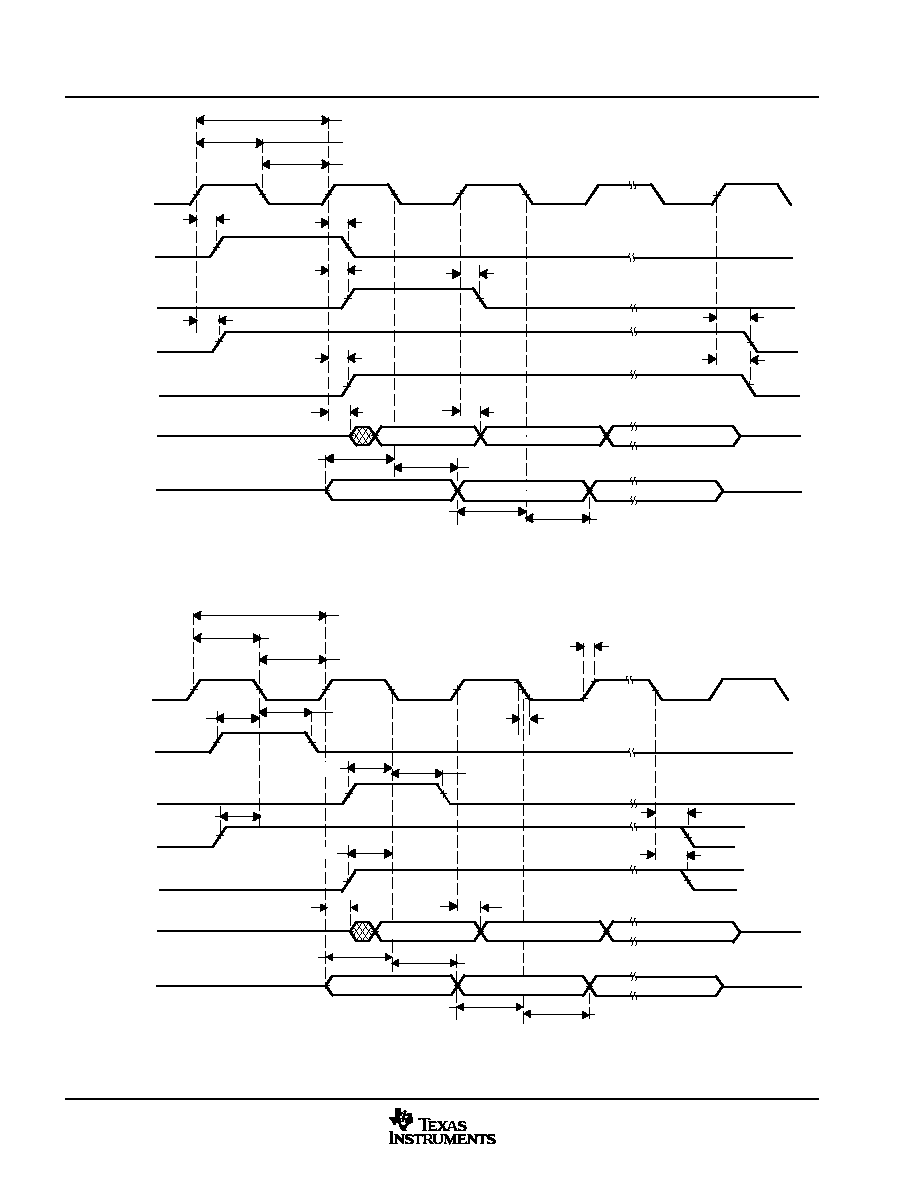

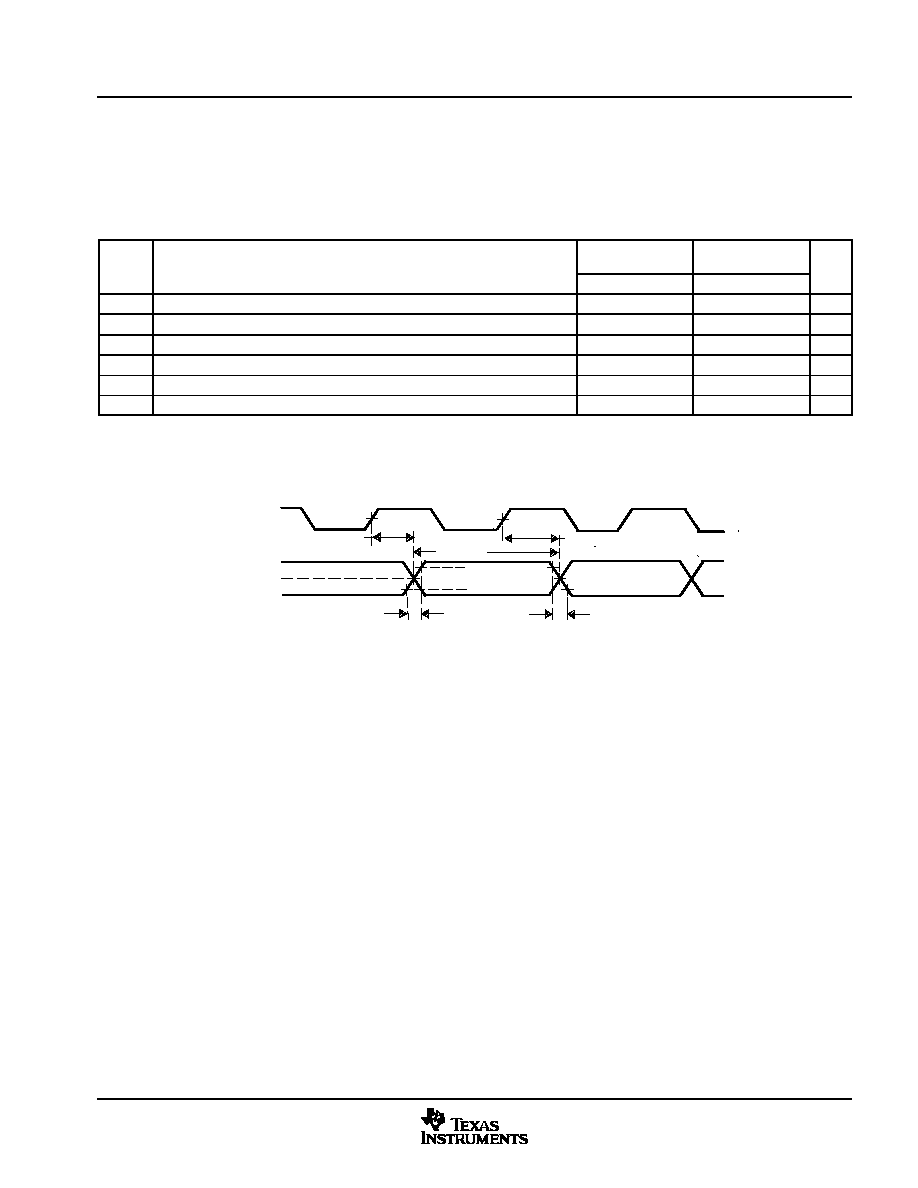

5.9.2

McBSP as SPI Master or Slave Timing

145

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

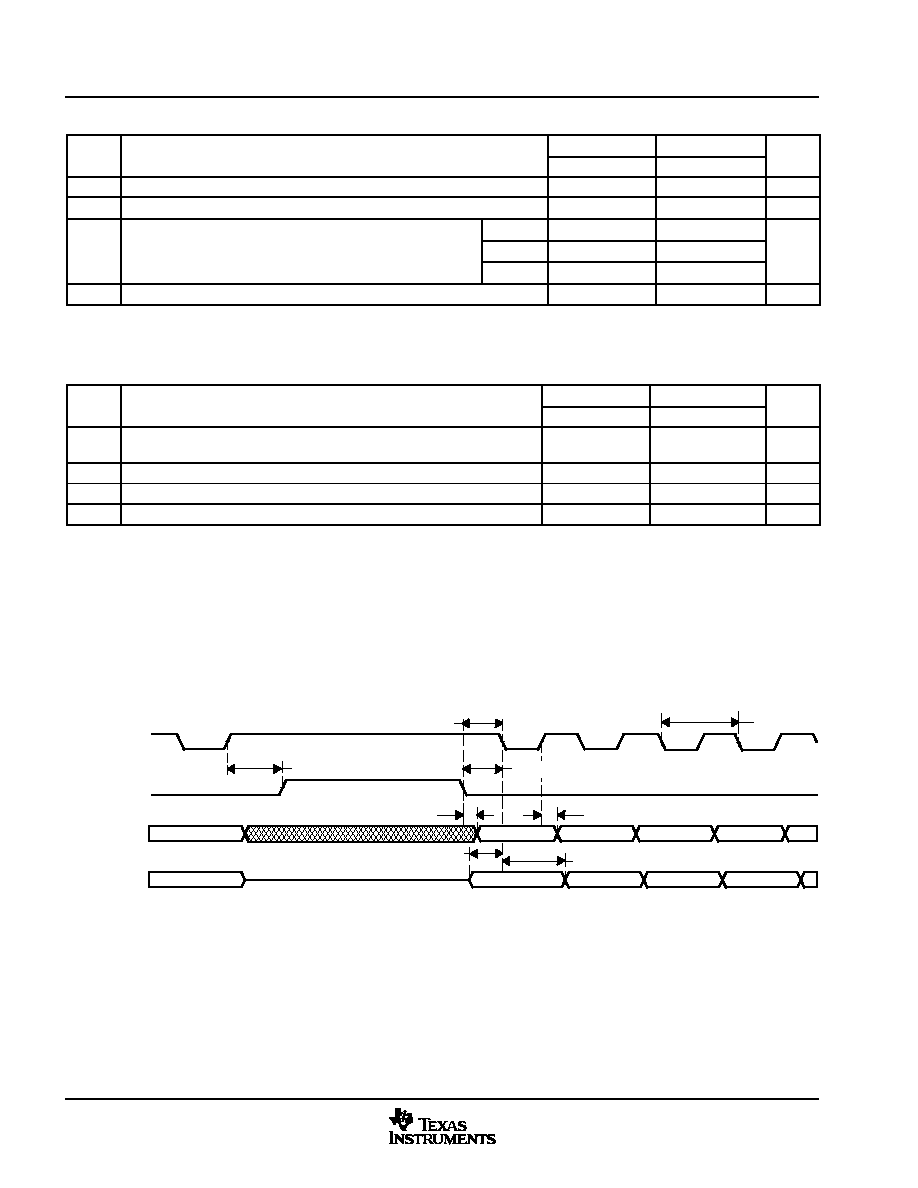

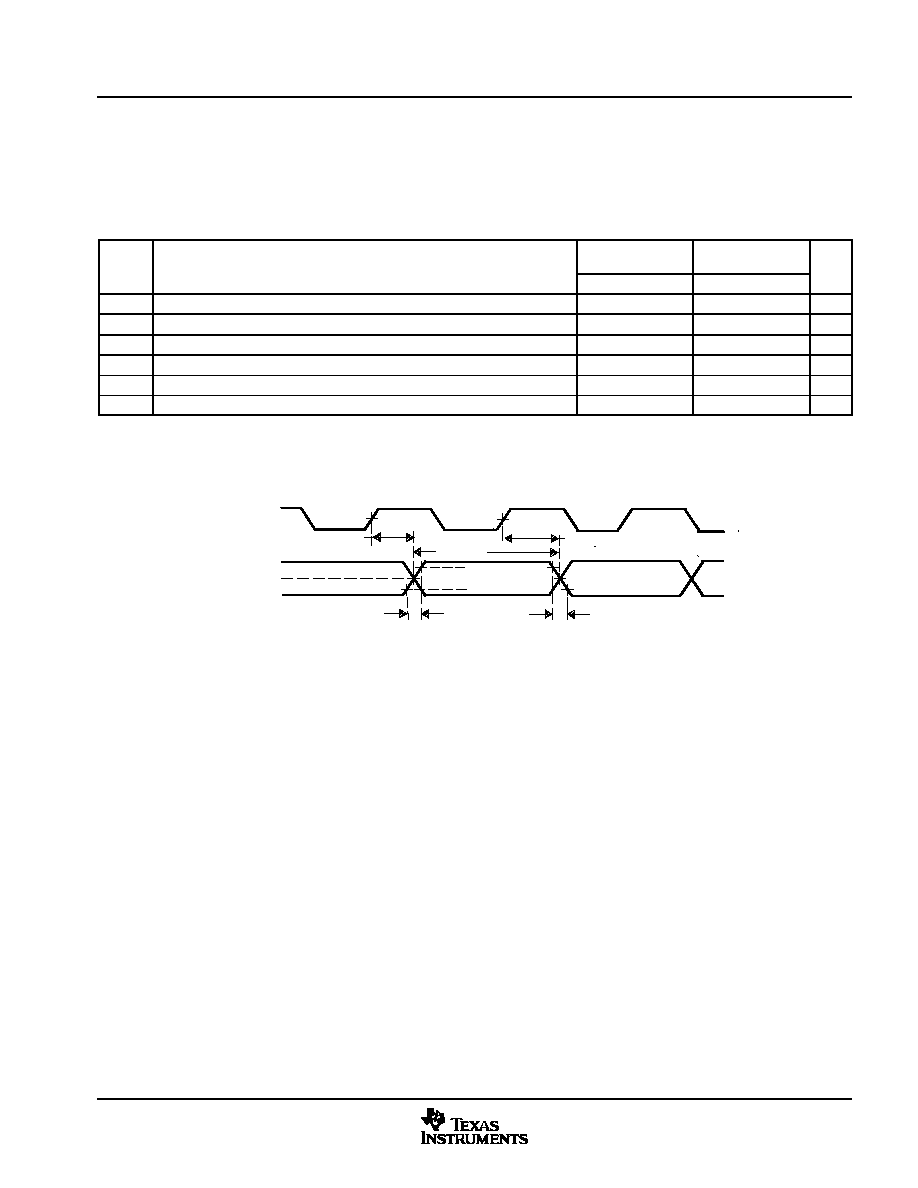

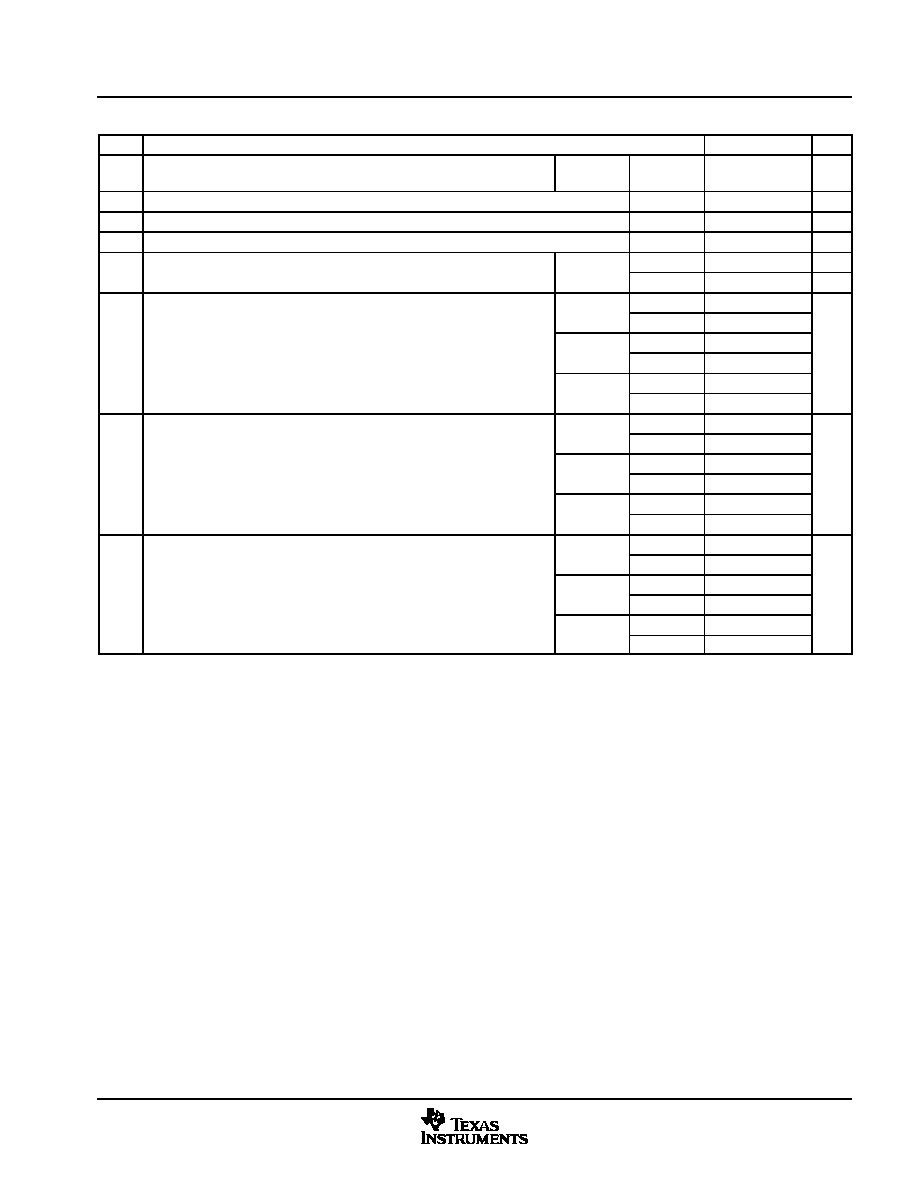

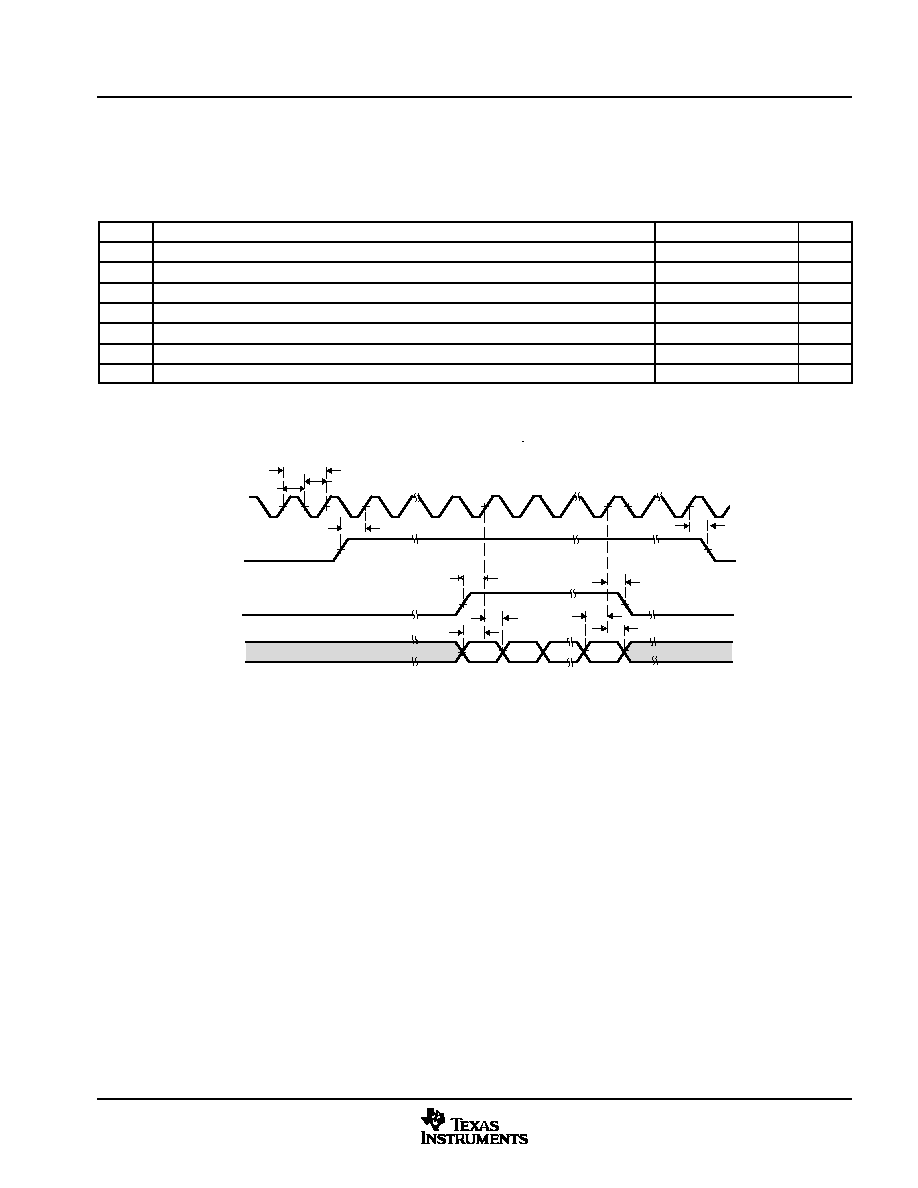

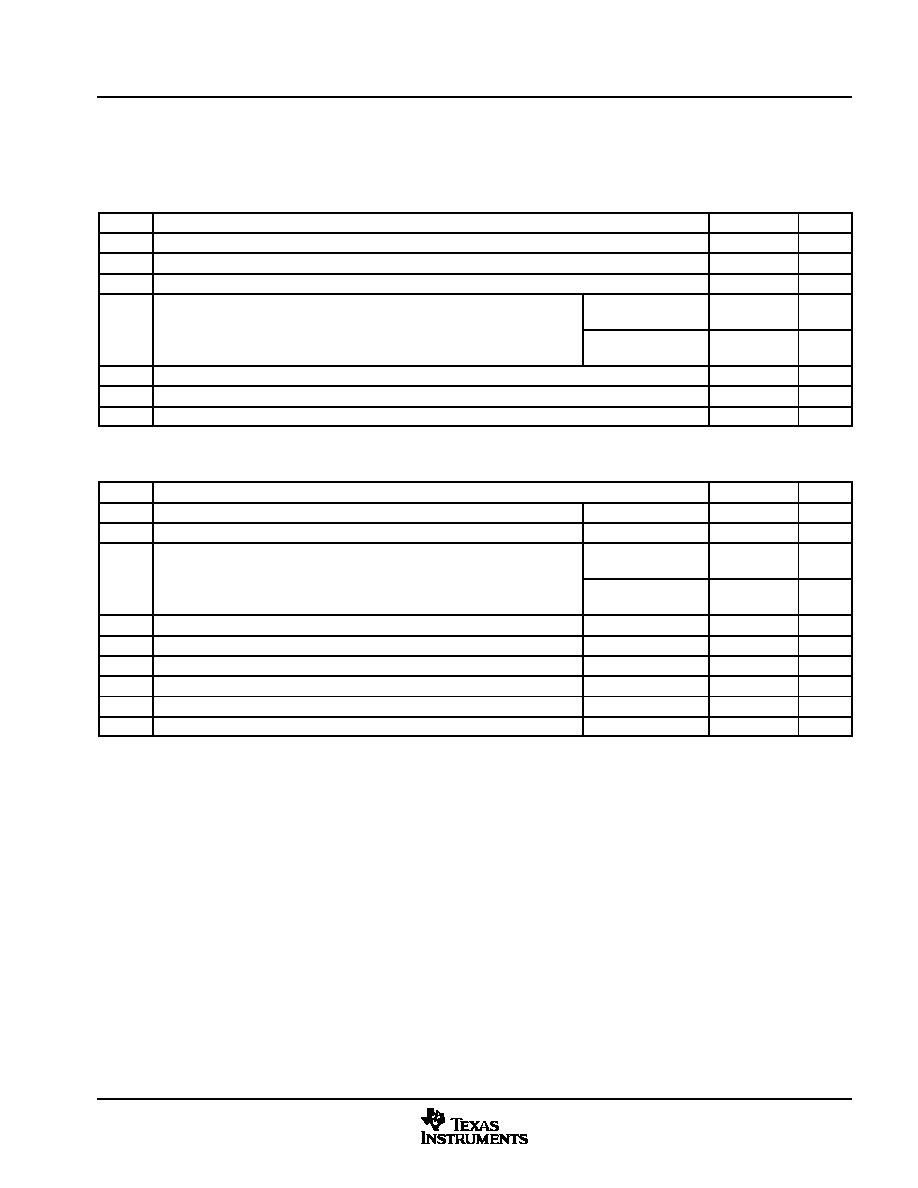

5.10

Multichannel Serial Interface (MCSI)

149

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

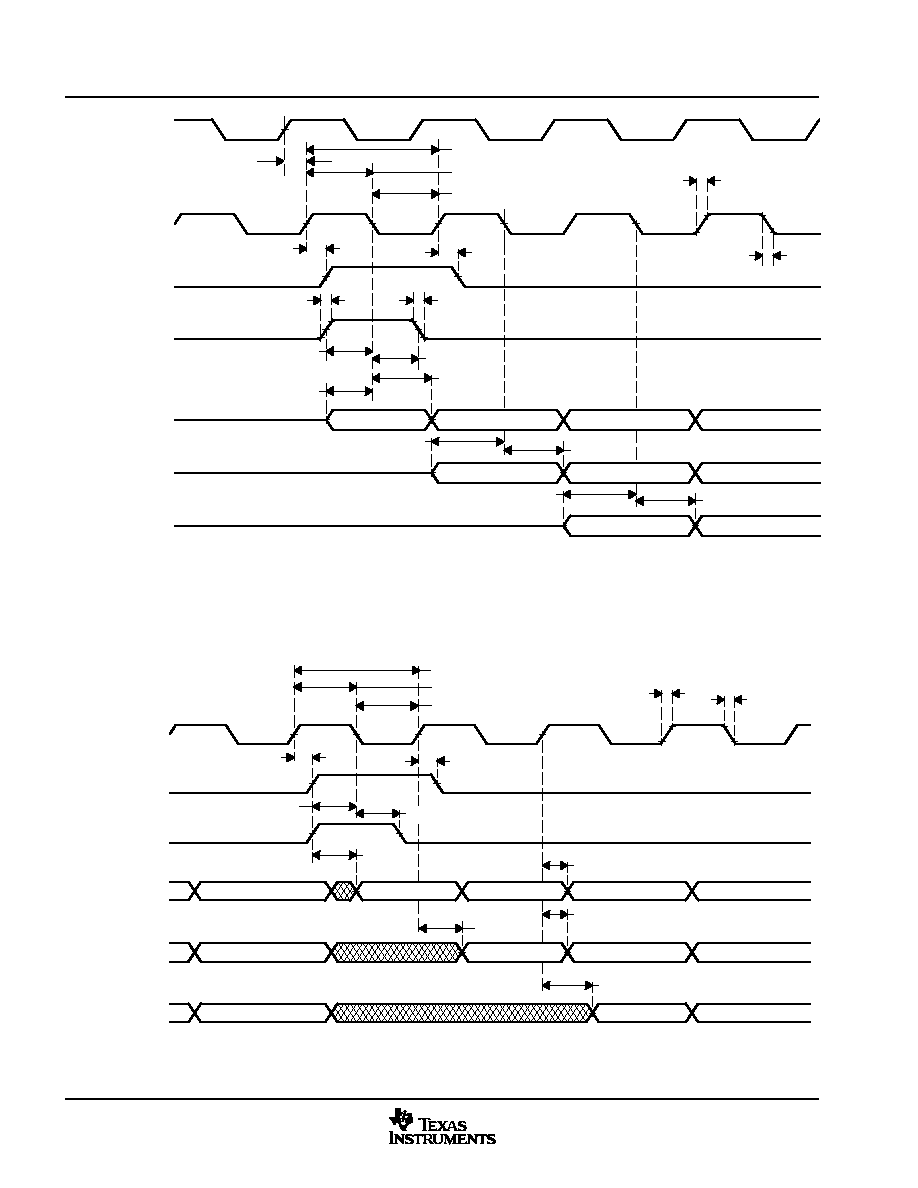

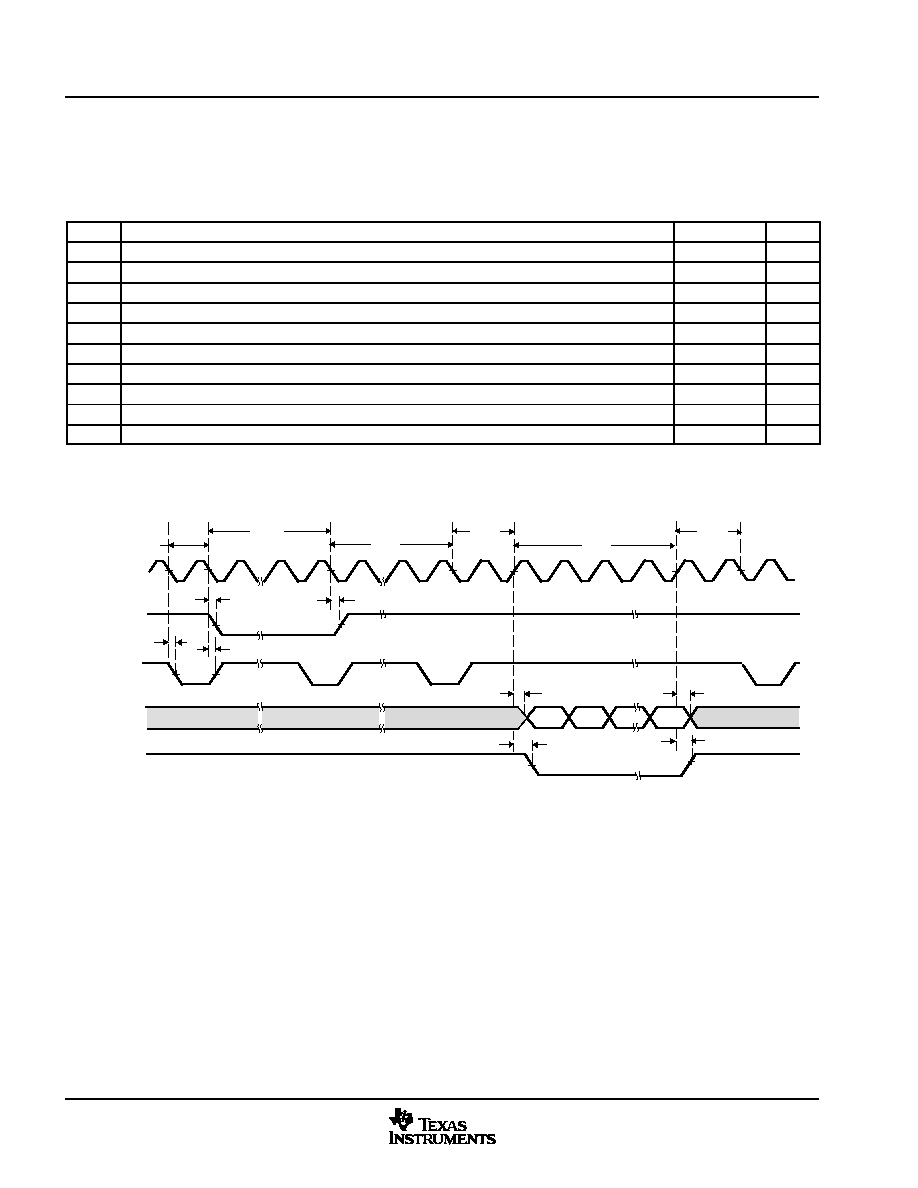

5.11

Camera Interface Timings

151

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

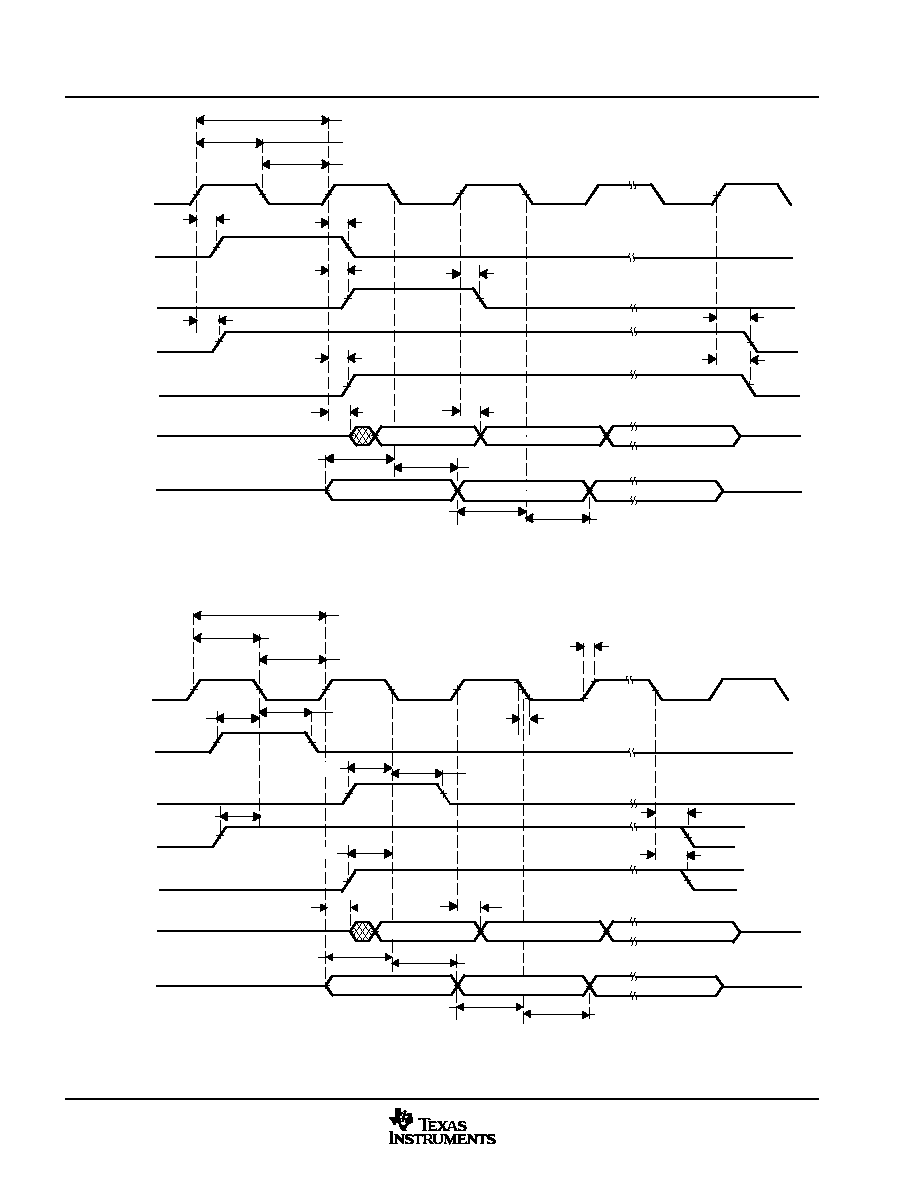

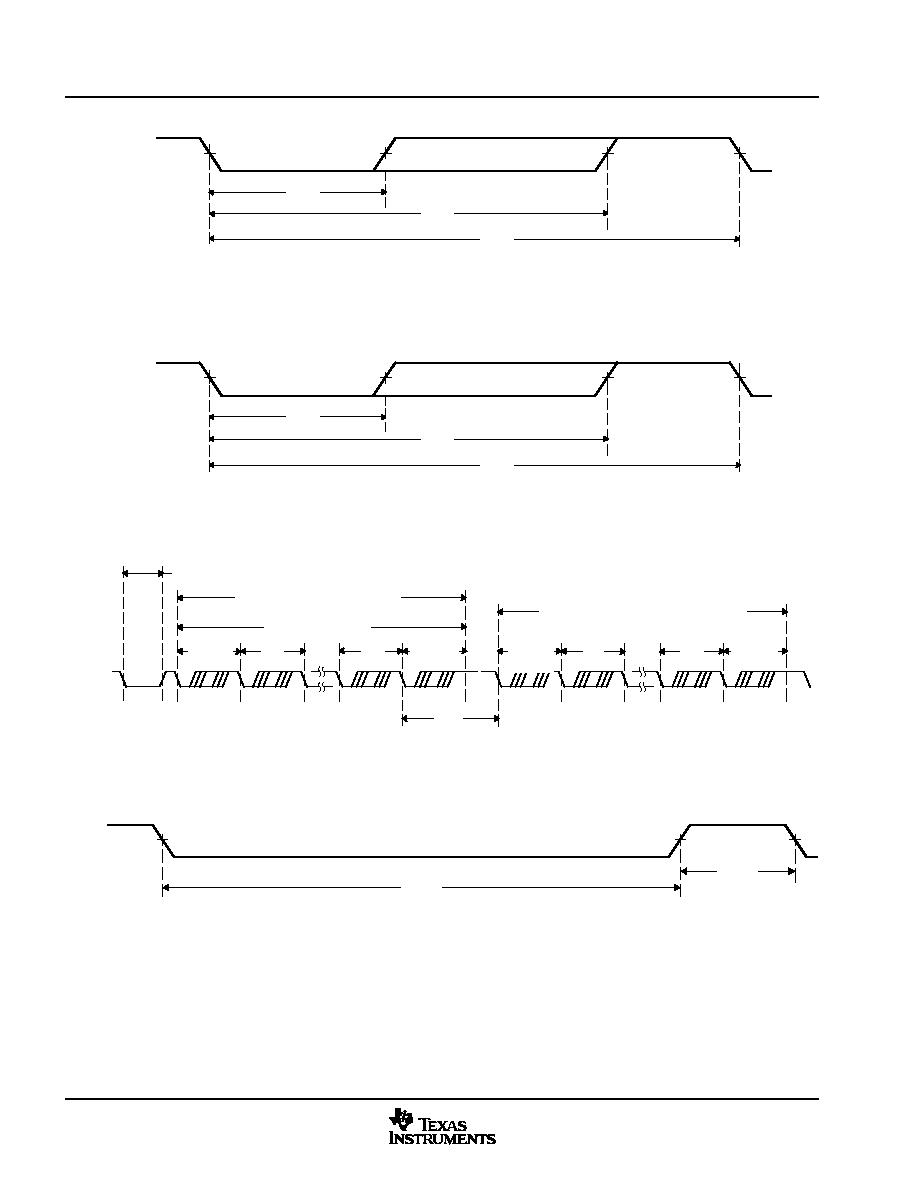

5.12

LCD Controller Timings

152

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

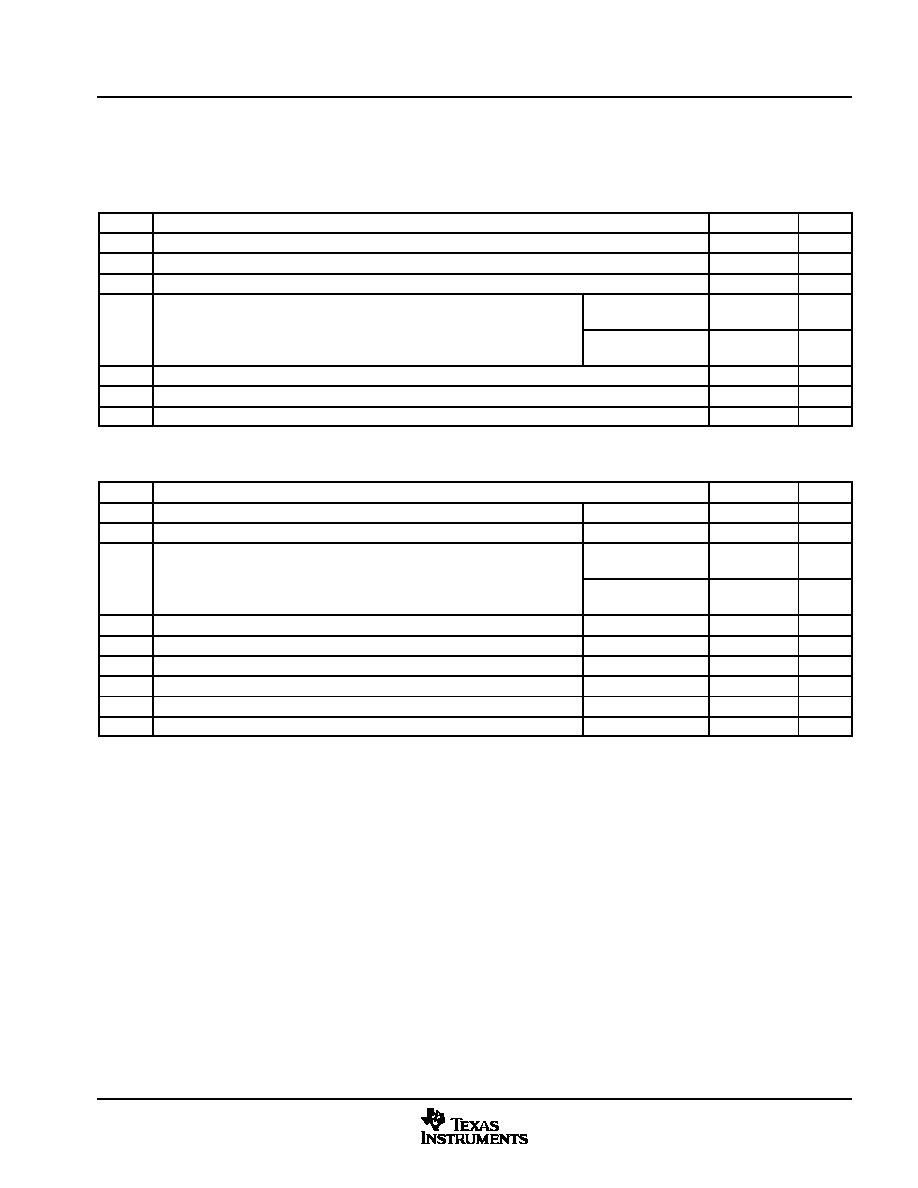

5.13

Multimedia Card/Secure Digital (MMC/SD) Timings

154

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

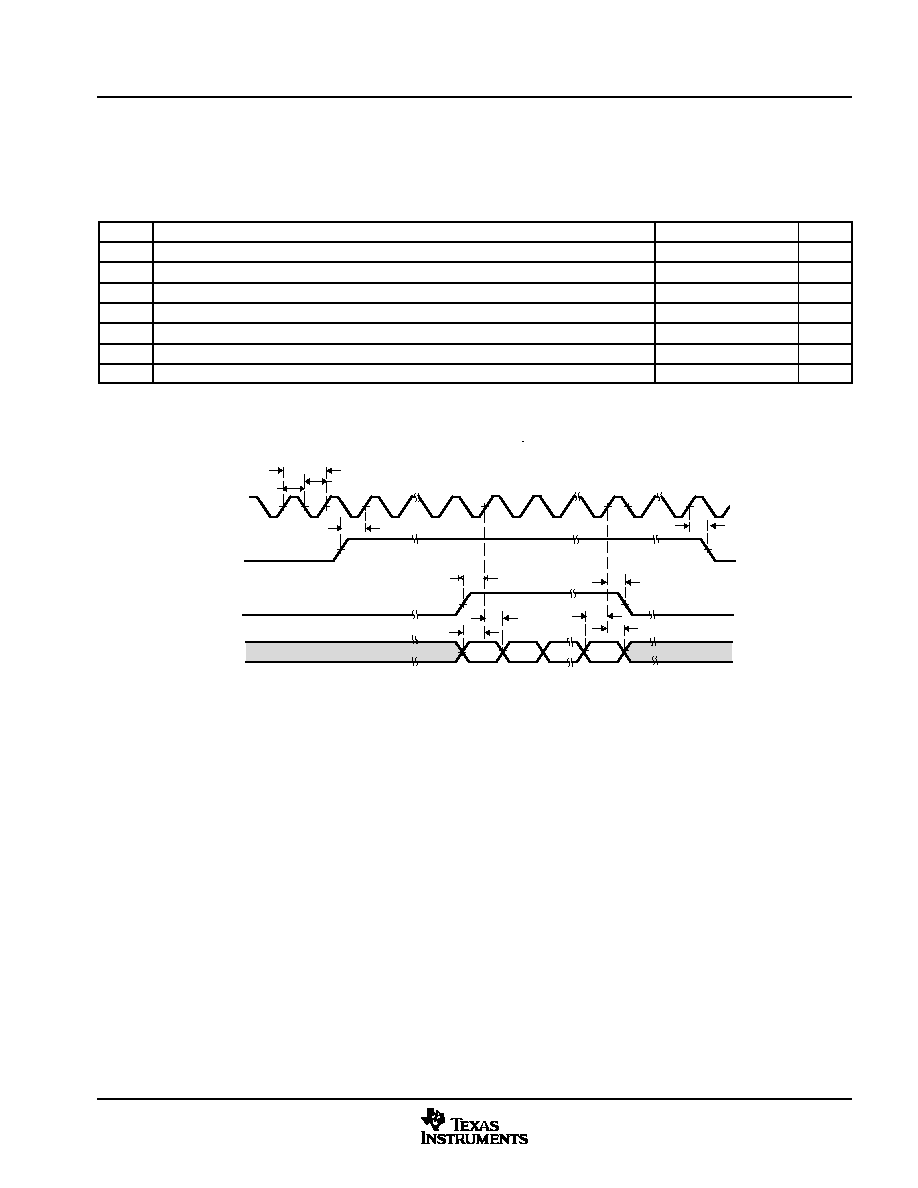

5.14

I

2

C Timings

156

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.15

Universal Serial Bus (USB) Timings

157

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.16

MICROWIRE Interface Timings

158

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.17

HDQ/1-Wire Interface Timings

159

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6

Glossary

161

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

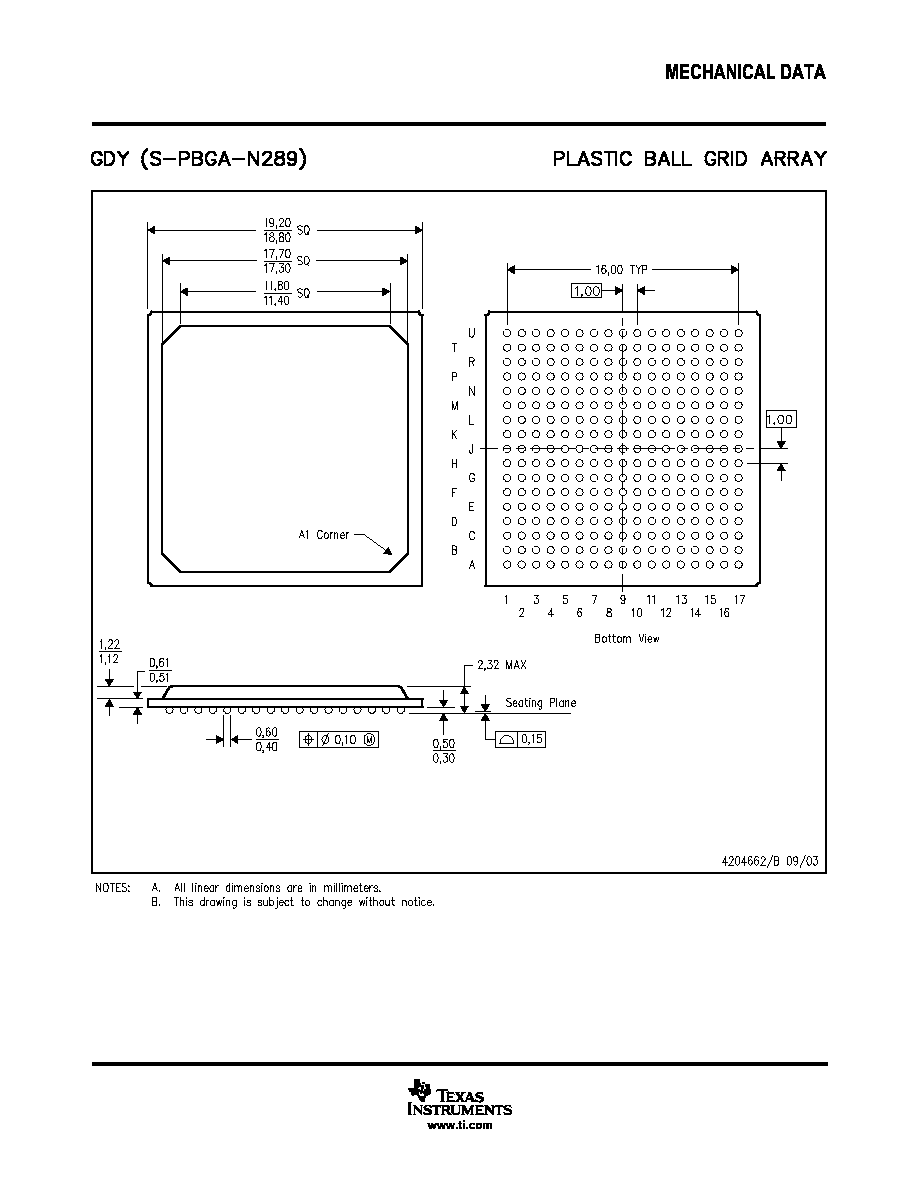

7

Mechanical Data

164

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contents

8

August 2002 - Revised August 2004

SPRS197D

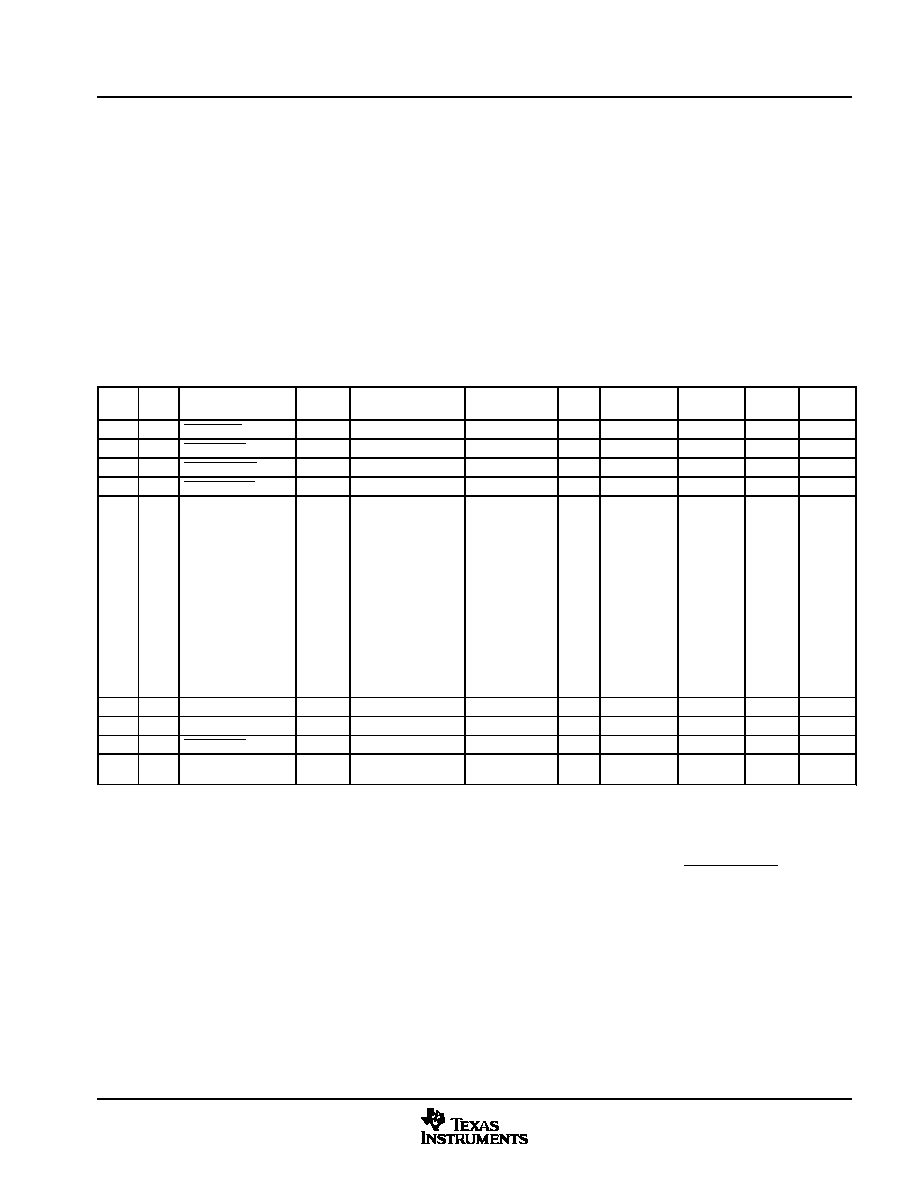

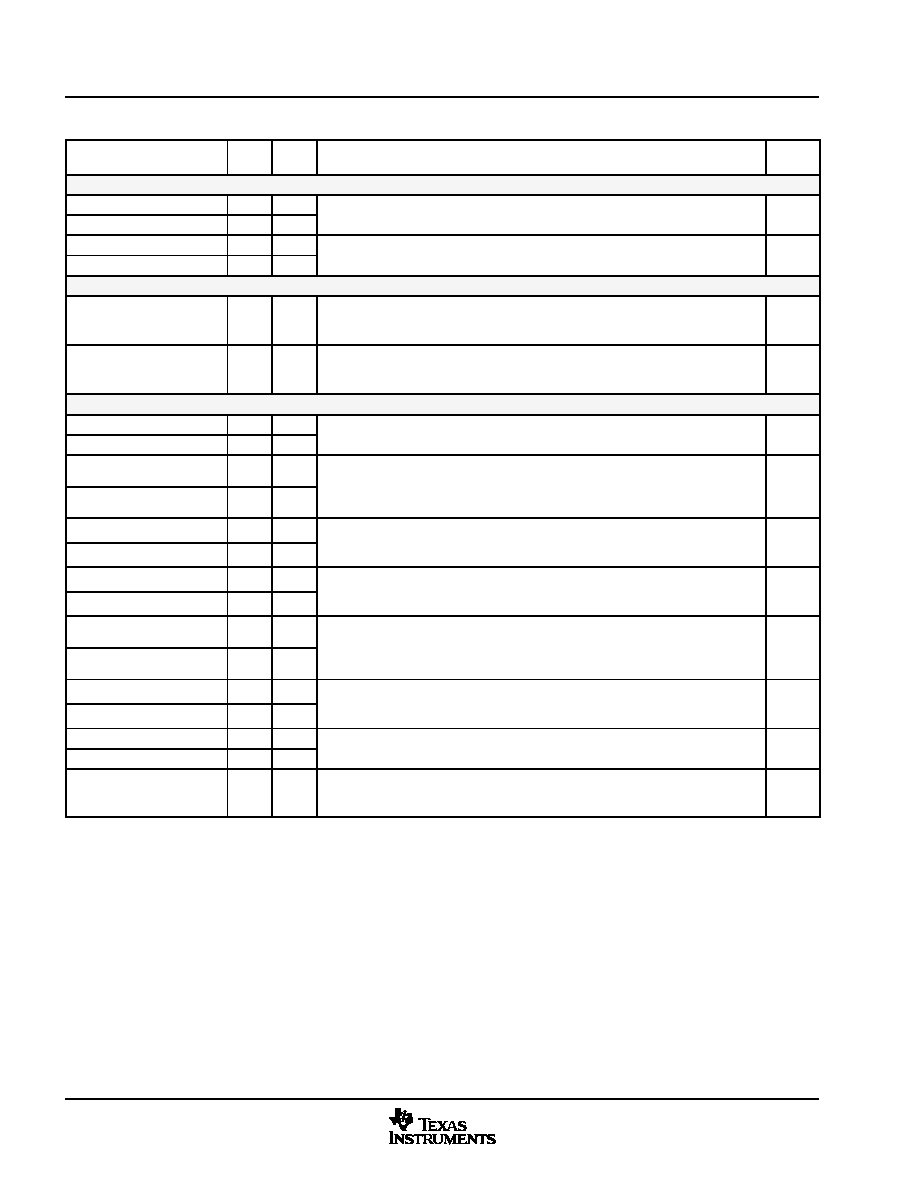

Figures

9

August 2002 - Revised August 2004

SPRS197D

List of Figures

Figure

Page

2-1

OMAP5910 GZG MicroStar BGA Package (Bottom View)

18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2

OMAP5910 GDY Package (Bottom View)

21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1

OMAP5910 Functional Block Diagram

47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2

DSP MMU Off

55

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3

DSP MMU On

56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4

Supply Connections for a Typical System

69

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5

Supply Connections for a System With 1.8-V SDRAM

70

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6

External RC Circuit for DPLL CVDD Noise Isolation

71

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

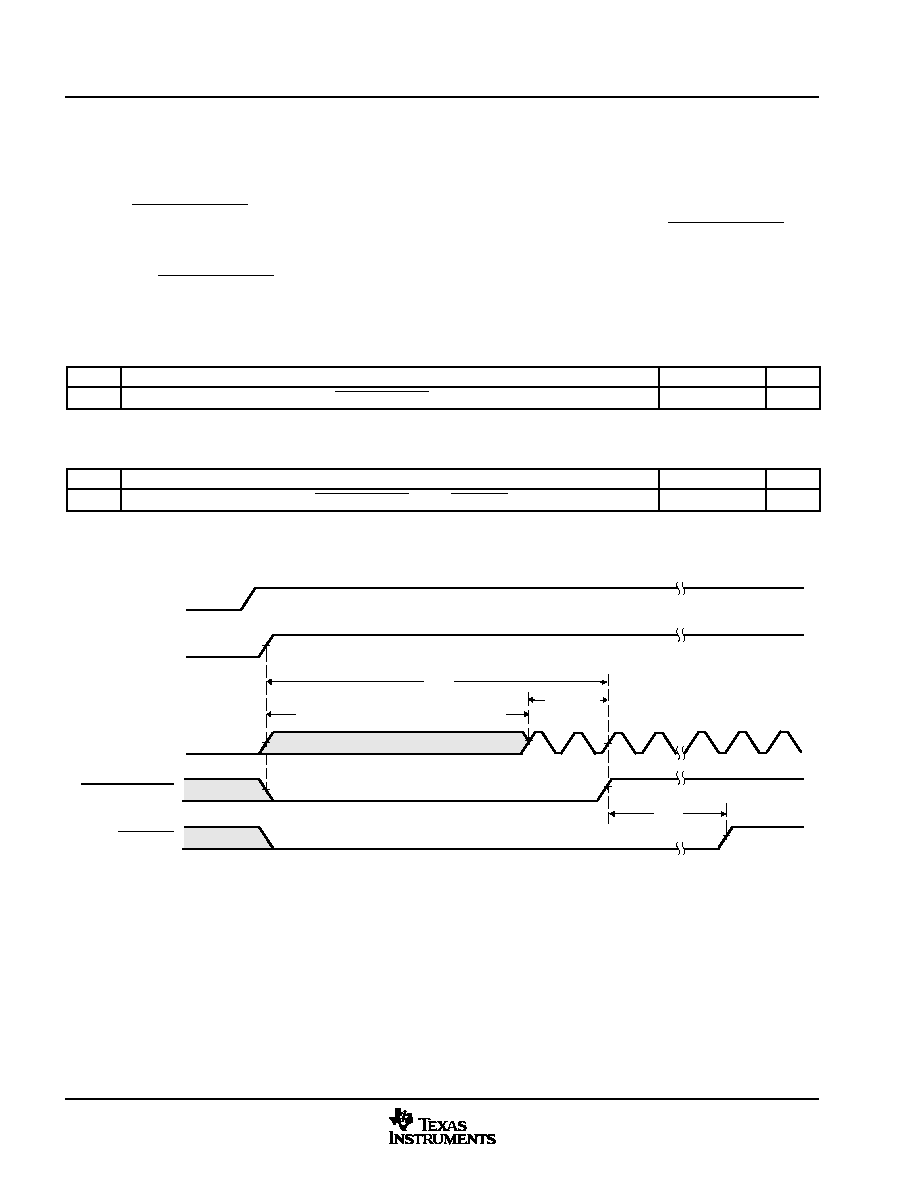

5-1

Tester Pin Electronics

124

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-2

32-kHz Oscillator External Crystal

125

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-3

32-kHz Input Clock

126

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-4

Internal System Oscillator External Crystal

126

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

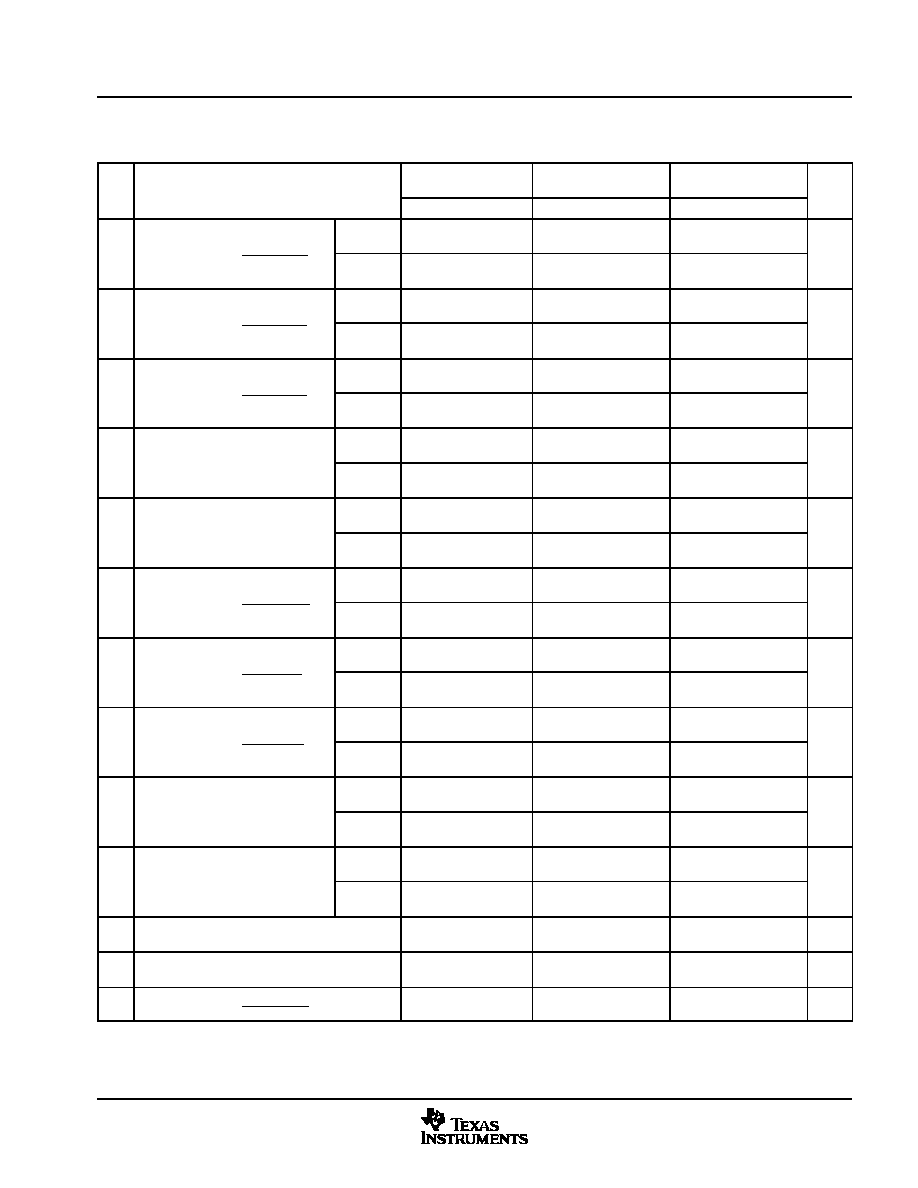

5-5

Device Reset Timings

128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-6

MPU Core Reset Timings

129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-7

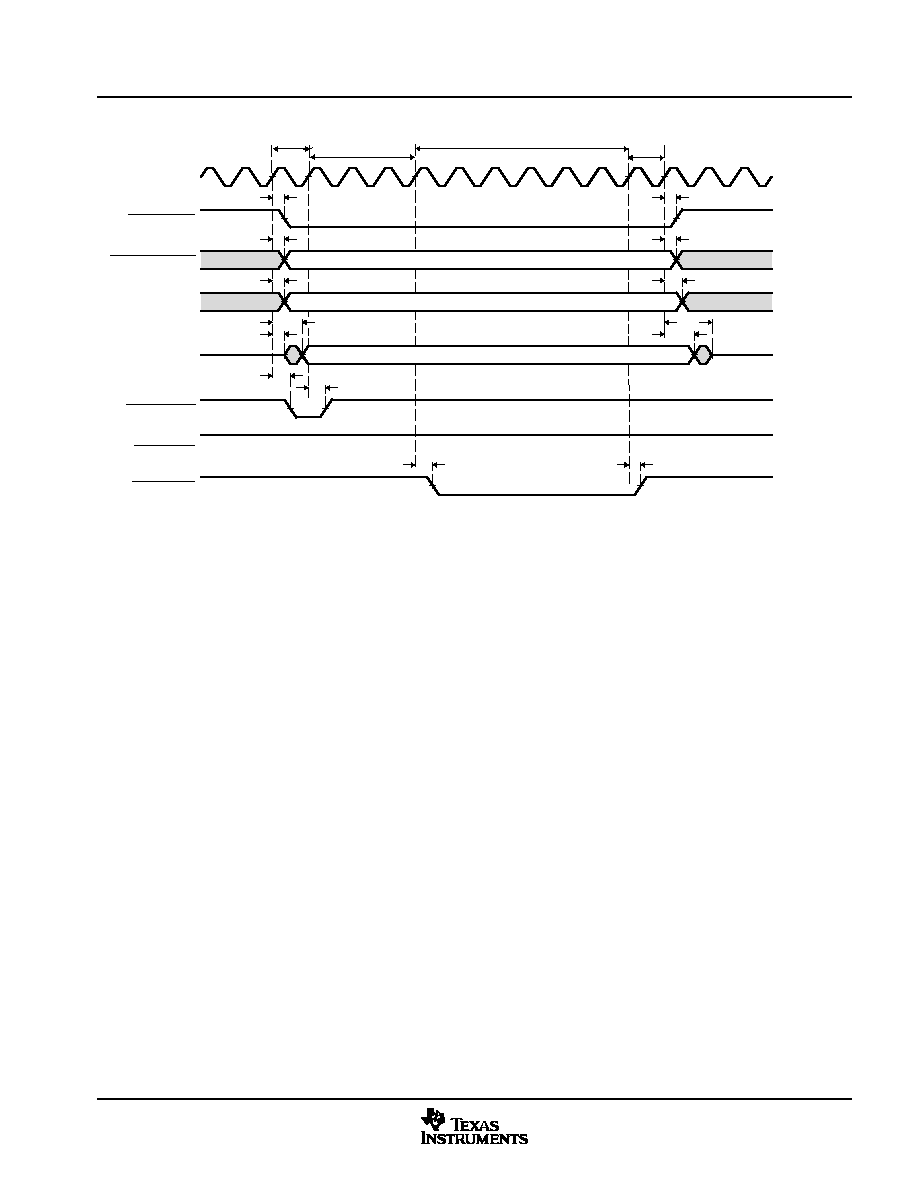

Asynchronous Memory Read Timing

132

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-8

Asynchronous 32-Bit Read

133

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-9

Asynchronous Read - Page Mode ROM

134

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-10

Asynchronous Memory Write Timing

135

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11

Synchronous Burst Read

136

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-12

32-Bit (2 x 16-Bit) SDRAM RD (Read) Command (Active Row)

138

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-13

32-Bit (2 x 16-Bit) SDRAM WRT (Write) Command (Active Row)

138

. . . . . . . . . . . . . . . . . . . . . . . . . . .

5-14

SDRAM ACTV (Activate Row) Command

139

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15

SDRAM DCAB (Precharge/Deactivate Row) Command

139

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16

SDRAM REFR (Refresh) Command

140

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-17

SDRAM MRS (Mode Register Set) Command

140

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-18

McBSP Receive Timings

144

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-19

McBSP Transmit Timings

144

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-20

McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0

145

. . . . . . . . . . . . . . . . . . . . . . . .

5-21

McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0

146

. . . . . . . . . . . . . . . . . . . . . . . .

5-22

McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1

147

. . . . . . . . . . . . . . . . . . . . . . . .

5-23

McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1

148

. . . . . . . . . . . . . . . . . . . . . . . .

5-24

MCSI Master Mode Timings

150

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-25

MCSI Slave Mode Timings

150

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-26

Camera Interface Timings

151

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-27

TFT Mode (LCD.HS/LCD.VS on Falling and LCD.Px on Rising LCD.PCLK)

152

. . . . . . . . . . . . . . . . . .

5-28

TFT Mode (LCD.HS/LCD.VS on Rising and LCD.Px on Falling LCD.PCLK)

153

. . . . . . . . . . . . . . . . . .

5-29

MMC/SD Host Command Timings

154

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figures

10

August 2002 - Revised August 2004

SPRS197D

5-30

MMC/SD Card Response Timings

154

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-31

MMC/SD Host Write Timings

155

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-32

MMC/SD Host Read and Card CRC Status Timings

155

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-33

I

2

C Timings

156

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-34

USB Integrated Transceiver Interface Timings

157

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-35

MICROWIRE Timings

158

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-36

OMAP5910 HDQ Interface Reading From HDQ Slave Device

160

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-37

OMAP5910 HDQ Interface Writing to HDQ Slave Device

160

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-38

Typical Communication Between OMAP5910 HDQ and HDQ Slave

160

. . . . . . . . . . . . . . . . . . . . . . . . .

5-39

HDQ/1-Wire Break (Reset) Timing

160

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

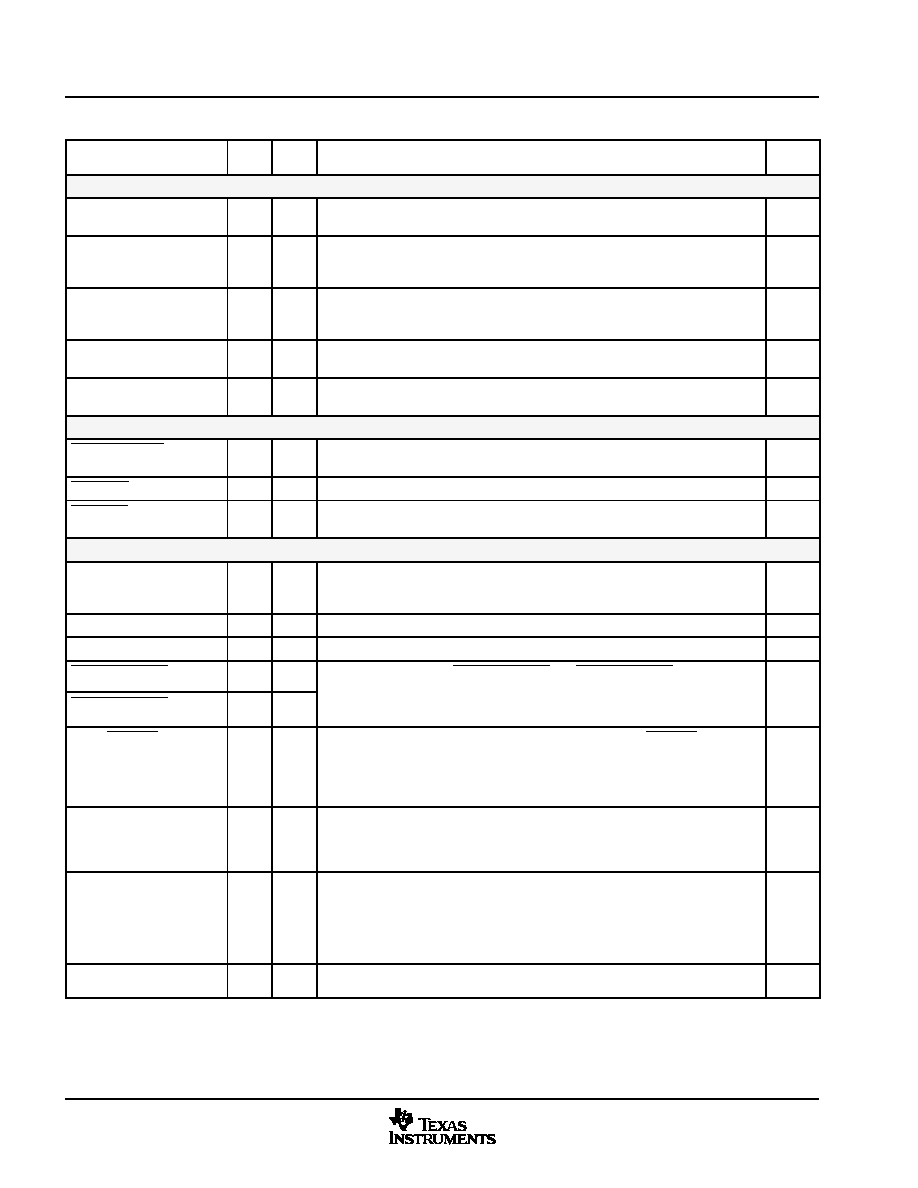

Tables

11

August 2002 - Revised August 2004

SPRS197D

List of Tables

Table

Page

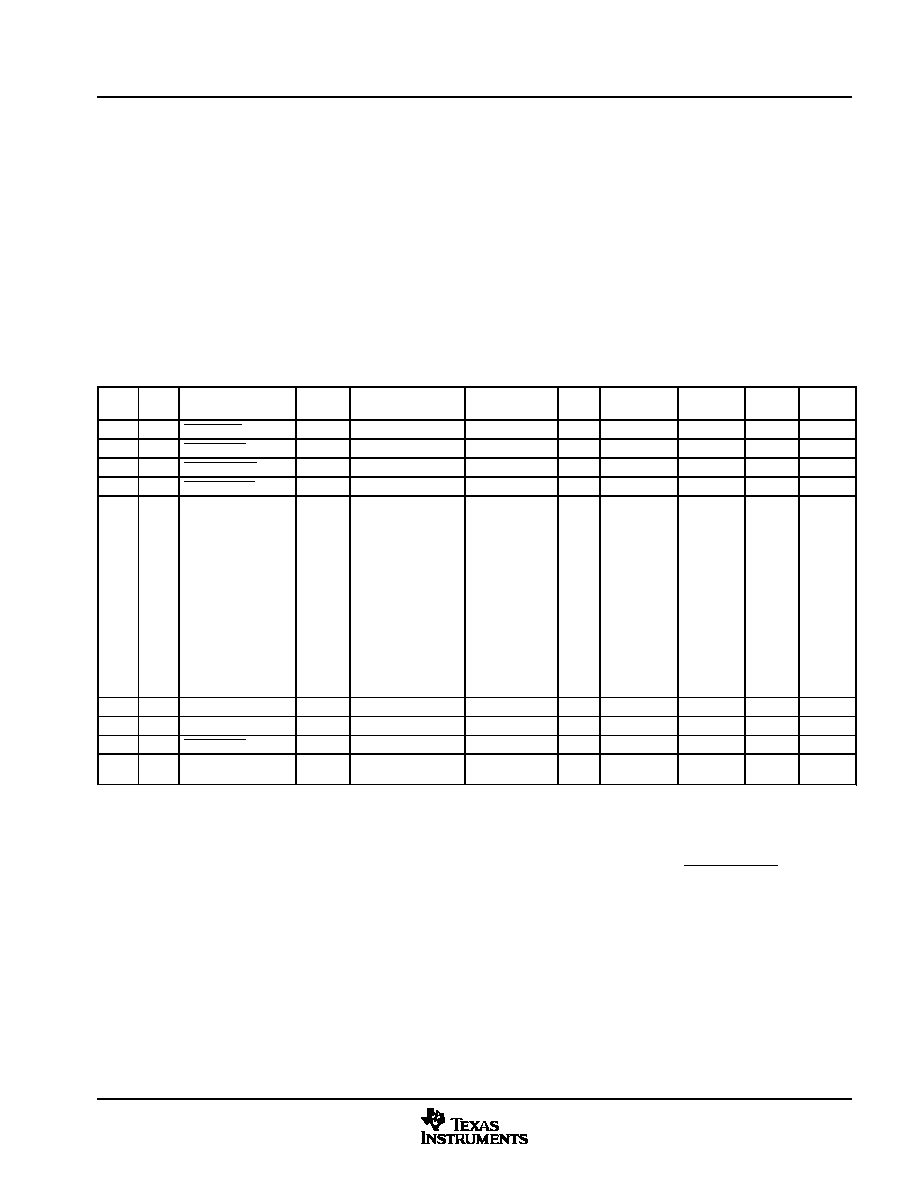

2-1

GZG BGA Terminal Assignments

18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2

GDY BGA Terminal Assignments

22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

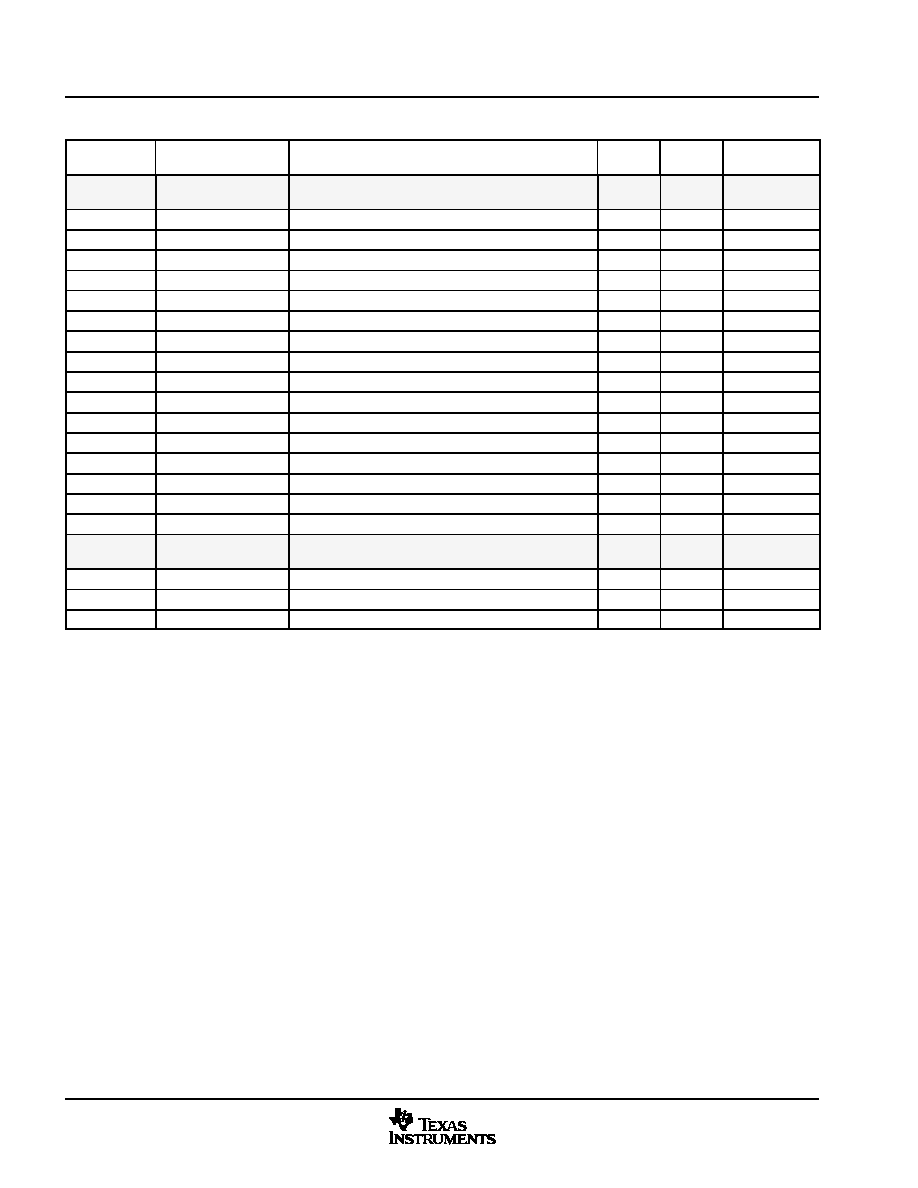

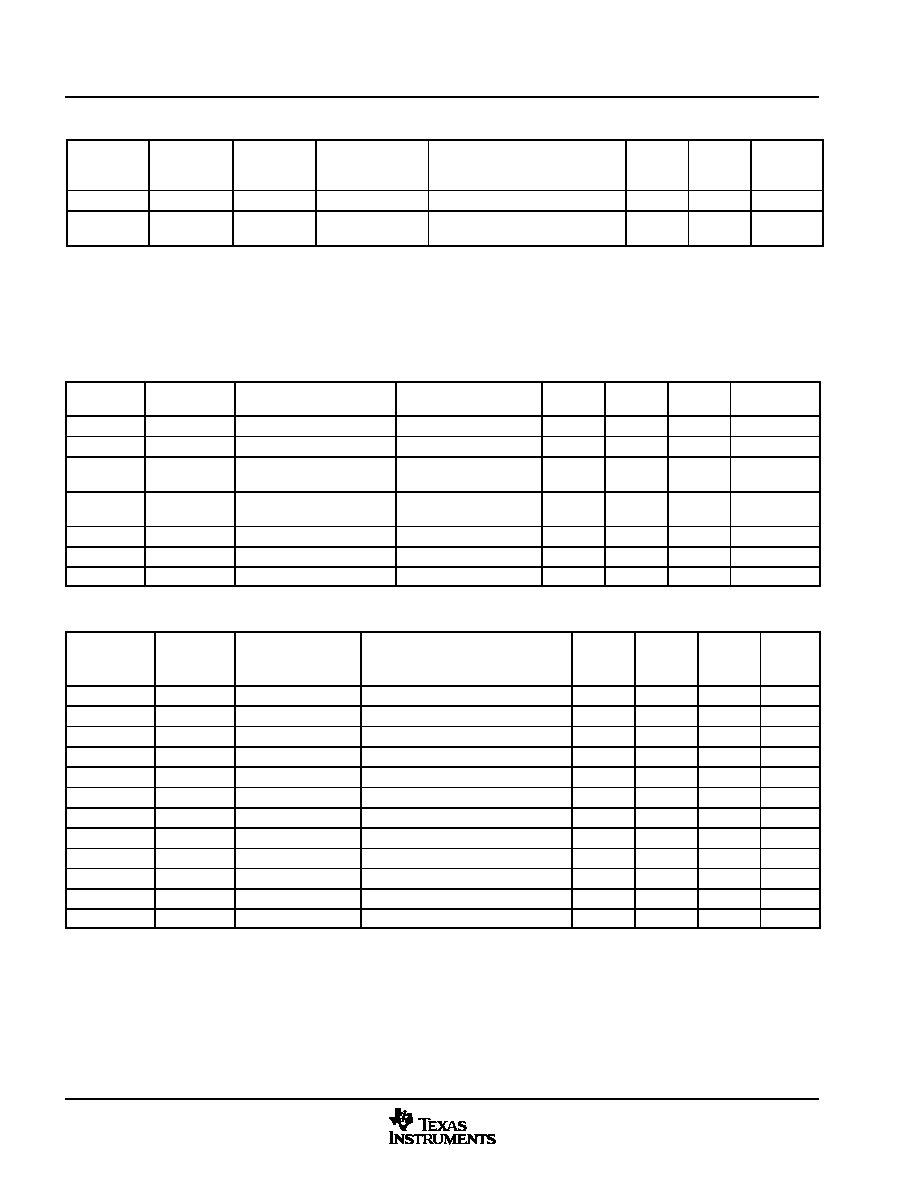

2-3

Terminal Characteristics and Multiplexing

25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

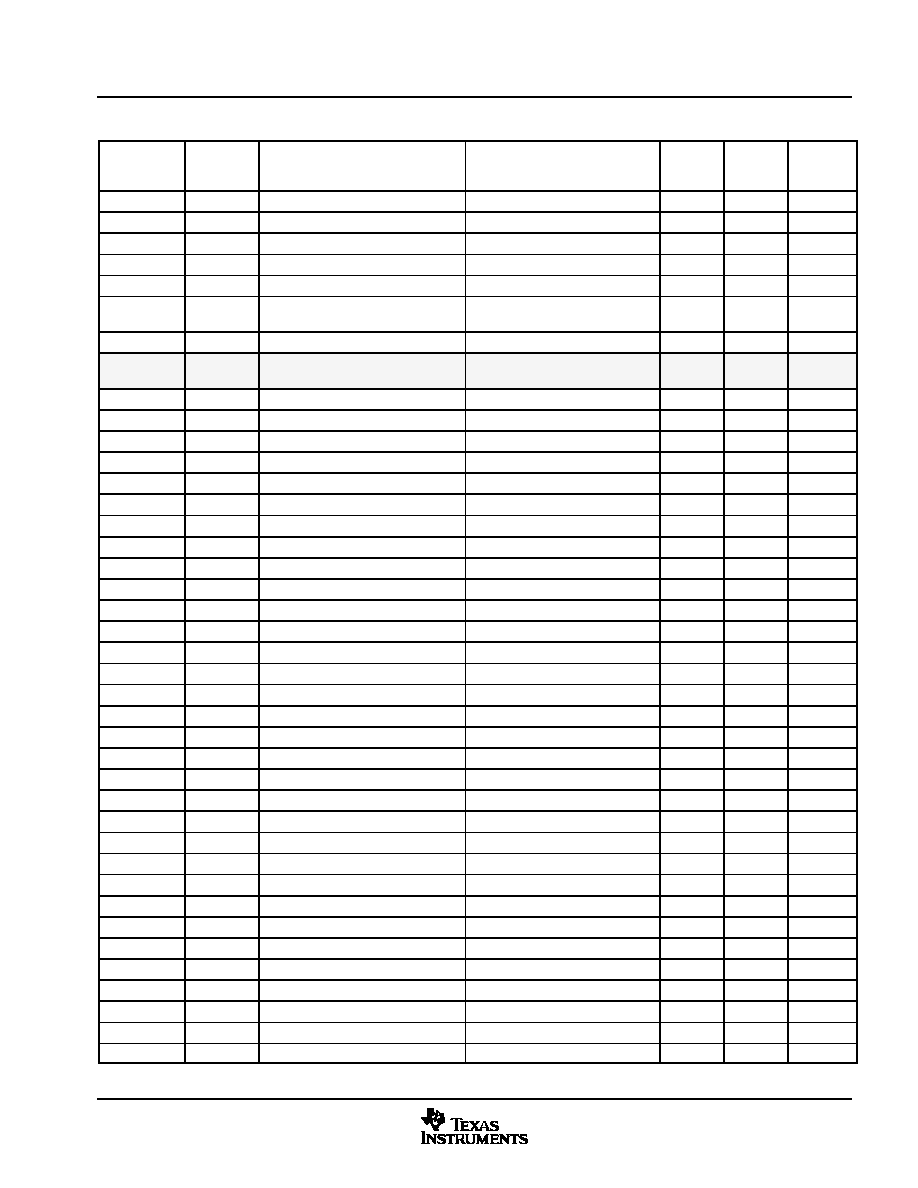

2-4

Signal Description

34

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1

OMAP5910 MPU Global Memory Map

50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2

MPU Private Peripheral Registers

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3

MPU Public Peripheral Registers

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4

MPU/DSP Shared Peripheral Registers

51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5

DSP Public Peripheral Registers (Accessible via MPUI Port)

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6

MPU Configuration Registers

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-7

DSP Global Memory Map

52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-8

DARAM Blocks

53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-9

SARAM Blocks

53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-10

DSP Private Peripheral Registers

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-11

DSP Public Peripheral Registers

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-12

DSP/MPU Shared Peripheral Registers

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-13

DSP Configuration Registers

54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-14

MPU Timer 1 Registers

72

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-15

MPU Timer 2 Registers

72

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-16

MPU Timer 3 Registers

72

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-17

MPU Watchdog Timer Registers

72

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-18

MPU Level 1 Interrupt Handler Registers

73

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-19

MPU Level 2 Interrupt Handler Registers

74

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-20

System DMA Controller Registers

75

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-21

LCD Controller Registers

78

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-22

McBSP2 Registers

80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-23

MICROWIRE Registers

80

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-24

I

2

C Registers

81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-25

HDQ/1-Wire Interface Registers

81

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-26

MMC/SD Registers

82

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-27

USB Function Registers

83

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-28

USB Host Controller Registers

85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-29

Camera Interface Registers

85

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-30

MPU I/O/Keyboard Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-31

PWL Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-32

PWT Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-33

LED Pulse Generator 1 Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-34

LED Pulse Generator 2 Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-35

32k Timer Registers

86

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-36

Real-Time Clock Registers

87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-37

Frame Adjustment Counter Registers

87

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-38

OMAP 5910 Pin Configuration Registers

89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-39

Local Bus Control Registers

89

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-40

Local Bus MMU Registers

90

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-41

DSP MMU Registers

91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

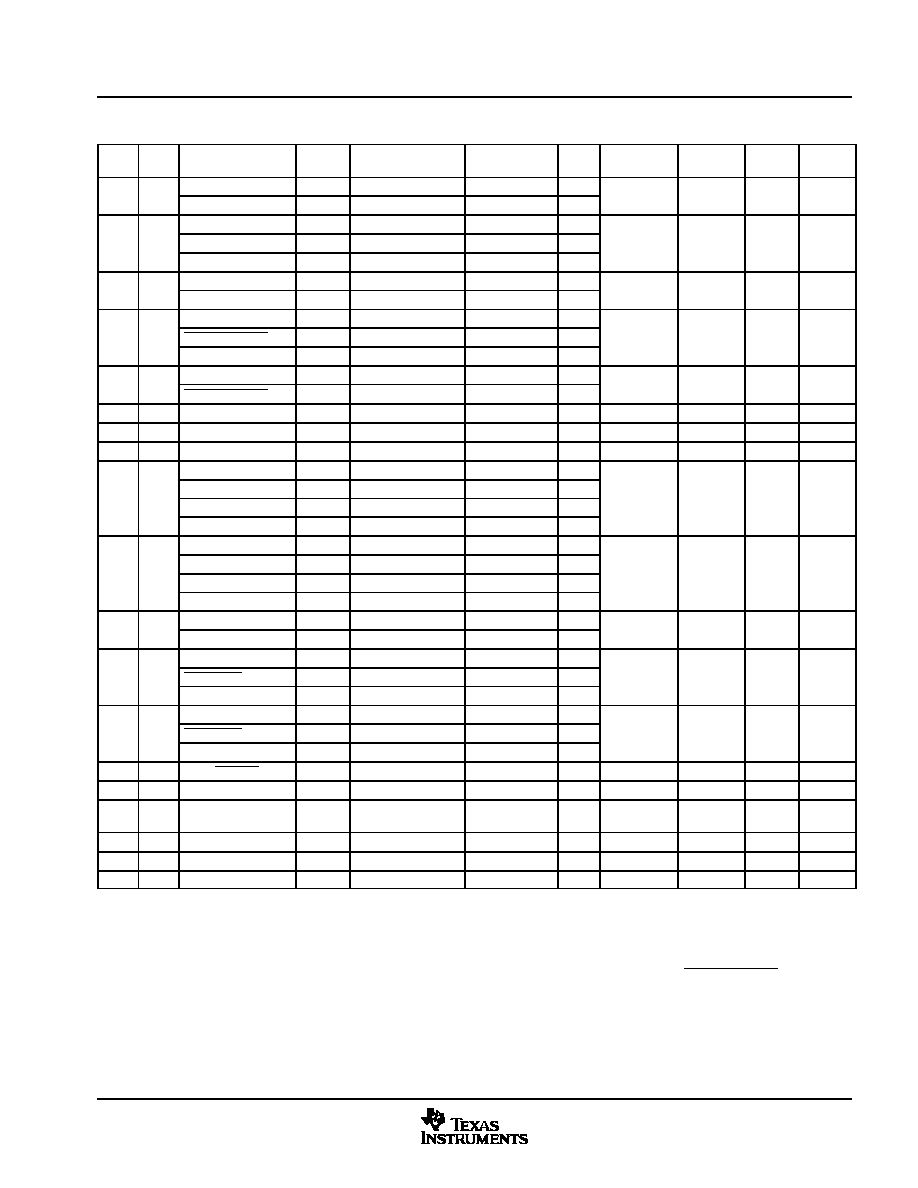

Tables

12

August 2002 - Revised August 2004

SPRS197D

Table

Page

3-42

MPUI Registers

91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-43

TIPB (Private) Bridge 1 Configuration Registers

91

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-44

TIPB (Public) Bridge 2 Configuration Registers

92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-45

MPU UART TIPB Bus Switch Registers

92

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-46

Traffic Controller Registers

93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-47

MPU Clock/Reset/Power Mode Control Registers

93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-48

DPLL1 Register

93

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-49

Ultra Low-Power Device Module Registers

94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-50

Device Die Identification Registers

94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-51

JTAG Identification Code Register

94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-52

DSP DMA Controller Registers

96

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-53

DSP Timer 1 Registers

99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-54

DSP Timer 2 Registers

99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-55

DSP Timer 3 Registers

99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-56

DSP Watchdog Timer Registers

99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-57

DSP Interrupt Interface Registers

99

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-58

DSP Level 2 Interrupt Handler Registers

100

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-59

McBSP1 Registers

101

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-60

McBSP3 Registers

102

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-61

MCSI1 Registers

104

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-62

MCSI2 Registers

105

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-63

DSP Instruction Cache Registers

106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-64

DSP EMIF Configuration Register

106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-65

DSP TIPB Bridge Configuration Registers

106

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-66

DSP UART TIPB Bus Switch Registers

107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-67

DSP Clock Mode Registers

107

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-68

UART1 Registers

109

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-69

UART2 Registers

110

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-70

UART3/IrDA Registers

111

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-71

MPU/DSP Shared GPIO Registers

112

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-72

MPU/DSP Shared Mailbox Registers

112

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-73

MPU Level 1 and Level 2 Interrupt Mappings

113

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-74

DSP Level 1 Interrupt Mappings

115

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-75

DSP Level 2 Interrupt Mappings

116

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-76

DMA Request Mapping

117

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-77

DSP DMA Mapping

118

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-1

Thermal Resistance Characteristics

124

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-2

32-kHz Oscillator Switching Characteristics

125

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-3

32-kHz Input Clock Timing Requirements

126

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-4

Base Oscillator Switching Characteristics

127

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-5

Internal Clock Speed Limitations

127

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-6

OMAP5910 Device Reset Timing Requirements

128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-7

OMAP5910 Device Reset Switching Characteristics

128

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-8

MPU_RST Timing Requirements

129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-9

MPU_RST Switching Characteristics

129

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tables

13

August 2002 - Revised August 2004

SPRS197D

Table

Page

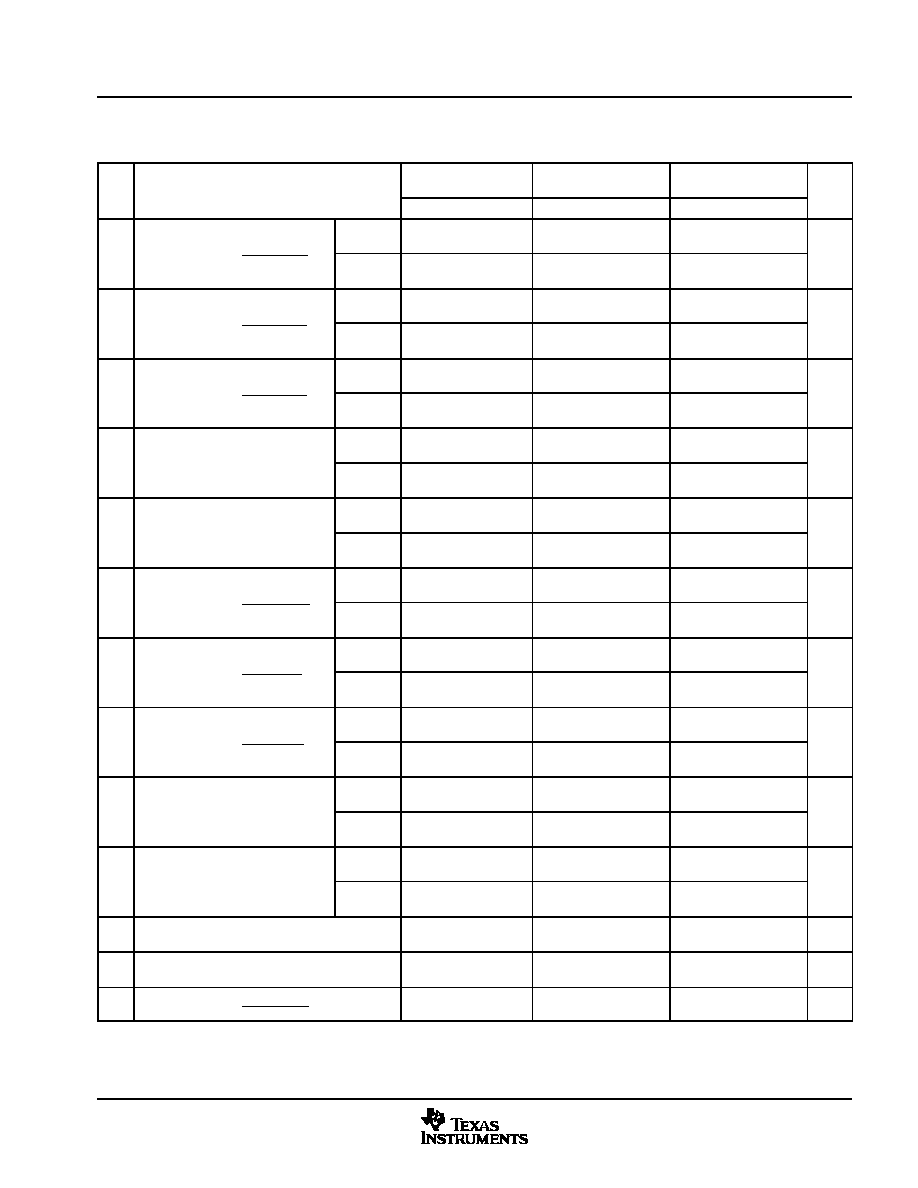

5-10

EMIFS/Flash Interface Timing Requirements

130

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-11

EMIFS/Flash Interface Switching Characteristics

131

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-12

EMIFF/SDRAM Interface Timing Requirements

137

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-13

EMIFF/SDRAM Interface Switching Characteristics

137

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

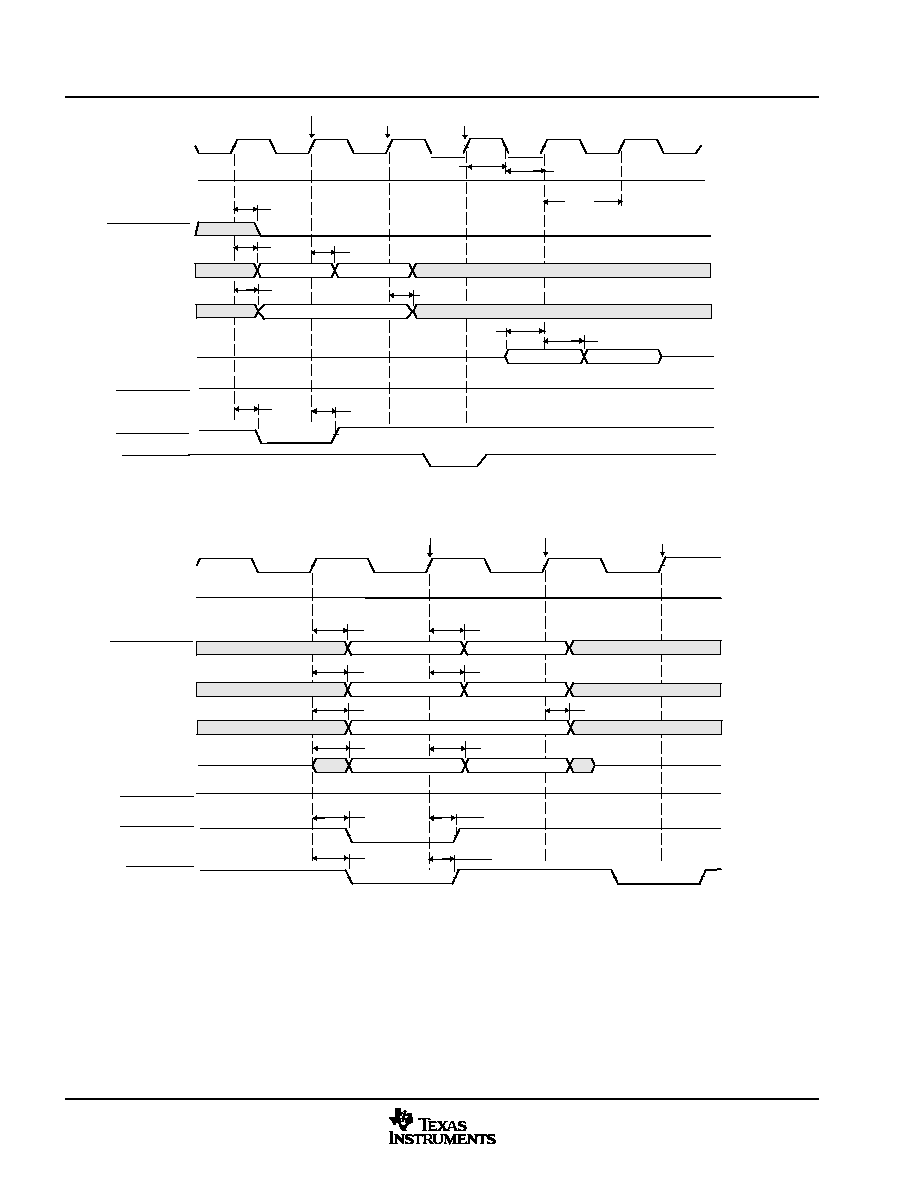

5-14

McBSP Timing Requirements

141

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-15

McBSP Switching Characteristics

143

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-16

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)

145

. . . . . . . . . .

5-17

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0)

145

. . . . . .

5-18

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0)

146

. . . . . . . . . .

5-19

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0)

146

. . . . . . .

5-20

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)

147

. . . . . . . . . .

5-21

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1)

147

. . . . . .

5-22

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1)

148

. . . . . . . . . .

5-23

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1)

148

. . . . . . .

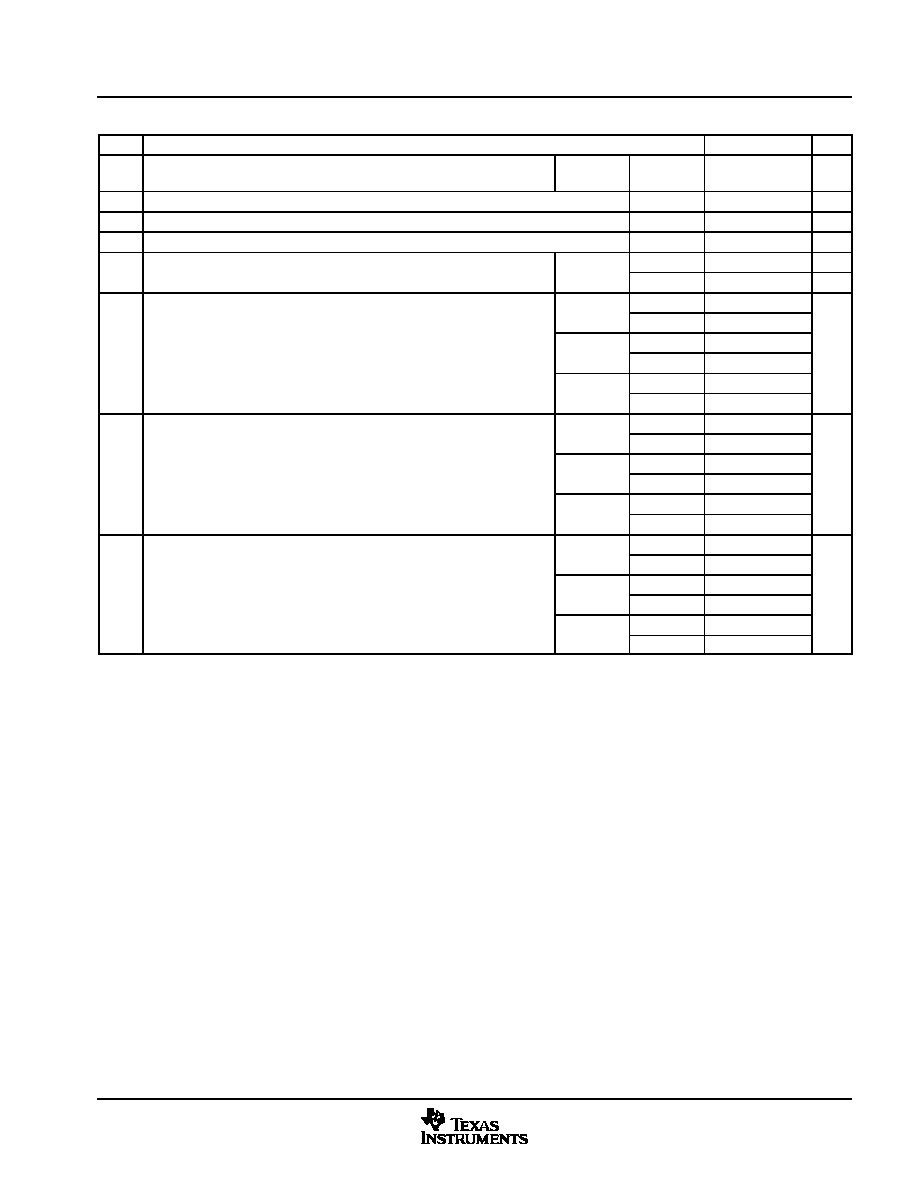

5-24

MCSI Timing Requirements

149

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-25

MCSI Switching Characteristics

149

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-26

Camera Interface Timing Requirements

151

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-27

LCD Controller Switching Characteristics

152

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-28

MMC/SD Timing Requirements

154

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-29

MMC/SD Switching Characteristics

154

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-30

I

2

C Signals (I2C.SDA and I2C.SCL) Switching Characteristics

156

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-31

USB Integrated Transceiver Interface Switching Characteristics

157

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-32

MICROWIRE Timing Requirements

158

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-33

MICROWIRE Switching Characteristics

158

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-34

HDQ/1-Wire Timing Requirements

159

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5-35

HDQ/1-Wire Switching Characteristics

159

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Tables

14

August 2002 - Revised August 2004

SPRS197D

Features

15

August 2002 - Revised August 2004

SPRS197D

1

OMAP5910 Features

D

Low-Power, High-Performance CMOS

Technology

- 0.13-�m Technology

- 1.6-V Core Voltage

D

TI925T (MPU) ARM9TDMI Core

- Support 32-Bit and 16-Bit (Thumb

Mode) Instruction Sets

- 16K-Byte Instruction Cache

- 8K-Byte Data Cache

- Data and Program Memory Management

Units (MMUs)

- Two 64-Entry Translation Look-Aside

Buffers (TLBs) for MMUs

- 17-Word Write Buffer

D

TMS320C55x (C55x) DSP Core

- One/Two Instructions Executed per Cycle

- Dual Multipliers (Two Multiply-

Accumulates per Cycle)

- Two Arithmetic/Logic Units

- One Internal Program Bus

- Five Internal Data/Operand Buses

(3 Read Buses and 2 Write Buses)

- 32K x 16-Bit On-Chip Dual-Access RAM

(DARAM) (64K Bytes)

- 48K x 16-Bit On-Chip Single-Access RAM

(SARAM) (96K Bytes)

- 16K x 16-Bit On-Chip ROM (32K Bytes)

- Instruction Cache (24K Bytes)

- Video Hardware Accelerators for DCT,

iDCT, Pixel Interpolation, and Motion

Estimation for Video Compression

D

192K Bytes of Shared Internal SRAM

D

Memory Traffic Controller (TC)

- 16-Bit EMIFS External Memory Interface

to Access up to 128M Bytes of Flash,

ROM, or ASRAM

- 16-Bit EMIFF External Memory Interface

to Access up to 64M Bytes of SDRAM

D

9-Channel System DMA Controller

D

DSP Memory Management Unit

D

Endianism Conversion Logic

D

Digital Phase-Locked Loop (DPLL) for

MPU/DSP/TC Clocking Control

D

DSP Peripherals

- Three 32-Bit Timers and Watchdog Timer

- Level1/Level2 Interrupt Handlers

- Six-Channel DMA Controller

- Two Multichannel Buffered Serial Ports

(McBSP)

- Two Multichannel Serial Interfaces

(MCSI)

D

TI925T Peripherals

- Three 32-Bit Timers and Watchdog Timer

- 32-kHz Timer

- Level1/Level2 Interrupt Handlers

- USB (Full/Low Speed) Host Interface

With up to 3 Ports

- USB (Full Speed) Function Interface

- One Integrated USB Transceiver for

Either Host or Function

- Multichannel Buffered Serial Port

- Inter-Integrated Circuit (I

2

C) Master and

Slave Interface

- MICROWIRE Serial Interface

- Multimedia Card (MMC) and Secure

Digital (SD) Interface

- HDQ/1-Wire Interface

- Camera Interface for CMOS Sensors

- ETM9 Trace Module for TI925T Debug

- Keyboard Matrix Interface (6 x 5 or 8 x 8)

- Up to Ten MPU General-Purpose I/Os

- Pulse-Width Tone (PWT) Interface

- Pulse-Width Light (PWL) Interface

- Two LED Pulse Generators (LPGs)

- Real-Time Clock (RTC)

- LCD Controller With Dedicated System

DMA Channel

D

Shared Peripherals

- Three Universal Asynchronous

Receiver/Transmitters (UARTs) (One

Supporting SIR Mode for IrDA)

- Four Interprocessor Mailboxes

- Up to 14 Shared General-Purpose I/Os

D

Individual Power-Saving Modes for

MPU/DSP/TC

D

On-Chip Scan-Based Emulation Logic

D

IEEE Std 1149.1

(JTAG) Boundary Scan

Logic

D

Two 289-Ball Ball Grid Array Package

Options (GZG and GDY Suffixes)

TMS320C55x and C55x are trademarks of Texas Instruments.

ARM9TDMI is a trademark of ARM Limited.

Thumb is a registered trademark of ARM Limited.

MICROWIRE is a trademark of National Semiconductor Corporation.

1-Wire is a registered trademark of Dallas Semiconductor Corporation.

IEEE Standard 1149.1-1990 Standard Test-Access Port and Boundary Scan Architecture.

Introduction

16

August 2002 - Revised August 2004

SPRS197D

2

Introduction

This section describes the main features of the OMAP5910 device, lists the terminal assignments, and

describes the function of each terminal. This data manual also provides a detailed description section,

electrical specifications, parameter measurement information, and mechanical data about the available

packaging.

2.1

Description

The OMAP5910 is a highly integrated hardware and software platform, designed to meet the application

processing needs of next-generation embedded devices.

The OMAP platform enables OEMs and ODMs to quickly bring to market devices featuring rich user

interfaces, high processing performance, and long battery life through the maximum flexibility of a fully

integrated mixed processor solution.

The dual-core architecture provides benefits of both DSP and RISC technologies, incorporating a

TMS320C55x DSP core and a high-performance TI925T ARM core.

The OMAP5910 device is designed to run leading open and embedded RISC-based operating systems, as

well as the Texas Instruments (TI) DSP/BIOS software kernel foundation, and is available in a 289-ball

MicroStar BGA package.

The OMAP5910 is targeted at the following applications:

�

Applications processing devices

�

Mobile communications

-

802.11

-

Bluetooth wireless technology

-

GSM (including GPRS and EDGE)

-

CDMA

-

Proprietary government and other

�

Video and image processing (MPEG4, JPEG, Windows Media Video, etc.)

�

Advanced speech applications (text-to-speech, speech recognition)

�

Audio processing (MPEG-1 Audio Layer3 [MP3], AMR, WMA, AAC, and other GSM speech codecs)

�

Graphics and video acceleration

�

Generalized web access

�

Data processing (fax, encryption/decryption, authentication, signature verification and watermarking)

2.1.1 TMS320C55x DSP Core

The DSP core of the OMAP5910 device is based on the TMS320C55x DSP generation CPU processor core.

The C55x DSP architecture achieves high performance and low power through increased parallelism and total

focus on reduction in power dissipation. The CPU supports an internal bus structure composed of one program

bus, three data read buses, two data write buses, and additional buses dedicated to peripheral and DMA

activity. These buses provide the ability to perform up to three data reads and two data writes in a single cycle.

In parallel, the DMA controller can perform up to two data transfers per cycle independent of the CPU activity.

OMAP, DSP/BIOS, and MicroStar BGA are trademarks of Texas Instruments.

Bluetooth is a trademark owned by Bluetooth SIG, Inc.

Windows is a registered trademark of Microsoft Corporation.

Other trademarks are the property of their respective owners.

Introduction

17

August 2002 - Revised August 2004

SPRS197D

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication

in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of

the ALUs is under instruction set control, providing the ability to optimize parallel activity and power

consumption. These resources are managed in the address unit (AU) and data unit (DU) of the C55x CPU.

The C55x DSP generation supports a variable byte width instruction set for improved code density. The

instruction unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions

for the program unit (PU). The program unit decodes the instructions, directs tasks to AU and DU resources,

and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution

of conditional instructions. The OMAP5910 DSP core also includes a 24K-byte instruction cache to minimize

external memory accesses, improving data throughput and conserving system power.

2.1.1.1

DSP Tools Support

The 55x DSP core is supported by the industry's leading eXpressDSP software environment including the

Code Composer Studio integrated development environment, DSP/BIOS software kernel foundation, the

TMS320 DSP Algorithm Standard, and the industry's largest third-party network. Code Composer Studio

features code generation tools including a C-Compiler, Visual Linker, simulator, Real-Time Data Exchange

(RTDX), XDS510 emulation device drivers, and Chip Support Libraries (CSL). DSP/BIOS is a scalable

real-time software foundation available for no cost to users of Texas Instruments' DSP products providing a

preemptive task scheduler and real-time analysis capabilities with very low memory and megahertz overhead.

The TMS320 DSP Algorithm Standard is a specification of coding conventions allowing fast integration of

algorithms from different teams, sites, or third parties into the application framework. Texas Instruments'

extensive DSP third-party network of over 400 providers brings focused competencies and complete solutions

to customers.

2.1.1.2

DSP Software Support

Texas Instruments has also developed foundation software available for the 55x DSP core. The C55x DSP

Library (DSPLIB) features over 50 C-callable software kernels (FIR/IIR filters, Fast Fourier Transforms (FFTs),

and various computational functions). The DSP Image/Video Processing Library (IMGLIB) contains over

20 software kernels highly optimized for C55x DSPs and is compiled with the latest revision of the C55x DSP

code generation tools. These imaging functions support a wide range of applications that include

compression, video processing, machine vision, and medical imaging.

2.1.2 TI-Enhanced TI925T RISC Processor

The MPU core is a TI925T reduced instruction set computer (RISC) processor. The TI925T is a 32-bit

processor core that performs 32-bit or 16-bit instructions and processes 32-bit, 16-bit, or 8-bit data. The core

uses pipelining so that all parts of the processor and memory system can operate continuously.

The MPU core incorporates:

�

A coprocessor 15 (CP15) and protection module

�

Data and program Memory Management Units (MMUs) with table look-aside buffers.

�

A separate 16K-byte instruction cache and 8K-byte data cache. Both are two-way associative with virtual

index virtual tag (VIVT).

�

A 17-word write buffer (WB)

The OMAP5910 device uses the TI925T core in little endian mode only.

To reduce effective memory access time, the TI925T has an instruction cache, a data cache, and a write buffer.

In general, these are transparent to program execution.

eXpressDSP, Code Composer Studio, TMS320, RTDX, and XDS510 are trademarks of Texas Instruments.

Introduction

18

August 2002 - Revised August 2004

SPRS197D

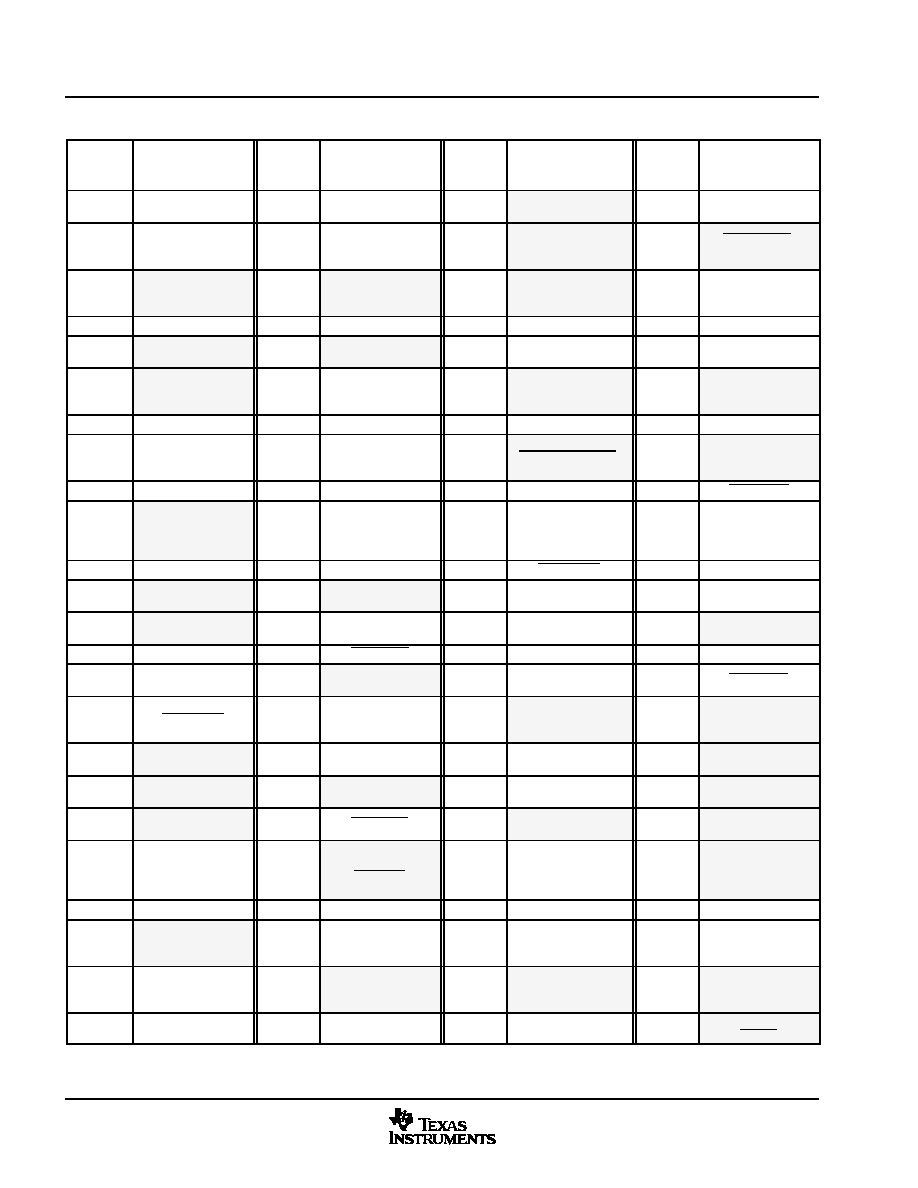

2.2

Terminal Assignments

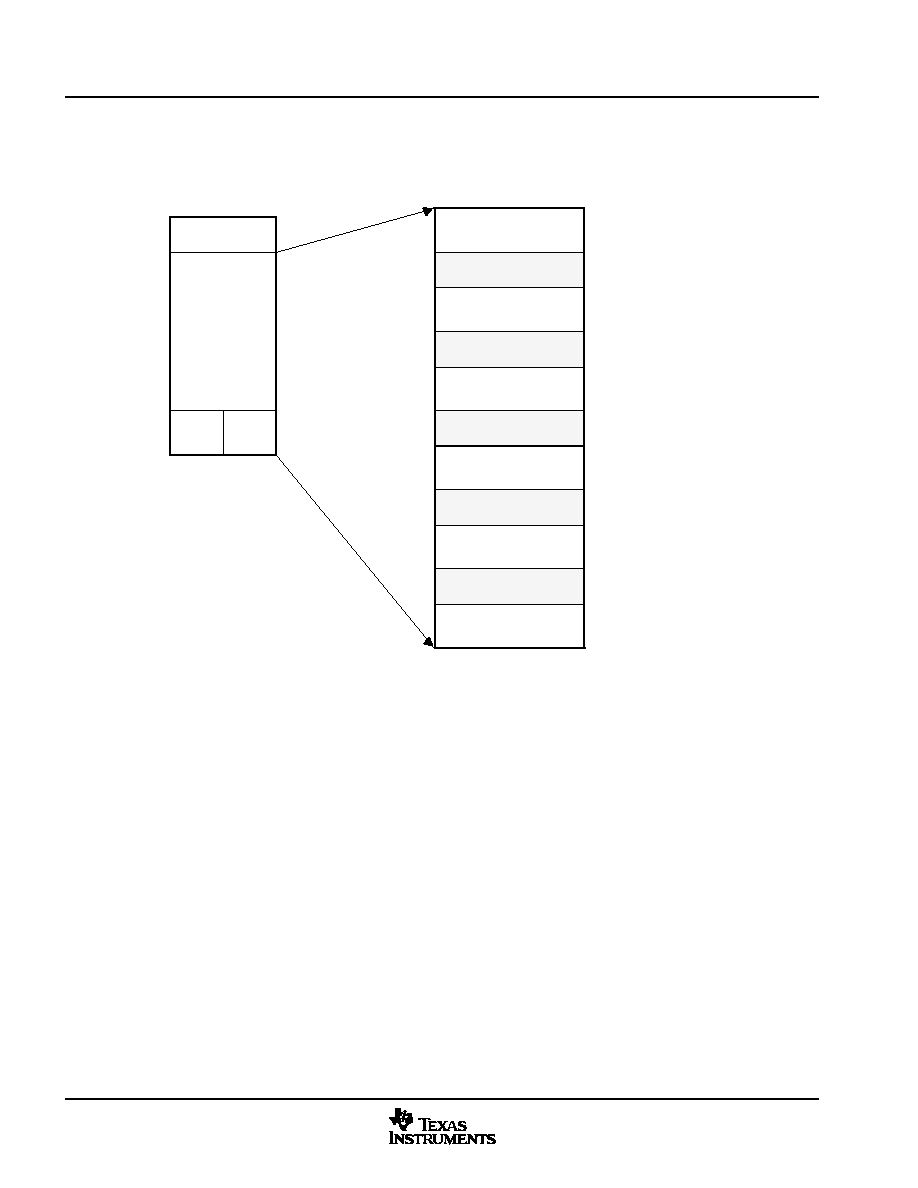

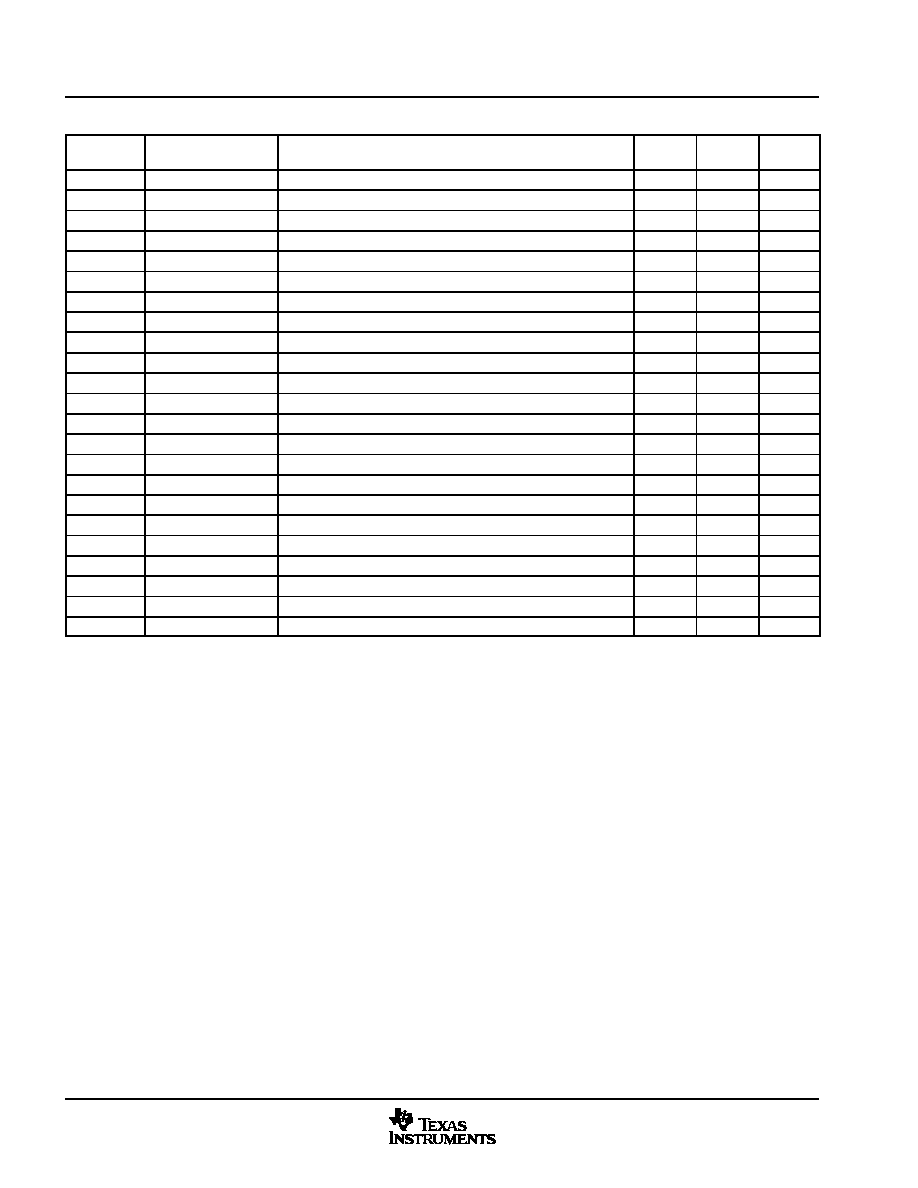

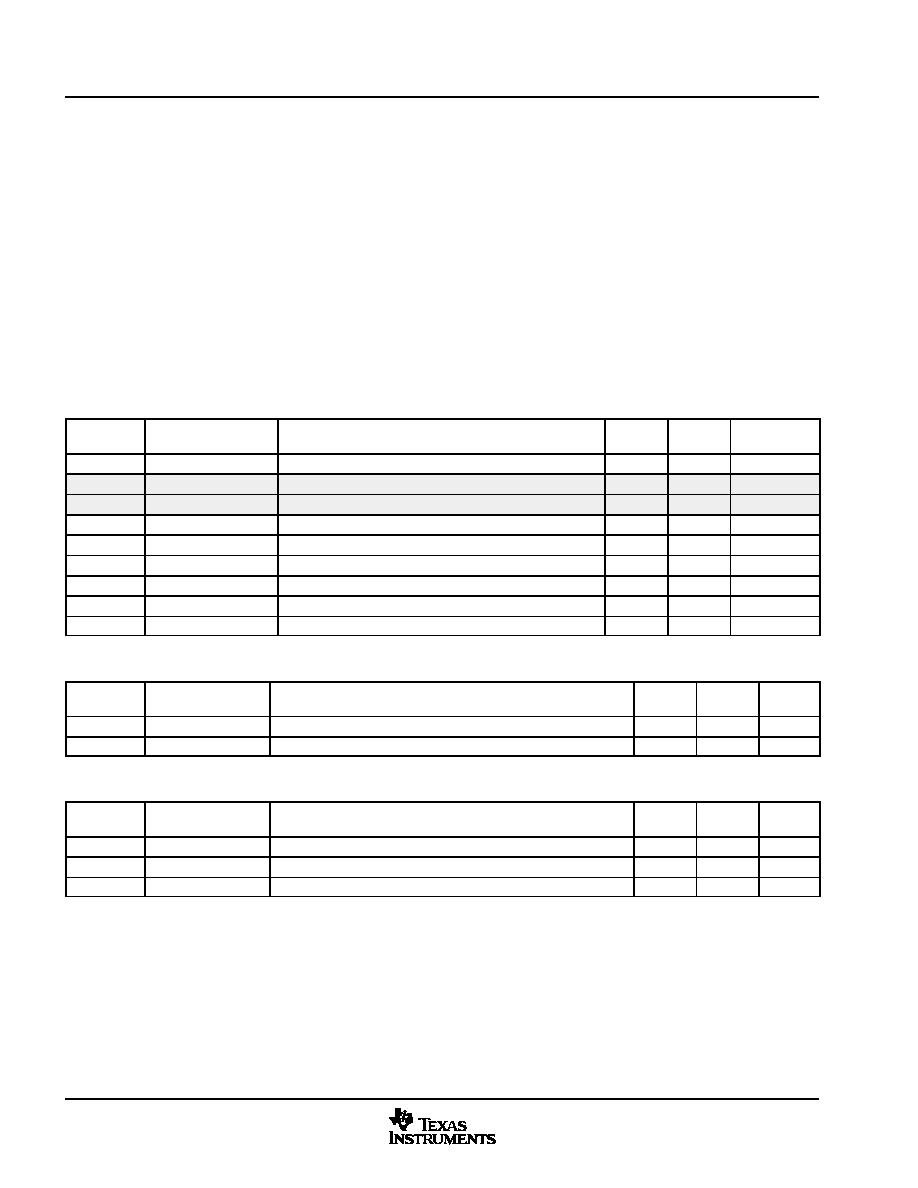

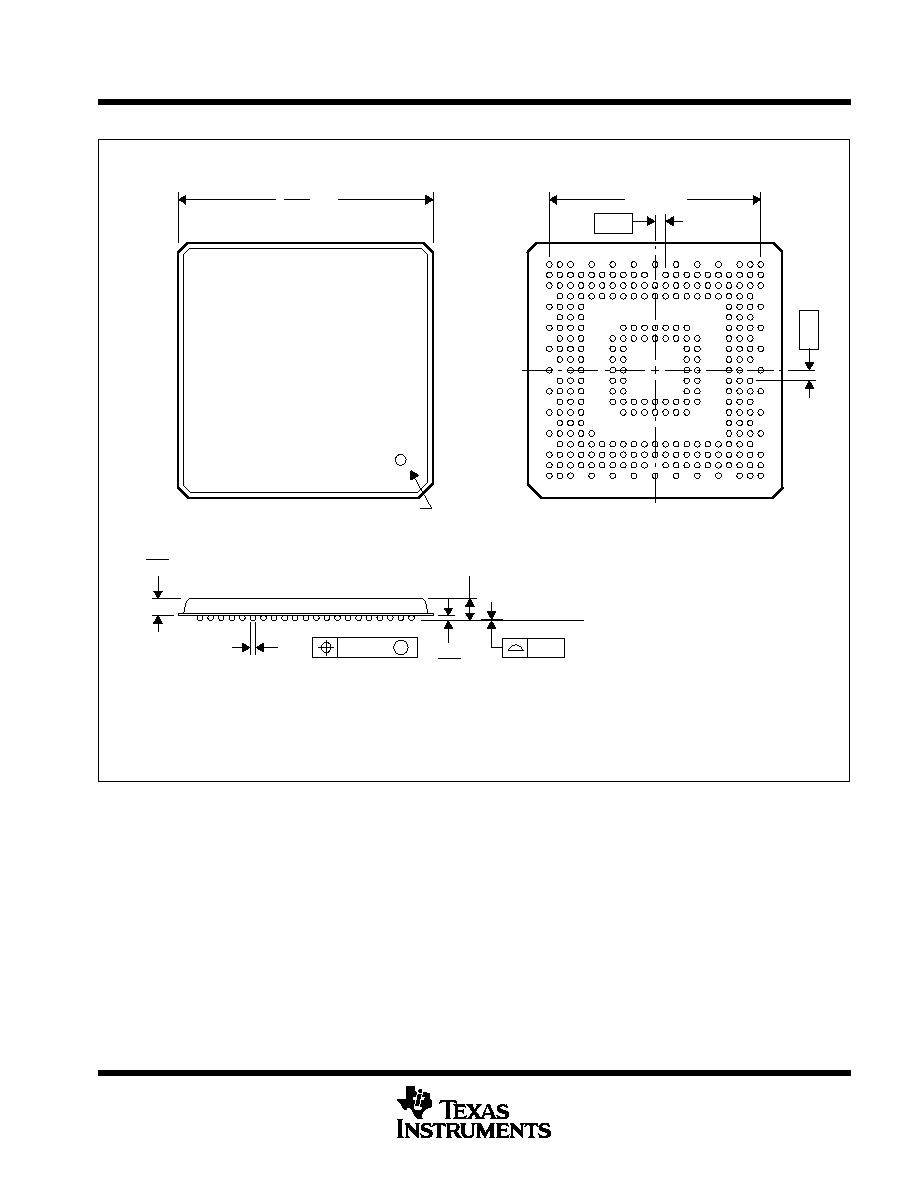

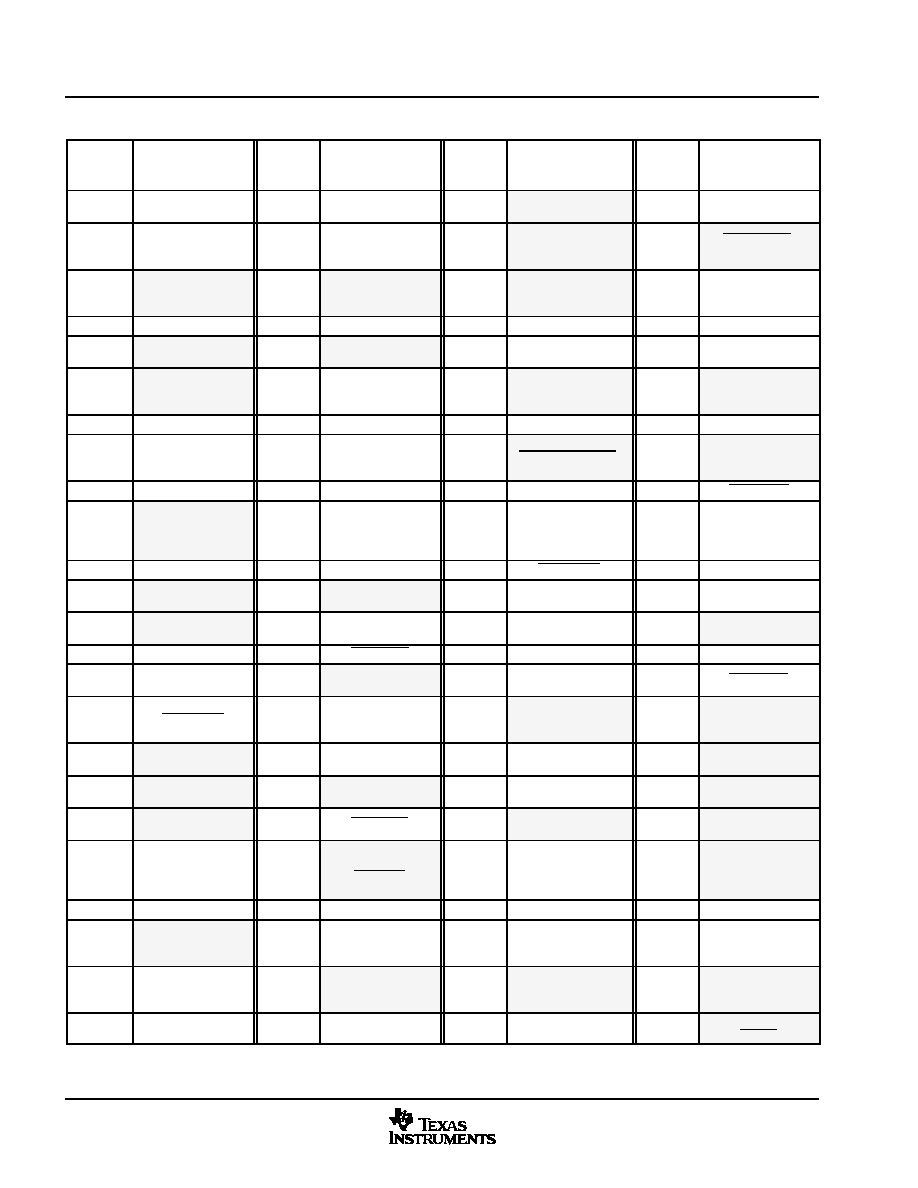

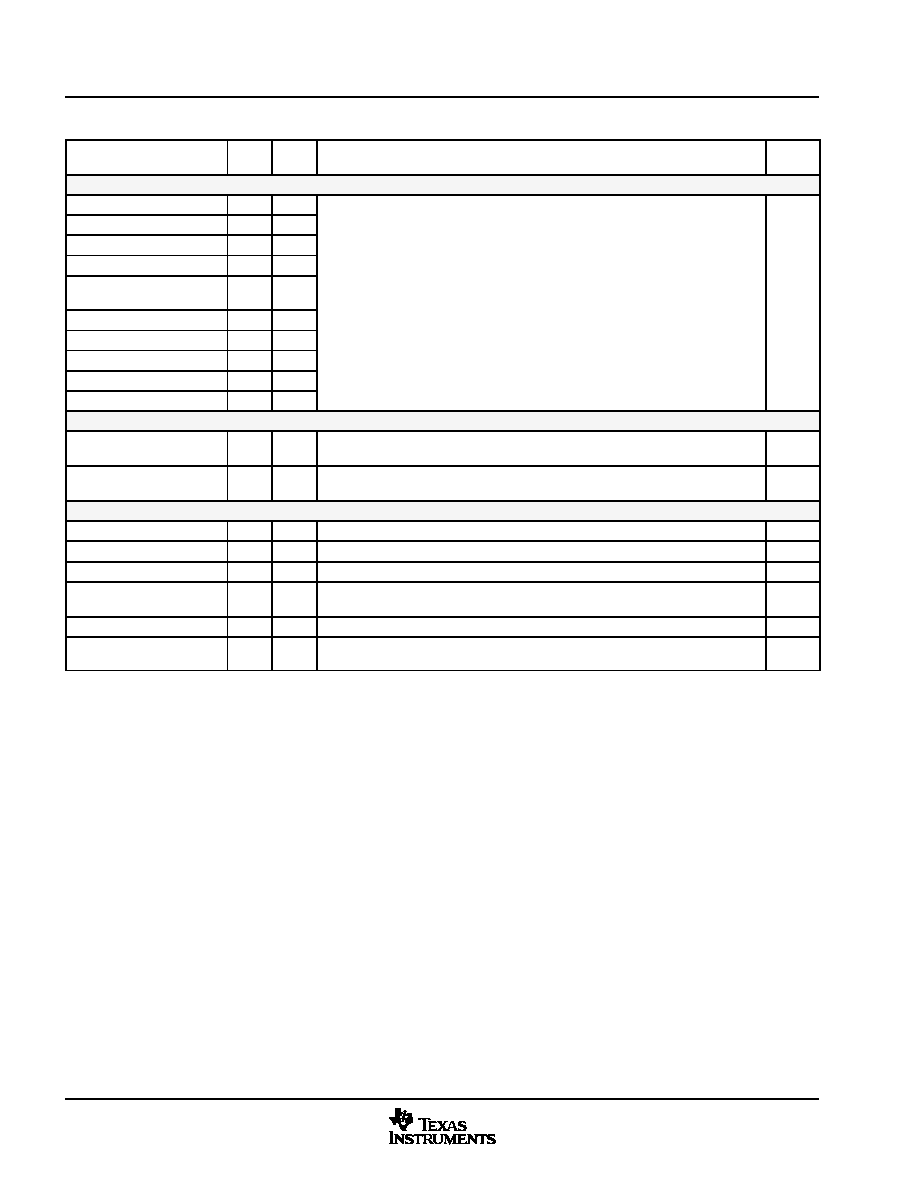

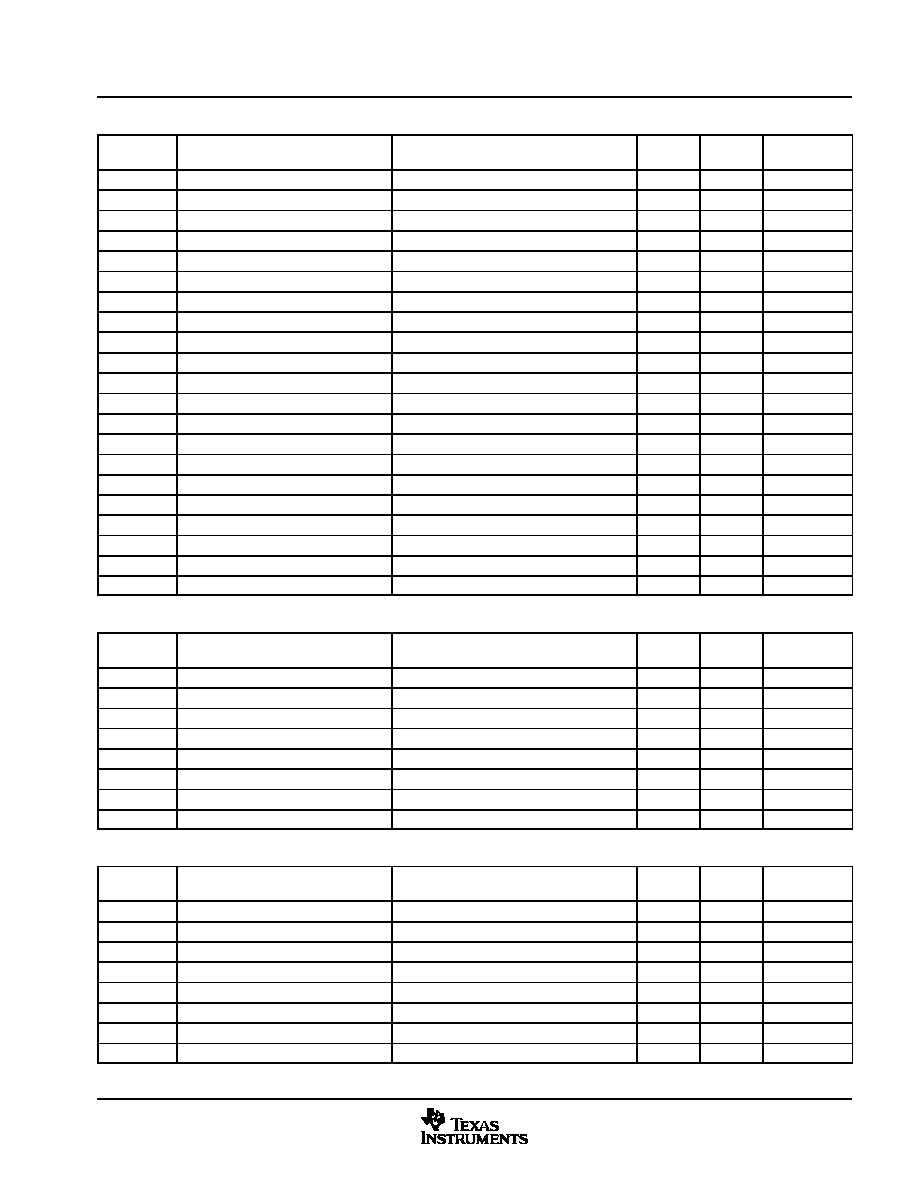

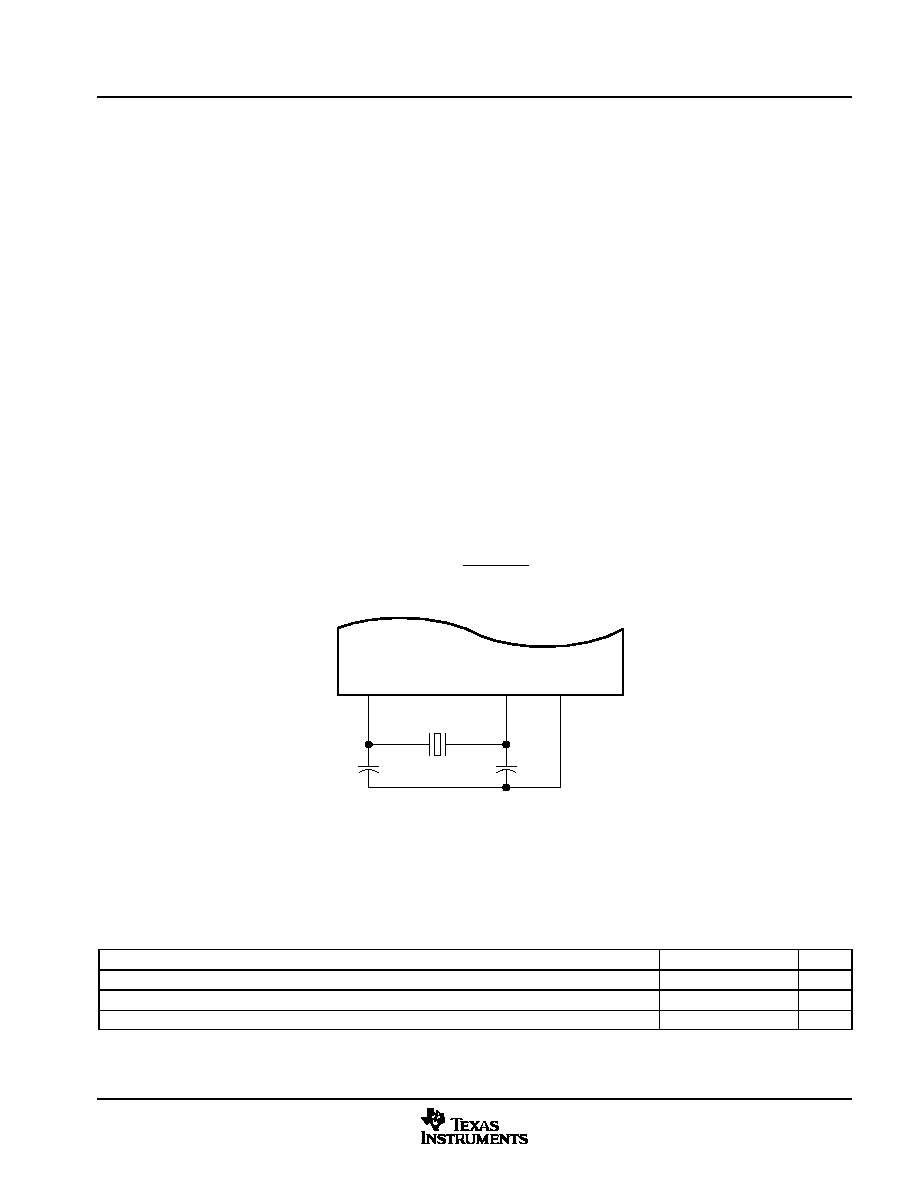

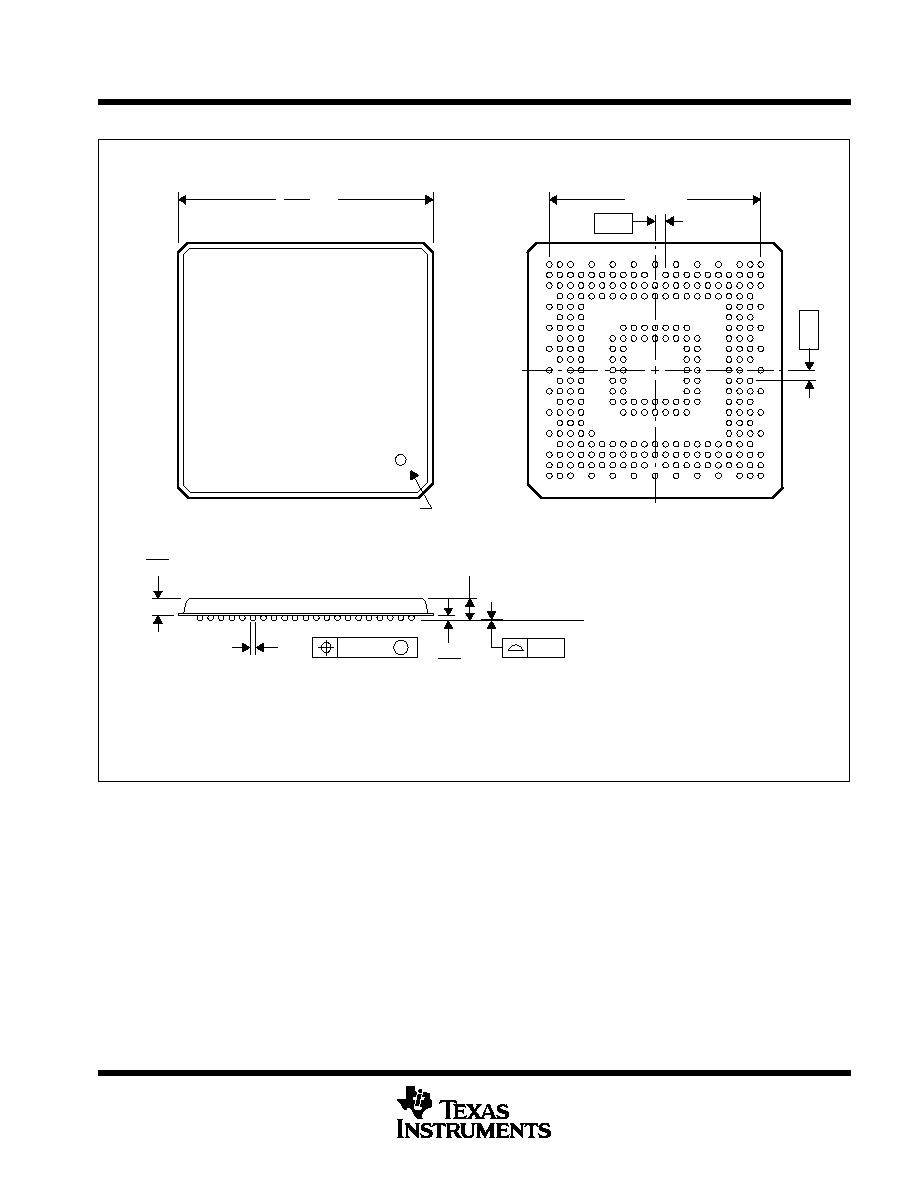

Figure 2-1 illustrates the ball locations for the 289-ball GZG ball grid array (BGA) package and is used in

conjunction with Table 2-1 to locate signal names and ball grid numbers. GZG BGA ball numbers in Table 2-1

are read from left-to-right, top-to-bottom.

8

L

B

A

1

F

D

C

E

H

K

G

J

3

2

4

7

5

6

R

M

P

N

V

T

U

W

AA

Y

15

11

9

10

13

12 14

18

17

16

21

19

20

Figure 2-1. OMAP5910 GZG MicroStar BGA Package (Bottom View)

In Table 2-1, signals with multiplexed functions are separated with forward slashes as follows:

�

signal1/signal2/signal3 (for example, GPIO11/HDQ)

Signals which are associated with specific peripherals are denoted by using the peripheral name, followed

by a period, and then the signal name; as follows:

�

peripheral1.signal1 (for example, MCBSP1.DR)

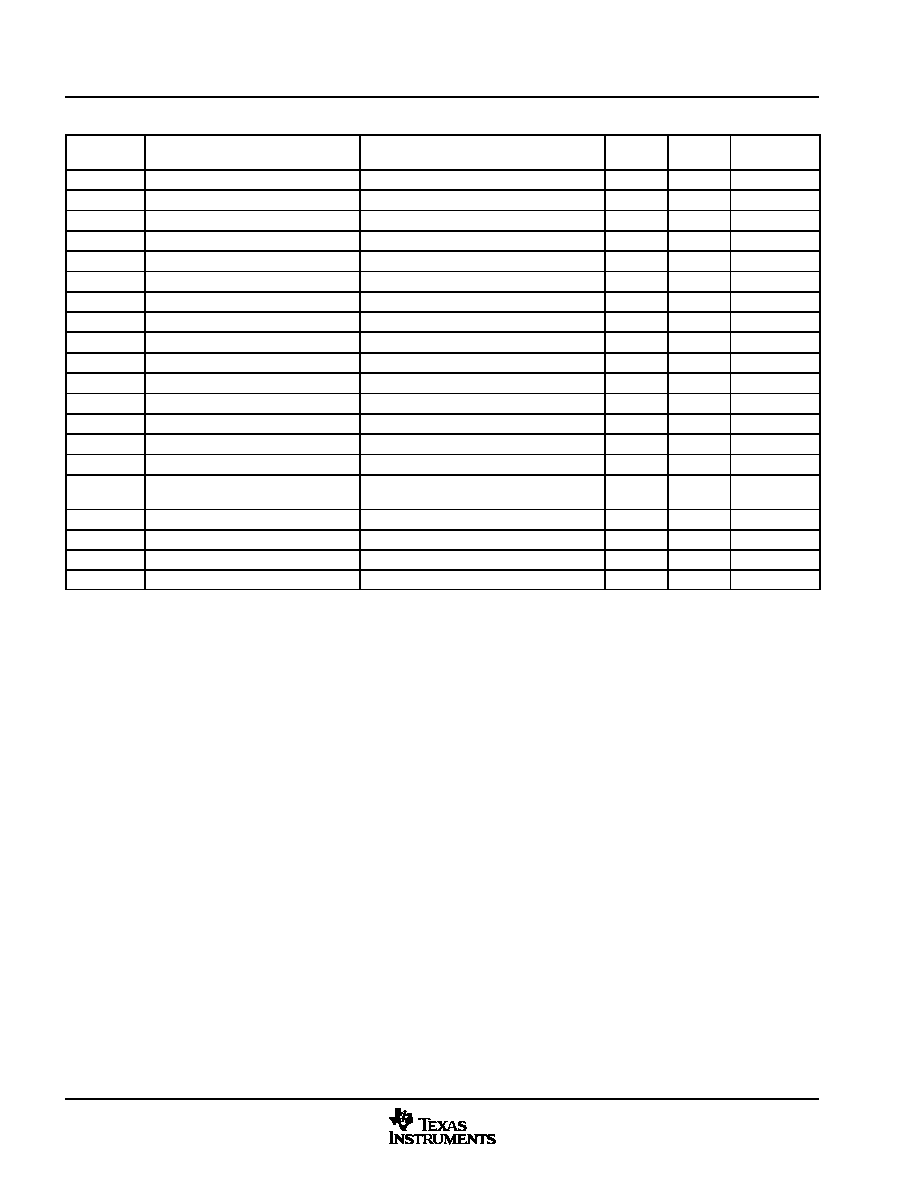

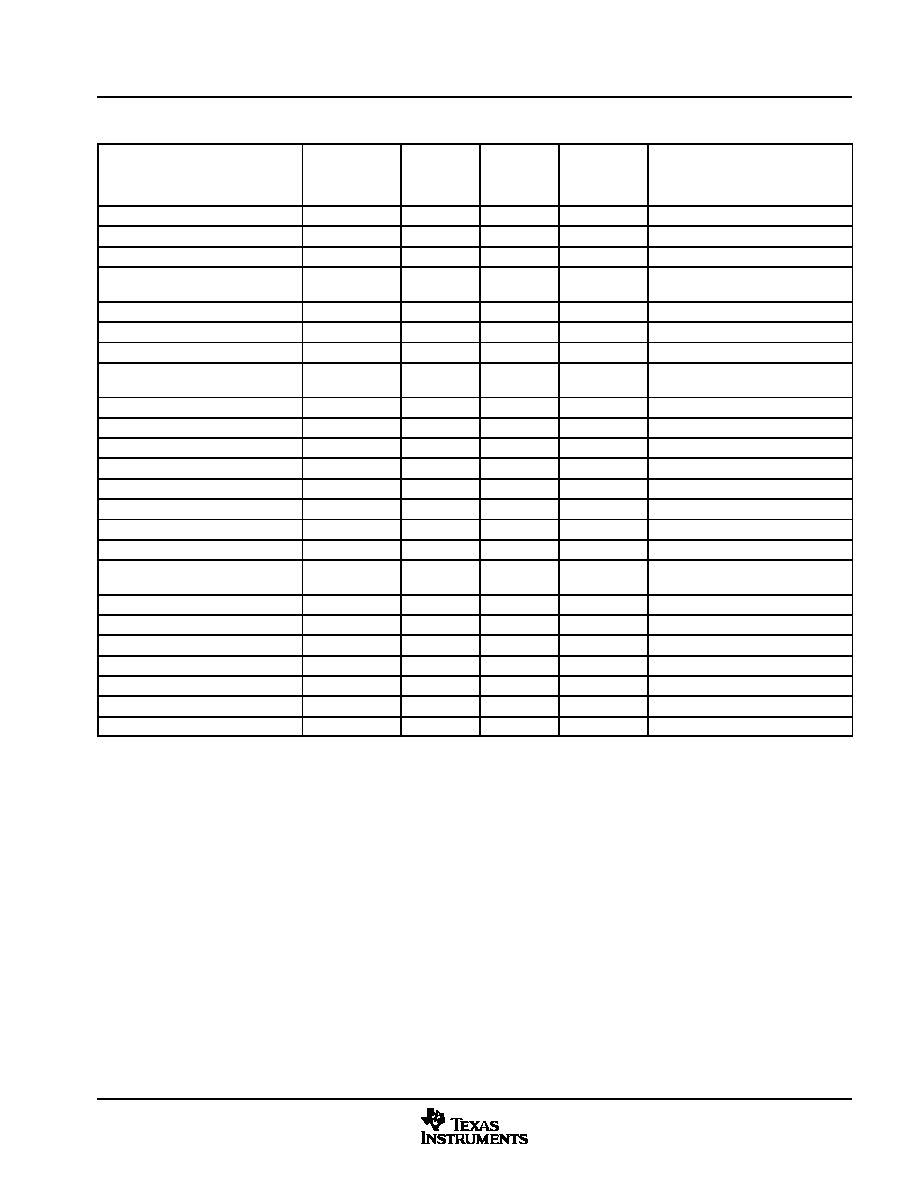

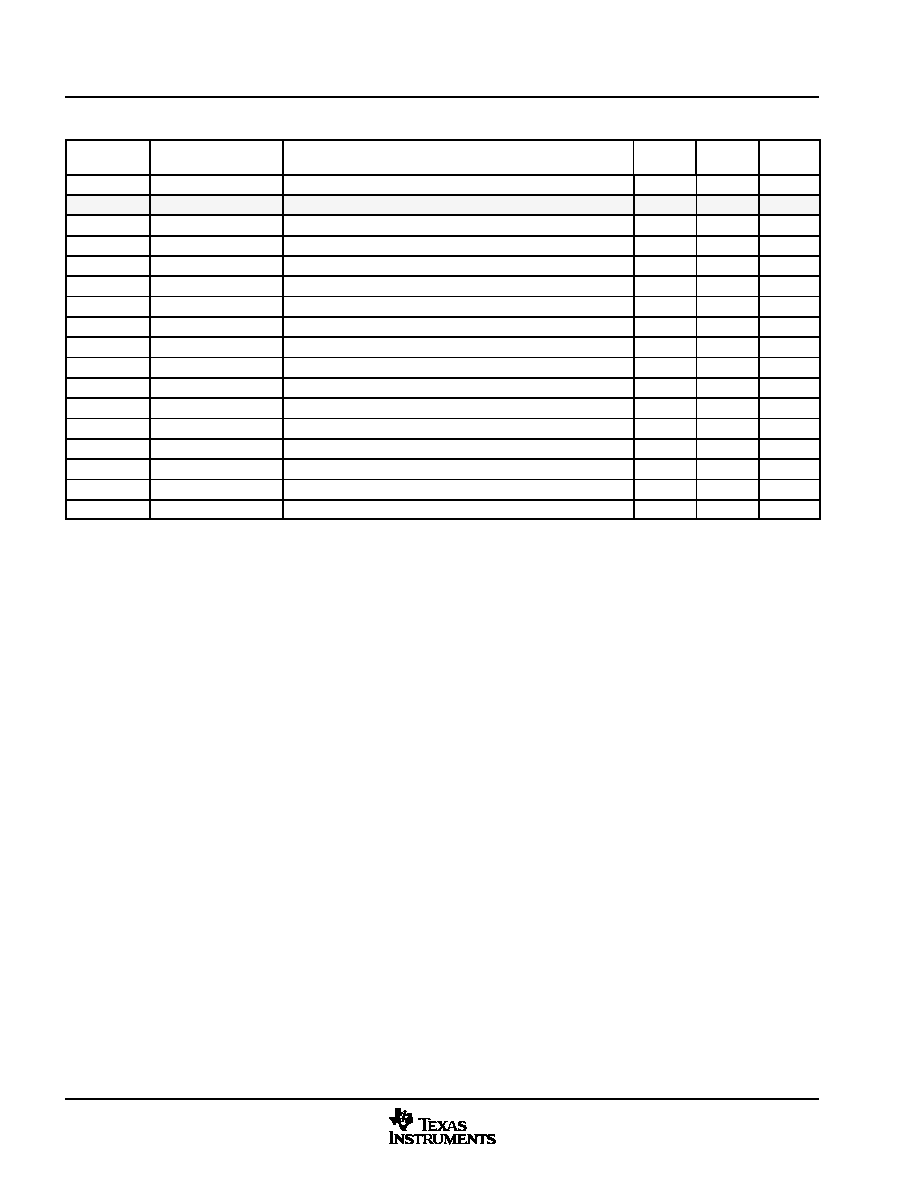

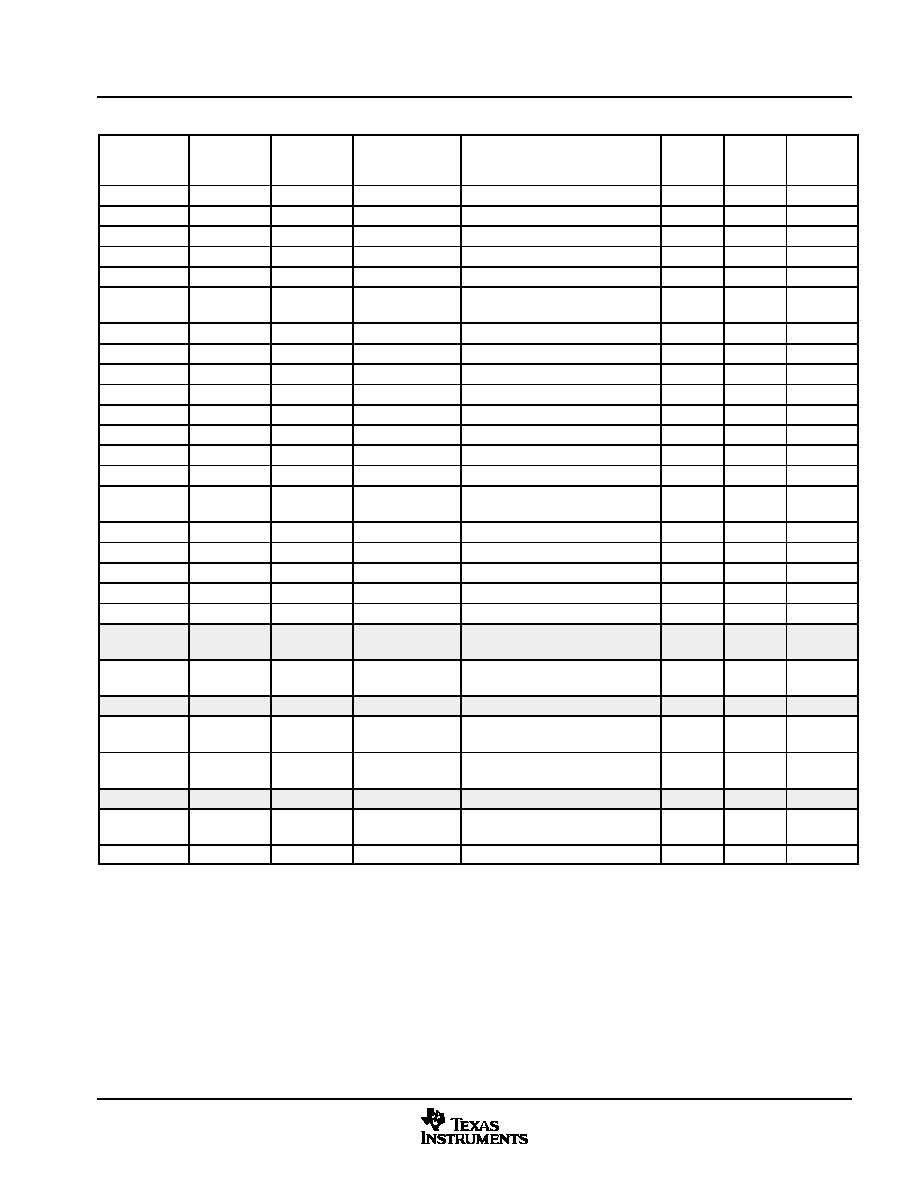

Table 2-1. GZG BGA Terminal Assignments

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

A1

DV

DD4

A2

SDRAM.RAS

A3

CV

DD1

A5

DV

DD4

A7

DV

DD4

A9

CV

DD

A11

V

SS

A13

V

SS

A15

DV

DD1

A17

LCD.P[13]

A19

DV

DD1

A20

LCD.P[5]

A21

V

SS

B1

V

SS

B2

V

SS

B3

SDRAM.DQML

B4

SDRAM.D[13]

B5

V

SS

B6

SDRAM.D[8]

B7

V

SS

B8

SDRAM.D[4]

B9

SDRAM.D[0]

B10

DV

DD4

B12

DV

DD4

B13

CV

DD3

B14

SDRAM.A[0]

B15

LCD.AC

B16

V

SS

B17

LCD.P[11]

B18

V

SS

B19

LCD.P[6]

B20

CV

DD3

B21

LCD.P[1]

C1

FLASH.A[3]

C2

DV

DD5

C3

SDRAM.WE

C4

SDRAM.D[14]

C5

SDRAM.D[11]

C6

SDRAM.D[9]

C7

SDRAM.D[6]

C8

SDRAM.D[2]

C9

SDRAM.CLK

C10

SDRAM.BA[0]

C11

SDRAM.A[10]

C12

SDRAM.A[7]

C13

SDRAM.A[4]

C14

SDRAM.A[1]

C15

LCD.PCLK

See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with ocillator circuits.

MicroStar BGA is a trademark of Texas Instruments.

Introduction

19

August 2002 - Revised August 2004

SPRS197D

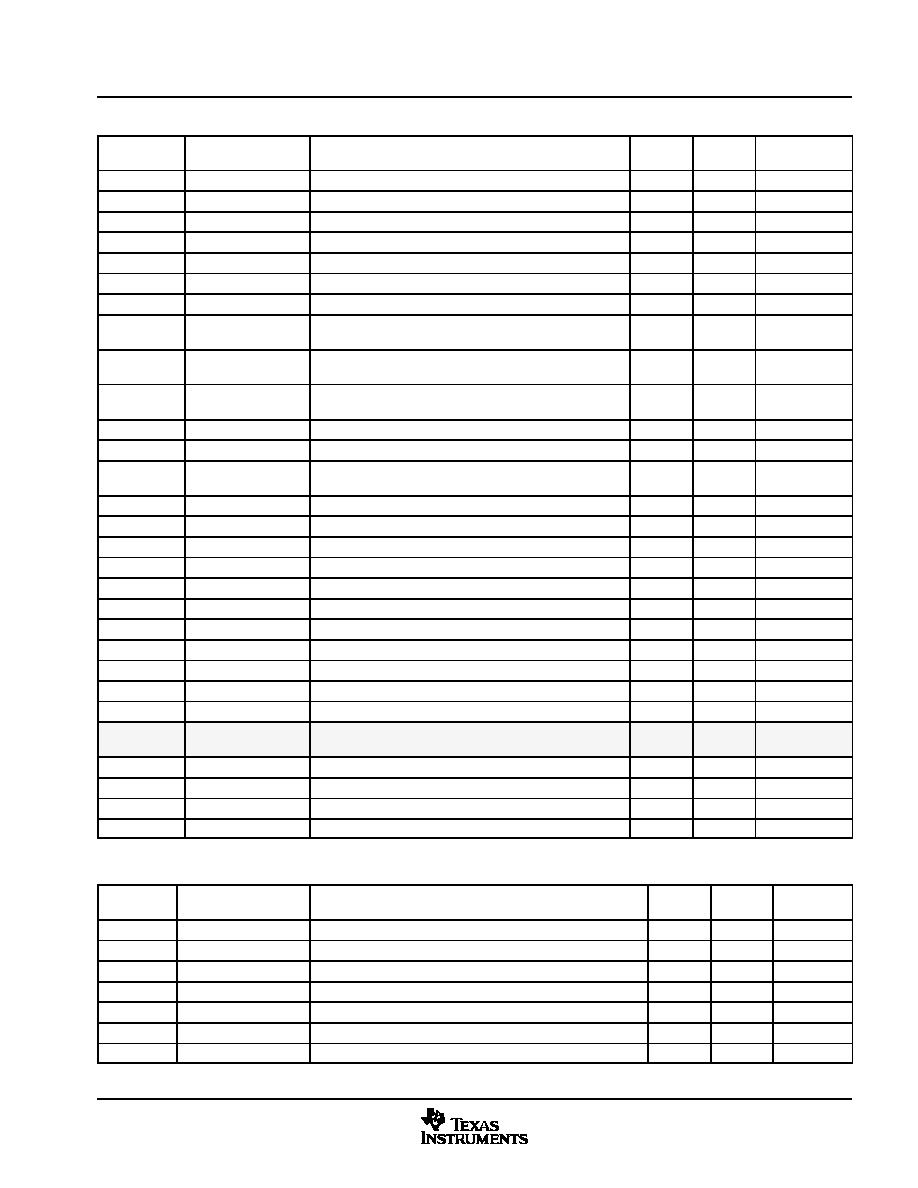

Table 2-1. GZG BGA Terminal Assignments (Continued)

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

C16

LCD.P[14]

C17

LCD.P[10]

C18

LCD.P[7]

C19

LCD.P[2]

C20

KB.C[5]

C21

KB.C[4]

D2

FLASH.A[5]

D3

FLASH.A[2]

D4

SDRAM.DQMU

D5

SDRAM.D[15]

D6

SDRAM.D[12]

D7

SDRAM.D[7]

D8

SDRAM.D[5]

D9

SDRAM.CKE

D10

SDRAM.BA[1]

D11

SDRAM.A[9]

D12

SDRAM.A[6]

D13

SDRAM.A[3]

D14

LCD.VS

D15

LCD.P[15]

D16

LCD.P[9]

D17

LCD.P[8]

D18

LCD.P[0]

D19

KB.C[2]

D20

KB.C[1]

E1

DV

DD5

E2

V

SS

E3

FLASH.A[7]

E4

FLASH.A[4]

E5

RSVD

E18

KB.C[3]

E19

KB.R[4]

E20

KB.R[3]

E21

DV

DD1

F2

CV

DD

F3

FLASH.A[9]

F4

FLASH.A[6]

F18

KB.C[0]

F19

KB.R[1]

F20

V

SS

G1

V

SS

G2

FLASH.A[12]

G3

FLASH.A[11]

G4

FLASH.A[10]

G8

SDRAM.D[3]

G9

SDRAM.D[1]

G10

SDRAM.A[12]

G11

SDRAM.A[8]

G12

SDRAM.A[2]

G13

LCD.P[12]

G14

LCD.P[3]

G18

KB.R[0]

G19

PWRON_RESET

G20

MCBSP1.CLKS

G21

MCBSP1.CLKX

H2

DV

DD5

H3

FLASH.A[15]

H4

FLASH.A[14]

H7

FLASH.RDY

H8

SDRAM.D[10]

H9

SDRAM.CAS

H10

SDRAM.A[11]

H11

SDRAM.A[5]

H12

LCD.HS

H13

LCD.P[4]

H14

KB.R[2]

H15

MCBSP1.FSX/

MCBSP1.DX

H18

MCBSP1.DX/

MCBSP1.FSX

H19

CAM.EXCLK/

ETM.SYNC/

UWIRE.SDO

H20

MCBSP1.DR

J1

FLASH.A[20]

J2

FLASH.A[17]

J3

FLASH.A[19]

J4

FLASH.A[18]

J7

FLASH.A[8]

J8

FLASH.A[1]

J14

CAM.D[5]/

ETM.D[5]/

UWIRE.SDI

J15

CAM.LCLK/

ETM.CLK/

UWIRE.SCLK

J18

CAM.D[7]/

ETM.D[7]/

UWIRE.CS0

J19

CAM.D[6]/

ETM.D[6]/

UWIRE.CS3

J20

V

SS

J21

CV

DD3

K2

V

SS

K3

FLASH.A[23]

K4

FLASH.A[22]

K7

FLASH.A[16]

K8

FLASH.A[13]

K14

CAM.D[1]/ETM.D[1]/

UART3.RTS

K15

CAM.D[2]/

ETM.D[2]/

UART3.CTS

K18

CAM.D[4]/

ETM.D[4]/

UART3.TX

K19

CAM.D[3]/

ETM.D[3]/

UART3.RX

K20

V

SS

L1

DV

DD5

L3

FLASH.BE[0]

L4

FLASH.ADV

L7

FLASH.A[24]

L8

FLASH.A[21]

L14

UART3.RX/PWL/

UART2.RX

L15

CAM.HS/

ETM.PSTAT[1]/

UART2.CTS

L18

CAM.VS/

ETM.PSTAT[2]

L19

CAM.D[0]/

ETM.D[0]/

MPUIO12

L21

DV

DD1

M2

CV

DD4

M3

FLASH.CS1

M4

FLASH.CS2/

FLASH.BAA

M7

FLASH.CS0

M8

FLASH.BE[1]

M14

GPIO2/

SPI.CLK

M15

GPIO7/

MMC.DAT2

M18

UART3.TX/

PWT/

UART2.TX

M19

CAM.RSTZ/

ETM.PSTAT[0]/

UART2.RTS

M20

GPIO15/

KB.R[7]

N1

V

SS

N2

FLASH.D[1]

N3

FLASH.CLK

N4

FLASH.D[0]

N7

FLASH.D[2]

N8

FLASH.CS3

N14

UWIRE.CS0/

MCBSP3.CLKX

N15

MPUIO2/

EXT_DMA_REQ0

N18

GPIO12/

MCBSP3.FSX

N19

GPIO13/

KB.R[5]

N20

GPIO11/

HDQ

N21

GPIO14/

KB.R[6]

P2

FLASH.D[3]

P3

DV

DD5

P4

FLASH.D[4]

P7

FLASH.D[5]

See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with ocillator circuits.

Introduction

20

August 2002 - Revised August 2004

SPRS197D

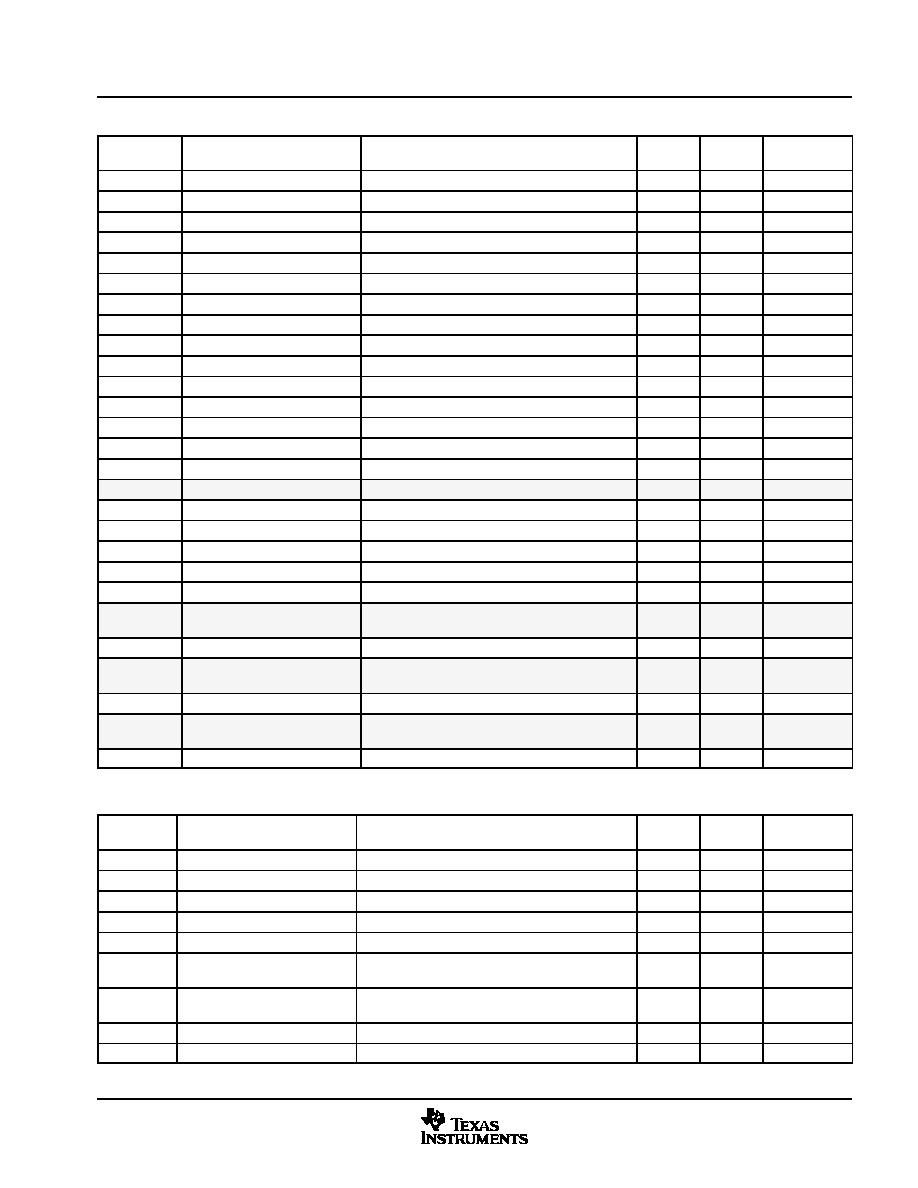

Table 2-1. GZG BGA Terminal Assignments (Continued)

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

P8

FLASH.D[11]

P9

USB.DP

P10

MCBSP2.DR/

MCBSP2.DX

P11

MMC.CMD/SPI.DO

P12

CV

DD

P13

CLK32K_IN

P14

RST_HOST_OUT/

MCBSP3.DX/

USB1.SE0

P15

UWIRE.CS3/

KB.C[6]

P18

GPIO3/

SPI.CS3/

MCBSP3.FSX/LED1

P19

GPIO6/

SPI.CS1/

MCBSP3.FSX

P20

GPIO4/

SPI.CS2/

MCBSP3.FSX

R1

DV

DD5

R2

FLASH.D[6]

R3

FLASH.D[7]

R4

FLASH.D[8]

R8

USB.DM

R9

UART2.RX/

USB2.VM

R10

MCLKREQ/EXT_

MASTER_REQ

R11

MMC.DAT0/SPI.DI

R12

OSC32K_OUT

R13

BCLKREQ/

UART3.CTS/

UART1.DSR

R14

UART1.CTS

R18

GPIO0/

SPI.RDY/

USB.VBUS

R19

GPIO1/

UART3.RTS

R20

CV

DD3

R21

V

SS

T2

FLASH.D[9]

T3

FLASH.D[10]

T4

FLASH.D[14]

T18

I2C.SCL

T19

MPUIO4/

EXT_DMA_REQ1/

LED2

T20

MPUIO5/

LOW_PWR

U1

FLASH.D[12]

U2

V

SS

U3

FLASH.D[13]

U4

FLASH.OE

U18

UWIRE.SDI/

UART3.DSR/

UART1.DSR/

MCBSP3.DR

U19

MPUIO1

U20

V

SS

U21

DV

DD1

V2

DV

DD5

V3

FLASH.D[15]

V4

FLASH.WP

V5

V

SS

V6

UART2.TX/

USB2.TXD

V7

MCBSP2.CLKR/

GPIO11

V8

MPUIO3

V9

MCSI2.SYNC/

GPIO7

V10

MMC.DAT1/

MPUIO7

V11

MMC.CLK

V12

V

SS

V13

MCSI1.SYNC/

USB1.VP

V14

UART1.RX

V15

MPU_RST

V16

EMU0

V17

TMS

V18

CONF

V19

UWIRE.SCLK/

KB.C[7]

V20

I2C.SDA

W1

FLASH.RP

W2

FLASH.WE

W3

OSC1_OUT

W4

USB.PUEN/

USB.CLKO

W5

UART2.RTS/

USB2.SE0/

MPUIO5

W6

MCBSP2.FSR/

GPIO12

W7

MCBSP2.FSX

W8

GPIO9

W9

MCSI2.DOUT/

USB2.TXEN

W10

MMC.DAT2/

MPUIO11

W11

MMC.DAT3/

MPUIO6

W12

OSC32K_IN

W13

MCSI1.DIN/

USB1.RCV

W14

MCSI1.DOUT/

USB1.TXD

W15

RST_OUT

W16

MCBSP3.CLKX/

USB1.TXEN

W17

EMU1

W18

TCK

W19

BFAIL/

EXT_FIQ

W20

V

SS

W21

UWIRE.SDO/

UART3.DTR/

UART1.DTR/

MCBSP3.DX

Y1

CV

DD2

Y2

OSC1_IN

Y3

V

SS

Y4

UART2.BCLK

Y5

UART2.CTS/

USB2.RCV/

GPIO7

Y6

MCBSP2.CLKX

Y7

DV

DD3

Y8

GPIO8

Y9

MCLK

Y10

MCSI2.CLK/

USB2.SUSP

Y12

CLK32K_OUT/

MPUIO0/

USB1.SPEED

Y13

BCLK/

UART3.RTS/

UART1.DTR

Y14

UART1.TX

Y15

V

SS

Y16

DV

DD1

Y17

STAT_VAL/

WKUP

See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with ocillator circuits.

Introduction

21

August 2002 - Revised August 2004

SPRS197D

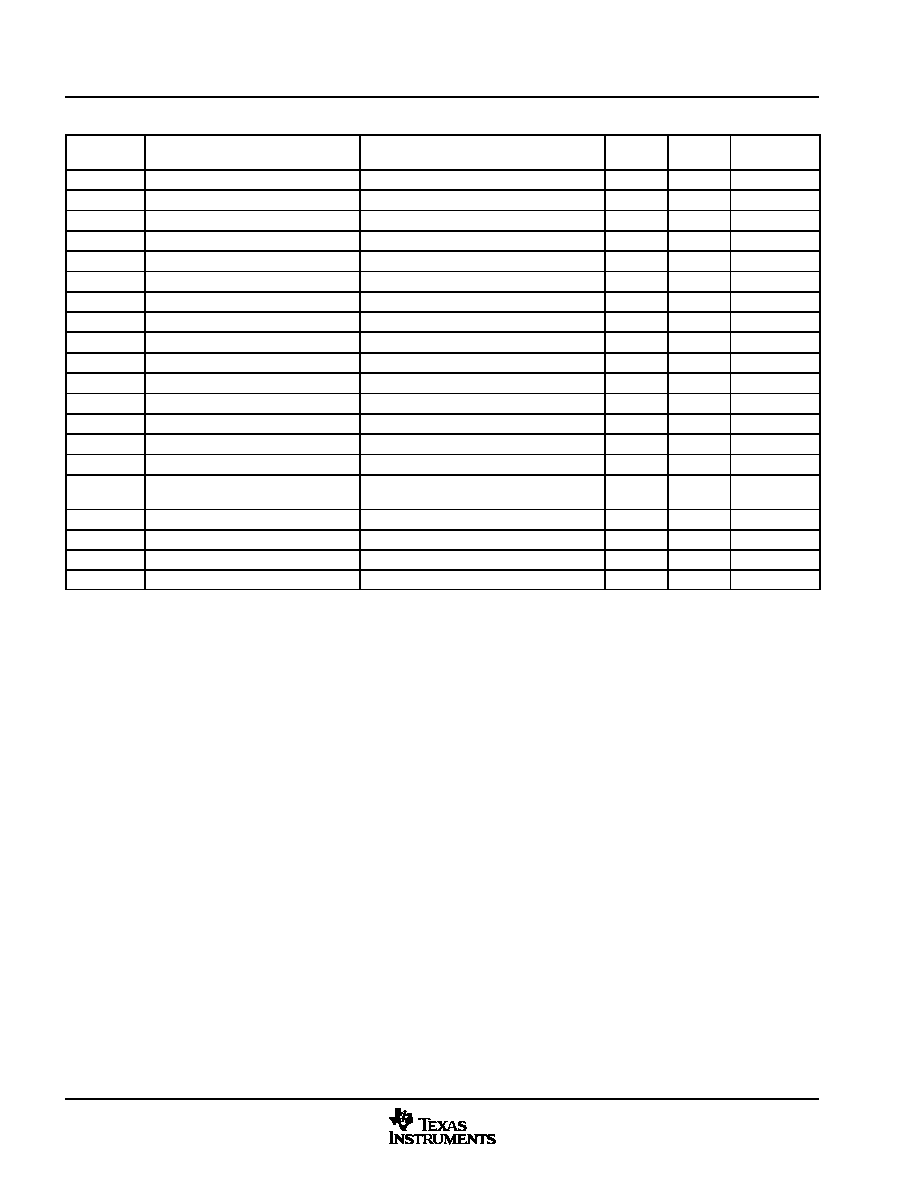

Table 2-1. GZG BGA Terminal Assignments (Continued)

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

GZG

BGA

BALL #

SIGNAL

Y18

TRST

Y19

TDI

Y20

CV

DD

Y21

CV

DDA

AA1

V

SS

AA2

DV

DD2

AA3

CV

DD2

AA5

MCBSP2.DX/

MCBSP2.DR

AA7

V

SS

AA9

MCSI2.DIN/

USB2.VP

AA11

DV

DD1

AA13

MCSI1.CLK/

USB1.VM

AA15

UART1.RTS

AA17

MPU_BOOT/

MCBSP3.DR/

USB1.SUSP

AA19

TDO

AA20

CLK32K_CTRL

AA21

V

SS

See Section 5.6.1 and Section 5.6.2 for special V

SS

considerations with ocillator circuits.

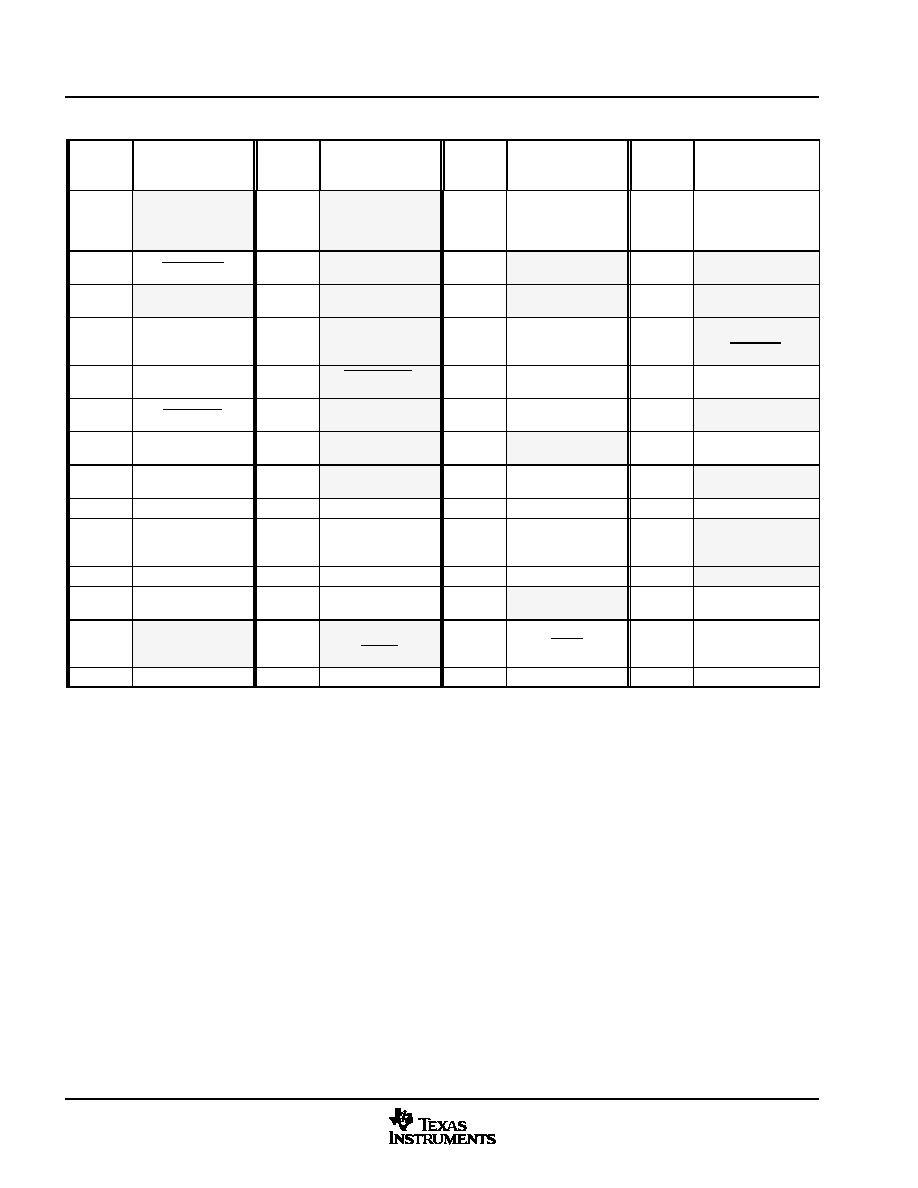

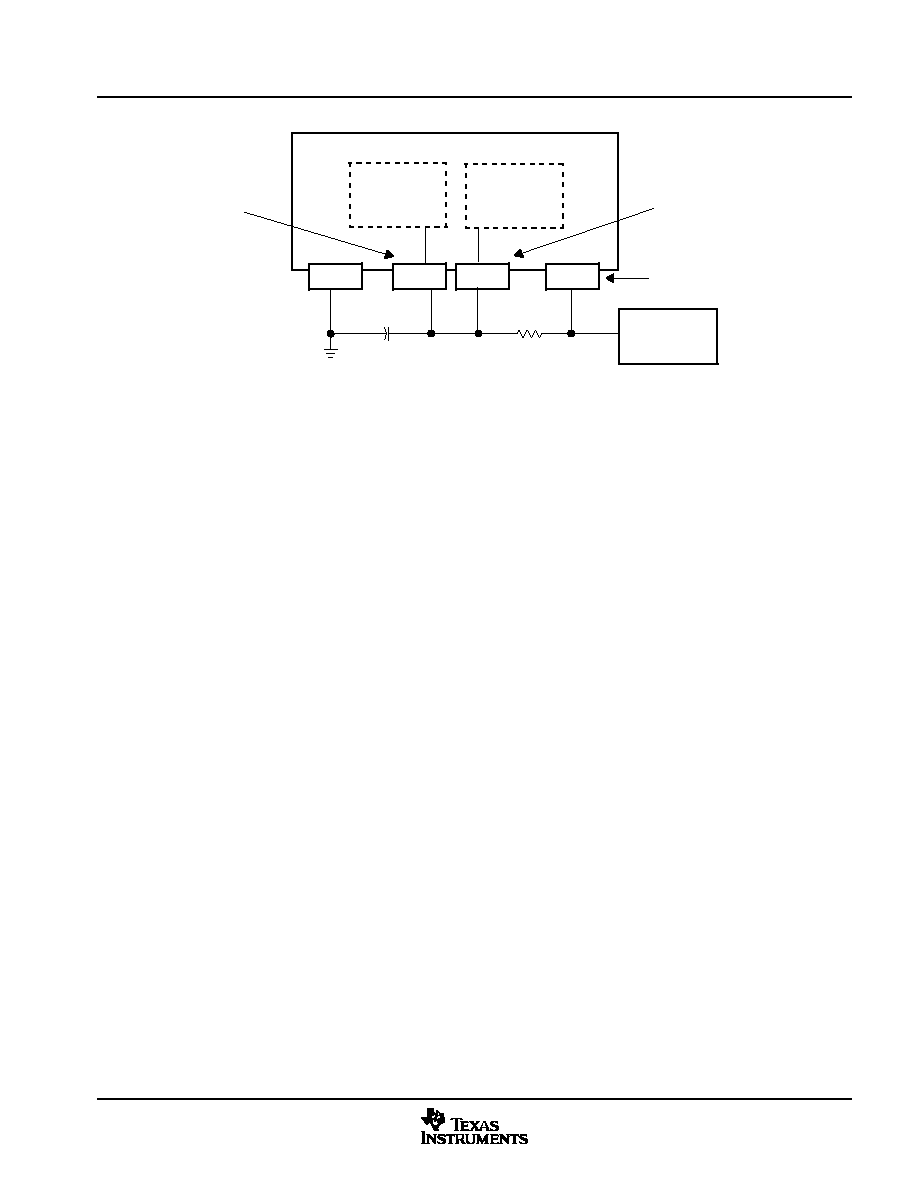

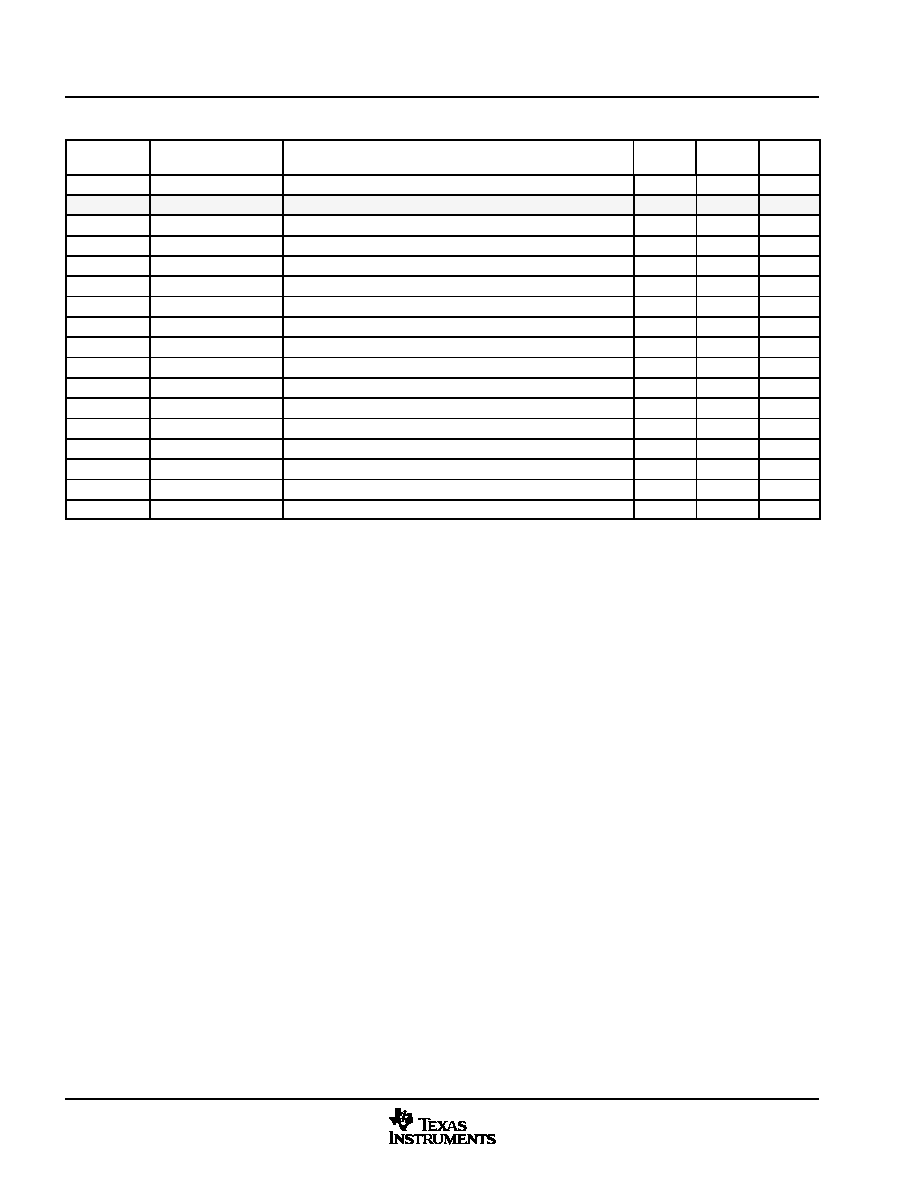

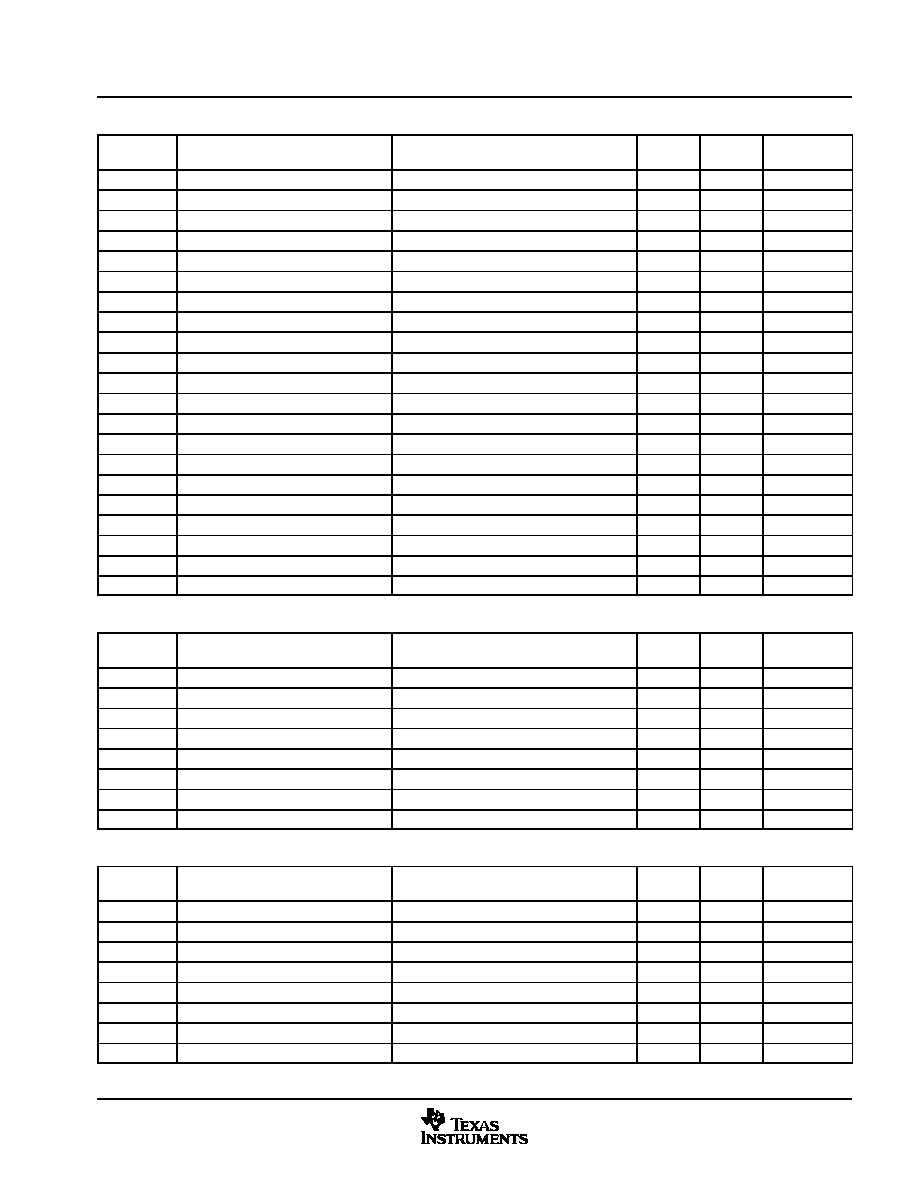

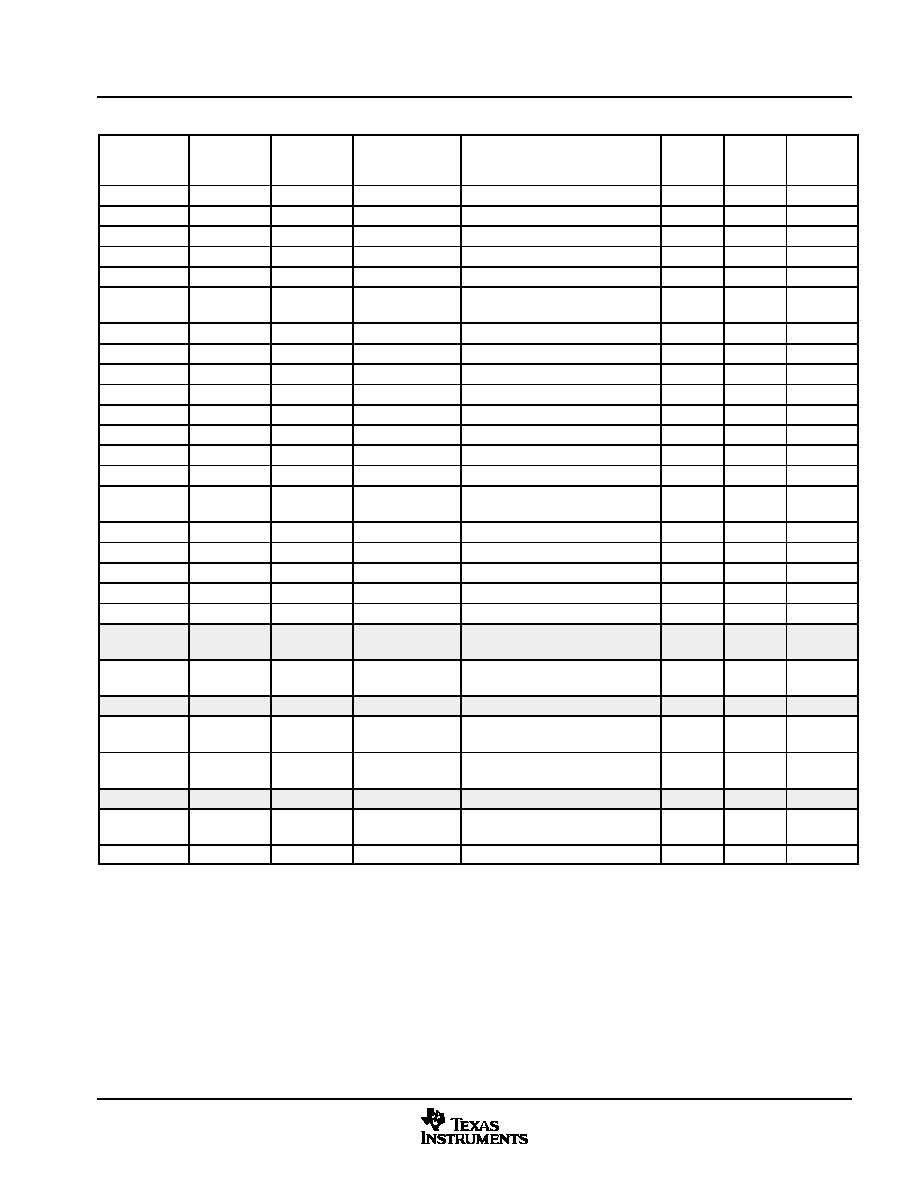

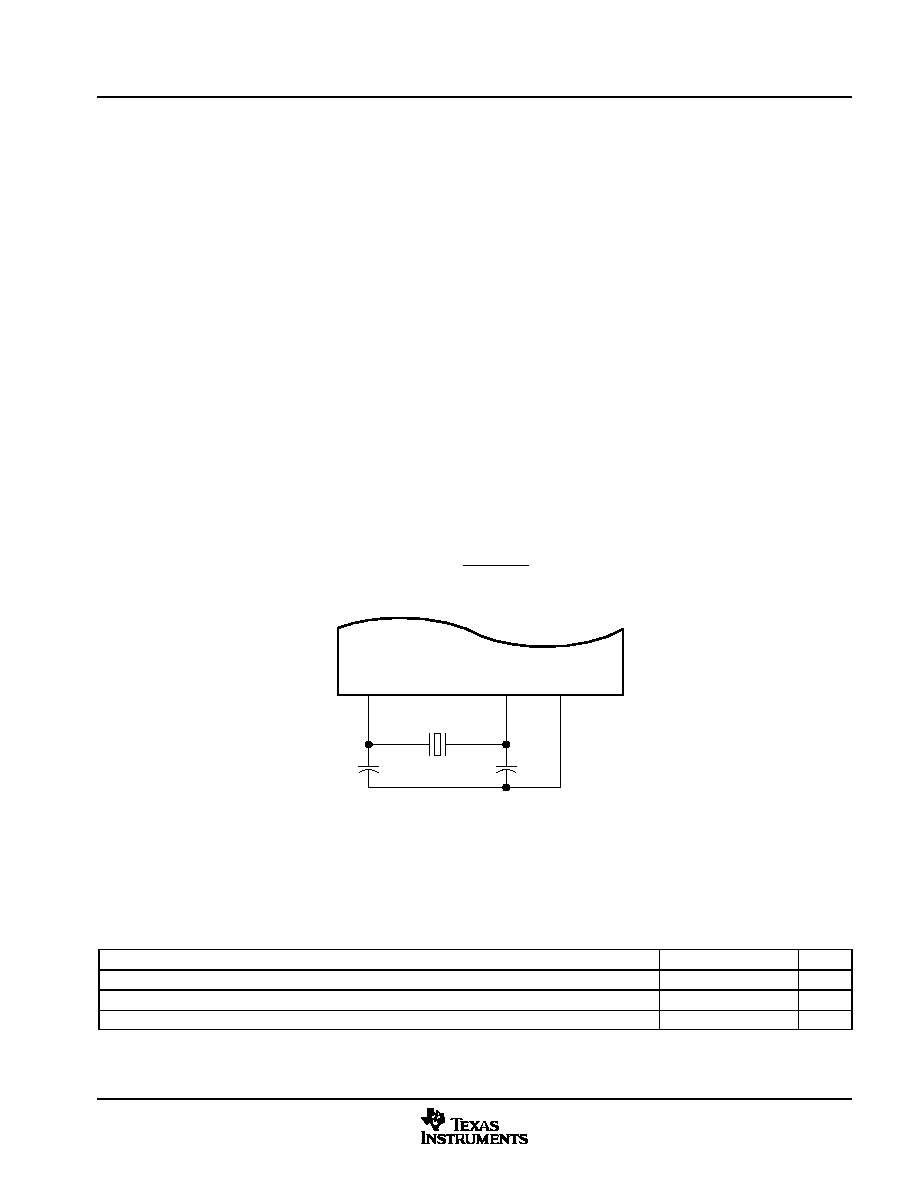

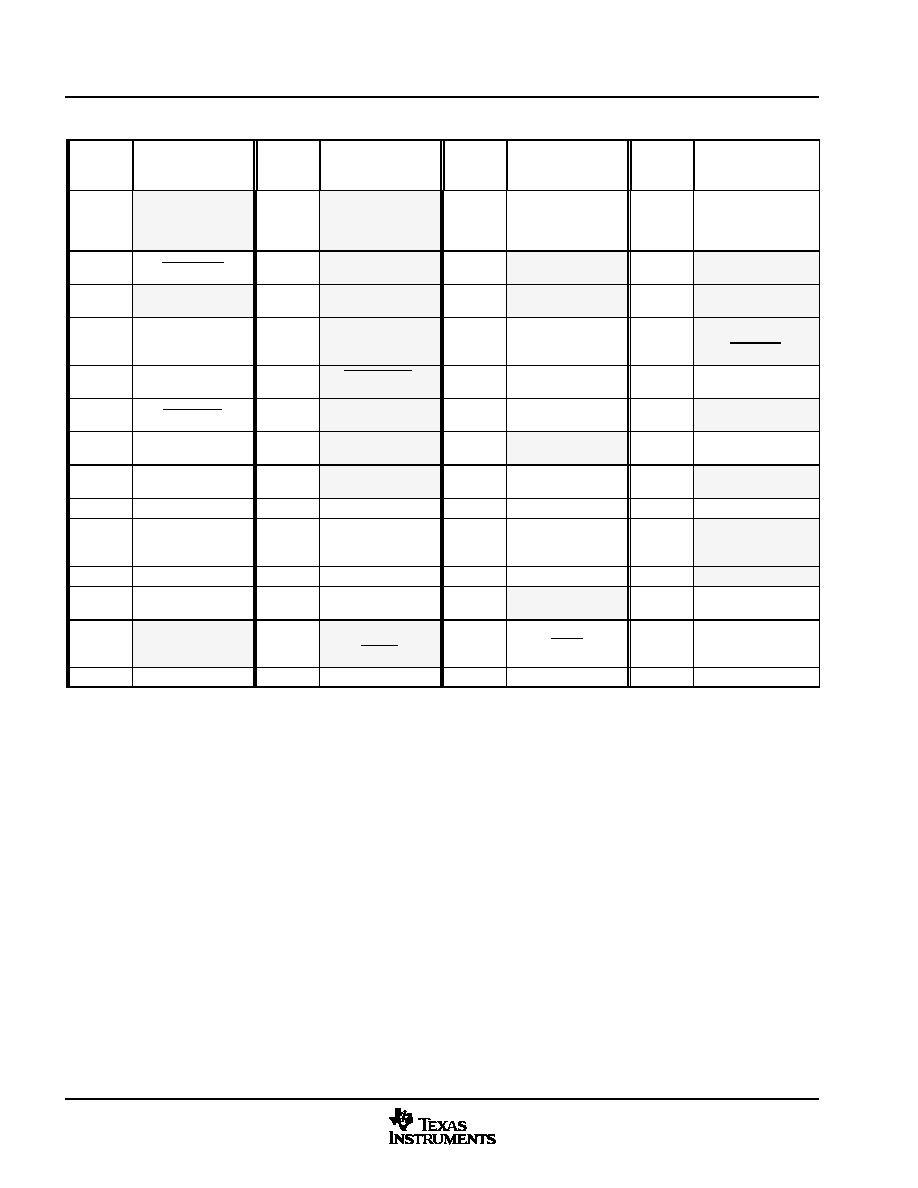

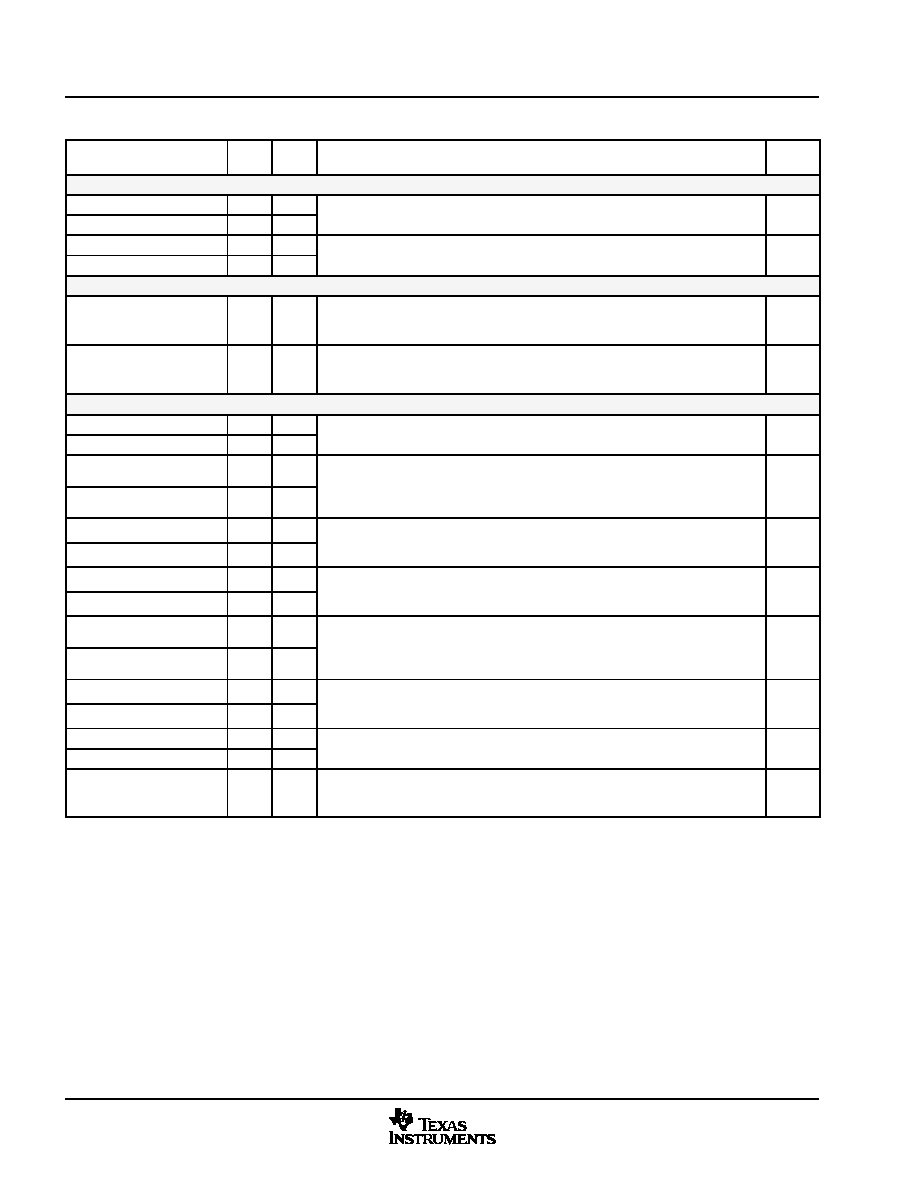

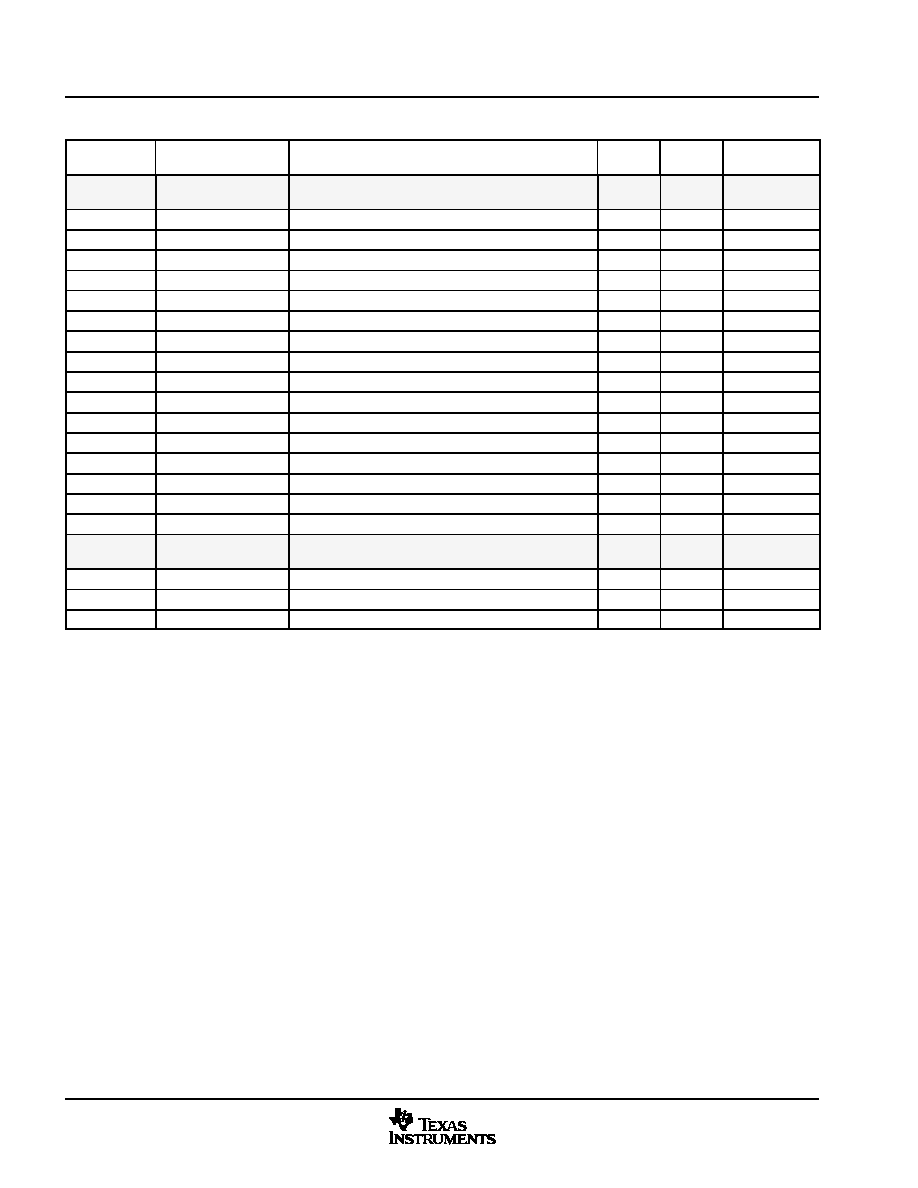

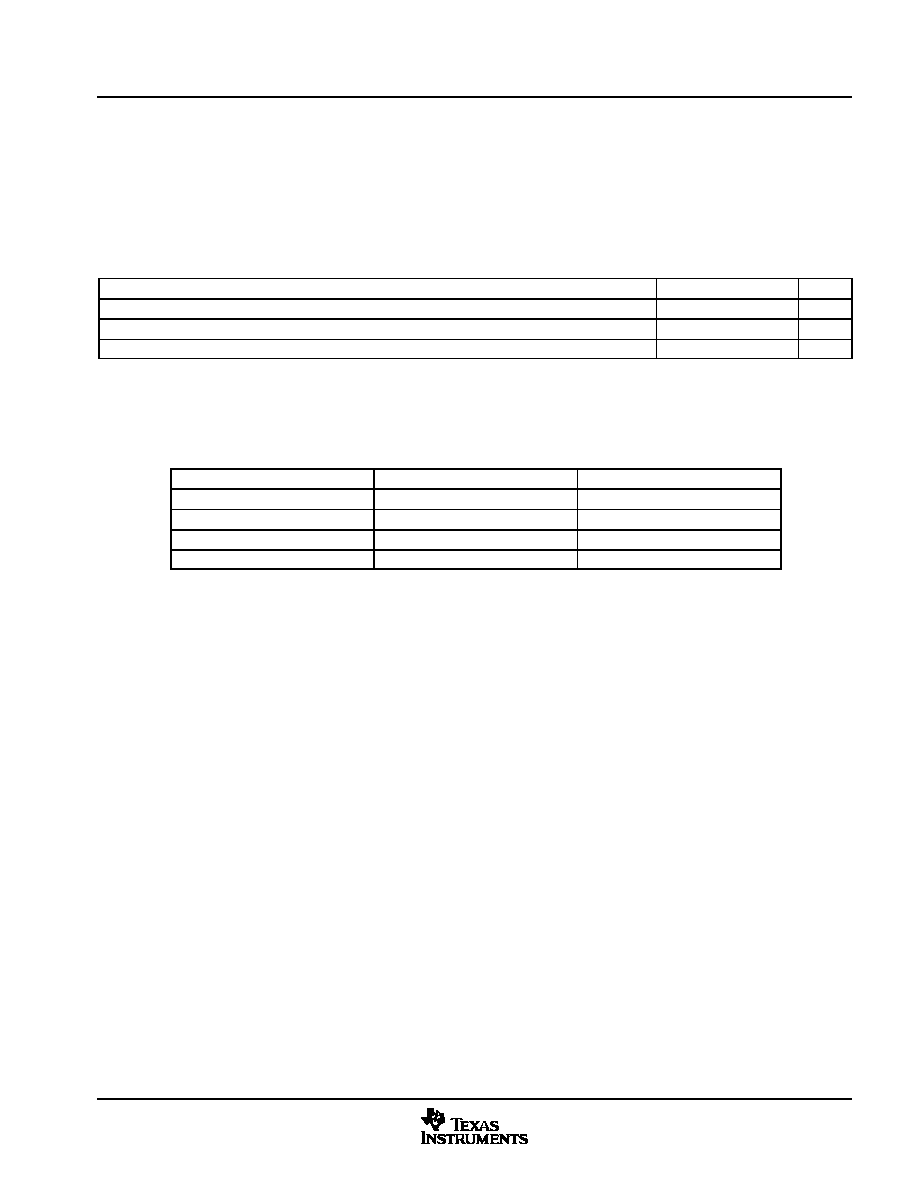

Figure 2-2 illustrates the ball locations for the 289-ball GDY ball grid array (BGA) package and is used in

conjunction with Table 2-1 to locate signal names and ball grid numbers. GDY BGA ball numbers in

Figure 2-2 are read from left-to-right, top-to-bottom.

A

1

2

B

4

3

6

5

8

7

10

9

12

11

14

13

16

15

17

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

Bottom View

Figure 2-2. OMAP5910 GDY Package (Bottom View)

In Table 2-2, signals with multiplexed functions are separated with forward slashes as follows:

�

signal1/signal2/signal3 (for example, GPIO11/HDQ)

Signals which are associated with specific peripherals are denoted by using the peripheral name, followed

by a period, and then the signal name; as follows:

�

peripheral1.signal1 (for example, MCBSP1.DR)

Introduction

22

August 2002 - Revised August 2004

SPRS197D

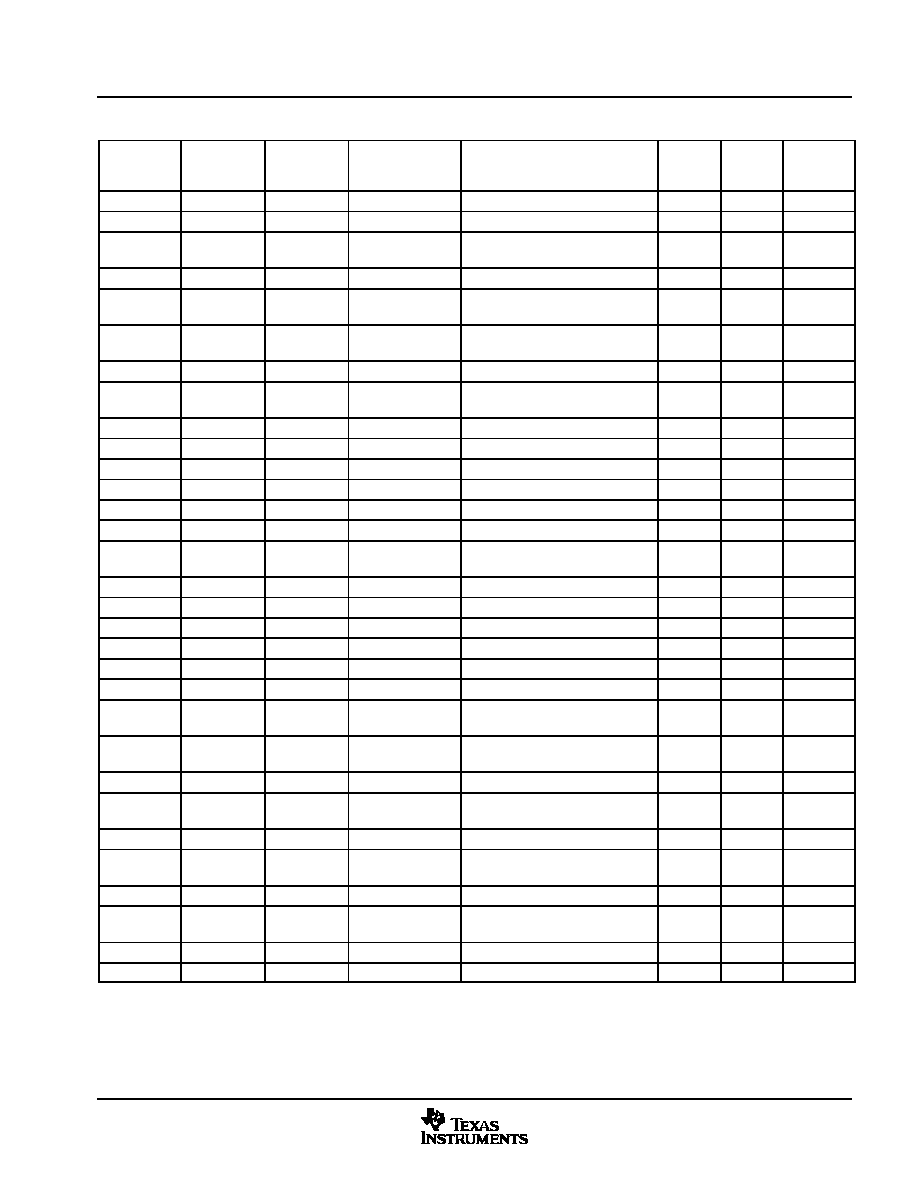

Table 2-2. GDY BGA Terminal Assignments

GDY

BGA

BALL #

SIGNAL

GDY

BGA

BALL #

SIGNAL

GDY

BGA

BALL #

SIGNAL

GDY

BGA

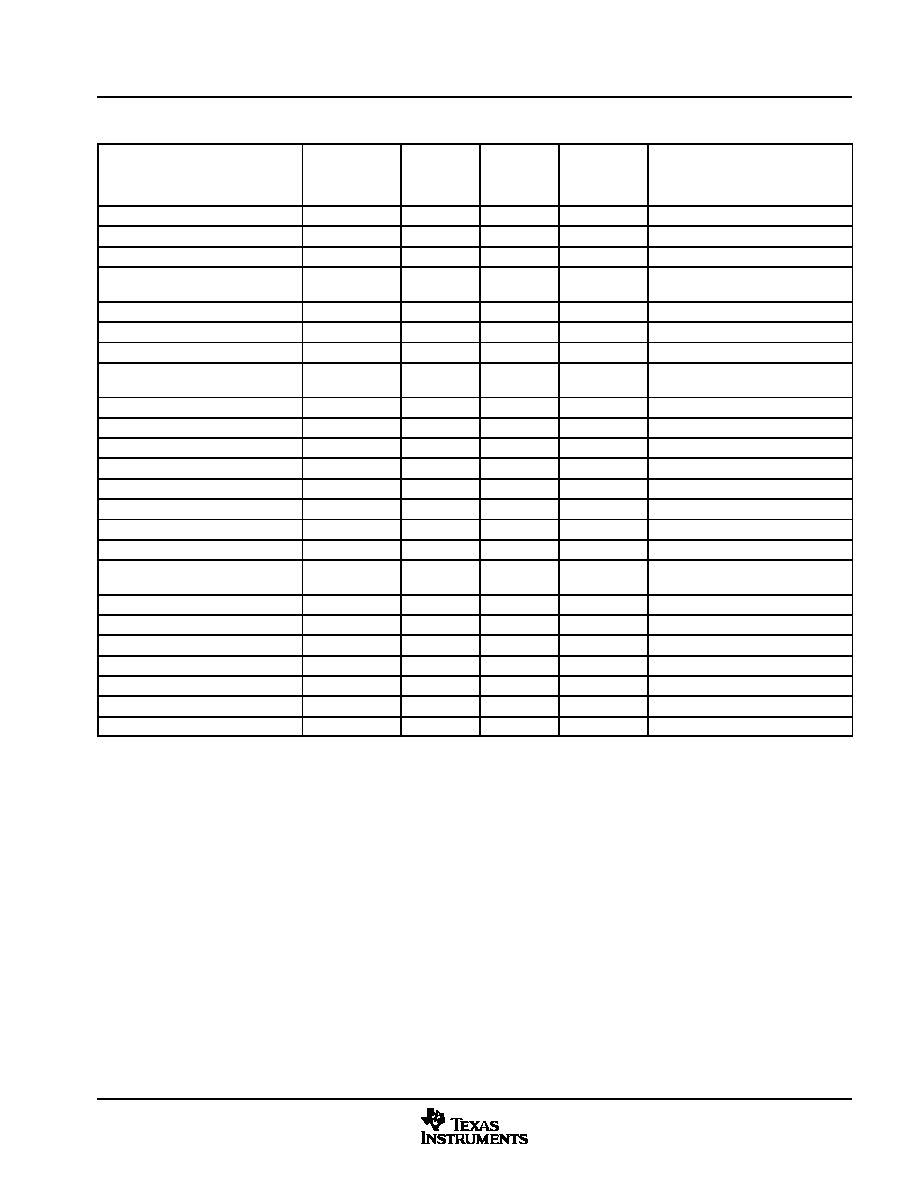

BALL #