SN74LVC1G57

CONFIGURABLE MULTIPLE FUNCTION GATE

SCES414G - NOVEMBER 2002 - REVISED SEPTEMBER 2003

1

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

D

Available in the Texas Instruments

NanoStar

and NanoFree

Packages

D

Supports 5-V V

CC

Operation

D

Inputs Accept Voltages to 5.5 V

D

Max t

pd

of 6.3 ns at 3.3 V

D

Low Power Consumption, 10-

µ

A Max I

CC

D

±

24-mA Output Drive at 3.3 V

D

I

off

Supports Partial-Power-Down Mode

Operation

D

Latch-Up Performance Exceeds 100 mA

Per JESD 78, Class II

D

ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

description/ordering information

This configurable multiple-function gate is designed for 1.65-V to 5.5-V V

CC

operation.

The SN74LVC1G57 features configurable multiple functions. The output state is determined by eight patterns

of 3-bit input. The user can choose the logic functions AND, OR, NAND, NOR, XNOR, inverter, and noninverter.

All inputs can be connected to V

CC

or GND.

This device functions as an independent gate, but because of Schmitt action, it may have different input

threshold levels for positive-going (V

T+

) and negative-going (V

T-

) signals.

NanoStar

and NanoFree

package technology is a major breakthrough in IC packaging concepts, using the

die as the package.

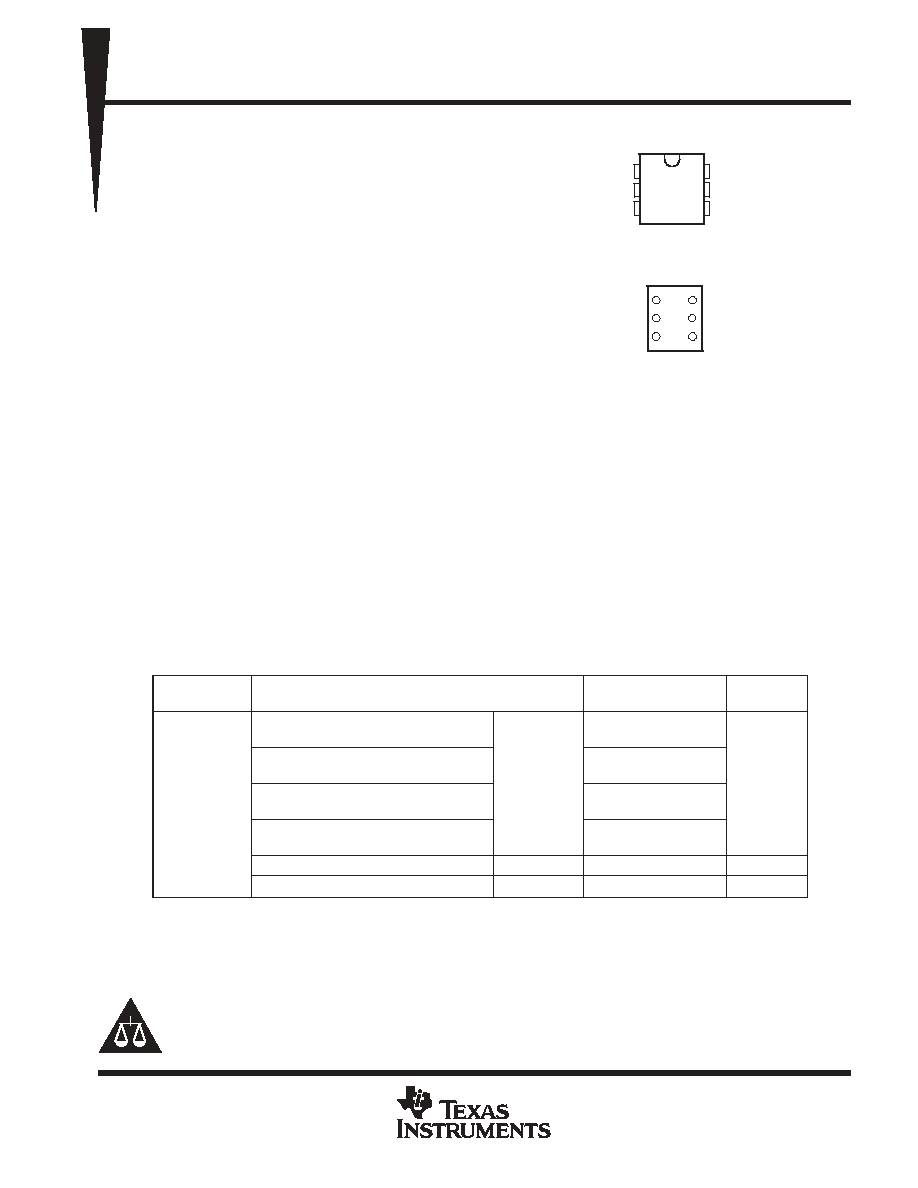

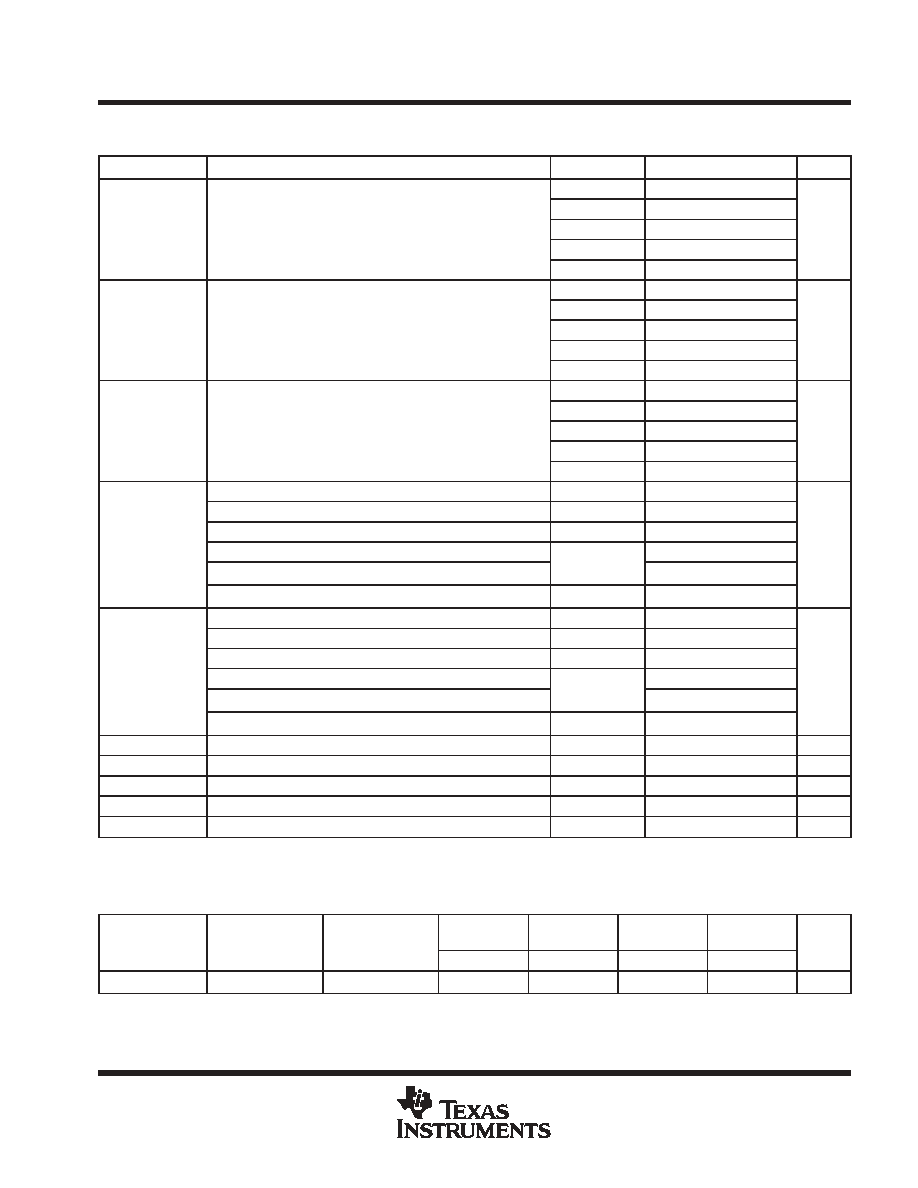

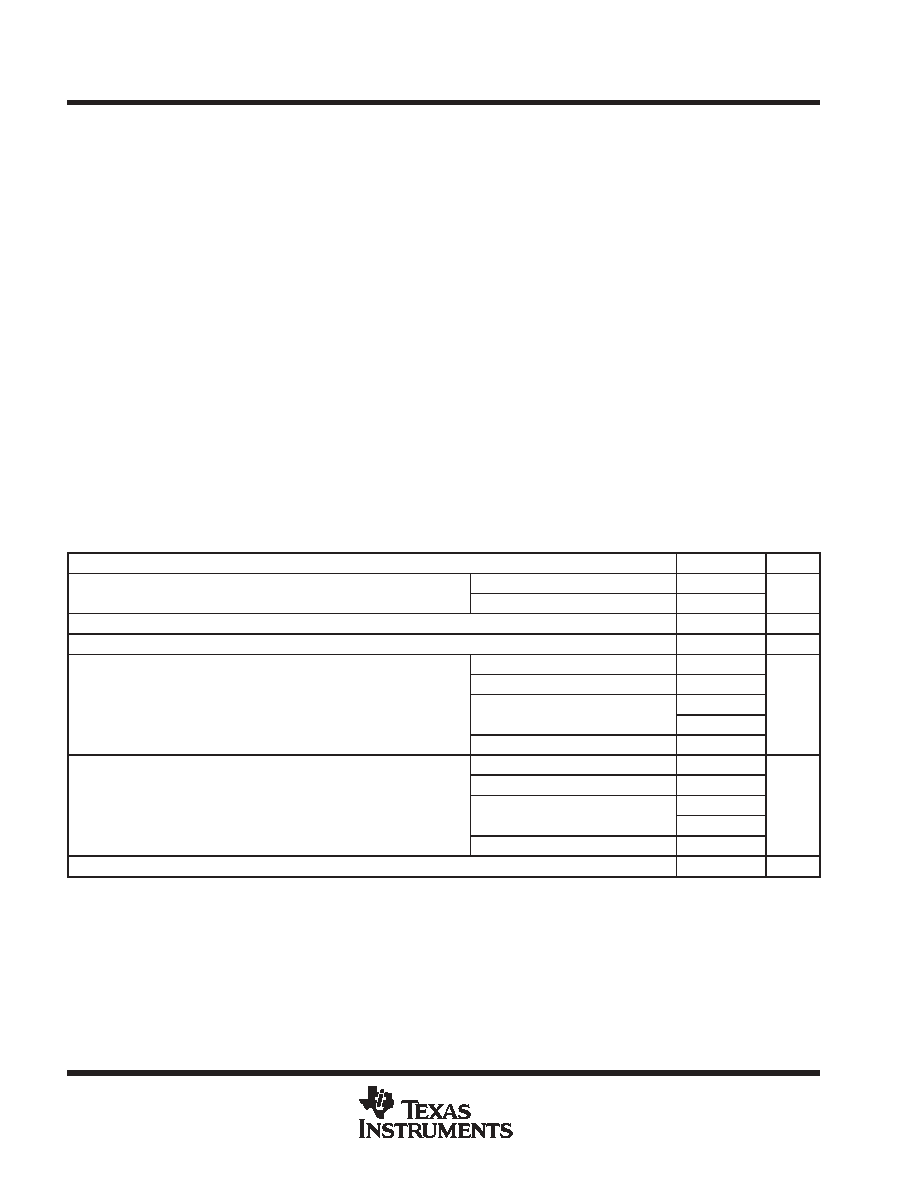

ORDERING INFORMATION

TA

PACKAGE

ORDERABLE

PART NUMBER

TOP-SIDE

MARKING

NanoStar

- WCSP (DSBGA)

0.17-mm Small Bump - YEA

SN74LVC1G57YEAR

NanoFree

- WCSP (DSBGA)

0.17-mm Small Bump - YZA (Pb-free)

Tape and reel

SN74LVC1G57YZAR

_ _ _CL_

-40

∞

C to 85

∞

C

NanoStar

- WCSP (DSBGA)

0.23-mm Large Bump - YEP

Tape and reel

SN74LVC1G57YEPR

_ _ _CL_

NanoFree

- WCSP (DSBGA)

0.23-mm Large Bump - YZP (Pb-free)

SN74LVC1G57YZPR

SOT (SOT-23) - DBV

Tape and reel

SN74LVC1G57DBVR

CA7_

SOT (SC-70) - DCK

Tape and reel

SN74LVC1G57DCKR

CL_

Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at

www.ti.com/sc/package.

DBV/DCK: The actual top-side marking has one additional character that designates the assembly/test site.

YEA/YZA,YEP/YZP: The actual top-side marking has three preceding characters to denote year, month, and sequence code,

and one following character to designate the assembly/test site. Pin 1 identifier indicates solder-bump composition

(1 = SnPb,

∑

= Pb-free).

Copyright

2003, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

NanoStar and NanoFree are trademarks of Texas Instruments.

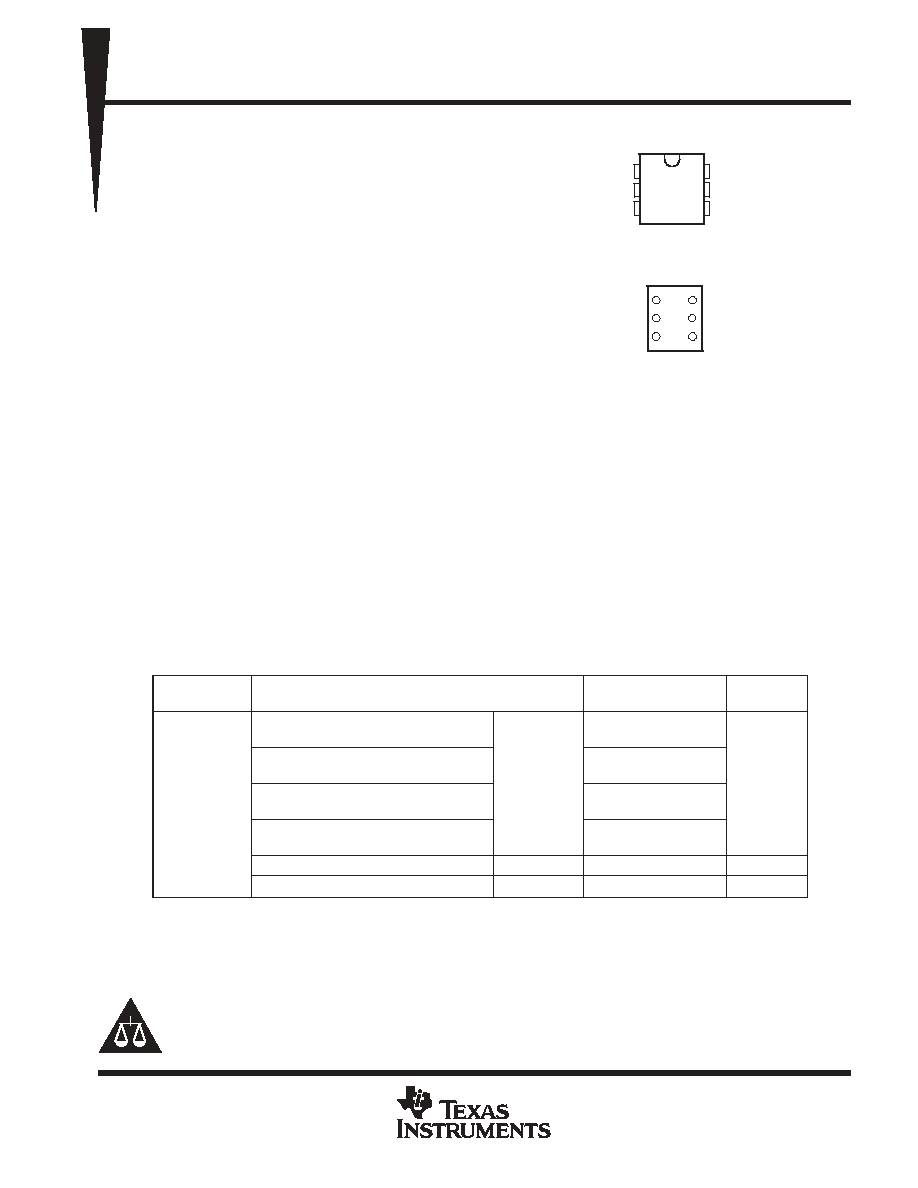

DBV OR DCK PACKAGE

(TOP VIEW)

1

2

3

6

5

4

In1

GND

In0

In2

V

CC

Y

3

2

1

4

5

6

In0

GND

In1

Y

V

CC

In2

YEA, YEP, YZA OR YZP PACKAGE

(BOTTOM VIEW)

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

SN74LVC1G57

CONFIGURABLE MULTIPLE FUNCTION GATE

SCES414G - NOVEMBER 2002 - REVISED SEPTEMBER 2003

2

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

description/ordering information (continued)

This device is fully specified for partial-power-down applications using I

off

. The I

off

circuitry disables the outputs,

preventing damaging current backflow through the device when it is powered down.

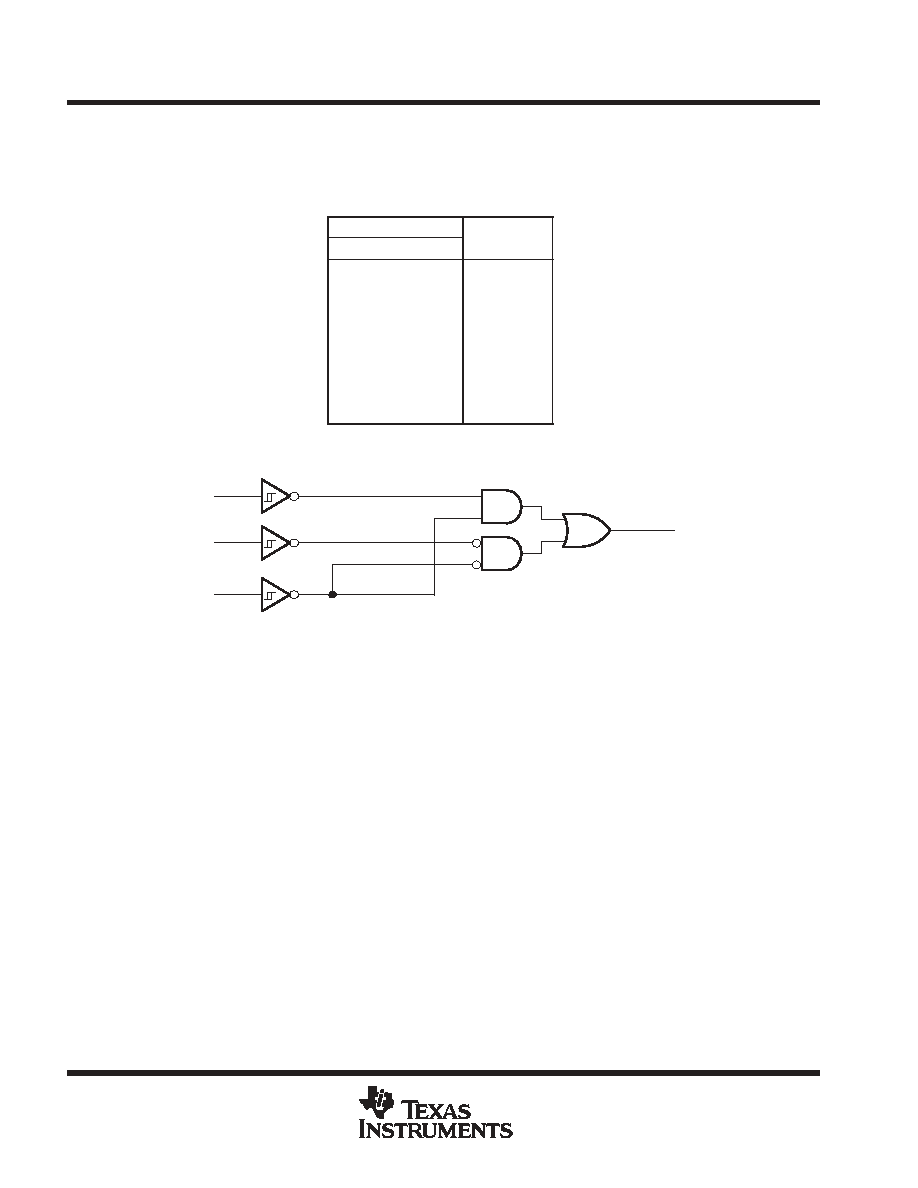

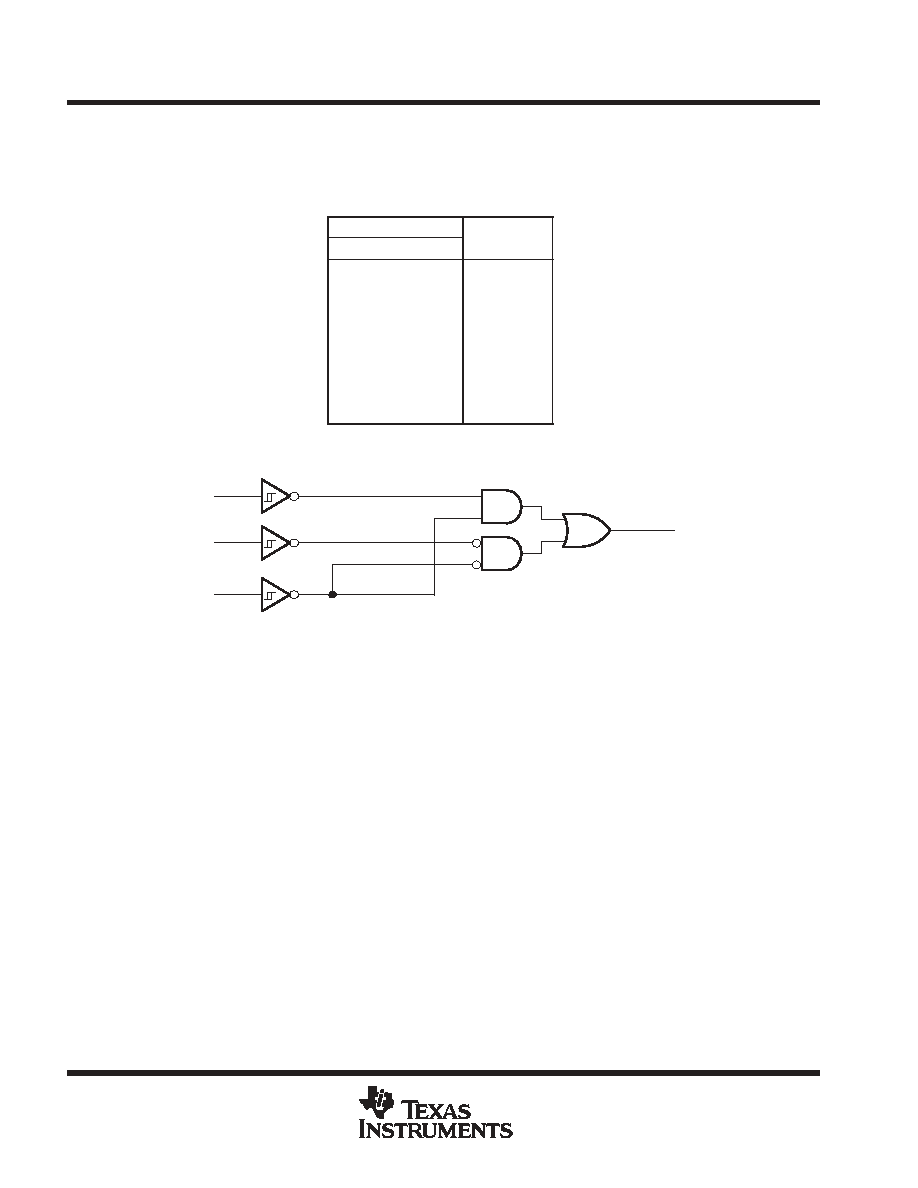

FUNCTION TABLE

INPUTS

OUTPUT

In2

In1

In0

OUTPUT

Y

L

L

L

H

L

L

H

L

L

H

L

H

L

H

H

L

H

L

L

L

H

L

H

L

H

H

L

H

H

H

H

H

logic diagram (positive logic)

3

1

6

In2

In1

In0

4

Y

SN74LVC1G57

CONFIGURABLE MULTIPLE FUNCTION GATE

SCES414G - NOVEMBER 2002 - REVISED SEPTEMBER 2003

3

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

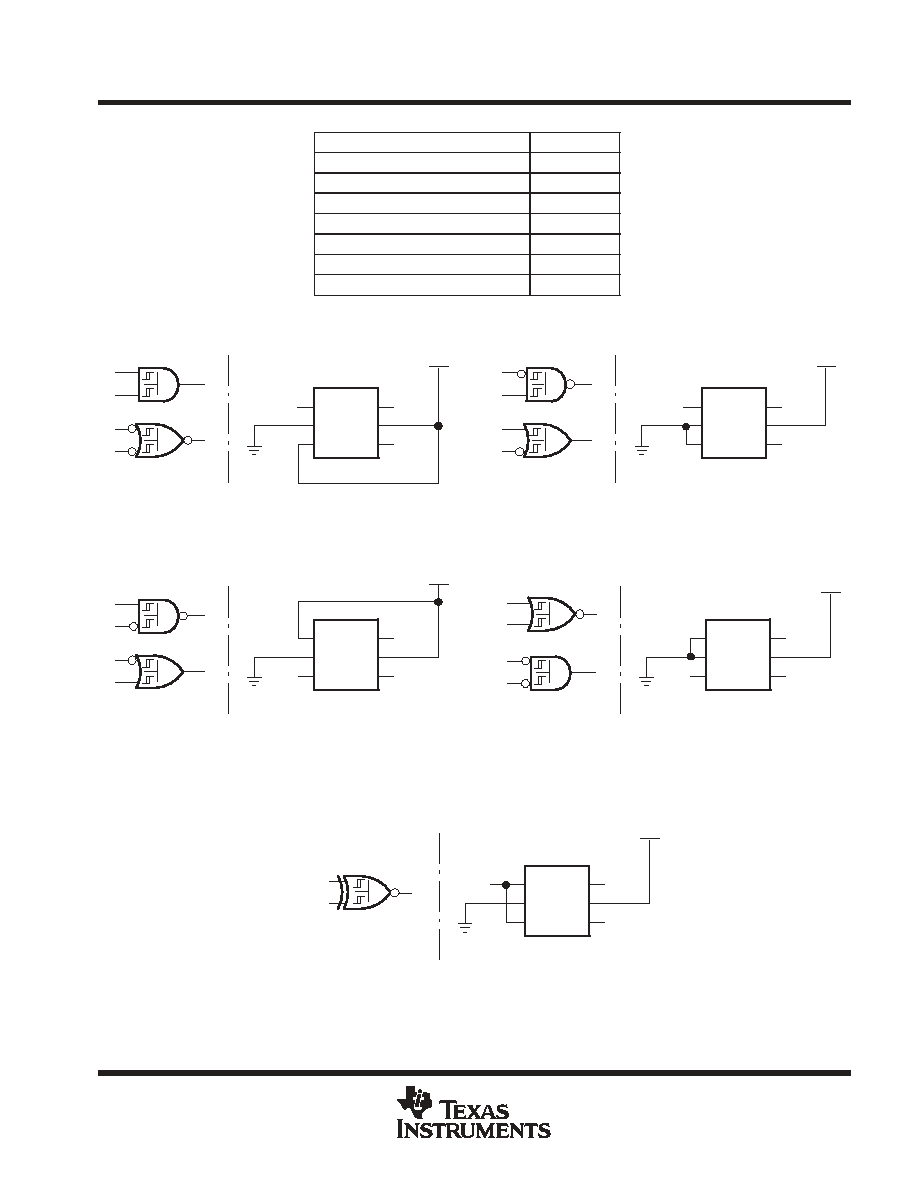

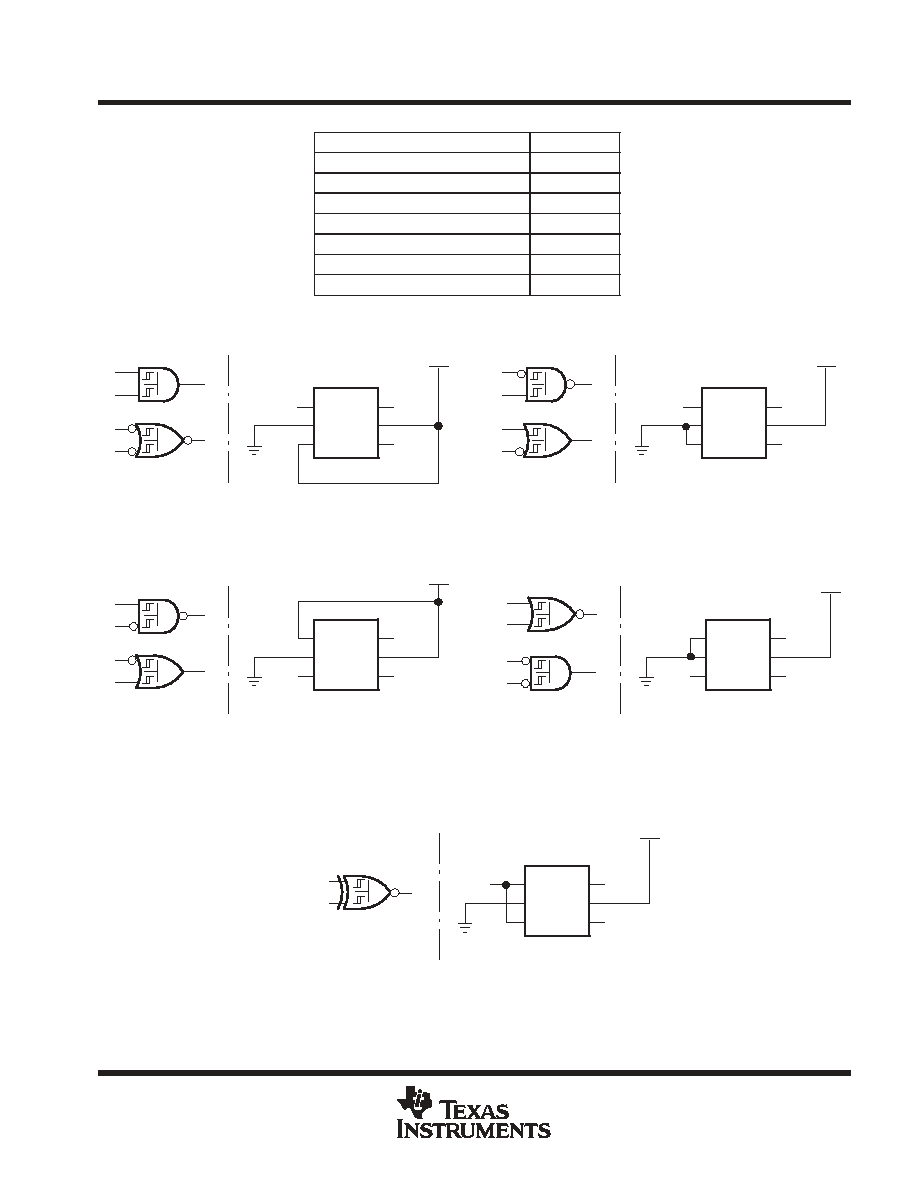

FUNCTION SELECTION TABLE

LOGIC FUNCTION

FIGURE NO.

2-input AND

1

2-input AND with both inputs inverted

4

2-input NAND with inverted input

2, 3

2-input OR with inverted input

2, 3

2-input NOR

4

2-input NOR with both inputs inverted

1

2-input XNOR

5

logic configurations

A

Y

B

1

2

3

6

5

4

A

Y

B

VCC

A

Y

B

Figure 1. 2-Input AND Gate

A

Y

B

1

2

3

6

5

4

A

Y

B

VCC

A

Y

B

Figure 2. 2-Input NAND Gate

With Inverted A Input

A

Y

B

1

2

3

6

5

4

A

Y

B

VCC

A

Y

B

Figure 3. 2-Input NAND Gate

With Inverted B Input

A

Y

B

1

2

3

6

5

4

A

Y

B

VCC

A

Y

B

Figure 4. 2-Input NOR Gate

1

2

3

6

5

4

A

Y

B

VCC

Y

Figure 5. 2-Input XNOR Gate

A

B

SN74LVC1G57

CONFIGURABLE MULTIPLE FUNCTION GATE

SCES414G - NOVEMBER 2002 - REVISED SEPTEMBER 2003

4

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, V

CC

-0.5 V to 6.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

(see Note 1)

-0.5 V to 6.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high-impedance or power-off state, V

O

(see Note 1)

-0.5 V to 6.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range applied to any output in the high or low state, V

O

(see Notes 1 and 2)

-0.5 V to V

CC

+ 0.5 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input clamp current, I

IK

(V

I

< 0)

-50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output clamp current, I

OK

(V

O

< 0)

-50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous output current, I

O

±

50 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous current through V

CC

or GND

±

100 mA

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package thermal impedance,

JA

(see Note 3): DBV package

165

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DCK package

259

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

YEA/YZA package

143

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . .

YEP/YZP package

123

∞

C/W

. . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

-65

∞

C to 150

∞

C

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES:

1. The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

2. The value of VCC is provided in the recommended operating conditions table.

3. The package thermal impedance is calculated in accordance with JESD 51-7.

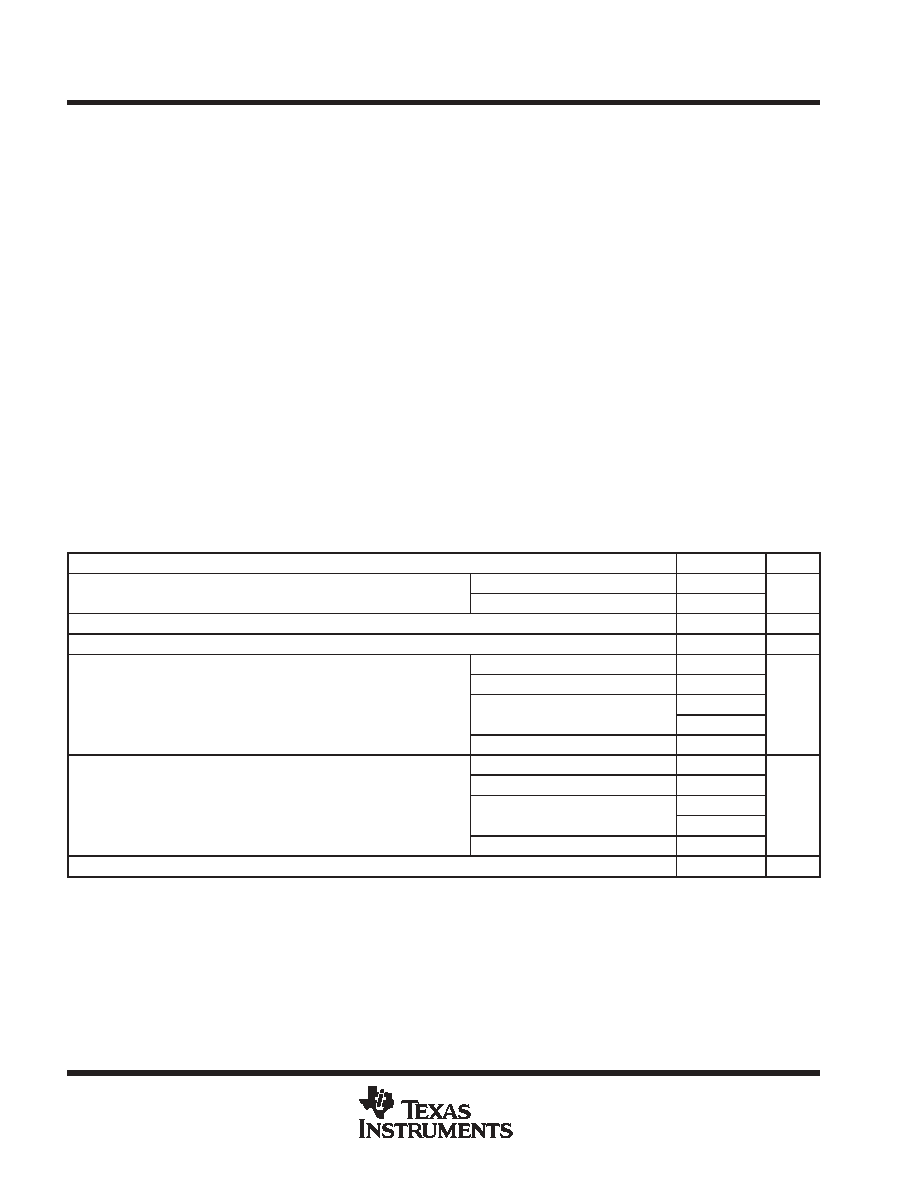

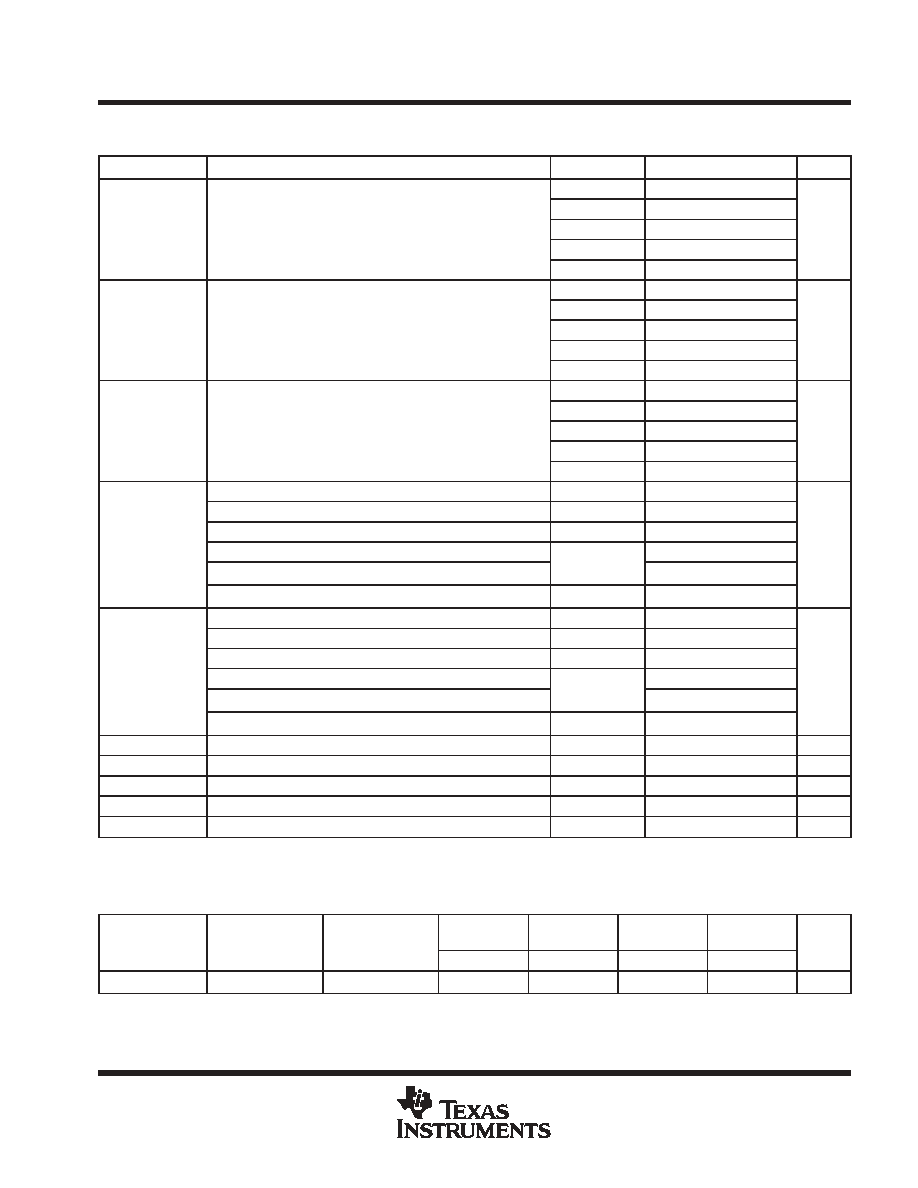

recommended operating conditions (see Note 4)

MIN

MAX

UNIT

VCC

Supply voltage

Operating

1.65

5.5

V

VCC

Supply voltage

Data retention only

1.5

V

VI

Input voltage

0

5.5

V

VO

Output voltage

0

VCC

V

VCC = 1.65 V

-4

VCC = 2.3 V

-8

IOH

High-level output current

VCC = 3 V

-16

mA

IOH

High-level output current

VCC = 3 V

-24

mA

VCC = 4.5 V

-32

VCC = 1.65 V

4

VCC = 2.3 V

8

IOL

Low-level output current

VCC = 3 V

16

mA

IOL

Low-level output current

VCC = 3 V

24

mA

VCC = 4.5 V

32

TA

Operating free-air temperature

-40

85

∞

C

NOTE 4: All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

SN74LVC1G57

CONFIGURABLE MULTIPLE FUNCTION GATE

SCES414G - NOVEMBER 2002 - REVISED SEPTEMBER 2003

5

POST OFFICE BOX 655303

∑

DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted)

PARAMETER

TEST CONDITIONS

VCC

MIN

TYP

MAX

UNIT

1.65 V

0.79

1.16

VT+

Positive-going

2.3 V

1.11

1.56

VT+

Positive-going

input threshold

3 V

1.5

1.87

V

input threshold

voltage

4.5 V

2.16

2.74

V

voltage

5.5 V

2.61

3.33

1.65 V

0.39

0.62

VT-

Negative-going

2.3 V

0.58

0.87

VT-

Negative-going

input threshold

3 V

0.84

1.14

V

input threshold

voltage

4.5 V

1.41

1.79

V

voltage

5.5 V

1.87

2.29

1.65 V

0.37

0.62

VT

2.3 V

0.48

0.77

VT

Hysteresis

(V

- V

)

3 V

0.56

0.87

V

Hysteresis

(VT+ - VT-)

4.5 V

0.71

1.04

V

T+

T-

5.5 V

0.71

1.11

IOH = -100

m

A

1.65 V to 5.5 V

VCC-0.1

IOH = -4 mA

1.65 V

1.2

V

IOH = -8 mA

2.3 V

1.9

V

VOH

IOH = -16 mA

3 V

2.4

V

IOH = -24 mA

3 V

2.3

IOH = -32 mA

4.5 V

3.8

IOL = 100

m

A

1.65 V to 5.5 V

0.1

IOL = 4 mA

1.65 V

0.45

V

IOL = 8 mA

2.3 V

0.3

V

VOL

IOL = 16 mA

3 V

0.4

V

IOL = 24 mA

3 V

0.55

IOL = 32 mA

4.5 V

0.55

II

VI = 5.5 V or GND

0 to 5.5 V

±

1

m

A

Ioff

VI or VO = 5.5 V

0

±

10

m

A

ICC

VI = 5.5 V or GND,

IO = 0

1.65 V to 5.5 V

10

m

A

ICC

One input at VCC - 0.6 V,

Other inputs at VCC or GND

3 V to 5.5 V

500

m

A

Ci

VI = VCC or GND

3.3 V

3.5

pF

All typical values are at VCC = 3.3 V, TA = 25

∞

C.

switching characteristics over recommended operating free-air temperature range (unless

otherwise noted) (see Figure 6)

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

VCC = 1.8 V

±

0.15 V

VCC = 2.5 V

±

0.2 V

VCC = 3.3 V

±

0.3 V

VCC = 5 V

±

0.5 V

UNIT

PARAMETER

(INPUT)

(OUTPUT)

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

tpd

Any In

Y

3.2

14.4

2

8.3

1.5

6.3

1.1

5.1

ns