TAS3103

Digital Audio Processor With 3D Effects

October 2002

Digital Audio Solutions

Data Manual

SLES038A

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,

enhancements, improvements, and other changes to its products and services at any time and to discontinue

any product or service without notice. Customers should obtain the latest relevant information before placing

orders and should verify that such information is current and complete. All products are sold subject to TI's terms

and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in

accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI

deems necessary to support this warranty. Except where mandated by government requirements, testing of all

parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for

their products and applications using TI components. To minimize the risks associated with customer products

and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,

copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process

in which TI products or services are used. Information published by TI regarding third-party products or services

does not constitute a license from TI to use such products or services or a warranty or endorsement thereof.

Use of such information may require a license from a third party under the patents or other intellectual property

of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without

alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction

of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for

such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that

product or service voids all express and any implied warranties for the associated TI product or service and

is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright

2002, Texas Instruments Incorporated

iii

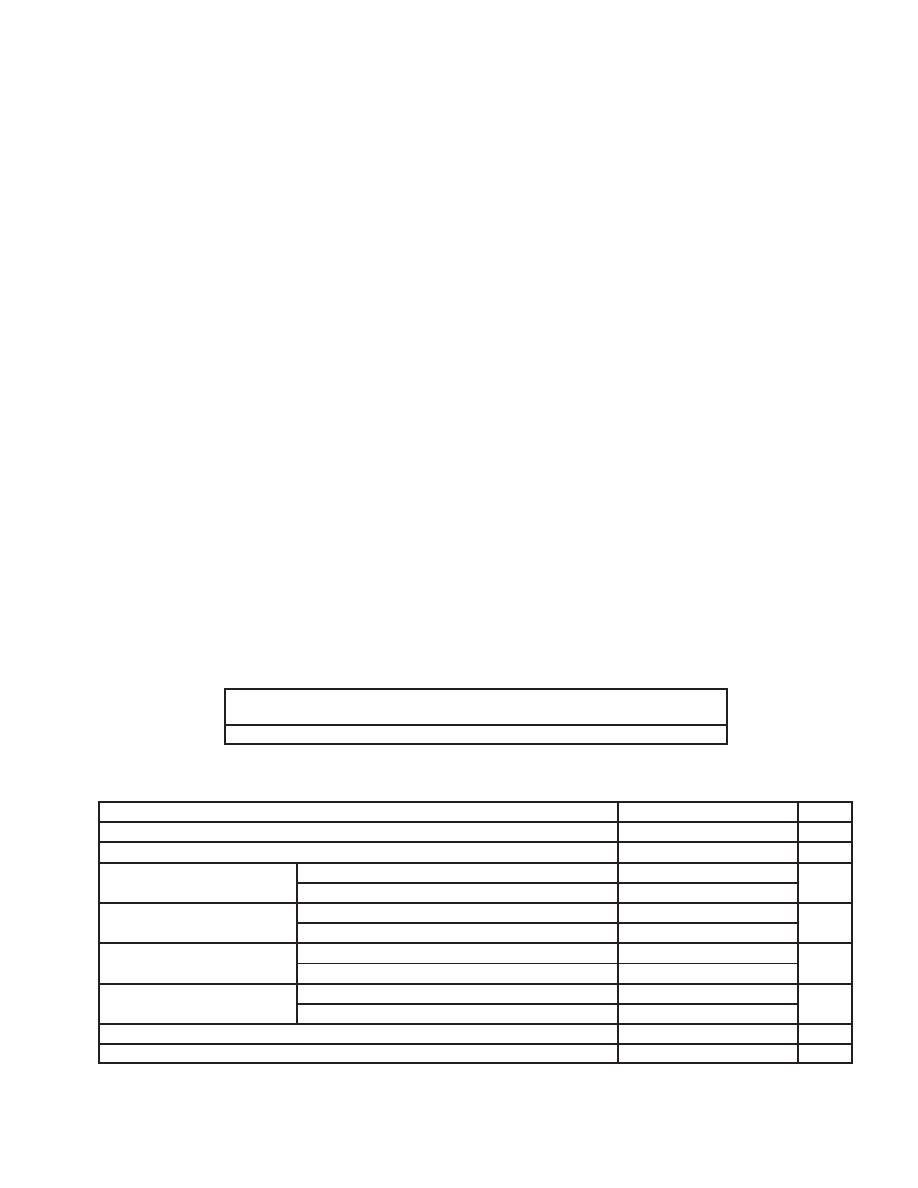

Contents

Section

Title

Page

1

Introduction

1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1

Features

1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2

Terminal Assignments

1-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3

Hardware Block Diagram

1-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4

Functional Block Diagram

1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5

Ordering Information

1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6

Terminal Functions

1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7

Operational Modes

1-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7.1

Terminal-Controlled Modes

1-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7.2

I

2

C Bus-Controlled Modes

1-10

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2

Hardware Architecture

2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1

Input and Output Serial Audio Ports (SAPs)

2-3

. . . . . . . . . . . . . . . . . . . . . .

2.1.1

SAP Configuration Options

2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2

Processing Flow--SAP Input to SAP Output

2-10

. . . . . . . . . . .

2.2

DPLL and Clock Management

2-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3

Controller

2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.1

8051 Microprocessor

2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3.2

I

2

C Bus controller

2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4

Digital Audio Processor (DAP) Arithmetic Unit

2-21

. . . . . . . . . . . . . . . . . . .

2.5

Reset

2-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6

Power Down

2-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7

Watchdog Timer

2-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8

General-Purpose I/O (GPIO) Ports

2-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8.1

GPIO Functionality--I

2

C Master Mode

2-25

. . . . . . . . . . . . . . . .

2.8.2

GPIO Functionality--I

2

C Slave Mode

2-26

. . . . . . . . . . . . . . . . . .

3

Firmware Architecture

3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

I

2

C Coefficient Number Formats

3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1

28-Bit 5.23 Number Format

3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.2

48-Bit 25.23 Number Format

3-2

. . . . . . . . . . . . . . . . . . . . . . . . . .

3.2

Input Crossbar Mixers

3-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3

3D Effects Block

3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.1

CH1/CH2 Effects Block

3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2

CH3 Effects Block

3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4

Biquad Filters

3-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

Bass and Treble Processing

3-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1

Treble and Bass Processing and Concurrent I

2

C

Read Transactions

3-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6

Soft Volume/Loudness Processing

3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

3.6.1

Soft Volume

3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.2

Loudness Compensation

3-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6.3

Time Alignment and Reverb Delay Processing

3-26

. . . . . . . . . .

3.7

Dynamic Range Control (DRC)

3-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1

DRC Implementation

3-31

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.2

Compression/Expansion Coefficient Computation

Engine Parameters

3-33

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.3

DRC Compression/Expansion Implementation Examples

3-35

3.8

Spectrum Analyzer/VU Meter

3-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9

Dither

3-47

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.1

Dither Seeds

3-48

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.2

Dither Mix Options

3-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.3

Dither Gain Mixers

3-50

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9.4

Dither Statistics

3-51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.10

Output Crossbar Mixers

3-54

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4

Electrical Specifications

4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1

Absolute Maximum Ratings Over Operating Temperature Ranges

4-1

. .

4.2

Recommended Operating Conditions

4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3

Electrical Characteristics Over Recommended Operating

Conditions

4-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4

TAS3100 Timing Characteristics

4-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.1

Master Clock Signals Over Recommended Operating

Conditions

4-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.2

Control Signals Over Recommended Operating Conditions

4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.3

Serial Audio Port Slave Mode Signals Over Recommended

Operating Conditions )

4-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.4

Serial Audio Port Master Mode Signals Over Recommended

Operating Conditions

4-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.4.5

I2C Slave Mode Interface Signals Over Recommended

Operating Conditions

4-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

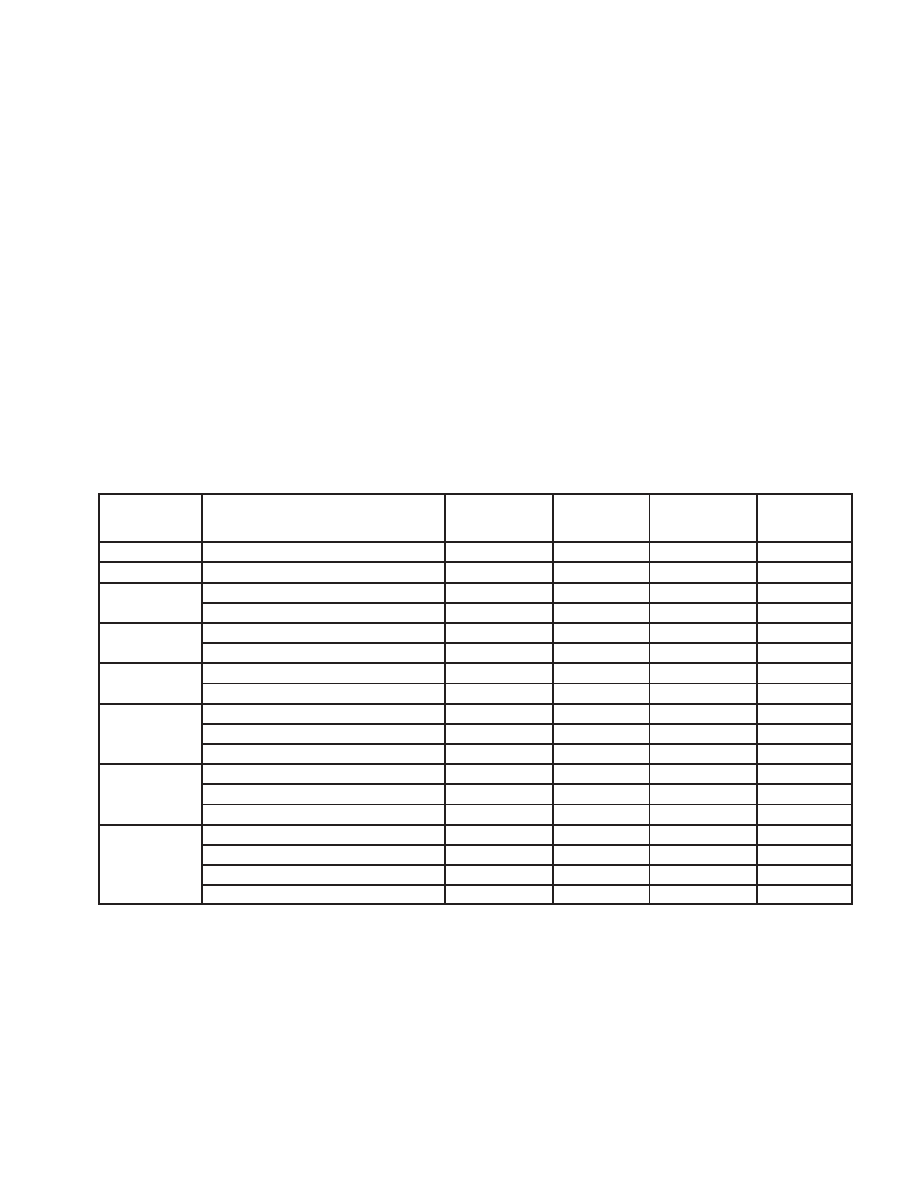

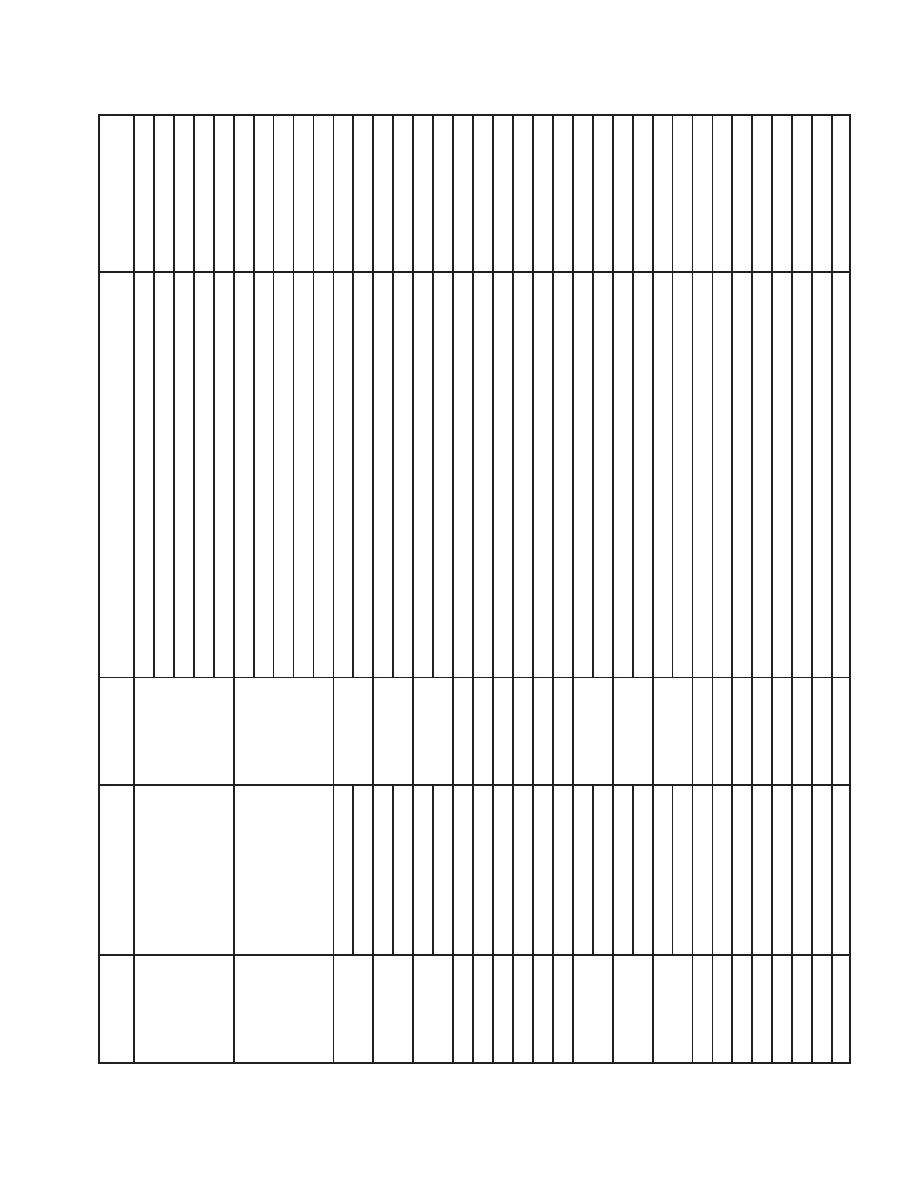

A.1

I

2

C Subaddress Table

A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A.2

TAS3103 Firmware Block Diagram

A-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Illustrations

Figure

Title

Page

2-1 TAS3103 Detailed Hardware Block Diagram

2-2

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2 Discrete Serial Data Formats

2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3 Four-Channel TDM Serial Data Formats

2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4 SAP Configuration Subaddress Fields

2-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-5 Recommended Procedure for Issuing SAP Configuration Updates

2-5

. . . . . . .

2-6 Format Options: Input Serial Audio Port

2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-7 TDM Format Options: Output Serial Audio Port

2-8

. . . . . . . . . . . . . . . . . . . . . . . .

2-8 Discrete Format Options: Output Serial Audio Port

2-9

. . . . . . . . . . . . . . . . . . . . .

2-9 Word Size Settings

2-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-10 8 CH TDM Format Using SAP Modes 0101 and 1000

2-10

. . . . . . . . . . . . . . . .

2-11 6 CH Data, 8 CH Transfer TDM Format Using SAP Modes

0101 and 1000

2-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

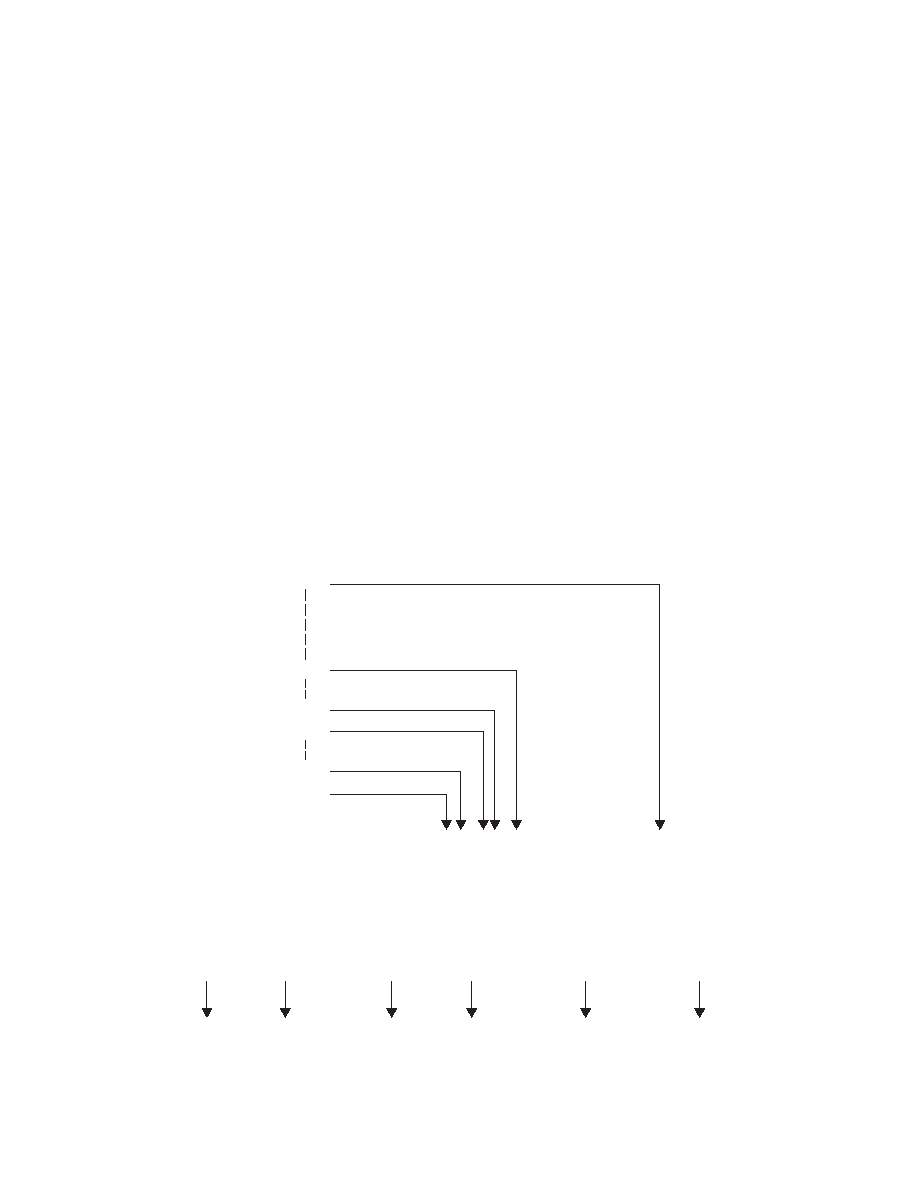

2-12 SAP Input-to-Output Latency

2-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-13 SAP Input-to-Output Latency for I

2

S Format Conversions

2-12

. . . . . . . . . . . . .

2-14 DPLL and Clock Management Block Diagram

2-15

. . . . . . . . . . . . . . . . . . . . . . .

2-15 I

2

C Slave Mode Communication Protocol

2-17

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2-16 I

2

C Subaddress Access Protocol

2-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-17 Digital Audio Processor Arithmetic Unit Block Diagram

2-21

. . . . . . . . . . . . . . . .

2-18 DAP Arithmetic Unit Data Word Structure

2-22

. . . . . . . . . . . . . . . . . . . . . . . . . . .

2-19 DAP ALU Operation With Intermediate Overflow

2-22

. . . . . . . . . . . . . . . . . . . . .

2-20 TAS3103 Reset Circuitry

2-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-21 GPIO Port Circuitry

2-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-22 Volume Adjustment Timing--Master I

2

C Mode

2-27

. . . . . . . . . . . . . . . . . . . . . . .

3-1 5.23 Format

3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2 Conversion Weighting Factors--5.23 Format to Floating Point

3-1

. . . . . . . . . . .

3-3 Alignment of 5.23 Coefficient in 32-Bit I

2

C Word

3-2

. . . . . . . . . . . . . . . . . . . . . . .

3-4 25.23 Format

3-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5 Alignment of 5.23 Coefficient in 32-Bit I2C Word

3-3

. . . . . . . . . . . . . . . . . . . . . . .

3-6 Alignment of 25.23 Coefficient in Two 32-Bit I

2

C Words

3-3

. . . . . . . . . . . . . . . . .

3-7 Serial Input Port to Processing Node Topology

3-5

. . . . . . . . . . . . . . . . . . . . . . . . .

3-8. Input Mixer and Effects Block Topology--Internal Processing

Nodes A, B, C, D, E, and F

3-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-9 Input Mixer Topology--Internal Processing Nodes G and H

3-7

. . . . . . . . . . . . . .

vi

3-10 TAS3103 3D Effects Processing Block

3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-11 Biquad Filter Structure and Coefficient Subaddress Format

3-10

. . . . . . . . . . . .

3-12 Bass and Treble Filter Selections

3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-13 Bass and Treble Application Example--Subaddress Parameters

3-14

. . . . . . .

3-14 I

2

C Bass/Treble Activity Monitor Procedure

3-16

. . . . . . . . . . . . . . . . . . . . . . . . .

3-15 Soft Volume and Loudness Compensation Block Diagram

3-18

. . . . . . . . . . . . .

3-16 Detailed Block Diagram--Soft Volume and Loudness Compensation

3-25

. . .

3-17 Delay Line Memory Implementation

3-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-18 Maximum Delay Line Lengths

3-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-19 DRC Positioning in TAS3103 Processing Flow

3-29

. . . . . . . . . . . . . . . . . . . . . . .

3-20 Dynamic Range Compression (DRC) Transfer Function Structure

3-30

. . . . . .

3-21 DRC Block Diagram

3-32

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-22 DRC Input Word Structure for 0-dB Channel Processing Gain

3-36

. . . . . . . . .

3-23 DRC Transfer Curve--Example 1

3-38

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-24 DRC Transfer Curve--Example 2

3-40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-25 DRC Transfer Curve--Example 3

3-42

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-26 DRC Transfer Curve--Example 4

3-44

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-27 Spectrum Analyzer/VU Meter Block Diagram

3-46

. . . . . . . . . . . . . . . . . . . . . . . .

3-28 Logarithmic Number Conversions--Spectrum Analyzer/VU Meter

3-47

. . . . . .

3-29 Dither Data Block Diagram

3-49

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-30 Dither Data Magnitude (Gain = 1.0)

3-51

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-31 Triangular Dither Statistics

3-52

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-32 Triangular Dither Statistics

3-53

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-33 Processing Node to Serial Output Port Topology

3-55

. . . . . . . . . . . . . . . . . . . . .

3-34 Output Crossbar Mixer Topology

3-56

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-1 Master Clock Signals Timing Waveforms

4-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-2 Control Signals Timing Waveforms

4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-3 Serial Audio Port Slave Mode Timing Waveforms

4-5

. . . . . . . . . . . . . . . . . . . . . .

4-4 TAS3100 Serial Audio Port Master Mode Timing Waveforms

4-6

. . . . . . . . . . . . .

4-5 I

2

C SCL and SDA Timing Waveforms

4-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-6 I

2

C Start and Stop Conditions Timing Waveforms

4-8

. . . . . . . . . . . . . . . . . . . . . .

vii

List of Tables

Table

Title

Page

2-1 TAS3103 Throughput Latencies vs MCLK and LRCLK

2-13

. . . . . . . . . . . . . . . . .

2-2 TAS3103 Clock Default Settings

2-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3 I

2

C EEPROM Data

2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-4 Four Byte Write Exceptions--Reserved and Factory-Test I

2

C

Subaddresses

2-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-5 Four Byte Read Exceptions--Reserved and Factory-Test I

2

C

Subaddresses

2-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-6 GPIO Port Functionality--I

2

C Master Mode

2-25

. . . . . . . . . . . . . . . . . . . . . . . . . .

3-1 Biquad Filter Breakout

3-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2 Bass Shelf Filter Indices for 1/2-dB Adjustments

3-14

. . . . . . . . . . . . . . . . . . . . . .

3-3 Treble Shelf Filter Indices for 1/2-dB Adjustments

3-15

. . . . . . . . . . . . . . . . . . . . .

3-4 Volume Adjustment Gain Coefficients

3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5 DRC Example 2 Parameters

3-39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6 DRC Example 3 Parameters

3-41

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-7 DRC Example 4 Parameters

3-45

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-8 Mixer Gain Setting for LSB Dither Data Insertion

3-50

. . . . . . . . . . . . . . . . . . . . . .

viii

1-1

1 Introduction

The TAS3103 is a fully configurable digital audio processor that preserves high-quality audio by using a 48-bit data

path, 28-bit filter coefficients, and a single cycle 28 x 48-bit multiplier and 76-bit accumulator. Because of the

coefficient-configurable fixed-program architecture of the TAS3103, a complete set of user-specific audio processing

functions can be realized, with short development times, in a small, low power, low-cost device. A personal computer

(PC) GUI-based software development package and a comprehensive evaluation board provide additional facilities

to further reduce development times. The TAS3103 uses 1.8-V core logic with 3.3-V I/O buffers, and requires only

3.3-V power. The TAS3103 is available in a 38-pin TSSOP package.

1.1

Features

∑

Audio Input/Output

-

Four Serial Audio Input Channels

-

Three Serial Audio Output Channels

-

8-kHz to 96-kHz Sample Rates Supported

-

15 Stereo/TDM Data Formats Supported

-

Input/Output Data Format Selections Independent

-

16-, 18-, 20-, 24-, and 32-Bit Word Sizes Supported

∑

Serial Master/Slave I

2

C Control Channel

∑

Three Independent Monaural Processing Channels

-

Programmable Four Stereo Input Digital Mixer

-

3D Effect and Reverb Structure and Filters

-

Programmable 12 Band Digital Parametric EQ

-

Programmable Digital Bass and Treble Controls

-

Programmable Digital Soft Volume Control (24 dB to --

dB)

-

Soft Mute/Unmute

-

Programmable Dither

-

Programmable Loudness Compensation

-

VU Meter and Spectral Analysis I

2

C Output

-

Programmable Channel Delay (Up to 42 ms at 48 kHz)

-

192-dB Dynamic Range (Supports Up to 32-Bit Audio Data)

-

Dual Threshold Dynamic Range Compression/Expansion

∑

Electrical and Physical

-

Single 3.3-V Power Supply

-

38-Pin TSSOP Package

-

Low Power Standby

1-2

1.2

Terminal Assignments

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

SCLKIN

PWRDN

REGULATOR_EN

XTALI (1.8-V logic)

XTALO (1.8-V logic)

AVDD_BYPASS_CAP

A_VDDS (3.3 V)

AVSS

MCLKI

TEST

MICROCLK_DIV

I2C_SDA

I2C_SCL

SDIN1

SDIN2

SDIN3

SDIN4

GPIO0

GPIO1

LRCLK

ORIN

SCLKOUT2

SCLKOUT1

MCLKO

SDOUT3

SDOUT2

VDDS (3.3 V)

SDOUT1

DVDD_BYPASS_CAP

DVSS

I2CM_S

RST

CS1

CS0

PLL1

PLL0

GPIO3

GPIO2

DBT PACKAGE

(TOP VIEW)

1-3

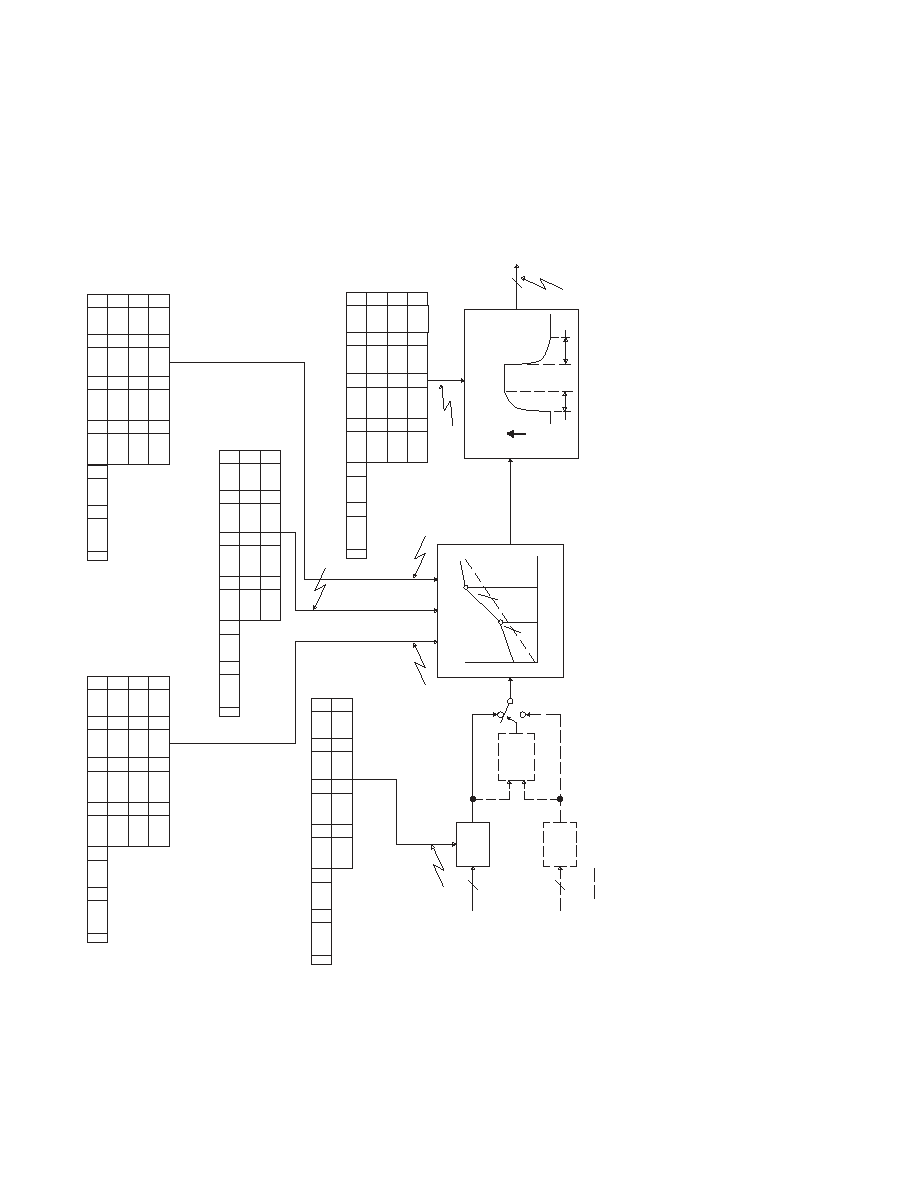

1.3

Hardware Block Diagram

SDIN1

COEF

RAM

Data

RAM

Code

ROM

Data

Path

Memory

Interface

Delay

Memory

(4K x 16)

8051

MCU

Control

Registers

Volume

Update

4

I2C_SCL

I2C_SDA

CS1

CS0

GPIO[3:0]

8

54

48

28

SDIN2

SDIN4

SDIN3

SDOUT1

SDOUT2

SDOUT3

LRCLK

SCLKIN

MCLKO

SCLKOUT1

SCLKOUT2

76-Bit

ALU

Digital Audio Processor

Serial

Audio

Port

Controller

(8-Bit)

4

External

Data

RAM

Internal

Data

RAM

Code

ROM

8

28

28

64

Oscillator

and

PLL

XTALI

XTALO

PWRDN

PLL0

PLL1

TEST

48

64

64

64

64

64

64

I2C

Serial

Interface

RST

I2CM_S

1-4

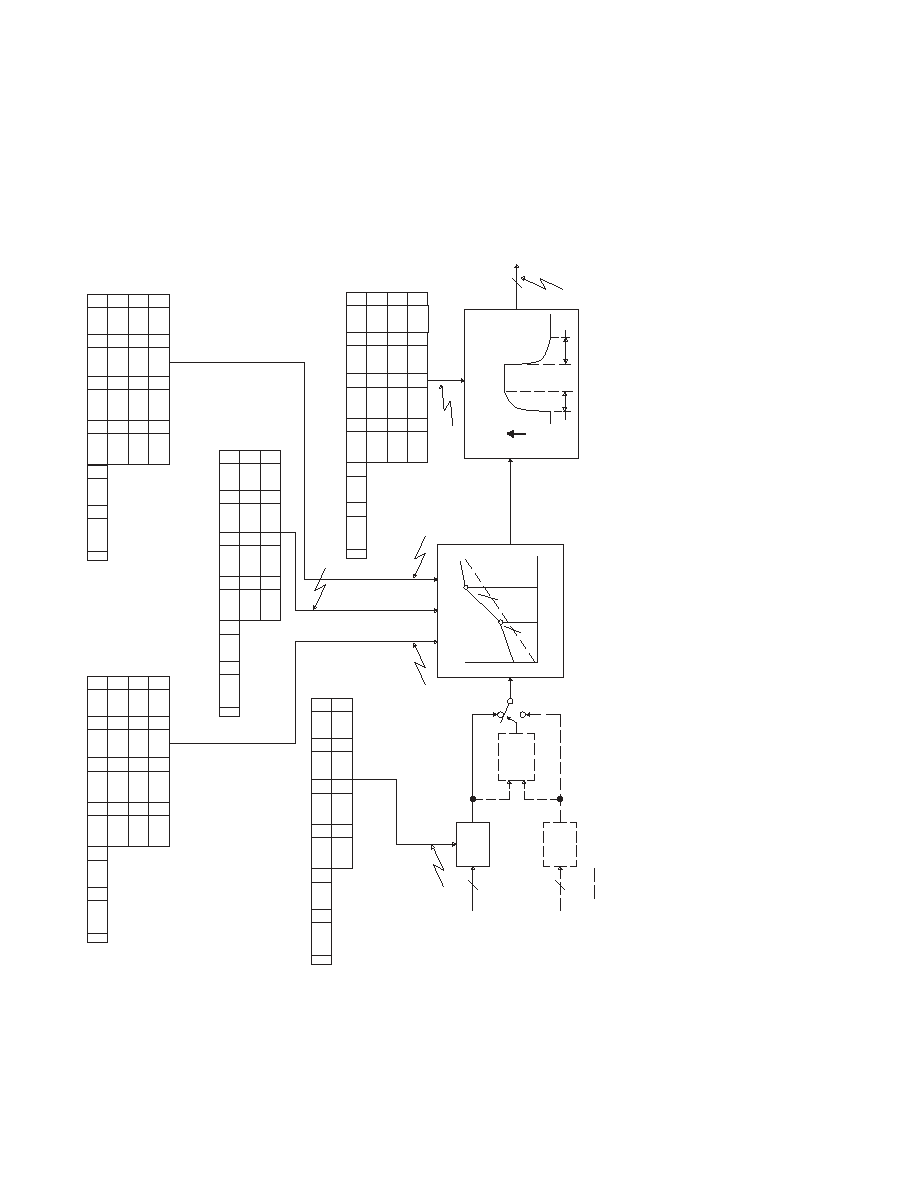

1.4

Functional Block Diagram

Cross-

bar

Mixer

Multi-

Mode

3D

Ef

fects

Block

Multi-

Mode

Serial

to

PCM

Input

Port

SDIN1

SDIN2

SDIN3

DRC

Center

Output

Cross-

bar

Multi-

plexer

Multi-

mode

PCM

to

Serial

Output

Port

PLL

and

Dividers

Oscillator

3 Mono Processing Channels

GPIO(3:0)

CS0

CS1

PLL1

VDDS

DVSS

XT

ALI

T

est

PWRDN

LRCLK

SCLKIN

SCLKOUT1

SCLKOUT2

MCLKO

DVDD_

BYP

ASS_

SDIN4

Input

T

reble

and

Soft

V

olume

Loudness

Compensation

Ganged

DRC

Delay

Programmable

Dither

Ch1

MCLKI

Ch1

Microprocessor

PLL0

MC/Div

V

oltage Regulation

XT

ALO

or

Spectrum Analyzer

Bass

12

Biquad

Filters

Ch2

Ch3

T

reble

and

Soft

V

olume

Loudness

Compensation

Bass

12

Biquad

Filters

T

reble

and

Soft

V

olume

Loudness

Compensation

Bass

12

Biquad

Filters

VU Meter

Delay

Delay

SDOUT1

SDOUT2

SDOUT3

ORIN

Programmable

Dither

Programmable

Dither

Ch2

Ch3

I2C_

SDA

I2C_

SCL

I2C_

M_S

CAP

A

VSS

A_VDDS

A

VDD_

BYP

ASS_

CAP

I2

S Clock Input/Generation

Ch3

RST

1-5

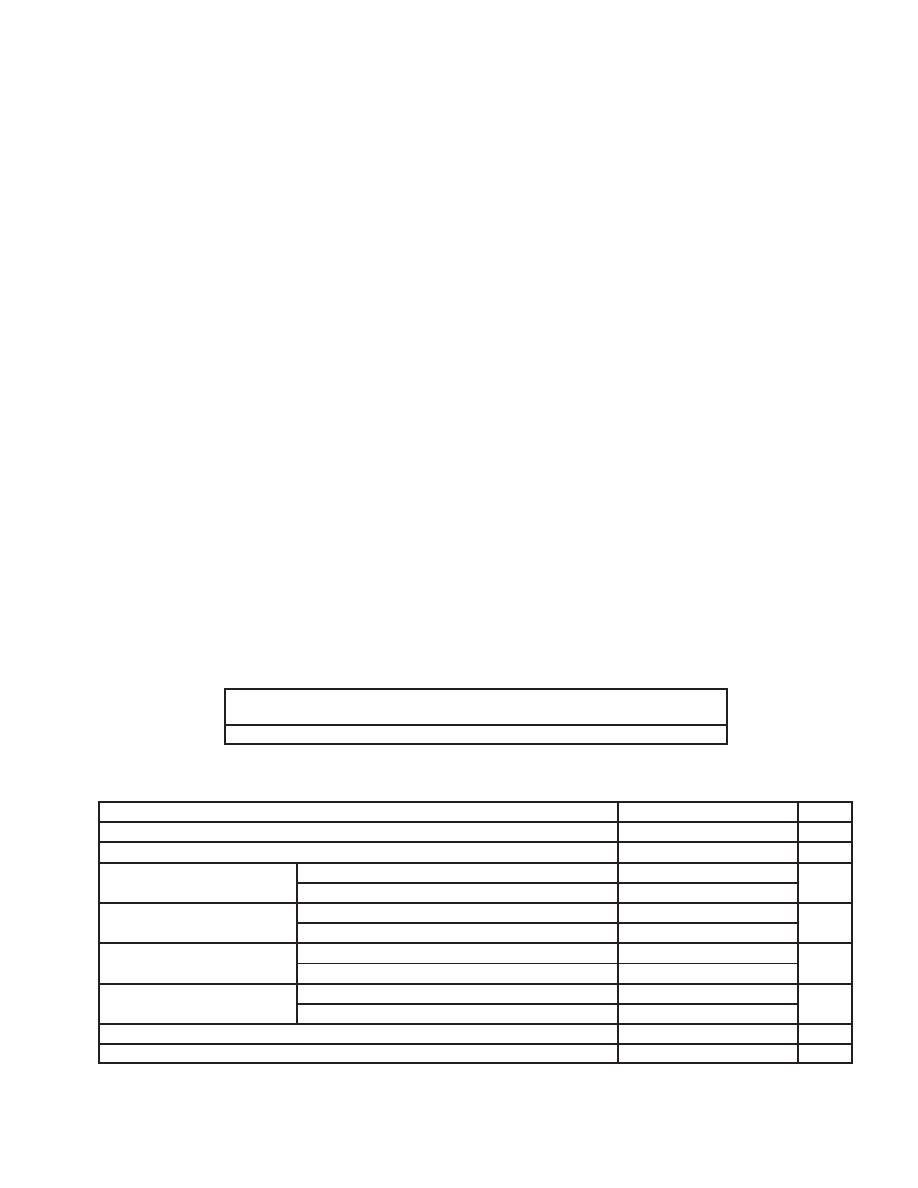

1.5

Ordering Information

TA

PLASTIC

38-PIN TSSOP

(DBT)

0

∞

C to 70

∞

C

TAS3103DBT

1.6

Terminal Functions

TERMINAL

DESCRIPTION

PULLUP/

(2)

NAME

NO.

I/O

TYPE(1)

DESCRIPTION

PULLUP/

DOWN(2)

A_VDDS (3.3 V)

7

PWR

The PWR pin is used to input 3.3-V power to the DPLL and clock oscillator.

This pin can be connected to the same power source used to drive the DVSS

power pin. To achieve low DPLL jitter, this pin should be bypassed to AVSS

with a 0.01-

µ

F capacitor (low ESR preferable).

None

AVDD_BYPASS_CAP

6

PWR

AVDD_BYPASS_CAP is a pinout of the internally regulated 1.8-VDC power

used by the DPLL and crystal oscillator. This pin should be connected to pin 8

with a 0.01-

µ

F capacitor (low ESR preferable). This pin must not be used to

power external devices.

None

AVSS

8

PWR

AVSS is the ground reference for the internal DPLL and oscillator circuitry.

This pin needs to reference the same ground as DVSS power pin. To achieve

low DPLL jitter, ground noise at this pin must be minimized. The availability of

the AVSS pin allows a designer to use optimizing techniques such as star

ground connections, separate ground planes, or other quiet ground

distribution techniques to achieve a quiet ground reference at this pin.

None

CS0

24

I

D

CS0 is the LSB of a 2-bit code used to generate part of an I2C device address

that makes it possible to address four TAS3103 ICs on the same bus without

additional chip select logic. The pulldowns on the inputs select 00 as a default

when neither pin is connected.

Pulldown

CS1

25

I

D

CS1 is the MSB of a 2-bit code used to generate part of an I2C device address

that makes it possible to address four TAS3103 ICs on the same bus without

additional chip select logic.

Pulldown

DVDD_BYPASS_CAP

29

PWR

DVDD_BYPASS_CAP is a pin-out of the internally regulated 1.8-V power

used by all internal digital logic. A low ESR capacitor in the range of 0.01

µ

F

should be connected between this pin and pin 28. This pin must not be used to

power external devices

None

DVSS

28

PWR

DVSS is the digital ground pin.

None

GPIO0

18

I/O

D

GPIO0 is a general-purpose I/O, controlled by the internal microprocessor

through I2C commands. When in the I2C master mode, GPIO0 serves as a

volume up command for CH1/CH2

Pullup

GPIO1

19

I/O

D

GPIO1 is a general-purpose I/O, controlled by the internal microprocessor

through I2C commands. When in the I2C master mode, GPIO1 serves as a

volume down command for CH1/CH2

Pullup

GPIO2

20

I/O

D

GPIO2 is a general-purpose I/O, controlled by the internal microprocessor

through I2C commands. When in the I2C master mode, GPIO2 serves as a

volume up command for CH3

Pullup

GPIO3

21

I/O

D

GPIO3 is a general-purpose I/O, controlled by the internal microprocessor

through I2C commands. When in the I2C master mode, GPIO3 serves as a

volume down command for CH3

Pullup

I2CM_S

27

I

D

I2CM_S is a non-latched input that determines whether the TAS3103 acts as

an I2C master or slave. Logic high, or no connection, sets the TAS3103 as an

I2C master device. A logic low sets the TAS3103 as an I2C slave device. As a

master I2C device, the TAS3103 I2C port must have access to an external

EEPROM for input.

Pullup

1-6

TERMINAL

PULLUP/

DOWN(2)

DESCRIPTION

NAME

PULLUP/

DOWN(2)

DESCRIPTION

TYPE(1)

I/O

NO.

I2C_SCL

13

I/O

D

I2C_SCL is the I2C clock pin. When the TAS3103 I2C port is a master,

I2C_SCL is (1/2N) x (1/(M+1)) x 1/10 times the microprocessor clock, where N

and M are set to 2 and 8 respectively. When the TAS3103 I2C port is a slave,

input clock rates up to 400 kHz can be supported. This pin must be provided an

external pullup (5 k

is recommended for most applications).

External

pullup

required

I2C_SDA

12

I/O

D

I2C_SDA is the I2C bidirectional data pin. The TAS3103 I2C port can support

data rates up to 400K bits/sec. This pin must be provided an external pullup

(5 k

is recommended for most applications).

External

pullup

required

LRCLK

38

I/O

D

LRCLK is either an input or an output, depending on whether the TAS3103 is in

a master or slave serial audio port mode.

Pulldown

MCLKI

9

I

D

MCLKI is a master clock input that provides an alternative to using a fixed

crystal frequency. In DPLL modes, the input frequency of this clock can range

from 2.8 MHz to 24.576 MHz. In PLL bypass mode, frequencies up to 147 MHz

can be used. Whenever MCLKI is not used and XTALI/XTALO provide the

master clock input, MCLKI must be grounded.

None

MCLKO

34

O

D

MCLKO is the master output clock pin. It is produced by dividing MCLKI/XTALI

by 1, 2, or 4 (depending on the setting of a subaddress control field). MCLKO is

provided to interconnect, without the need for additional glue logic, the

TAS3103 interfaces chips that require different multiples of the audio sample

rate (FS) as a master clock.

None

MICROCLK_DIV

11

I

D

MICROCLK_DIV sets the division ratio between the digital audio processing

clock and the internal microprocessor clock. The audio-processing clock is the

DPLL output clock if PLL_bypass is not enabled. The audio-processing clock

is MCLKI/XTALI master clock if PLL_bypass is enabled. Logic high on this pin

sets the microprocessor clock equal to the audio-processing clock. A logic low

sets the microprocessor clock to 1/4 the digital audio-processing clock.

MICROCLK_DIV must be set low if the audio processing clock is > 36 MHz.

MICROCLK_DIV must be set high if the audio processing clock is

36 MHz.

Pulldown

ORIN

37

I

D

ORIN allows the processing of a multichannel signal set through two

TAS3103s without any additional components. One use of ORIN would be to

fully emulate a 6-channel audio processor at speeds up to a 96-kHz sample

rate with only two TAS3103s and no glue logic.

The two-chip configuration is accomplished by wiring the SDOUT1 port of one

of the two TAS3103 chips to the ORIN port of the second TAS3103. Internal to

the chip, the ORIN input is OR'ed with internal SDOUT1 data to generate the

resulting output data on channel SDOUT1. For TDM output formats, the

SDOUT1 outputs of the two chips differ in phasing in both the left and right

channels to arrive at the proper composite output. For discrete outputs, one

chip contributes the left channel of the composite SDOUT1, and the other chip

contributes the right channel of the composite SDOUT1.

If not used, ORIN must be connected to ground.

Pulldown

PLL0

22

I

D

PLL0 is the LSB of a 2-bit code used to select four different modes of DPLL

multiplexer/input divider operation. PLL[1:0] values of 00, 01, and 10 select

the DPLL input clock to be MCLKI/XTALI divided by 1, 2, and 4 respectively. A

value of 11 results in MCLKI/XTALI being substituted for the DPLL output. The

pullup/pulldown combination provides a default of 01 when neither pin is

connected.

Pullup

PLL1

23

I

D

PLL1 is the MSB of a 2-bit code used to select four different modes of DPLL

multiplexer/input divider operation. PLL[1:0] values of 00, 01, and 10 select

the DPLL input clock to be MCLKI/XTALI divided by 1, 2, and 4 respectively. A

value of 11 results in MCLKI/XTALI being substituted for the DPLL output. The

pullup/pulldown combination provides a default of 01 when neither pin is

connected.

Pulldown

PWRDN

2

I

D

PWRDN powers down all logic and stops all clocks whenever logic high is

applied. However, the coefficient memory remains stable through a power

down cycle, as long as a reset is not sent after a power down cycle.

Pulldown

1-7

TERMINAL

PULLUP/

DOWN(2)

DESCRIPTION

NAME

PULLUP/

DOWN(2)

DESCRIPTION

TYPE(1)

I/O

NO.

REGULATOR_EN

3

I

D

REGULATOR_EN is only used in factory tests. This pin should always be tied

to ground.

None

RST

26

I

D

RST is the master reset input. Applying a logic low to this pin generates a

master reset. The master reset results in all coefficients being set to their

power-up default state, all data memories being cleared, and all logic signals

being returned to their default values.

Pullup

SCLKIN

1

I

D

SCLKIN is the serial audio port (SAP) input data clock. This clock is only used

when the SAP is a slave. In master mode, SCLKOUT1 internally provides the

serial input clock (SCLKOUT1 from a given TAS3103 must not be connected

to SCLKIN on the same TAS3103 chip).

Pulldown

SCLKOUT1

35

O

D

SCLKOUT1 is one of two serial output bit clocks. It is divided from

MCLKI/XTALI in master mode, and SCLKIN in slave mode. Subaddress

control fields determine the divide ratio in both cases. When the serial audio

port is in a master mode, SCLKOUT1 is used to receive incoming serial data

and should be wired to the data source(s) providing data to the SDIN inputs.

None

SCLKOUT2

36

O

D

SCLKOUT2 is one of two serial output bit clocks. It is divided from

MCLKI/XTALI in master mode, and SCLKIN in slave mode. Subaddress

control fields determine the divide ratio in both cases. SCLKOUT2 is always

used to clock out serial data from the three serial SDOUT output data

channels. SCLKOUT2 is provided separately from SCLKOUT1 to allow

discrete in to TDM out and TDM in to discrete out data format conversions

without the use of external glue logic.

Output

SDIN1

14

I

D

SDIN1, SDIN2, SDIN3, and SDIN4 are the four TAS3103 serial data input

ports. All four input ports support four discrete (stereo) data formats. SDIN1 is

the only data input port that also supports eleven time division multiplexed

data formats. All four ports are capable of receiving data with bit rates up to

24.576 MHz.

Pulldown

SDIN2

15

I

D

SDIN2 is one of the four TAS3103 serial data input ports. SDIN2 supports four

discrete (stereo) data formats, and is capable of receiving data with bit rates

up to 24.576 MHz.

Pulldown

SDIN3

16

I

D

SDIN3 is one of the four TAS3103 serial data input ports. SDIN4 supports four

discrete (stereo) data formats, and is capable of receiving data with bit rates

up to 24.576 MHz.

Pulldown

SDIN4

17

I

D

SDIN4 is one of the four TAS3103 serial data input ports. SDIN4 supports four

discrete (stereo) data formats, and is capable of receiving data with bit rates

up to 24.576 MHz.

Pulldown

SDOUT1

30

O

D

SDOUT1, SDOUT2, and SDOUT3 are the three TAS3103 serial data output

ports. All three output ports support four discrete (stereo) data formats.

SDOUT1 is the only data output port that also supports eleven time division

multiplexed data formats. All three ports are capable of outputting data at bit

rates up to 24.576 MHz.

None

SDOUT2

32

O

D

SDOUT2 is one of the three serial data output ports. SDOUT2 supports four

discrete (stereo) data formats, and is capable of outputting data at bit rates up

to 24.576 MHz.

None

SDOUT3

33

O

D

SDOUT3 is one of the three serial data output ports. SDOUT3 supports four

discrete (stereo) data formats, and is capable of outputting data at bit rates up

to 24.576 MHz.

None

TEST

10

I

D

TEST is only used in factory tests. This pin must be left unconnected or

grounded.

Pulldown

VDDS (3.3 V)

31

-

PWR

VDDS is the 3.3-V pin that powers (1) the 1.8 V internal power regulator used

to supply logic power to the chip and (2) the I/O ring. It is recommended that

this pin be bypassed to DVSS (pin 28) with a low ESR capacitor in the range of

0.01

µ

F.

None

1-8

TERMINAL

PULLUP/

DOWN(2)

DESCRIPTION

NAME

PULLUP/

DOWN(2)

DESCRIPTION

TYPE(1)

I/O

NO.

XTALI (1.8-V logic)

4

I

A

XTALO and XTALI provide a master clock for the TAS3103 via use of an

external fundamental mode crystal. XTALI is the 1.8-V input port for the

oscillator circuit. See Note 3 for recommended crystal type and accompanying

circuitry. This pin should be grounded when the MCLKI pin is used as the

source for the master clock.

None

XTALO (1.8-V logic)

5

O

A

XTALO and XTALI provide a master clock for the TAS3103 via use of an

external fundamental mode crystal. XTALO is the 1.8-V output drive to the

crystal. XTALO can support crystal frequencies between 2.8 MHz and

20 MHz. See Note 3 for recommended crystal type and accompanying

circuitry. This pin should be left unconnected in applications using an external

clock input to MCLKI

None

NOTES:

1. TYPE: A = analog; D = 3.3-V digital; PWR = power/ground/decoupling

2. All pullups are 20-

µ

A weak pullups, and all pulldowns are 20-

µ

A weak pulldowns. The pullups and pulldowns are included to assure

proper input logic levels if the pins are left unconnected (pullups => logic 1 input; pulldowns => logic 0 input). Devices that drive inputs

with pullups must be able to sink 20

µ

A while maintaining a logic 0 drive level. Devices that drive inputs with pulldowns must be able

to source 20

µ

A while maintaining a logic 1 drive level.

3. Crystal type and recommended circuit:

OSC

Circuit

XO

XI

C1

C2

rd

AVSS

TAS3103

∑

Crystal type = parallel-mode, fundamental-mode crystal

∑

r

d

= drive level control resistor--vendor specified

∑

C

L

= Crystal load capacitance (capacitance of circuitry between the two terminals of the crystal)

∑

C

L

= (C

1

◊

C

2

) / (C

1

+ C

2

) + C

S

(where C

S

= board stray capacitance ~2 pF)

-

Example: Vendor recommended C

L

= 18 pF, C

S

= 3 pF

C

1

= C

2

= 2 x (18 - 3) = 30 pF

1.7

Operational Modes

The TAS3103 operation is governed by I/O terminal voltage level settings and register / coefficient settings within the

TAS3103. The terminal settings are wholly sufficient to address all external environments - allowing the remaining

configuration settings to be determined by either I

2

C commands or by the content of an I

2

C serial EEPROM (when

the I

2

C master mode is selected).

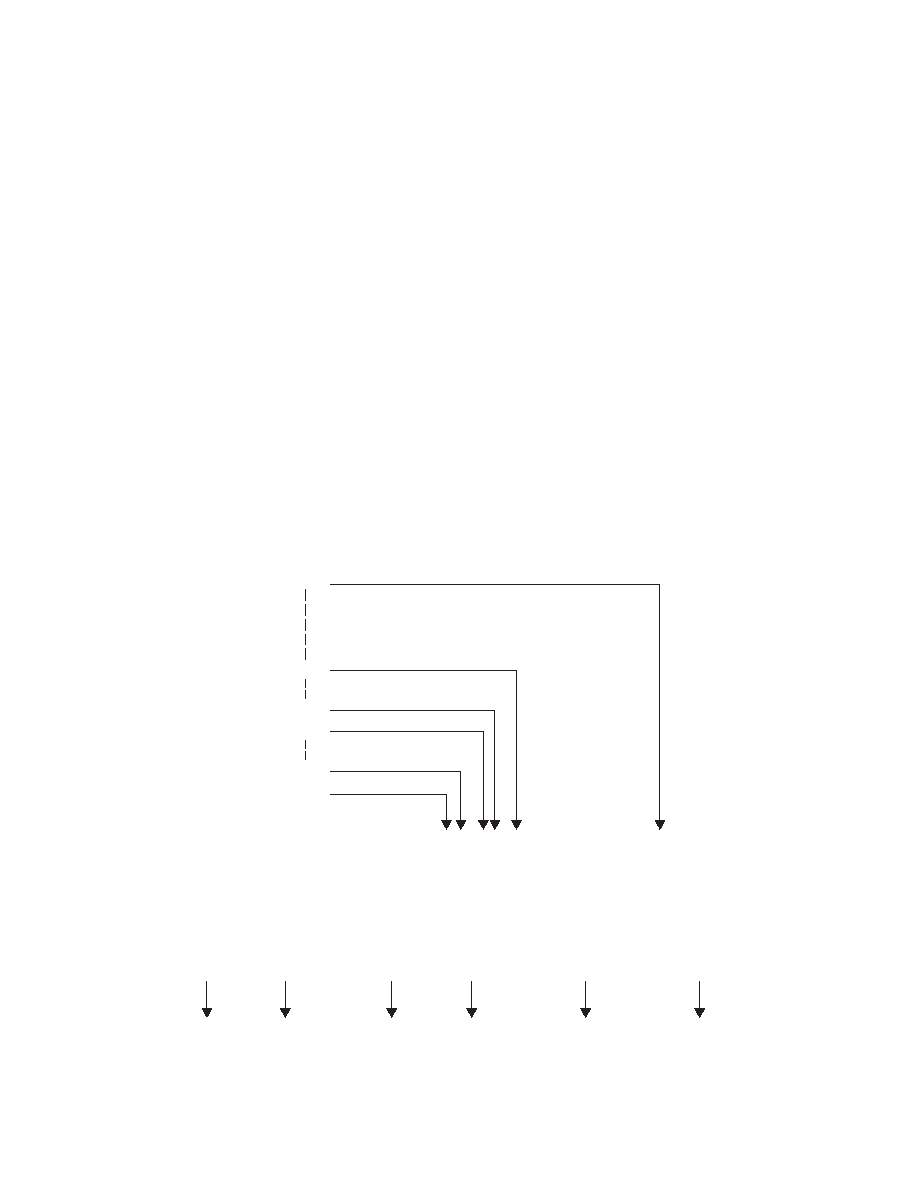

1-9

1.7.1

Terminal-Controlled Modes

1.7.1.1 Clock Control

PLL1

PLL0

DAP Clock

0

0

11 MCLK

0

1

(11 MCLK)/2

1

0

(11 MCLK)/4

1

1

MCLK (PLL bypass)

MICROCLK_DIV

MICROPROCESSOR CLOCK

0

DAP clock/4

1

DAP clock

XTALI

MCLKI

Reference

Divider

PLL

PLL0

Digital

Audio Processor

(DAP) Clock

Microprocessor

MICROCLK_DIV

Microprocessor

Clock

MCLK

PLL1

Scaler

˜

11

1.7.1.2 I

2

C Bus Setup

I2CM_S

I2C BUS MODE

0

Slave

1

Master

a6 = 0

a5 = 1

a4 = 1

a3 = 0

a2 = 1

a1=CS1

a0=CS0

R/W

ACK

SDA

SCL

1

2

3

4

5

6

7

8

9

Start

ŒŒŒ

ŒŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

ŒŒ

TAS3103 I2C Slave Address

1.7.1.3 Power-Down/Sleep Selection

PWRDN

POWER STATUS

0

Active

1

Power-down/sleep

1-10

1.7.2

I

2

C Bus-Controlled Modes

SUBADDRESS(es)

P

ARAMETER(s)

0x00

≠ Starting I

2

C Check W

ord

0xFC ≠ Ending I

2

C Check W

ord

S

Check words apply to

I2

C master mode only

S

In master I

2

C mode, the two check words are compared after EEPROM

download.

If comparison fails, a second attempt is made. If the second

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxxxxxx

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

download.

If comparison fails, a second attempt is made. If the second

comparison

fails, the parameters default to the slave default values.

S

In slave I

2

C mode, the default value for both check words is:

0x81_42_24_18

Input Mixer 28-Bit Gain Coef

ficients

0x01 - 0x33

Output Mixer 28-Bit Gain Coef

ficients

0x84 ≠ 0xA1

Gain Coefficient

(Format = 5.23)

28

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

Node

32 or 48

48

Node

Effects

Block BiQuad Filter Coefficients

0x34-0x4B

b

0

28

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

a

1

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

a

2

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

0

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

2

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

1

b

1

b

2

a

1

a

2

28

28

28

28

28

48

76

76

48

48

76

76

76

48

48

76

Magnitude

T

runcation

48

z

-1

z

-1

z

-1

z

-1

NOTE:

All gain coef

ficients 5.23 numbers.

Reverberation

Block Gains

Gain

Coef

ficient G0

Reverberation Block

Subaddress

Gain

Coef

ficient G0

(Format = 5.23)

Channel 1

0x4C

(Format = 5.23)

28

48

48

48

Channel 2

0x4D

48

48

48

Channel 3

0x4E

Gain

Coef

ficient G1

(Format = 5.23)

(Format = 5.23)

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

G0

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

G1

28

Reverberation

Delay

Reverberation Block

48

1-11

SUBADDRESS(es)

P

ARAMETER(s)

Cascaded

(T

welve/Channel) Main Filter BiQuads

MAIN FIL

TER

BLOCK

Subaddress

b

0

Channel 1

0x4F-0x5A

b

0

28

48

76

76

Magnitude

48

Channel 2

0x5B-0x66

28

48

76

76

Magnitude

T

runcation

48

Channel 3

0x67-0x72

b

1

a

1

T

runcation

b

1

a

1

28

28

z

-1

z

-1

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

a

1

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

a

2

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

0

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

2

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

b

1

NOTE: All gain coef

ficients 5.23 numbers

b

2

a

2

28

28

28

28

48

48

76

76

76

48

48

76

z

-1

z

-1

z

-1

z

-1

Bass and T

reble Gain Coefficients

Inline Gain Coeeficient

Channel 1 = 0x73

Inline Gain Coeeficient

(Format = 5.23)

28

Channel 2 = 0x74

Bass

T

reble

28

Channel 3 = 0x75

Bass

Shelf Filter

T

reble

Shelf Filter

Bypass Gain Coeeficient

(Format = 5.23)

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

Bypass Gain

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

Inline Gain

Bypass Gain Coeeficient

(Format = 5.23)

28

Bass and

T

reble

Block

1-12

Dynamic Range Control (DRC) Mixer Coef

ficients

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

m

s

b

S

Slave Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

W

ord1

m

s

b

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

W

ord2

CH1

0x76

= Mix u to i

0x79

= Mix j to i

CH2

0x77

= Mix v to k

0x7A

= Mix l to k

CH3

0x78

= Mix w to m

0x7B

= Mix n to m

CH1-

0x7C

W

ord 1

=

Mix j to o - Inline

W

ord 2

=

Mix j to o - Bypass

CH2-

0x7D

W

ord 1

=

Mix l to p - Inline

W

ord 2

=

Mix l to p - Bypass

CH1-

0x7E

W

ord 1

=

Mix n to q - Inline

W

ord 2

=

Mix n to q - Bypass

CH 1

Bass and

T

reble

Block

u

CH 1 Soft

V

olume

Loudness

j

Mix_u_to_i

Mix_j_to_i

i

Dynamic

Range Control

v

l

CH 2 Soft

V

olume

Loudness

Mix_v_to_k

k

Mix_l_to_k

Dynamic

Range Control

w

n

Loudness

Mix_w_to_m

m

Mix_n_to_m

Mix_j_to_o_via_DRC_mult

Mix_l_to_p_via_DRC_mult

o

p

DRC_bypass_1

DRC_bypass_2

Mix_n_to_q_via_DRC_mult

q

DRC_bypass_3

CH 2

Bass and

T

reble

Block

CH 3

Bass and

T

reble

Block

CH 3 Soft

V

olume

CH1

CH2

CH3

1-13

SUBADDRESS(es)

P

ARAMETER(s)

Dither Mix Gain Coefficients

Channel 1

0x7F = Mix Dither 1 to o - 28-Bit Coef

ficient

Channel 2

0x80 = Mix Dither 2 to p - 28-Bit Coef

ficient

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

o

Channel 1

Loudness / Soft V

olume

Processed Output

Dynamic

Range Control

Dither 1

Mix_Dither1_to_o

Dither-Processed

Audio Out _ CH

1

Channel 2

0x80 = Mix Dither 2 to p - 28-Bit Coef

ficient

Channel 3

0x81 = Mix Dither 3 to q - 28-Bit Coef

ficient

p

Channel 2

Loudness / Soft V

olume

Processed Output

Range Control

Mix_Dither2_to_p

Dither 2

Dither-Processed

Audio Out _ CH 2

q

Channel 3

Loudness / Soft V

olume

Processed Output

Dynamic

Range Control

Mix_Dither3_to_q

Dither 3

Dither-Processed

Audio Out _ CH

3

Channel

3 to Channel 1 and Channel 2 Mix Gain Coefficients

m

s

b

S

Slave

Addr

Ack

Sub-Addr

Ack

xxx

0000

Ack

xxxxxxxx

Ack

xxxxxxxx

Ack

xxxxxx

l

s

b

Ack

32-Bit T

runcate

Node o

Channel 1

Processed

Audio

Delay 1

Mix-Delay3_to_o

Channel 1

0x82 = Mix Channel 3 Output to o - 28-Bit Coef

ficient

Channel 2

0x83 = Mix Channel 3 Output to p - 28-Bit Coef

ficient

Mix-Delay3_to_o

Node p

Delay 2

Channel 2

Processed

Audio

32-Bit T

runcate

Mix-Delay3_to_p

Node q

Channel 3

Processed

Audio

Delay 3

32-Bit T

runcate

1-14

Soft V

olume and Loudness Subaddress

S

Slave

Addr

Ack

Sub-Addr

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

a

1

b

0

b

1

b

2

a

1

a

2

28

28

28

28

28

z

-1

z

-1

z

-1

z

-1

All biquad gain coef

ficients 5.23 numbers.

48

Loudness Compensation

48

48

AUDIO OUT

AUDIO IN

28

48

a

2

b

0

b

1

b

2

O

G

CH 1 = 0xA3

CH 2 = 0xA8

CH 3 = 0xAD

LO Is

A

25.23 Format Number

CH 1 = 0xA4

CH 2 = 0xA9

CH 3 = 0xAE

G Is

A

5.23 Format Number

CH 1 = 0xA5

CH 2 = 0xAA

CH 3 = 0xAF

O Is

A

25.23 Format Number

S

Slave Addr

Ack

Sub-Addr

Ack

00000000

Ack

00000000

Ack

Ack

xxxxxxxx

Ack

LO

MSBs

xxxxxxx

m

s

b

xxxxxxxx

xxxxxxxx

xxxxxxx

l

s

b

Ack

LO LSBs

xxxxxxxx

2

LO

CH 1 = 0xA2

CH 2 = 0xA7

CH 3 = 0xAC

LG Is

A

5.23 Format Number

LOUDNESS

BiQuad Coef

ficients

CH 1 = 0xA6

CH 2 = 0xAB

CH 3 = 0xB0

LG

( )

LG

Commanded 5.23

V

olume Command

S

Slave

Addr

Sub-Addr

xxxxxxxx

xxxxxxxx

xxxxxxxx

VCS

xxxxxxx

v

c

s

0xF1

Original

V

olume

Commanded

V

olume

VCS

= 0

t

t

r

ans

it

ion

= 2048/FS

VCS = 1

t

t

r

ans

it

ion

= 4096/FS

SOFT VOLUME

t

t

r

ans

it

ion

I

2

C Master Mode

I

2

C Slave Mode

V

olume Commands

- GPIO

T

erminals

GPIO0 - V

olume Up - CH1 / CH2

GPIO1 - V

olume Down - CH1 / CH2

GPIO2 - V

olume Up - CH3

GPIO3 - V

olume Down - CH1 / CH2

S

Slave

Addr

Ack

Sub-Addr

xxxxxxxx

xxxxxxxx

xxxxxxxx

xxxxx

CCC

HHH

321

Mute / Unmute Command

0xF0

CH 1 = 0xF2

CH 2 = 0xF3

CH 3 = 0xF4

Mute Command = 1 => 0x0000000 V

olume Control

V

olume

Command

V

olume Command

(5.23 Precision)

Note: Negative V

olume Commands Result In

Audio Polarity Inversion

= x16 Boost

MA

X

= 1/2

23

Cut

MA

X

(LSB)

= Zero Output For 0x0000000 V

olume Control

V

olume

Commands

I

2

C Bus

Ack

Ack

Ack

S

Slave

Addr

Ack

Sub-Addr

Ack

Ack

Ack

Ack

Ack

G

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

m

s

b

xxx

0000

S

Slave Addr

Ack

Sub-Addr

Ack

00000000

Ack

00000000

Ack

Ack

xxxxxxxx

Ack

0 MSBs

xxxxxxx

m

s

b

xxxxxxxx

xxxxxxxx

xxxxxxx

l

s

b

Ack

0 LSBs

xxxxxxxx

Ack

Ack

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

m

s

b

xxx

0000

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

m

s

b

xxx

0000

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

m

s

b

xxx

0000

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

m

s

b

xxx

0000

Ack

Ack

Ack

Ack

S

Slave

Addr

Ack

Sub-Addr

Ack

xxxxxxxx

xxxxxxxx

xxxxxx

l

s

b

m

s

b

xxx

0000

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

Ack

S

Slave Addr

Ack

Sub-Addr

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

Soft

V

olume

Loudness

S

Mute/Unmute = 0xF0

S

V

olume Slew Command = 0xF1

V

olume Command

Parameter

V

olume Command

Subaddress

CH1

CH2

CH3

0xF2

0xF3

0xF4

Parameter

Subaddress

CH1

CH2

CH3

LG

0xA2 0xA7 0xAC

LO

0xA3 0xA8 0xAD

G

0xA4 0xA9 0xAE

O

0xA5 0xAA 0xAF

BiQuad

0xA6 0xAB 0xB0

1-15

Subaddress -- Dynamic Range Control (DRC) Block

S

Slave

Addr

Ack

Sub-Addr

00000000

O1-MSBits

xxxxxxx

m

s

b

xxxxxxxx

Ack

Ack

00000000

Ack

Ack

Ack

xxxxxxxx

O1-LSBits

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

00000000

O2-MSBits

xxxxxxx

m

s

b

xxxxxxxx

Ack

00000000

Ack

Ack

Ack

xxxxxxxx

O2-LSBits

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

CH1/CH2

= 0xB4

CH3 = 0xB9

S

Slave

Addr

Ack

Sub-Addr

00000000

T1-MSBits

xxxxxxx

m

s

b

xxxxxxxx

Ack

Ack

00000000

Ack

Ack

Ack

xxxxxxxx

T1-LSBits

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

00000000

T2-MSBits

xxxxxxx

m

s

b

xxxxxxxx

Ack

00000000

Ack

Ack

Ack

xxxxxxxx

T2-LSBits

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

CH1/CH2

= 0xB2

CH3 = 0xB7

S

Slave

Addr

Ack

Sub-Addr

K0

Ack

Ack

Ack

Ack

Ack

K1

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

K2

Ack

Ack

Ack

Ack

CH1/CH2

= 0xB3

CH3 = 0xB8

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

xxxxxxxx

m

s

b

xxx

0000

m

s

b

xxx

0000

m

s

b

xxx

0000

S

Slave

Addr

Ack

Sub-Addr

aa

Ack

Ack

Ack

Ack

Ack

1-aa

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

ad

Ack

Ack

Ack

Ack

CH1/CH2

= 0xB5

CH3 = 0xBA

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

xxxxxxxx

m

s

b

xxx

0000

m

s

b

xxx

0000

m

s

b

xxx

0000

1-ad

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

S

Slave

Addr

Ack

Sub-Addr

00000000

ae

xxxxxxx

m

s

b

xxxxxxxx

Ack

Ack

00000000

Ack

Ack

Ack

xxxxxxxx

1-ae

xxxxxxxx

xxxxxxx

l

s

b

Ack

xxxxxxxx

Ack

Ack

Ack

CH1/CH2

= 0xB1

CH3 = 0xB6

Cut

Attack / Decay Control

V

olume

t

a

-1/[F

S

x ln(1-aa)]

t

d

-1/[F

S

x ln(1-ad)]

t

a

t

d

DRC-Derived

Gain Coef

ficient

28

5.23 Format

5.23 Format

5.23 Format

25.23

Format

25.23

Format

K2

T2

K1

K0

T1

{

O1

{

O2

Compression / Expansion

Coef

ficient Computation

NOTE: Compression / Expansion / Compression Displayed

t

Window

-1/[F

S

x ln(1-ae)] Where F

S

= Audio Sample Frequency

ae and (1-ae) Set T

i

me Window Over Which RMS V

alue is Computed

Applies to DRC Servicing CH1/CH2 Only

Comparator

RMS

V

oltage

Estimator

RMS

V

oltage

Estimator

5.23 Format

32

32

Audio Input

CH1 or CH3

Audio Input

CH2

1-16

Spectrum

Analyzer/VU Meter

Spectrum Analyzer/VU Meter

BiQuad 1 to 10 Subaddresses = 0xBC to 0xC5

S

Slave

Addr

Ack

Sub-Addr

a

1

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

a

2

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

b

0

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

b

1

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

b

2

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

BiQuad 1

RMS V

oltage

Estimator

Spectrum

Analyzer / VU Meter

Log

RMS Window T

ime Constant Subaddress = 0xBB

BiQuad 1

RMS V

oltage

Estimator

RMS V

oltage

Log

S

Slave

Addr

Ack

Sub-Addr

asa

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

1-asa

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

BiQuad 2

BiQuad 3

BiQuad 4

r

RMS V

oltage

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Log

Log

Log

Spectrum

Analyzer Output Subaddress = 0xFD

BiQuad 4

s

coder

RMS V

oltage

Estimator

Log

S

Slave

Addr

Ack

Sub-Addr

BiQuad

1

Ack

Ack

xxxxx.xxx

BiQuad 2

Ack

xxxxx.xxx

BiQuad 3

Ack

xxxxx.xxx

BiQuad 4

Ack

xxxxx.xxx

BiQuad 5

Ack

xxxxx.xxx

BiQuad 6

Ack

xxxxx.xxx

BiQuad 7

Ack

xxxxx.xxx

BiQuad 8

Ack

xxxxx.xxx

BiQuad 9

Ack

xxxxx.xxx

BiQuad 10

Ack

xxxxx.xxx

BiQuad 5

BiQuad 6

BiQuad 7

BiQuad 9

BiQuad 10

s

t

Sub-Address Decod

BiQuad 8

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Estimator

RMS V

oltage

Estimator

t Window

-1/[F

S

x ln(1-asa)] Where F

S

= Audio Sample Frequency

asa and (1-asa) Set T

ime Window Over Which RMS V

alue Is

Computed

I2

C Bus

Log

Log

Log

Log

Log

Log

VU Meter Output = 0xFE

S

Slave

Addr

Ack

Sub-Addr

VU Meter Output 1

(BiQuad 5)

Ack

Ack

xxxxx.xxx

Ack

xxxxx.xxx

VU Meter Output 1

(BiQuad 6)

1-17

Dither Block

S

Slave

Addr

Ack

Sub-Addr

Distribution 1 Mix

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

Distribution 2 Mix

Ack

Ack

Ack

Ack

xxxxxxxx

xxxxxxx

l

s

b

xxxxxxxx

m

s

b

xxx

0000

LFSR1 Mix and LFSR2 Mix Are 5.23 Format Coef

ficients

S

Slave Addr

Ack

Sub-Addr

Dither Seed

Ack

Ack

Ack

Ack

Ack

xxxxxx

l

s

b

00000000

00000000

m

s

b

xxxxxx

l

s

b

m

s

b

0xC6

0xC7

Condensed

LFSR2

Seed

Condensed

LFSR1

Seed

Linear Feedback Shift Register Block

Dither 1

Dither 2

Dither 3

LFSR1

LFSR2

Seed Build Logic

L

- W 0 +W

0.25

0.5

p

Output

Sampler

S

t1

S

t2

S

t3

S

t4

S

t5

S

t6

NOTE: W = 16.0 => 0x000008000000 in 25.23 Format

O

G

I

C

1-18

GPIO and W

atchdog T

imer Subaddresses

SUBADDRESS(es)

P

ARAMETER(s)

0xC8-0xC9

Factory T

est Subaddresses

0xCA-0xCF

SDIN4 Input Mixers

0xD0-0xD1

CH1/CH2 to CH3

After Effects

Mixers

0xD2-0xEA

Reserved

GPIO0

GPIO1

GPIO2

GPIO3

D

Q

D

Q

D

Q

D

Q

Sample

Logic

0xEF

Down

Counter

LD

LRCLK

Decode 0

W

atchdog

Counter

Reset

0xEB

PWRDN

DA

T

A

P

A

TH

SWITCH

Reset

GPIODIR

3

READ

EN

Determines

How Many Consecutive Logic 0 Samples

(Where Each Sample Is Spaced by GPIOFSCOUNT LRCLKs)

Are Required to Read a Logic 0 on a GPIO Input Port

S

Slave Addr

Sub-Addr

Ack

00000000

Ack

Ack

21

0

0000

Ack

GPIOFSCOUNT

Ack

GPIO_samp_int

Ack

31

24

23

20

19

16

15

8

7

0

S

Slave Addr

Sub-Addr

Ack

00000000

Ack

Ack

31

24

00000000

23

16

Ack

00000000

15

8

Ack

0000000x

70

Ack

1 (Default State)

Disables W

atchdog

T

imer

Decode 2

16

Microprocessor

Clock

Microprocessor

Microprocessor

Firmware

Microprocessor

Bus

Microprocessor

Control

0xEE

GPIO_in_out

3

S

Slave Addr

Sub-Addr

Ack

00000000

Ack

Ack

21

0

Ack

31

24

23

16

0

00000000

15

8

00000000

Ack

74

0000

Ack

3

I2

C Slave Mode

and

I2

C Master Mode

W

rite

I2

C Master

Mode Read

1-19

SUBADDRESS(es)

P

ARAMETER(s)

0xEC-0xED

Reserved/Factory

T

est Subaddresses

0xEE-0xEF--See Subaddress 0xEB

GPIO Port I/O V

alues and GPIO Parameters

0xF0--See Subaddress 0xA2

Master Mute/Un-Mute

0xF1--Also See Subaddress 0xA2 and Subaddress 0xF5

S

Slave

Addr

Ack

Sub-Addr

t T

r

ans

ition

= TBLC[7:0] x 1/LRCLK

Ack

Ack

Ack

Ack

Ack

xxxxxxxx

0000000

v

s

c

00000000

00000000

T

reble and Bass

Slew Rate

TBLC[7:0]

0xF1

31

24

23

16

15

8

7

0

Bass

Filter Set N

T

reble

Filter Set N

t T

r

ans

ition

= TBLC[7:0] x 1/LRCLK

0xF2-0xF4--See

Subaddress 0xA2

CH1-CH3 V

olume CMDS

1-20

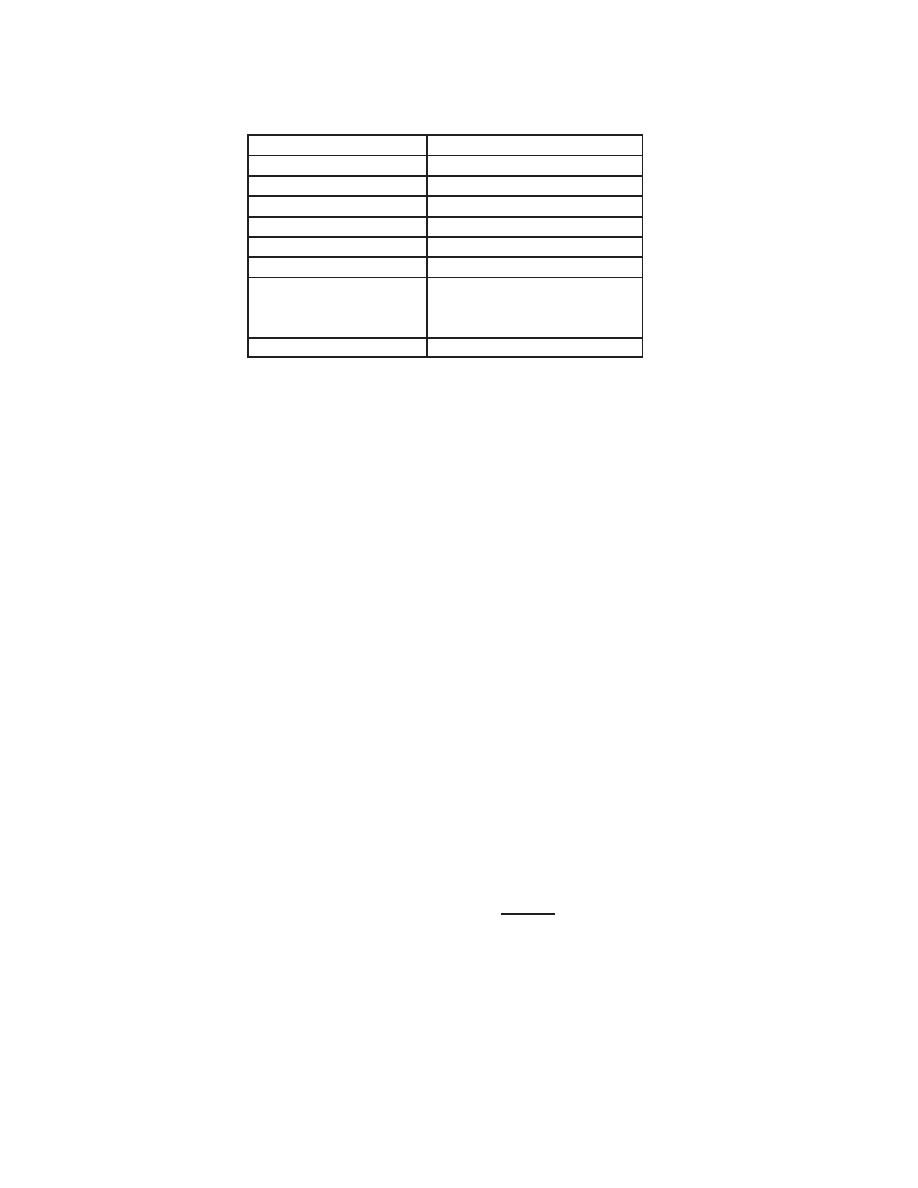

Subaddress--Bass and Treble Shelf Filter Parameters

S

Slave Addr

Ack Sub-Addr Ack

Ack

Ack

00000xxx

00000000

0xF5

CH3

Ack

00000xxx

CH2

Ack

00000xxx

CH1

S

Slave Addr

Ack Sub-Addr Ack

Ack

Ack

00000xxx

00000000

0xF7

CH3

Ack

00000xxx

CH2

Ack

00000xxx

CH1

S

Slave Addr

Ack Sub-Addr Ack

Ack

Ack

xxxxxxxx

00000000

0xF6

Ack

xxxxxxxx

Ack

xxxxxxxx

S

Slave Addr

Ack Sub-Addr Ack

Ack

Ack

xxxxxxxx

00000000

0xF8

Ack

xxxxxxxx

Ack

xxxxxxxx

CH1

Treble Shelf Selection (Filter Index)

CH2

CH3

CH1

CH2

CH3

Bass Shelf Selection (Filter Index)

Treble Filter Set Selection

Bass Filter Set Selection

BASS

FILTER 5

BASS

FILTER 4

BASS

FILTER 3

BASS

FILTER 2

BASS

FILTER 1

TREBLE

FILTER 5

TREBLE

FILTER 3

TREBLE

FILTER 1

TREBLE

FILTER 4

TREBLE

FILTER 2

MID-BAND

MAX BOOST

SHELF

MAX CUT

SHELF

Treble & Bass Filter Set Commands

0 => No Change

1 - 5 => Filter Sets 1 - 5

6 - 7 => Illegal (Behavior Indeterminate)

Treble & Bass Filter Shelf Commands

0 =>

Illegal (Behavior Indeterminate)

1 - 150 => Filter Shelves 1 - 150

1 => +18-dB Boost

150 => -18-dB Cut

151 - 255 => Illegal (Behavior Indeterminate)

FREQUENCY

S

Slave Addr

Ack Sub-Addr Ack

Ack

Ack

00000000

00000000

0xF1

Ack

0000000

Ack

xxxxxxxx

Treble/Bass Slew Rate = TBLC

(Slew Rate = TBLC/FS,

Where FS = Audio Sample Rate)

Treble/Bass Slew Rate Selection

V

C

S

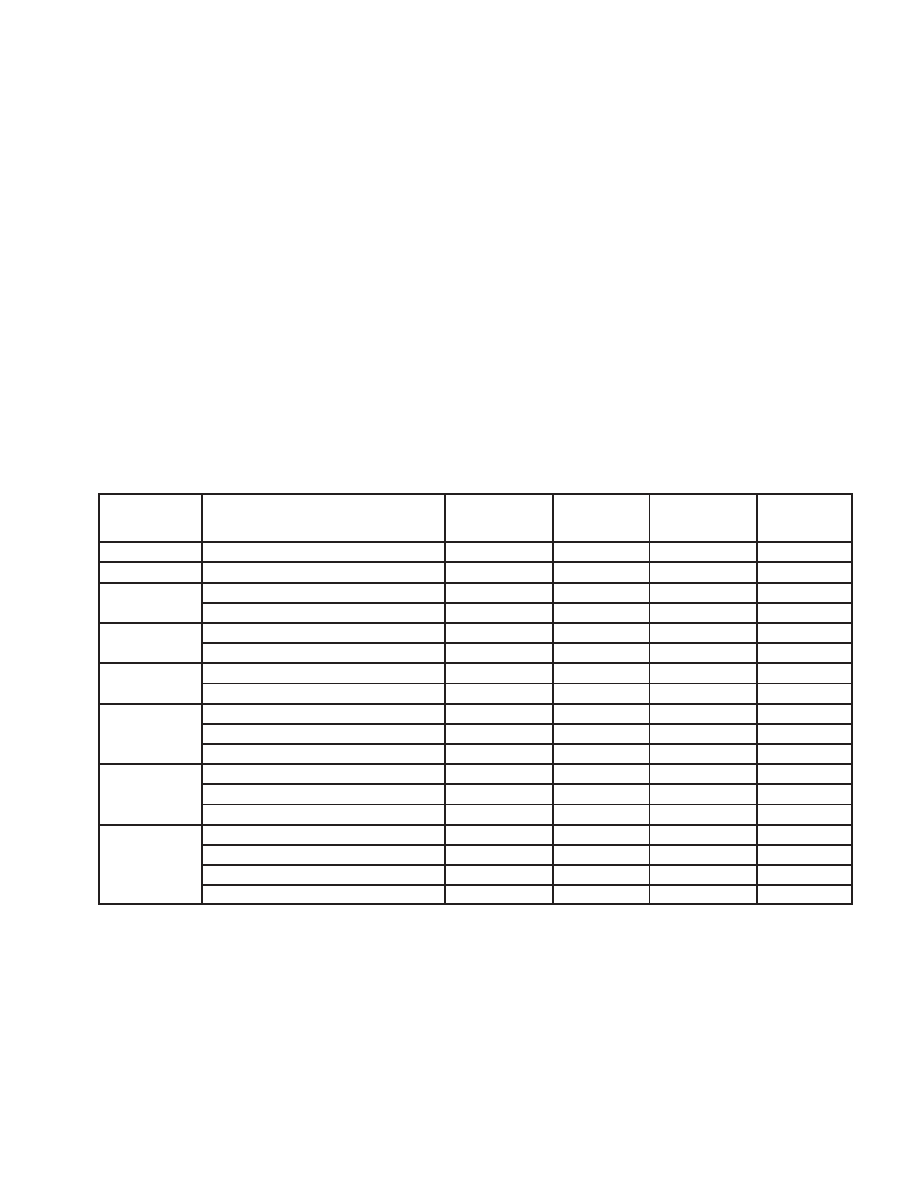

0

7

FS

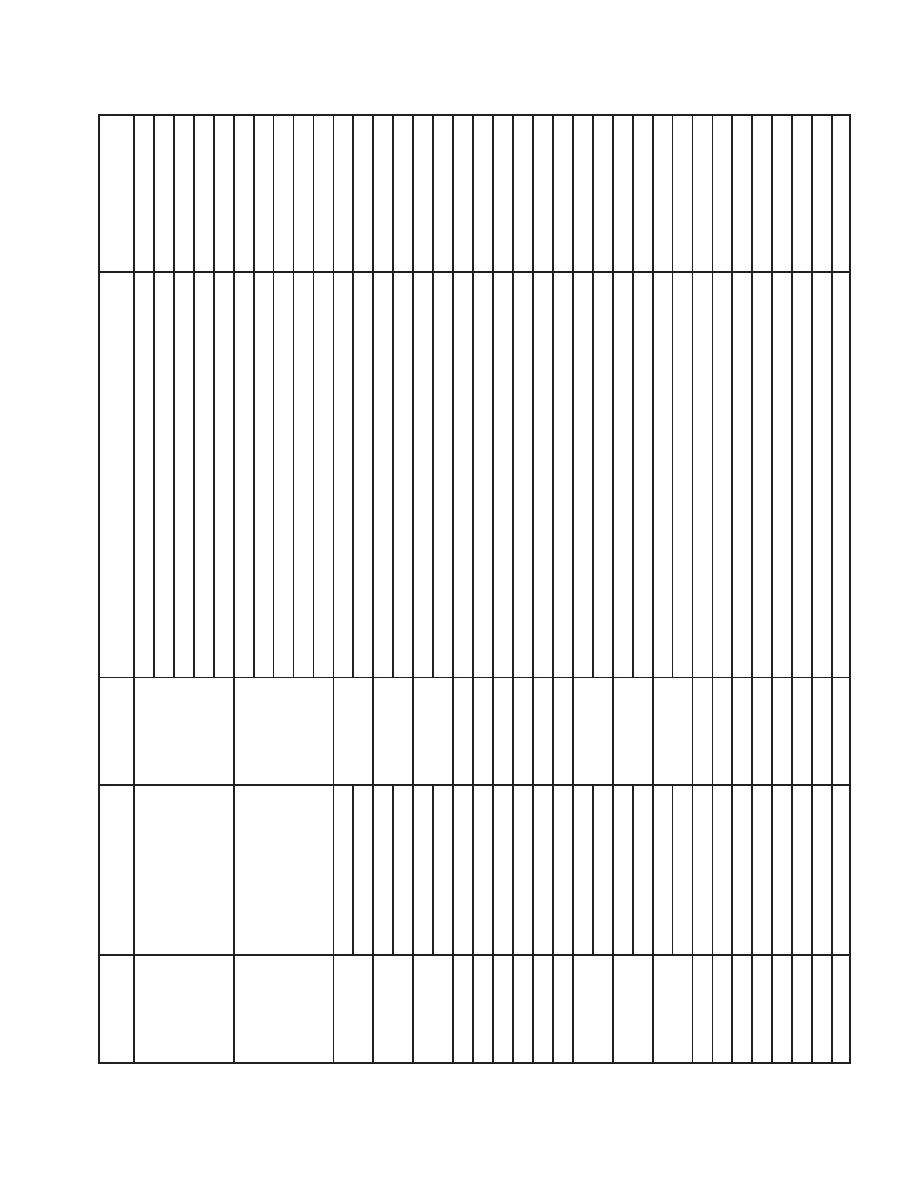

3-dB CORNERS (kHz)

FS

(LRCLK)

FILTER SET 5

FILTER SET 4

FILTER SET 3

FILTER SET 2

FILTER SET 1

(LRCLK)

BASS

TREBLE

BASS

TREBLE

BASS

TREBLE

BASS

TREBLE

BASS

TREBLE

96 kHz

0.25

6

0.5

12

0.75

18

1

24

1.5

36

88.4 kHz

0.23

5.525

0.46

11.05

0.691

16.575

0.921

22.1

1.381

33.15

64 kHz

0.167

4

0.333

8

0.5

12

0.667

16

1

24

48 kHz

0.125

3

0.25

6

0.375

9

0.5

12

0.75

18

44.1 kHz

0.115

2.756

0.23

5.513

0.345

8.269

0.459

11.025

0.689

16.538

32 kHz

0.083

2

0.167

4

0.25

6

0.333

8

0.5

12

24 kHz

0.063

1.5

0.125

3

0.188

4.5

0.25

6

0.375

9

22.05 kHz

0.057

1.378

0.115

2.756

0.172

4.134

0.23

5.513

0.345

8.269

16 kHz

0.042

1

0.083

2

0.125

3

0.167

4

0.25

6

12 kHz

0.031

0.75

0.063

1.5

0.094

2.25

0.125

3

0.188

4.5

11.025 kHz

0.029

0.689

0.057

1.378

0.086

2.067

0.115

2.756

0.172

4.134

1-21

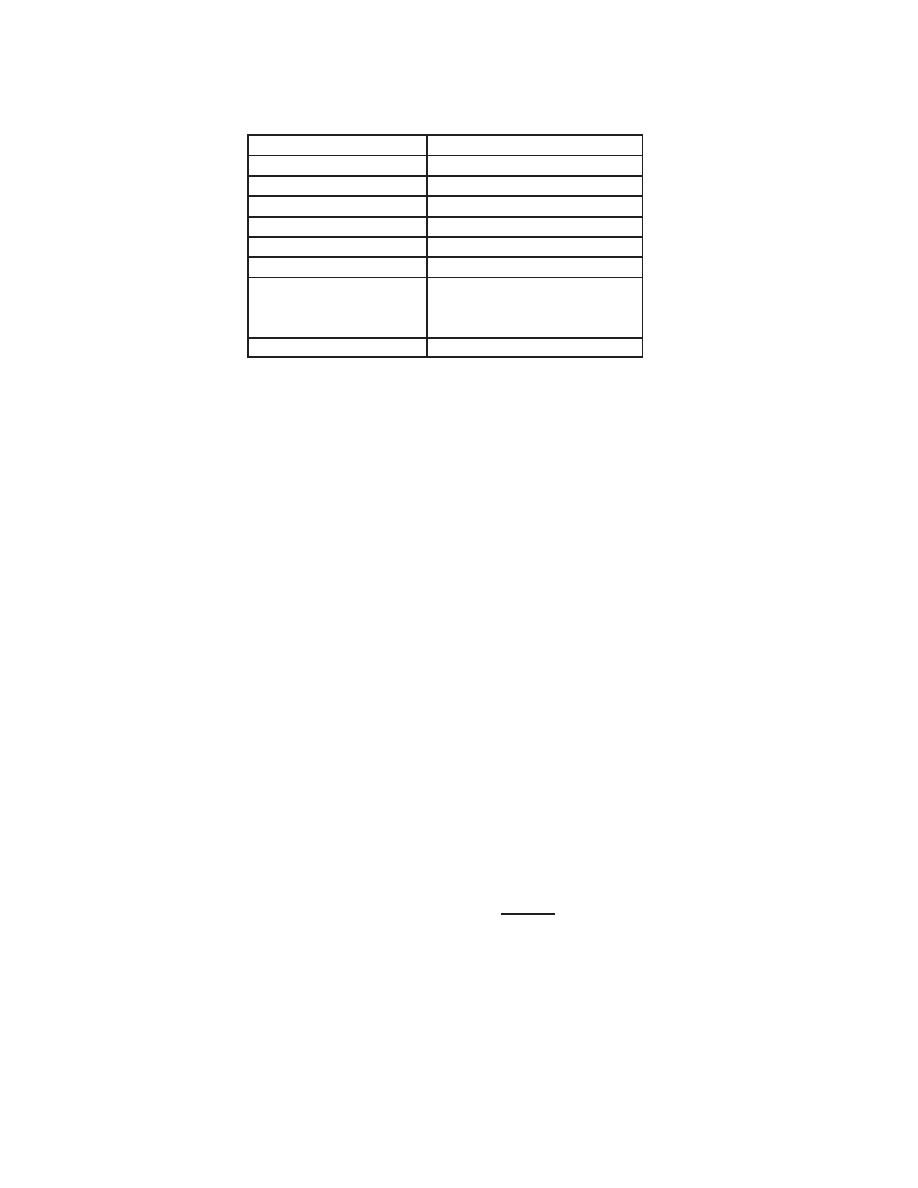

W

ord Size Code

I

2

S FORMA

T

,

CLOCK MANAGEMENT

, AND I

2

C M AND N ASSIGNMENTS

n[2:0]

0

2

m[3:0]

3

6

OSC

XT

ALI

0

1

2

3

MCLKO

0

1

2

PLL0

x1

1

PLL

MUX

MUX

PLL

BYP

ASS

Digital Audio

Processor

Clock

PLL[1:0]

1

0

MUX

MICROCLK_DIV

1/(M+1)

I2C_SDA

0

1

2

3

4

5

6

7

MUX

MUX

CR

YST

AL

0

1

2

3

MUX

1

0

MUX