| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: UCC3973 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

UCC1972/3

UCC2972/3

UCC3972/3

DESCRIPTION

Design goals for a Cold Cathode Fluorescent Lamp (CCFL) converter used

in a notebook computer or portable application include small size, high effi-

ciency, and low cost. The UCC3972/3 CCFL controllers provide the neces-

sary circuit blocks to implement a highly efficient CCFL backlight power

supply in a small footprint 8 pin TSSOP package. The BiCMOS controllers

typically consume less than 1mA of operating current, improving overall

system efficiency when compared to bipolar controllers requiring 5mA to

10mA of operating current.

External parts count is minimized and system cost is reduced by integrat-

ing such features as a feedback controlled PWM driver stage, open lamp

protection, startup delay and synchronization circuitry between the buck

and push-pull stages. The UCC3972/3 include an internal shunt regulator,

allowing the part to operate with input voltages from 4.5V up to 25V. The

part supports both analog and externally generated low frequency dimming

modes of operation.

The UCC3973 adds a programmable voltage clamp at the BUCK pin. This

feature can be used to protect the transformer from overvoltage during

startup or when an open lamp occurs. Transformer voltage is controlled by

reducing duty cycle when an over-voltage is detected.

BiCMOS Cold Cathode Fluorescent Lamp Driver Controller

FEATURES

∑ 1mA Typical Supply Current

∑ Accurate Lamp Current Control

∑ Analog or Low Frequency Dimming

Capability

∑ Open Lamp Protection

∑ Programmable Startup Delay

∑ 4.5V to 25V Operation

∑ PWM Frequency Synchronized to

External Resonant Tank

∑ 8 Pin TSSOP and SOIC Packages

Available

∑ Internal Voltage Clamp Protects

Transformer from Over-voltage

(UCC3973)

SLUS252A - JANUARY 2000

3

8

6

5

VBAT

4

2

1

7

VDD

GND

MODE

COMP

BUCK

OUT

FB

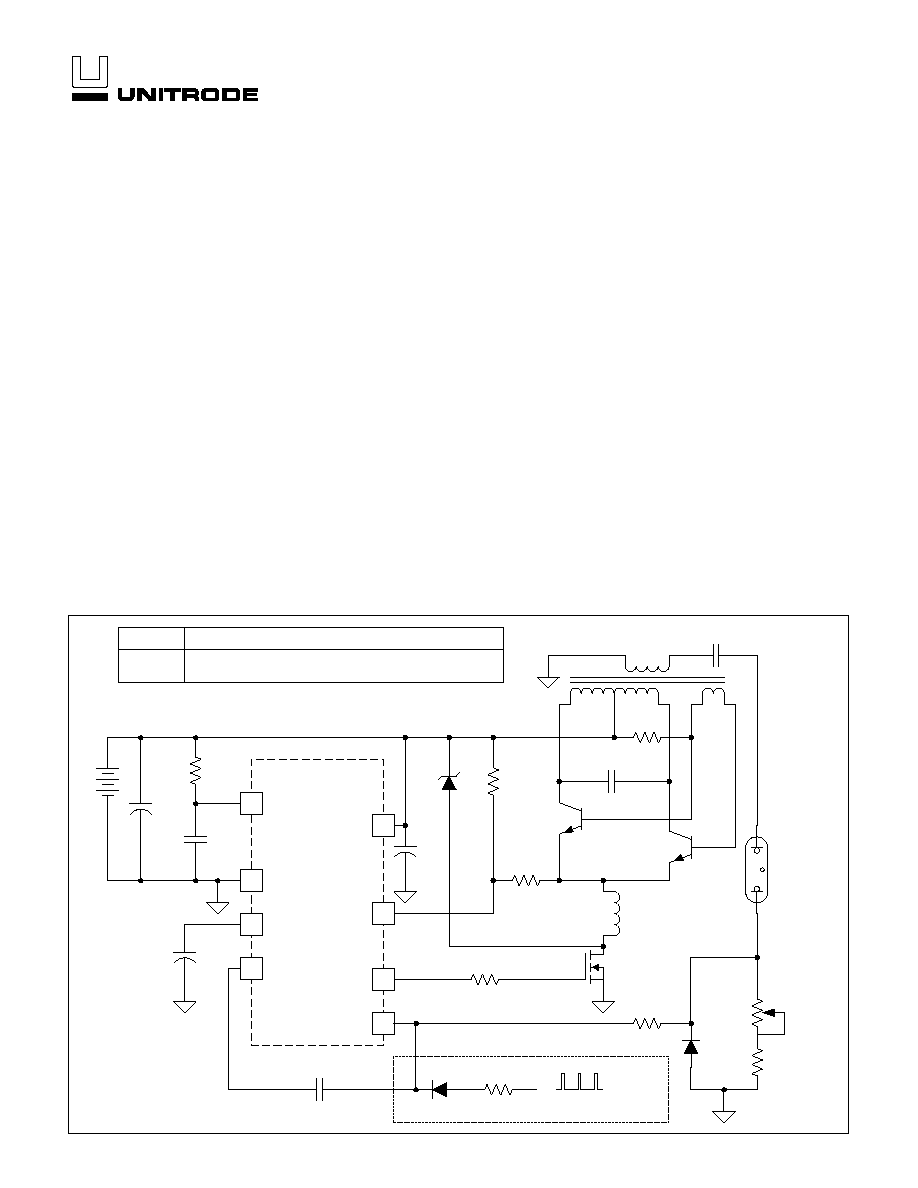

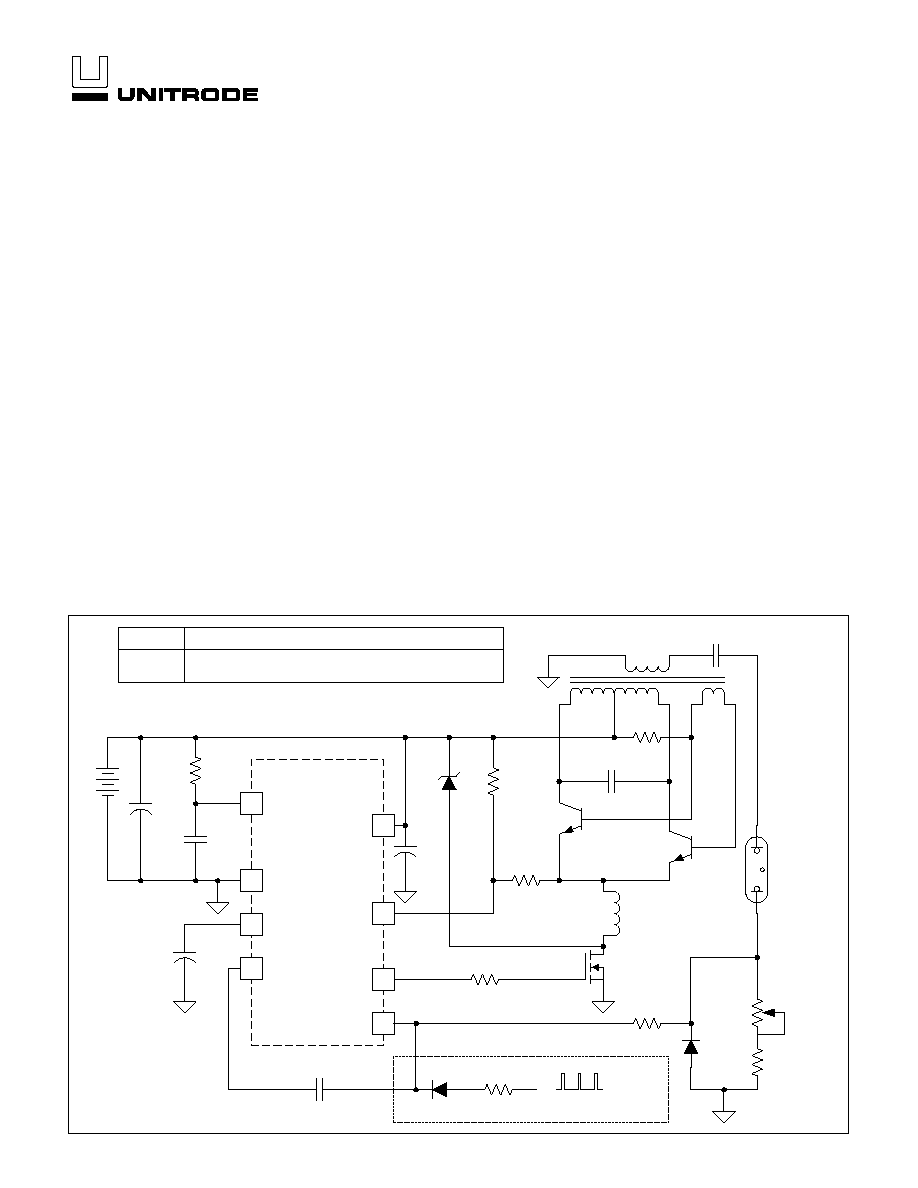

C7

0.1

µF

D1

R10

R11

Q3

C5 0.1

µF

L1

68

µH

R6 75

Q2

R2 1k

T1

C6 27pF

LAMP

HV

LAMP

LV

R3 68k

D2

R5 10k

R4 750

ANALOG

DIMMING

D

LFD

R

LFD

68k

0V-5V LOW FREQUENCY CONTROL SIGNAL

C4 33nF

LOW FREQUENCY DIMMING

C2

1

µF

R1

1k

C1

6.8

µF

SYSTEM VOLTAGE

(4.5V TO 25V)

C3

1

µF

UCC3972

UCC3973

NO INTERNAL VOLTAGE CLAMP

INTERNAL VOLTAGE CLAMP LIMITS TRANSFORMER

VOLTAGE AT START-UP OR DURING FAULT

UCC3972/3

TYPICAL APPLICATION CIRCUIT

UDG-99154

2

UCC1972/3

UCC2972/3

UCC3972/3

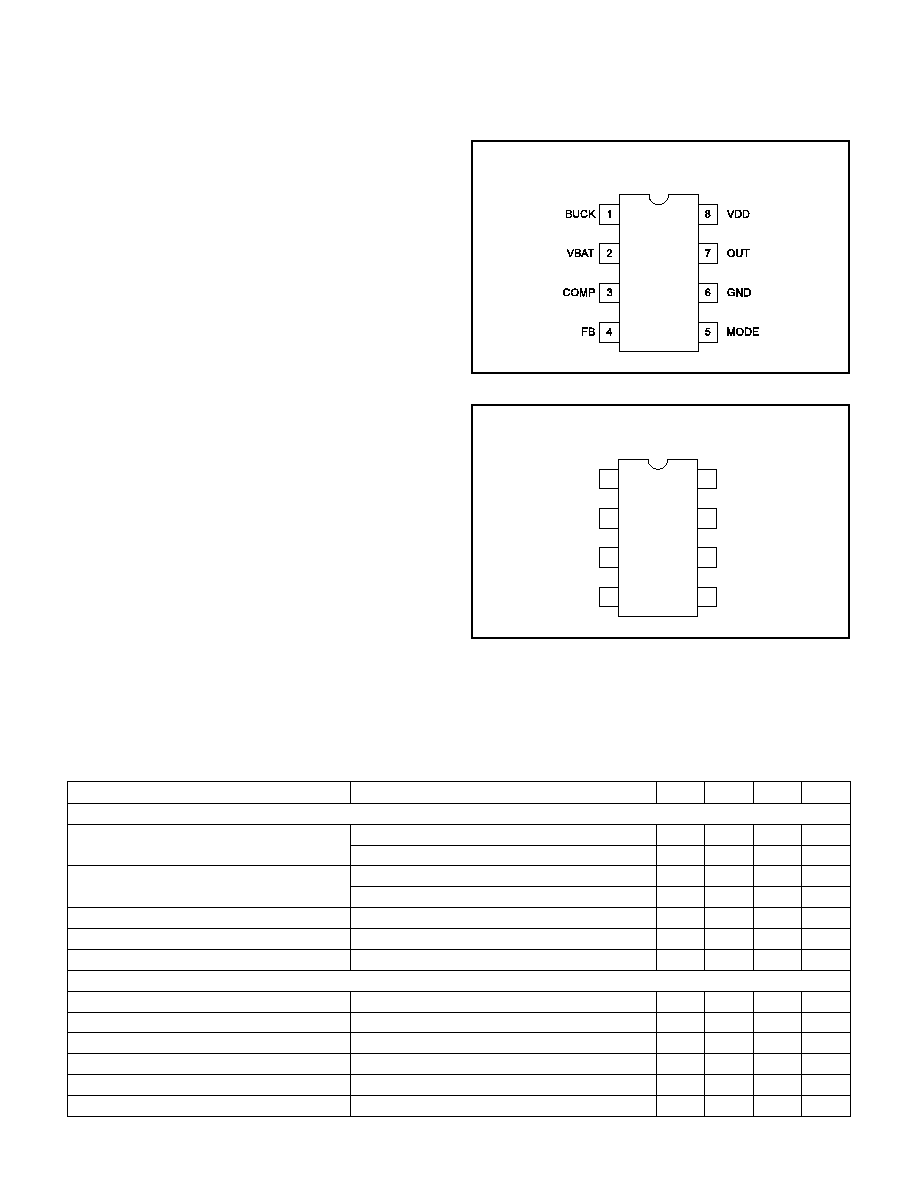

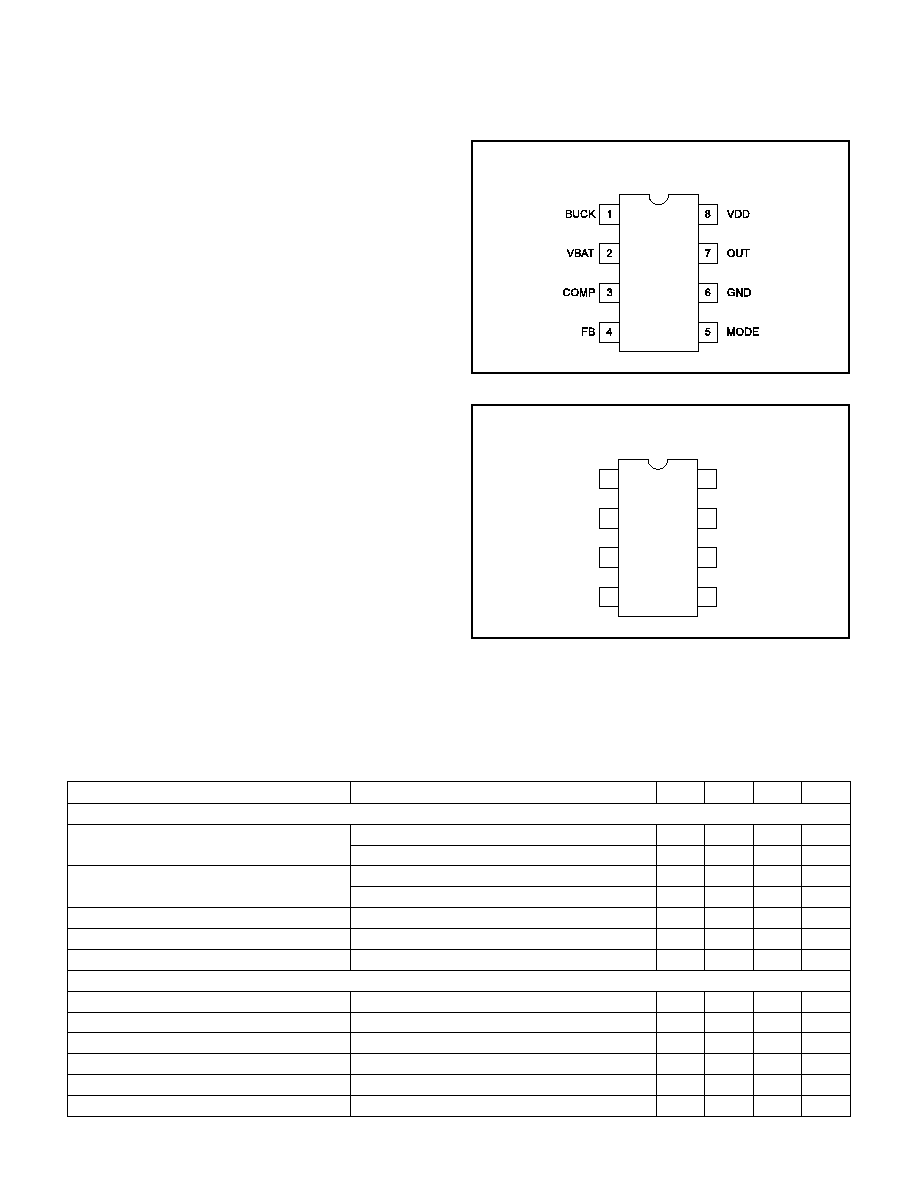

TSSOP-8 (TOP VIEW)

PW Package

ABSOLUTE MAXIMUM RATINGS

VBAT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +27V

VDD Maximum Forced Current . . . . . . . . . . . . . . . . . . . . 30mA

Maximum Forced Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . 17V

BUCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≠5V to VBAT

MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≠0.3V to 4.0V

MODE Maximum Forced Current . . . . . . . . . . . . . . . . . . 300

µA

Operating Junction Temperature . . . . . . . . . . ≠55∞C to +150∞C

Storage Temperature . . . . . . . . . . . . . . . . . . . ≠65∞C to +150∞C

Unless otherwise indicated, currents are positive into, negative

out of the specified terminal. Pulse is defined as less than 10%

duty cycle with a maximum duration of 500

µ

s. Consult Pack-

aging Section of Databook for thermal limitations and consider-

ations of packages. All voltages are referenced to GND.

CONNECTION DIAGRAMS

ELECTRICAL CHARACTERISTICS:

Unless otherwise specified these specifications hold for T

A

=0∞C to +70∞C for the

UC3972/3, ≠40∞C to +85∞C for the UC2972/3, and ≠55∞C to +125∞C for the UC1972/3; T

A

=T

J

; VDD=VBAT=VBUCK=12V;

MODE=OPEN. For any tests with VBAT>17V, place a 1k resistor from VBAT to VDD.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Input supply

VDD Supply Current

VDD = 12V

1

1.5

mA

VBAT = 25V

7

10.5

mA

VBAT Supply Current

VBAT = 12V

30

60

µ

A

VBAT = 25V

70

140

µ

A

VDD Regulator Turn-on Voltage

I

SOURCE

= 2mA to 10mA

17

18

19

V

VDD UVLO Threshold

Low to high

3.6

4

4.4

V

UVLO Threshold Hysteresis

100

200

300

mV

Output Section

Pull Down Resistance

I

SINK

= 10mA to 100mA

25

50

Pull Up Resistance

I

SOURCE

= 10mA to 100mA

25

50

Output Clamp Voltage

VBAT = 25V, Shunt Regulator on

16

18

V

Output Low

MODE = 0.5V, I

SINK

= 1mA

0.05

0.2

V

Rise Time

CL = 1nF, Note 1

200

ns

Fall Time

CL = 1nF, Note 1

200

ns

FB

MODE

GND

COMP

VDD

OUT

BUCK

VBAT

1

2

3

4

8

7

6

5

DIL-8 (TOP VIEW)

J, N Packages

3

UCC1972/3

UCC2972/3

UCC3972/3

ELECTRICAL CHARACTERISTICS:

Unless otherwise specified these specifications hold for T

A

=0∞C to +70∞C for the

UC3972/3, ≠40∞C to +85∞C for the UC2972/3, and ≠55∞C to +125∞C for the UC1972/3; T

A

=T

J

; VDD=VBAT=VBUCK=12V;

MODE=OPEN. For any tests with VBAT>17V, place a 1k resistor from VBAT to VDD.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Oscillator Section

Minimum Frequency

BUCK = VBAT≠ 2, V

BAT

= 12V to 25V,

T

A

= ≠40∞C to +85∞C

52

66

80

kHz

BUCK = VBAT≠2, V

BAT

= 12V to 25V

T

A

= ≠55∞C to +125∞C

44

66

80

kHz

Maximum Synchronizable Frequency

BUCK = VBAT, V

BAT

= 12V to 25V

T

A

= ≠40∞C to +85∞C

160

220

280

kHz

BUCK = VBAT, V

BAT

= 12V to 25V

T

A

= ≠55∞C to +125∞C

145

220

280

kHz

Maximum Duty Cycle

FB = 1V, T

A

< 0∞C

84

%

FB = 1V, T

A

= 0∞C to 70∞C

92

95

%

Minimum Duty Cycle

FB = 2V

0

%

BUCK Input Bias Current

BUCK = VBAT = 12V

40

90

µ

A

BUCK = VBAT = 25V

80

110

A

Zero Detect Threshold

Measured at BUCK w/respect to VBAT,

VBAT=12V to 25V, T

A

< 0∞C

≠2.4

≠1

≠0.3

V

Measured at BUCK w/respect to VBAT,

VBAT=12V to 25V, T

A

= 0∞C to 70∞C

≠2.0

≠1

≠0.3

V

Error Amplifier

Input Voltage

COMP = 2V, T

A

= 0

∞C to +70∞C

1.465

1.5

1.535

V

COMP = 2V

1.455

1.545

V

Line Regulation

≠2

2

10

mV

Input Bias Current

≠500

≠100

nA

Open Loop Gain

COMP = 0.5V to 3.0V

60

80

dB

Output High Voltage

FB = 1V

3.3

3.7

4.1

V

Output Low Voltage

FB = 2V

0.15

0.35

V

Output Source Current

FB = 1V, COMP = 2V

≠1.2

≠0.4

mA

Output Sink Current

FB = 2V, COMP = 2V

2

4

mA

Output Source Current

FB = 1V, COMP = 2V, MODE = 0.5V

≠1

1

µ

A

Output Sink Current

FB = 2V, COMP = 2V, MODE = 0.5V

≠1

1

µ

A

Unity Gain Bandwidth

T

J

= 25C, Note 1

2

MHz

Mode Select

Output Enable Threshold

0.85

1

1.15

V

Open Lamp Detect Enable Threshold

2.75

3

3.25

V

Mode Output Current

MODE = 0.5V

15

20

25

µ

A

MODE Clamp Voltage

MODE = OPEN

3.3

3.7

4

V

Open Lamp

Open Lamp Detect Threshold

Measured at BUCK with respect to VBAT,

VBAT=12V to 25V

≠8

≠7

≠6

V

Over-voltage Clamp Threshold (UCC3973) Measured at BUCK with respect to VBAT,

VBAT=12V to 25V, I

FB

= 100

µA

≠10.3

≠9

≠7.7

V

Note 1. Guaranteed by design. Not 100% tested in production.

4

UCC1972/3

UCC2972/3

UCC3972/3

BUCK: Senses the voltage on the top side of the induc-

tor feeding the resonant tank. The voltage at this point

is used to synchronize the internally generated ramp

and to detect whether an open lamp condition exists.

An open lamp condition exists when this voltage is be-

low the specified threshold for seven clock cycles. If the

MODE pin is held below the open lamp detect enable

threshold, this protective feature is disabled.

On the UCC3973, this pin is also used to sense an

over-voltage across the transformer primary. If the volt-

age at this pin exceeds the clamp threshold, current will

be sourced fron the FB pin.

COMP: Output of the error amplifier.Compensation

components set the bandwidth of the entire system and

are normally connected between COMP and FB. The

error amplifier averages lamp current against a fixed in-

ternal reference. The resulting voltage on the COMP

pin is compared to an internally generated ramp, set-

ting the PWM duty cycle. During UVLO, this pin is ac-

tively pulled low.

FB: This pin is the inverting input to the error amplifier.

On the UCC3973, current is sourced form this pin if the

clamp threshold is exceeded at the BUCK pin (see be-

low). The sourced current will reduce OUT duty cycle to

control transformer primary voltage. The source current

is disabled on the UCC3972.

GND: Ground reference for the IC.

MODE: The voltage on this pin is used to control start-up

and various modes of operation for the part (refer to the ta-

ble in the block diagram).

When the voltage is below 1V, OUT is forced low, open

lamp detection is disabled and the error amplifier is

tri-stated.

When the voltage is between 1V and 3V, OUT is enabled

and the error amplifier output is connected to COMP.

Open lamp detection is still disabled and a constant 20

µA

current is sourced from this pin. Placing an appropriate

value external capacitor between this pin and ground al-

lows the user to disable open lamp detection for a set pe-

riod of time at start-up to allow the lamp to strike.

When MODE reaches 3V, open lamp detection is enabled

and normal operation is activated.

OUT: Drives the buck regulator N-channel MOSFET. OUT

turn-on is synchronized to twice the tank resonant fre-

quency. OUT is actively pulled low when in UVLO, an

open lamp condition has been detected or MODE is less

than 1V.

VBAT: Positive input supply to power stage. This voltage

is

required

by

internal

control

circuitry

to

provide

open-lamp detection and synchronization. Operating range

is from 4.5V to 25V.

VDD: This pin connects to the battery voltage from which

the CCFL inverter will operate. If the potential on VBAT

can exceed 18V in the application, a series resistor must

be placed between VBAT and this pin (see applications

section). The voltage at the VDD pin will then be regulated

to 18V. This pin should be bypassed with a minimum ca-

pacitance of 0.1

µF.

PIN DESCRIPTIONS

0

200

400

600

800

8.7

9.2

9.7

V

BAT

- V

BUCK

CURRENT

OUT

O

F

F

B

(

uA)

Clamp current vs. tank voltage for UCC3973.

5

UCC1972/3

UCC2972/3

UCC3972/3

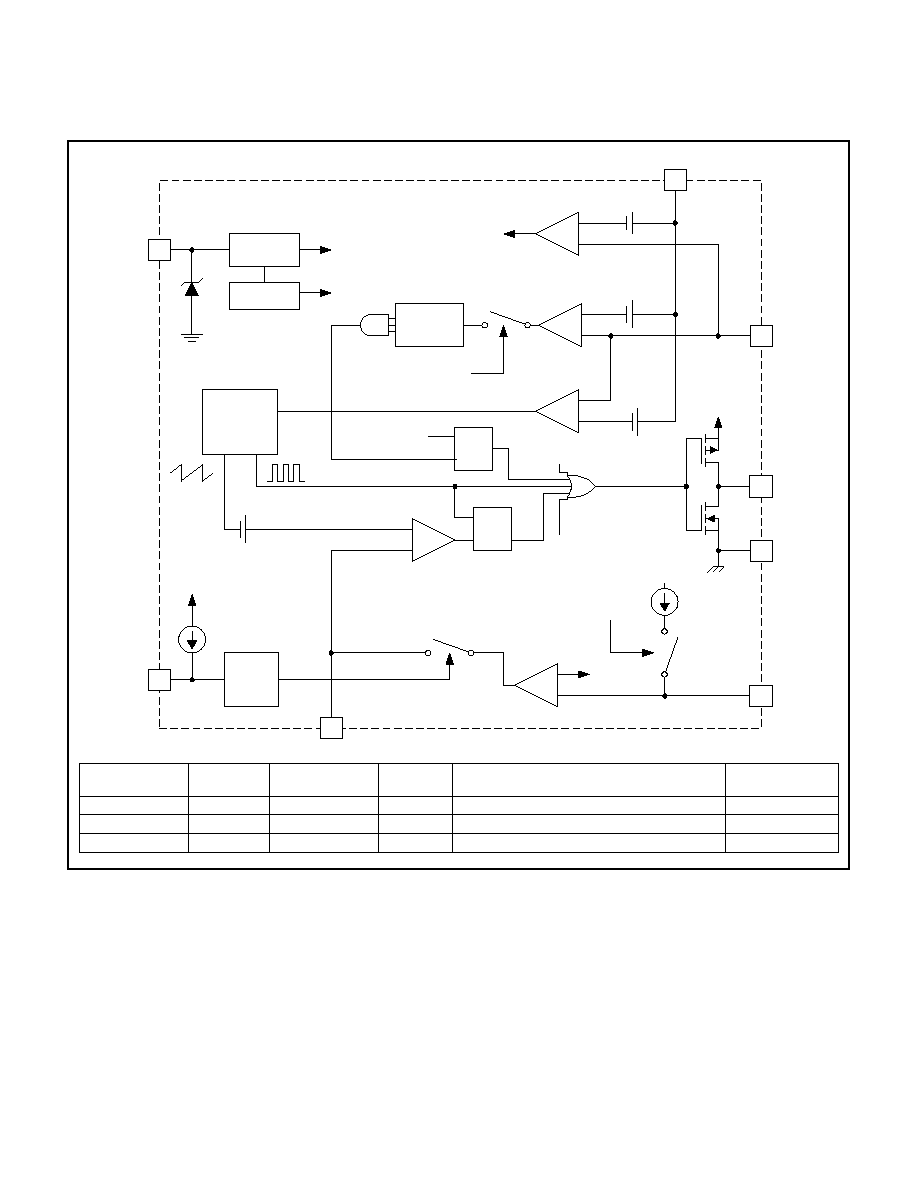

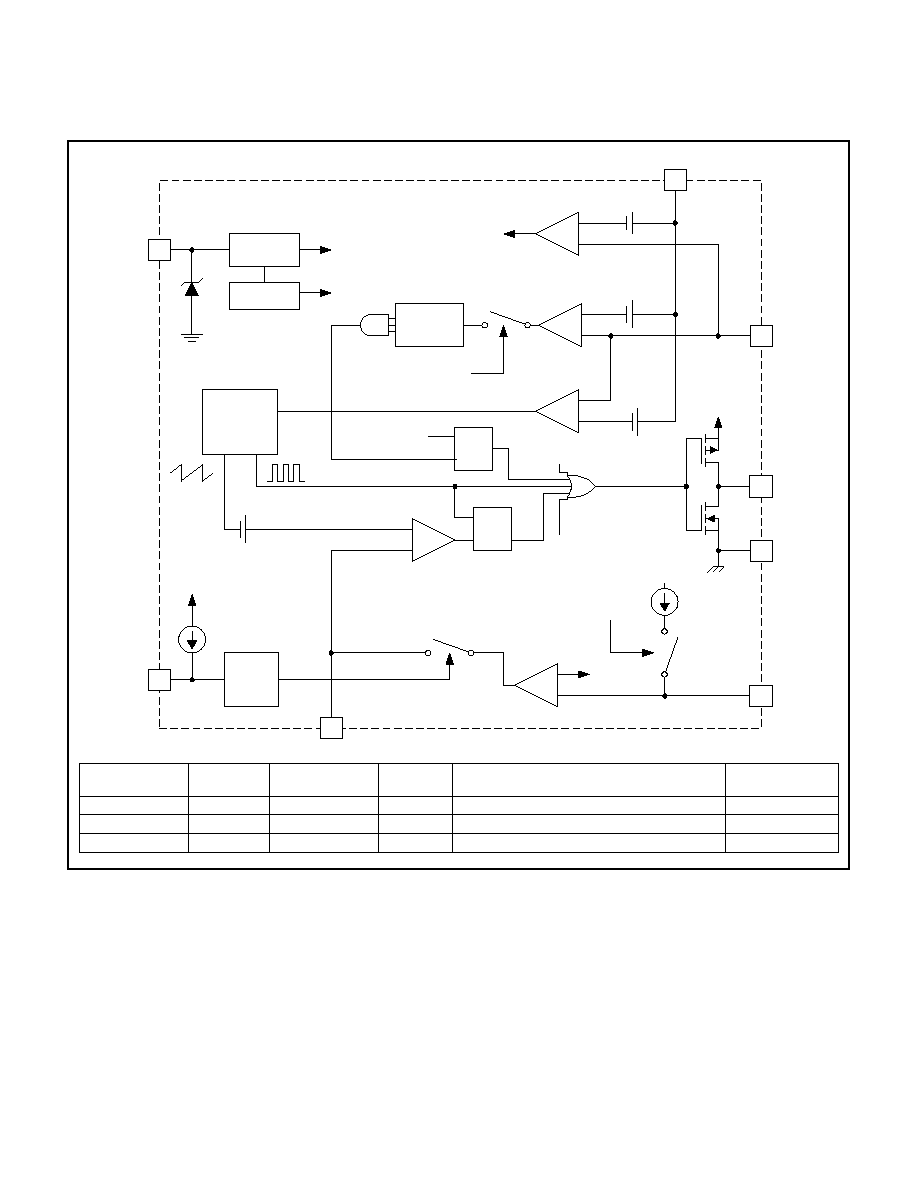

UDG-98154

*MODE

Output

Open Lamp

Detection

S2

Error Amplifier Output

S1

<1V

OFF

DISABLED

OPEN

DISCONNECTED FROM COMP

OPEN

1V< MODE< 3V

ON

DISABLED

OPEN

CONNECTED TO COMP

CLOSED

>3V

ON

ENABLED

CLOSED

CONNECTED TO COMP

CLOSED

8

5

3

4

2

1

7

6

VDD

20

µA

+

≠

+

≠

1.5V

ERROR

AMPLIFIER

S1

R

Q

S

R

Q

S

+

≠

+

≠

+

+

1.0V

7.0V

SYNC

OUT

RAMP

+

0.2V

66kHz-200kHz

OSCILLATOR

*MODE

SELECT

UVLO

4.0V/3.8V

3V REF

VREF

UVLO=1

3 BIT

UP-DOWN

COUNTER

S2

FROM MODE SELECT

OPEN LAMP DETECT

COMPARATOR

ZERO DETECT

COMPARATOR

UVLO

PWM

UVLO

OUTPUT OFF

(FROM MODE SELECT)

VDD

MODE

COMP

FB

GND

OUT

BUCK

VDD

VBAT

18V

+

≠

+

TO S3

OVER-VOLTAGE

CLAMP COMPARATOR

S3

(ALWAYS OPEN ON UCC3972)

FROM

CLAMP

COMP

I

CLAMP

9.0V

BLOCK DIAGRAM

Introduction

Cold Cathode Fluorescent Lamps (CCFL) are frequently

used as the backlight source for Liquid Crystal Displays

(LCDs). These displays are found in numerous applica-

tions such as notebook computers, portable instrumenta-

tion,

automotive

displays,

and

retail

terminals.

Fluorescent lamps provide superior light output effi-

ciency, making their use ideal for power sensitive porta-

ble applications where the backlight circuit can consume

a significant portion of the battery's capacity. The

backlight converter must produce the high voltage

needed to strike and operate the lamp. Although CCFLs

can be operated with a DC voltage, a symmetrical AC

operating voltage is recommended to maintain the rated

life of the lamp. Sinusiodal voltage and current lamp

waveforms are also recommended to achieve optimal

electrical to light conversion and to reduce high voltage

electromagnetic interference (EMI). A topology that pro-

vides these requirements while maintaining efficient op-

eration is presented below.

APPLICATION INFORMATION