Page 1 of 1 TOPRO CONFIDNETIAL 2003/7/28

Print

TP5208

64K SRAM

Echo Processor

D

D

D

a

a

a

t

t

t

a

a

a

S

S

S

h

h

h

e

e

e

e

e

e

t

t

t

Version: 1.0

Jun/2002

http://www.topro.com.tw

HQ:

5F, No.10, Prosperity Road 1, Science-Based Industrial Park, Hsinchu 300, Taiwan, R.O.C

300 10 5

TPE:

5 F, No.27, Min Chuan W. Rd. Taipei 104, Taiwan, R.O.C

104 27 5

SHENZHEN

:

Room 802, Tower A, World Trade Plaza, Fahong Rd., Fatian, Shenzhen, China

9 A 802 (518033)

H.Q.: Tel:886-3-5632515 Fax:886-3-5641728

TPE.: Tel:886-2-25856858 Fax:886-2-25941104

SHENZHEN:TEL:755-3679985 Fax:755-3679518

Page 2 of 2 TOPRO CONFIDNETIAL 2003/7/28

Print

TP5208

64K SRAM

Echo Processor

Description

The TP5208 is a developed for producing echo effects added to voice signals picked up by

microphone for karaoke applications. The IC has the largest memory among the digital delay

series. As its design is aimed at high performance, it is best suited to provide radio cassette tape

recorders and miniature unit audio system with quality echo function.

Being pin compatible with the Mitsubishi M65831AP/FP, M65830CP/FP, and M65843AP/FP,

the TP5208 is suitable for upgrading the series.

Features

Built-in input/output filters, A-D and D-A converters and memory realize a delay system

with only a single chip

Capable of composing low-noise and low�distortion delay system at low cost by ADM

system (No= -88dB typ, THD=0.17% typ)

Control mode selections available from 2 kinds: easy mode using parallel data and

microcomputer mode using serial data

Sleep mode can be selected to stop IC functions

Built-in automatic reset circuit

Page 3 of 3 TOPRO CONFIDNETIAL 2003/7/28

Print

TP5208

64K SRAM

Echo Processor

Pin Configuration

V

DD

1

24

V

CC

XIN 2

23

LPF1

IN

XOUT 3

22

LPF1

OUT

D1/REQ 4

21

OP1

OUT

D2/SCK 5

20

OP1

IN

D3/DATA 6

19

REF

D4/IDSW 7

18

CC1

TEST 8

17

CC2

EASY/U-COM 9

16

OP2

IN

SLEEP 10

15

OP2

OUT

D-GND 11

14

LPF2

IN

A-GND 12

13

LPF2

OUT

24 PINS DIP/SOP

Page 4 of 4 TOPRO CONFIDNETIAL 2003/7/28

Print

TP5208

64K SRAM

Echo Processor

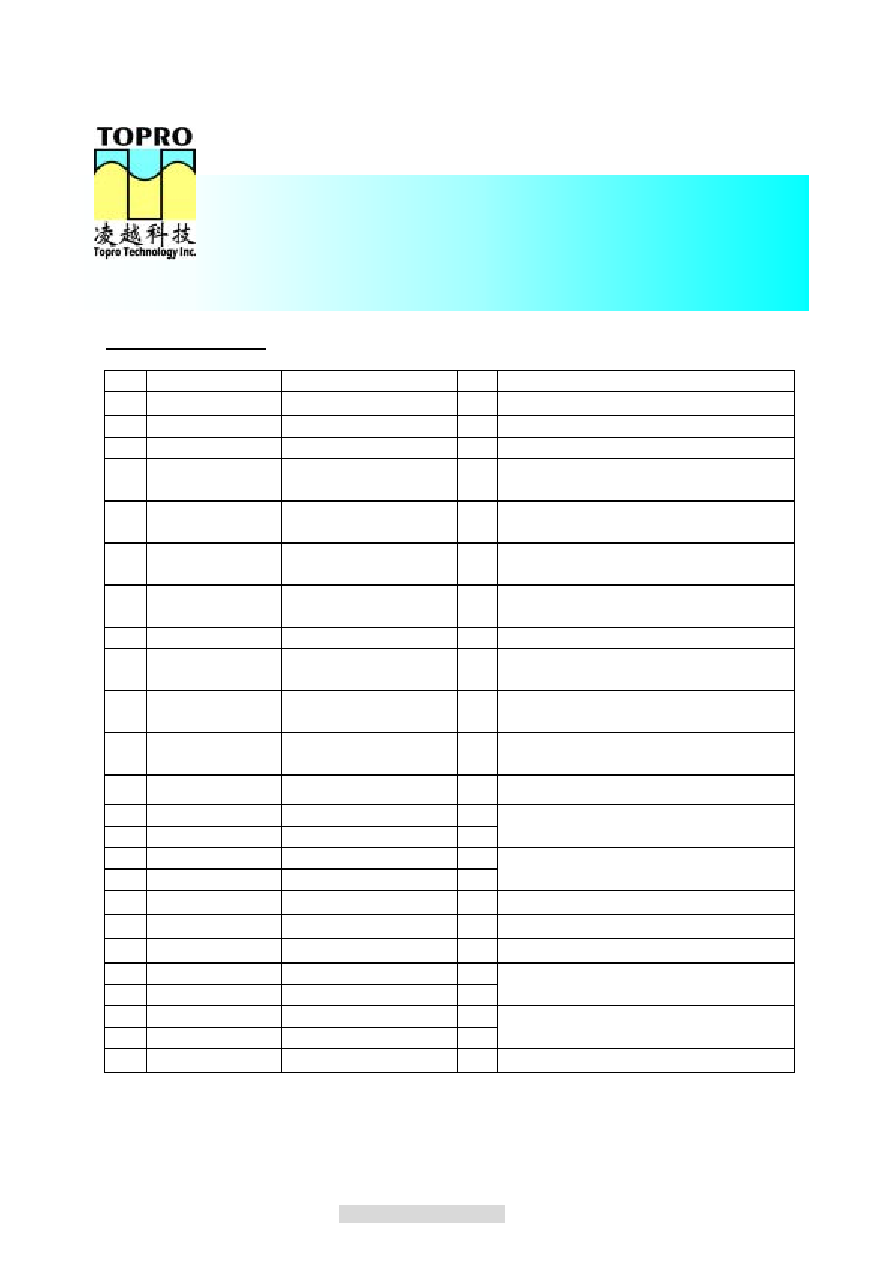

Pin Description

No. Symbol

Name I

/O

Function

1.

VDD

Digital

VDD

Supply voltage

2.

XIN

Oscillator

input

I

3. XOUT

Oscillator input

O Connects to 2MHz ceramic filter

4.

D1/REQ

Delay1/Request

I

Easy mode: inputs D1 data

U-COM mode: inputs request data

5.

D2/SCK

Delay2/Shift

clock

I

Easy mode: inputs D2 data

U-COM mode: inputs shift clock

6.

D3/DATA

Delay3/Serial

data

I

Easy mode : inputs D3 data

U-COM mode: inputs shift data

7.

D4/IDSW

Delay4/ID

switch

I

Easy mode : inputs D4 data

U-COM mode: controls ID code

8. TEST

Test

I L= normal mode

9.

EASY/U-COM EASY/U-COM

I

H= Easy mode

L= U-COM mode

10. SLEEP

Sleep

I

H= sleep mode

L= normal mode

11. DGND

Digital GND

Connects to analog GND at one point

12. AGND Analog

GND Connects to analog GND

13. LPF2 OUT

Low pass filter2 output O

14. LPF2 IN

Low pass filter2 input

I

Forms low pass filter with external C, R

15. OP2 OUT

OP-AMP2 output

O

16. OP2 IN

OP-AMP2 input

I

Forms integrator with external C.R

17. CC2

Current control 2

18. CC1

Current control 1

19. REF

Reference

= 1/2 VCC

20. OP1 IN

OP-AMP1 input

I

21. OP1 OUT

OP-AMP1 output

O

Forms integrator with external C, R

22. LPF1 OUT

Low pass filter1 output O

23. LPF1 IN

Low pass filter1 input

I

Forms low pass filter with external C, R

24. VCC Analog

Vcc Supply voltage

Page 5 of 5 TOPRO CONFIDNETIAL 2003/7/28

Print

TP5208

64K SRAM

Echo Processor

Operation

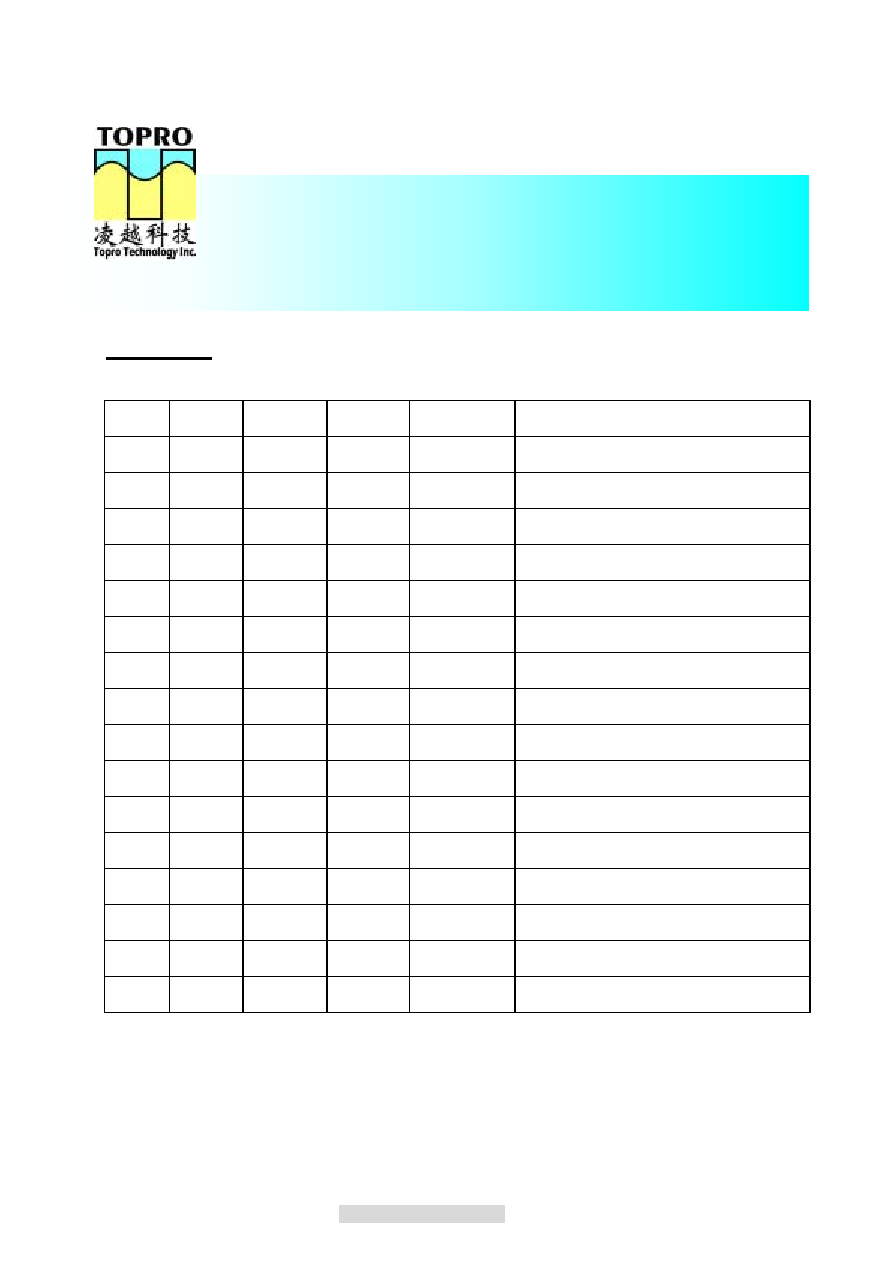

1) EASY Mode (EASY / U-COM =H)

D4 D3 D2 D1

fs

Td

L L L L 666

12.3

L L L H 666

24.6

L L H L 666

36.9

L L H H 666

49.2

L H L L 666

61.4

L H L H 666

73.7

L H H L 666

86.0

L H H H 666

98.3

H L L L 333

110.6

H L L H 333

122.9

H L H L 333

135.2

H L H H 333

147.5

H H L L 333

159.7

H H L H 333

172.0

H H H L 333

184.3

H H H H 333

196.6

f sSampling Frequenct (KHz)

TdDelay Time (msec)