| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TA1316AN | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TA1316AN

2002-10-04

1

Toshiba Bipolar Linear Integrated Circuit Silicon Monolithic

TA1316AN

YCbCr/YPbPr Signal and Sync Processor for Digital TV, Progressive Scan TV and Double

Scan TV

TA1316AN is a component signal and sync processor for Digital

TV, Progressive scan TV and Double scan TV.

TA1316AN provides high performance signal processors in the

luminance and color difference blocks. The sync circuit can

process 525I/P, 625I/P, 750P, 1125I/P, PAL100 Hz and

NTSC120 Hz formats.

TA1316AN provides I

2

C bus interface, so various functions and

controls are adjustable via the bus.

Features

Luminance Block

∑ Black stretch, DC restoration

∑ Dynamic correction

∑ SRT (LTI)

∑ Y group delay correction (shoot balance correction)

∑ APACON white peak limit

∑ White pulse limit (white letter improvement)

∑ Hi-bright color

∑ Color detail enhancer (CDE)

∑ VSM output

Color Difference Block

∑ Flesh color correction

∑ Dynamic Y/C correction

∑ Color SRT (CTI)

∑ Color

∑ White peak blue correction

Text Block

∑ OSD blending SW

∑ ACB (only black level)

∑ 2 analog RGB inputs

Synchronization Block

∑ Horizontal synchronization

(15.75 kHz, 31.5 kHz, 33.75 kHz, 45 kHz)

∑ Vertical synchronization

(525I/P, 625I/P, 750P, 1125I/P, PAL 100 Hz, NTSC 120 Hz)

∑ 2-and 3-level sync. separation circuit

∑ Accept both positive and negative HD/VD input

∑ Mask for copy-guard signal

∑ Vertical blanking

Weight: 5.55 g (typ.)

TA1316AN

2002-10-04

2

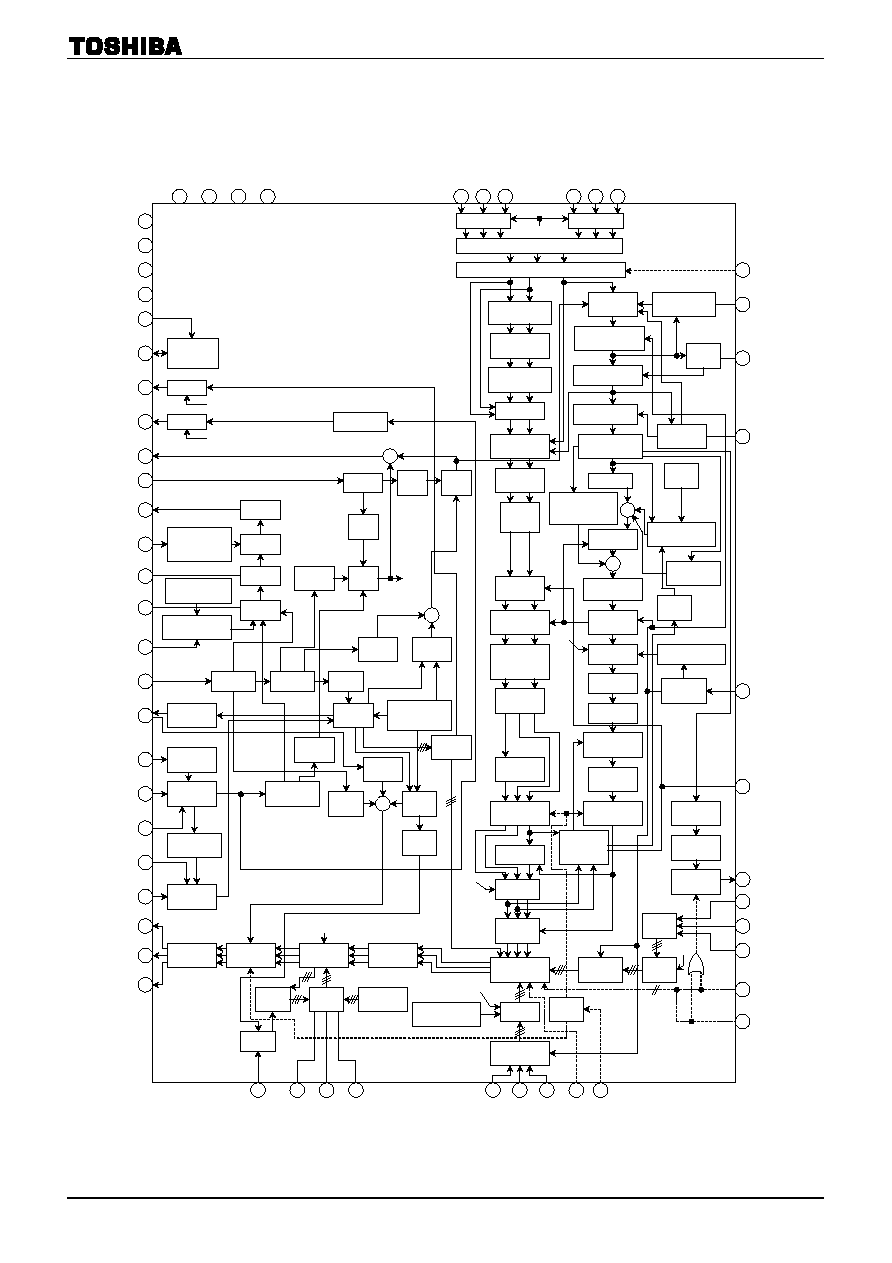

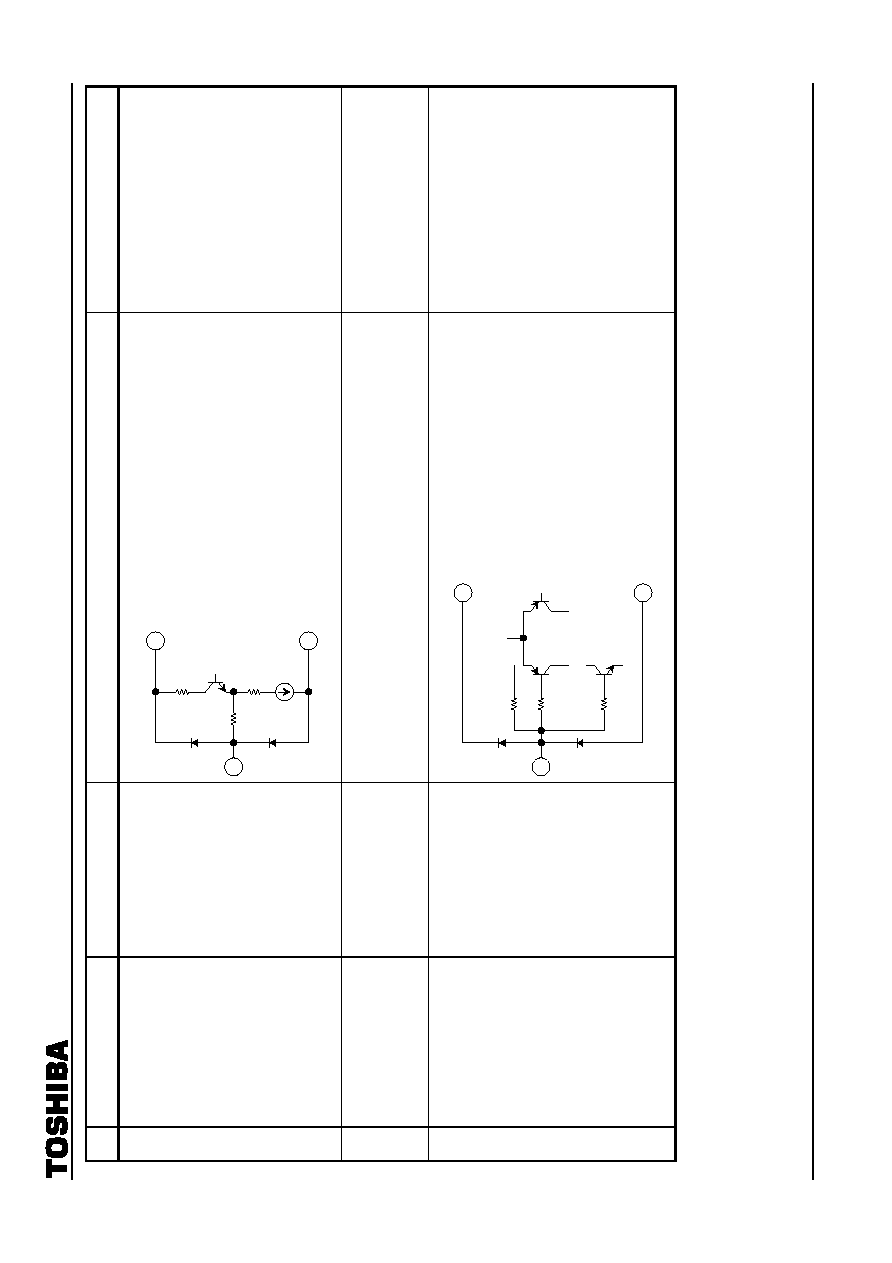

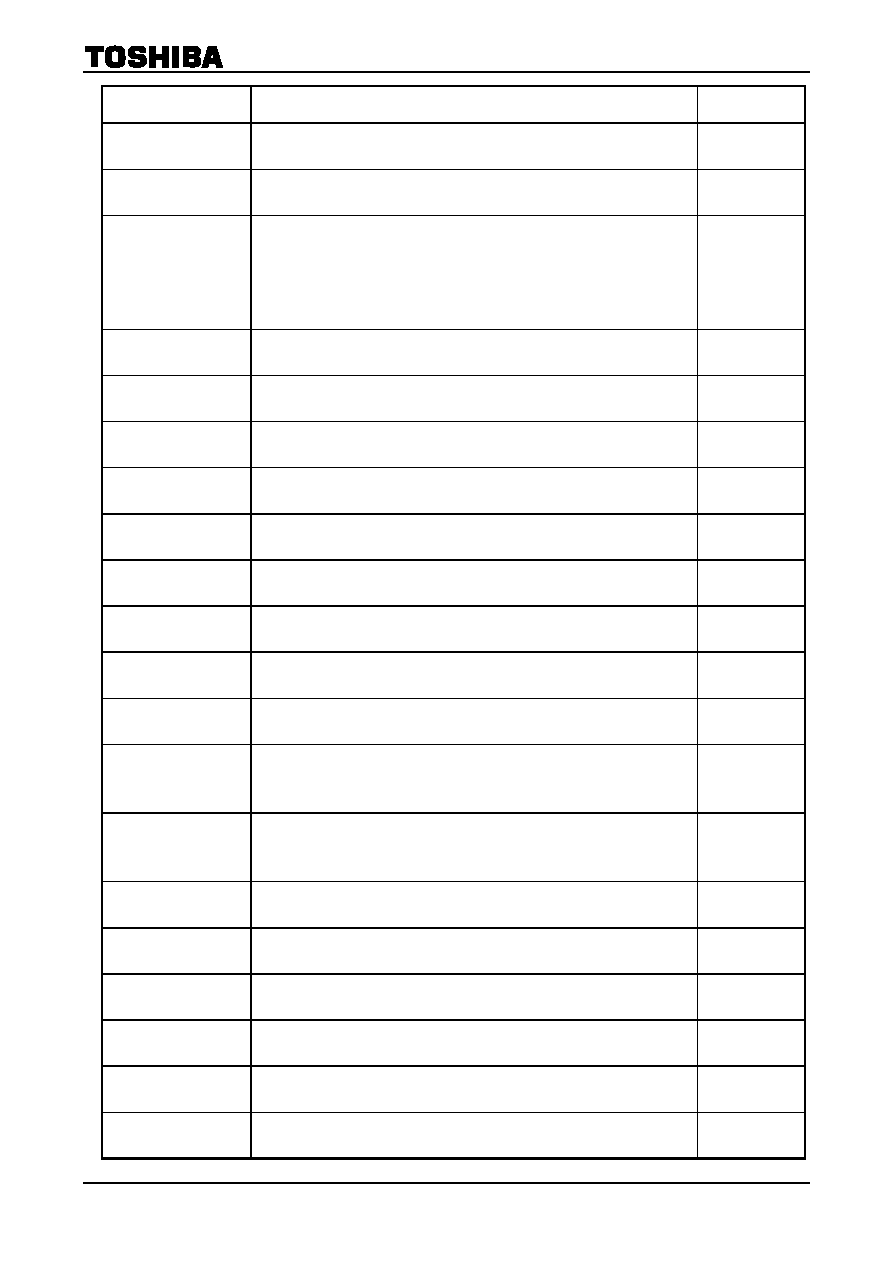

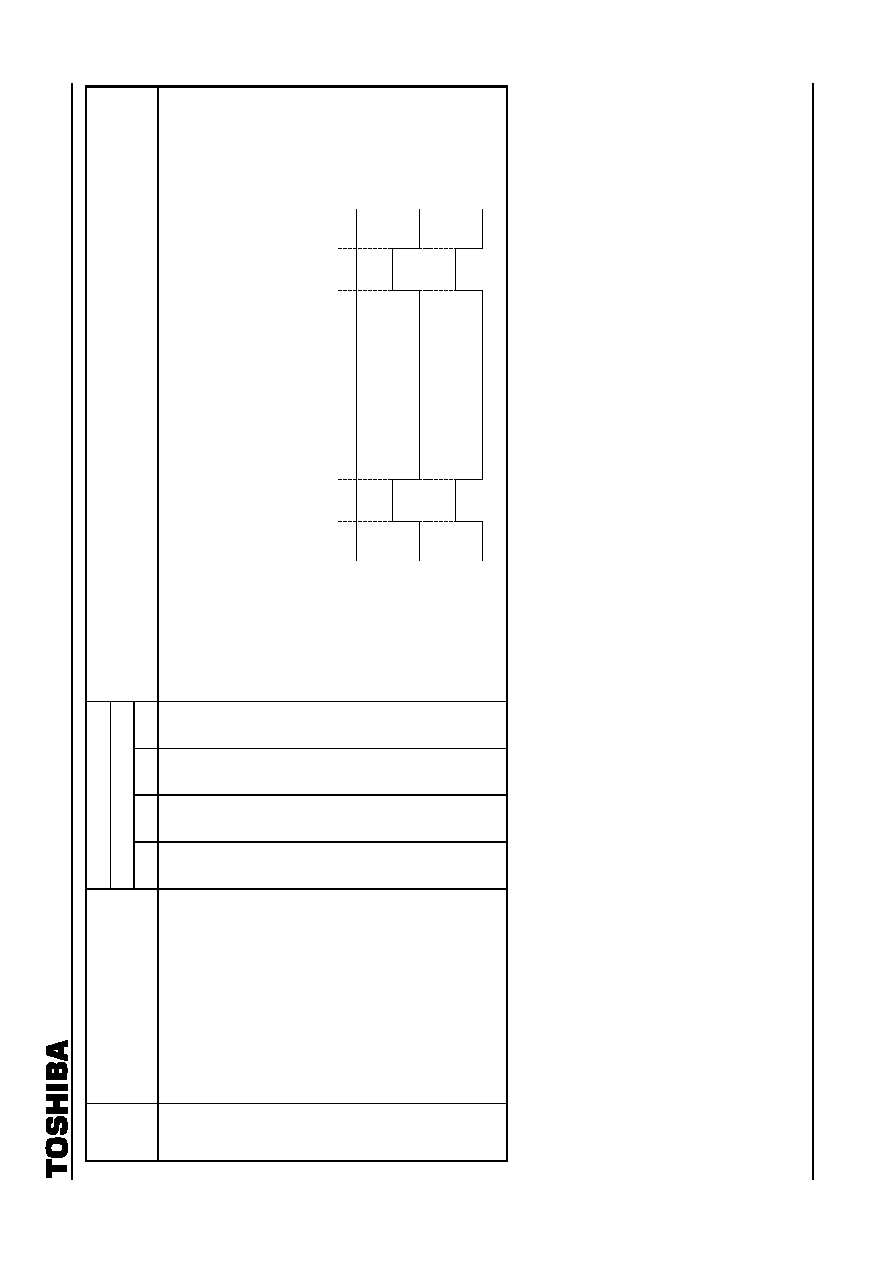

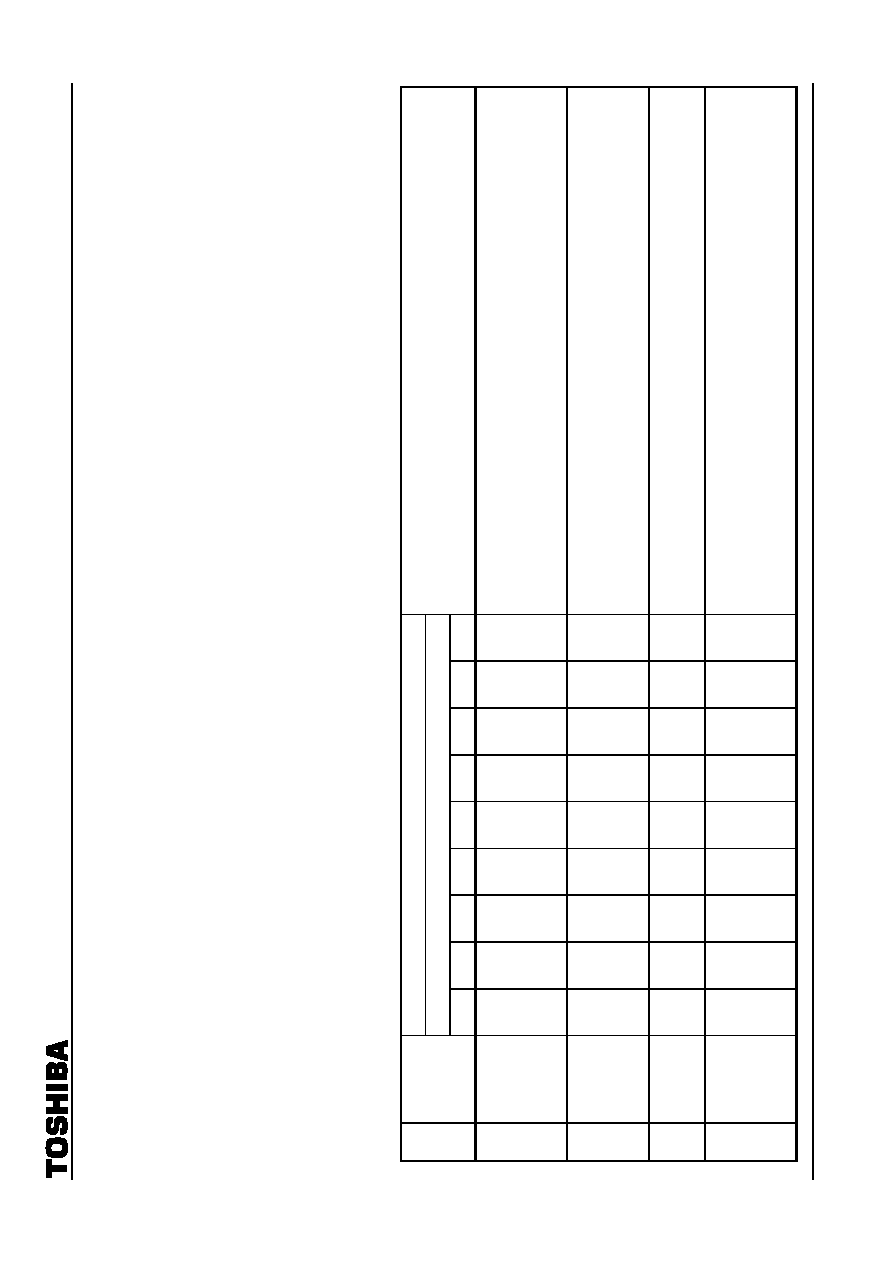

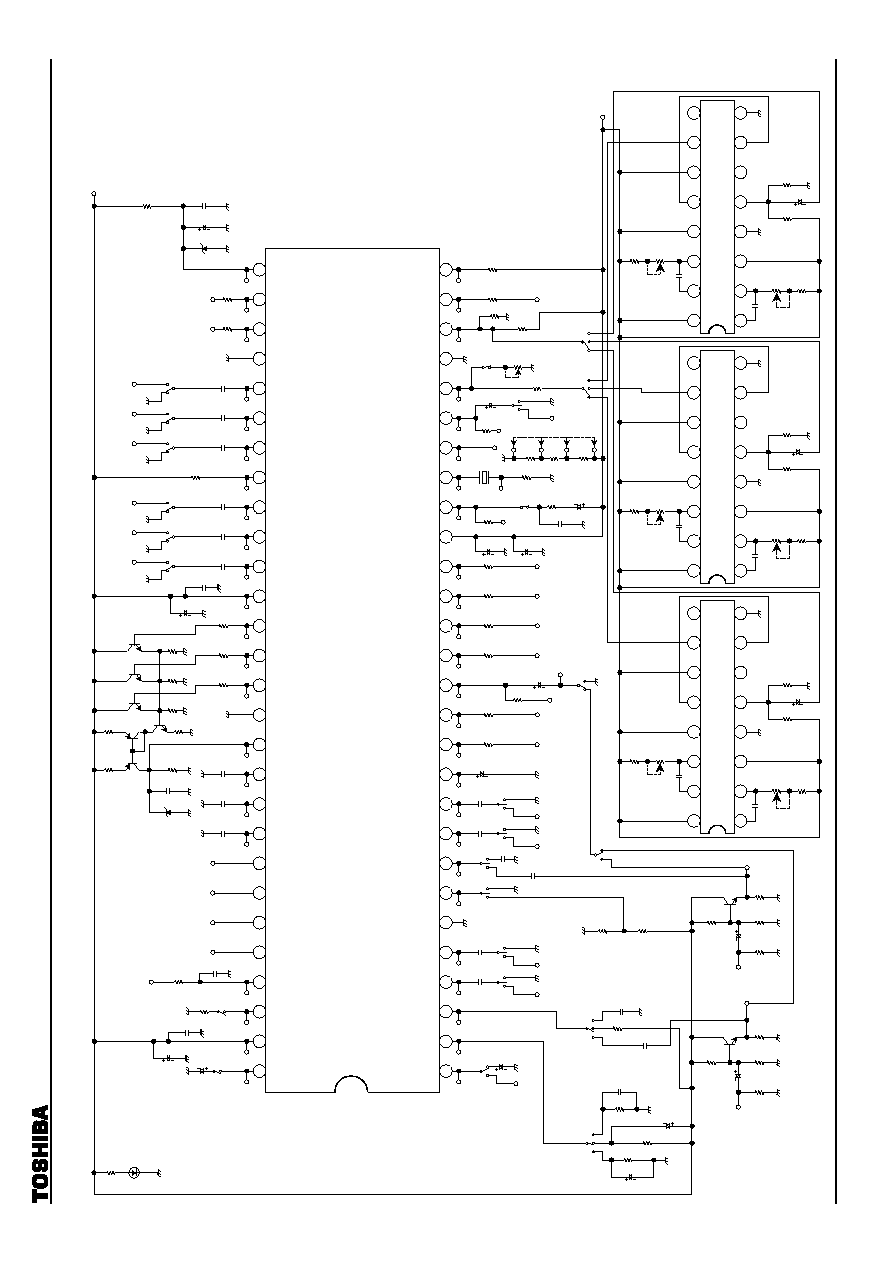

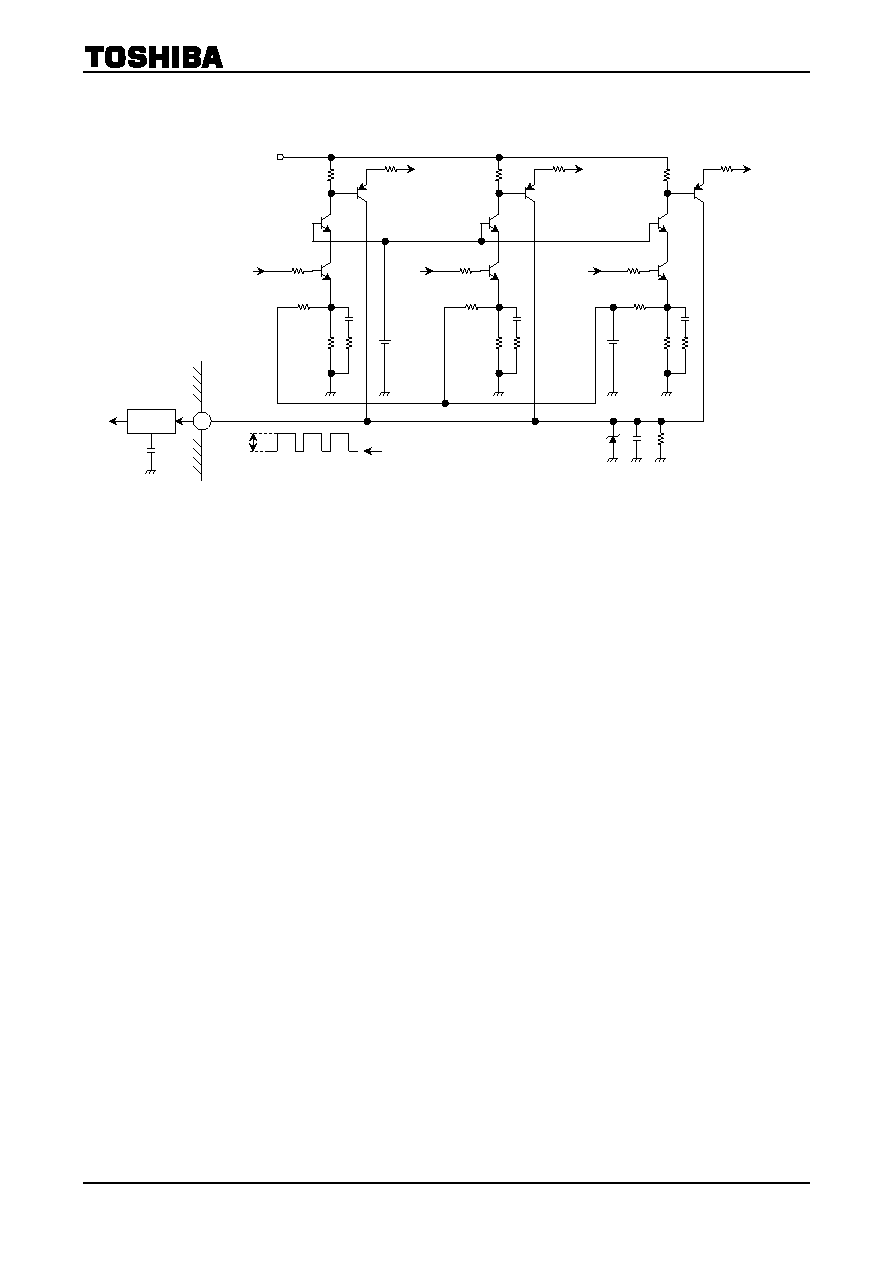

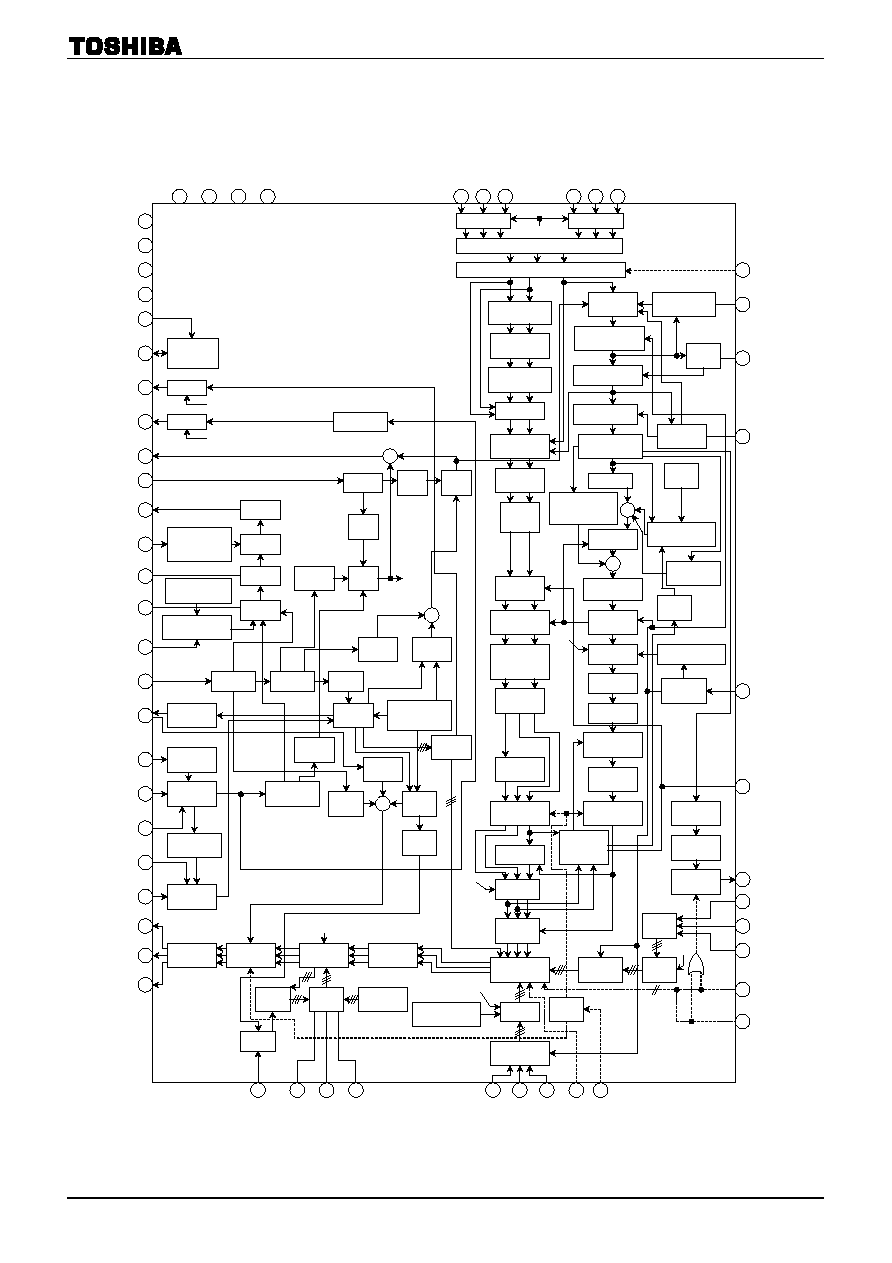

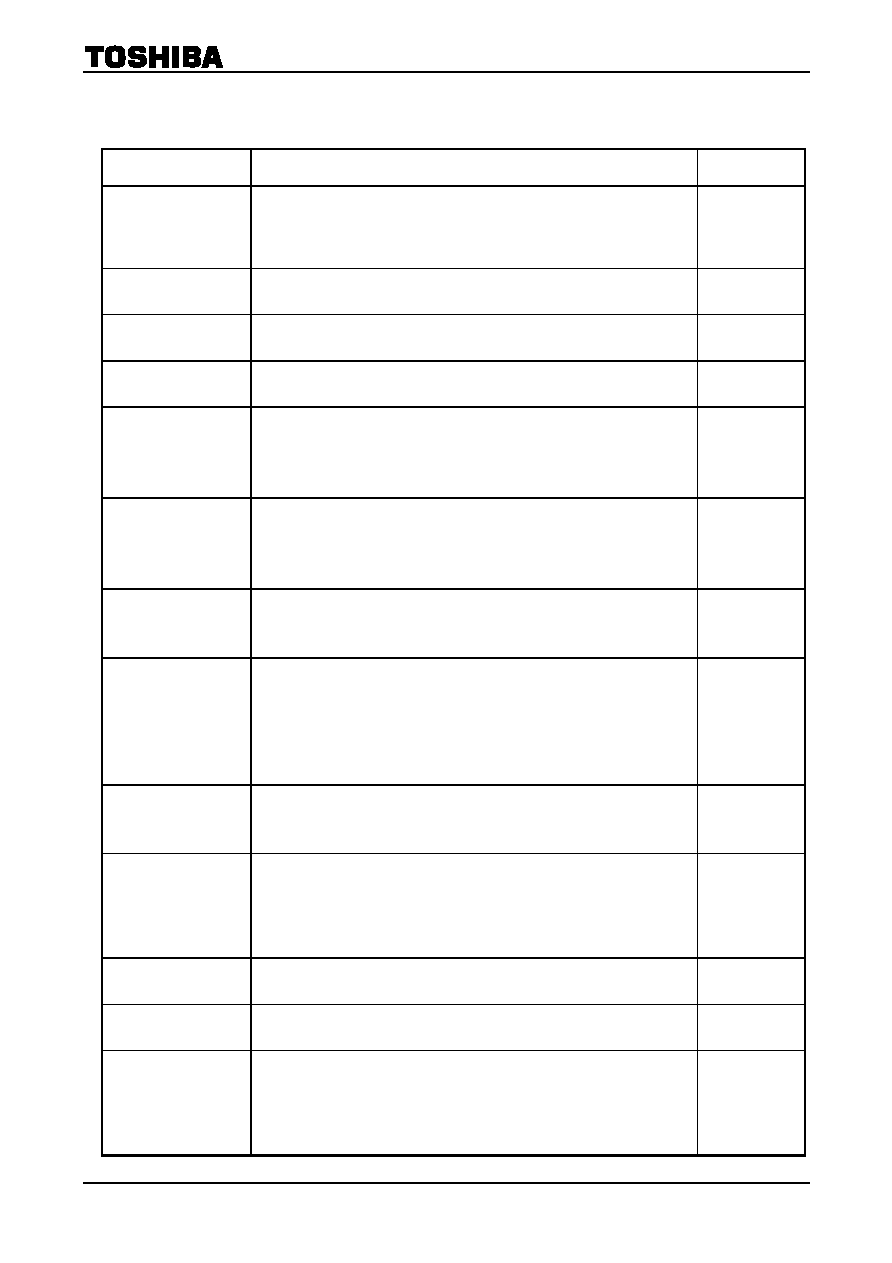

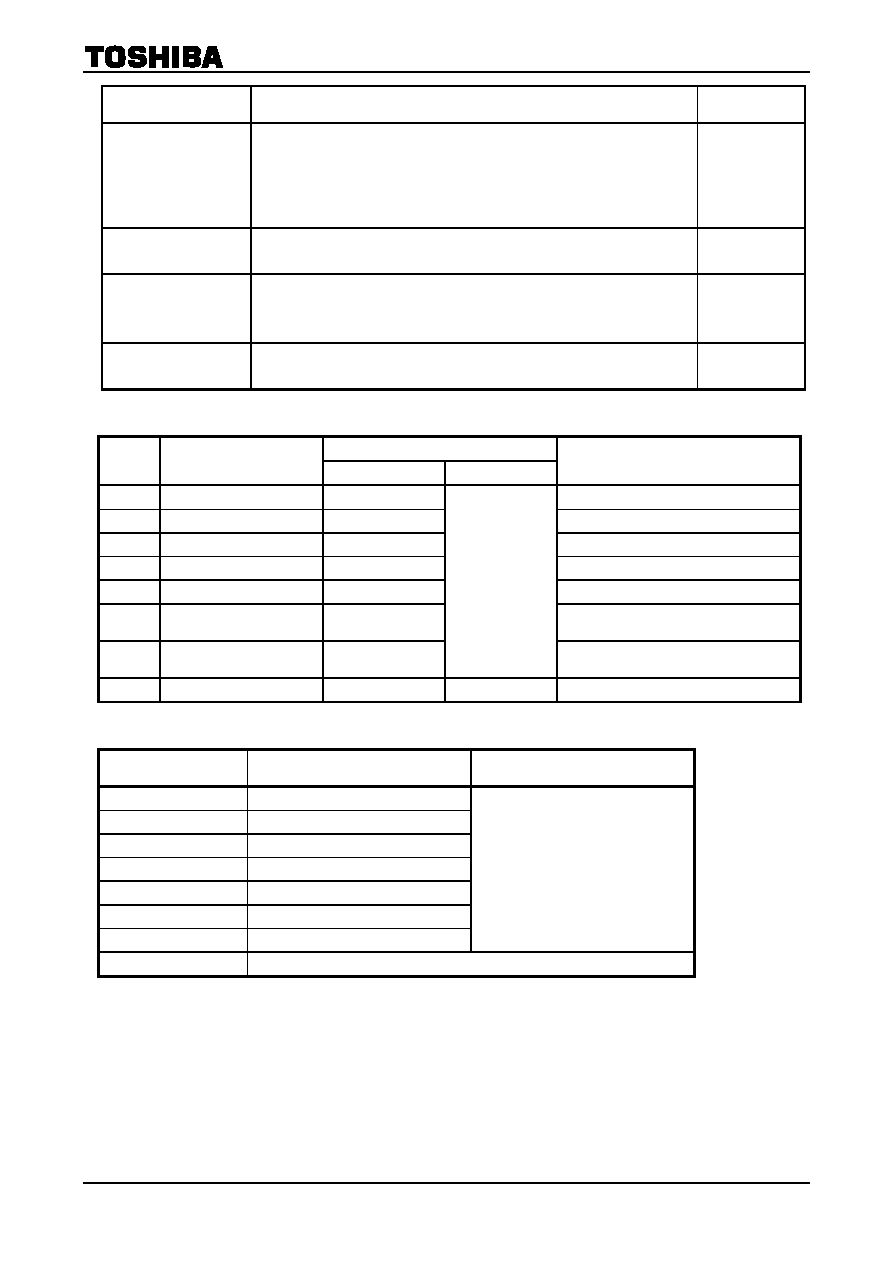

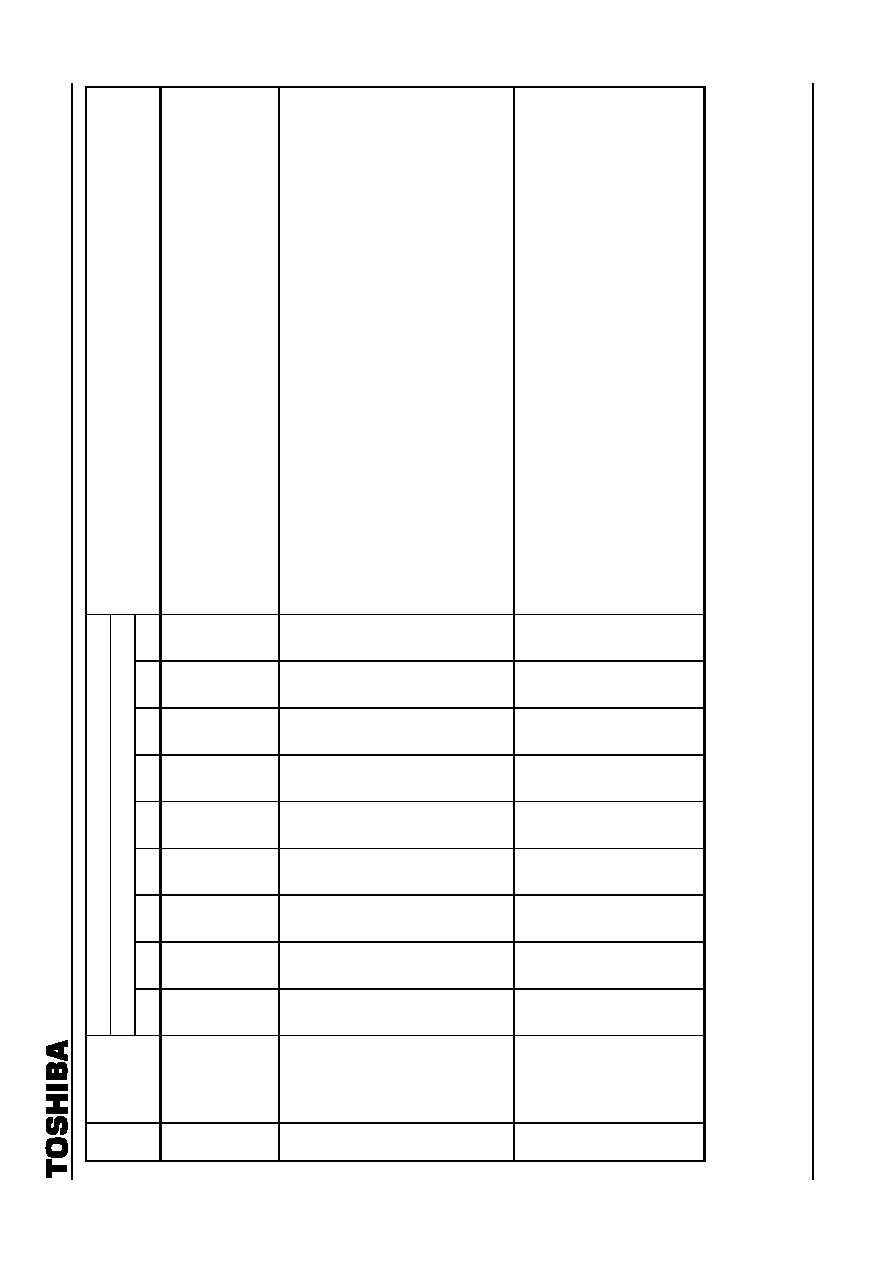

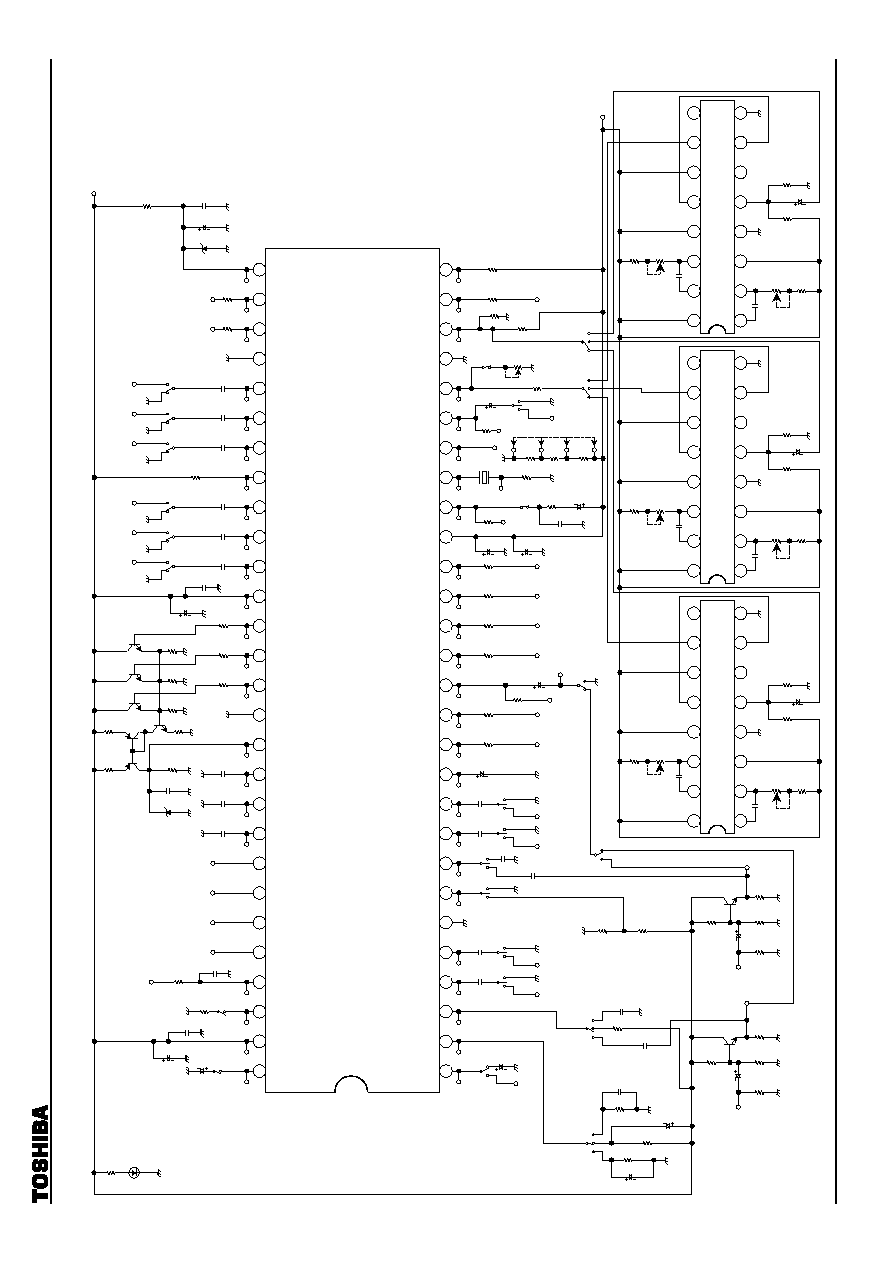

Block Diagram

DAC2

(ACB PLUSE)

HORIZONTAL

FREQUENCY

SW

AFC FILTER

H CURVE

CORRECTION

DE

F

/

D

A

C V

CC

SW

HORIZONTAL

PHASE

I

2

CBUS

DECODER

H

FREQUENCY

SW

CLAMP

H DUTY

I

2

L V

DD

I

2

L GND

Y1

IN

C

b1

/P

b1

IN

C

r1

/P

r1

IN

DE

F

/

D

A

C GND

VP OUT

Y

HD

PbPr/YCbCr YUV CONVERT

SW

H CURVE

CORRECTION

SYNC

SEPA

HD IN SW

V

INTEGRAL

VD IN SW

RGB OUT

H C/D

HVCO

H-AFC

H-RAMP

2

◊

f

H

V C/D

V

FREQUENCY

SW

ACB

PULSE

HD

POLARITY

CLAMP

PULSE

EXT

V-BLK

H-BLK

V-BLK

V-CLP

DRIVE

CLAMP

BLK

SW

I

K

CUT OFF

RGB

BRIGHTNESS

CLAMP

RGB

CONTRAST

MIXER SW/

BLUE BACK

RGB

MATRIX

CLAMP

WP BLUE

HALF TONE

/C MUTE

COLOR

G-Y

MATRIX

RELATIVE

PHASE/

AMPLITUDE

H-BPP

V-BPP

UNI-COLOR

COLOR

CLAMP

PULSE

CP

SW

EXT

CP

CP/BPP

SYNC OUT

BPP

SW

EXT

BPP

DL/

COLOR

SRT

TINT

Y/C LEVEL

COMP

SW

IQ UV

CONVERTER

UV IQ

CONVERTER

FRESH

COLOR

CLAMP

Y2

IN

C

b2

/P

b2

IN

C

r2

/P

r2

IN

BLACK

STRETCH

BLACK PEAK

DETECT

DARK

DET

BLACK LEVEL

CORECTION

DYNAMIC

DC REST

SHARPNESS

DELAY LINE

APL

DETECT

GROUP

DELAY

CORRECTION

YNR

SRT

WPL

CLAMP

UNI-

COLOR

APACON

WPL

SUB-

CONTRAST

WPS

HALF TONE

HI-BRIGHT

COLOR

Yout-

COLOR

PEAK

DETECT

SHARPNESS

CONTROL

Y DETAIL

CONTROL

CDE

BRIGHTNESS

ABCL

AMP

VSM

MUTE

VSM AMP

HPF

OSD

AMP

CLAMP

OSD

ACL SW

Y

M

SW

MATRIX SW

DARK AREA

DET FILTER

BPH FILTER

APL FILTER

ABCL IN

COLOR

LIMITER

ANALOG

OSD G IN

ANALOG

OSD R IN

VSM OUT

ANALOG

OSD B IN

Y

S

1

(ANALOG OSD)

Y

S

2

(ANALOG OSD)

I

K

IN

AN

AL

O

G

R I

N

R S/

H

G S

/

H

B S/H

AN

AL

O

G

GI

N

AN

AL

O

G

B IN

Y

S

3

(A

NA

LOG

RGB

)

Y

M

/P-

MU

T

E

/

B

L

K

Y/C V

CC

RGB GND

Y/C GND

RGB V

CC

SCL

SDA

SCP OUT

SCP IN

HVCO

H-OUT

FBP IN

VP OUT

SYNC IN

VD1 IN

HD1 IN

HD2 IN

VD2 IN

R OUT

G OUT

B OUT

CP

CP

CP

CP

DAC2

DAC1

CP

CP

OR

S/H

CP

SW

19

25

29

32

3

4

5

8

9

10

6

55

44

40

31

30

28

36

18

26

17

22

21

20

23

24

27

14

16

13

15

12

43

42

41

38

37

51

50

54

39

11

53

56

1

2

7

45

48

47

46

35

34

33

49 52

+

+

+

+

+

Y

B-Y

G-Y

R-Y

Y

V

U

FBP/BLK

TA1316AN

2002-10-04

3

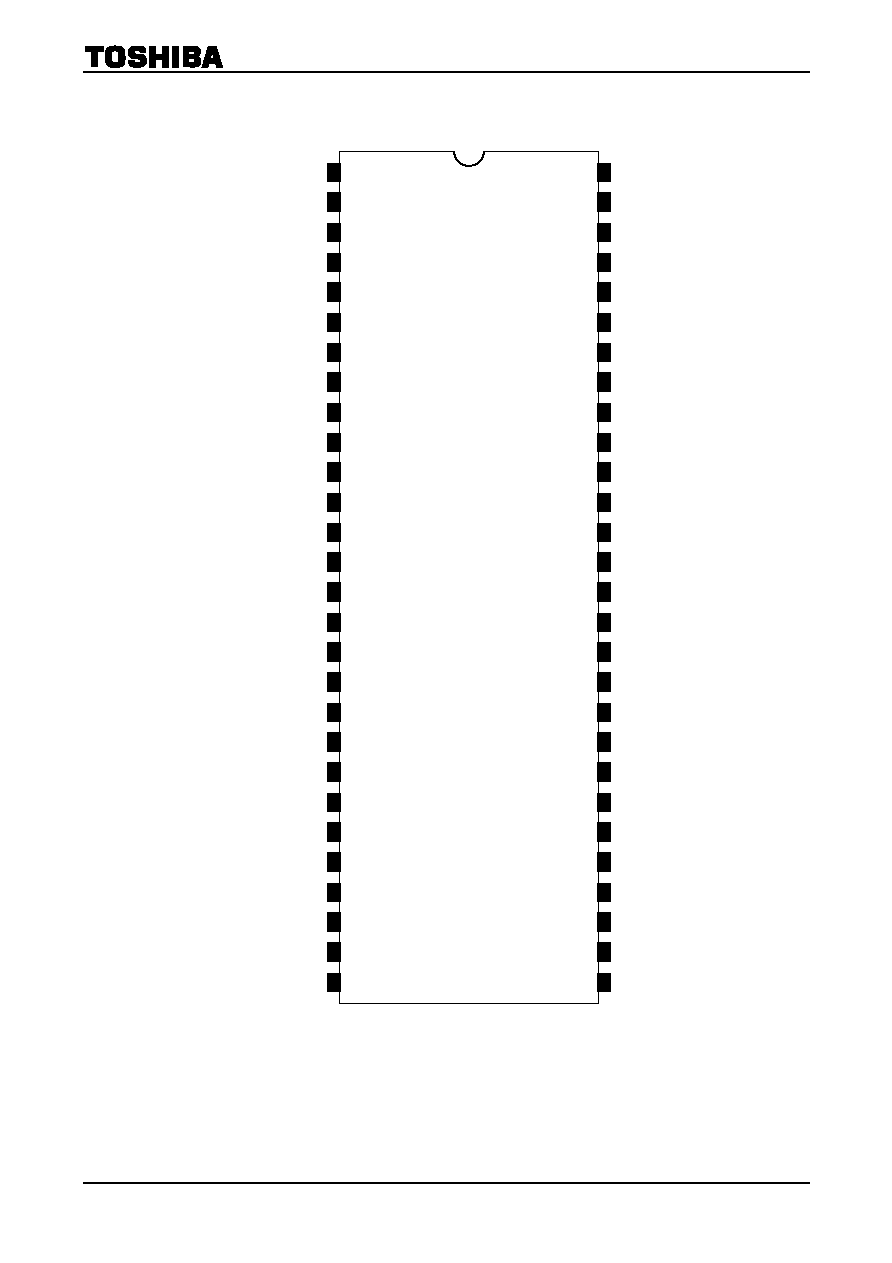

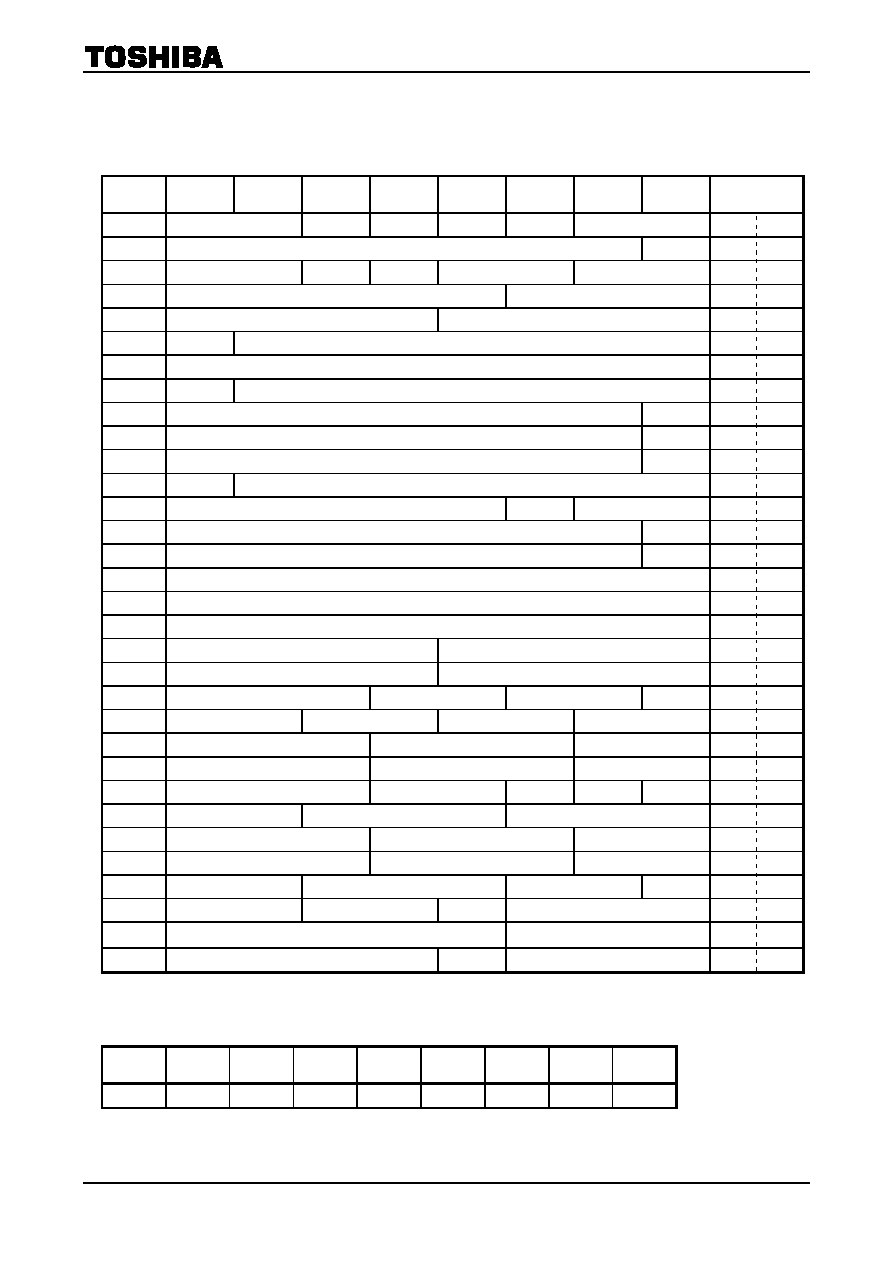

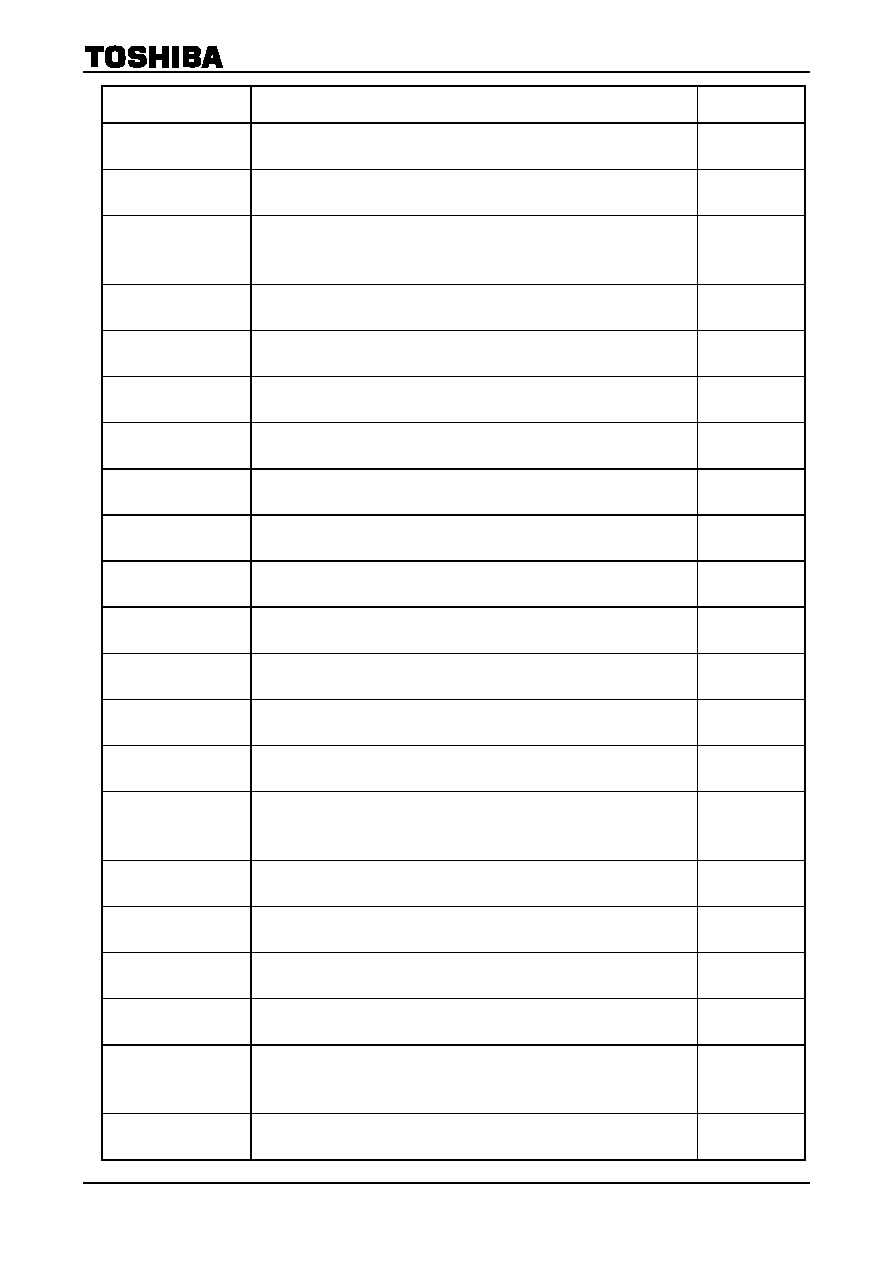

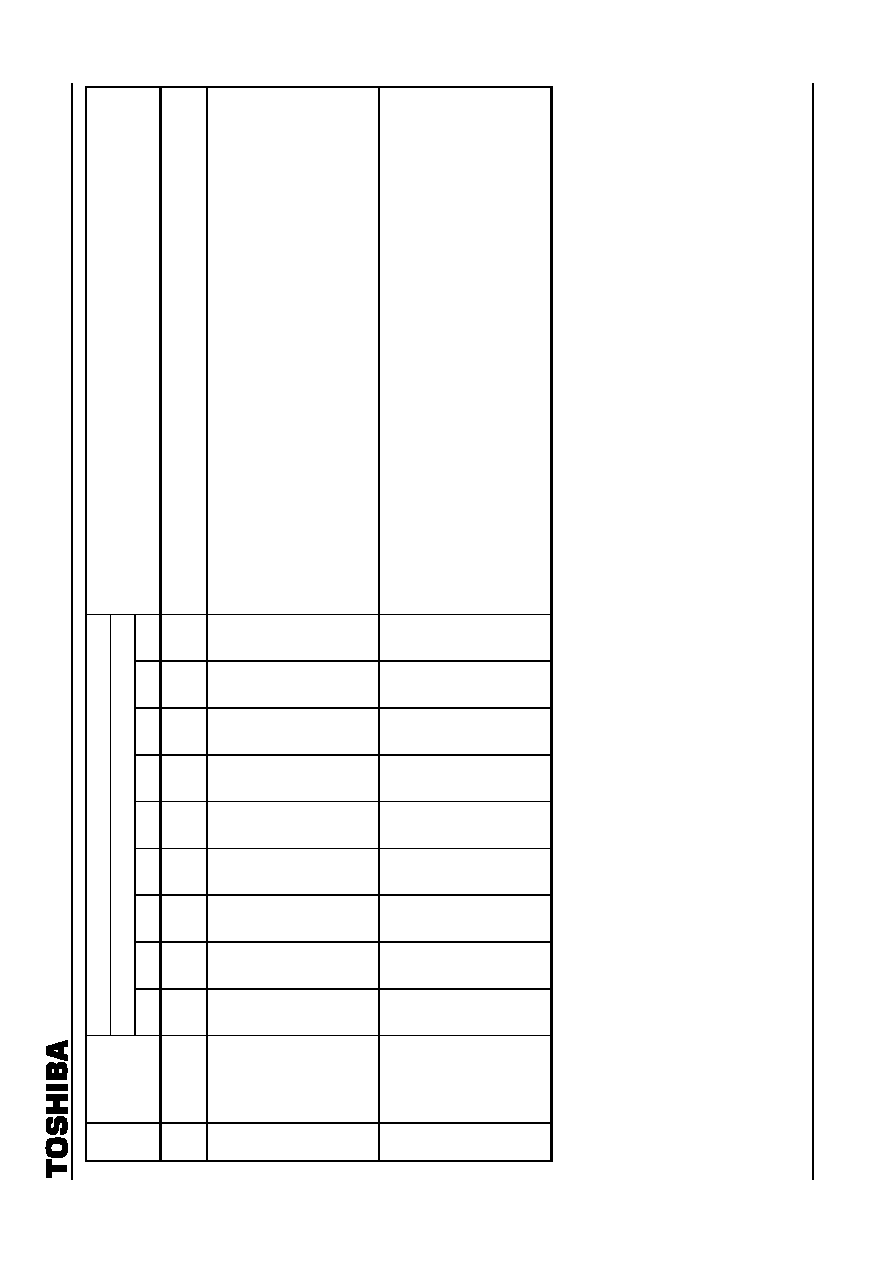

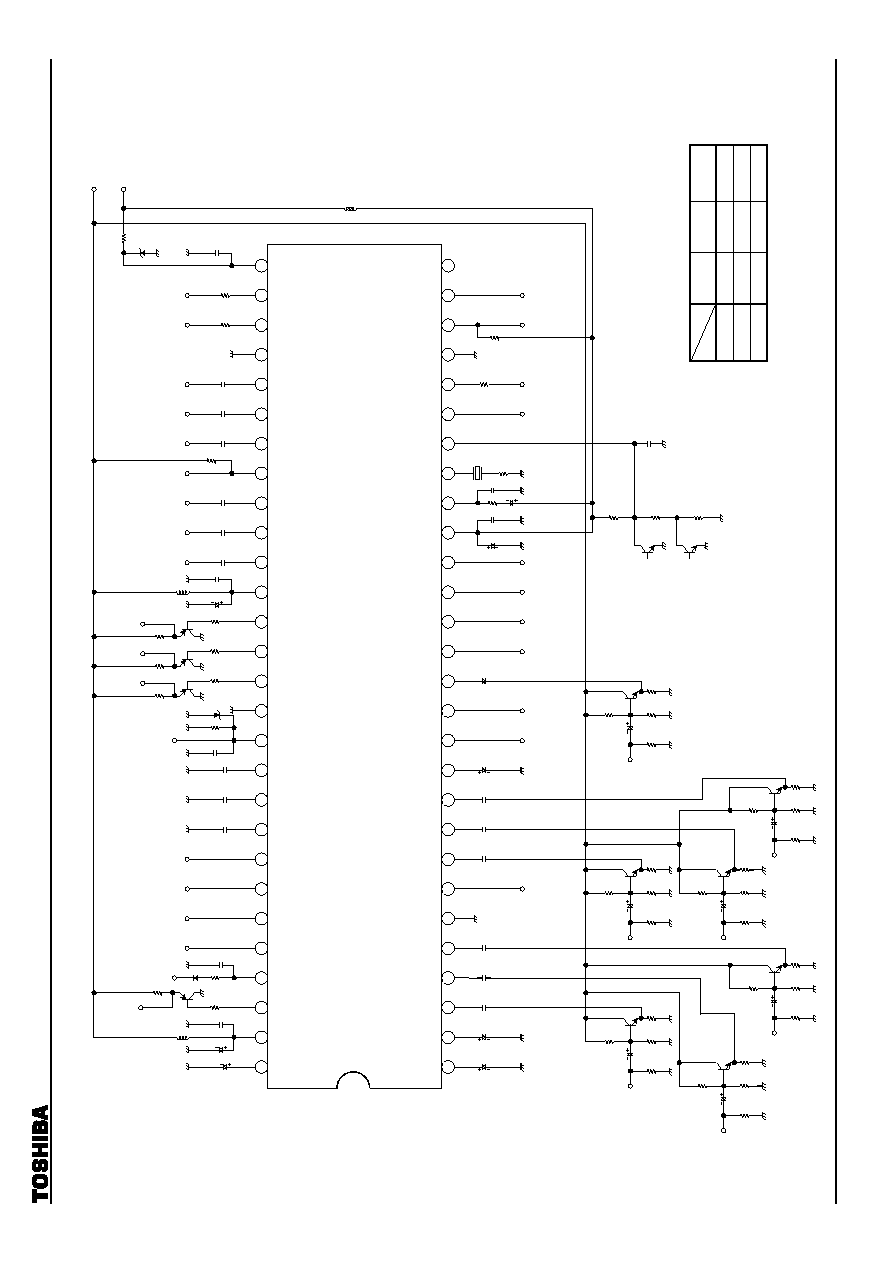

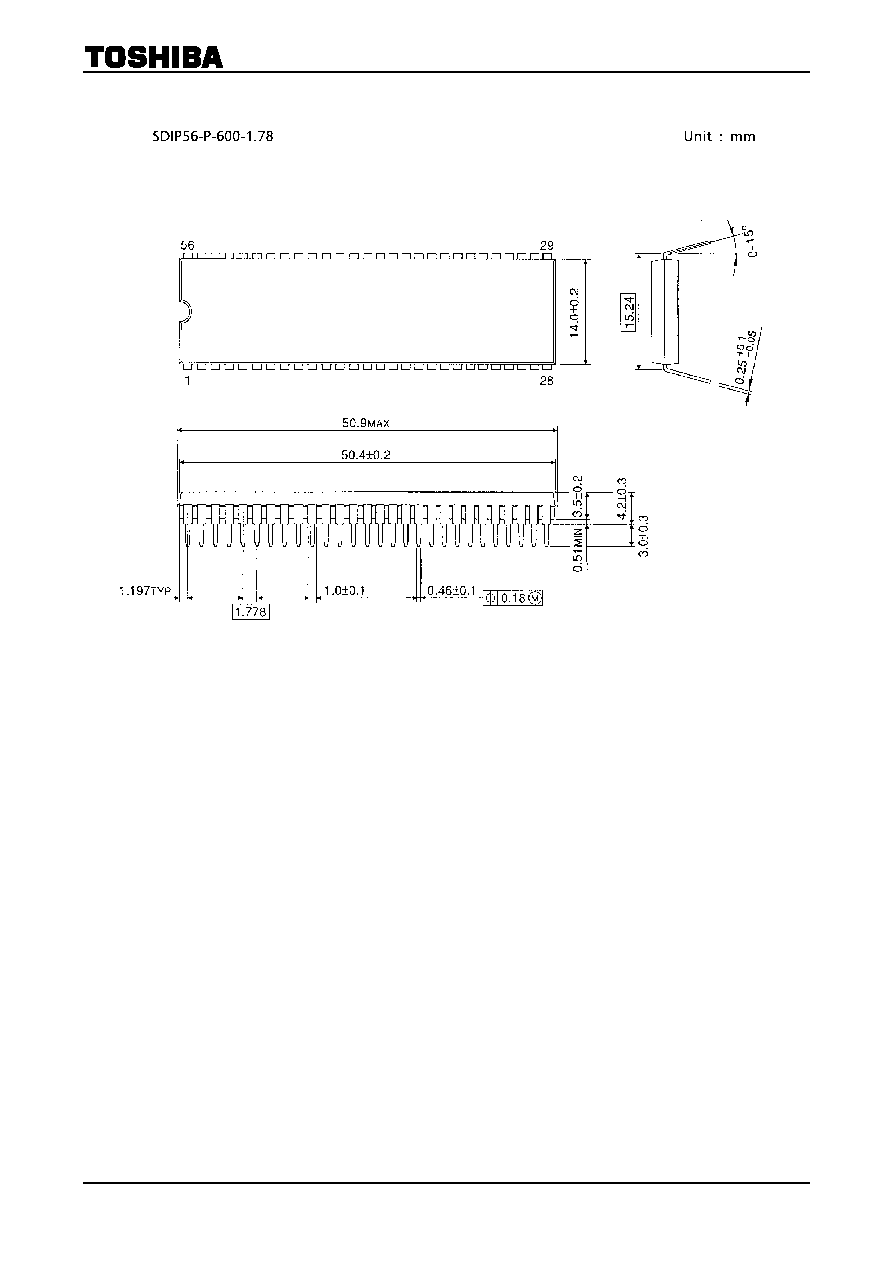

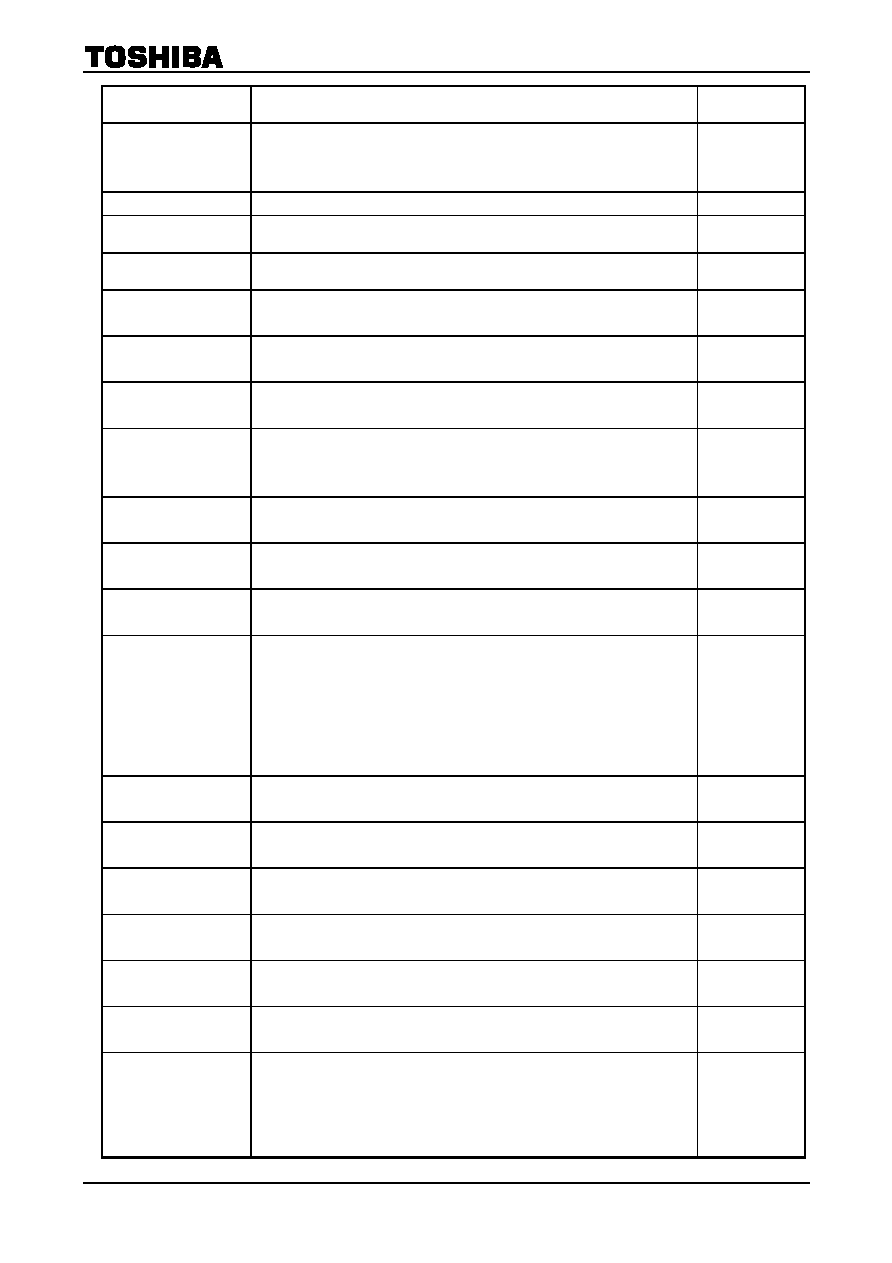

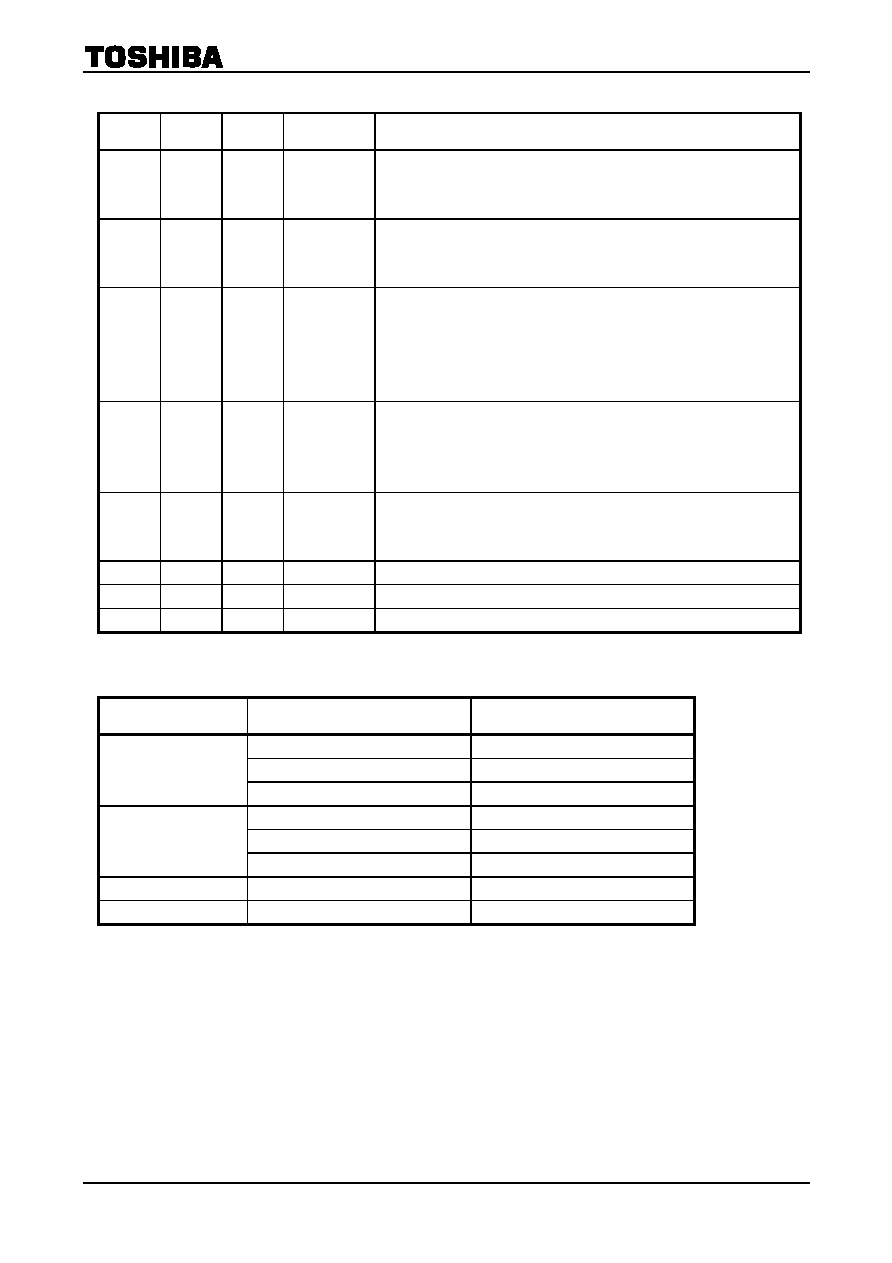

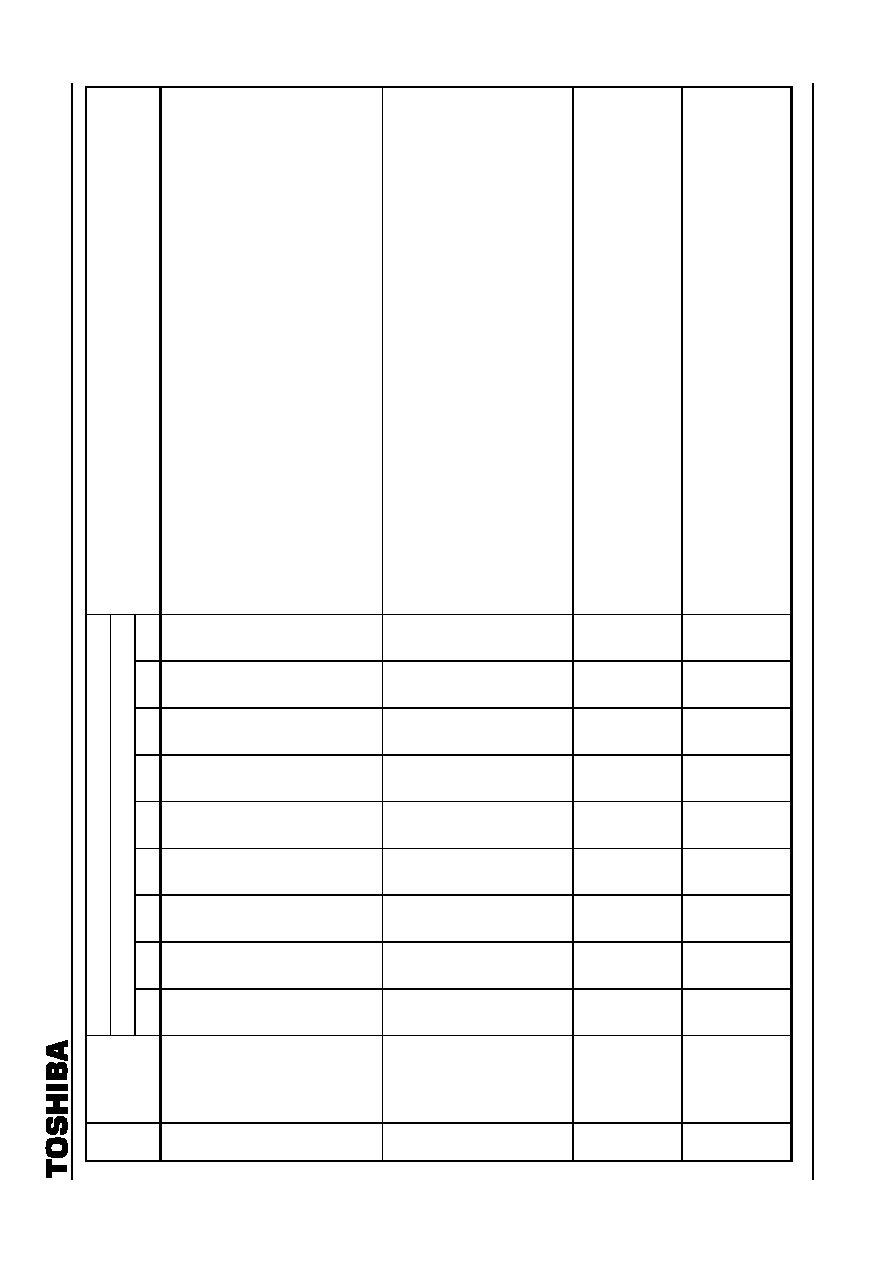

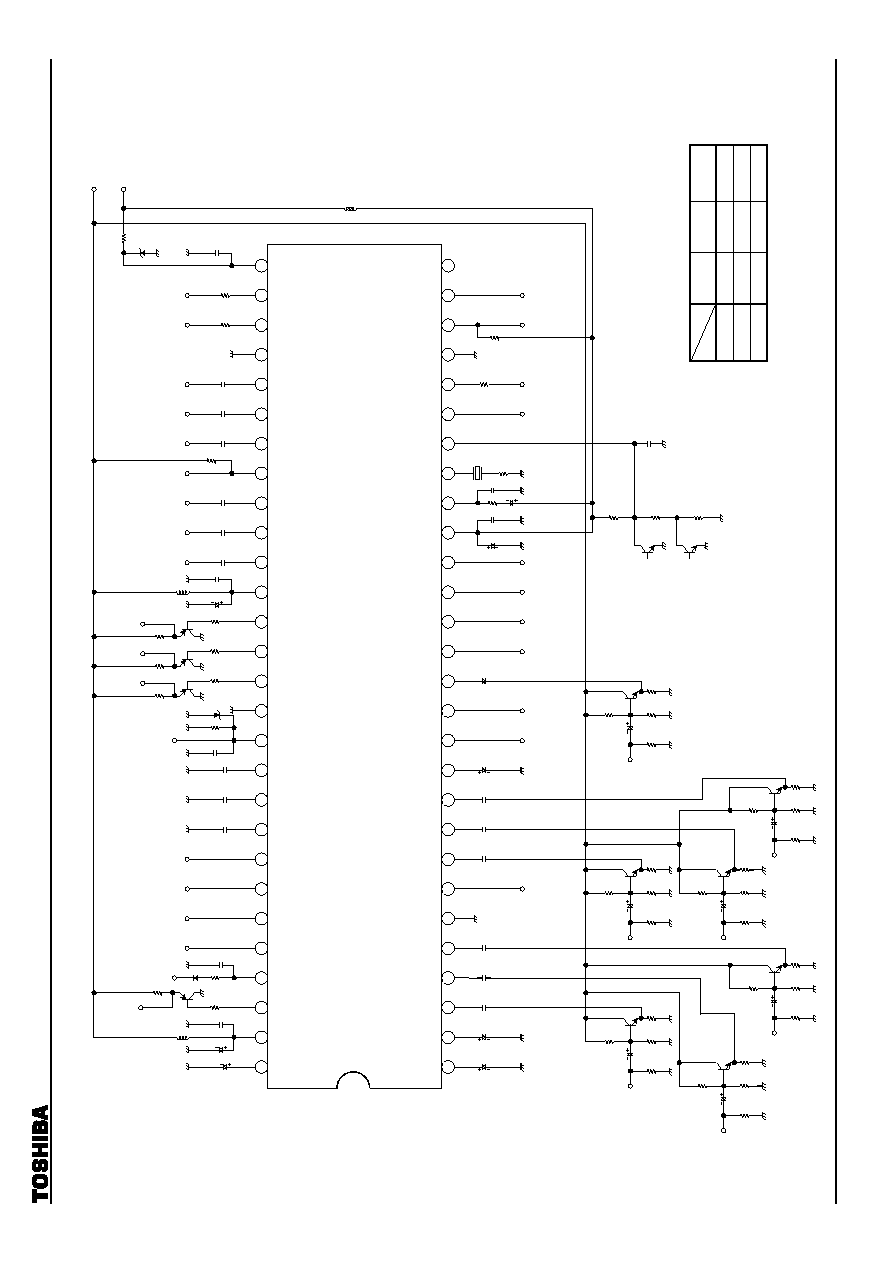

Pin Assignment

APL FILTER

56

Y/C V

CC

VSM OUT

ABCL IN

Y

M

/P-MUTE/BLK

Y

S

1 (analog OSD)

55

54

53

52

51

50

DARK AREA DET FILTER

1

2

3

4

5

6

7

BPH FILTER

Y1 IN

C

b1

/P

b1

IN

C

r1

/P

r1

IN

Y/C GND

MATRIX SW

Y

S

2 (analog OSD)

Y2 IN

8

9

10

11

12

13

14

C

b2

/P

b2

IN

C

r2

/P

r2

IN

COLOR LIMITER

VD2 IN

HD2 IN

SYNC IN

VD1 IN 15

16

17

18

19

20

21

HD1 IN

SCP IN

SCP OUT

DEF/DAC V

CC

AFC FILTER

HVCO

HORIZONTAL FREQUENCY SW 22

23

24

25

26

27

28

H CURVE CORRECTION

FBP IN

DEF/DAC GND

H-OUT

VP OUT

Y

S

3 (analog RGB)

49

R S/H

G S/H

48

47

B S/H

46

I

K

IN

RGB GND

R OUT

G OUT

B OUT

45

44

43

42

41

40 RGB V

CC

ANALOG OSD R IN

39

ANALOG OSD G IN

ANALOG OSD B IN

38

37

DAC2 (ACB pulse)

36

ANALOG R IN

ANALOG G IN

ANALOG B IN

I

2

L GND

SDA

35

34

33

32

31

30 SCL

I

2

L V

DD

29

TA1316AN

TA1316AN

2002-10-04

4

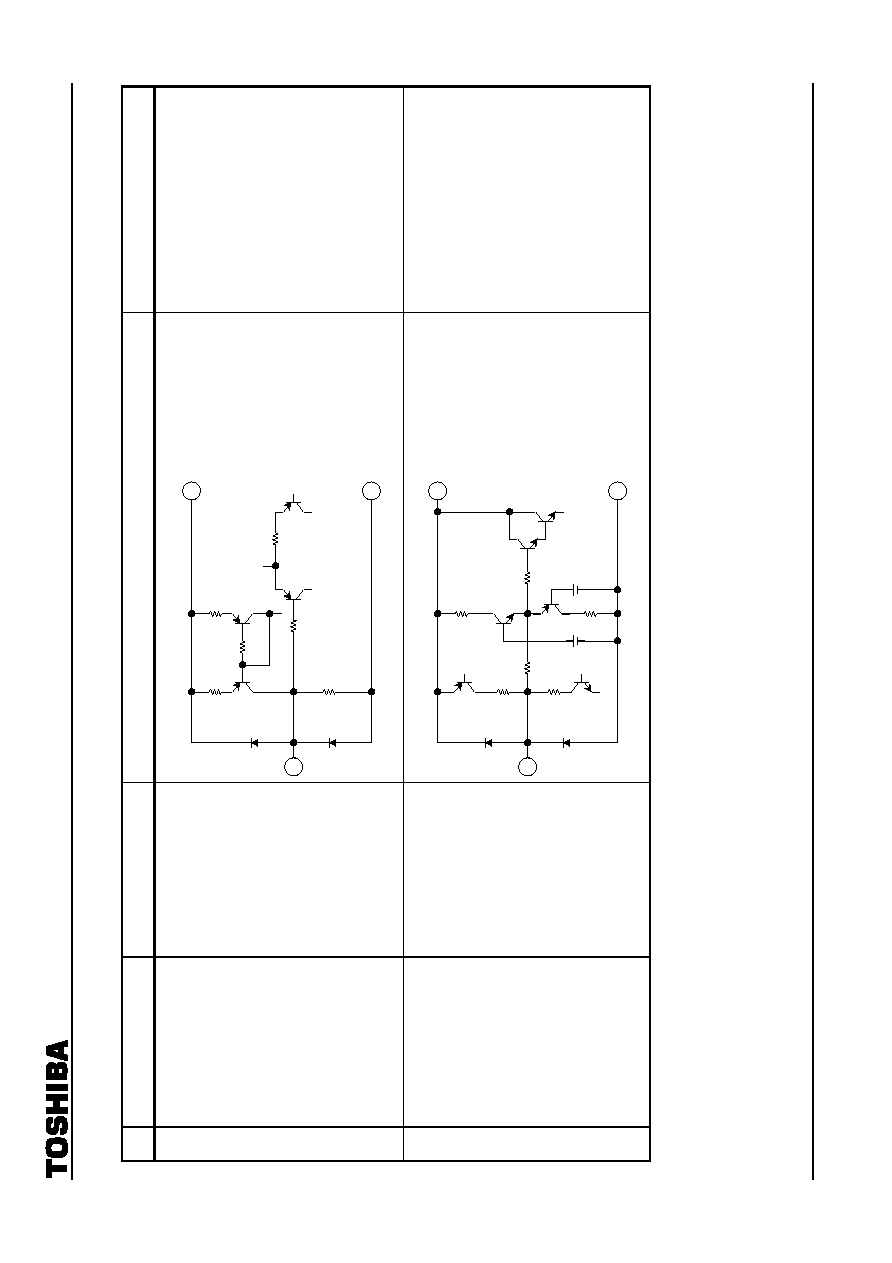

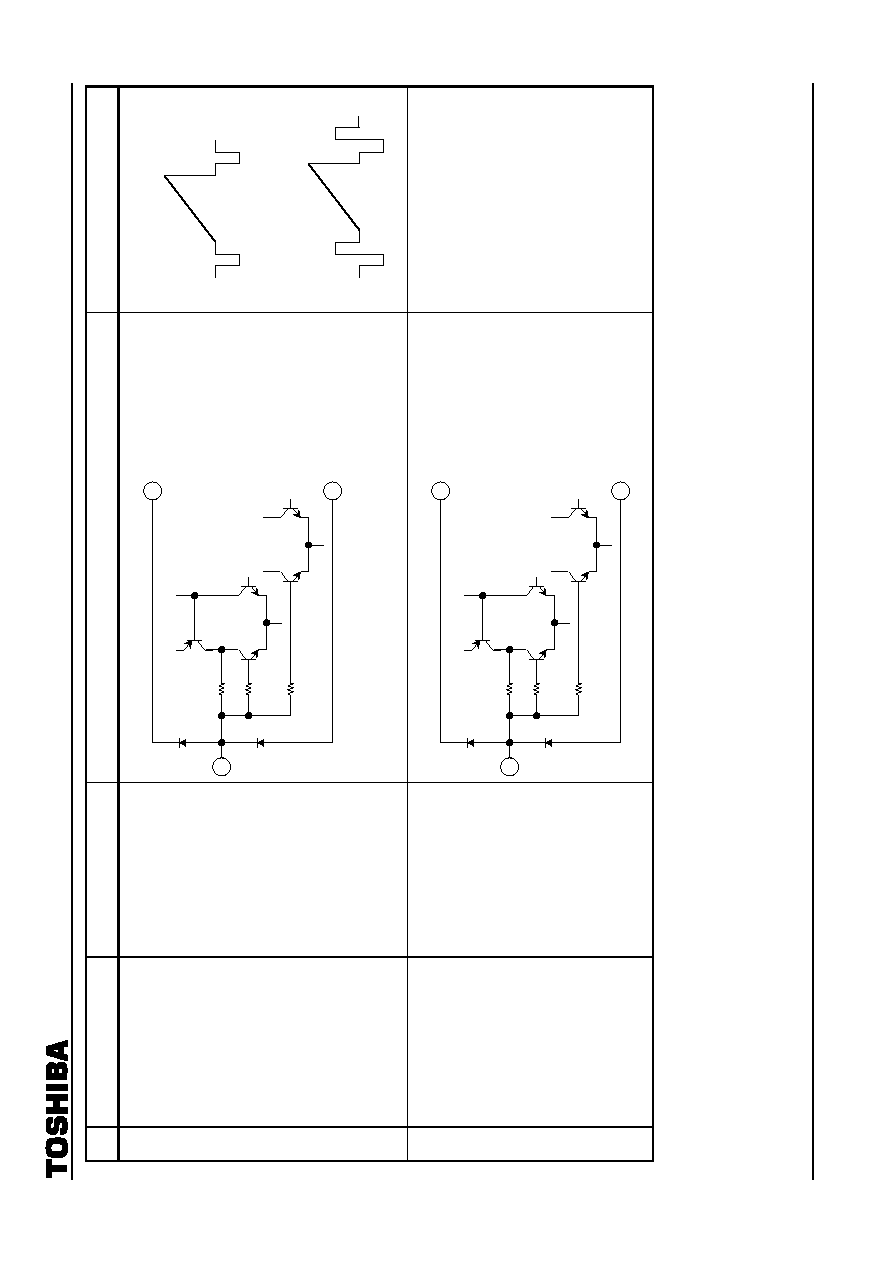

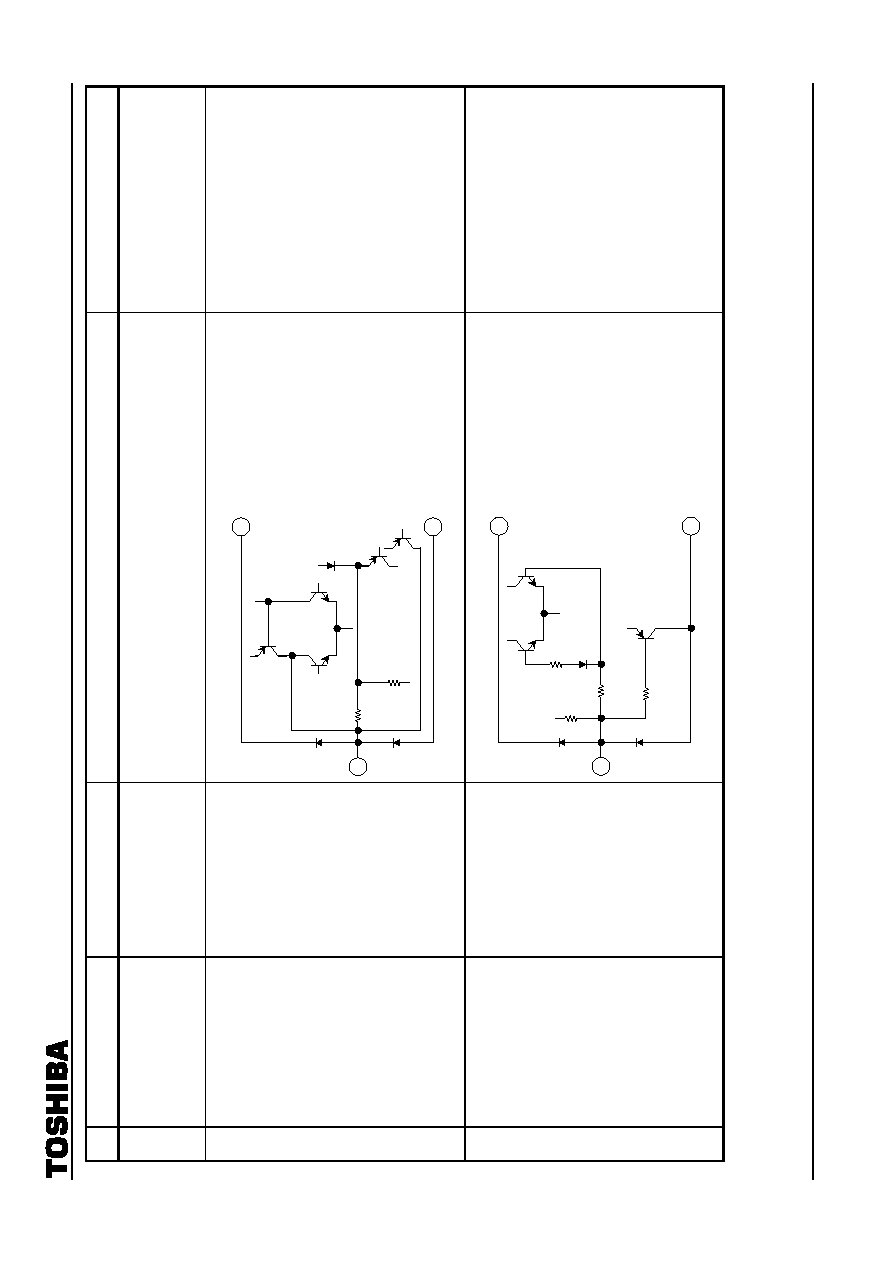

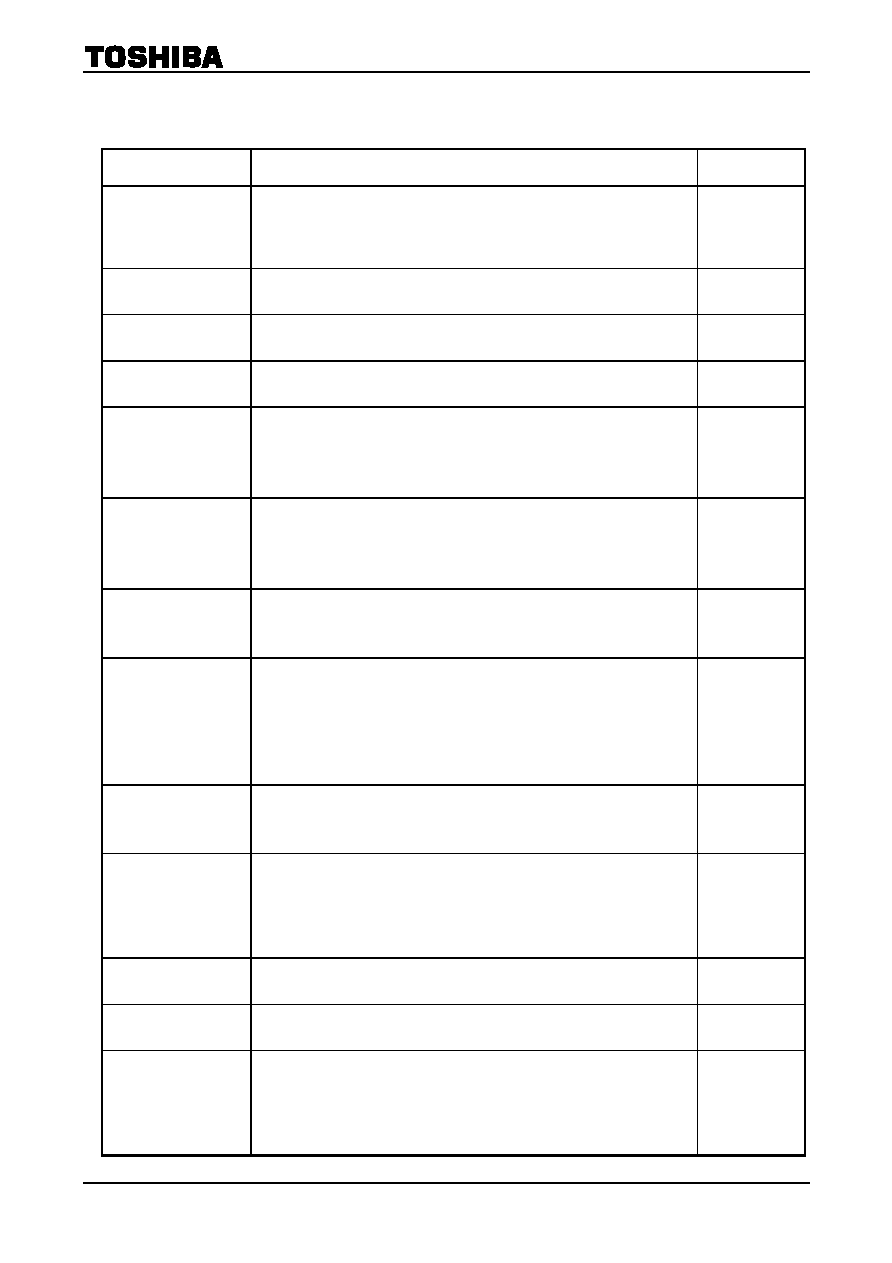

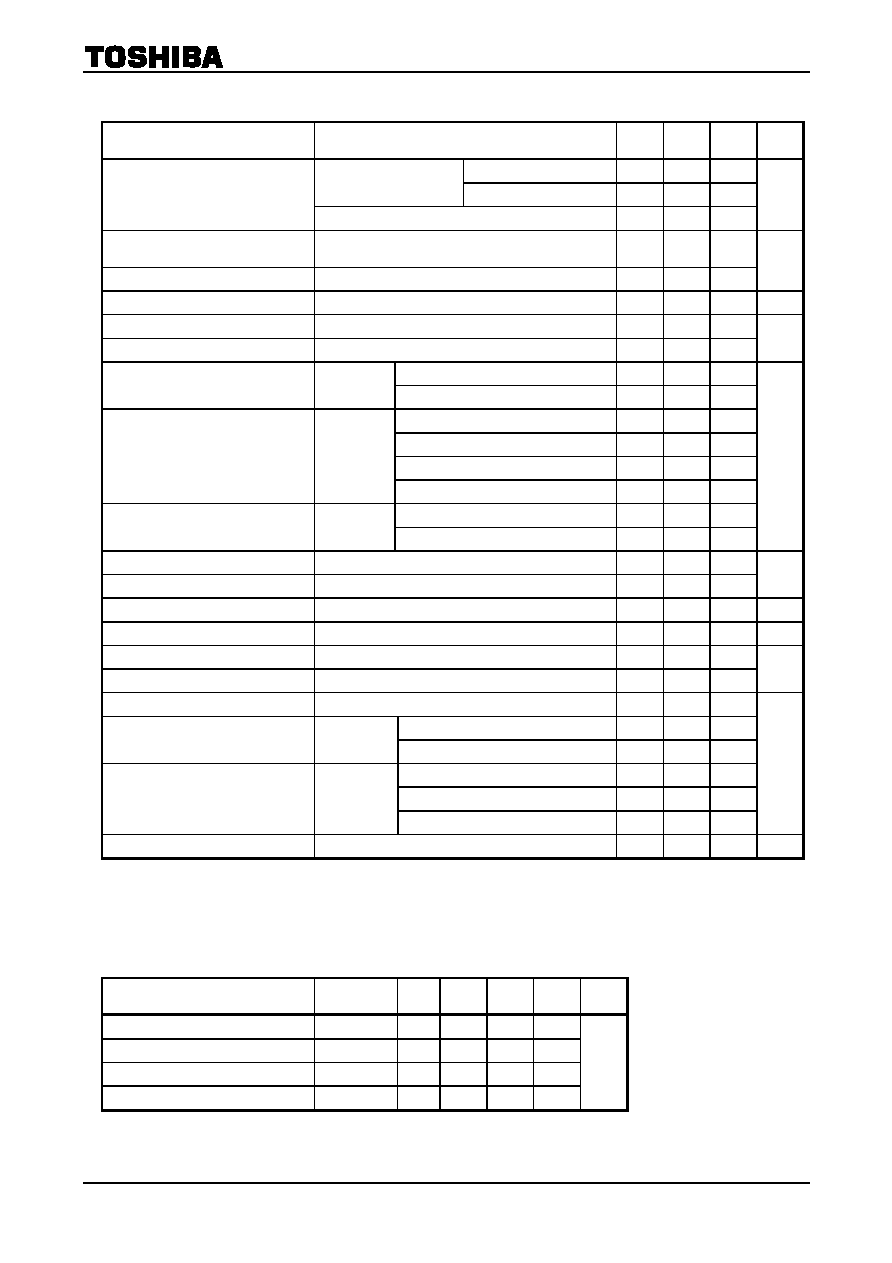

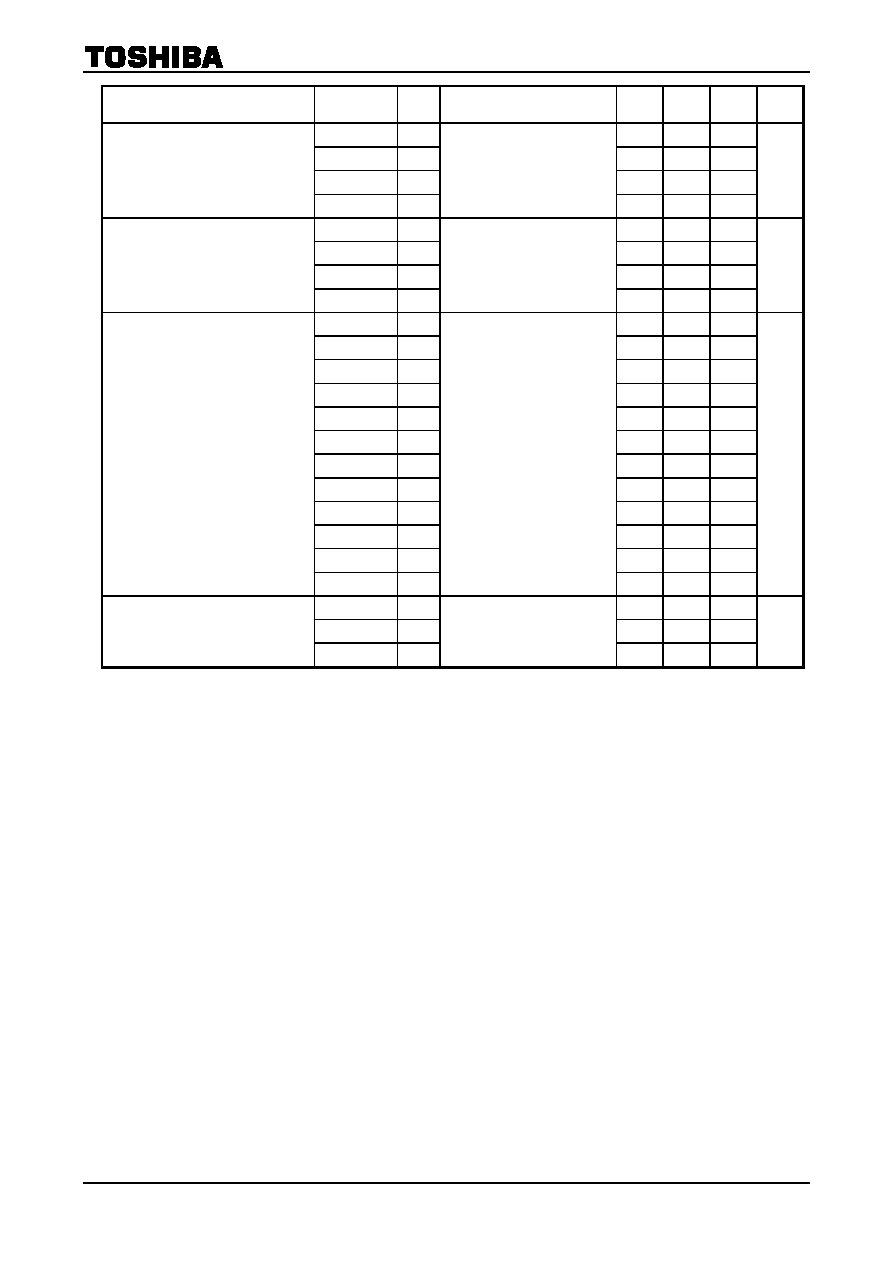

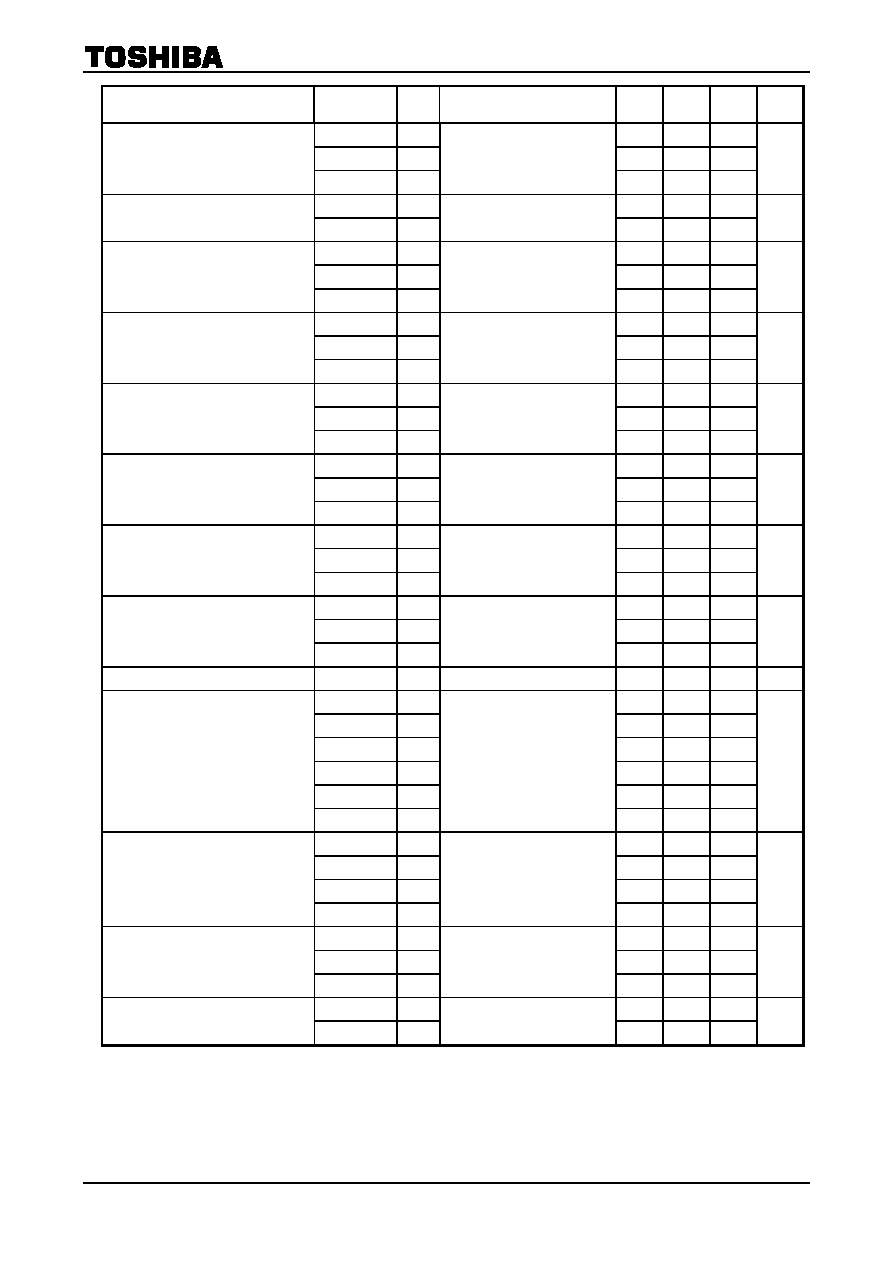

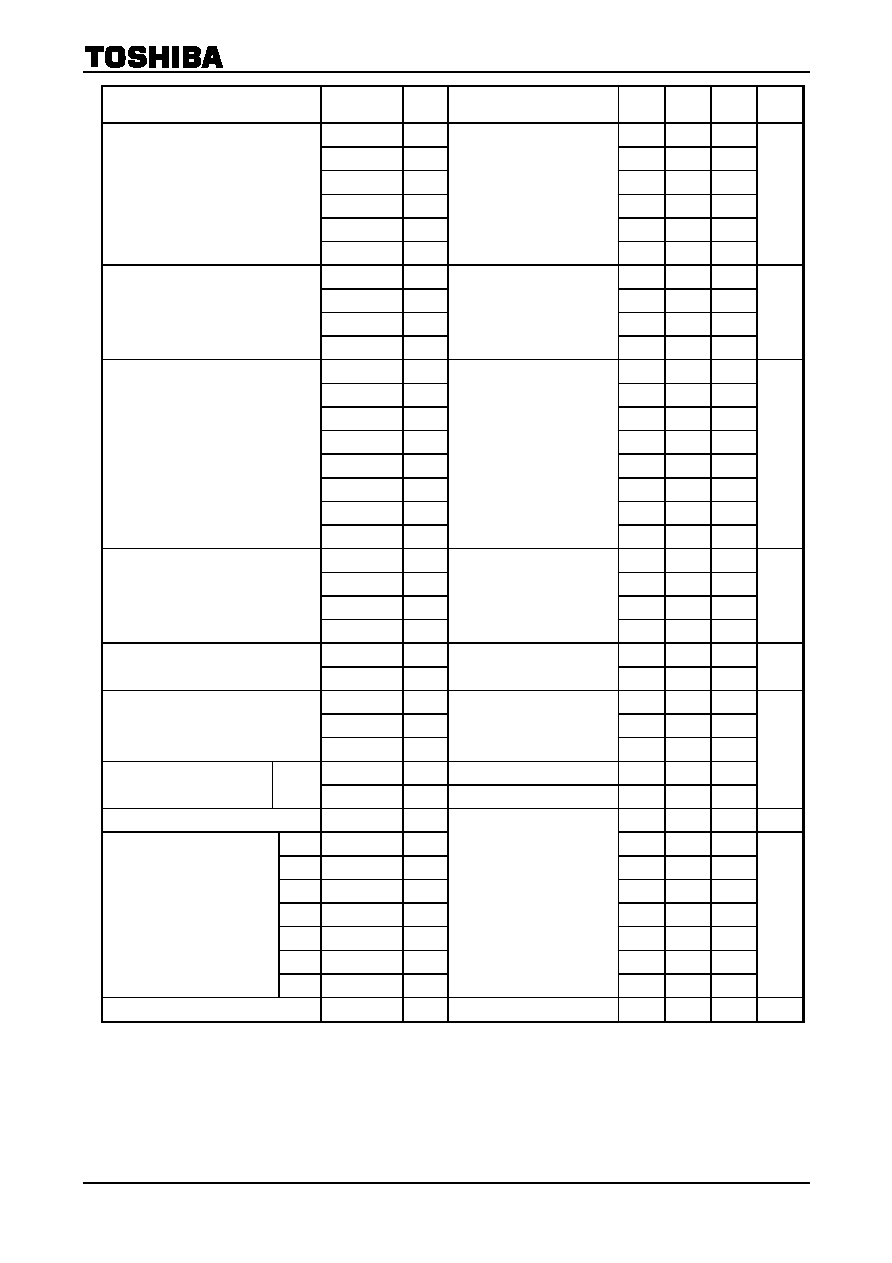

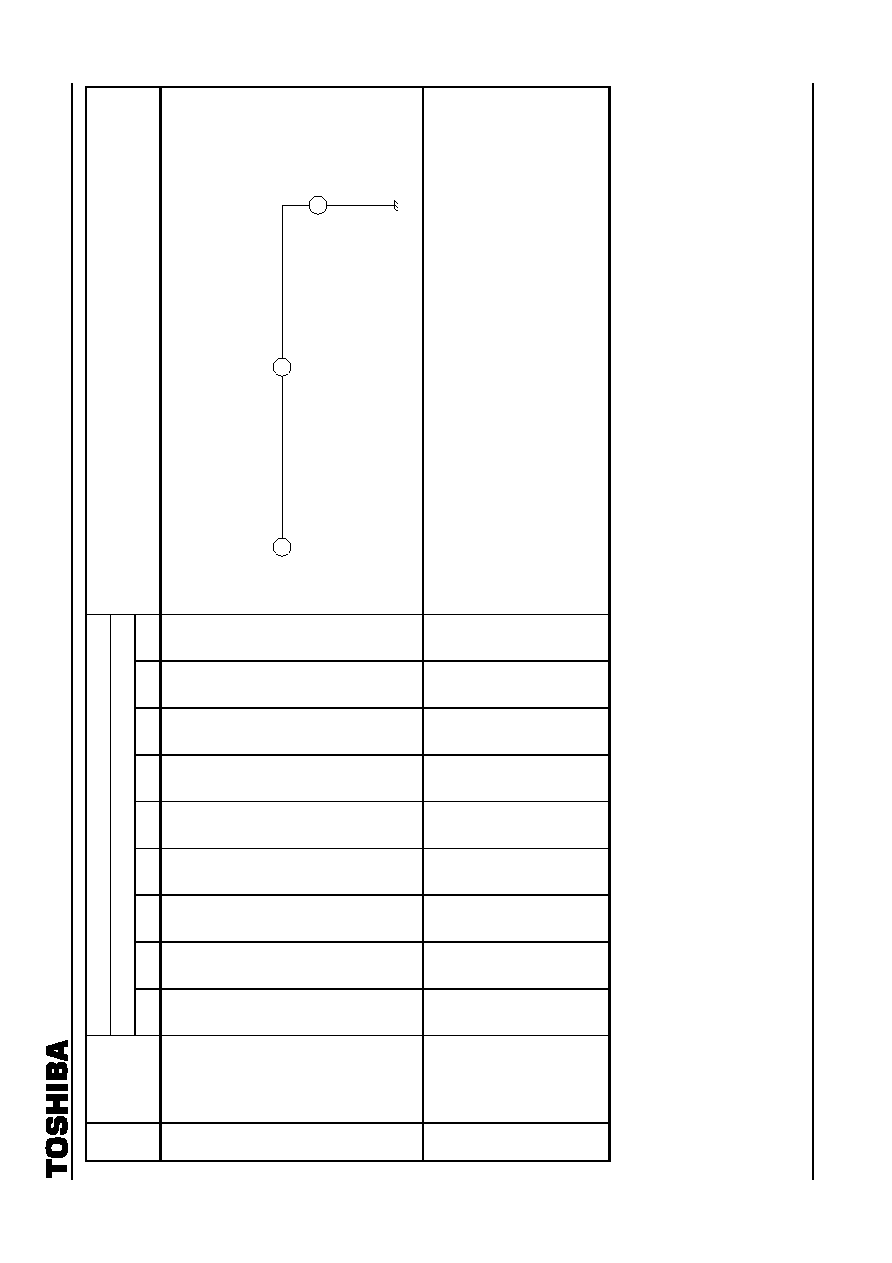

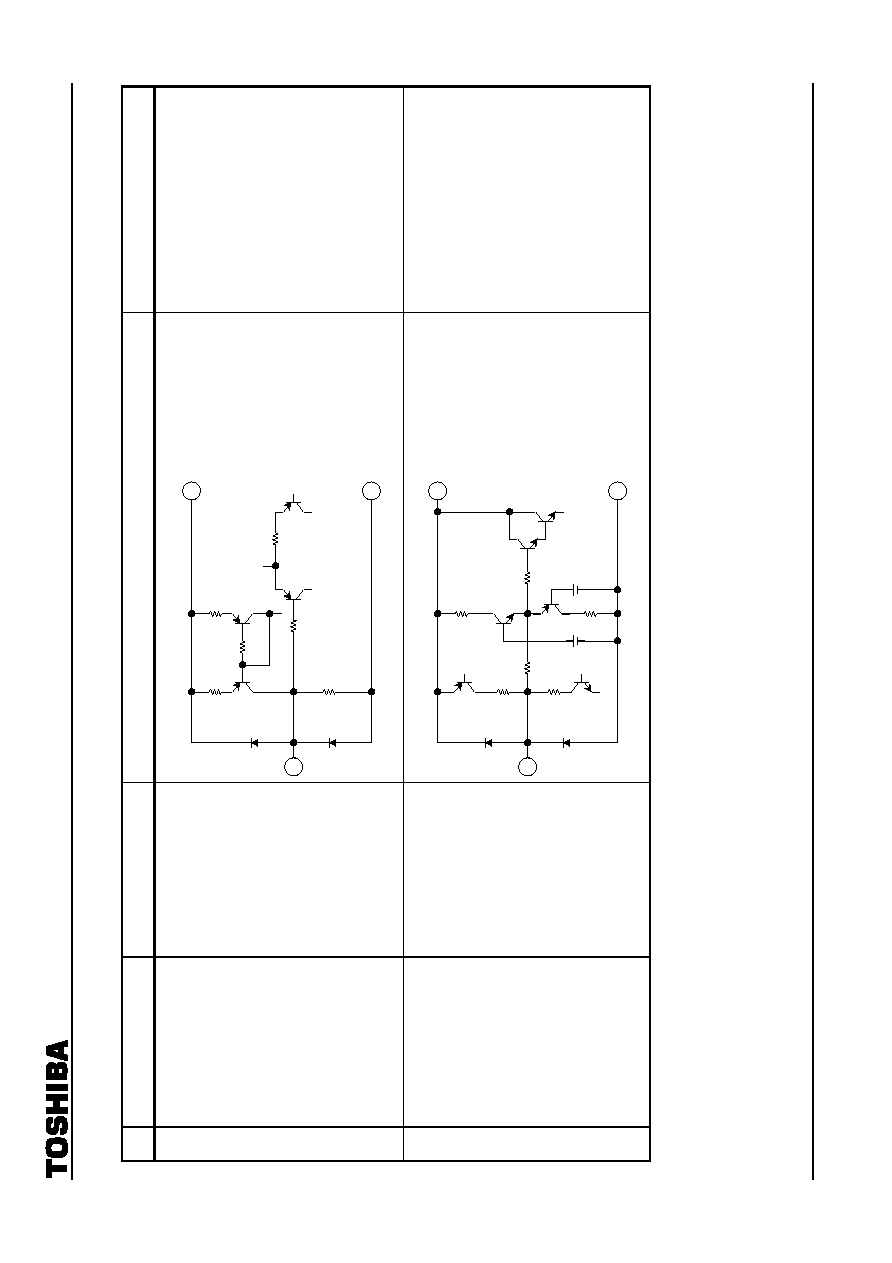

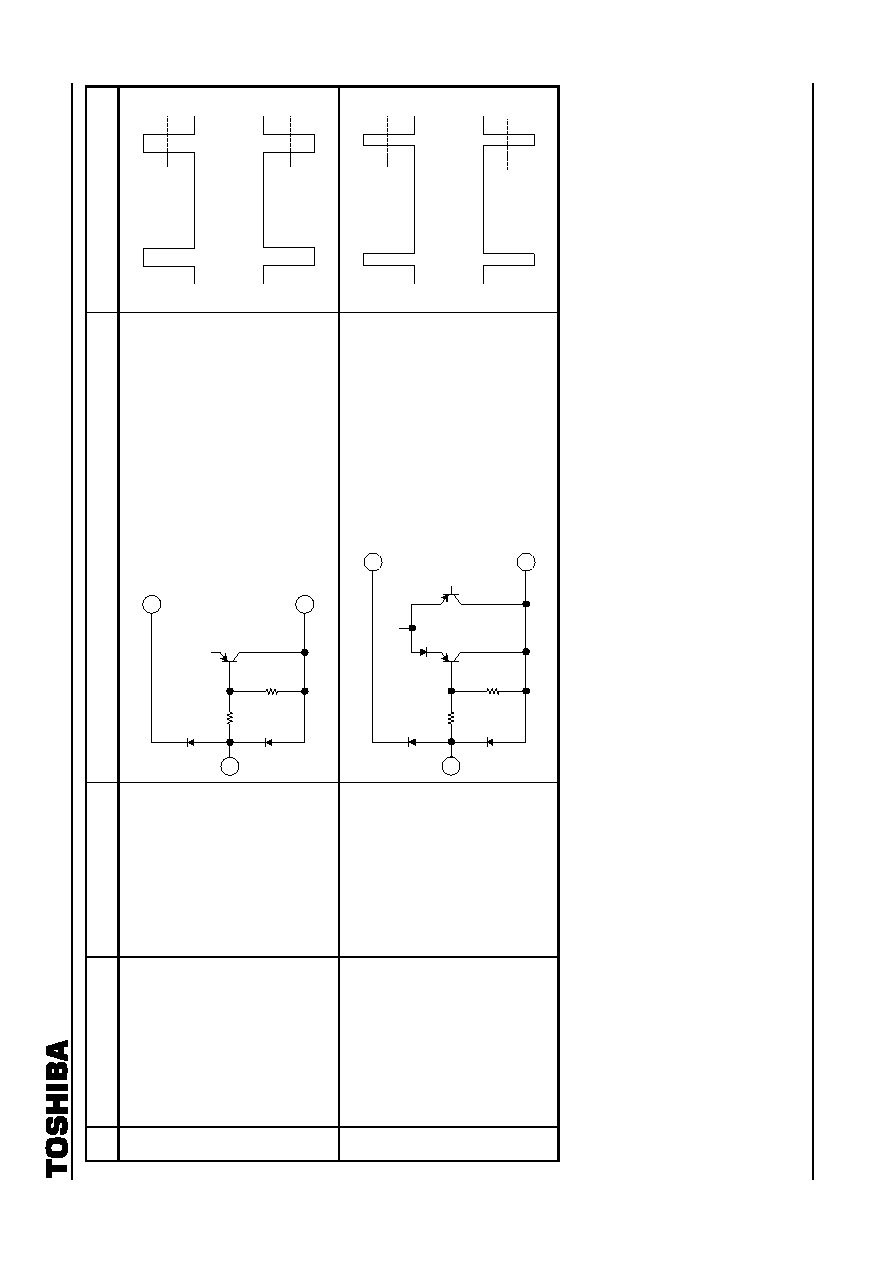

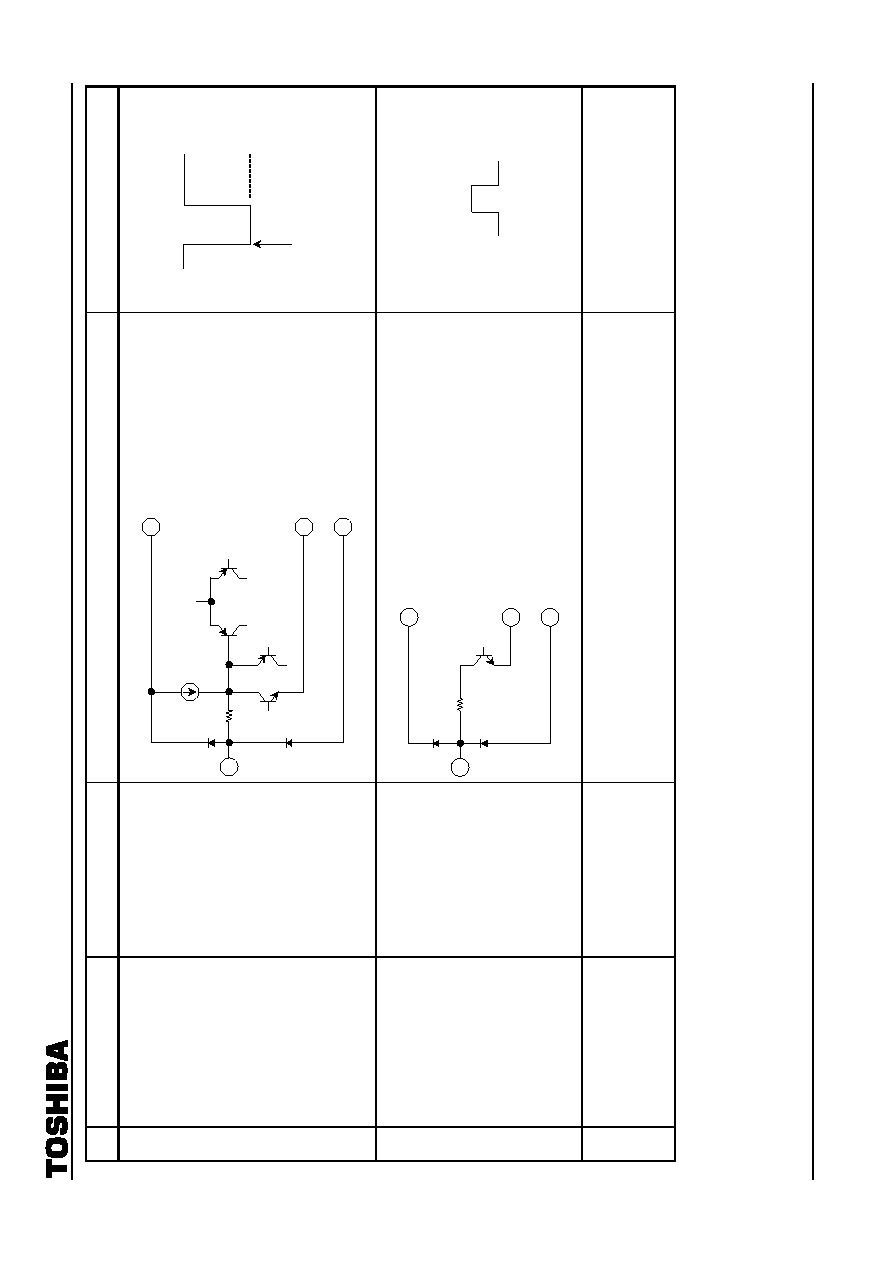

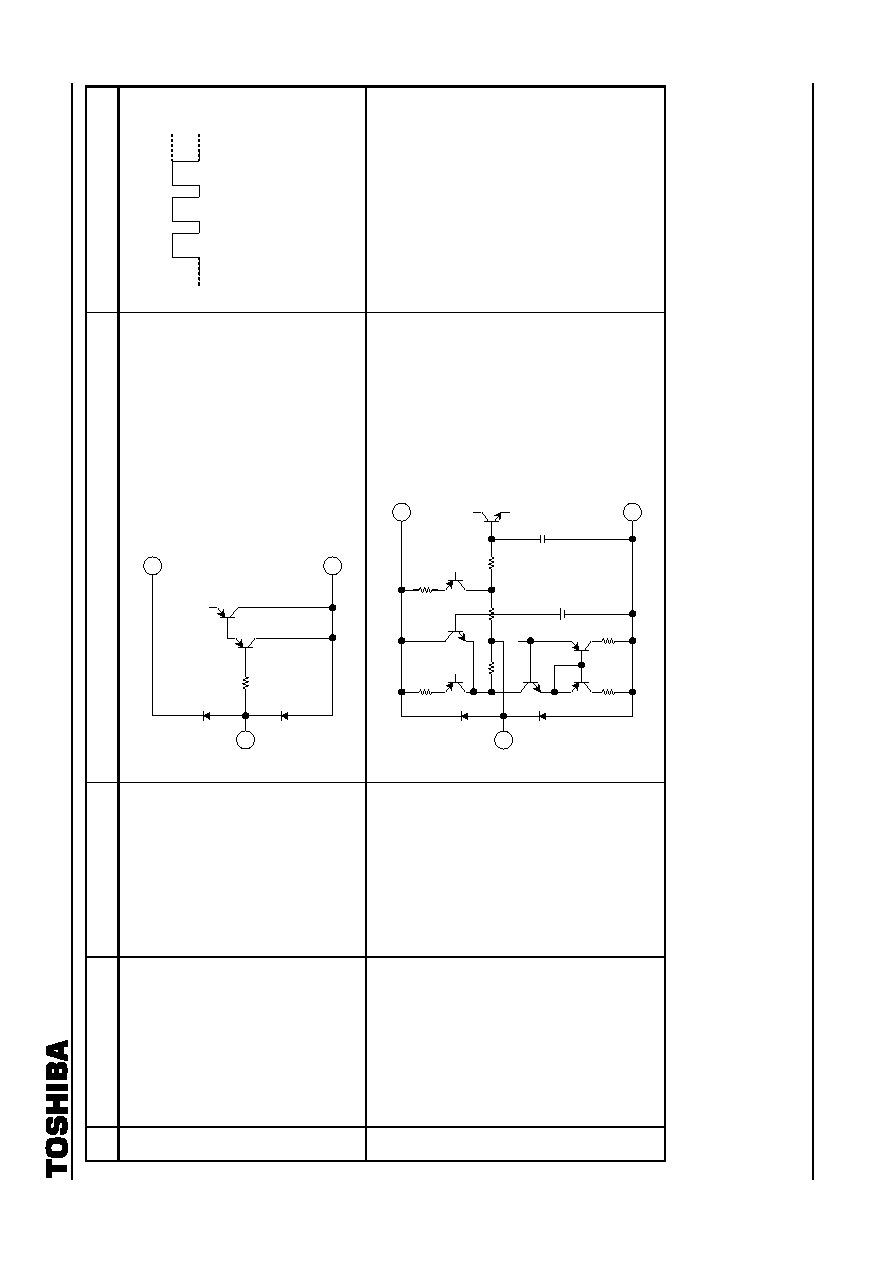

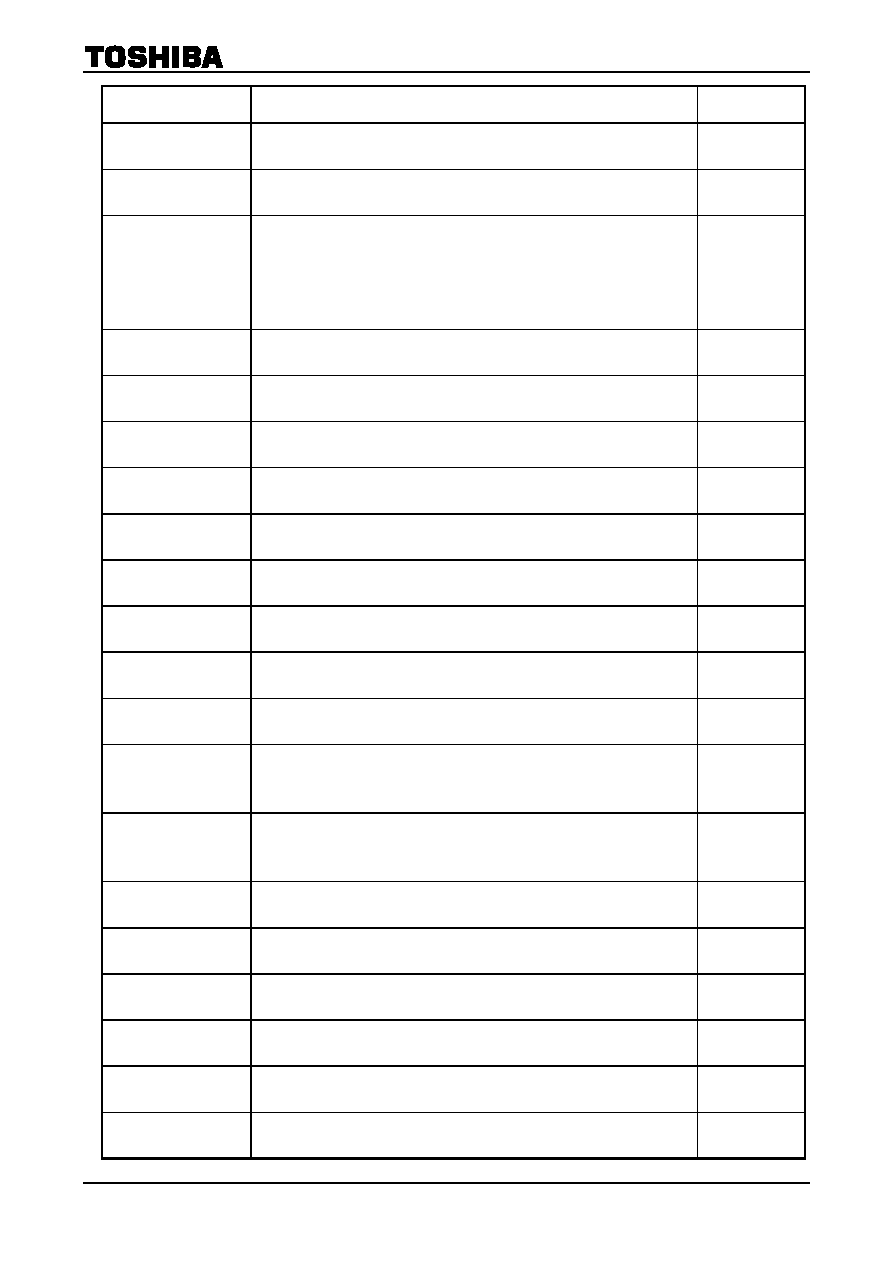

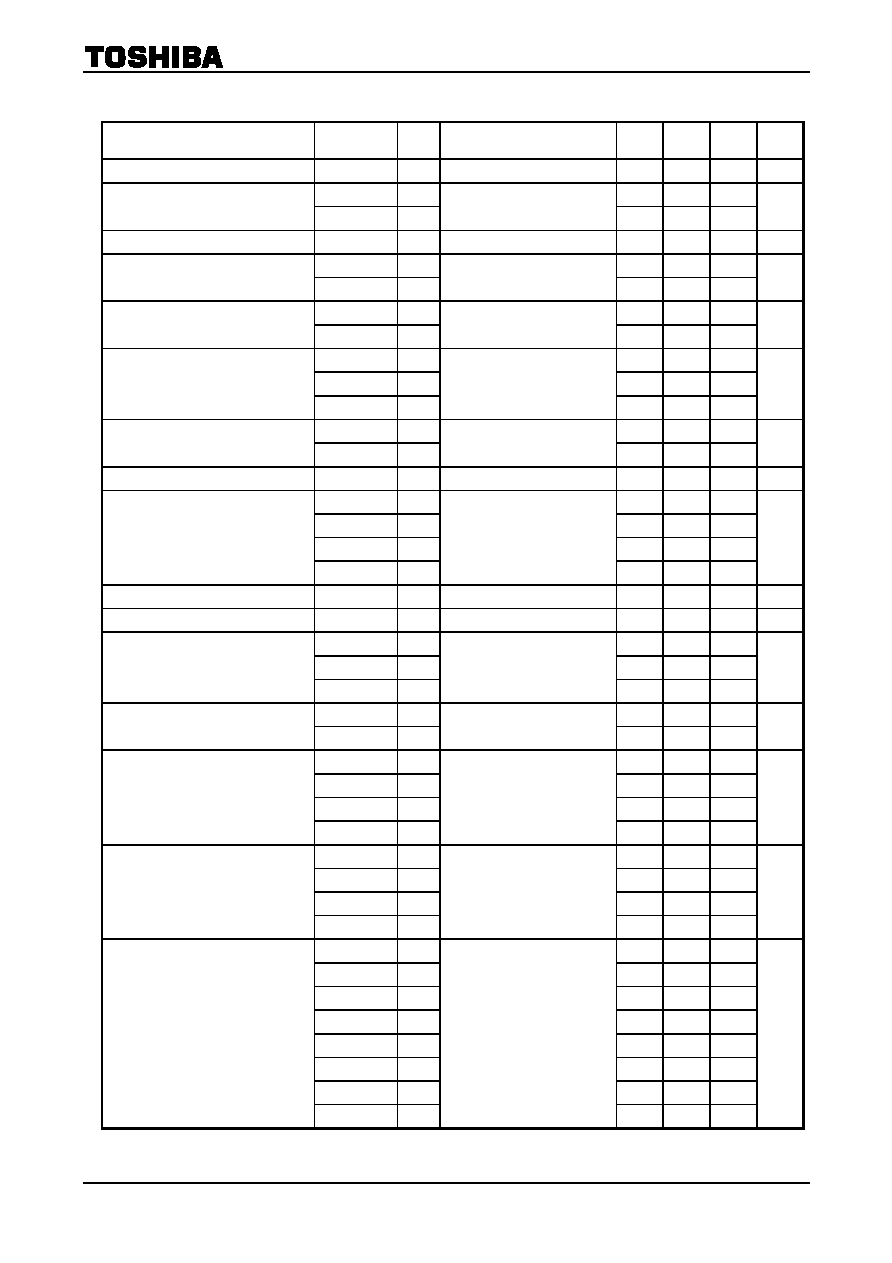

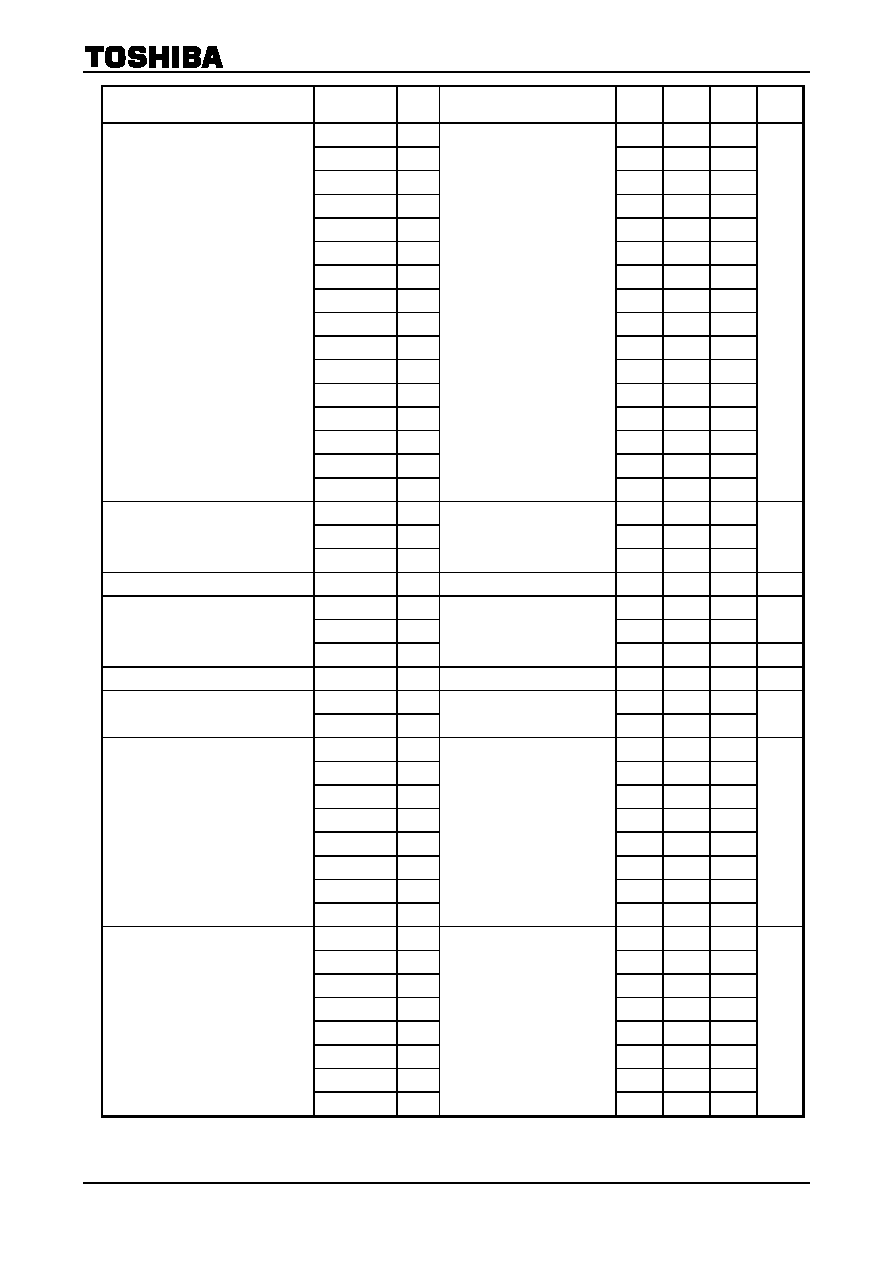

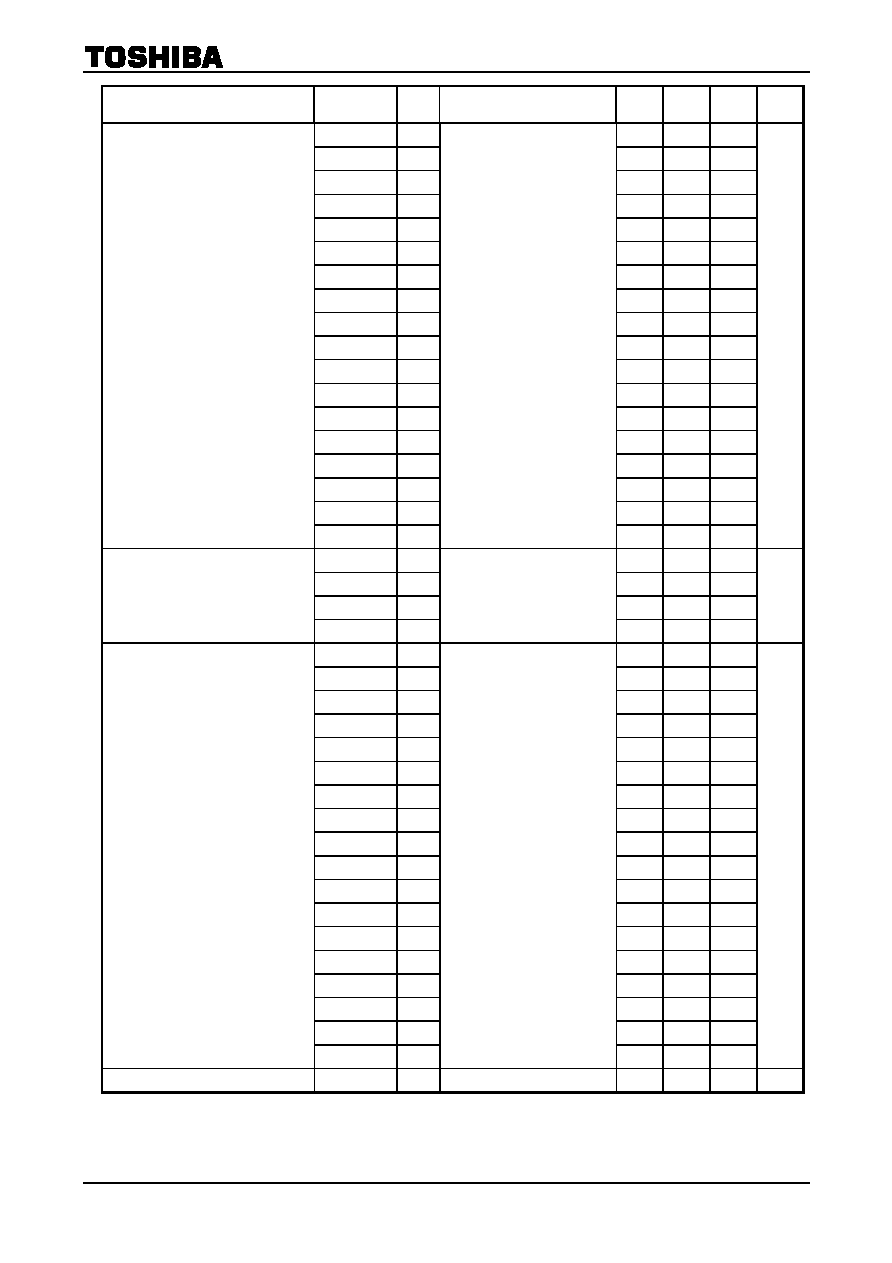

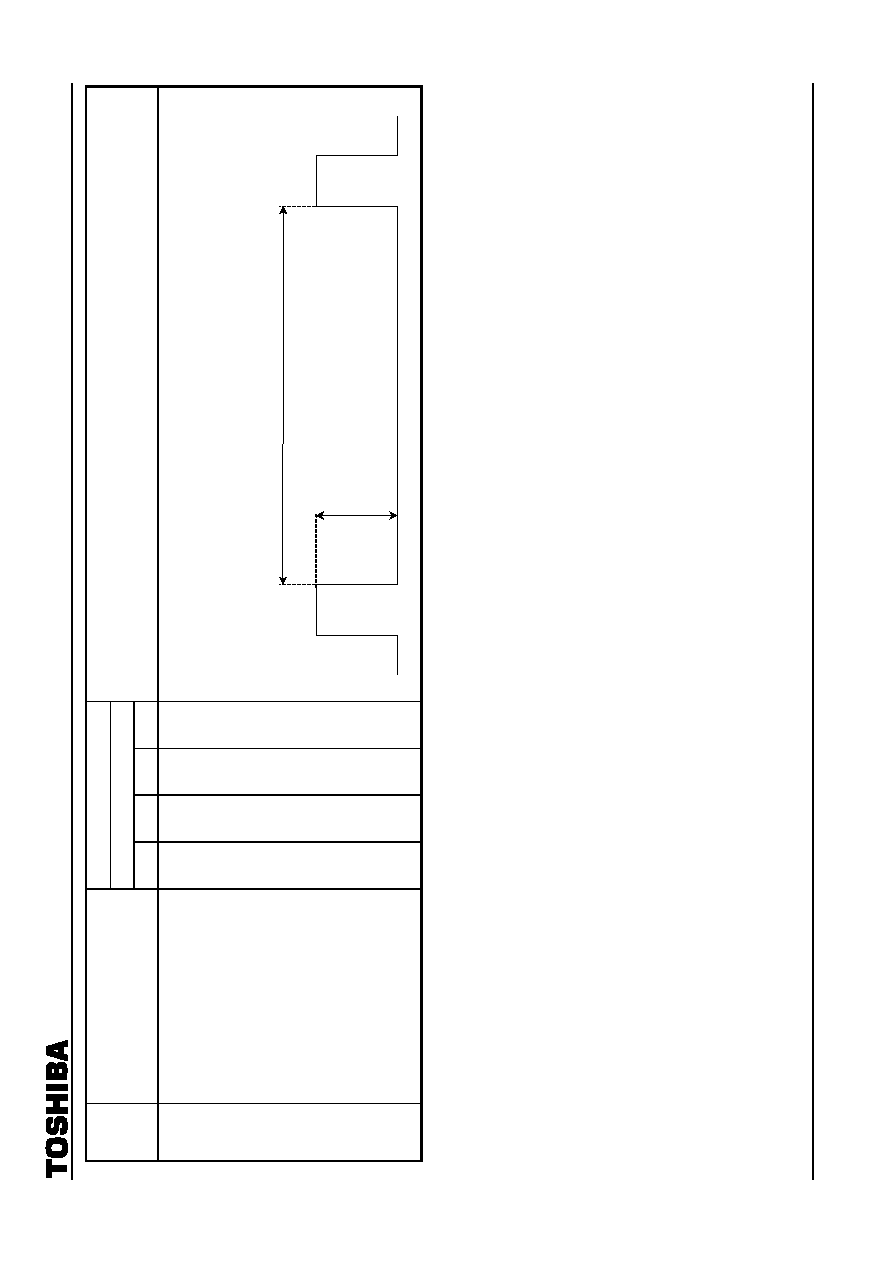

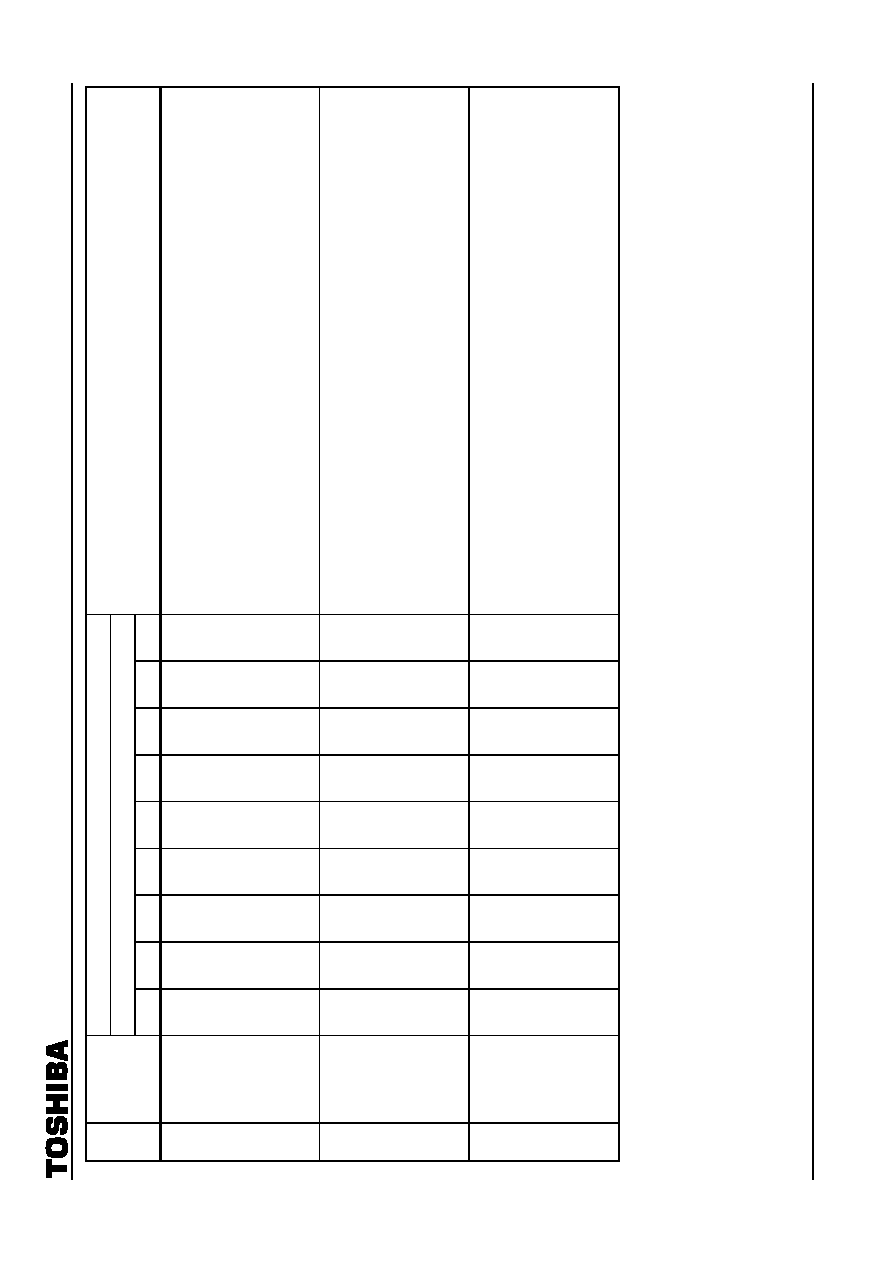

Pin Functions

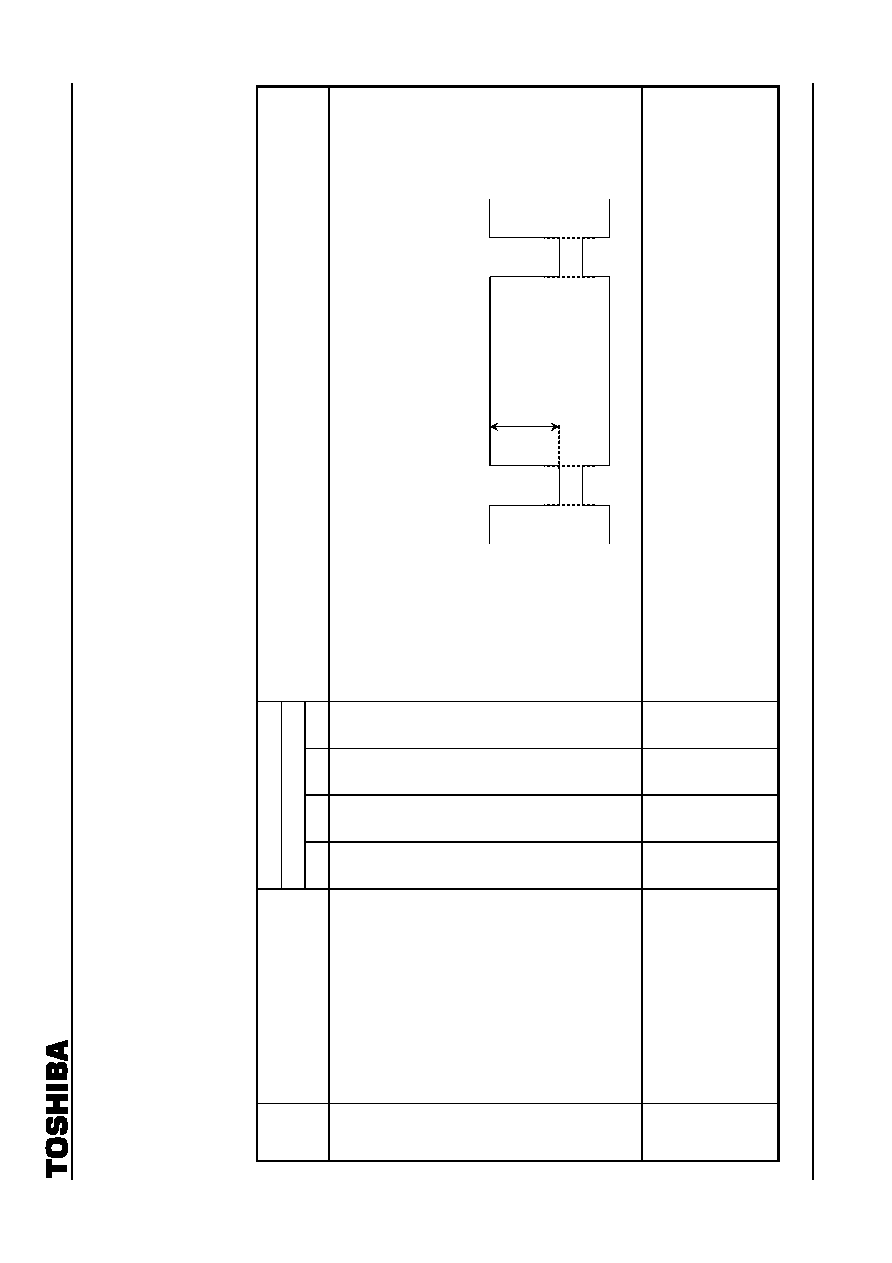

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

1

DARK AREA DET

FILTER

Connect filter for detecting

black area.

Voltage value of this pin

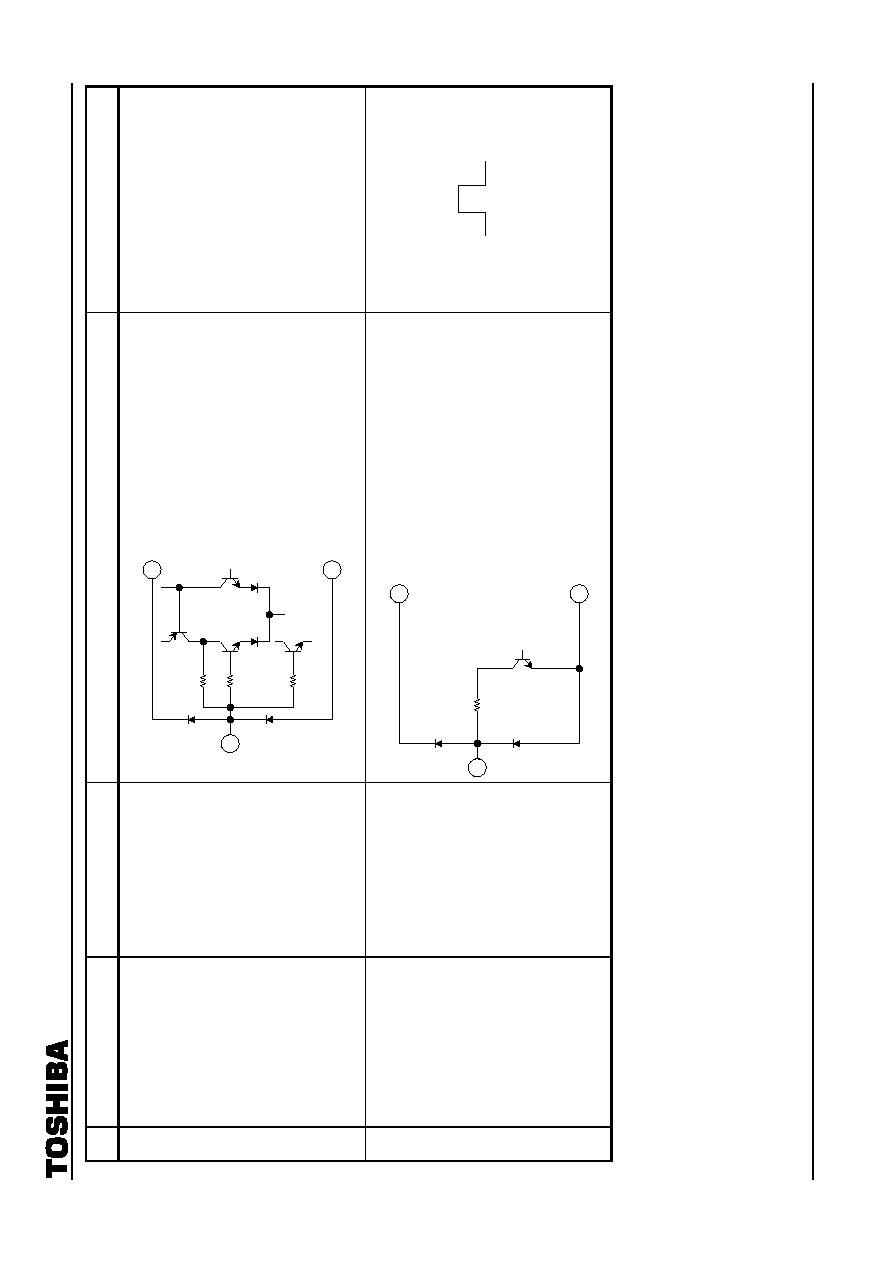

controls dynamic

circuit gain.

DC

2 BPH

FILTER

Connect filter for detecting

black peak.

Voltage value of this pin

controls black stretch gain.

DC

55

1

6

50 k

5 k

55

2

6

1 k

200

4 k

1 k

1 k

1 k

5 V

4.

25 V

TA1316AN

2002-10-04

5

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

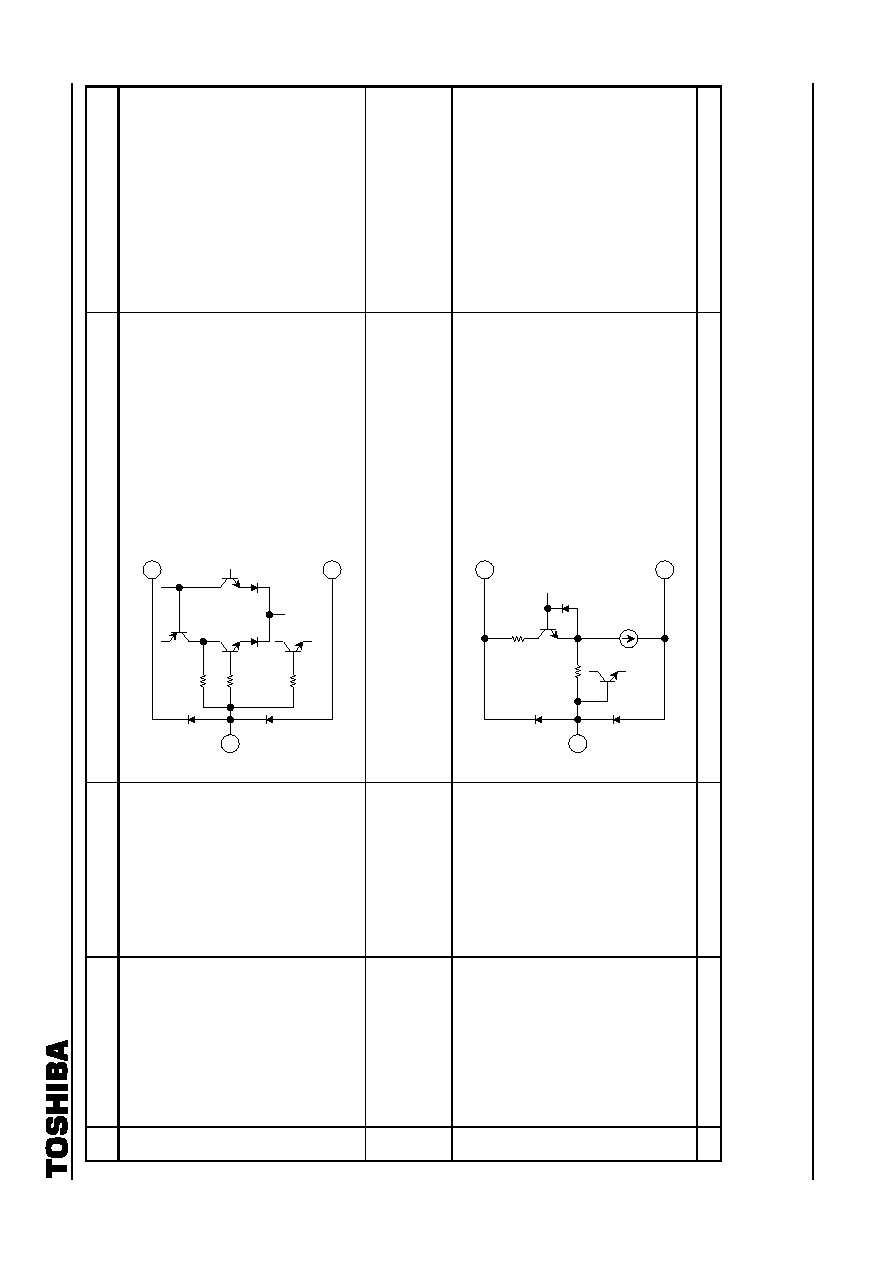

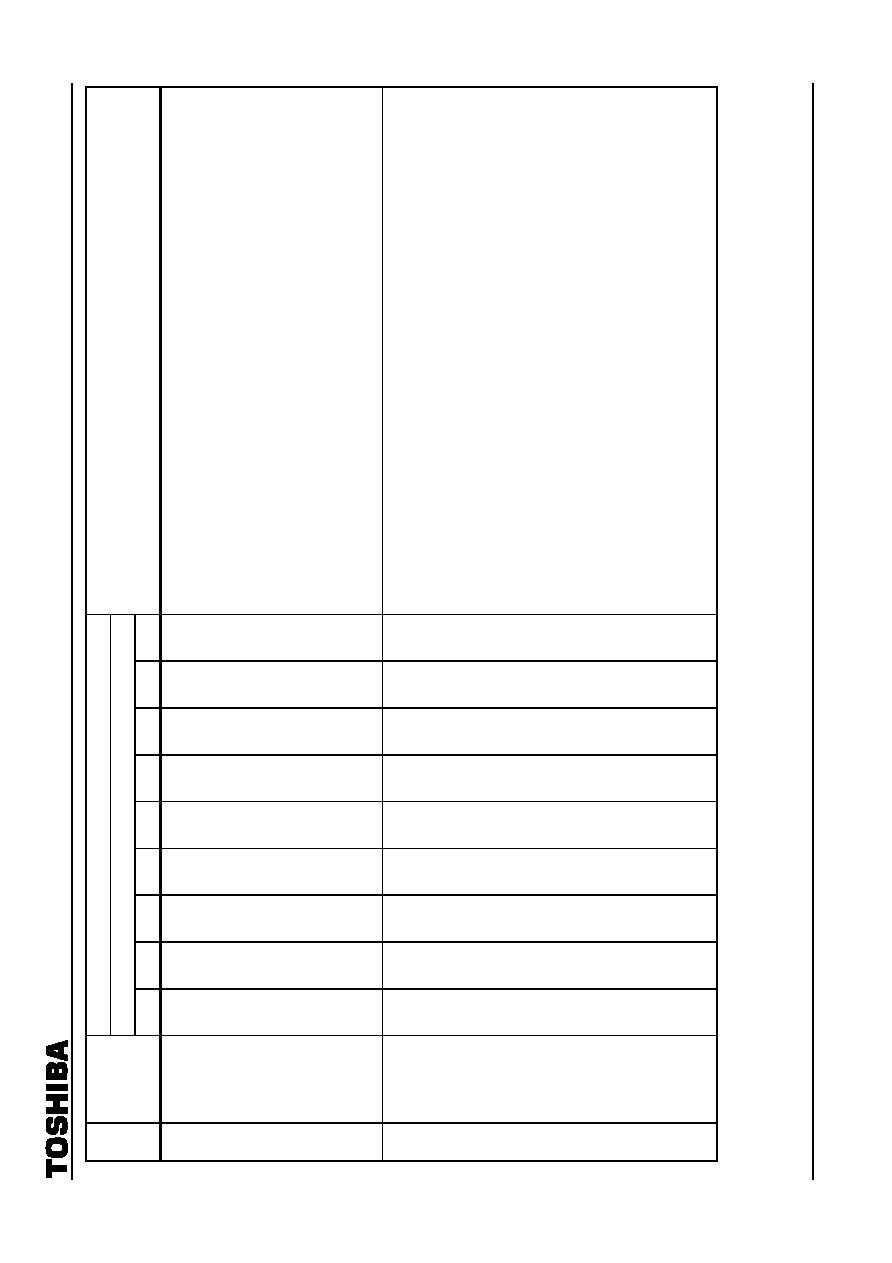

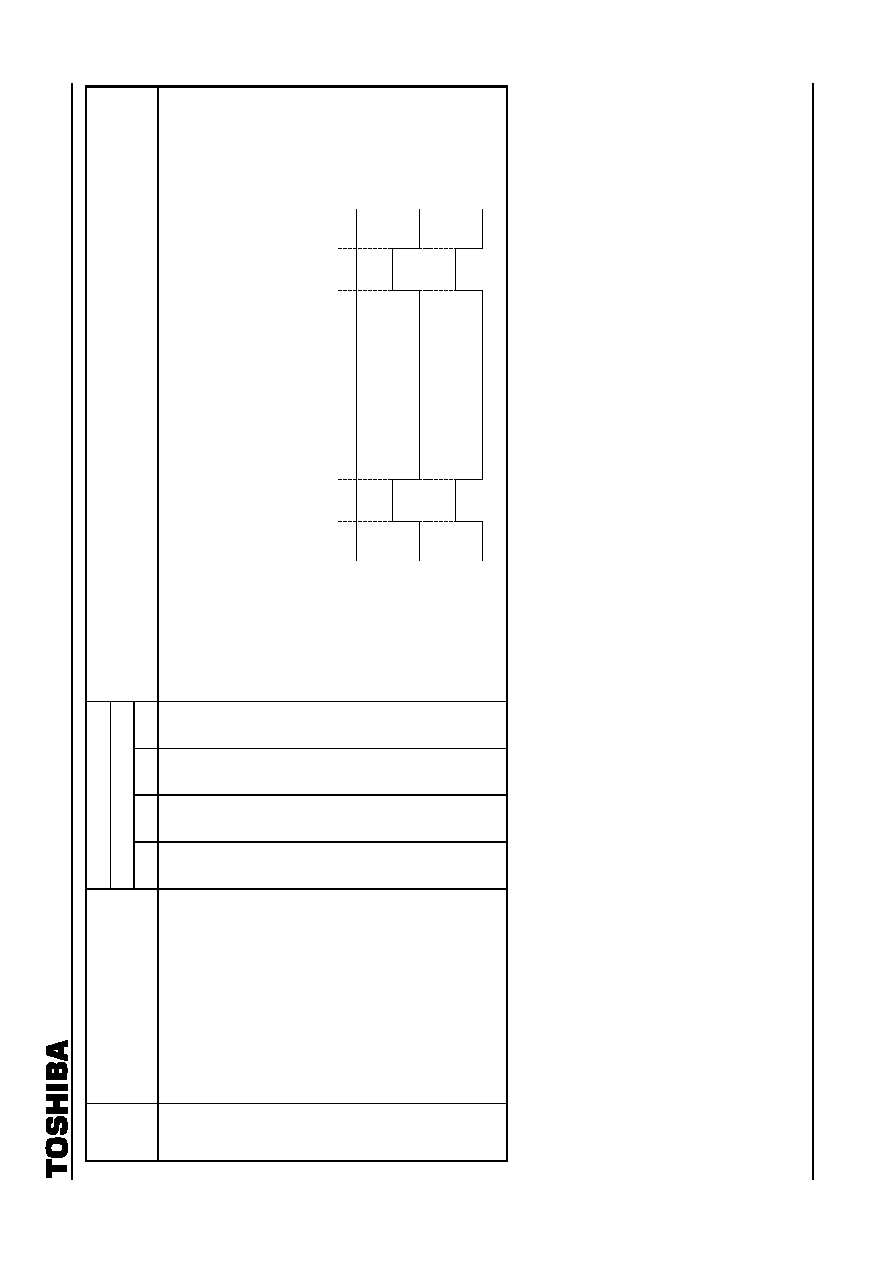

3 Y1

IN

Inputs Y1 signal via clamp

capacitor.

Recommended input

amplitude: 1 V

p-p

(including

sync) at 100% color bar.

1 V

p-p

(including sync) at 100% color bar

or

4 C

b1

/P

b1

IN

Inputs C

b1

/P

b1

signal via

clamp capacitor.

Recommended input

amplitude: 700 mV

p-p

at 100%

color bar.

700 mV

p-p

at 100% color bar for C

b1

/P

b1

55

3

6

1 k

1 k

5 k

55

4

6

1 k

1 k

5 k

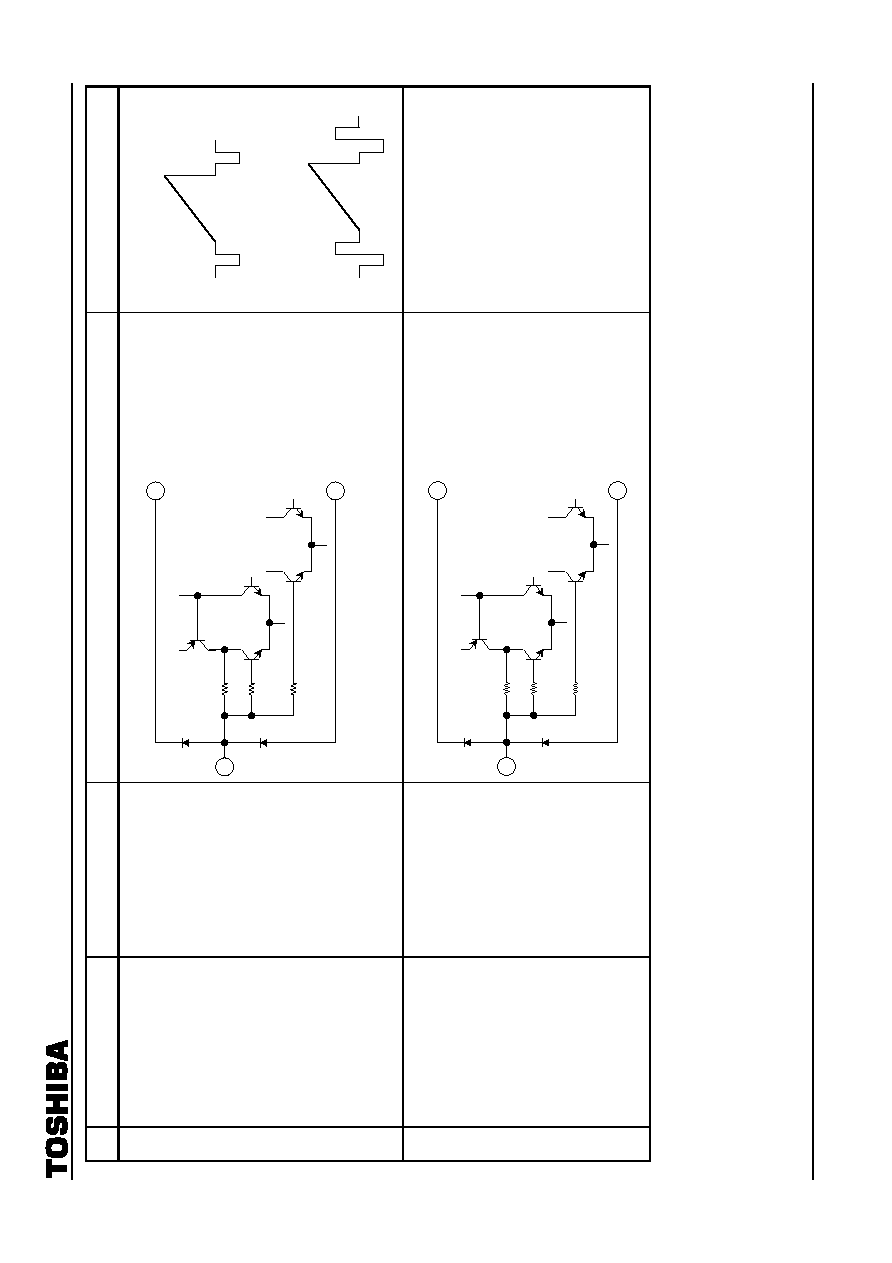

TA1316AN

2002-10-04

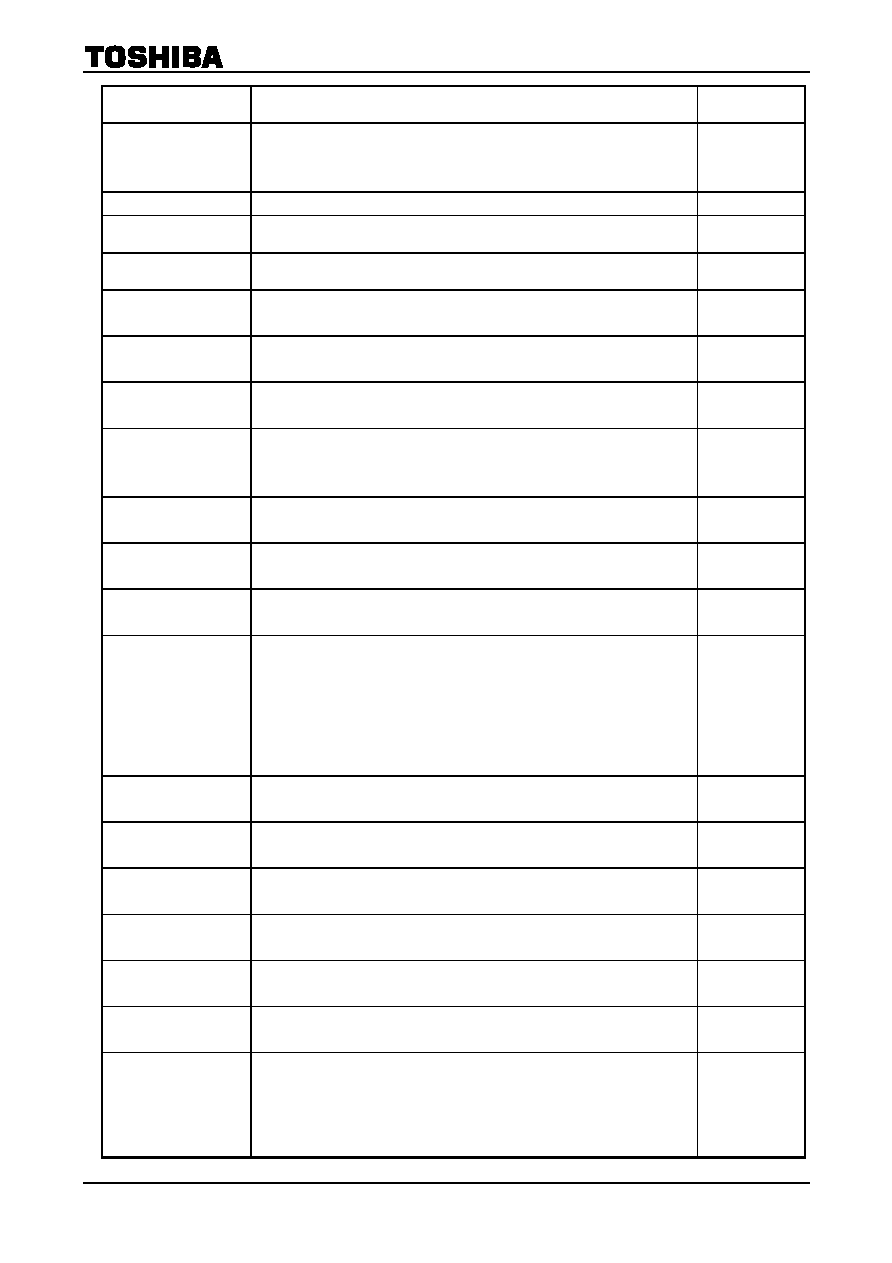

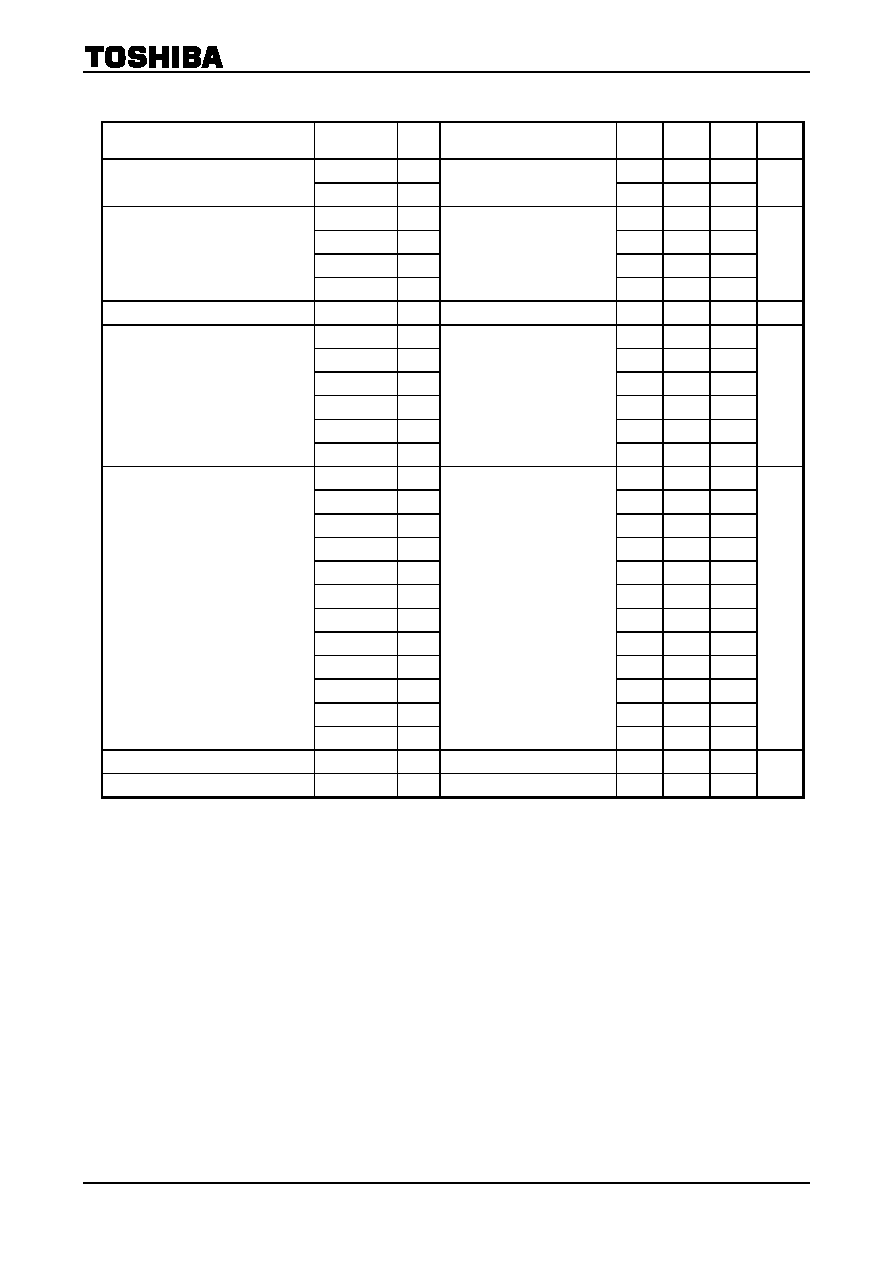

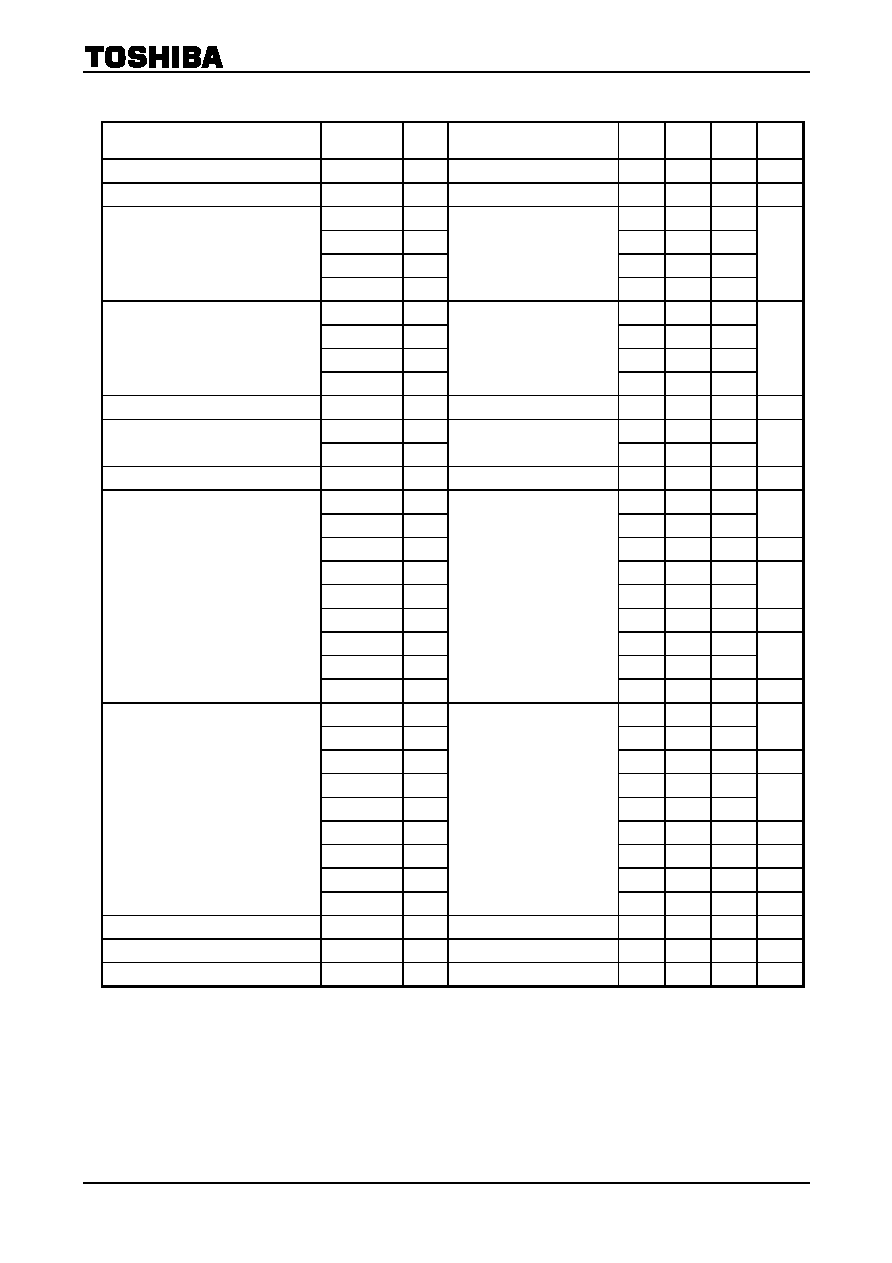

6

Pin

No.

Pin Name

Function

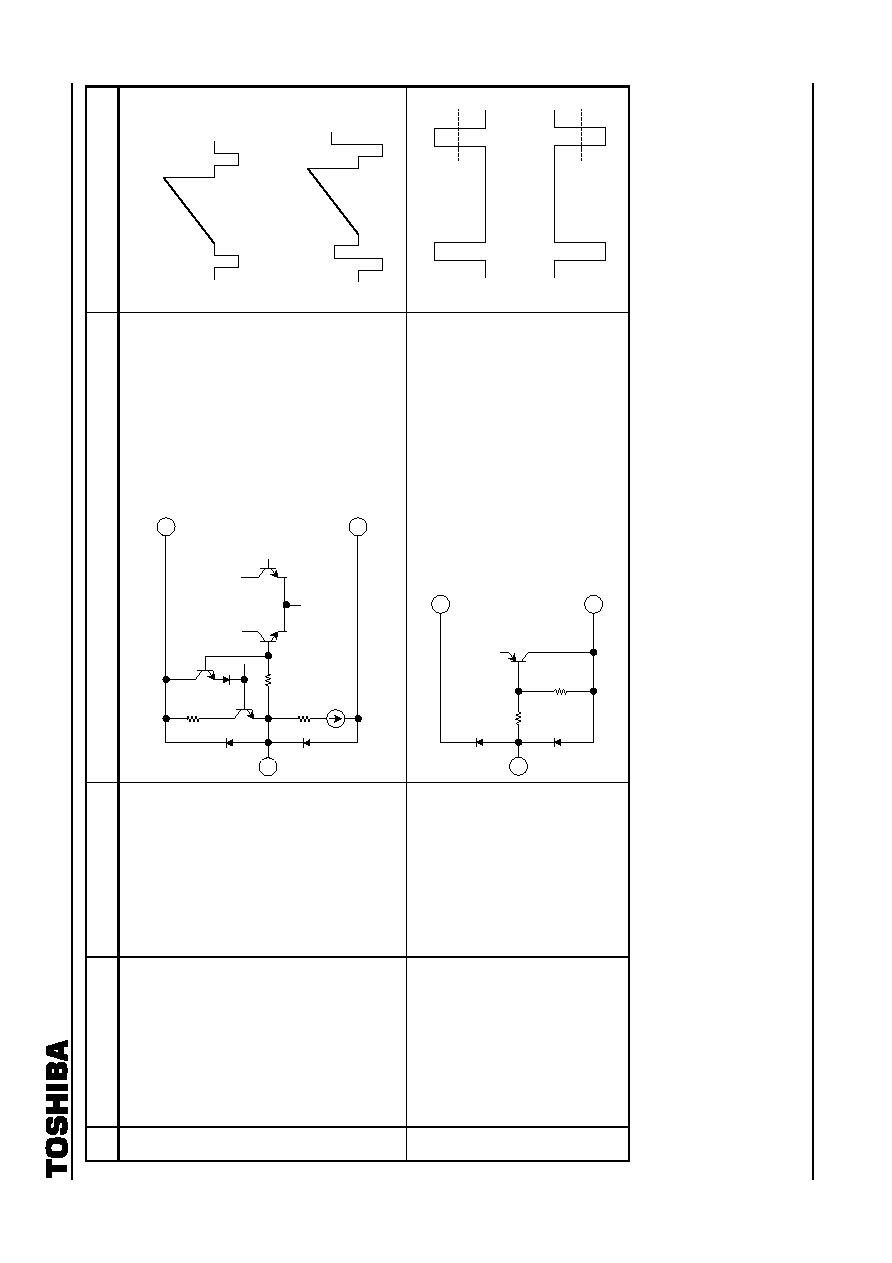

Interface Circuit

Input Signal/Output Signal

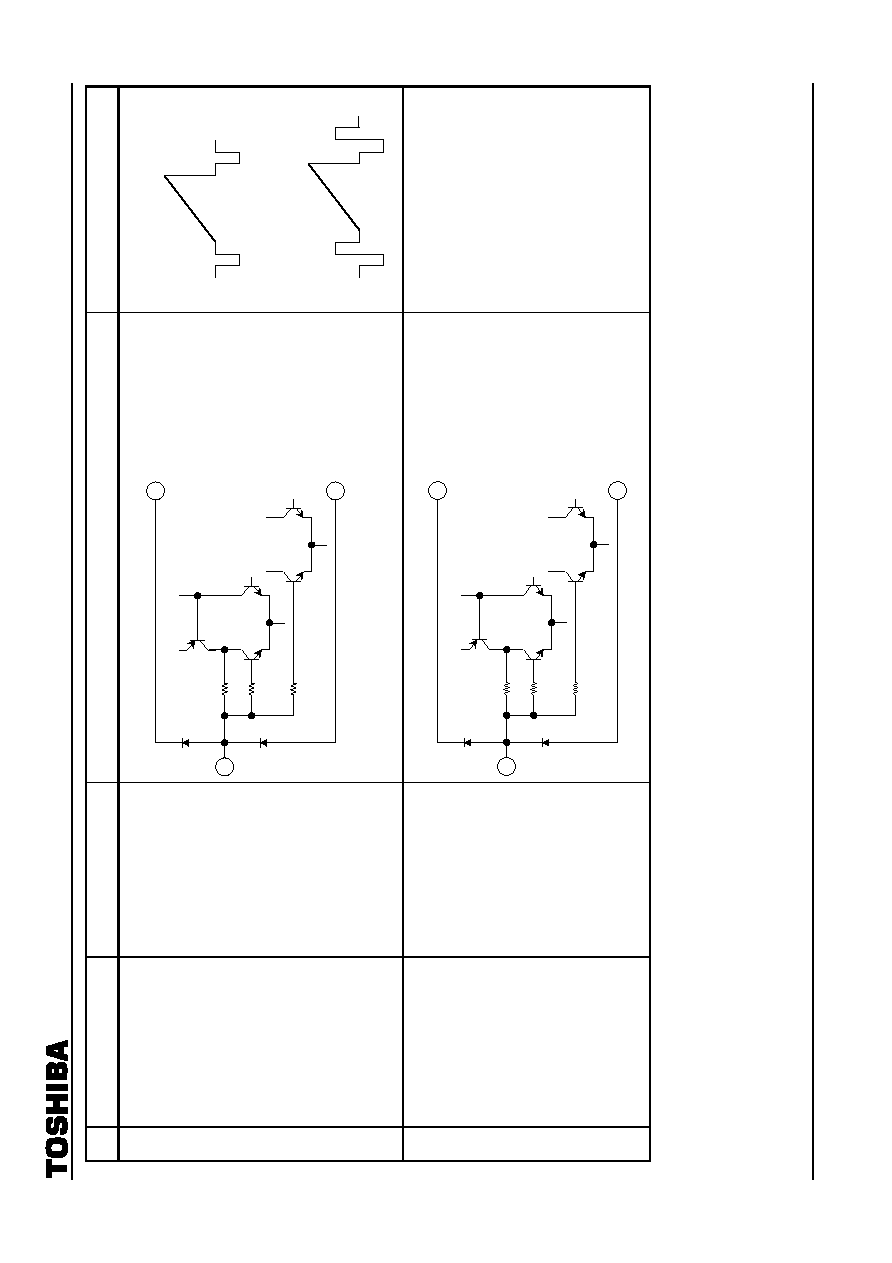

5 C

r1

/P

r1

IN

Inputs C

r1

/P

r1

signal via clamp

capacitor.

Recommended input

amplitude: 700 mV

p-p

at 100%

color bar.

100 mV

p-p

at 100% color bar for C

r1

/P

r1

6

Y/C GND

GND pin for Y/C block.

7 MATRIX

SW

Matrix switching pin for YCbCr

or YPbPr input.

Switches matrix according to

voltage value input to this pin

when BUS control "YUV

INPUT MODE"

=

00 or 01.

Then, control by pin has

priority over control by BUS

(see table 4).

When pin is not used, connect

0.01

µ

F capacitor between pin

and GND.

When YUV INPUT MODE

=

00 or 01,

0~0.6 V: YCbCr

Internal YUV

0.9~5 V: YPbPr

Internal YUV

Open: BUS control

55

5

6

1 k

1 k

5 k

55

7

6

1 k

112 k

25

µ

A

BUS

TA1316AN

2002-10-04

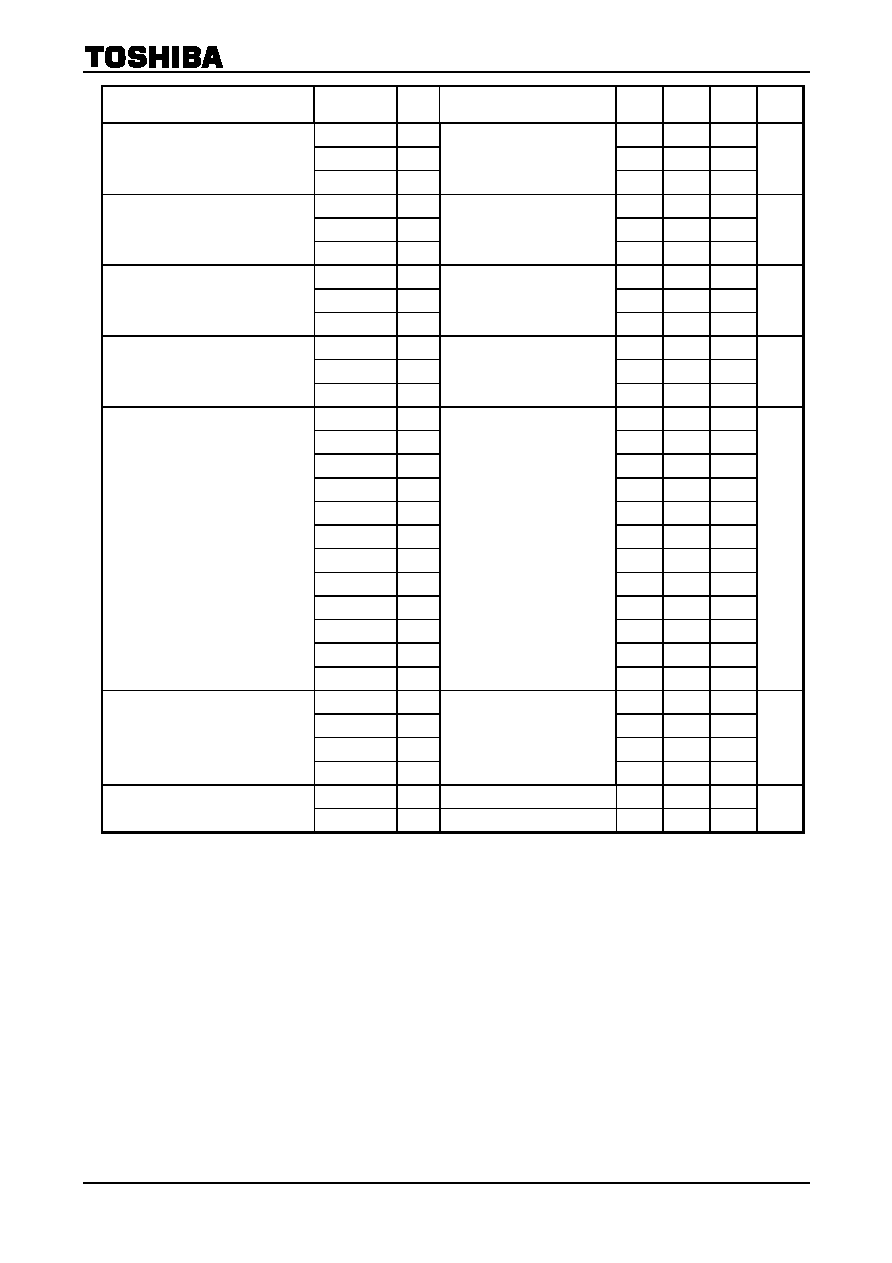

7

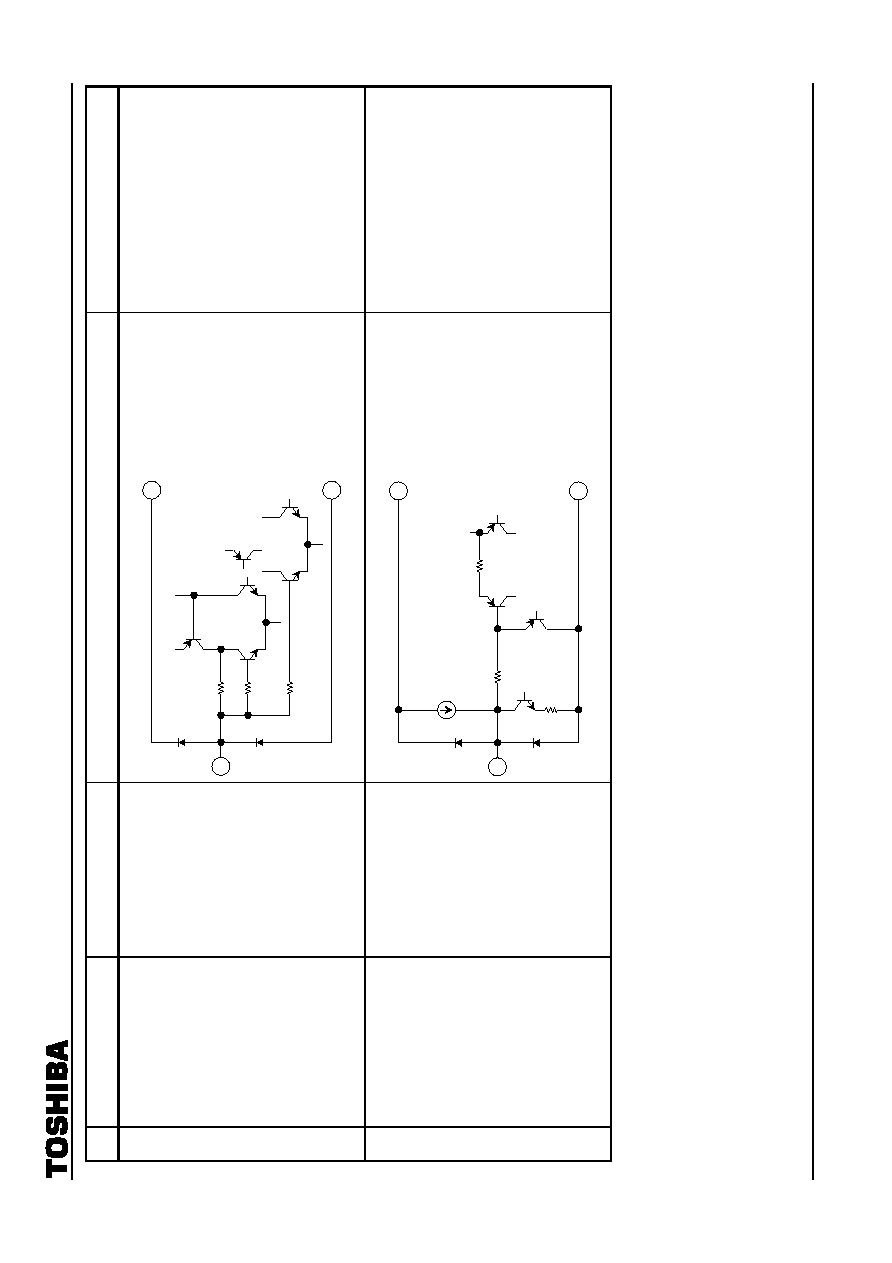

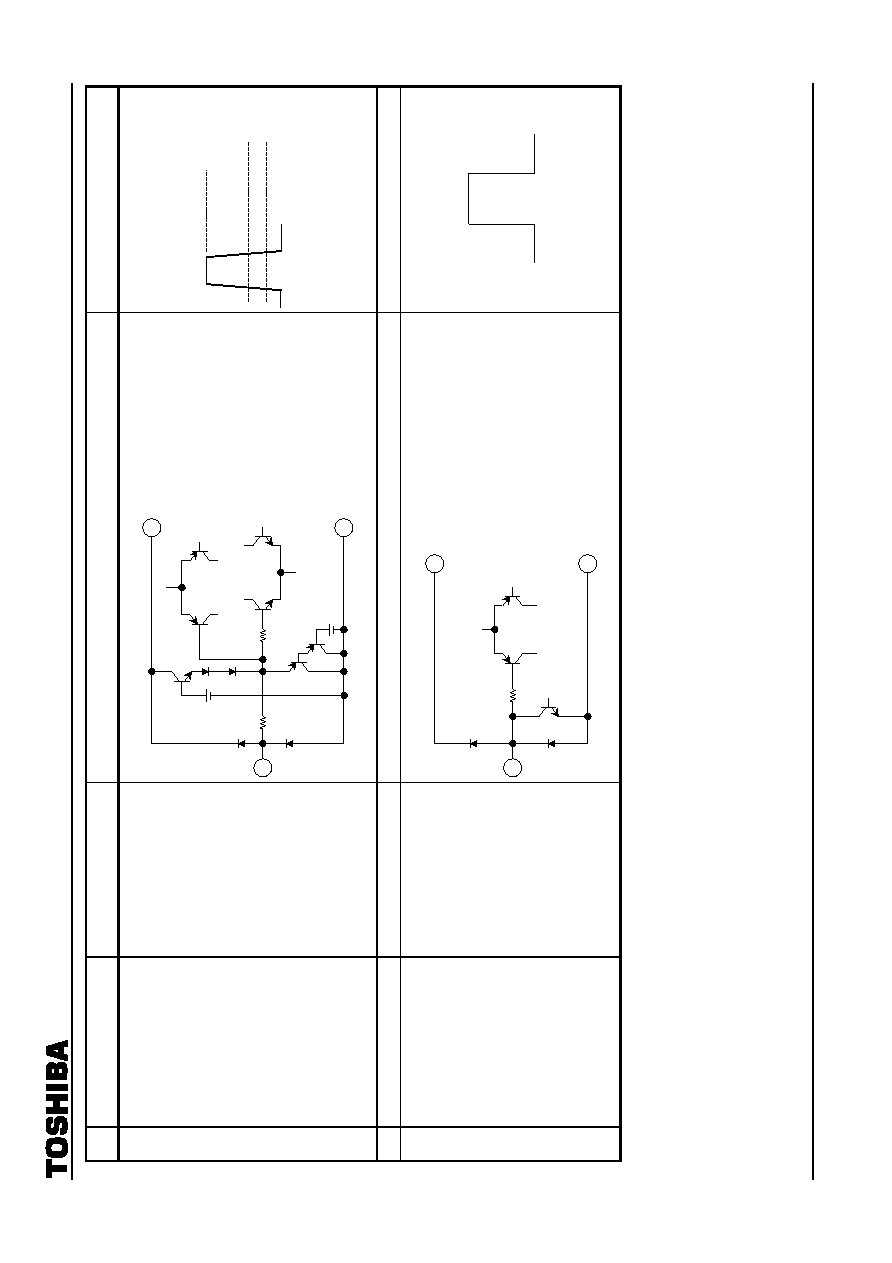

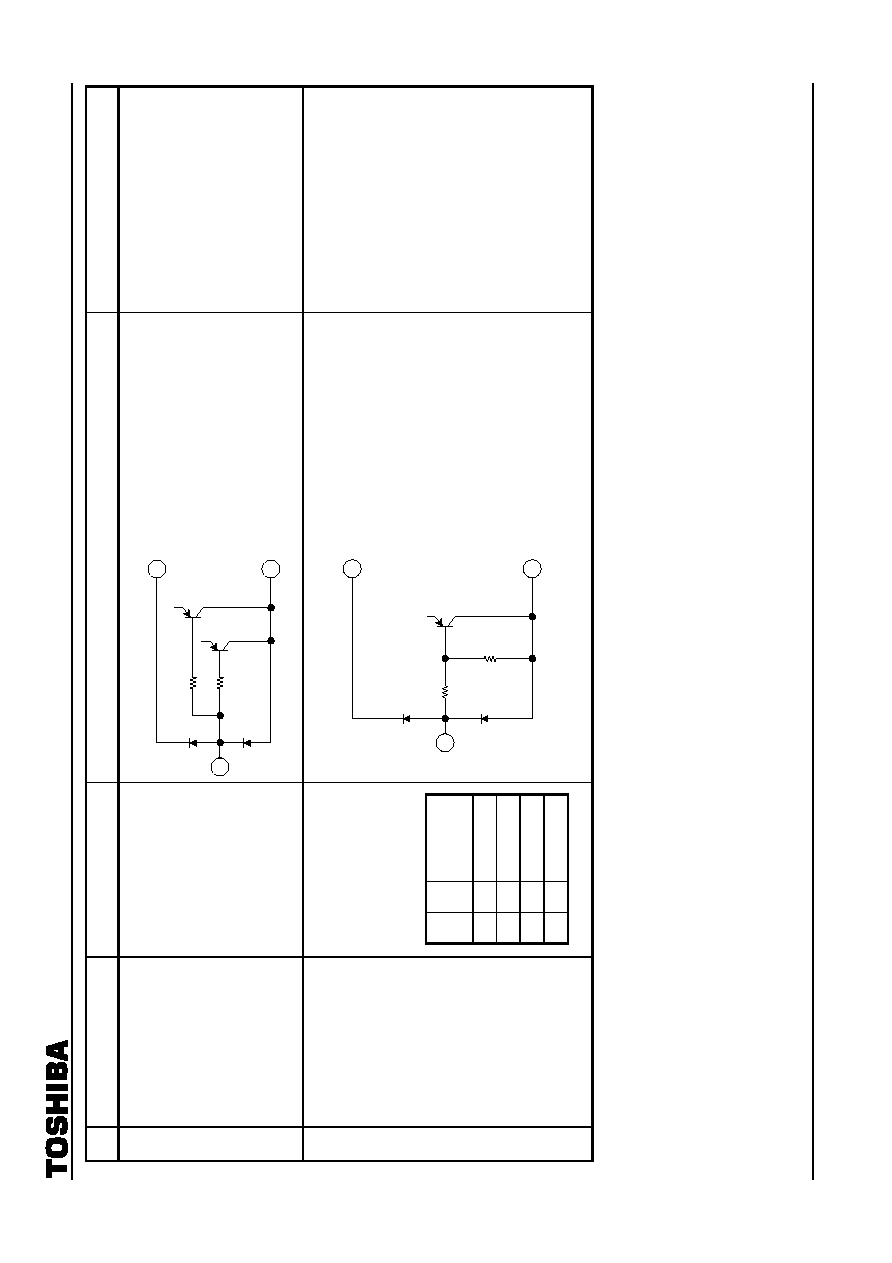

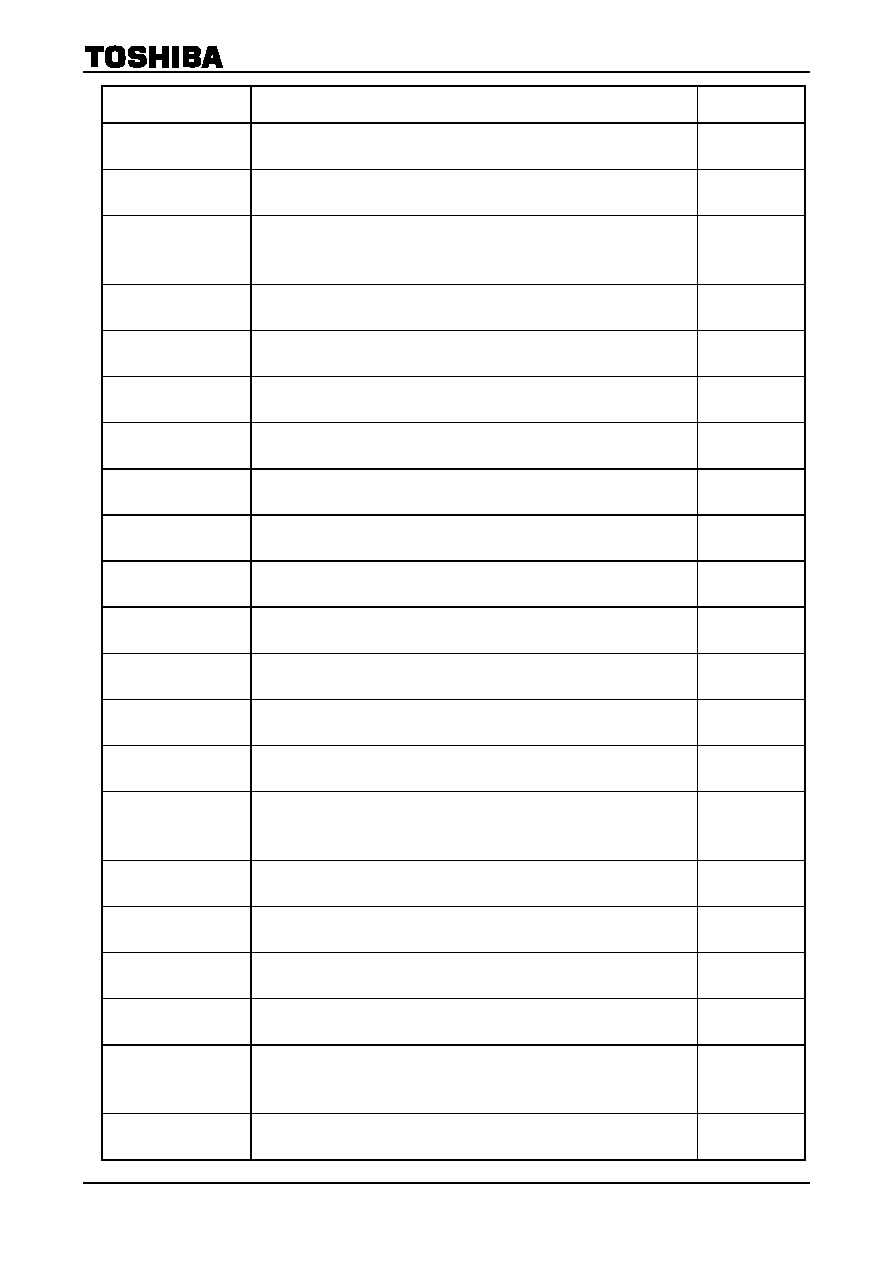

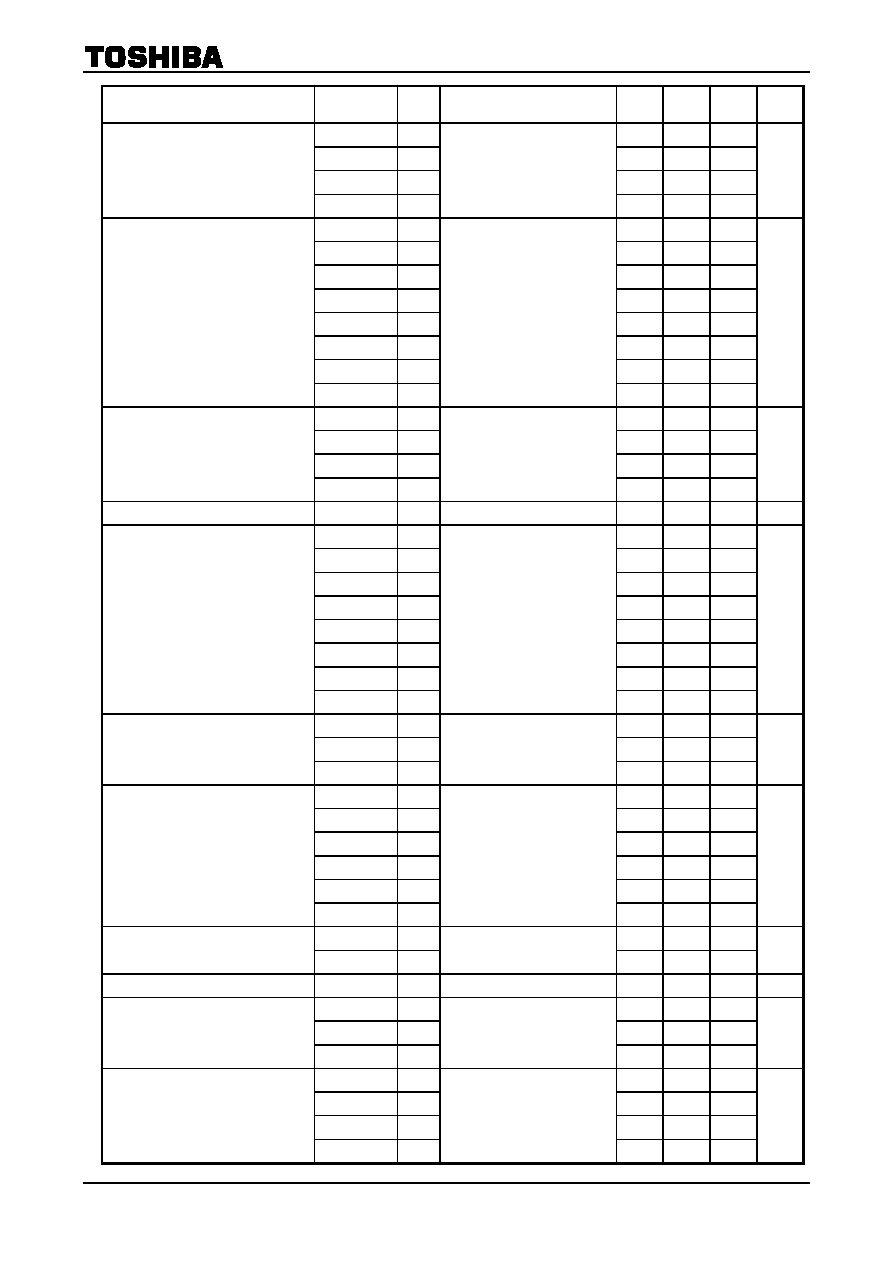

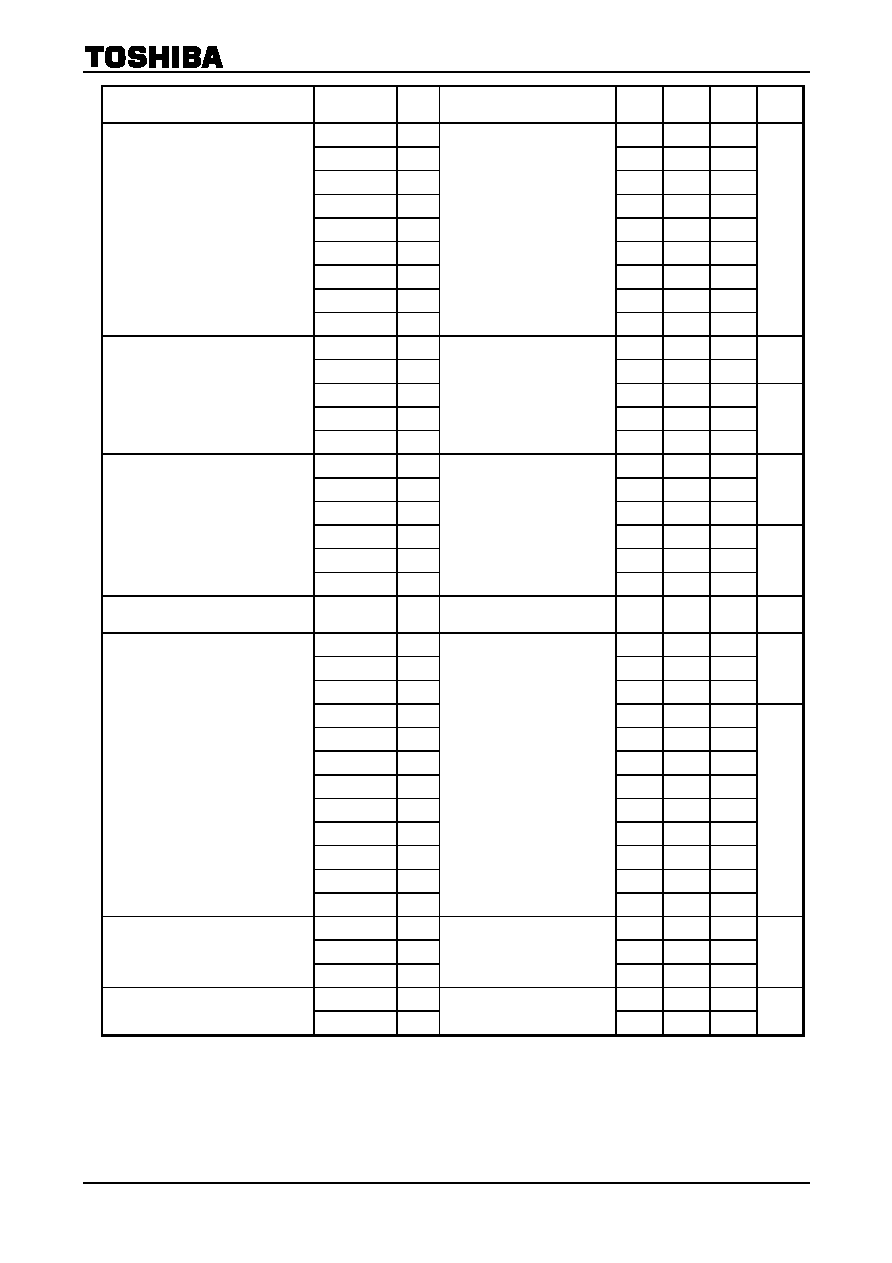

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

8 Y2

IN

Inputs Y2 signal via clamp

capacitor.

Recommended input

amplitude: 1 V

p-p

(including

sync) at 100% color bar.

1 V

p-p

(including sync) at 100% color bar

or

9 Cb2/Pb2

IN

Inputs C

b2

/P

b2

signal via

clamp capacitor.

Recommended input

amplitude: 700 mV

p-p

at 100%

color bar.

700 mV

p-p

at 100% color bar for C

b2

/P

b2

55

8

6

1 k

1 k

5 k

55

9

6

1 k

1 k

5 k

TA1316AN

2002-10-04

8

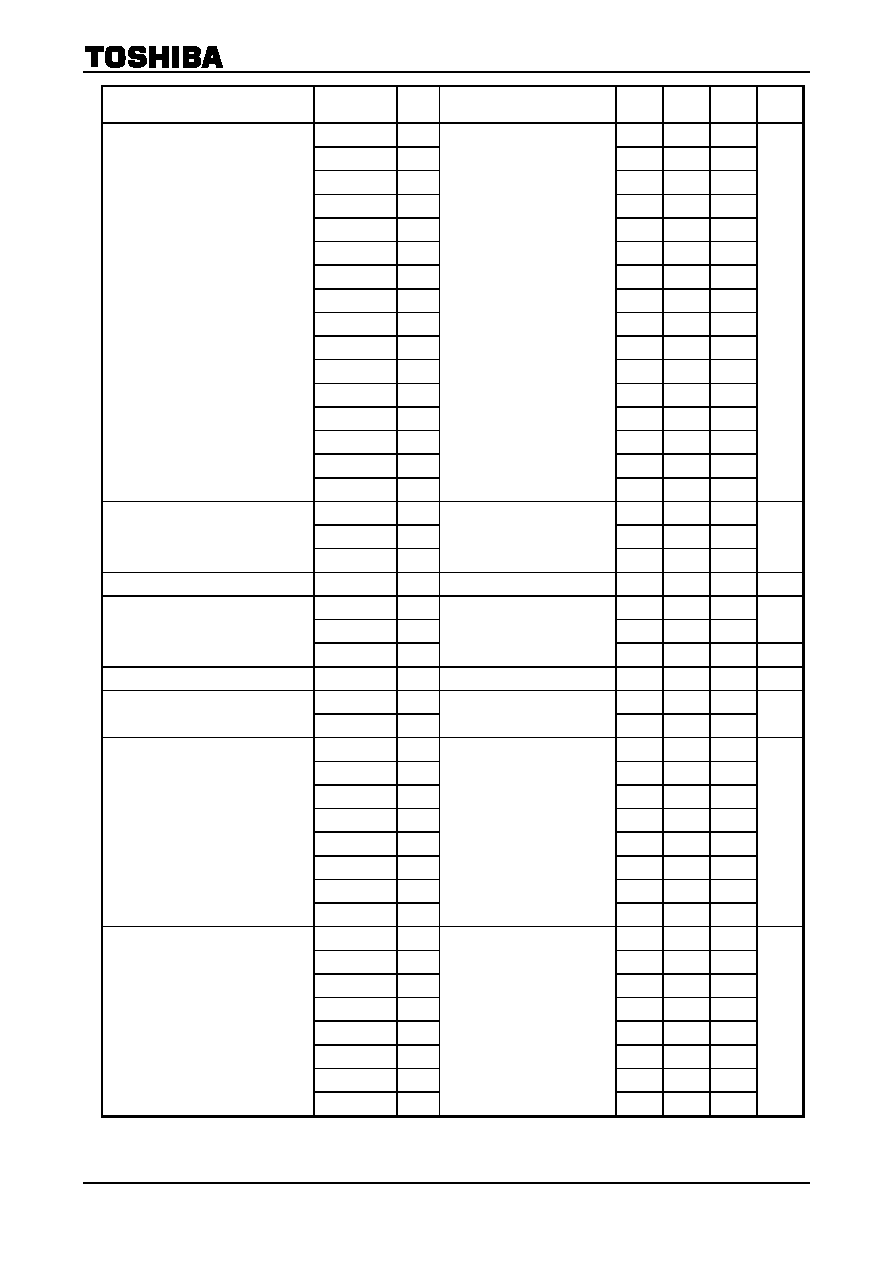

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

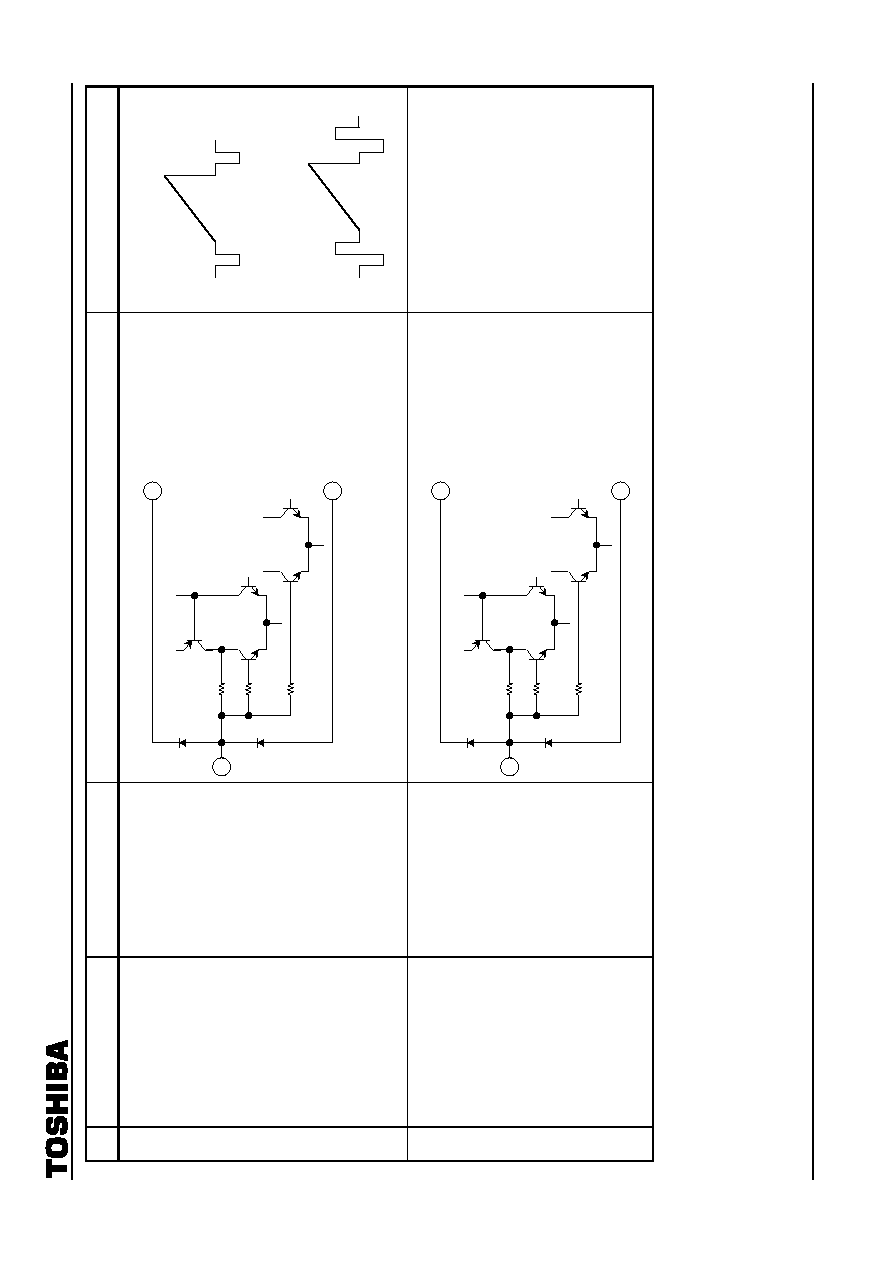

10 C

r2

/P

r2

IN

Inputs C

r2

/P

r2

signal via clamp

capacitor.

Recommended input

amplitude: 700 mV

p-p

at 100%

color bar.

700 mV

p-p

at 100% color bar for C

r2

/P

r2

11 COLOR

LIMITER

Connect filter for detecting

color limit.

DC

55

10

6

1 k

1 k

5 k

55

11

6

5 k

7

µ

A

TA1316AN

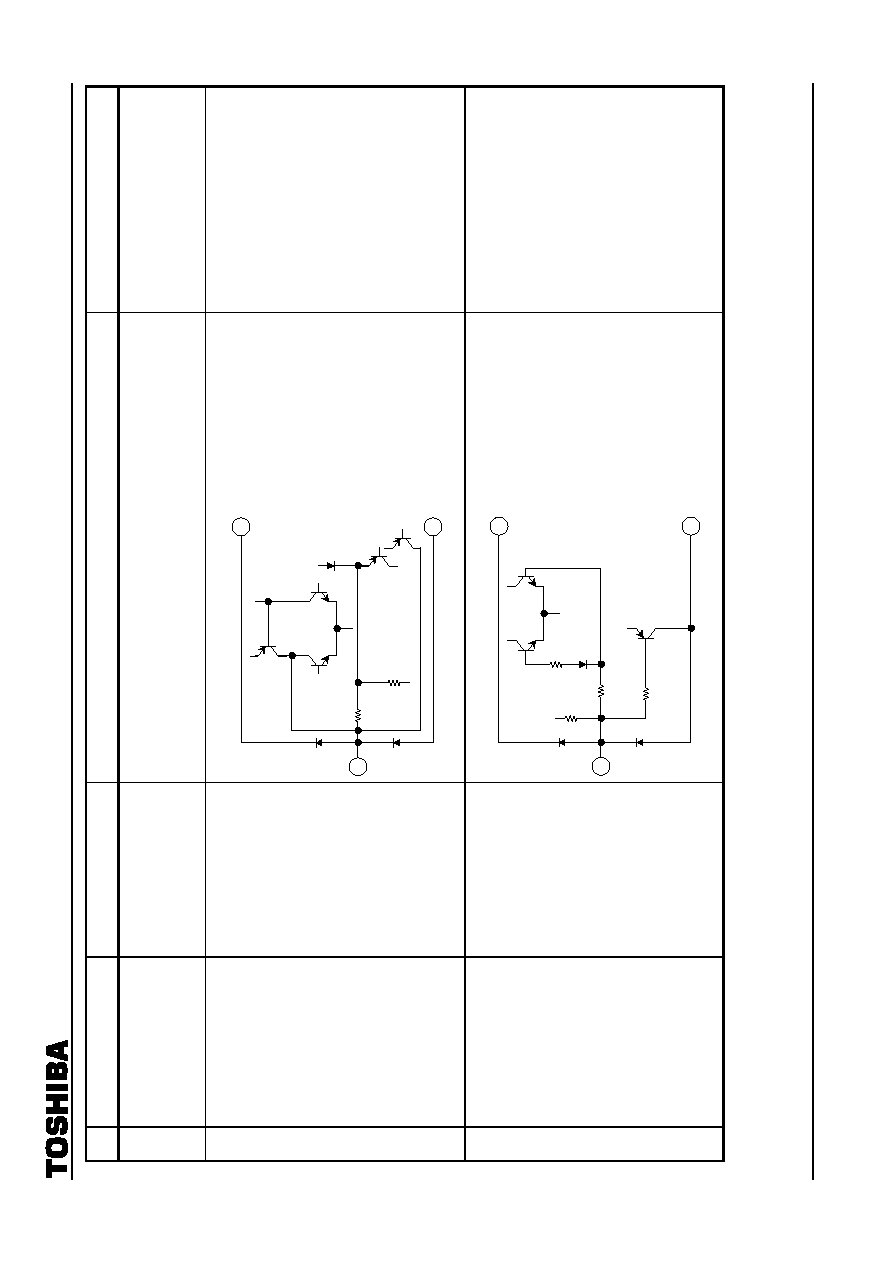

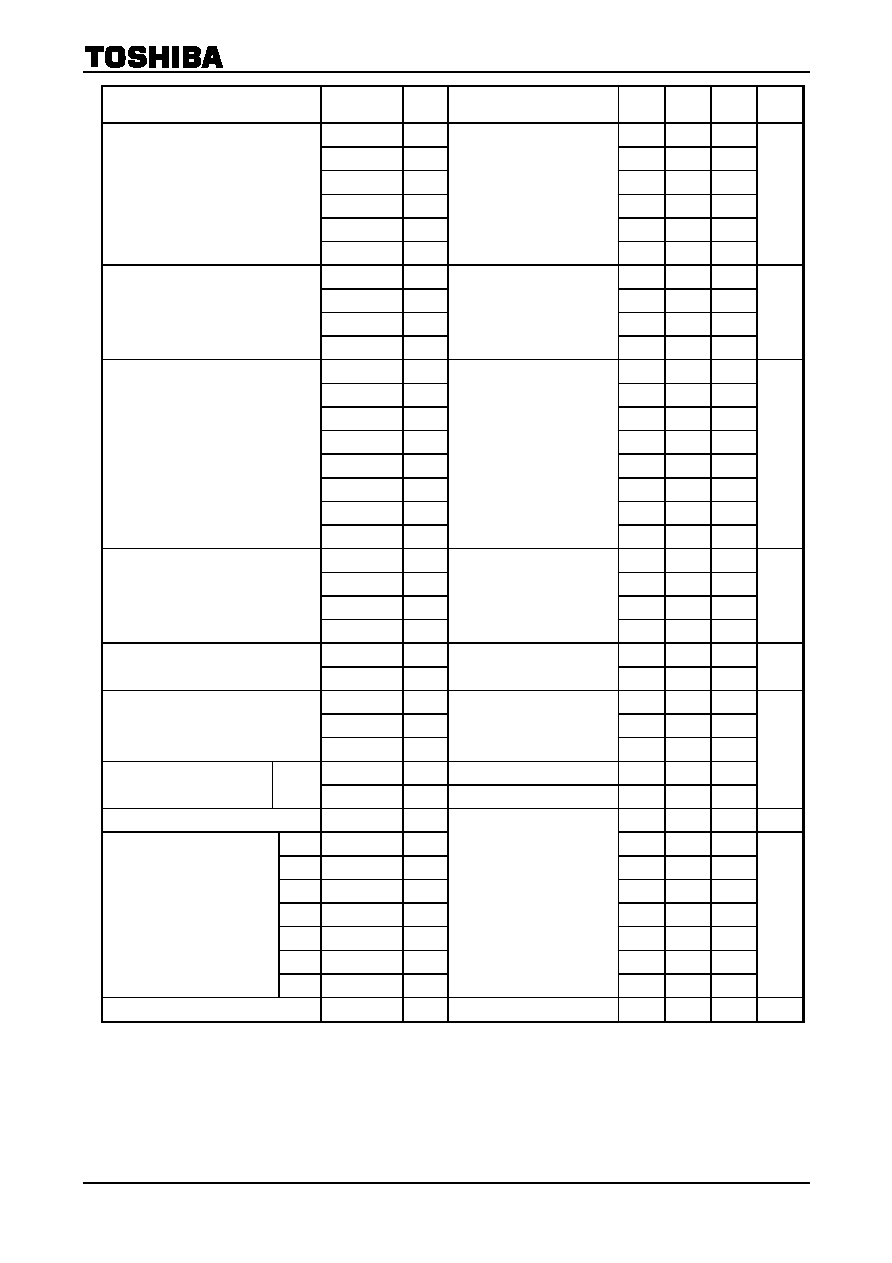

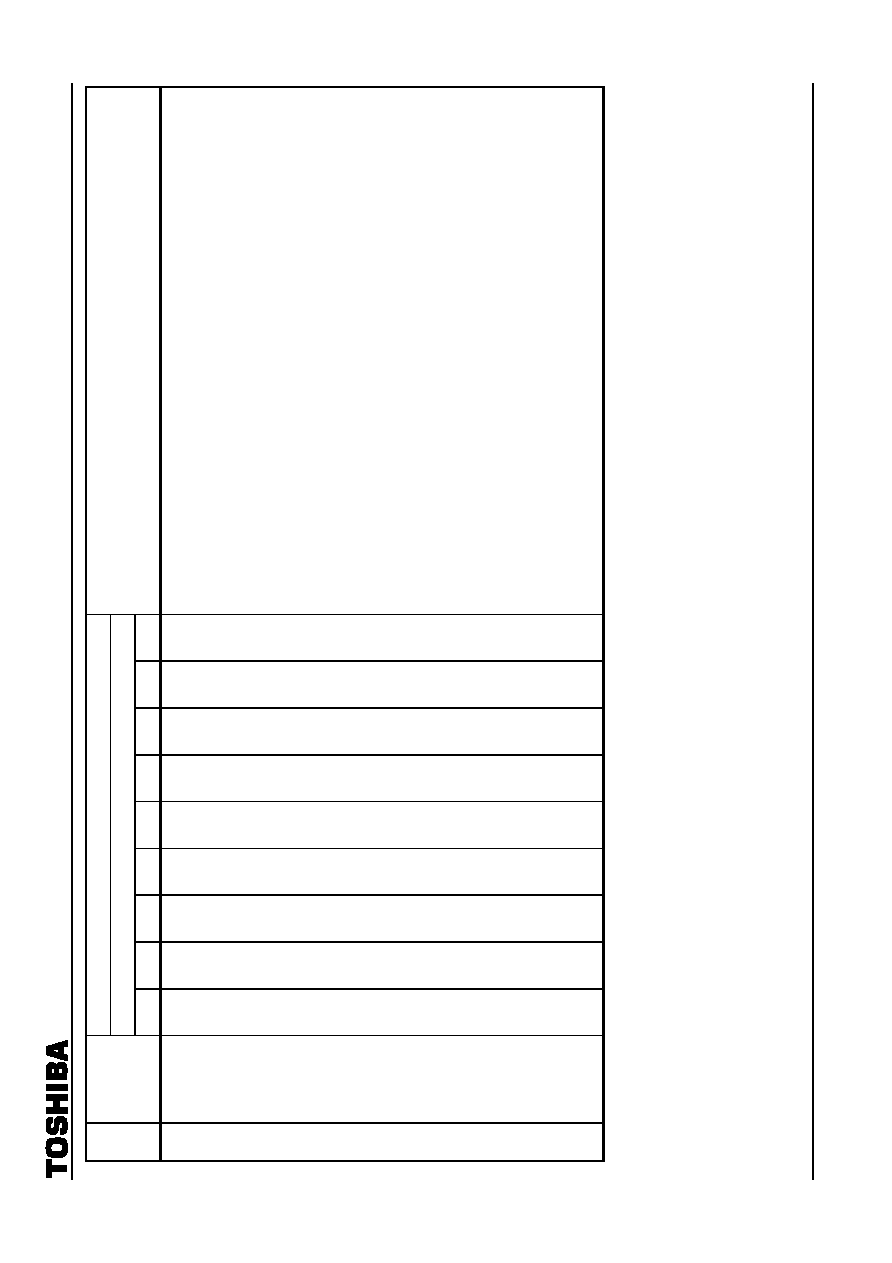

2002-10-04

9

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

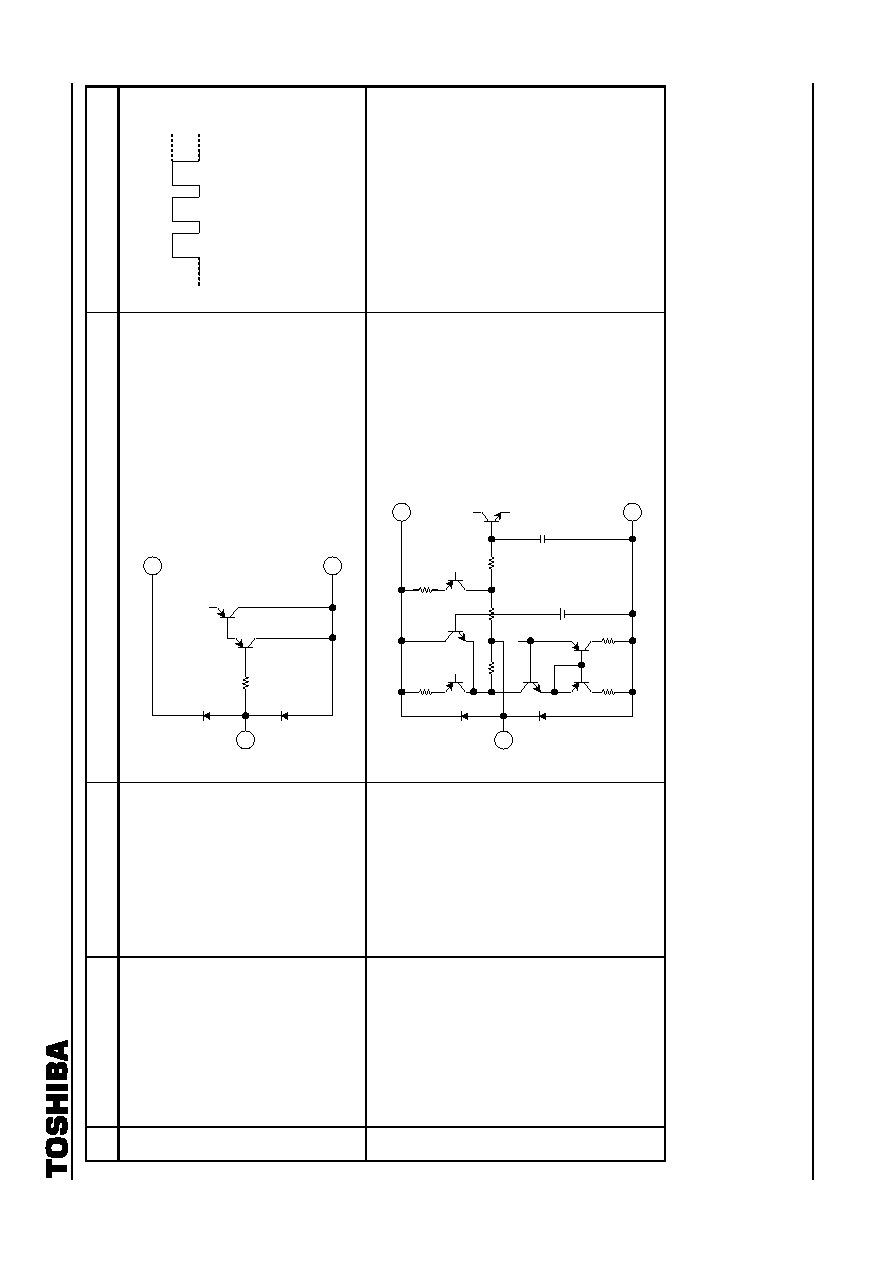

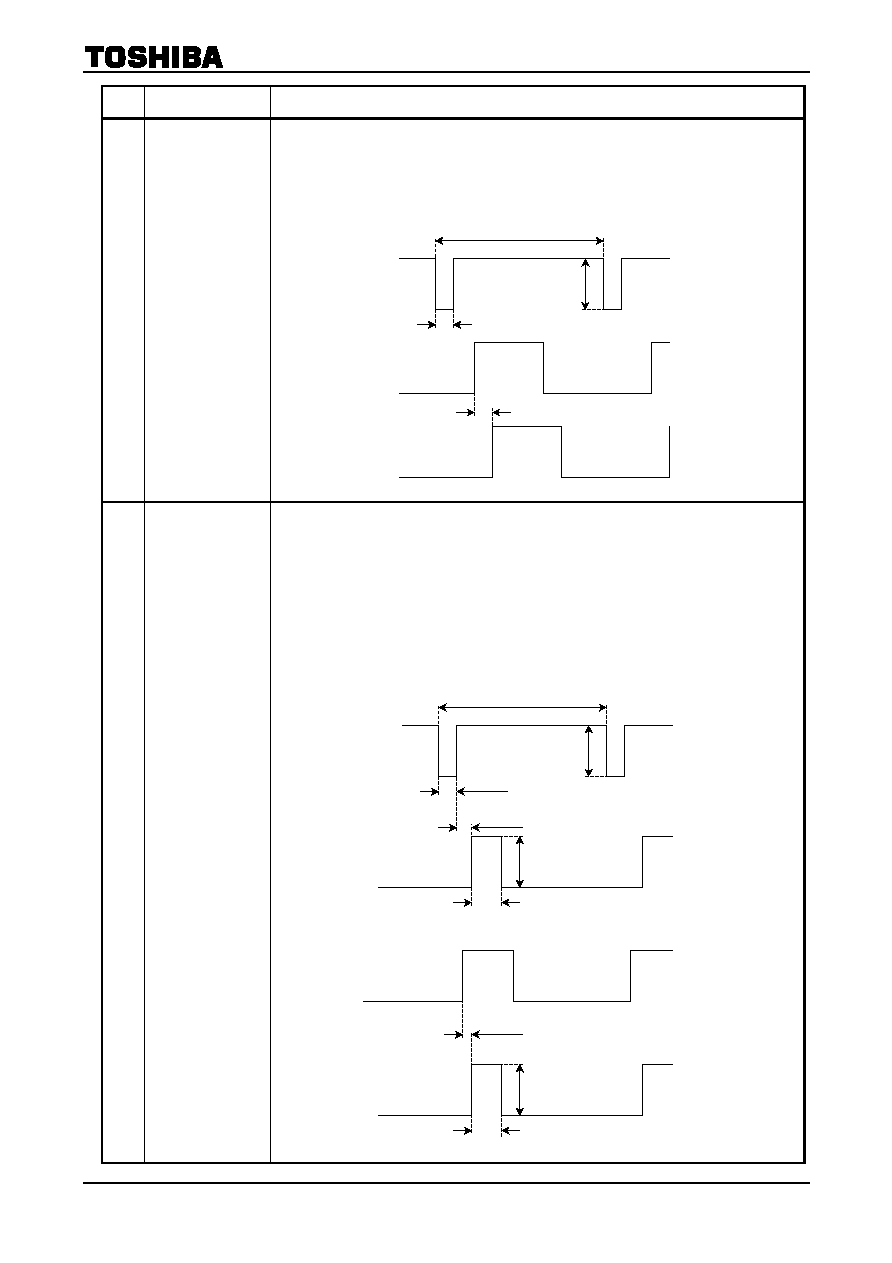

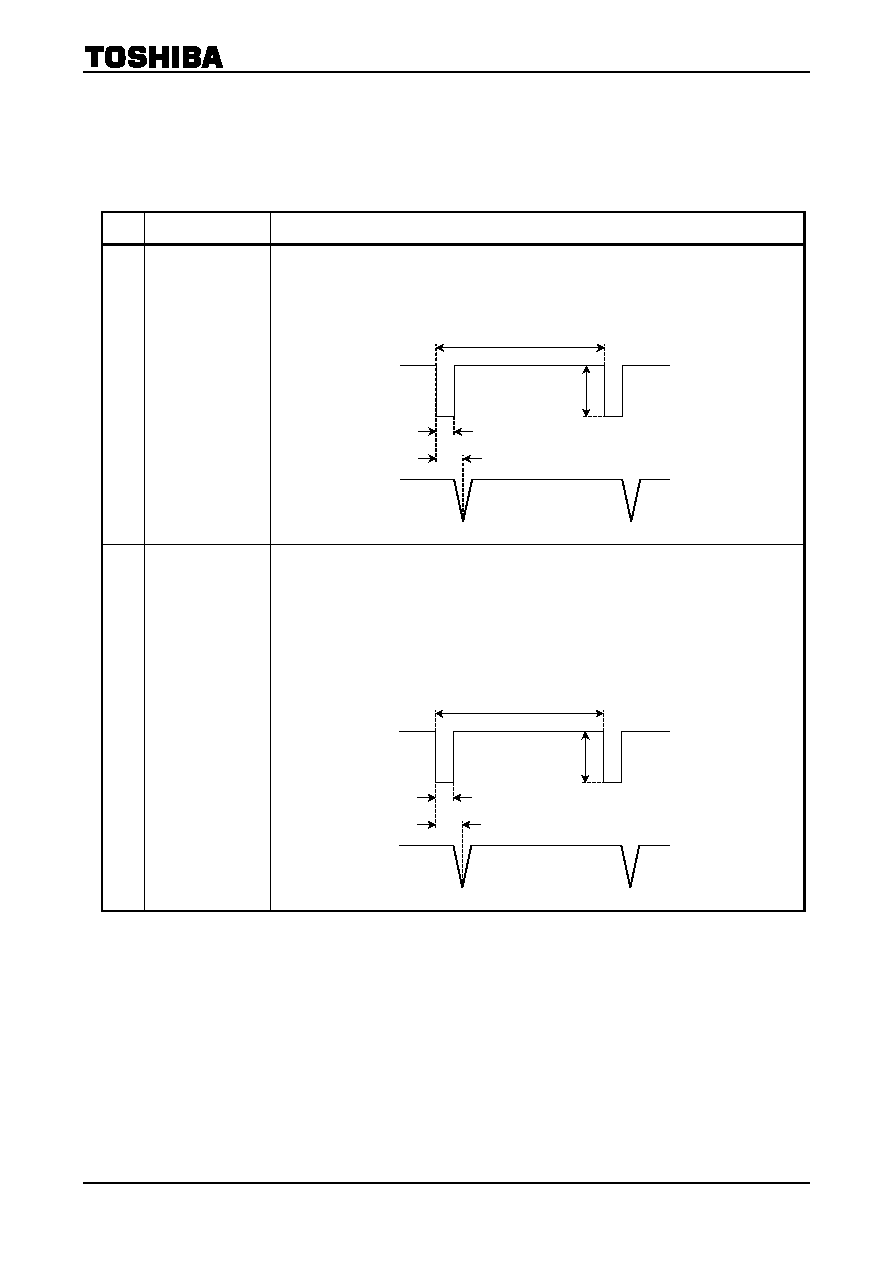

12 VD2

IN

Inputs vertical sync signal

VD2. Signal input can have

both positive and negative

polarity.

or

13 HD2

IN

Inputs horizontal sync signal

HD2. Signal input can have

both positive and negative

polarity.

or

19

12

25

1 k

45 k

19

13

25

1 k

50 k

Threshold:

0.75 V

Threshold:

0.75 V

Threshold:

0.75 V

Threshold:

0.75 V

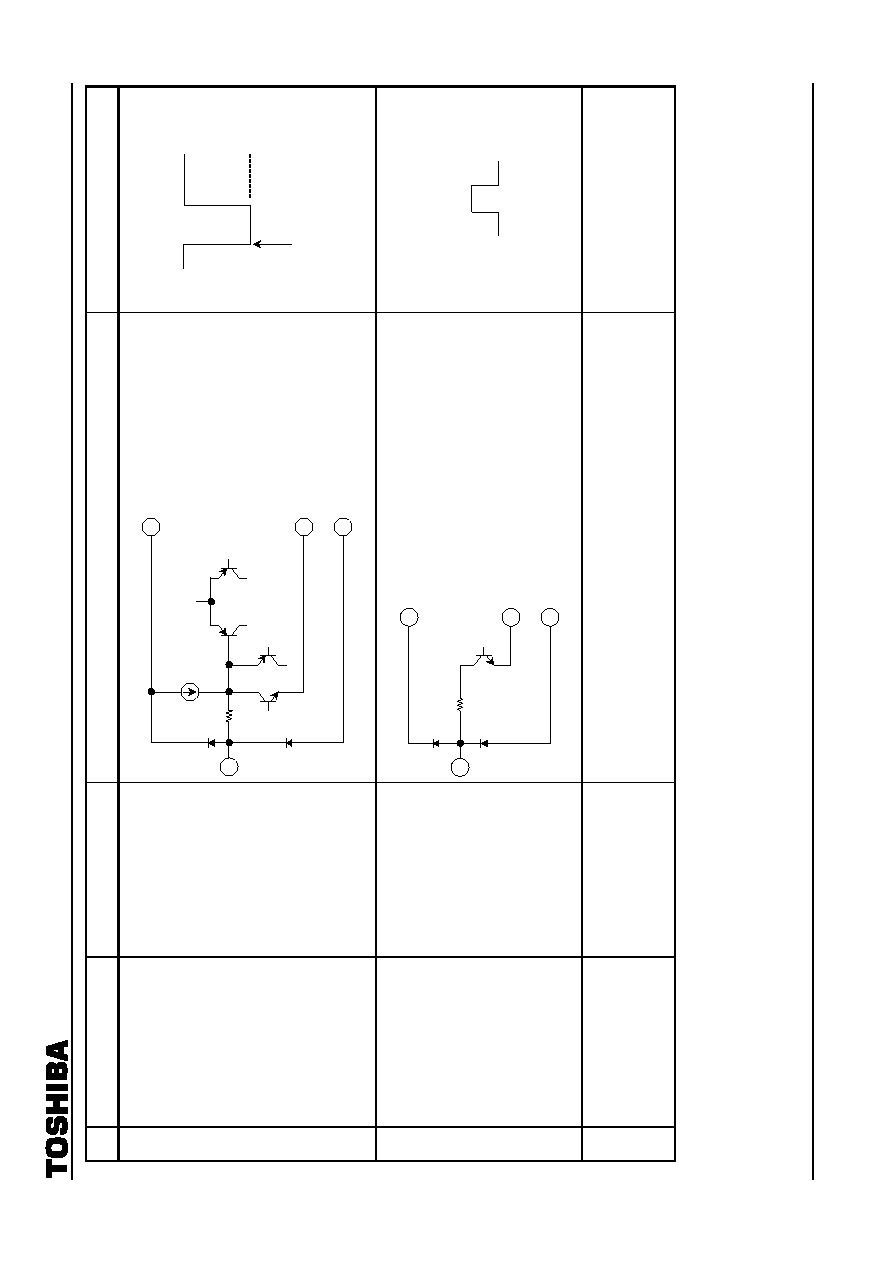

TA1316AN

2002-10-04

10

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

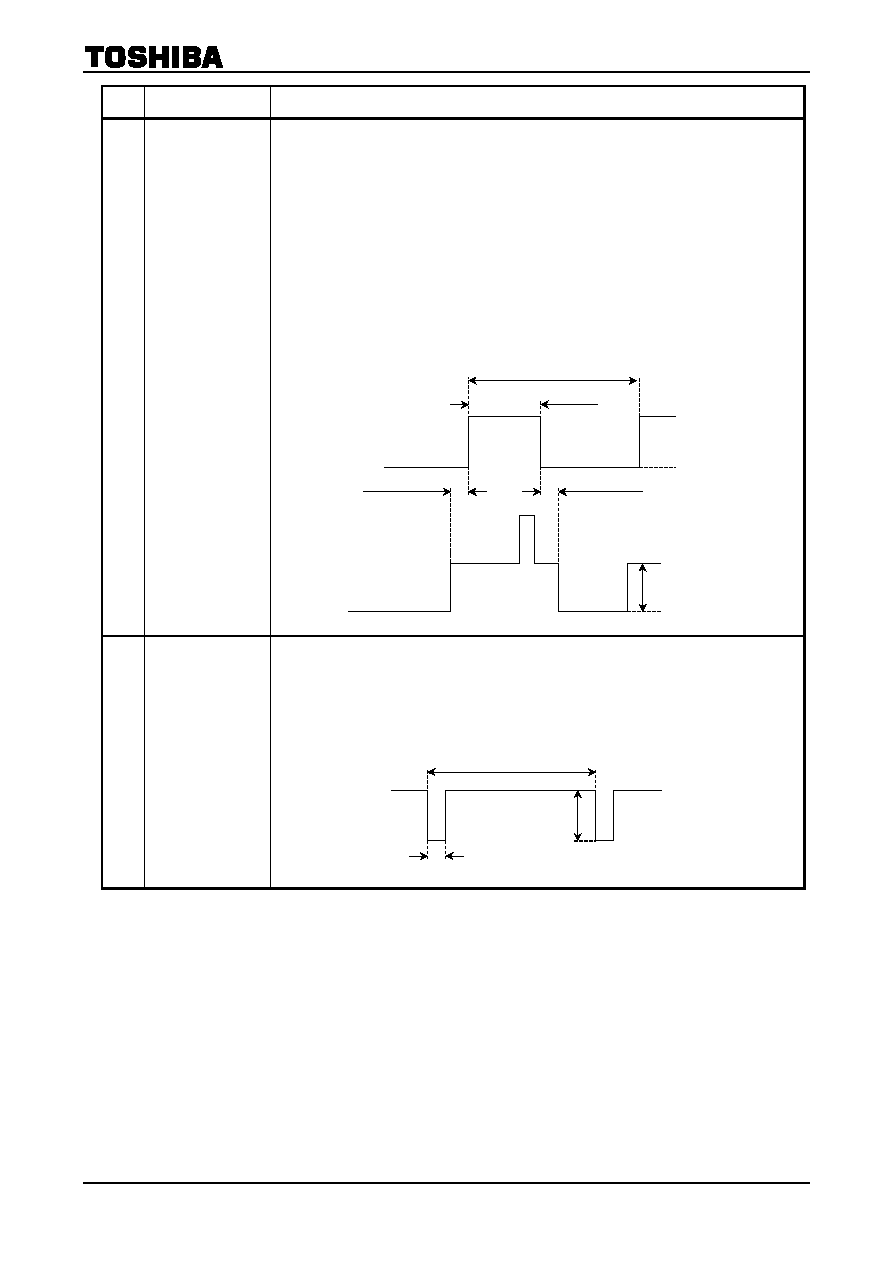

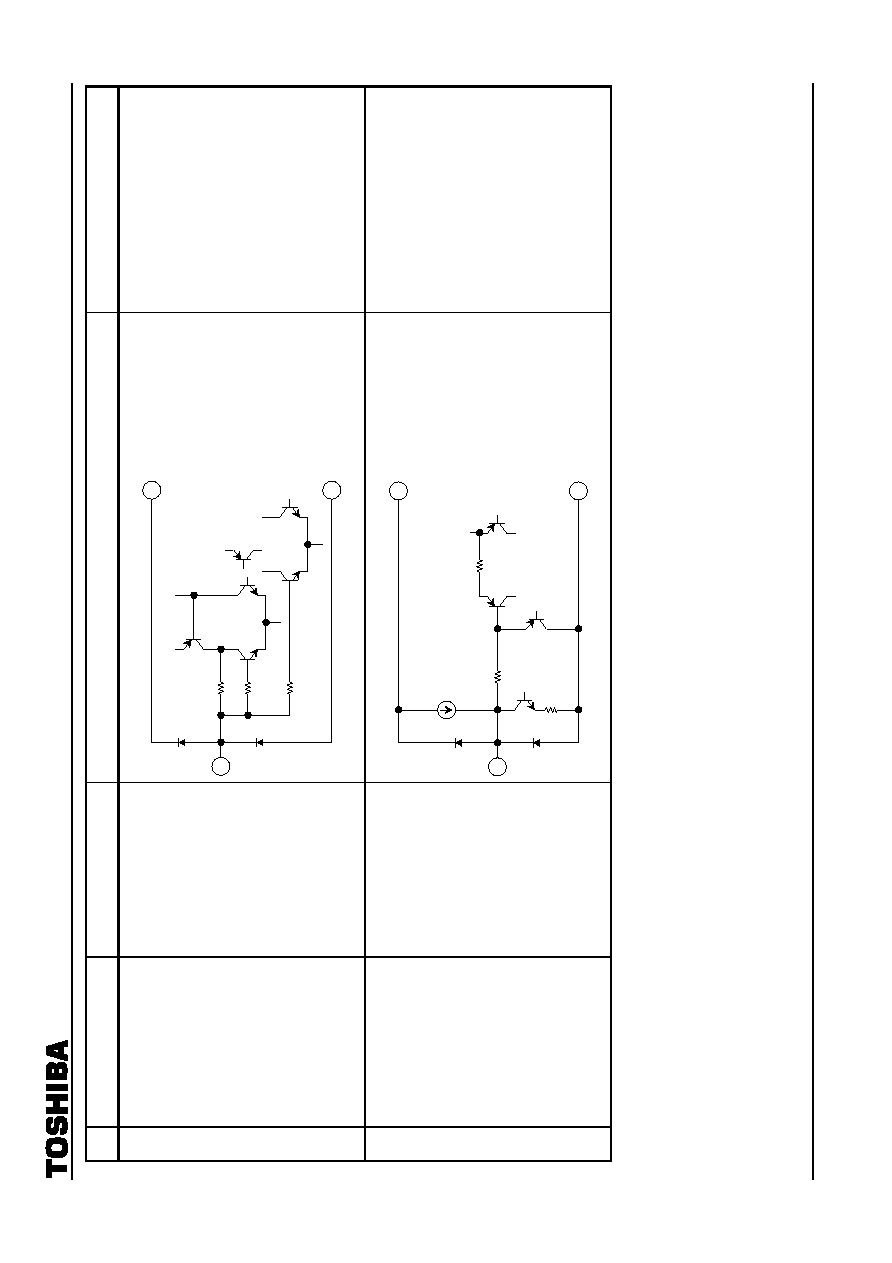

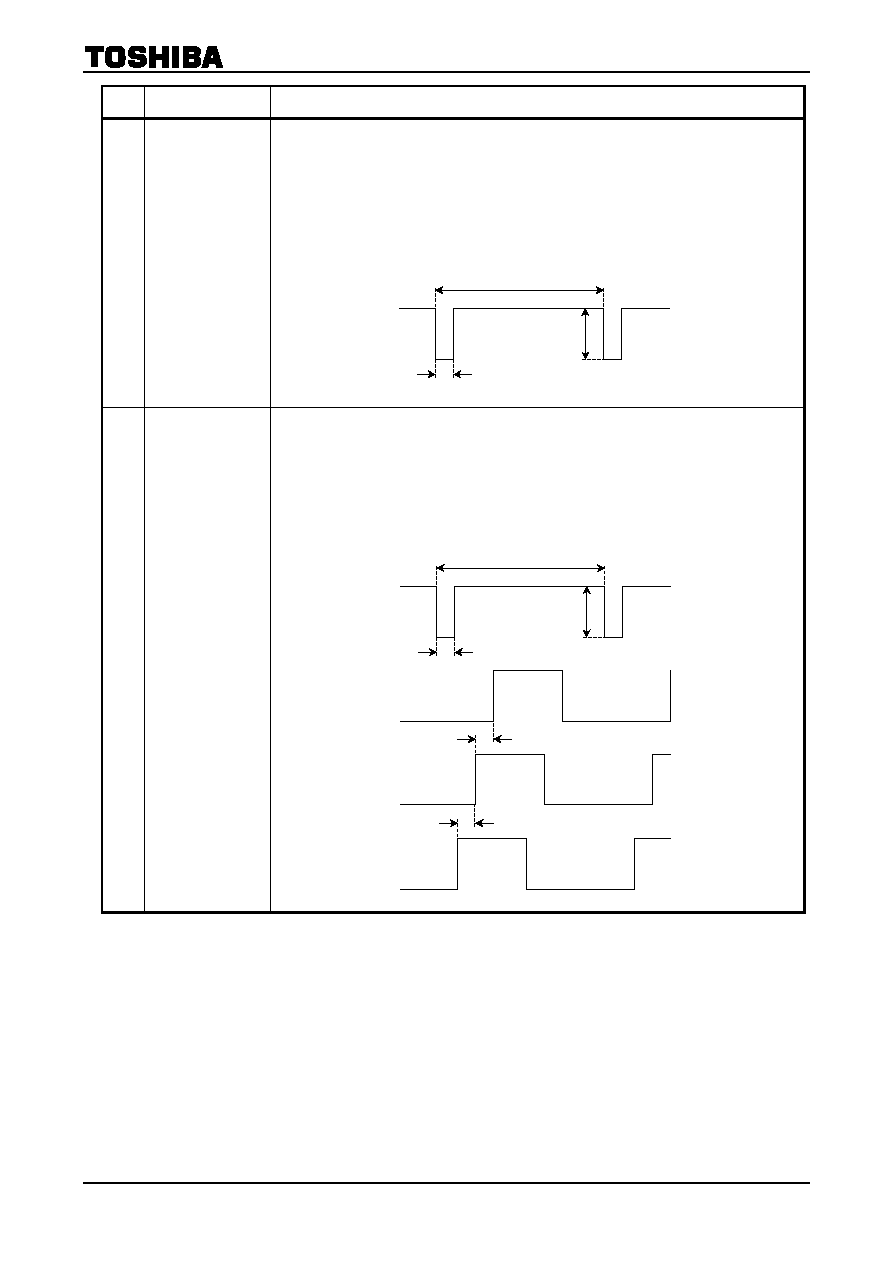

14 SYNC

IN

Inputs sync signal via clamp

capacitor.

White 100%: 1 V

p-p

or

15 VD1

IN

Inputs vertical sync signal

VD1. Signal input can have

both positive and negative

polarity.

or

19

15

25

1 k

45 k

Threshold:

0.75 V

Threshold:

0.75 V

19

14

25

1 k

1 k

10

µ

A

1 k

TA1316AN

2002-10-04

11

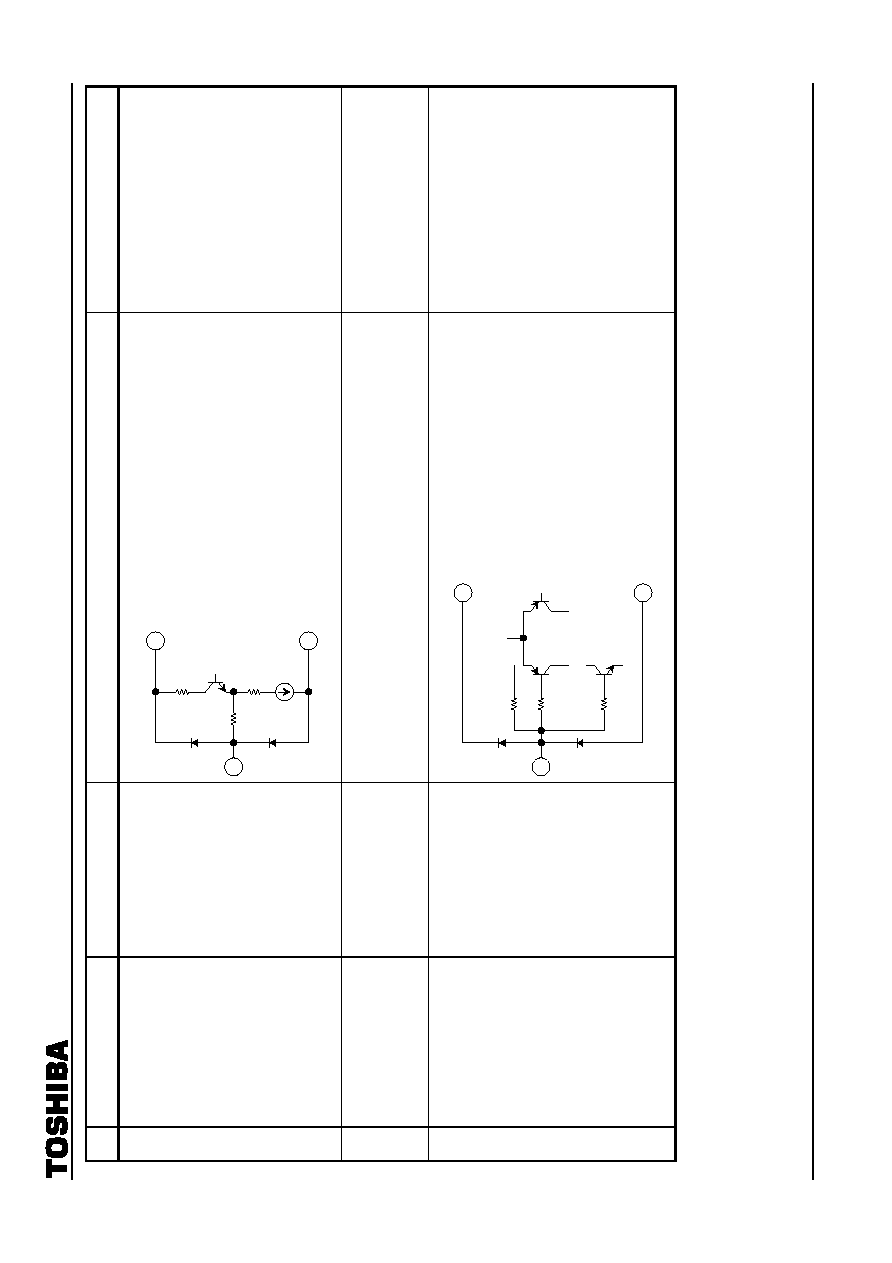

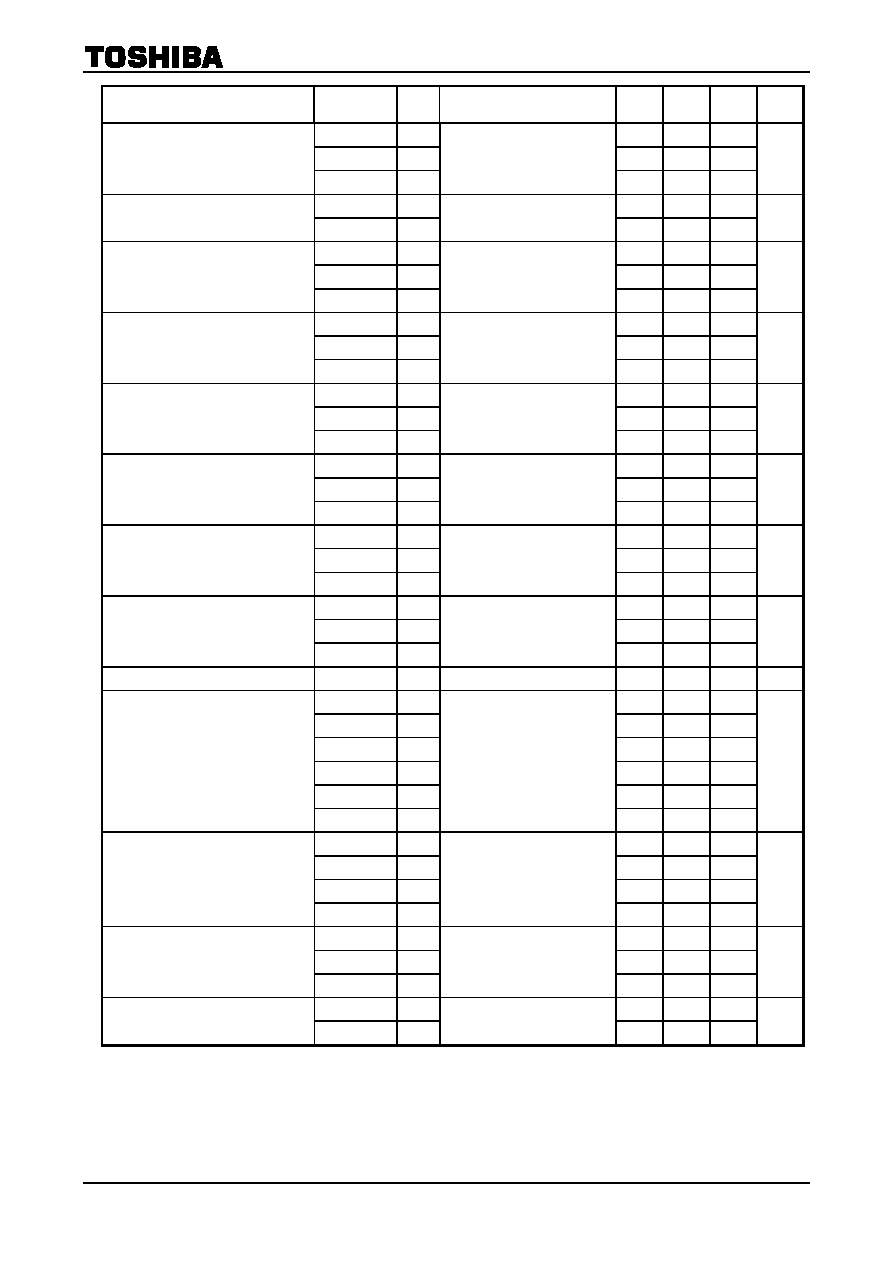

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

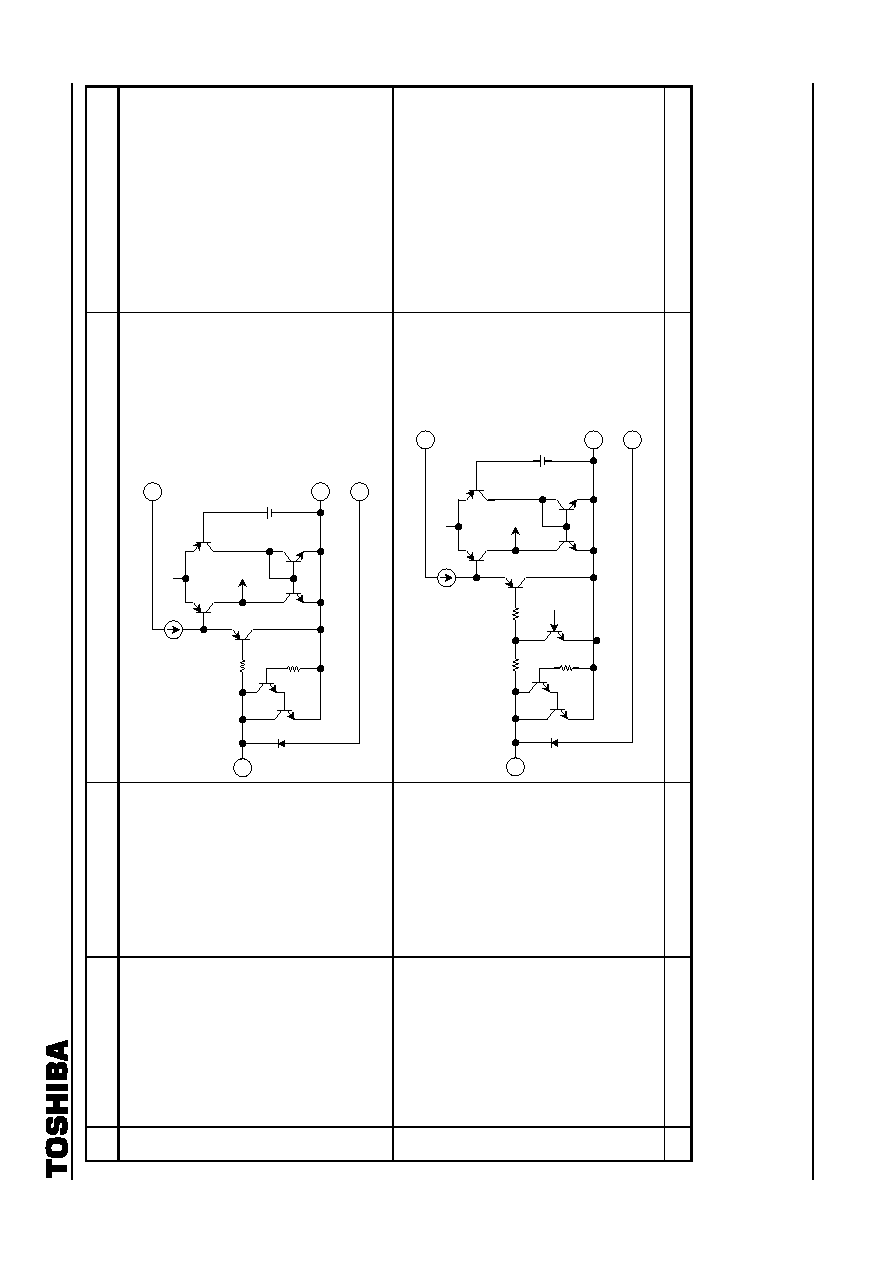

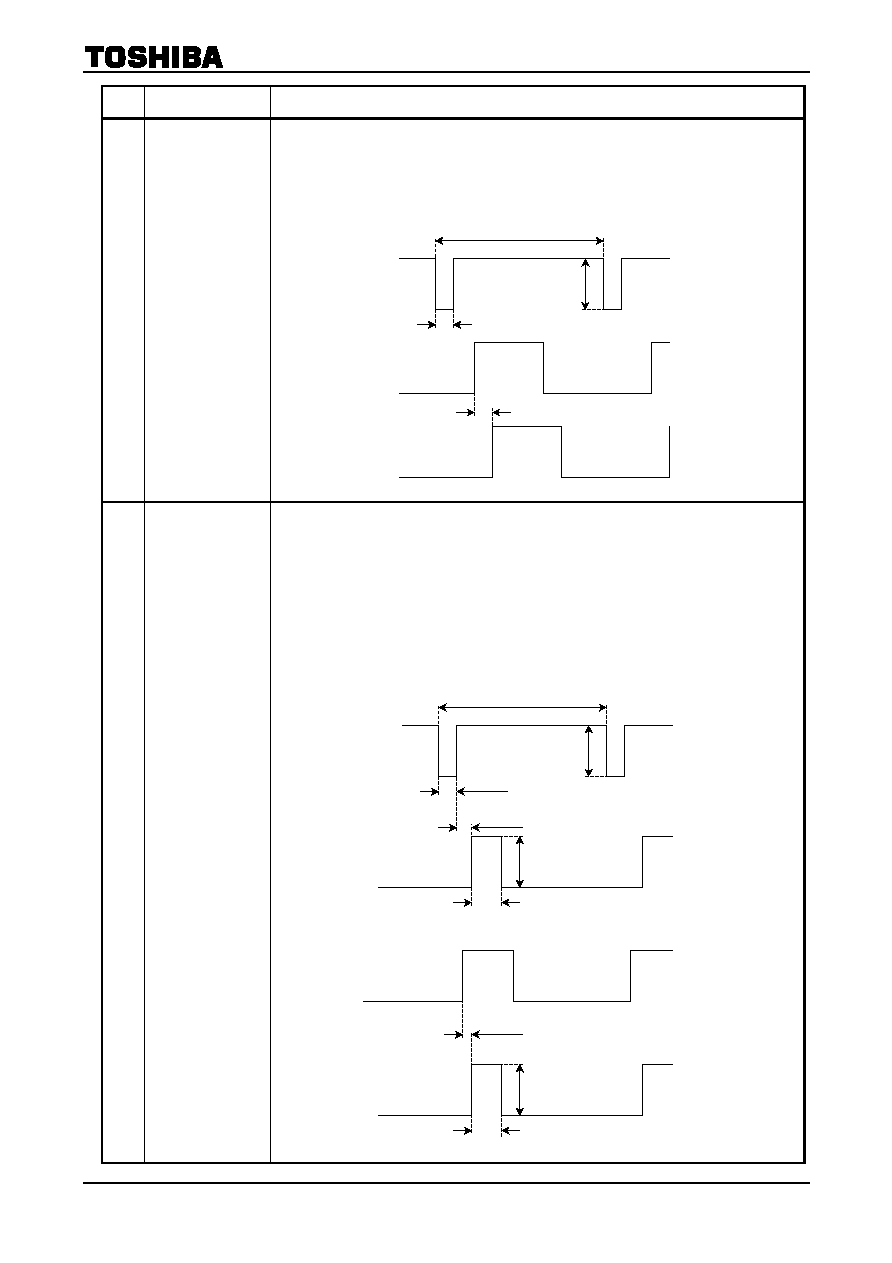

16 HD1

IN

Inputs horizontal sync signal

HD1. Input signal can have

both positive and negative

polarity.

or

17 SCP

IN

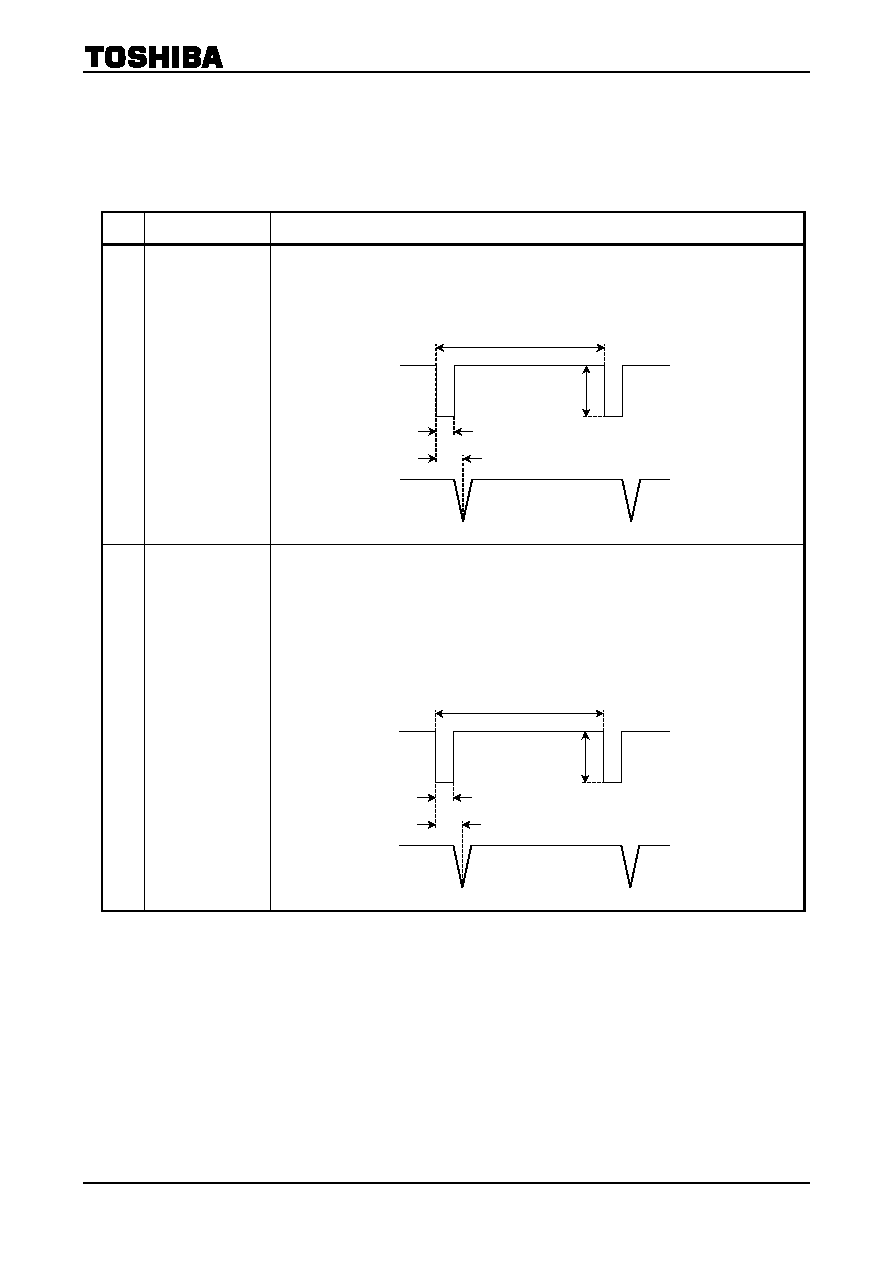

Inputs SCP from up converter.

Input signals are clamp pulse

(CP) and black peak detection

stop pulse (BPP).

2.2 V~2.8 V: BPP

4.7 V~9 V: CP

18 SCP

OUT

Outputs SCP.

Output signals are clamp pulse

(CP) and black peak detection

stop pulse (BPP).

(Note) Don't use

Horizontal-BPP (H-BPP) for

the timing pulse of picture

period on the screen (e.g.

H-BLK) because H-BPP width

will be changed by the

temperature.

19

16

25

1 k

50 k

19

18

25

500

2.

5 k

200

CP: 5.0 V

BPP: 2.5 V

0 V

19

17

25

5 k

50 k

50 k

40 k

Threshold:

0.75 V

Threshold:

0.75 V

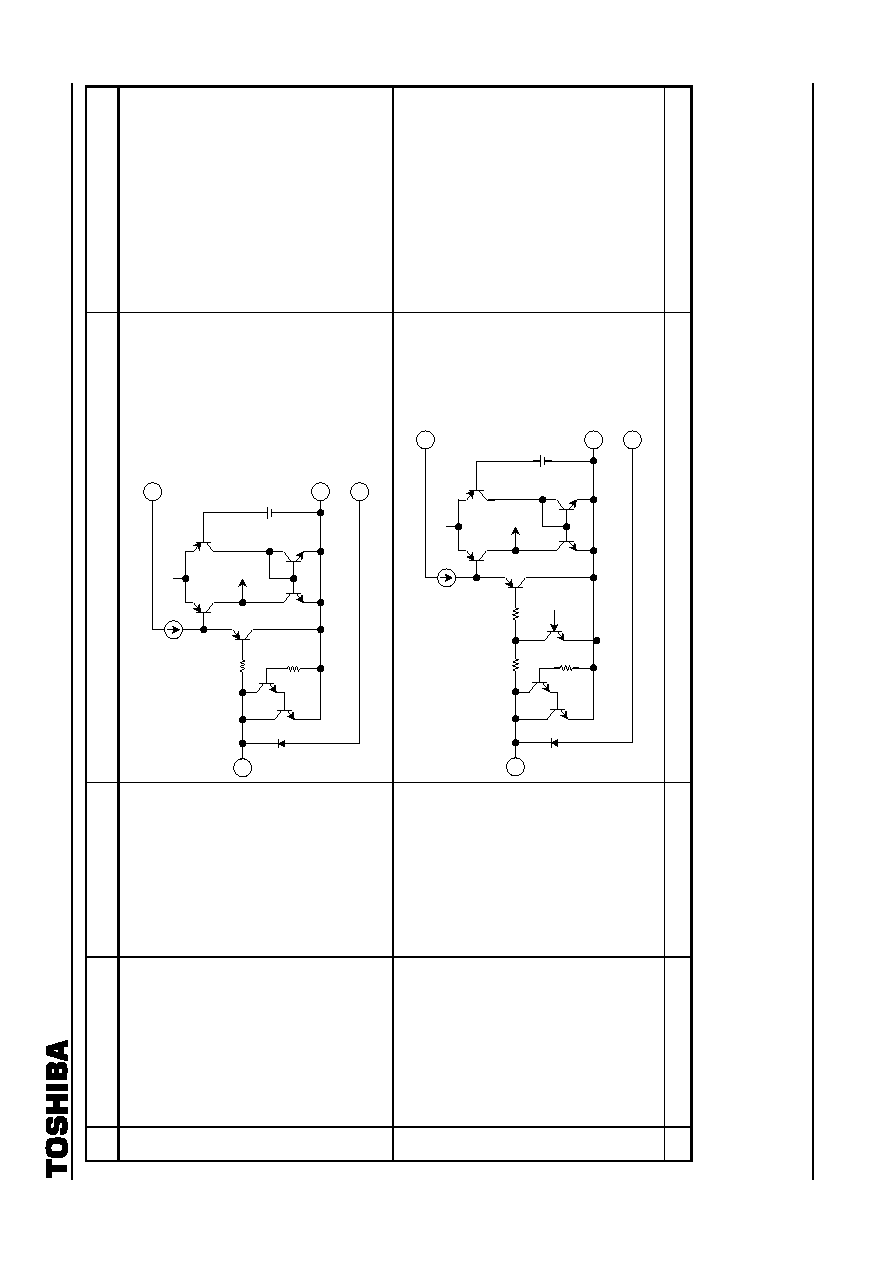

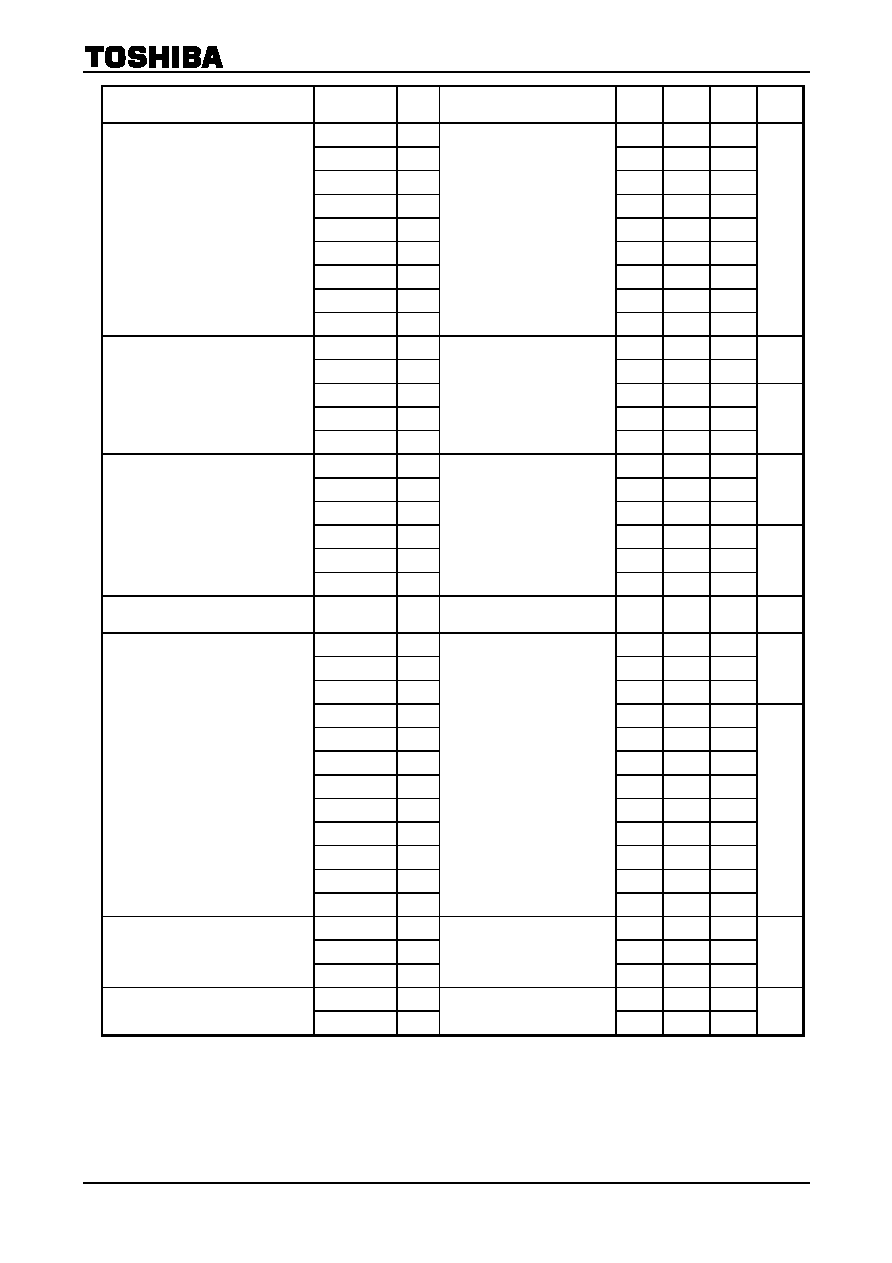

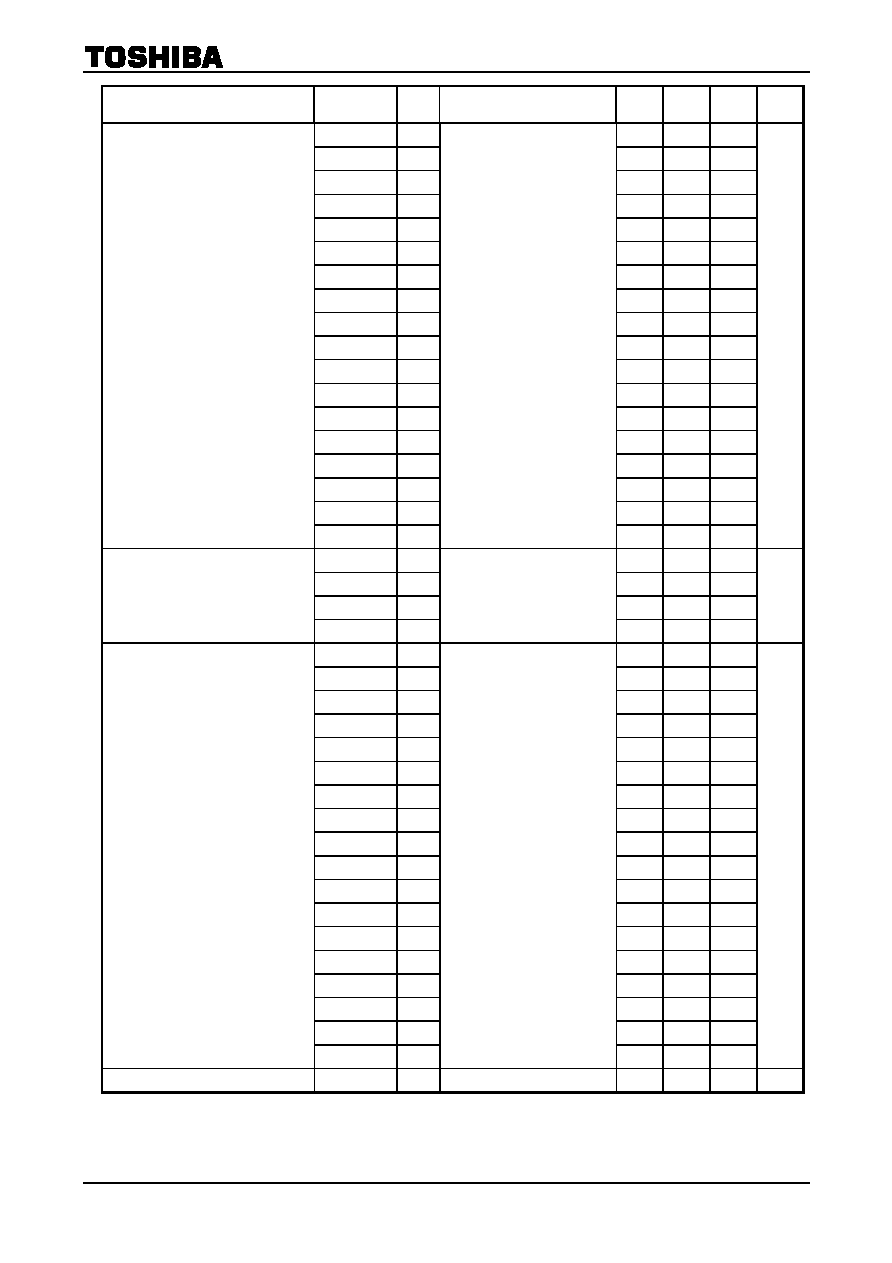

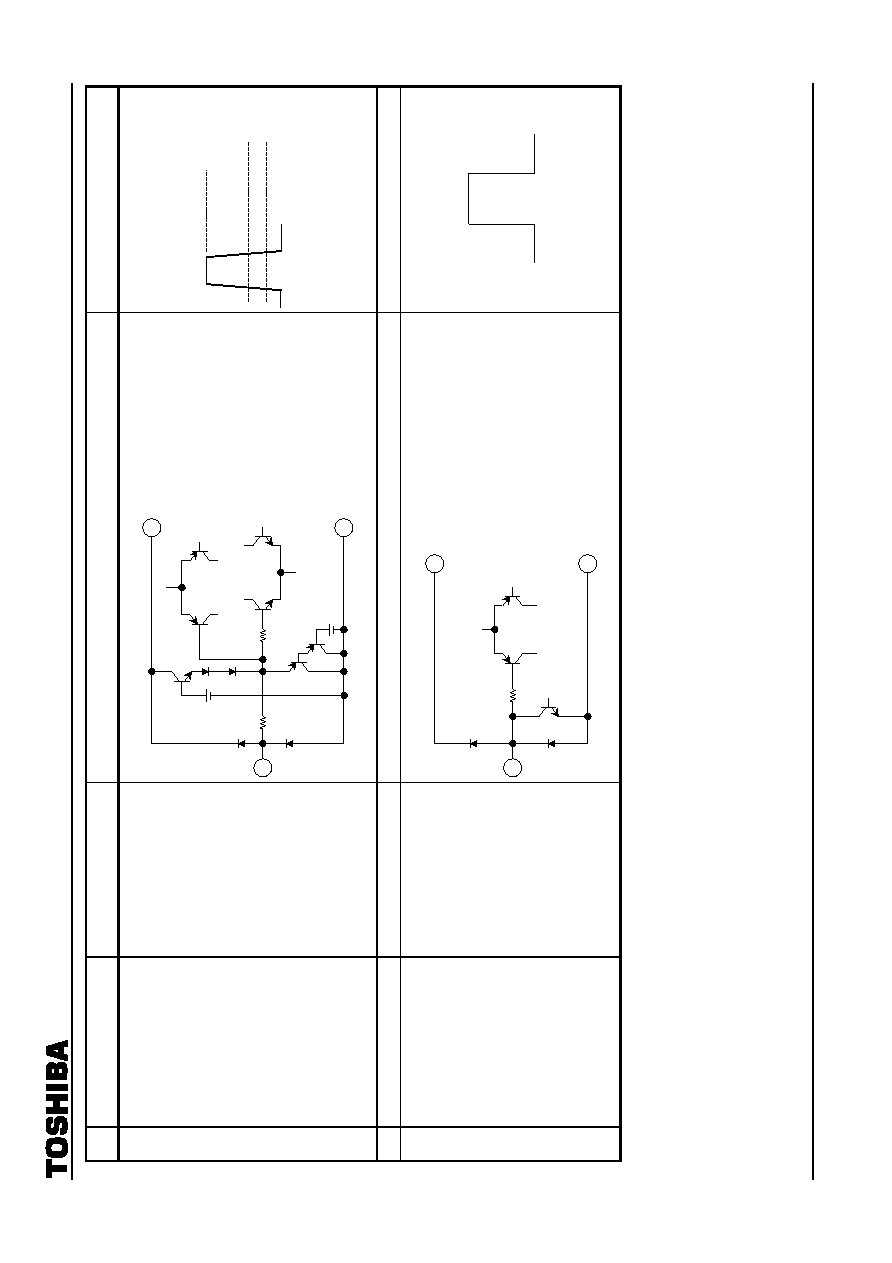

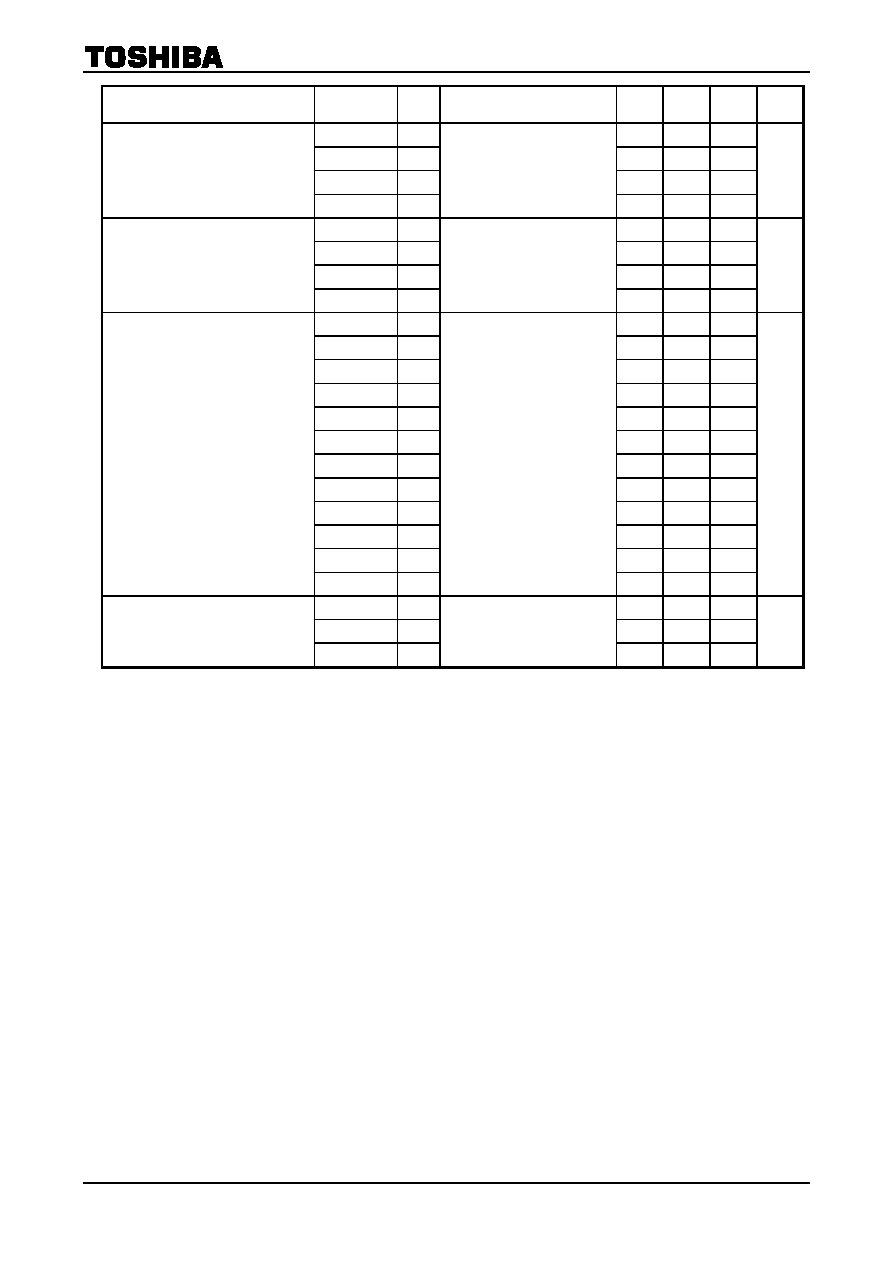

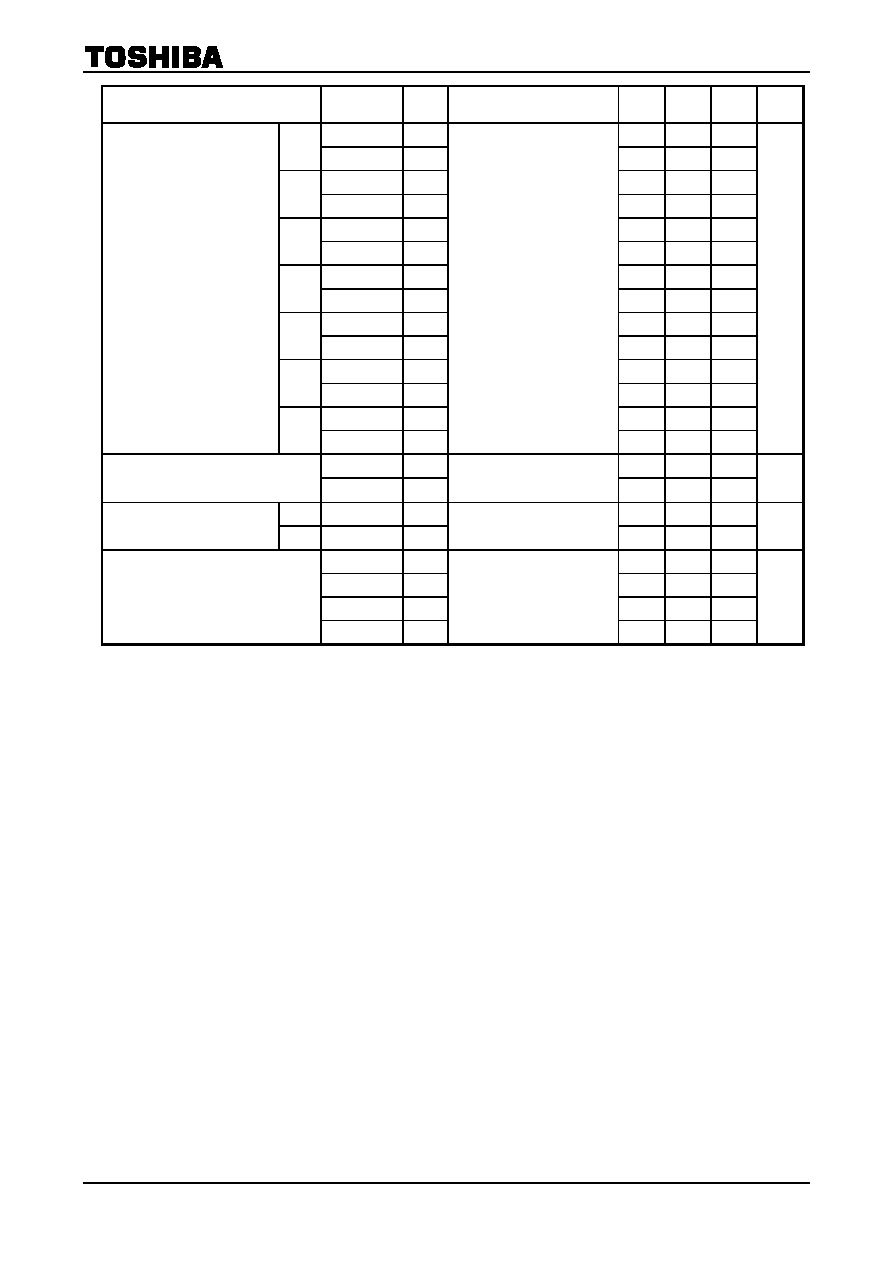

TA1316AN

2002-10-04

12

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

19 DEF/DAC

V

CC

V

CC

pin for DEF/DAC block.

To ascertain the correct

voltage for V

CC

, please refer to

the table entitled Maximum

Ratings.

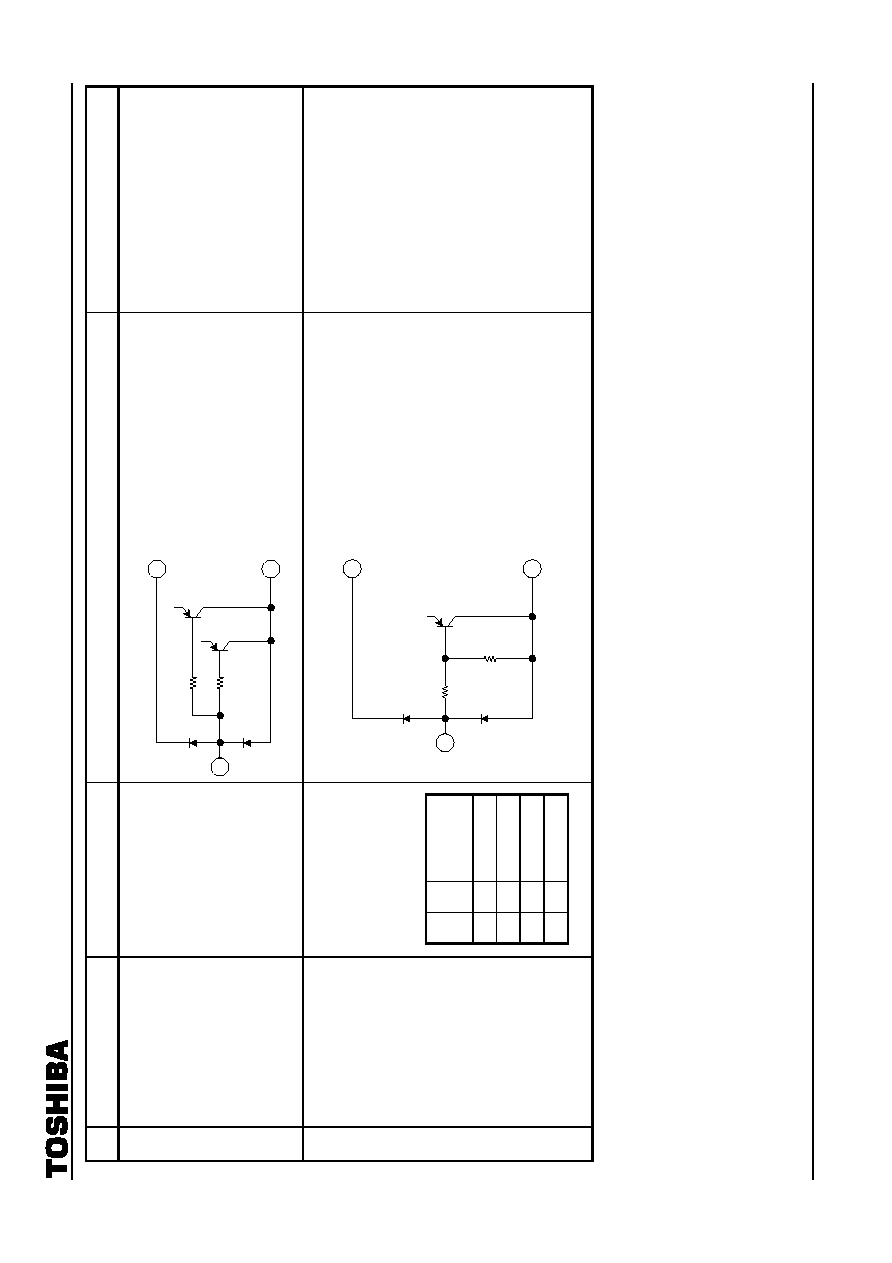

20 AFC

FILTER

Connect filter for detecting

AFC.

DC

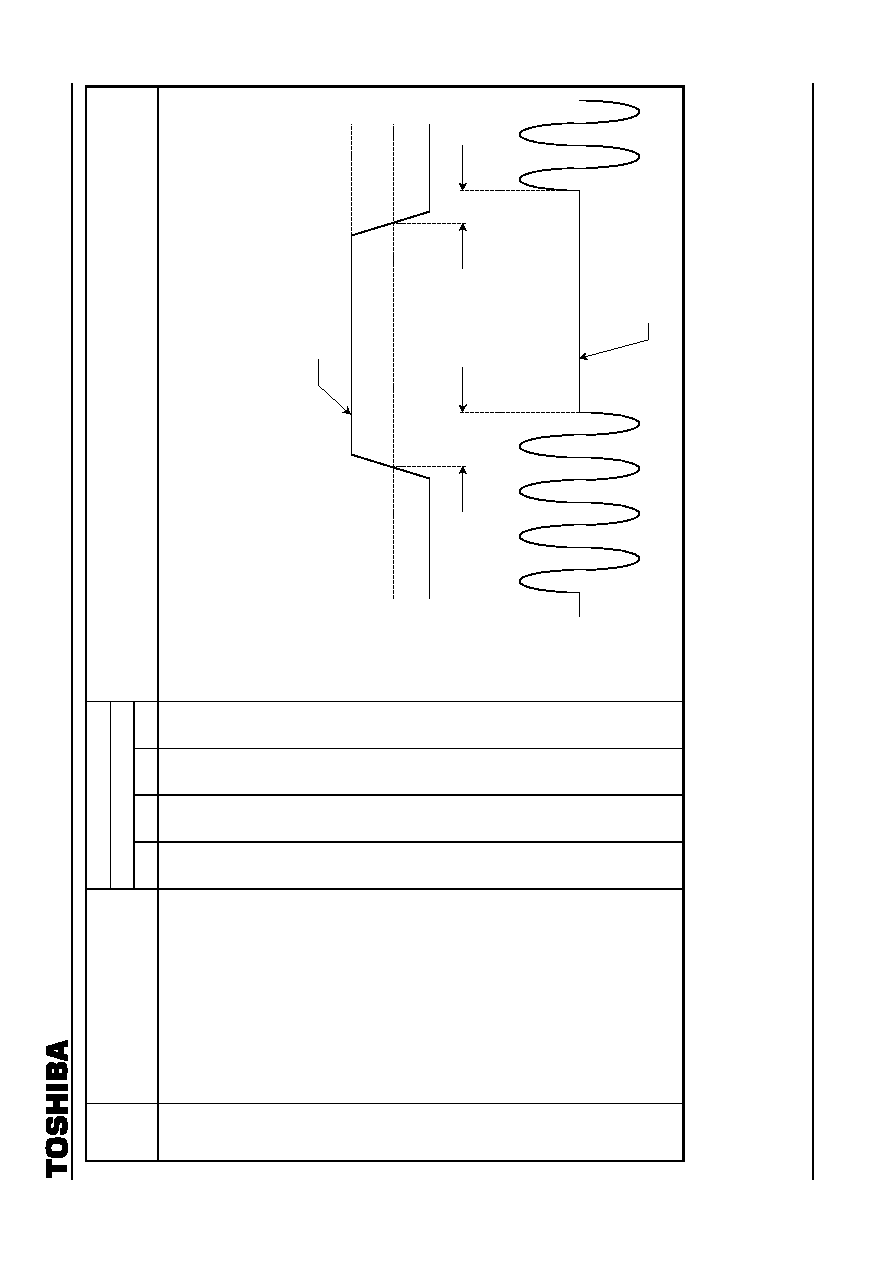

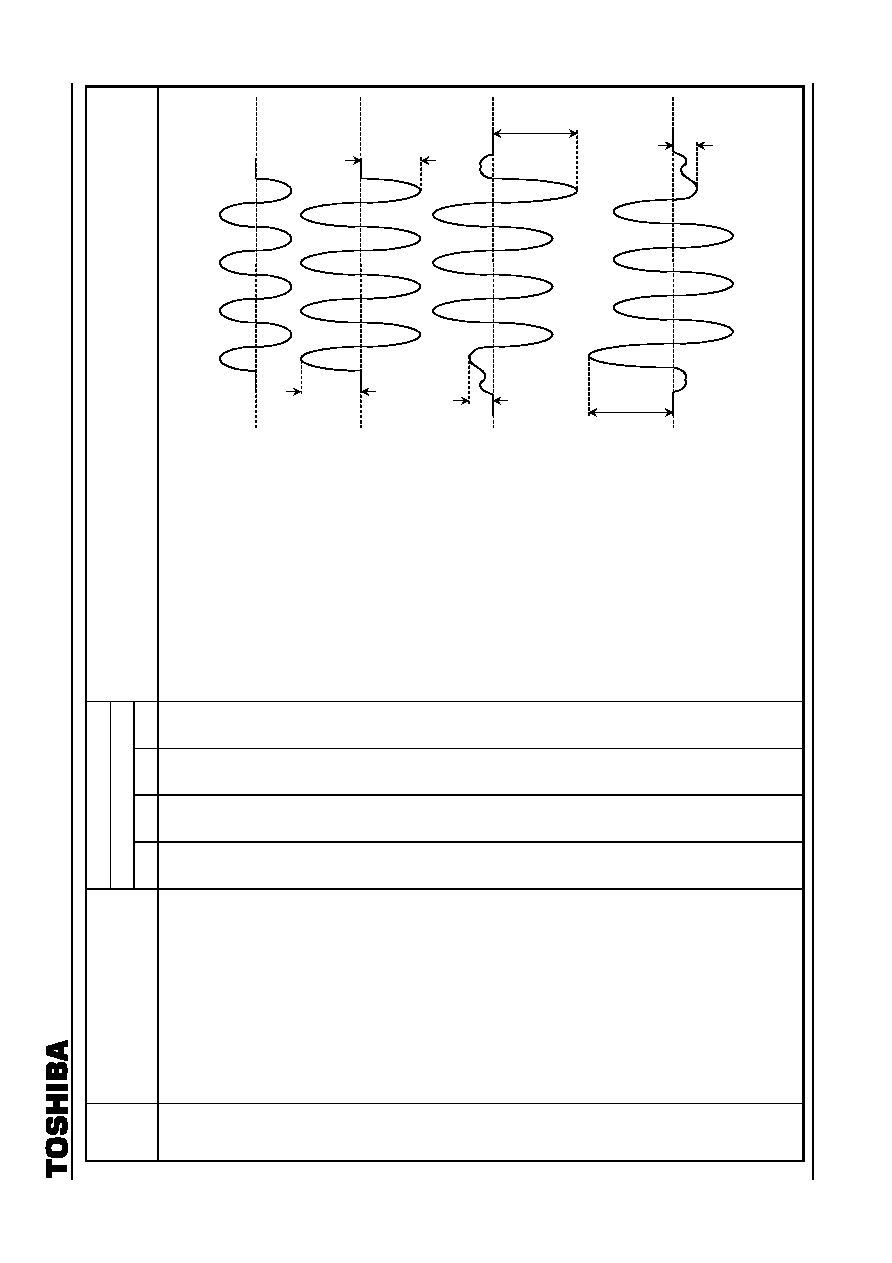

21 HVCO

Connect ceramic oscillator for

horizontal oscillation.

Use Murata

CSBLA503KECZF30

oscillator.

19

21

25

2 k

10 k

1 k

1 k

19

20

25

300

30 k

TA1316AN

2002-10-04

13

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

22

HORIZONTAL

FREQUENCY

SW

Horizontal frequency select

pin.

Selects horizontal frequency

according to voltage value

input to this pin.

When selecting horizontal

frequency by BUS control,

leave pin open. Control by pin

has priority over control by

BUS.

When this IC will be used on

CRT, the frequency of H-out

(pin 26) should be controlled

by DC voltage which is divided

from voltage of DEF V

CC

(pin

19) by resisters.

At BUS control (horizontal frequency):

output voltage value

00 (15.75 kHz): DC 9 V

01 (31.5 kHz): DC 6 V

10 (33.75 kHz): DC 3 V

11 (45 kHz):

DC 0 V

At pin 22 control, horizontal frequency

and input voltage value

0~1.0

V:

45

kHz

2.0~4.0

V:

33.75

kHz

5.0~7.0

V:

31.5

kHz

8.0~9.0

V:

15.75

kHz

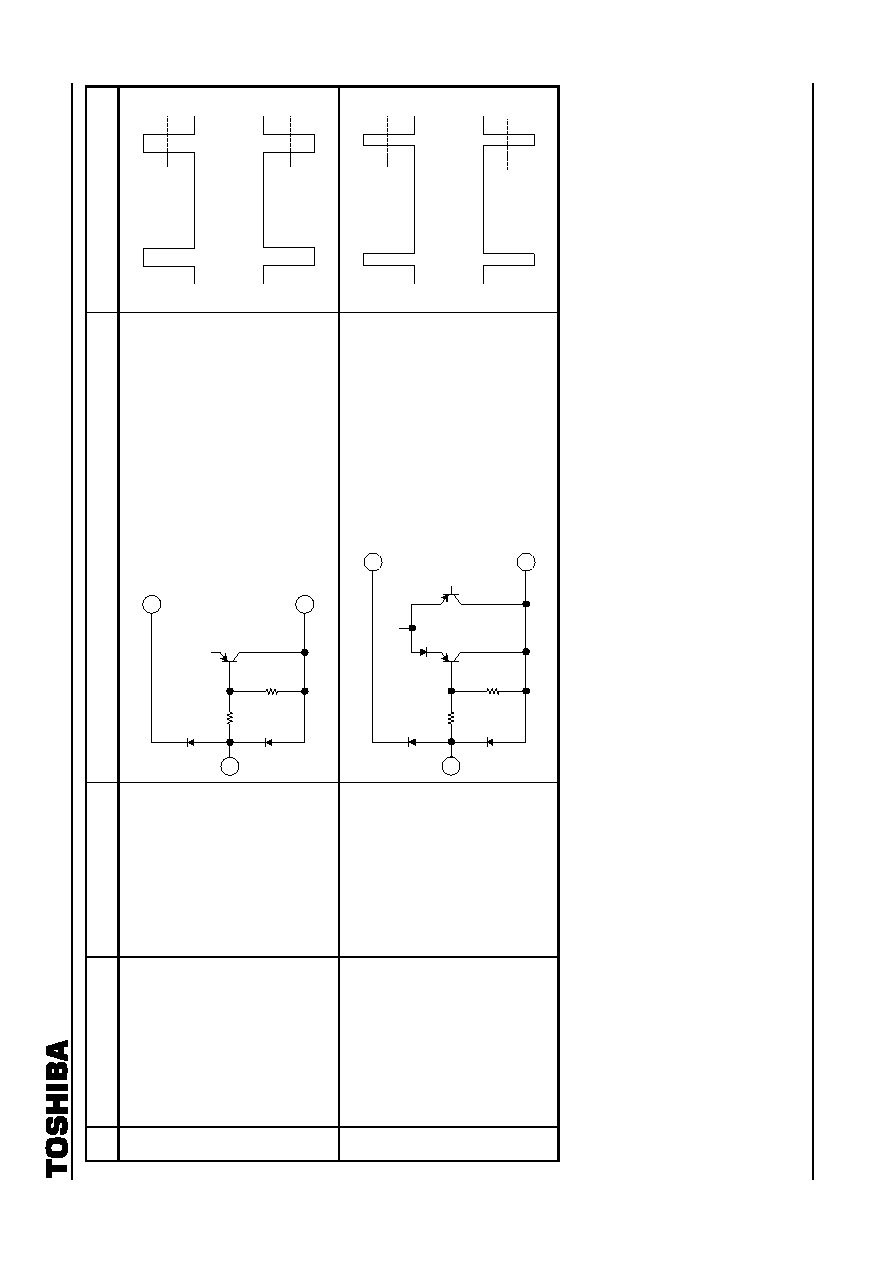

23

H CURVE

CORRECTION

Corrects curve at high-tension

fluctuation.

Input AC component of

high-tension fluctuation.

When pin is not used, connect

0.01

µ

F capacitor between pin

and GND.

DC

23

1 k

65 k

19

25

25 k

50 k

130 k

6.5 V

19

25

22

1 k

30 k

1 k

20 pF

60 k

60 k

60 k

16 k

15

k

4.5 V

7.5 V

1.5 V

TA1316AN

2002-10-04

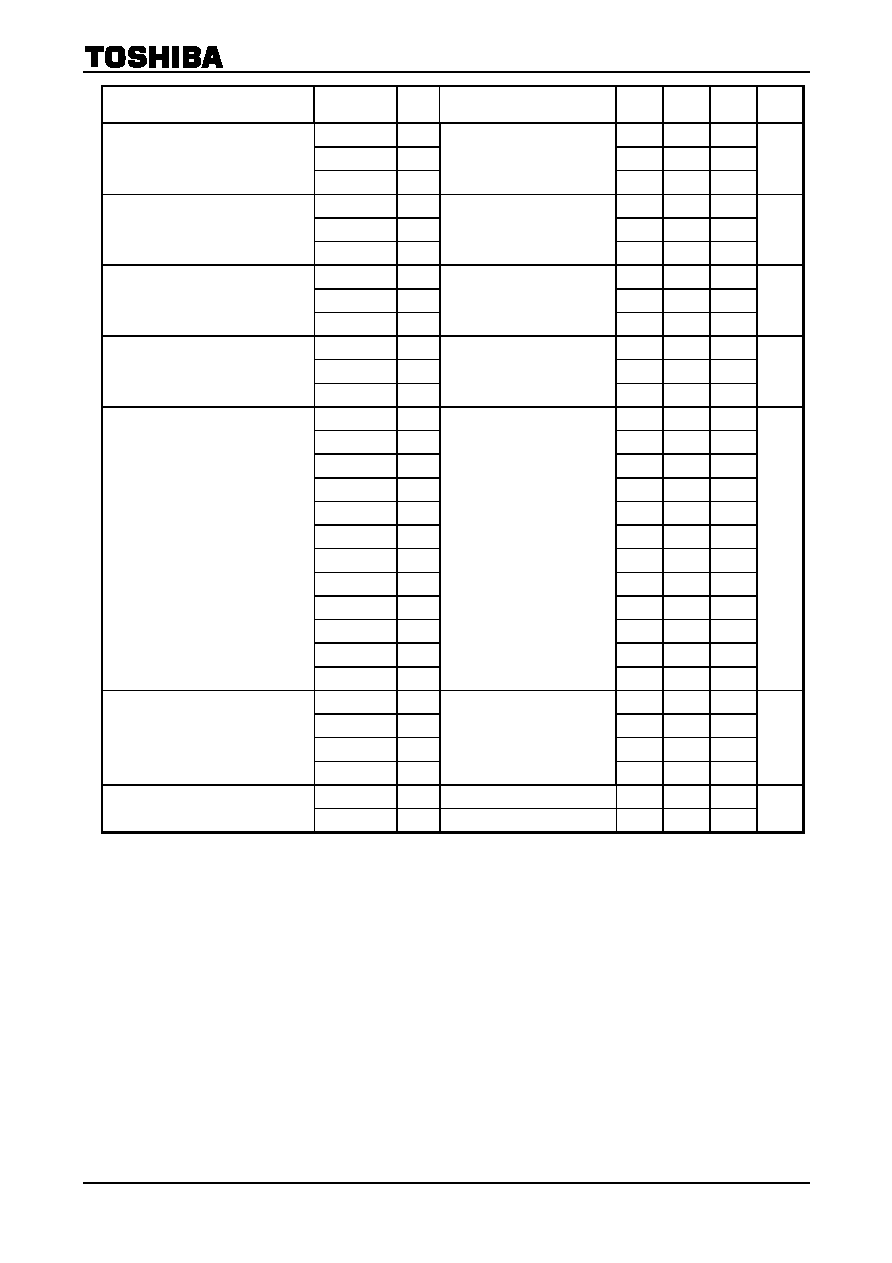

14

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

24 FBP

IN

Input FBP and H-BLK for

horizontal AFC.

25 DEF/DAC GND

GND pin for DEF/DAC block.

26 H-OUT

Horizontal output pin. Open

collector output.

max: 9 V

H-AFC threshold: 3.0 V

BLK threshold: 1.5 V

24

19

25

500

1 k

5 V

2.

25 V

19

26

25

5 k

TA1316AN

2002-10-04

15

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

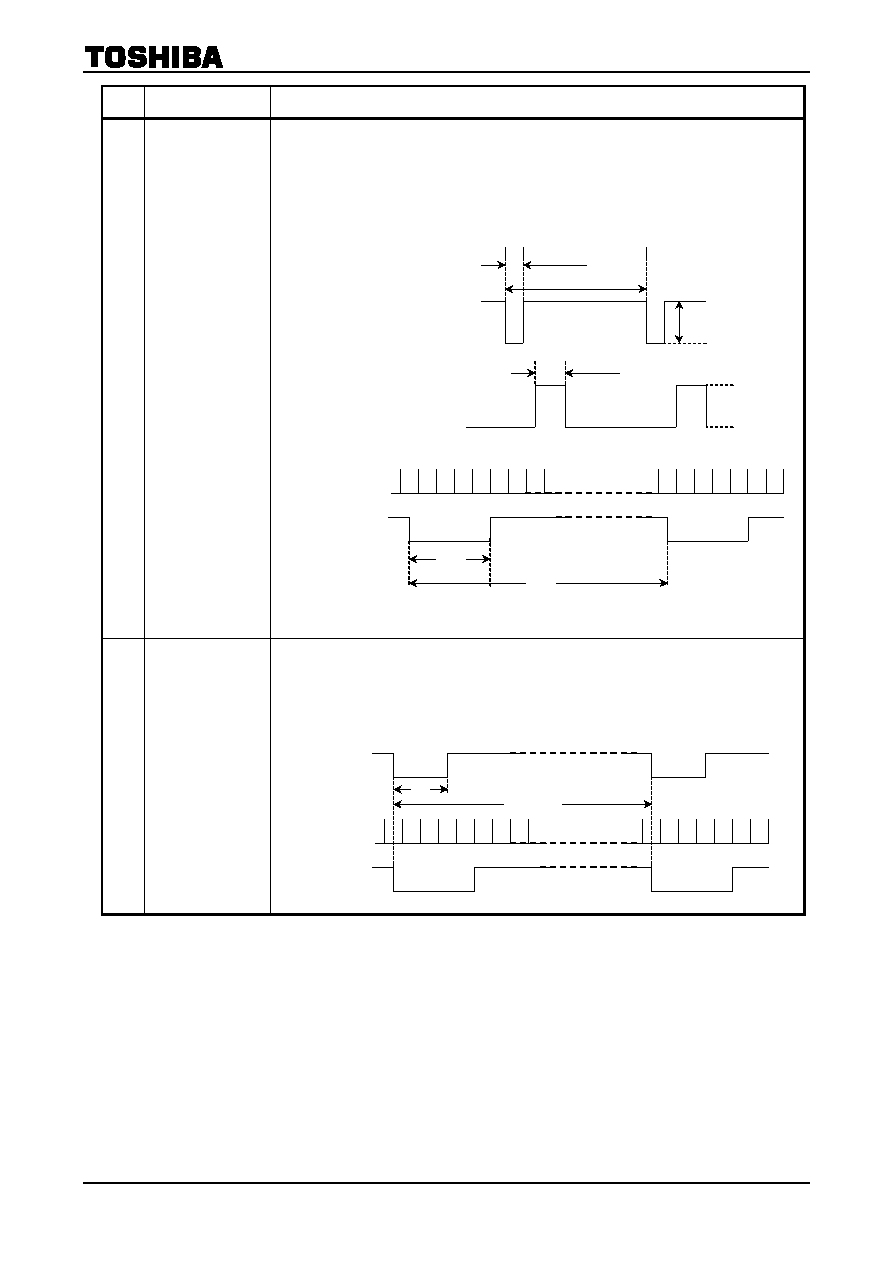

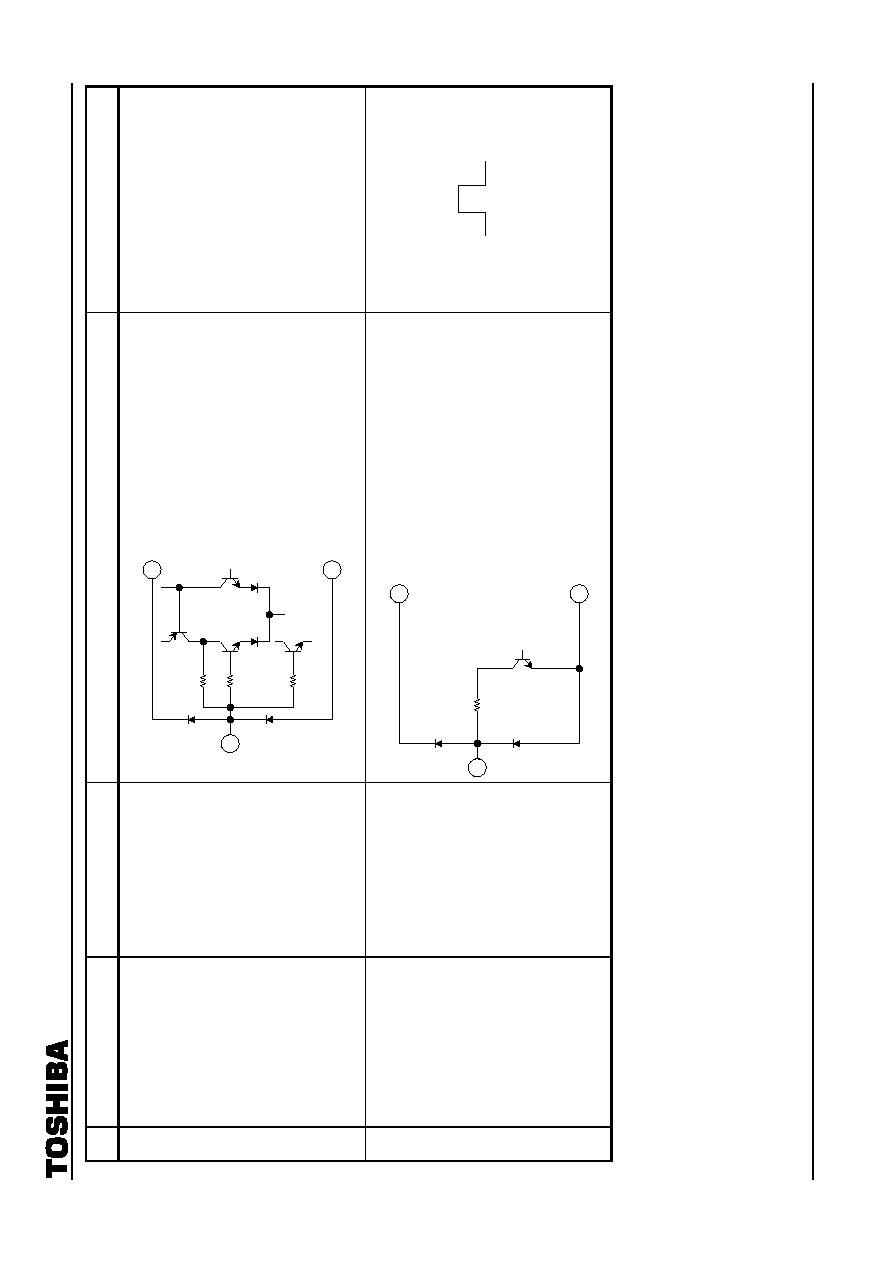

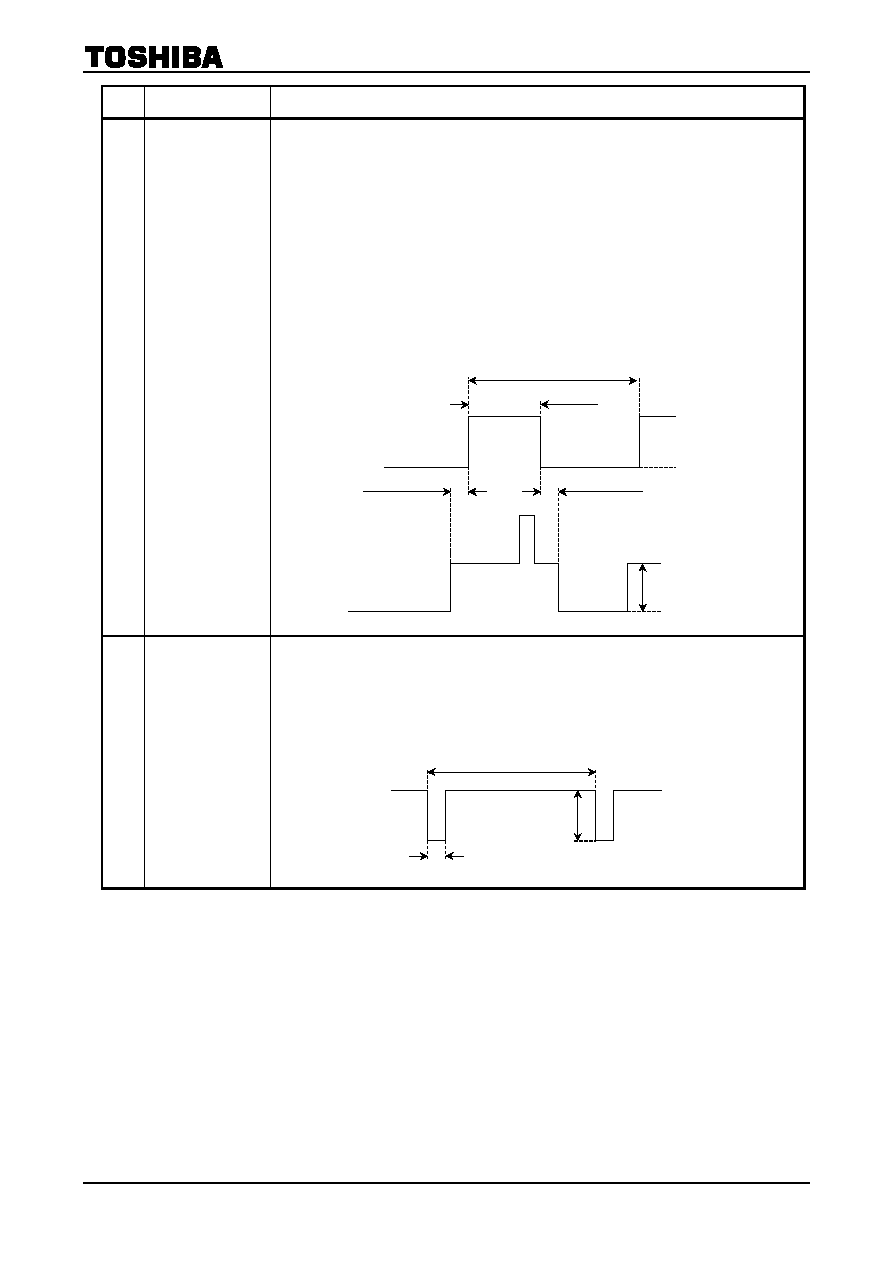

27 VP

OUT

Outputs vertical pulse.

When a current is applied to

the pin, external blanking is

carried out by ORing this

signal with the internal

blanking signal.

(Note) When H-POSITION will

be changed, VP width will

change. Use the start phase of

VP.

V-BLK input current: 780

µ

A~1 mA

28 DAC1

(SYNC OUT)

Outputs 1-bit DAC or

composite SYNC signal after

sync separation.

Open-collector output

(The output level for this pin

cannot be guaranteed since

leakage from internal signals

may occur.)

DC or SYNC OUT

29 I

2

L V

DD

V

DD

pin for I

2

L block.

Connect 2 V (typ.).

Power to pin 29 should be

supplied from pin 19 via zener

diode through resister.

5 V

0 V

Start phase

VP output:

19

25

28

500

32

19

25

27

200

200

µ

A

32

TA1316AN

2002-10-04

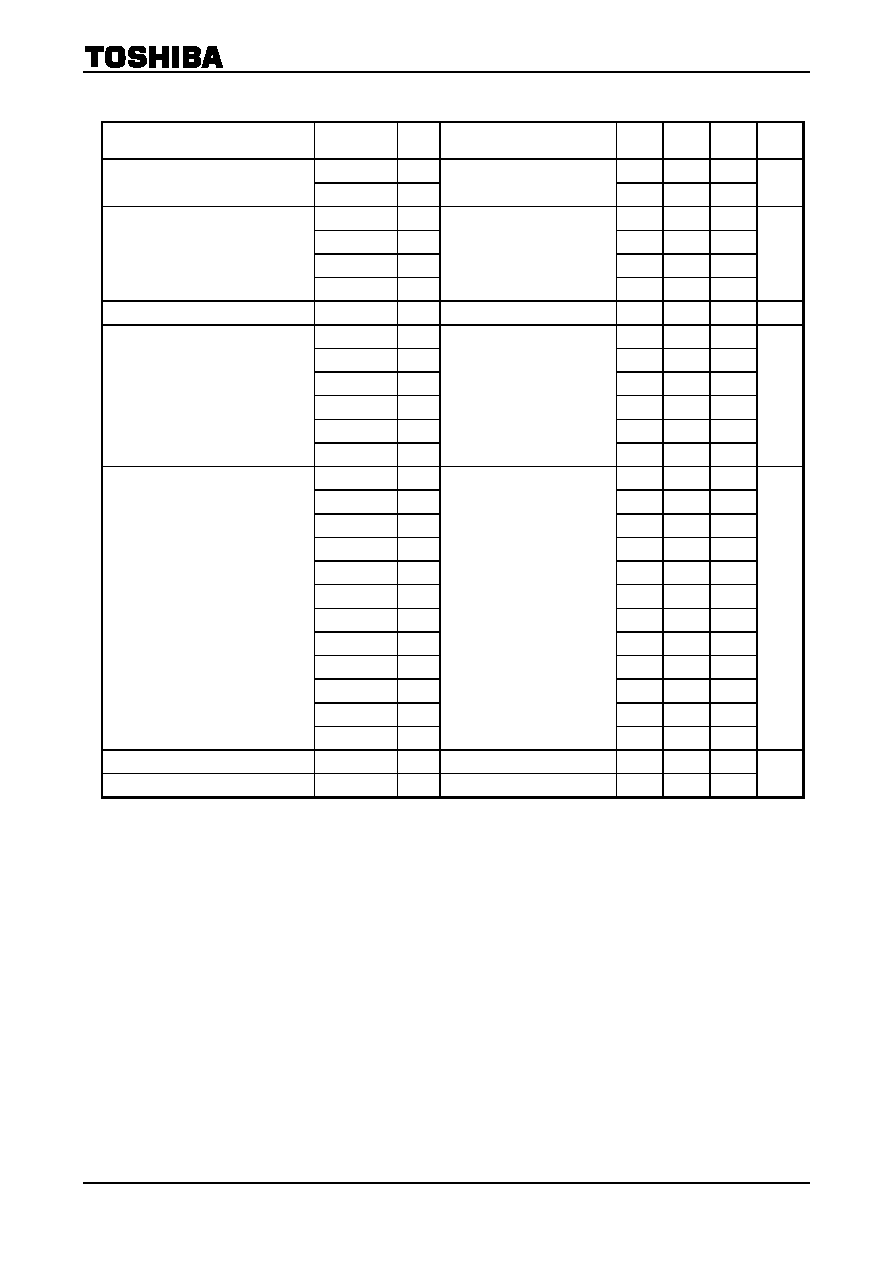

16

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

30 SCL

SCL pin for I

2

C BUS.

31 SDA

SDA pin for I

2

C BUS.

32 I

2

L GND

GND pin for I

2

L block.

19

30

32

5 k

25

SCL

2.

25 V

19

31

32

5 k

25

SDA

2.

25 V

50

ACK

TA1316AN

2002-10-04

17

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

33

34

35

ANALOG B IN

ANALOG G IN

ANALOG R IN

Inputs analog R/G/B signal via

clamp capacitor.

Recommended input

amplitude: 0.7 V

p-p

(no sync)

at 100% white

100 IRE: 0.7 V

p-p

36

DAC2

(ACB pulse)

Outputs 1-bit DAC or ACB

pulse

Open-collector output

DC or ACB pulse

40

44

1 k

33

34

35

1 k

1 k

40

36

44

500

TA1316AN

2002-10-04

18

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

37

38

39

ANALOG OSD B IN

ANALOG OSD G IN

ANALOG OSD R IN

Inputs analog OSD signal via

clamp capacitor.

Recommended input

amplitude: 0.7 V

p-p

(no sync)

at 100% white

100 IRE: 0.7 V

p-p

40 RGB

V

CC

V

CC

pin for text/RGB block.

To ascertain the correct

voltage for V

CC

, please refer to

the table entitled Maximum

Ratings.

41

42

43

B OUT

G OUT

R OUT

Outputs R/G/B signal.

Recommended output

amplitude: 100 IRE

=

2.3 V

p-p

100 IRE: 2.3 V

p-p

Conditions:

UNI-COLOR

=

max

SUB-CONT

=

Cent

Y

IN

=

0.7 V

p-p

44 RGB GND

GND pin for text/RGB block.

40

44

1 k

37

38

39

1 k

1 k

40

44

41

42

43

200

100

2.

7 m

A

TA1316AN

2002-10-04

19

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

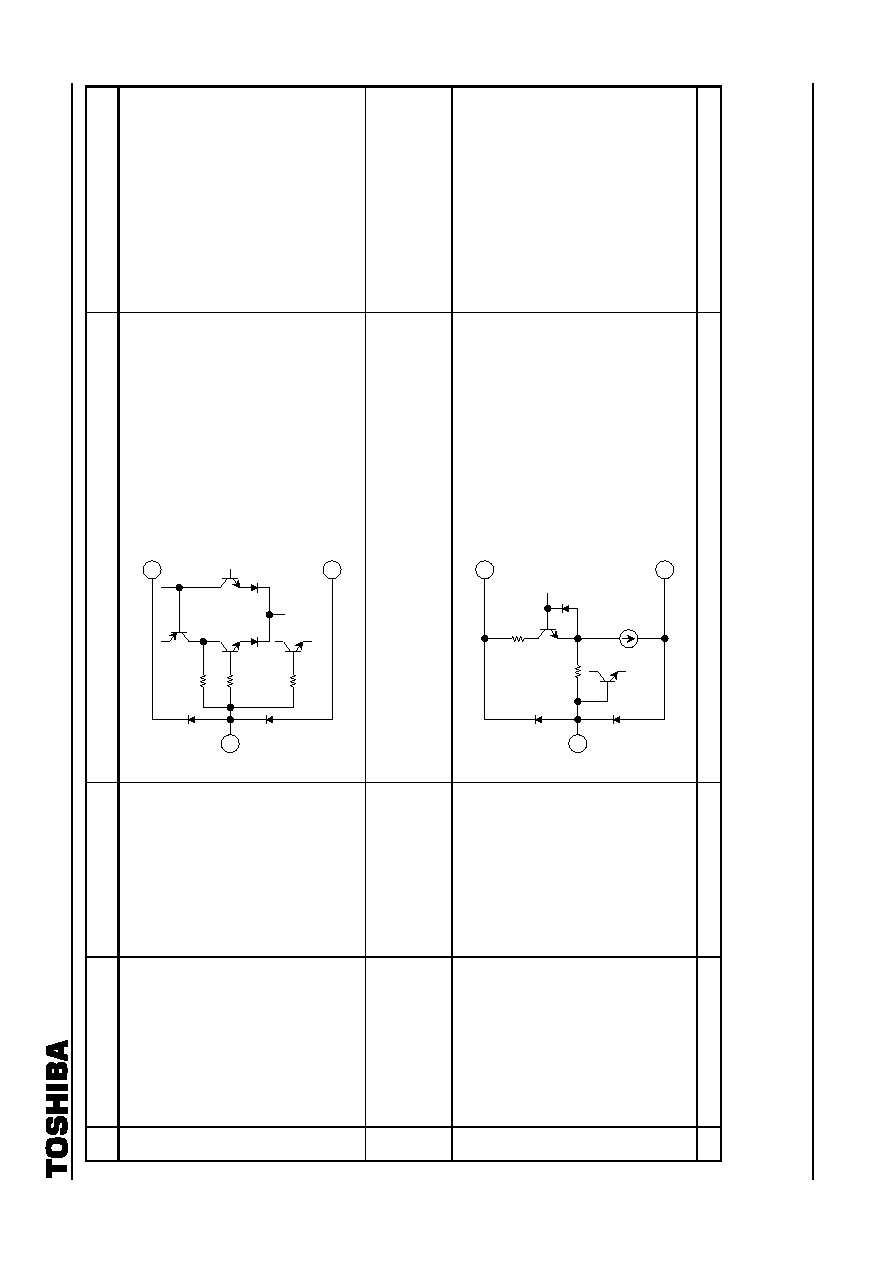

45 I

K

IN

Inputs the feedback signal

from CRT. (BLK level should

be 0 V to 3 V.)

When ACB is not used,

connect this pin to the RGB

V

CC

pin.

or RGB V

CC

46

47

48

B S/H

G S/H

R S/H

Sample-and-hold (S/H) pin.

In ACB mode connect a 2.2-

µ

F

capacitor. In CUTOFF mode

connect a 0.01-

µ

F capacitor.

DC

40

45

44

1 k

40

44

46

47

48

500

1 k

5 k

3 pF

3 V

1 V

p-p

(typ.)

R G B

0 V~3 V

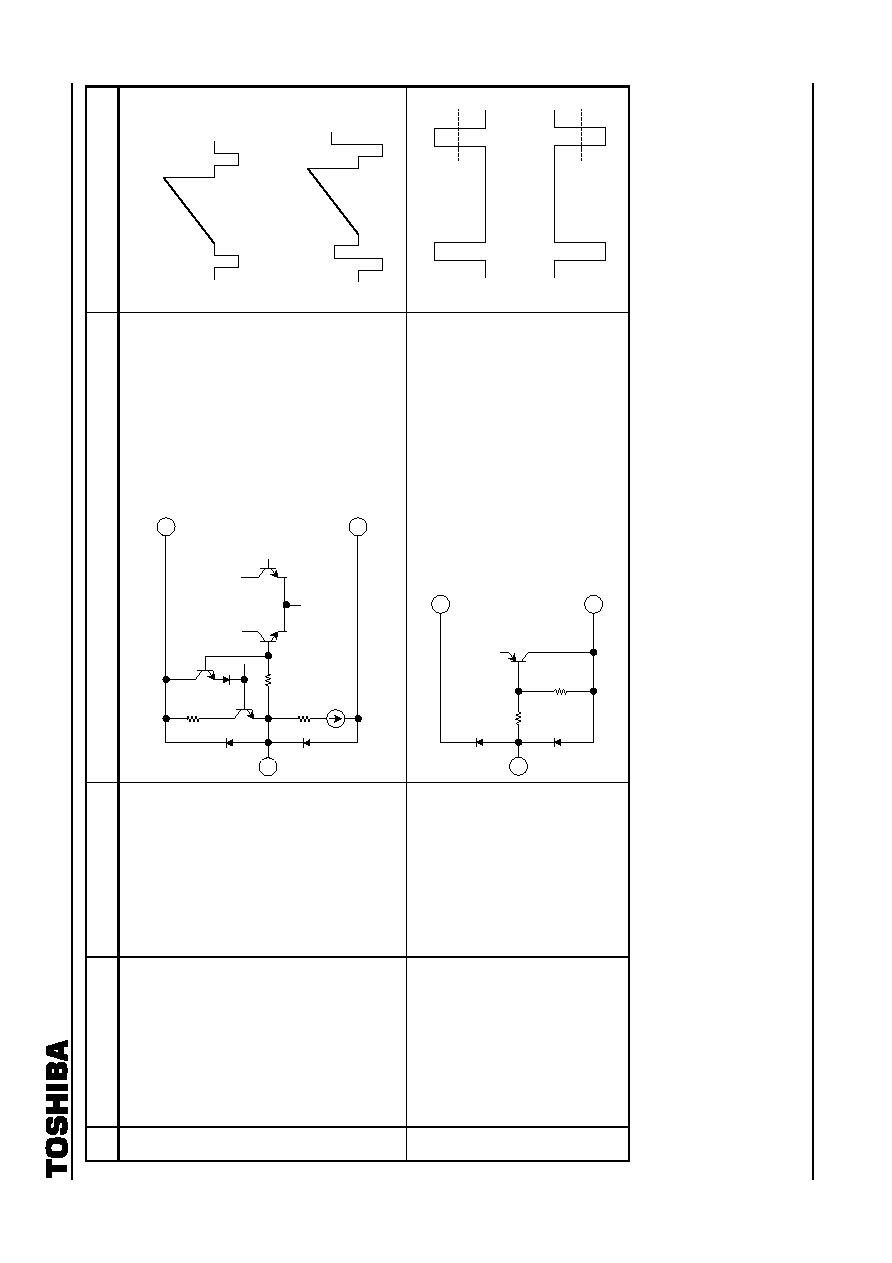

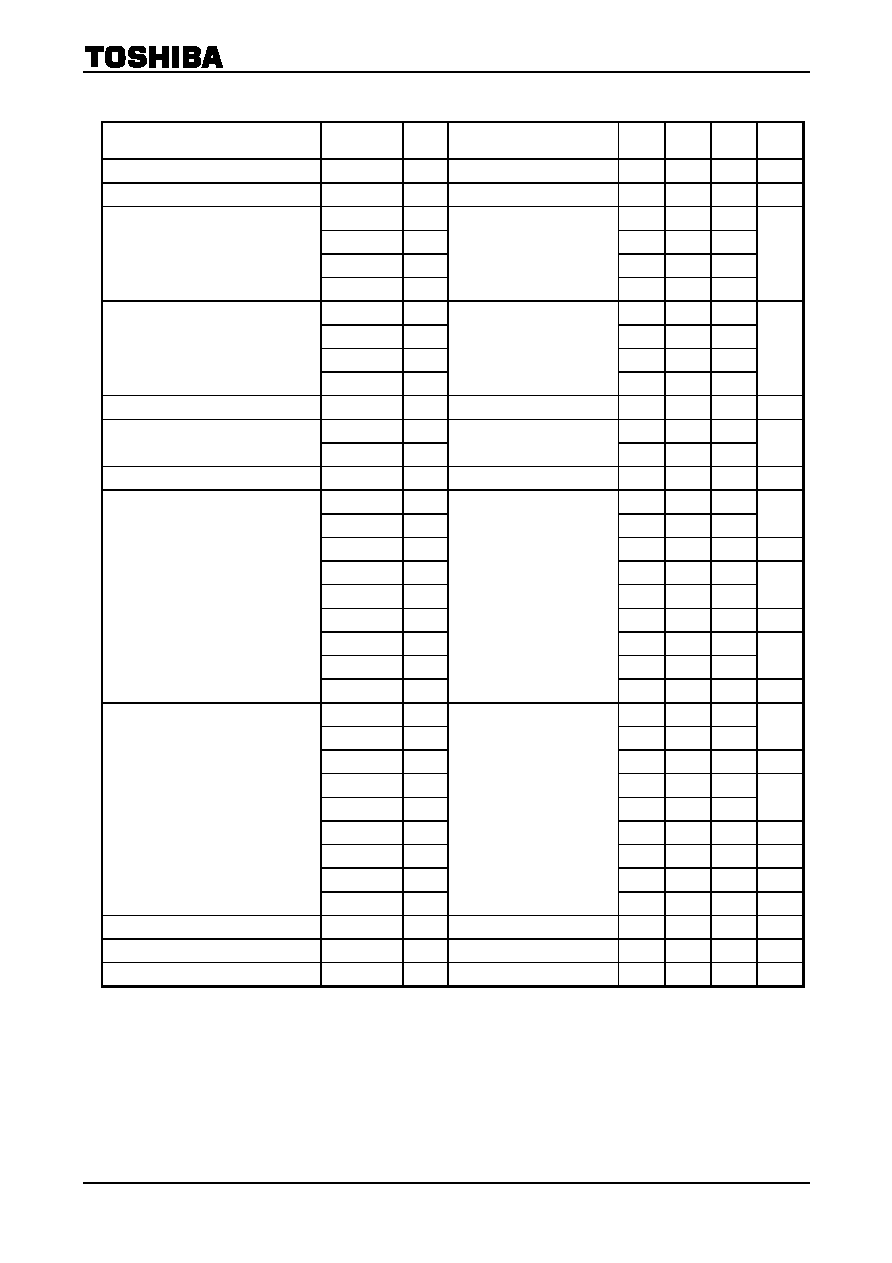

TA1316AN

2002-10-04

20

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

49 Y

S

3

(analog RGB)

Selects input between internal

RGB and external analog RGB

according to voltage value

input to this pin.

When analog RGB is selected,

mutes VSM output.

0~0.5 V: Internal

1.5~9 V: Analog RGB, VSM mute

50

51

Y

S

2

(analog OSD)

Y

S

1

(analog OSD)

Switches between internal

RGB and OSD input signals.

Voltage applied to Y

S

1 and

Y

S

2 adjusts blend ratio of

internal RGB and OSD signals.

When Y

S

1 or Y

S

2 is High,

mutes VSM output.

Y

S

2 Y

S

1

Blend ratio

Int RGB:

OSD RGB

L L 10:0

H L 7:3

L H 5:5

H H 0:10

0~0.5 V: Internal

1.1~1.7 V: VSM mute

2.9~9 V: OSD, VSM mute

40

49

44

300

300

40

44

50

51

300

50 k

TA1316AN

2002-10-04

21

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

52 Y

M

/P-MUTE/BLK

Fast half-tone switch for

internal RGB signal.

Also performs image mute or

blanking.

0~0.5 V: Internal

1.2~1.8 V: Half-tone

2.7~4.0 V: P-mute

7~9 V:

Blanking

53 ABCL

IN

ABL and ACL input pin.

Can set gain and start point for

ABL and dynamic ABL by BUS

control.

DC

53

44

40

30 k

3 k

6.

75 V

40

52

44

300

80 k

10 k

TA1316AN

2002-10-04

22

Pin

No.

Pin Name

Function

Interface Circuit

Input Signal/Output Signal

54 VSM

OUT

Outputs Y signal for VSM

which passes through HPF

circuit (primary differential

circuit).

Mutes output signal using pins

49, 50 and 51.

55 Y/C

V

CC

V

CC

pin for Y/C block.

To ascertain the correct

voltage for V

CC

, please refer to

the table entitled Maximum

Ratings.

56 APL

FILTER

Connect filter for correcting DC

restoration.

Leaving this pin open enables

user to monitor Y signal after

black stretch and dynamic

.

55

56

6

1 k

40 k

1 k

40

54

6

200

200

1 k

1.

6 m

A

TA1316AN

2002-10-04

23

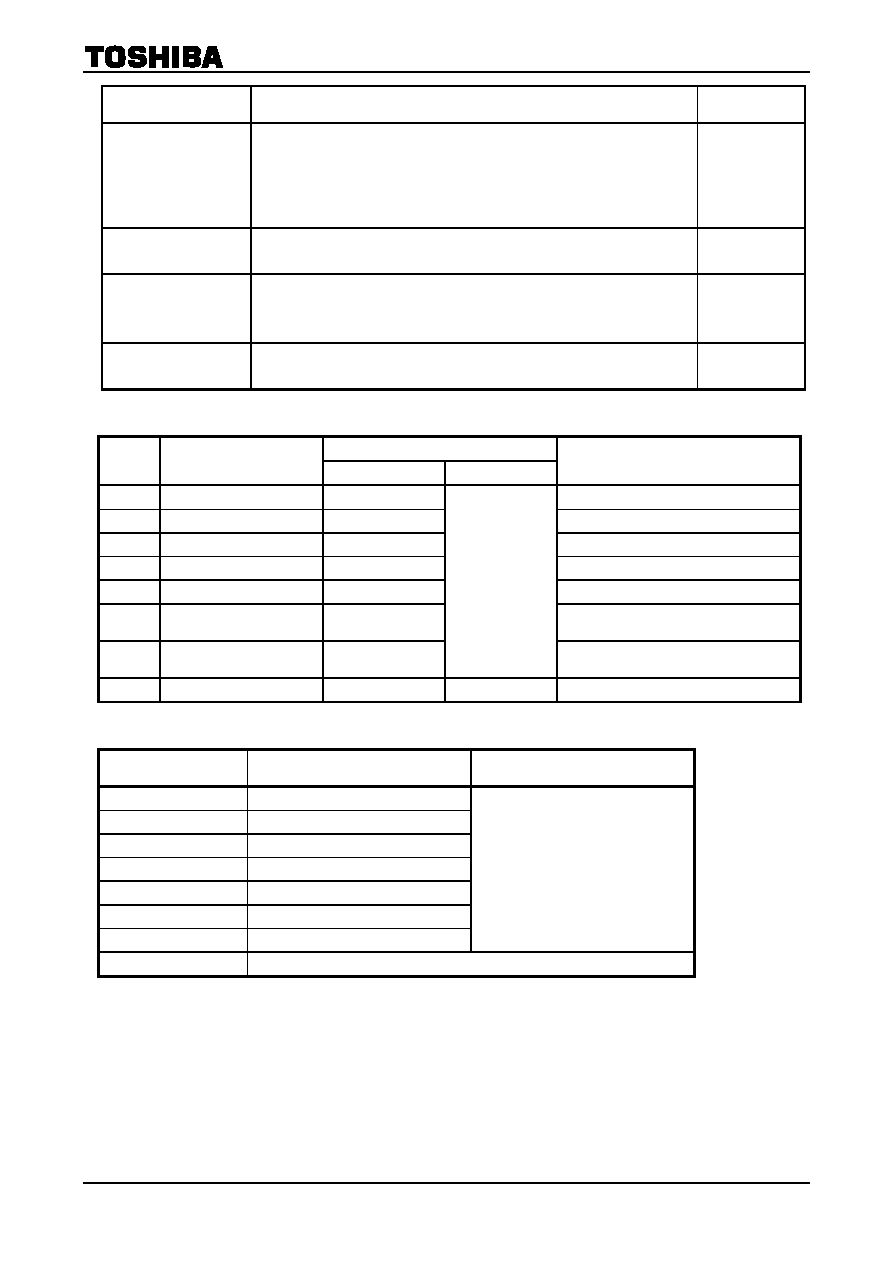

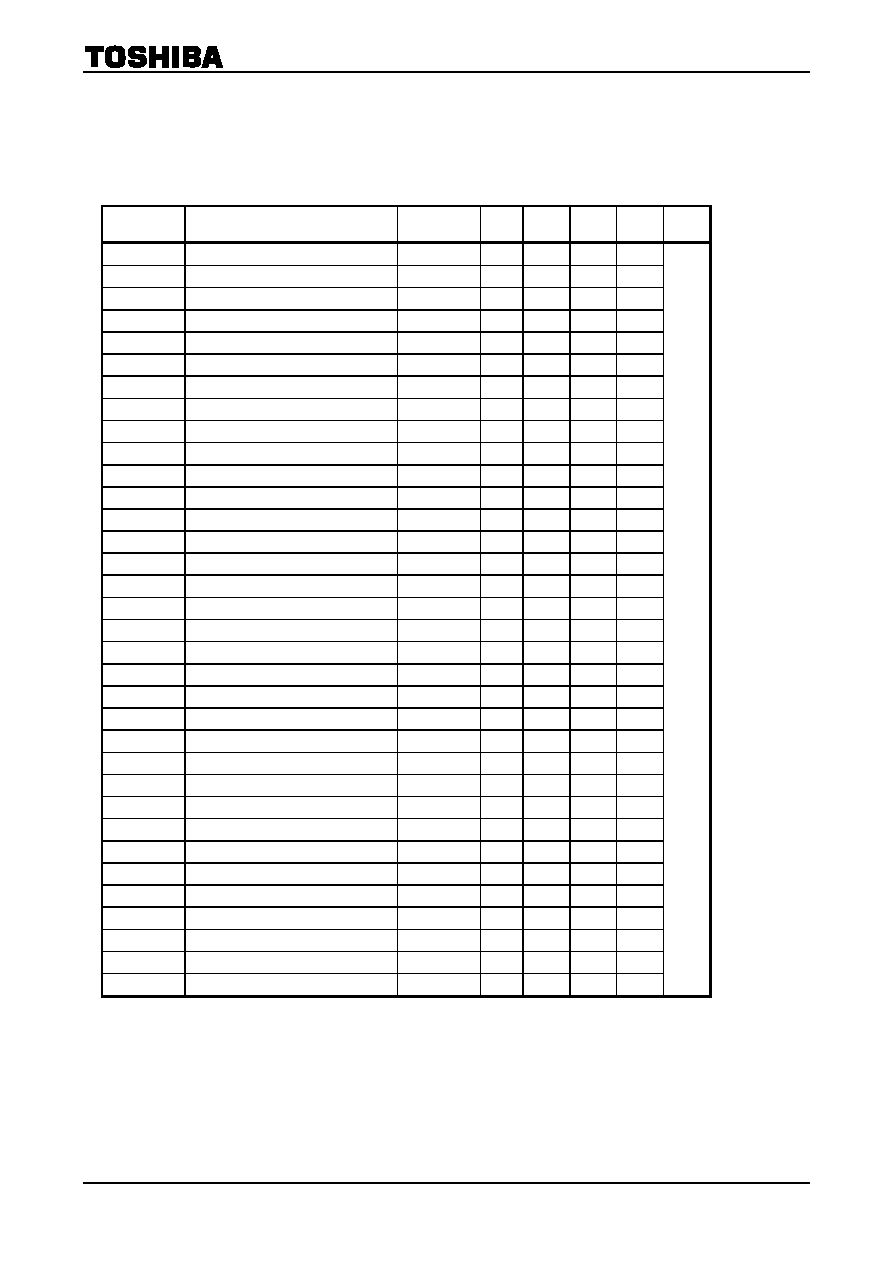

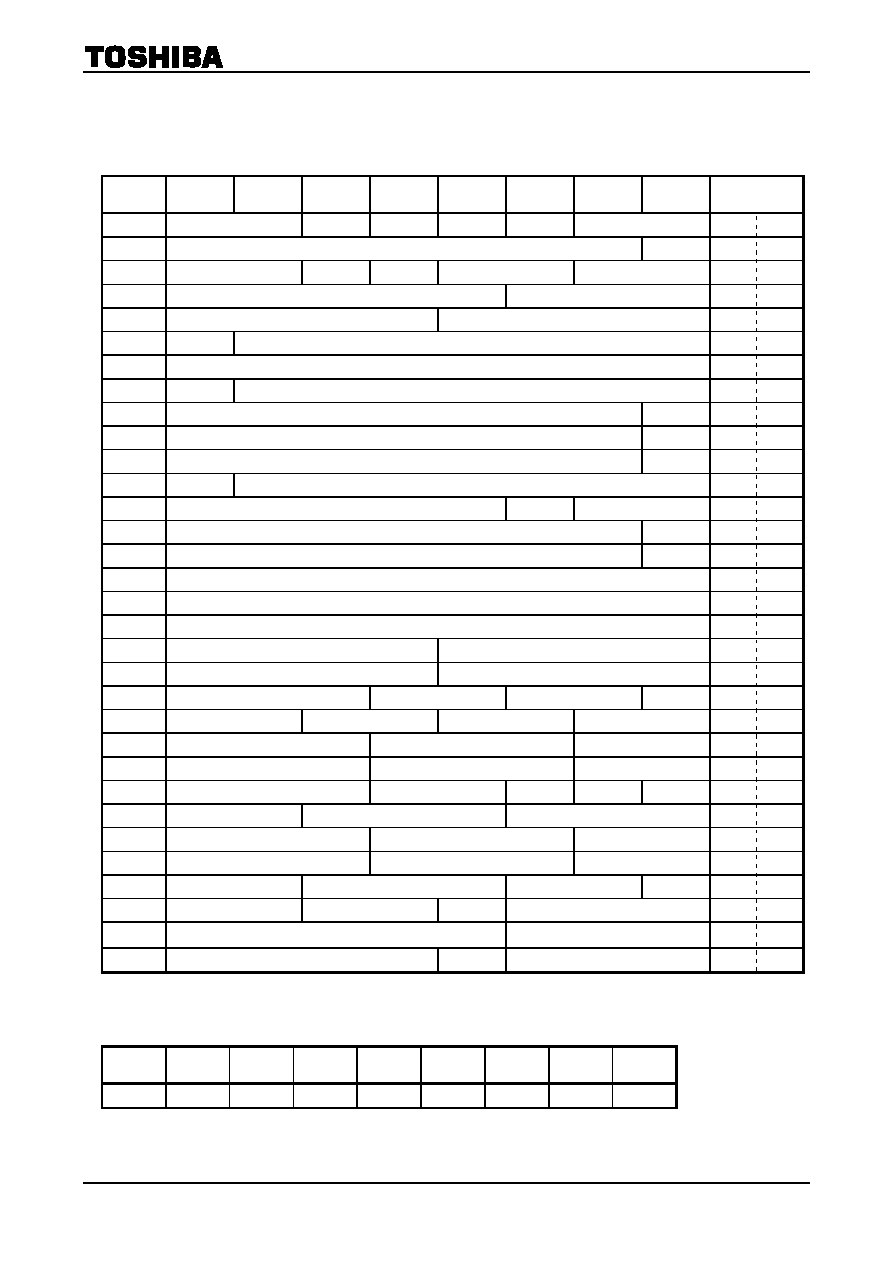

Bus Control Map

Write Mode

Slave Address: 88H

Sub-Add

D7 D6 D5 D4 D3 D2 D1 D0 Preset

00 H-FREQ

H-DUTY

YUV-SW

DAC1

DAC2

SYNC

INPUT-SW

1000

0000

01 HORIZONTAL

POSITION

CLP-PHS

1000

0000

02 ACB-MODE

SCP-SW

HBP-PHS

SYNC

SEP-LEVEL TEST 1000

0000

03 V-BLK

PHASE VERTICAL

FREQUENCY

1000

0000

04

COMPRESSION-BLK PHASE-1

COMPRESSION-BLK PHASE-2

1000

0000

05 P-MODE1

UNI-COLOR

1000

0000

06 BRIGHTNESS

1000

0000

07 OSD-ACL

COLOR

1000

0000

08 TINT

RGB-ACL

1000

0000

09 PICTURE

SHARPNESS YNR

1000

0000

0A RGB

BRIGHTNESS

DCRR-SW

1000

0000

0B HI

BRT

RGB

CONTRAST

1000

0000

0C

SUB CONTRAST

WPS

YUV INPUT MODE

1000

0000

0D DRIVE

GAIN1 DR-R

1000

0000

0E DRIVE

GAIN2

DR-B/G

1000

0000

0F

R CUT OFF

1000

0000

10

G CUT OFF

1000

0000

11 B

CUT

OFF

1000

0000

12 R-Y/B-Y

GAIN

R-Y/B-Y

PHASE

1000

0000

13 G-Y/B-Y

GAIN

G-Y/B-Y

PHASE

1000

0000

14

COLOR SRT GAIN

C-SRT FREQ

COLOR

CLT

1000

0000

15

C.D.E.

Y/C GAIN COMP1

Y/C GAIN COMP2

FRESH-COLOR

1000

0000

16

VSM PHASE

VSM GAIN

APACON PEAK FREQ 1000

0000

17

DC REST POINT

DC REST RATE

DC REST LIMIT

1000

0000

18

BLACK STRETCH POINT

APL VS BSP

B.L.C.

B.D.L

BS-ARE

1000

0000

19 SHR-TRACKING

WPL-LEVEL

WPL-FREQ

1000

0000

1A

DYNAMIC ABL POINT

DYNAMIC ABL GAIN

P-MODE2

1000

0000

1B

ABL POINT

ABL GAIN

RGB OUT MODE

1000

0000

1C DYNC

-POINT DYNC

GAIN VS DARK AREA

STATIC

-GAIN Y-OUT

1000 0000

1D OSD

BRIGHT

OSD

CONTRAST

Y/C-DL1

APACON

WPL

1000

0000

1E

Y DETAIL CONTROL

WP BLUE POINT

1000 0000

1F

Y GROUP DELAY CORRECTION

Y/C-DL2

WP BLUE GAIN

1000

0000

Read Mode

Slave Address: 89H

D7 D6 D5 D4 D3 D2 D1 D0

0 POR

IK-IN

RGB-OUT

YUV-IN

H-OUT

VP-OUT

RGB-IN

SYNC-IN

TA1316AN

2002-10-04

24

Bus Control Functions

Write Mode

Parameter Explanation

Preset

H-FREQUENCY

Selects horizontal oscillation frequency.

00: 15.75 kHz, 01: 31.5 kHz, 10: 33.75 kHz, 11: 45 kHz

Control by pin 22 has priority over BUS control. When this IC will be used on CRT,

the frequency of H-out should be controlled by pin 22.

33.75 kHz

H-DUTY

Switches horizontal output duty.

0: 41%, 1: 47%

41%

YUV-SW

Switches YUV input.

0: INPUT-1 (Y1/C

b1

/C

r1

), 1: INPUT-2 (Y2/C

b2

/C

r2

)

INPUT-1

DAC 1

Switches DAC control output.

Don't use this function

Open

DAC 2

Switches DAC control output.

0: On (low), 1: Open (high)

When TEST

=

00, controls 1-bit DAC when output is open-collector.

When TEST

=

01, outputs ACB reference pulse from pin 36.

On

SYNC INPUT-SW

Selects sync input.

00: Selects HD1/VD1 input.

01: Selects HD2/VD2 input.

10/11: Selects SYNC input.

HD/VD1

HORIZONTAL

POSITION

Adjusts horizontal picture phase.

0000000 (

-

10.5%)~1111111 (

+

10.5%)

(Note) When H-POSITION will be changed, VP width (pin 27) will change.

Center

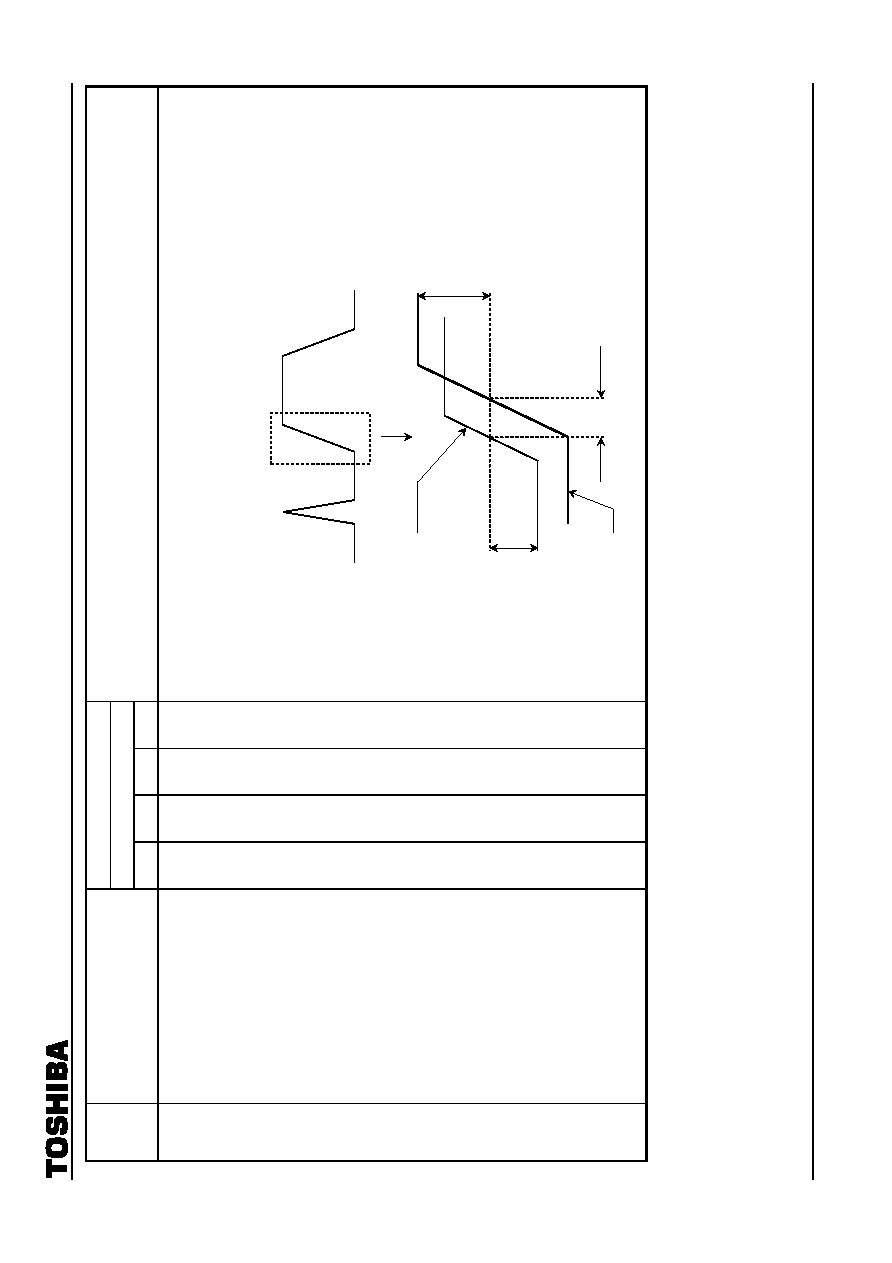

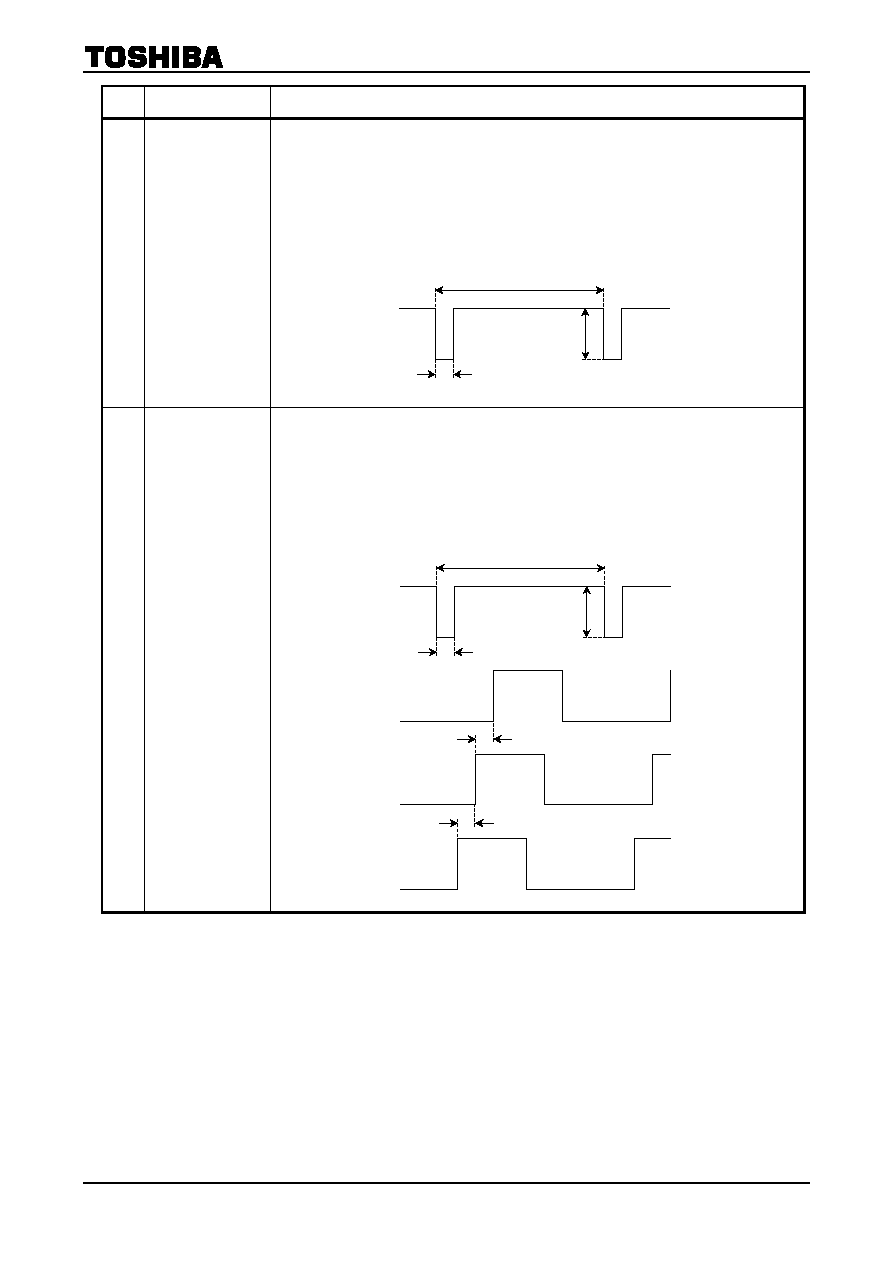

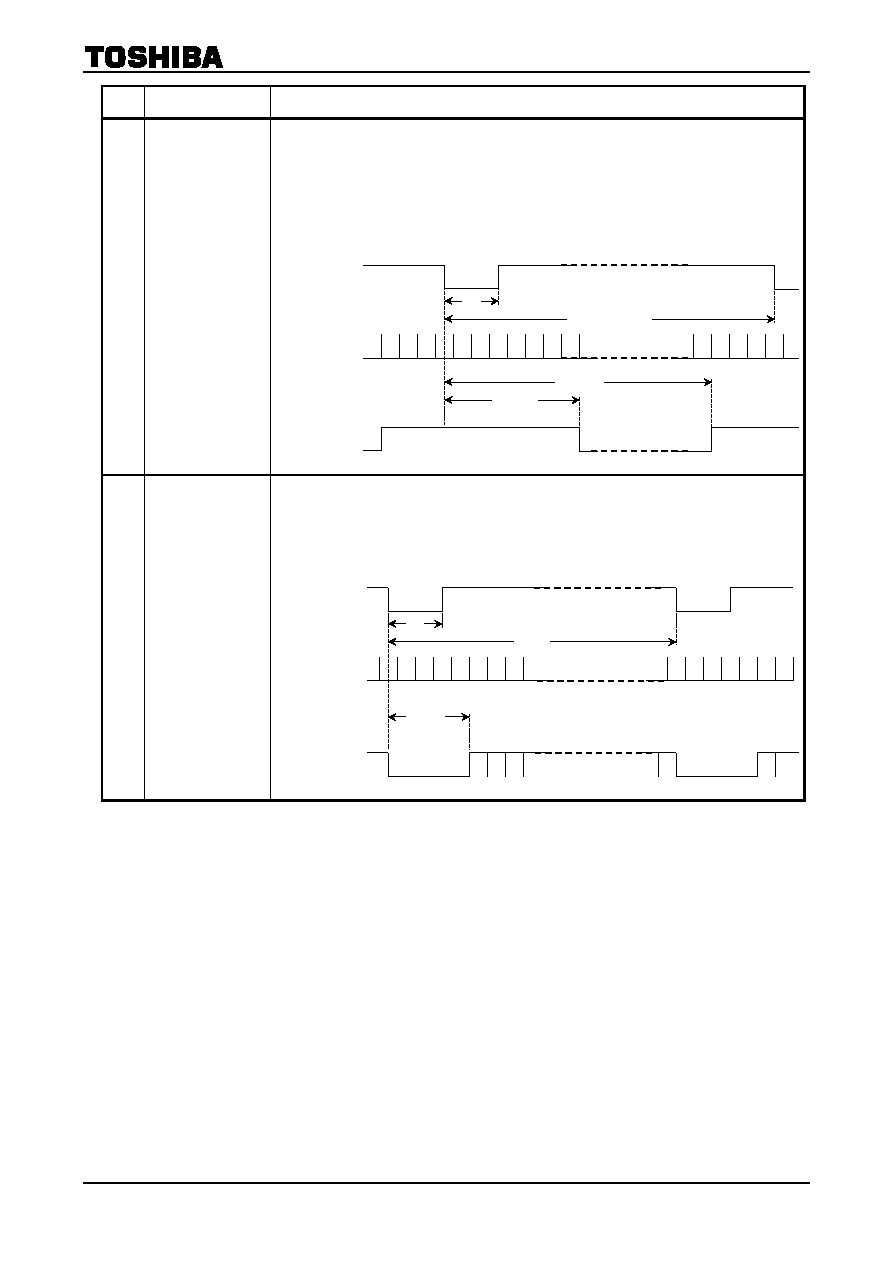

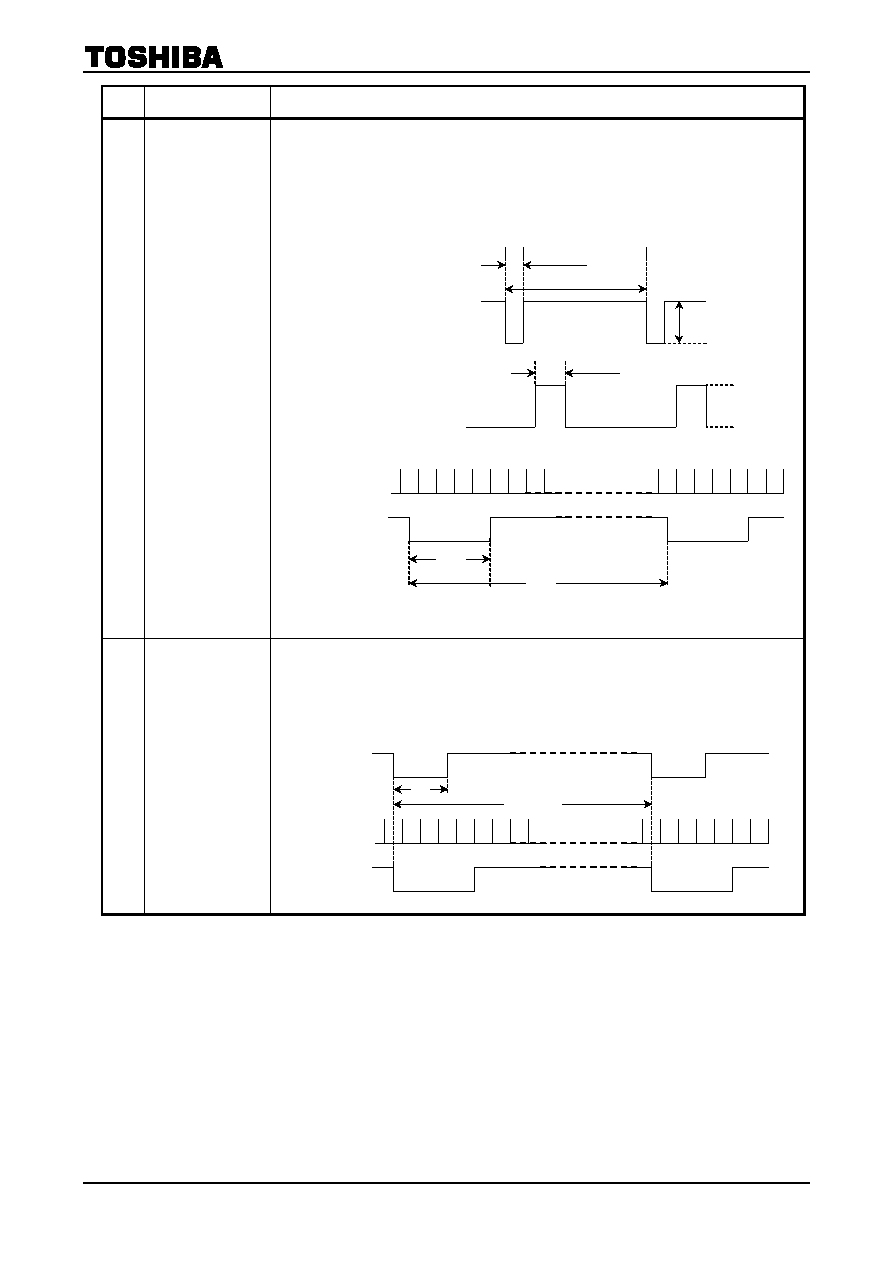

CLP-PHS

Switches clamp pulse phase.

0: 0.7-

µ

s (2.5%) width with 1.1-

µ

s (3.8%) delay from HD stop phase

1: 0.7-

µ

s (2.4%) width with 0.2-

µ

s (0.7%) delay from HD stop phase

While quiescent, 0.8-

µ

s (2.7%) width with 1.2-

µ

s (4.2%) delay from FBP start

phase

Also switches CP phase of SCP-OUT (pin 18).

1.1-

µ

s delay

ACB MODE

Sets ACB mode. Selects reference level for convergence.

00: ACB off (cutoff BUS control), 01: ACB on (5 IRE),

10: ACB on (10 IRE), 11: ACB on (20 IRE)

ACB on (10 IRE)

SCP-SW

Switches SCP (sandcastle pulse) mode.

0: Internal mode, 1: External input mode

Also switches SCP-OUT (pin 18).

(Note) Don't use H-BPP for the timing pulse, because H-BPP width of internal

mode will be changed by the temperature.

Inside IC

HBP-PHS

Switches horizontal black peak detection pulse phase.

0:

±

6.3% of FBP, 1:

±

3.5% of FBP

6.3% width

SYNC SEP-LEVEL

Selects SYNC separation level.

00: 8.5%, 01: 20%, 10: 30%, 11: 40%

min

TEST

Test mode

When TEST

=

00, controls 1-bit DAC when output is open-collector.

When TEST

=

01, outputs H-SYNC from pin 28 and ACB reference pulse from pin

36.

Do not use TEST

=

10/11 because this is used for IC Shipment Test mode.

00

TA1316AN

2002-10-04

25

Parameter Explanation

Preset

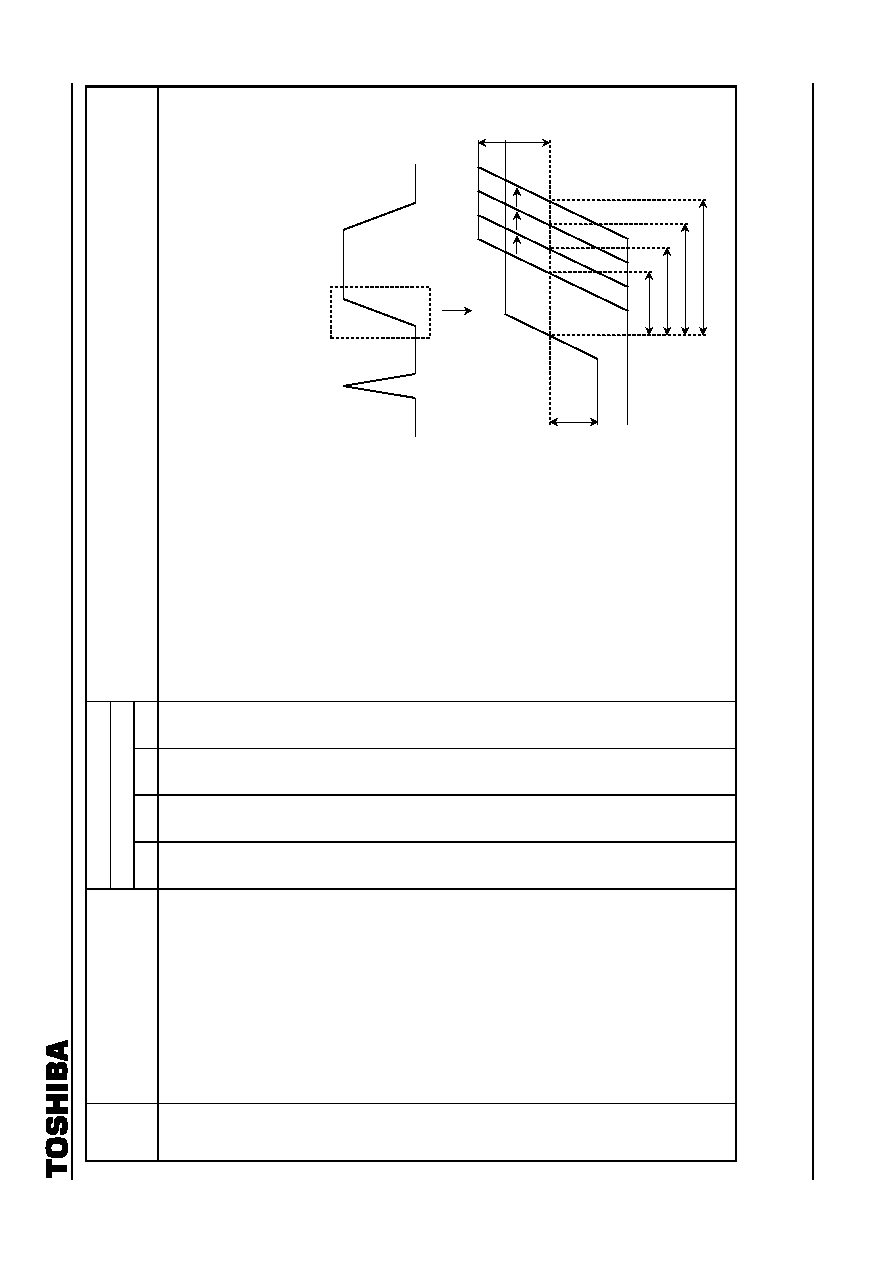

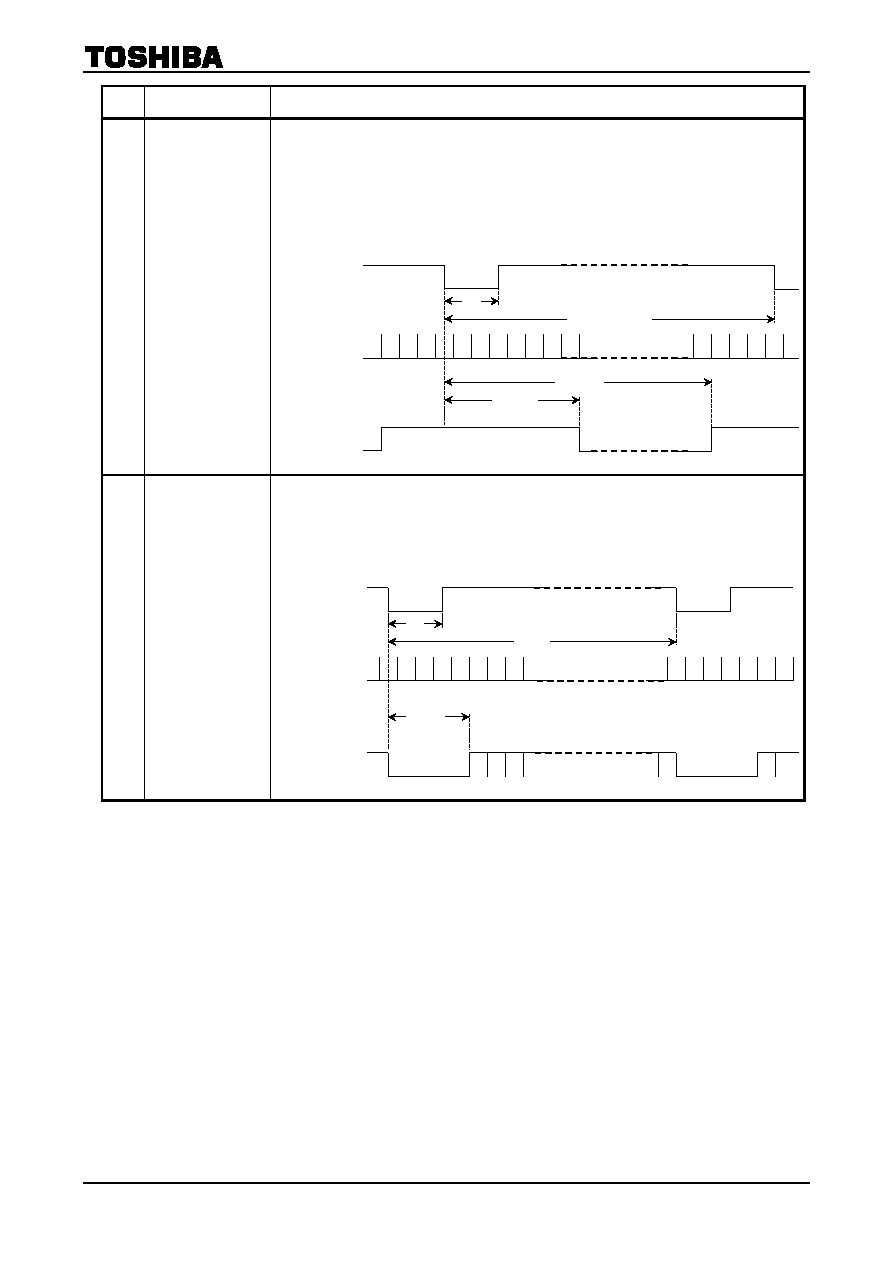

V-BLK PHASE

Adjusts vertical BLK stop phase.

00000 (16H) ~11110 (46H) (1 H/STEP),

11111: Internal V-BLK off

32 H

V-FREQUENCY

Vertical free-running frequency. Sets vertical pull-in range (Table 1).

1281 H

COMPRESSION-BLK

PHASE-1/2

Adjusts compression BLK phase. Adjusts BLK at top and bottom (Table 2).

Off

P-MODE1/2

Selects picture mode. Selects between picture mute, half-tone, blue background,

and Y mute (Table 3).

P-MUTE 1

UNI-COLOR

Adjusts unicolor.

0000000 (

-

16.5dB) ~111 (0dB)

min

BRIGHTNESS

Adjusts brightness.

00000000 (

-

40 IRE) ~11111111 (

+

40 IRE)

Center

OSD-ACL

Turns OSD-ACL on/off.

0: Off, 1: On

On

COLOR

Adjusts color.

0000000: Color mute,

0000001 (

-

20dB or more) ~1111111 (

+

4.6dB)

C-MUTE

TINT

Adjusts tint.

0000000 (

-

32 deg) ~1111111 (

+

32 deg)

Center

RGB-ACL

Switches analog RGB-ACL sensitivity.

0:

-

6dB, 1: Normal

-

6 dB

PICTURE-SHARPNESS

Adjusts sharpness.

0000000 (

-

10dB or more) ~1111111 (

+

17dB (at peak FREQ) )

Center

YNR

YNR: Turns luminance (Y) noise reduction (NR) on/off.

0: Off, 1: On

Lower two bits of PICTURE-SHARPNESS (09-D2/D1)

=

00: Trap (at peak FREQ)

=

11: Flat

YNR level is controlled by lower two bits (09-D2) of PICTURE-SHARPNESS.

DL-APACON gain control by PICTURE-SHARPNESS is invalid.

Off

RGB-BRIGHTNESS

Adjusts RGB brightness.

0000000 (

-

20 IRE) ~1111111 (

+

20 IRE)

Center

DCRR-SW

Switches DC restoration rate.

0: 100% or more, 1: 100% or less

100% or more

HI BRT

Turns high bright color on/off.

0: Off, 1: On

On

RGB-CONTRAST

Adjusts RGB contrast.

0000000 (

-

16.5dB) ~1111111 (0dB)

min

SUB-CONTRAST

Adjusts sub-contrast.

00000 (

-

3.5dB) ~11111 (

+

2.6dB)

Center

WPS

Adjusts WPS level.

0: 110 IRE 1: 130 IRE

110 IRE

YUV INPUT MODE

Selects Y/color difference signal input mode.

00: Y/Cb/Cr, 01: Y/Pb/Pr, 10: Through, 11: Y/U/V (TA1270)

Control by pin takes priority at 00 and 01 (table 4).

(Ref.) Y/Cb/Cr: ITU-R BT 601

Y/Pb/Pr: ITU-R BT 709 (1125/60/2:1)

Y/Cb/Cr

TA1316AN

2002-10-04

26

Parameter Explanation

Preset

DRIVE GAIN1/2

Adjusts drive gain 1 and drive gain 2.

0000000 (

-

5dB) ~1111111 (

+

3dB)

Center

DR-R

DR-B/G

Switches reference RGB drive gain (Table 5).

R

R/G/B CUT OFF

Adjusts R/G/B cutoff.

1) RGB-OUT when ACB off

00000000 (1.9 V) ~11111111 (2.9 V)

2)SENS-IN when ACB on

00000000 (0.5 V

p-p

) ~11111111 (1.5 V

p-p

)

Center

R-Y/B-Y GAIN

Adjusts R-Y/B-Y relative amplitude.

0000 (0.54) ~1111 (0.85)

Center

R-Y/B-Y PHASE

Adjusts R-Y/B-Y relative phase.

0000 (90 deg) ~1111 (111.5 deg)

min

G-Y/B-Y GAIN

Adjusts G-Y/B-Y relative amplitude.

0000 (0.28) ~1111 (0.38)

Center

G-Y/B-Y PHASE

Adjusts G-Y/B-Y relative phase.

0000 (232 deg) ~1111 (256 deg)

min

COLOR SRT GAIN

Adjusts color SRT gain.

000 (min) ~111 (max)

Center

C-SRT-FREQ

Selects color SRT peak frequency.

00: 4.5 MHz, 01: 5.8 MHz, 10: 8.5 MHz, 11: Off

4.3 MHz

COLOR

Selects color

correction point.

00: Off, 01: 0.23 V

p-p

, 10: 0.40 V

p-p

, 11: 0.58 V

p-p

Off

CLT

Switches color limiter level.

0: 1.65 V

p-p

, 1: 2 V

p-p

1.65 V

p-p

CDE

Adjusts color detail enhancer.

00: min 11: max

Center

Y/C GAIN COMP1/2

Selects dynamic Y/C compensation.

COMP1, 00: Off, 01: min, 10: mid, 11: max

COMP2, 00: Off, 01: min, 10: mid, 11: max

All off

FRESH-COLOR

Selects flesh color.

00: Off, 01:

±

33.7 deg, Normal,

10:

±

9.5 deg, High, 11:

±

9.5 deg, Normal

Off

VSM-PHASE

Adjusts VSM phase.

000 (

-

37.5 ns) ~101 (normal) ~111 (

+

15 ns)

-

7.5 ns

VSM GAIN

Adjusts VSM gain.

000: OFF, 001:

+

3 dB, 111:

+

19 dB

Off

APACON PEAK f

0

Selects APACON peak frequency.

00: 13.5 MHz, 01: 9.5 MHz, 10: 7.3 MHz, 11: 4.7 MHz

13.5 MHz

DC REST POINT

DC restoration point

000: 0%, 111: 51%

Center

DC REST RATE

Adjusts DC restoration rate.

000 (100%) ~111 (135% (65%) )

100%

DC REST LIMIT

Selects DC restoration limit point.

00: 57%, 01: 71

, 10: 78%, 11: 78%

min

TA1316AN

2002-10-04

27

Parameter Explanation

Preset

BLACK STRETCH POINT

Adjusts black stretch point 1.

000: OFF, 001 (34 IRE) ~111 (53 IRE)

Center

APL VS BSP

Adjusts black stretch point 2.

00 (0 IRE) ~11 (24 IRE) up

0 IRE

B.L.C

Turns black level automatic correction on/off.

Max: 8.5 IRE, black stretch has priority.

0: Off, 1: On

Off

B.D.L.

Switches black detection level.

0: 3 IRE, 1: 0 IRE

3 IRE

BS-ARE

Turns black stretch area on/off.

0: On, 1: Off

On

SHR-TRACKING

SHR tracking (adjusts SRT component gain.)

00 (SRT-GAIN max) ~11 (SRT-GAIN min)

Center

WPL-LEVEL

Adjusts white letter improvement amplitude.

000: min 111: max

min

WPL-FREQ

Adjusts white letter improvement start frequency.

000 (5 MHz) ~111 (16 MHz)

5 MHz

DYNAMIC ABL POINT

Adjusts dynamic ABL detection voltage.

000 (min) ~111 (max)

Center

DYNAMIC ABL GAIN

Adjusts dynamic ABL sensitivity.

000 (min) ~111 (max)

min

ABL POINT

Adjusts ABL detection voltage.

000 (min) ~111 (max)

Center

ABL GAIN

Adjusts ABL sensitivity.

000 (min) ~111 (max)

min

RGB-OUT MODE

Switches RGB output mode (switch for RGB output mode for test and adjustment).

00: Normal, 01: R only, 10: G only, 11: B only

Normal

DYNC

-POINT

Switches dynamic Y

point.

00: 20 IRE, 01: 21.5 IRE, 10: 23.5 IRE, 11: 25 IRE

23.5 IRE

DYNC

GAIN VS DARK

AREA

Turns dynamic Y

gain VS dark area on/off.

000 (min) ~

111 (max (when 25 IRE or below is 25% or more of area ratio,

+

3dB) )

min

STATIC

-GAIN

Turns static Y

dark area gain on/off.

00: Off (0dB) 11: max (1.5dB, at this time, DYNC

gain is

+

1.5dB max)

Off

Y-out

Turns Y-out

on/off.

0: Off, 1: On

Off

OSD BRIGHT

Adjusts OSD brightness.

00: 5 IRE, 01: 0 IRE, 10:

-

5 IRE, 11:

-

10 IRE

-

5 IRE

OSD-CONTRAST

Adjusts OSD contrast.

00 (min (

-

9.5dB) ) ~11 (max (0dB) )

min

Y/C DL1/2

Adjust Y/C relative phase: Y phase before RGB matrix is changed.

Y/C DL2

=

0 and Y/C DL1

=

0:

-

10 ns, Y/C DL2

=

0 and Y/C DL1

=

1:

-

5 ns

Y/C DL2

=

1 and Y/C DL1

=

0: 0 ns, Y/C DL2

=

1 and Y/C DL1

=

1:

+

5 ns

-

10 ns

APACON WPL

Adjusts APACON white peak limiter.

000 (Off) ~111 (Maximum effect of positive limiter)

Off

TA1316AN

2002-10-04

28

Parameter Explanation

Preset

Y DETAIL CONTROL

Controls Y detail: Adjusts differential signal for frequency other than picture

sharpness.

00000 (min (trap) ) ~11111 (max (

+

6dB) )

Peak frequency linked to APACON PEAK FREQ

00: 5.5 MHz, 01: 3.7 MHz, 10: 14.5 MHz, 11: 10 MHz

Center

WP BLUE POINT

Adjusts white peak blue point.

000 (60 IRE) ~111 (112 IRE)

min

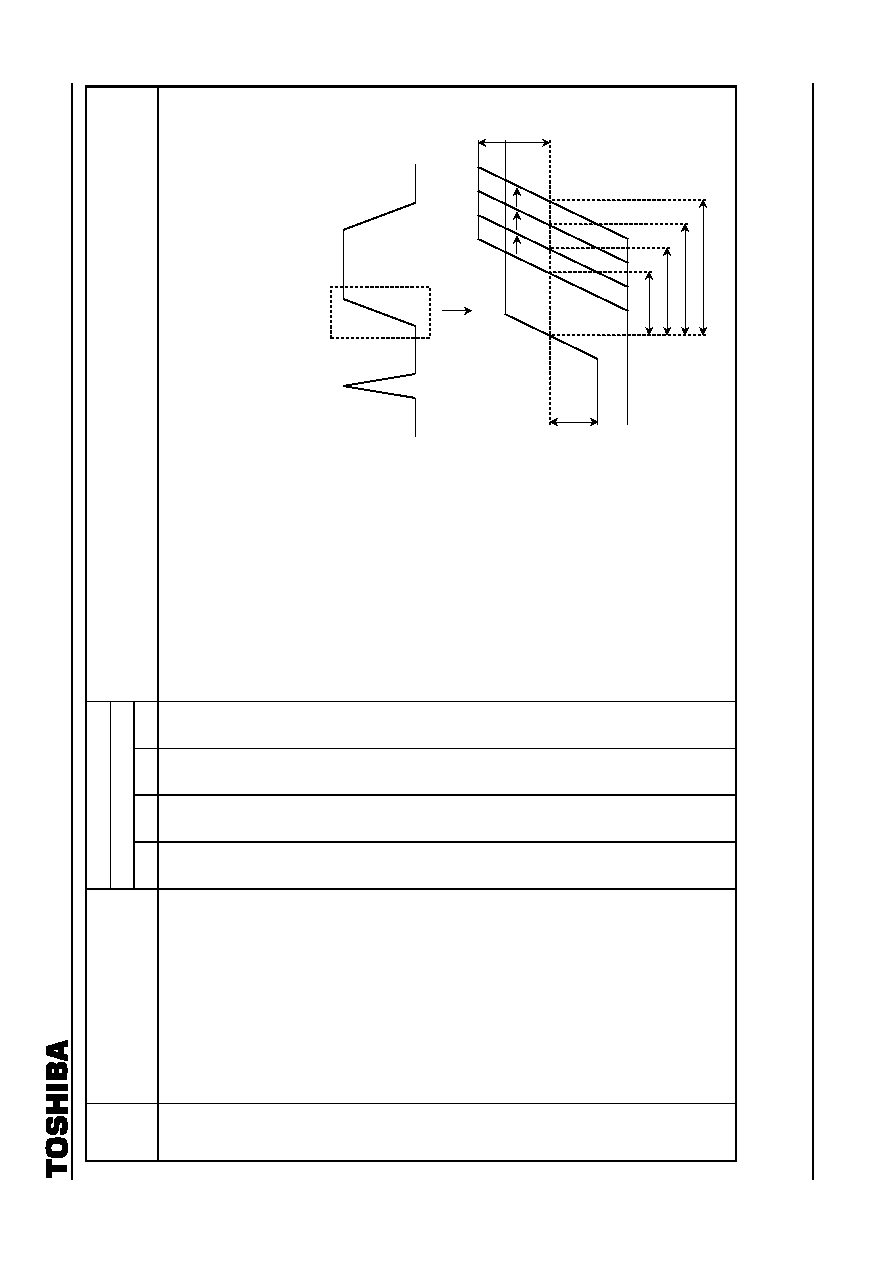

Y-GROUP DELAY

CORRECTION

Corrects Y group delay.

0000: Decreases preshoot gain (increases overshoot gain).

1111: Decreases overshoot gain (increases preshoot gain).

Center

WP BLUE GAIN

Adjusts white peak blue gain.

000 (min (

+

2.3 dB) ) ~111 (max (

+

10 dB) )

min

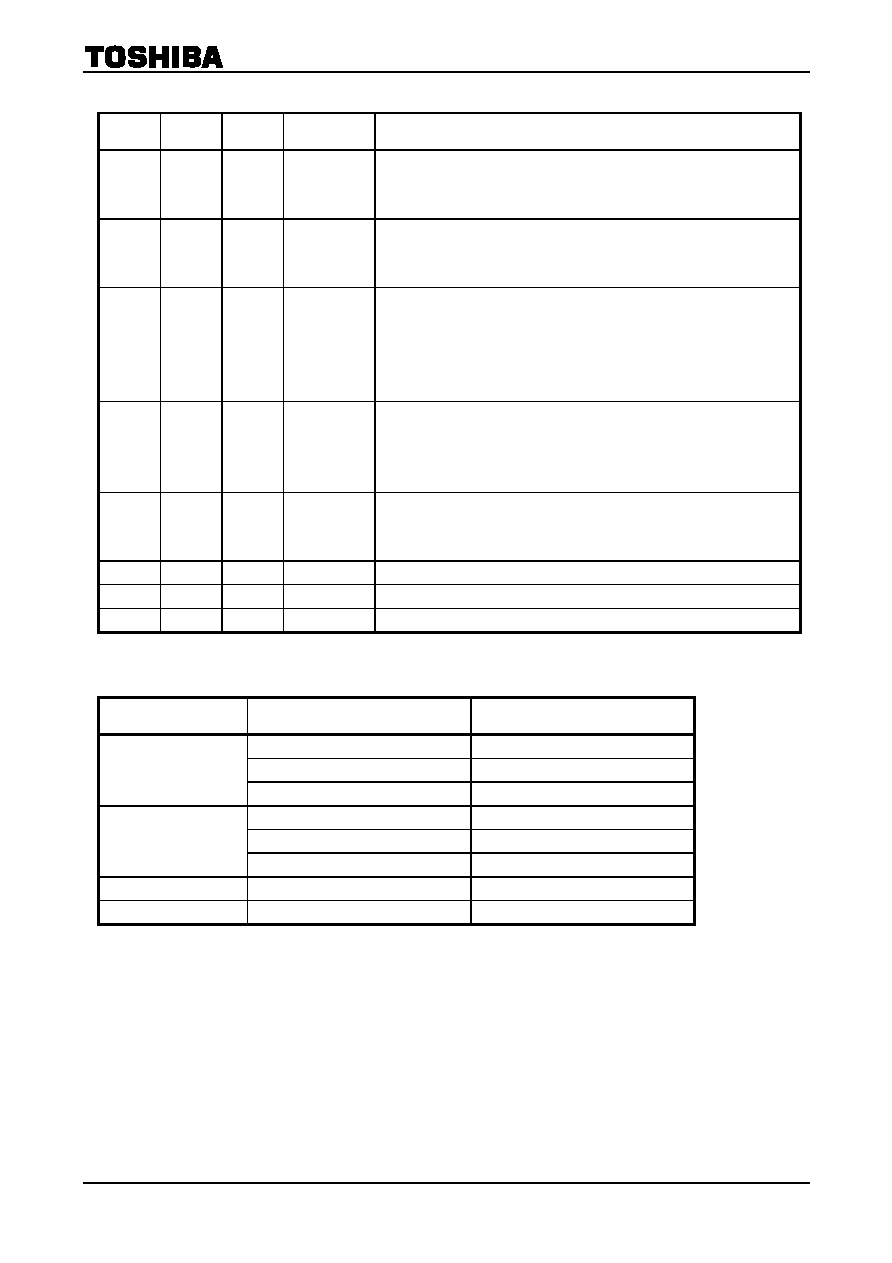

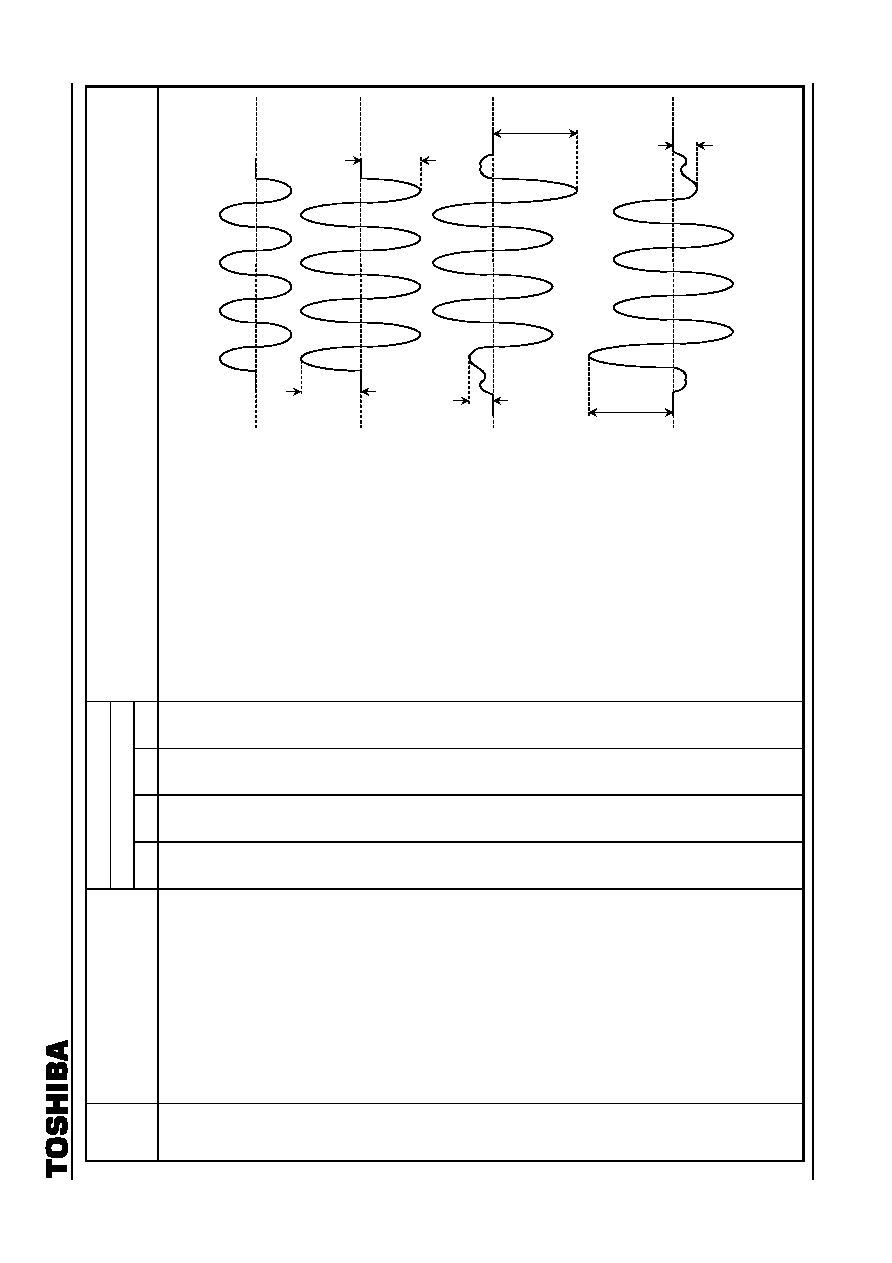

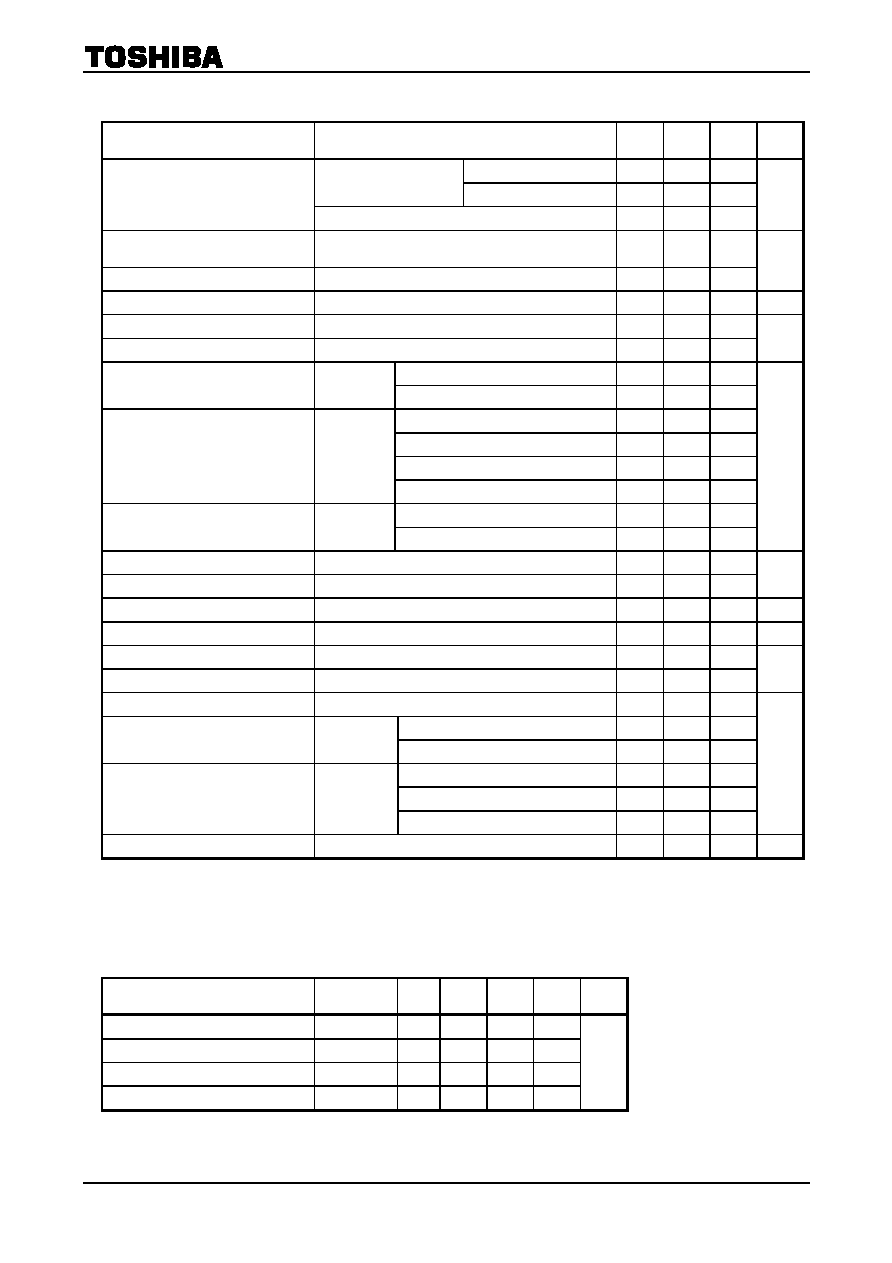

Table 1: Vertical Frequency

V-BPP

Data V

PULL-IN

Range

Start Phase

Stop Phase

Format/V-FREQUENCY, H-FREQUENCY

000 48~1281H

1100H

1125P/30

Hz

(33.75

kHz)

001 48~849H

730H

750P/60

Hz

(45

kHz)

010

48~725H

600H

625P/50 Hz (31.5 kHz)

011

48~660H

545H

1125I/60 Hz (33.75 kHz)

100

48~613H

500H

525P/60 Hz (31.5 kHz)

101 48~363H

290H

PAL/SECAM/50 Hz (15.625 kHz),

100 Hz (31.5 kHz)

110 48~307H

240H

V-BLK P.

(C.BLK P.)

+

20 H

NTSC/60 Hz (15.734 kHz),

120 Hz (31.5 kHz)

111 VP-OUT

HI

Table 2: Compression-BLK Phase

V-FREQUENCY

PHASE-1 (start phase)

PHASE-2 (stop phase)

000 1088H~1118H

001 720H~750H

010 592H~622H

011 528H~558H

100 488H~518H

101 280H~310H

110 224H~254H

50H~78H

(0000: C-BLK OFF)

111 C-BLK

OFF

TA1316AN

2002-10-04

29

Table 3: P-Mode

05-D7 1A-D1 1A-D0 MODE

Details

0 0 0

NORMAL

1

Can mute picture or half-tone main signal using Y

M

pin.

Can insert analog RGB-IN using Ys3; OSD-IN using Ys1/Ys2.

Analog RGB-IN

>

P-Mute

0 0 1 Y-MUTE

Mutes main signal Y in whole picture using BUS.

Can insert analog RGB-IN using Ys3; OSD-IN using Ys1/Ys2.

Analog RGB-IN

>

P-Mute

0 1 0 Y

M

1

Half-tones main signal in whole picture using BUS.

Can insert P-Mute using Y

M

pin.

Can insert analog RGB-IN using Ys3.

Blends OSD-IN with main H/T signal using Ys1/Ys2.

Analog RGB-IN

>

P-Mute

0 1 1 BB

Blue-backs main signal using BUS.

Can insert P-Mute using Y

M

pin.

Can insert analog RGB-IN using Ys3; OSD-IN using Ys1/Ys2.

Analog RGB-IN

>

P-Mute

1 0 0

P-MUTE

1

Mutes main signal in whole picture using BUS.

Can insert analog RGB-IN using Ys3; OSD-IN using Ys1/Ys2.

Analog RGB-IN

>

P-Mute

1 0 1 Y

M

2 Cannot

be

used.

1 1 0

P-MUTE

2

Cannot

be

used.

1 1 1

NORMAL

2

Cannot

be

used.

Output priority: main signal < BB < P-MUTE < RGB-IN < OSD-IN

Table 4: YUV INPUT MODE

YUV INPUT MODE

Pin 7

MATRIX

LOW YCbCr

Internal YUV

HIGH YPbPr

Internal YUV

00

OPEN YCbCr

Internal YUV

LOW YCbCr

Internal YUV

HIGH YPbPr

Internal YUV

01

OPEN YPbPr

Internal YUV

10

Through

11

YUV

Internal YUV

TA1316AN

2002-10-04

30

Table 5: DR-R, DR-B/G

0D-D0

0E-D0

Reference Axis

Drive Gain1

Drive Gain2

0 0

R

G

B

0 1

R

G

B

1 0

G

R

B

1 1

B

G

R

Read Mode

Parameter Explanation

POR

Power-on reset

0: Register preset, 1: Normal

After power-on, 0 is read on first read; 1 on subsequent reads.

IK-IN

IK input detection: detects input to pin 45.

0: NG (no input), 1: OK (input)

RGB-OUT

RGB-OUT self-check result: detects output from pins 41, 42 and 43.

0: NG (no output), 1: OK (output)

Returns OK when signal is detected on all three outputs. If signals are small, does not return

OK.

YUV-IN

YUV-IN self-check result: detects input to pins 3, 4 and 5 or pins 8, 9 and 10.

0: NG (no input), 1: OK (input)

Returns OK when AC signal is detected on all three inputs. If signals are small or are DC

voltage, does not return OK.

H-OUT

H-OUT self-check result: detects output from pin 26.

0: NG (no output), 1: OK (output)

VP-OUT

VP-OUT self-check result: detects output from pin 27.

0: NG (no output), 1: OK (output)

RGB-IN

RGB-IN self-check result: detects input to pins 33, 34 and 35.

0: NG (no input), 1: OK (input)

Returns OK when AC signal is detected on all three inputs. If signals are small or are DC

voltage, does not return OK.

SYNC-IN

SYNC-IN self-check result: detects input to pin 14.

0: NG (no input), 1: OK (input)

TA1316AN

2002-10-04

31

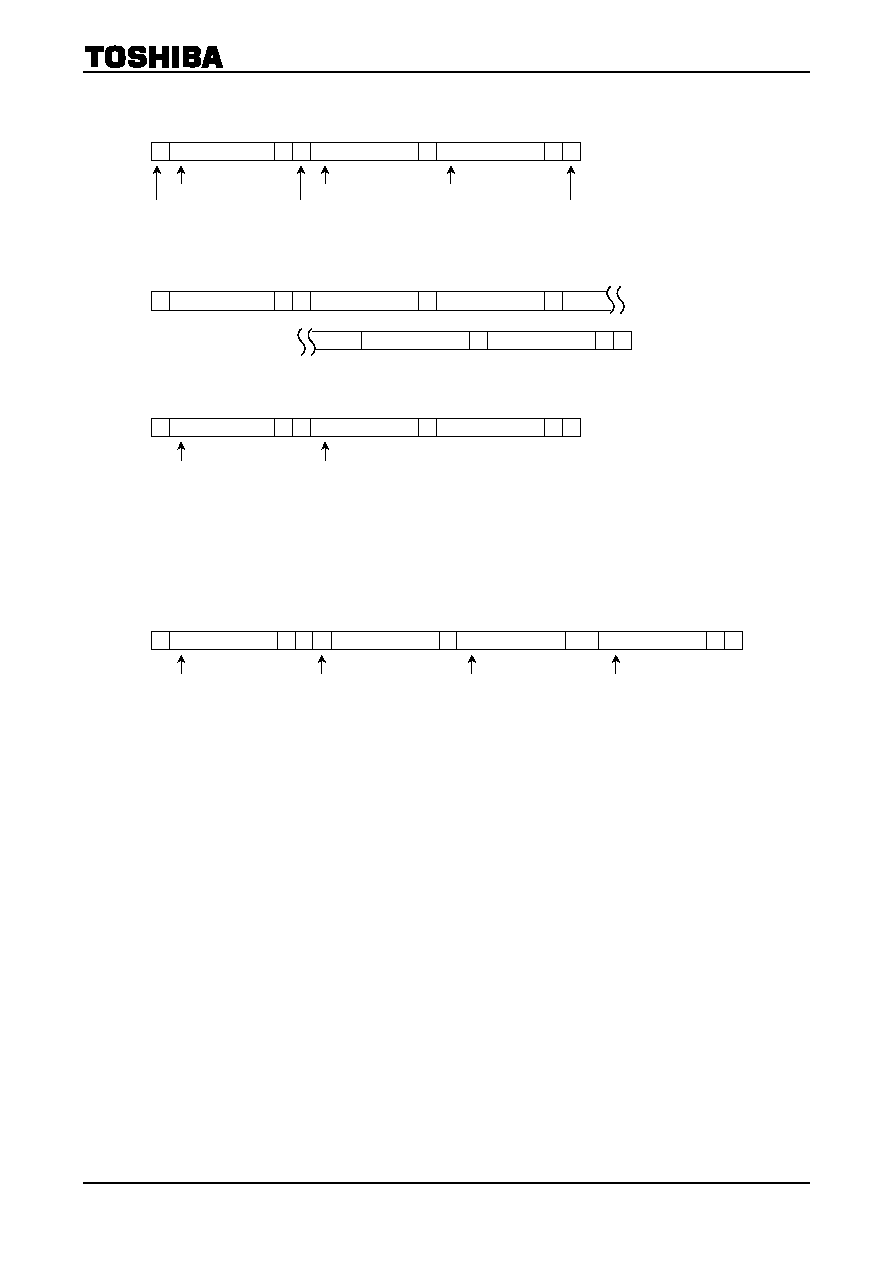

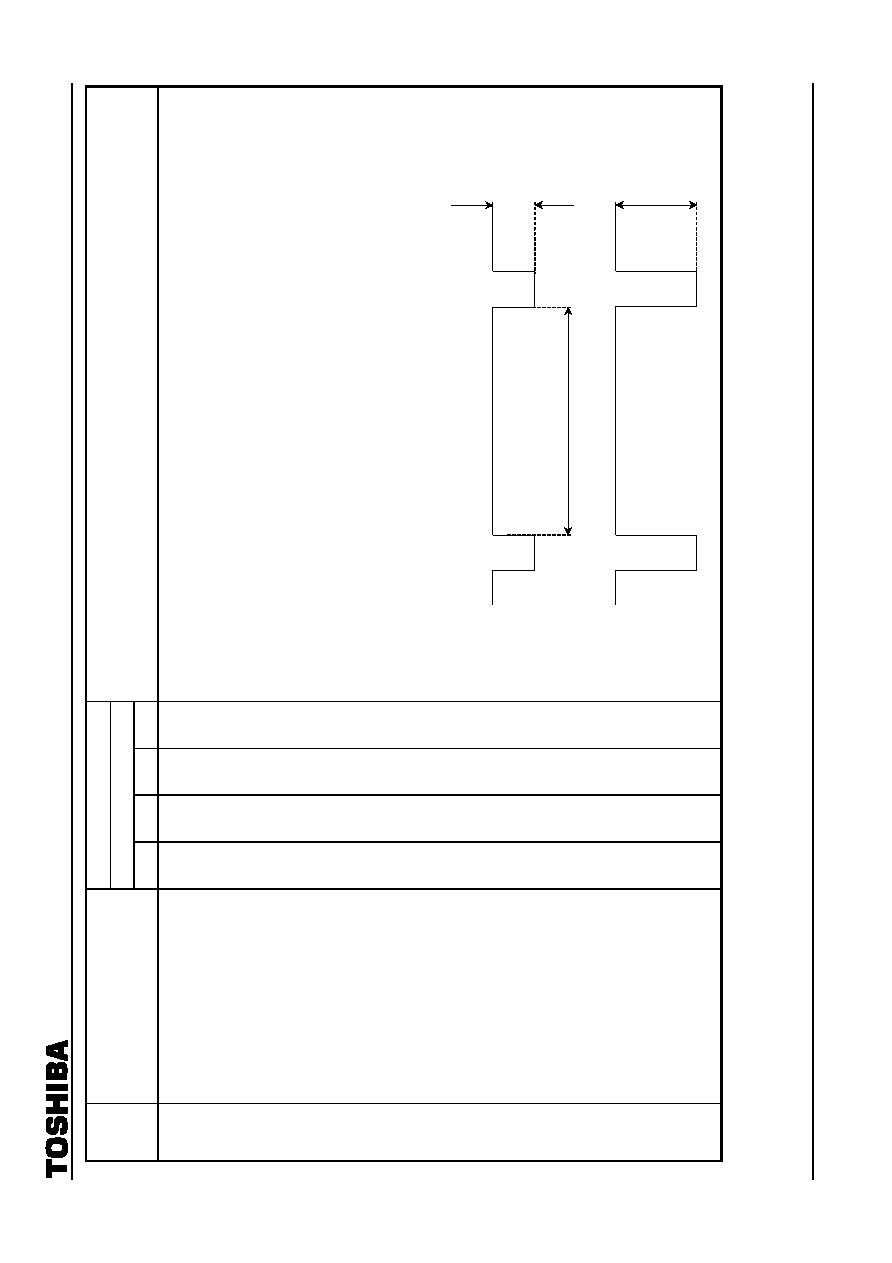

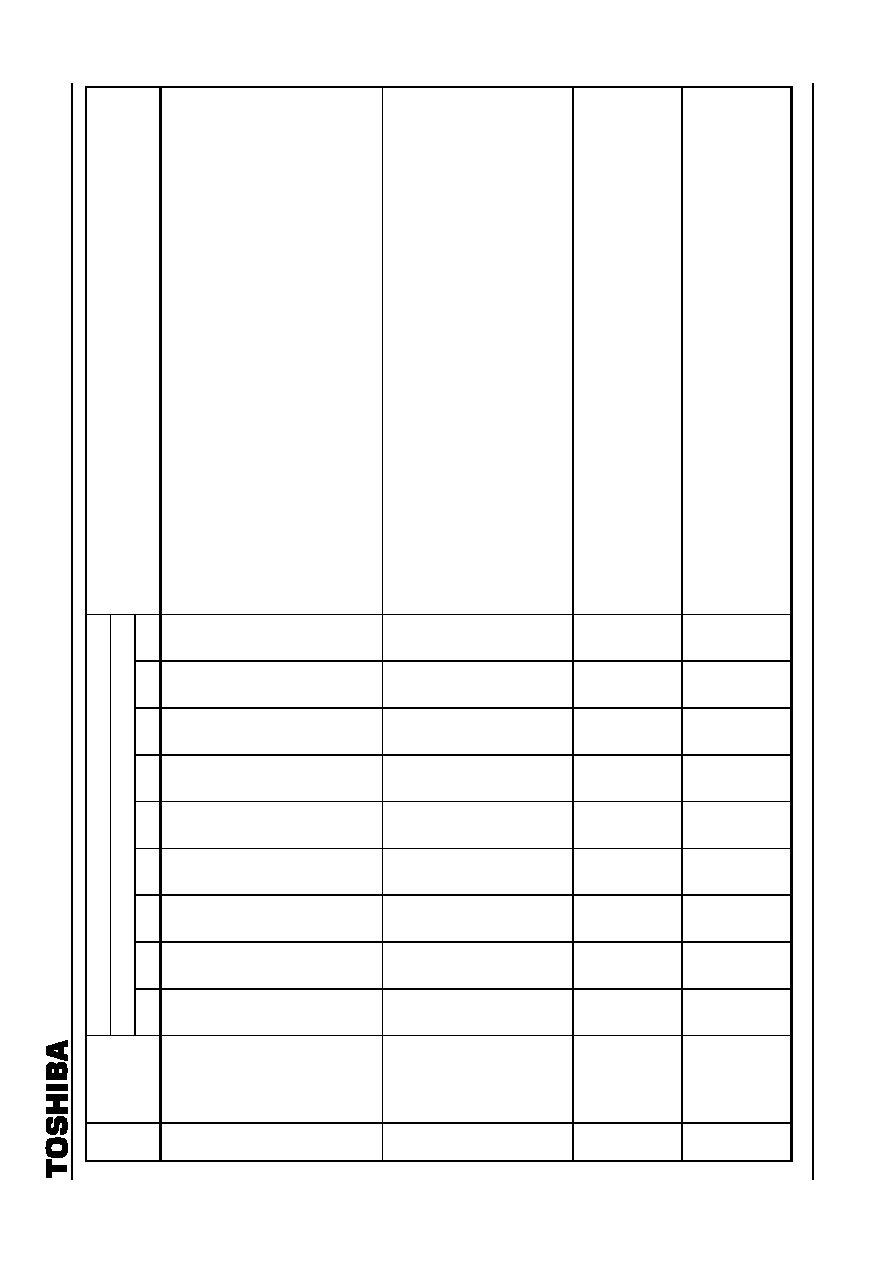

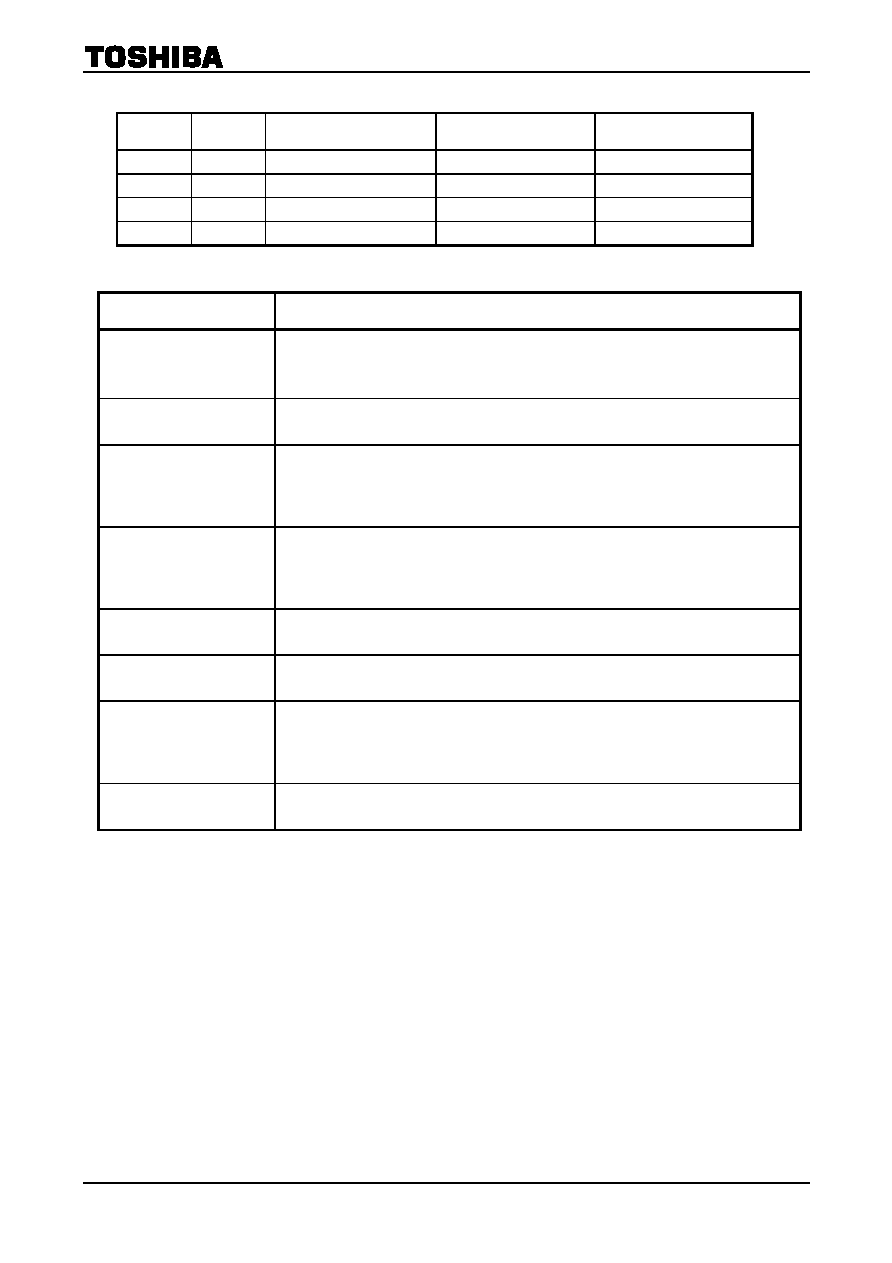

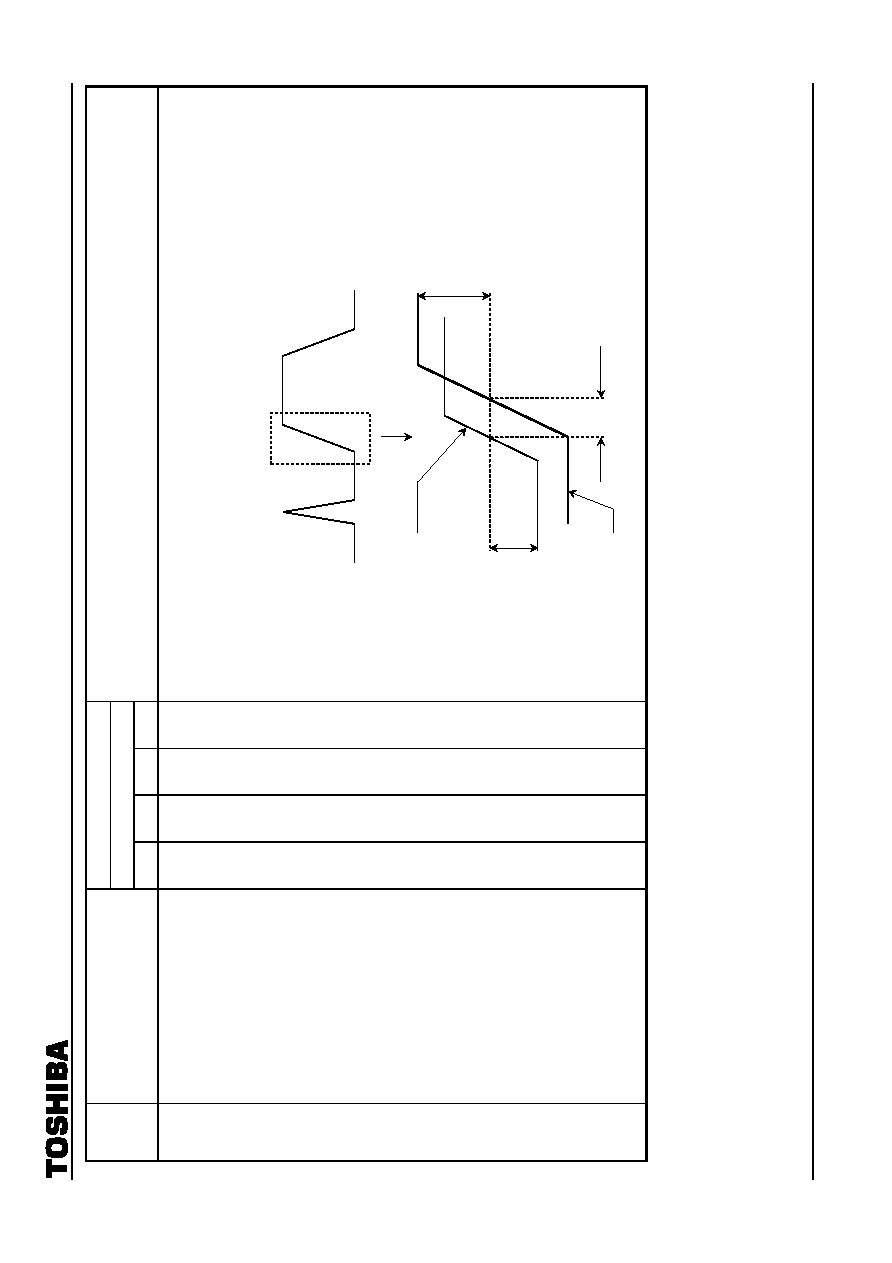

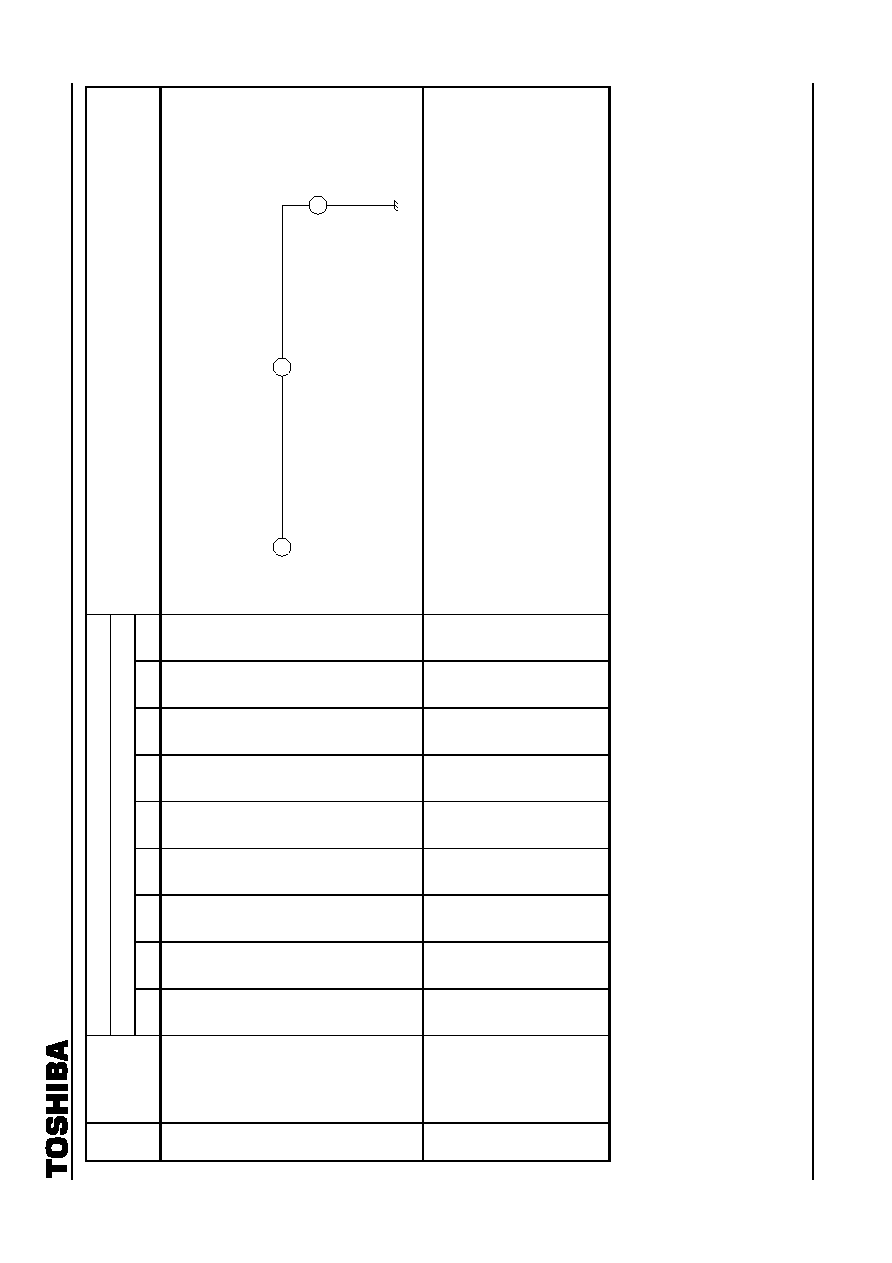

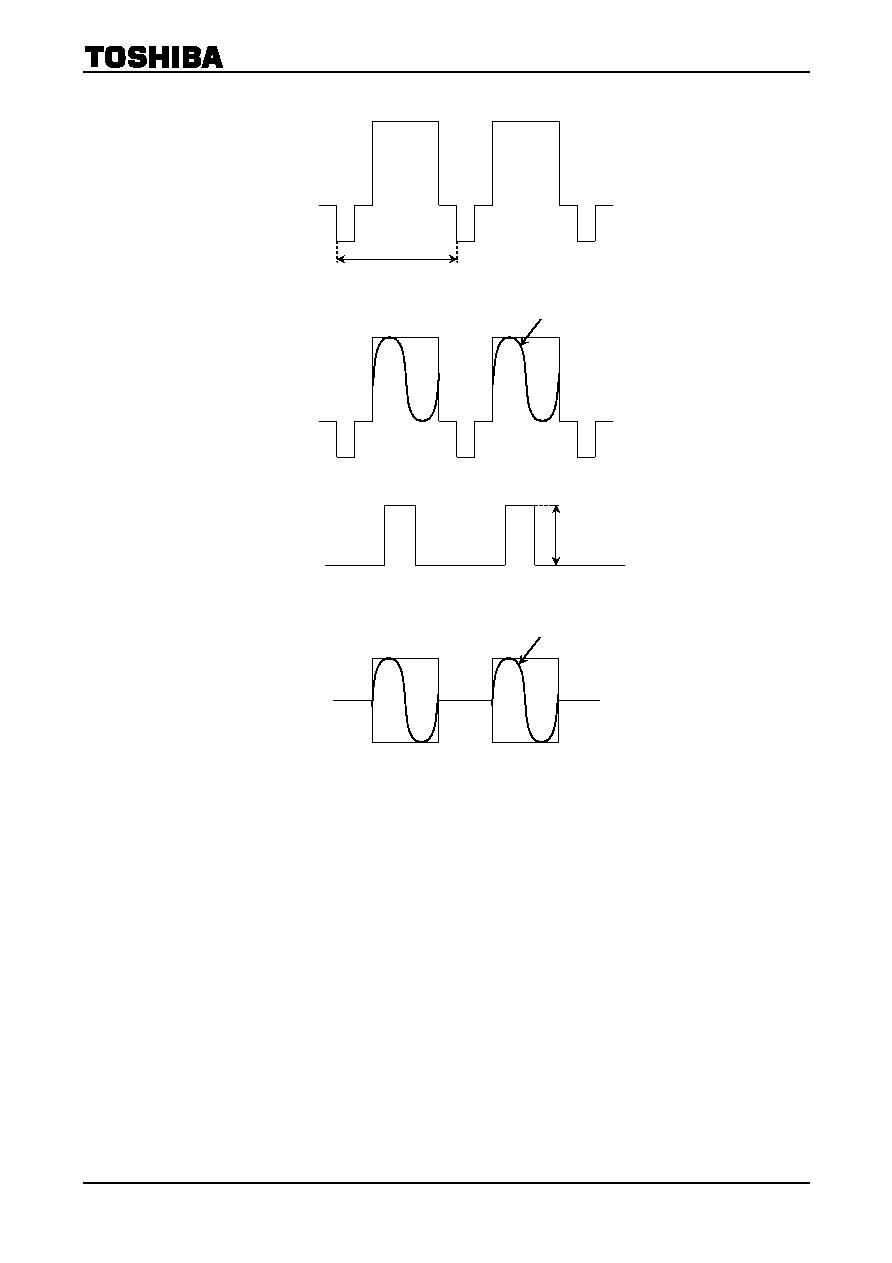

Data Transfer Format via I

2

C BUS

Slave Address: 88H

A6 A5 A4 A3 A2 A1 A0 W/R

1 0 0 0 1 0 0 0/1

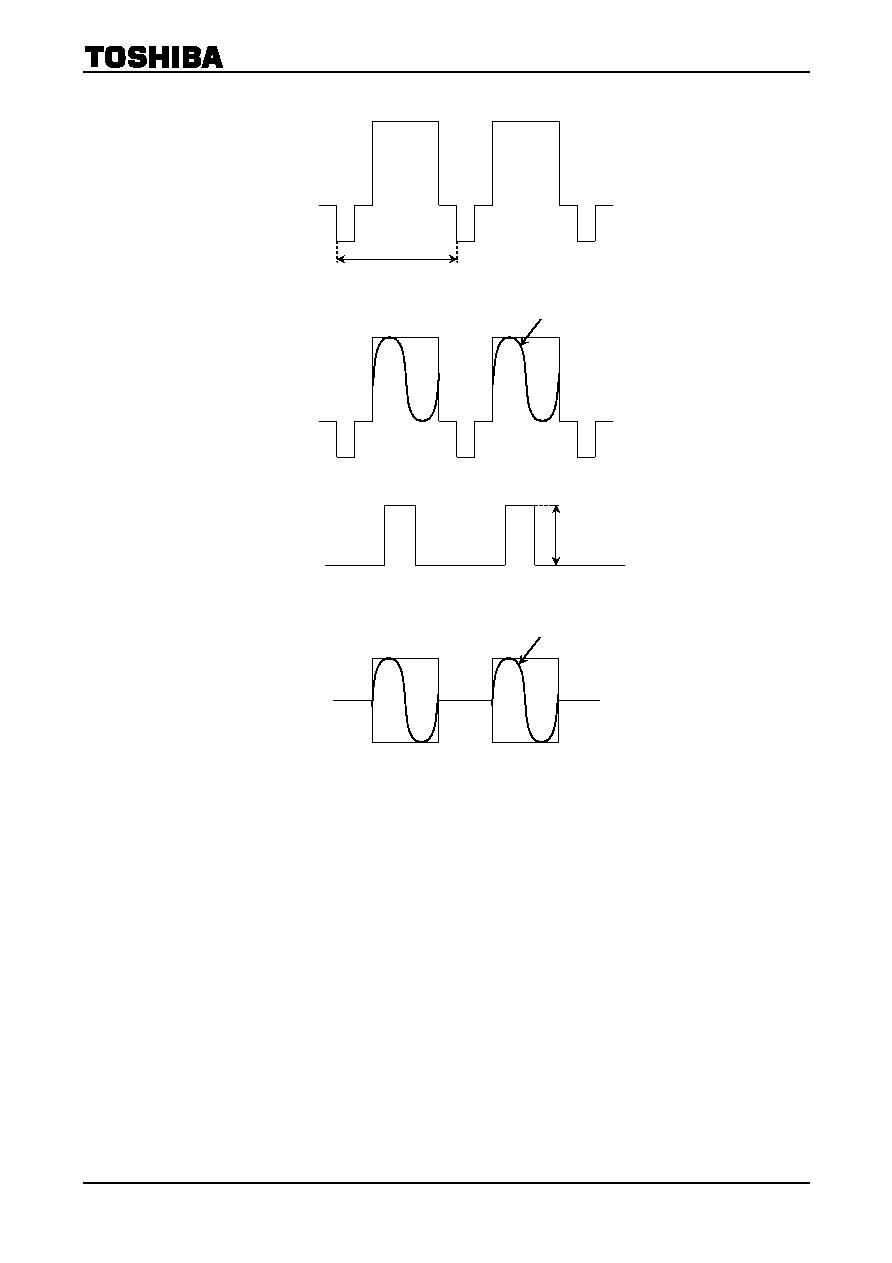

Start and Stop Condition

Bit Transfer

Acknowledge

SDA

SCL

S

Start condition

P

Stop condition

SDA

SCL

SDA stable

Change of SDA allowed

SDA by transmitter

Bit 9 only: Low-impedance

Clock pulse for acknowledge

S

1 8

9

SDA by receiver

SCL from master

Bit 9: High-impedance

TA1316AN

2002-10-04

32

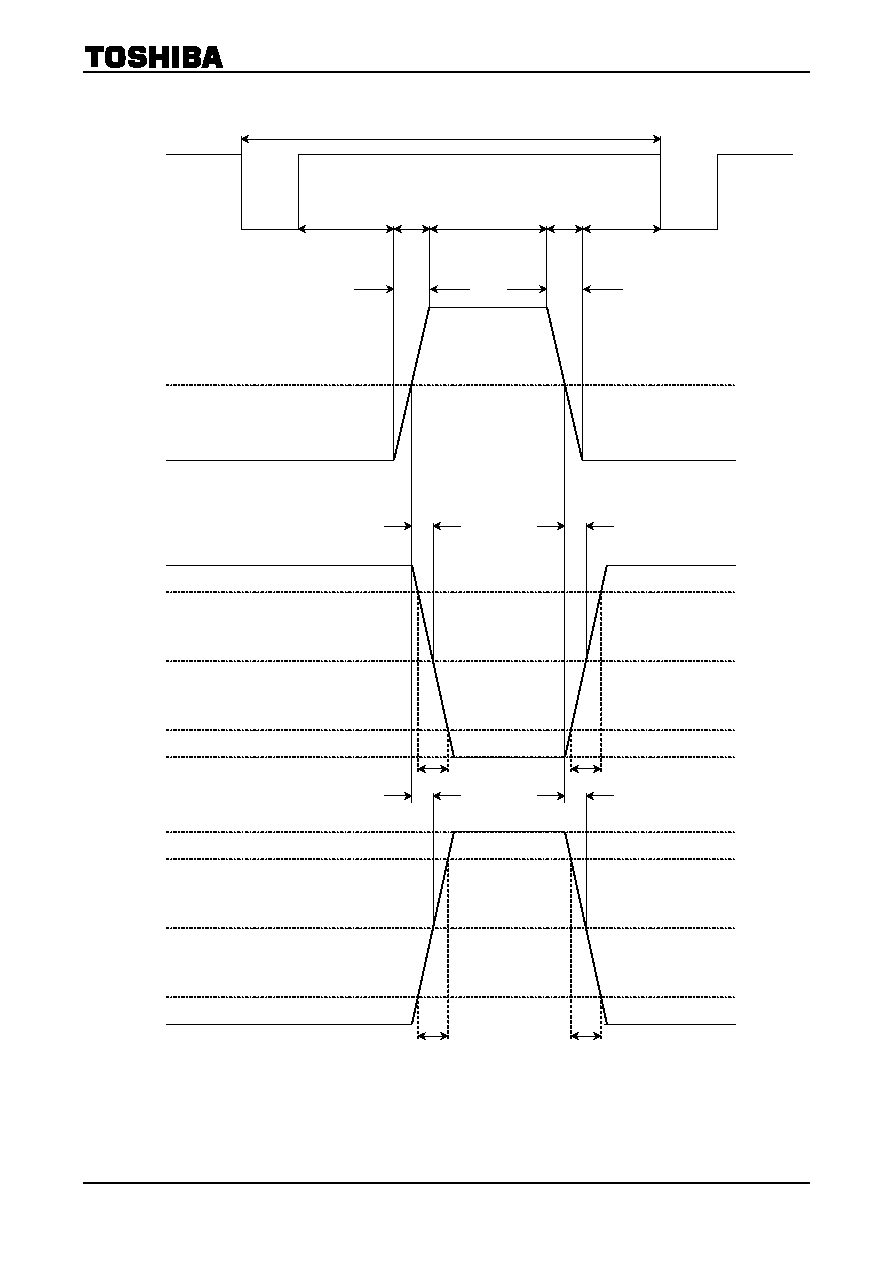

Data Transmit Format 1

Data Transmit Format 2

Data Receive Format

At the moment of the first acknowledge, the master transmitter becomes a master receiver and a slave

transmitter.

The Stop condition is generated by the master.

Details are provided in the Philips I

2

C specifications.

Optional Data Transmit Format: Automatic Increment Mode

In this transmission method, data is set on automatically incremented sub-address from the specified

sub-address.

Purchase of TOSHIBA I

2

C components conveys a license under the Philips I

2

C Patent Rights to use these

components in an I

2

C system, provided that the system conforms to the I

2

C Standard Specification as defined by

Philips.

S

Slave address

0 A

Transmit data

A

Sub address

A P

7 bits

MSB

S: Start condition

8 bits

MSB

A: Acknowledge

9 bits

MSB

P: Stop condition

S

Slave address

0 A

Transmit data

A

Sub address

A

Transmit data n

A

Sub address

A P

S

Slave address

1 A

Transmit data 2

A

Transmit data 1

A P

7 bits

MSB

8 bits

MSB

S

Slave address

A

Transmit data 2

Transmit data 1

A P

7 bits

MSB

8 bits

MSB

0

Sub address

7 bits

MSB

A 1

8 bits

MSB

TA1316AN

2002-10-04

33

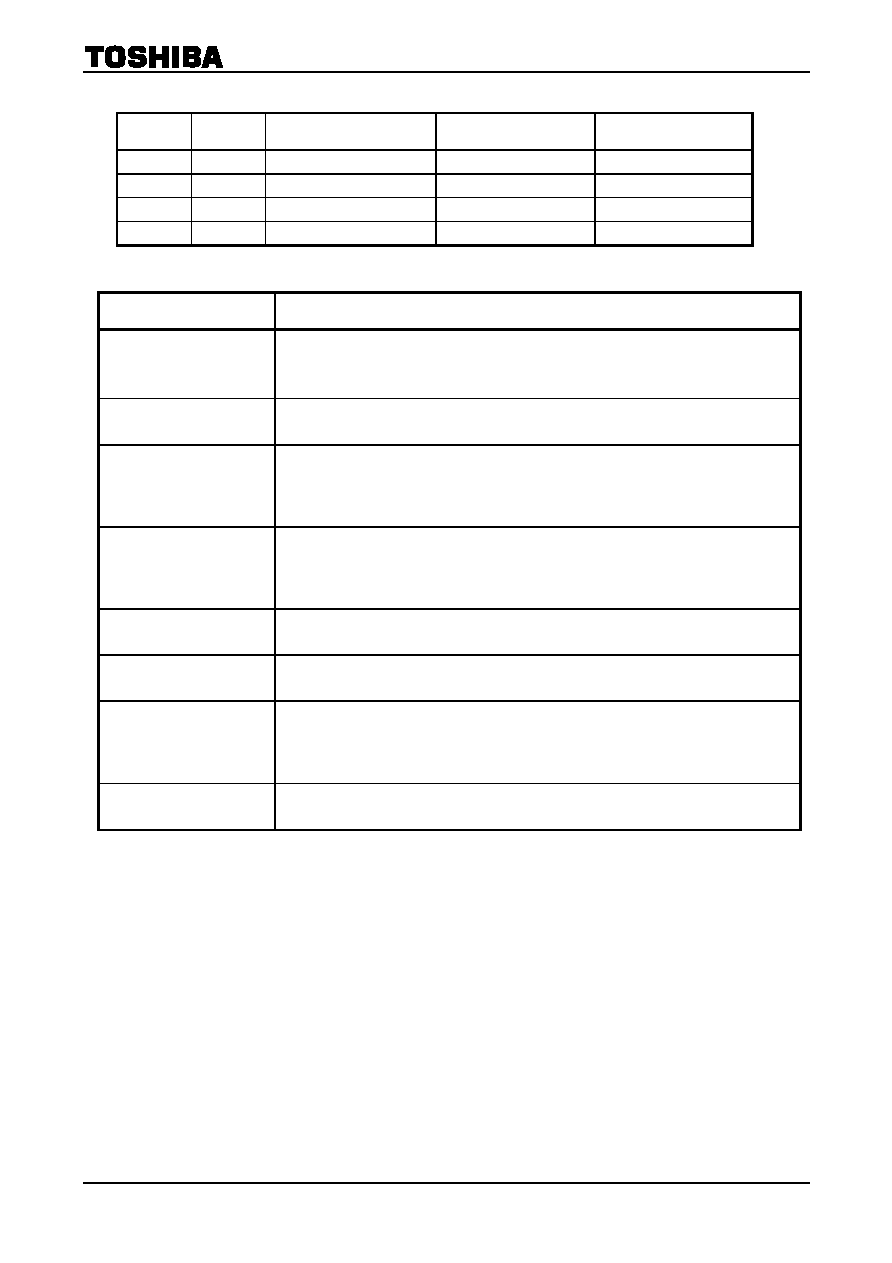

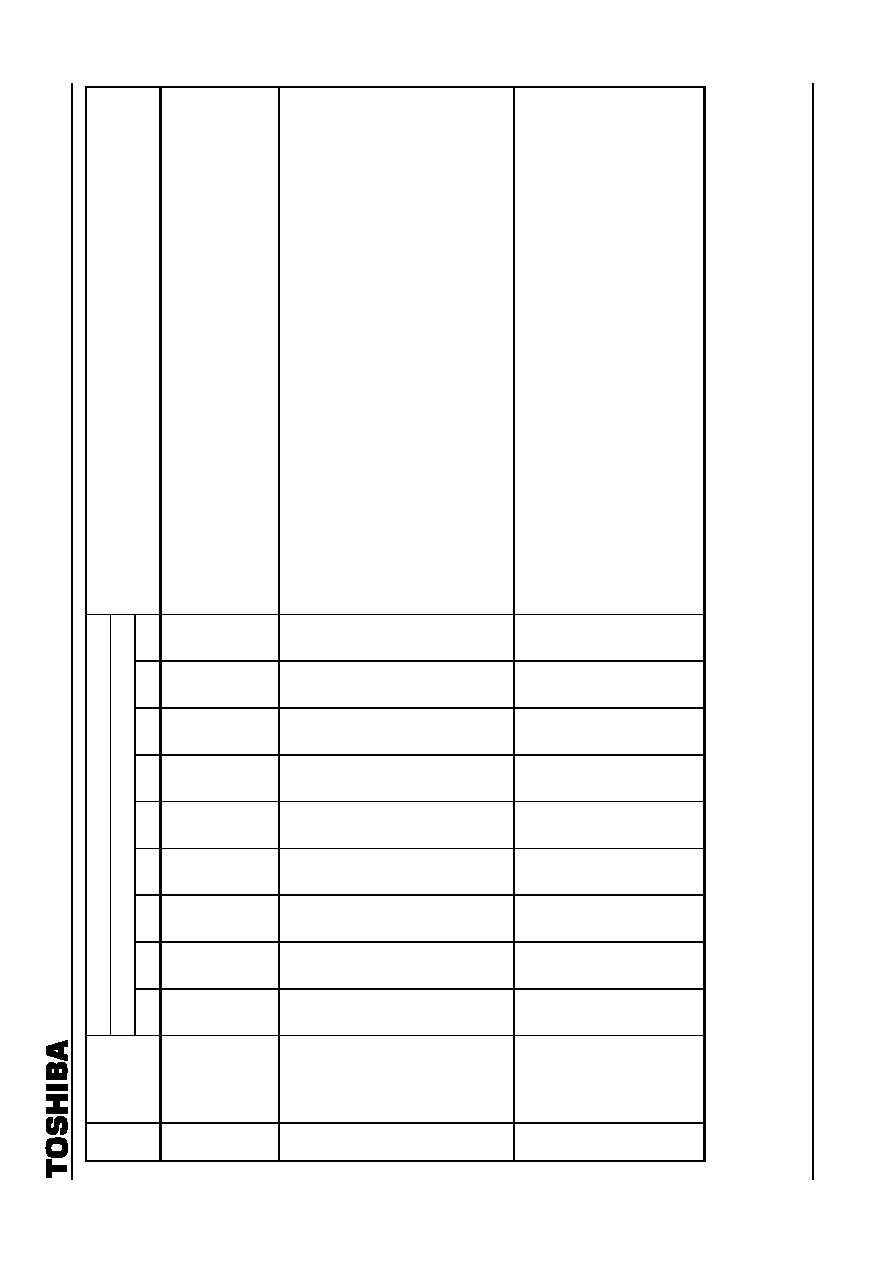

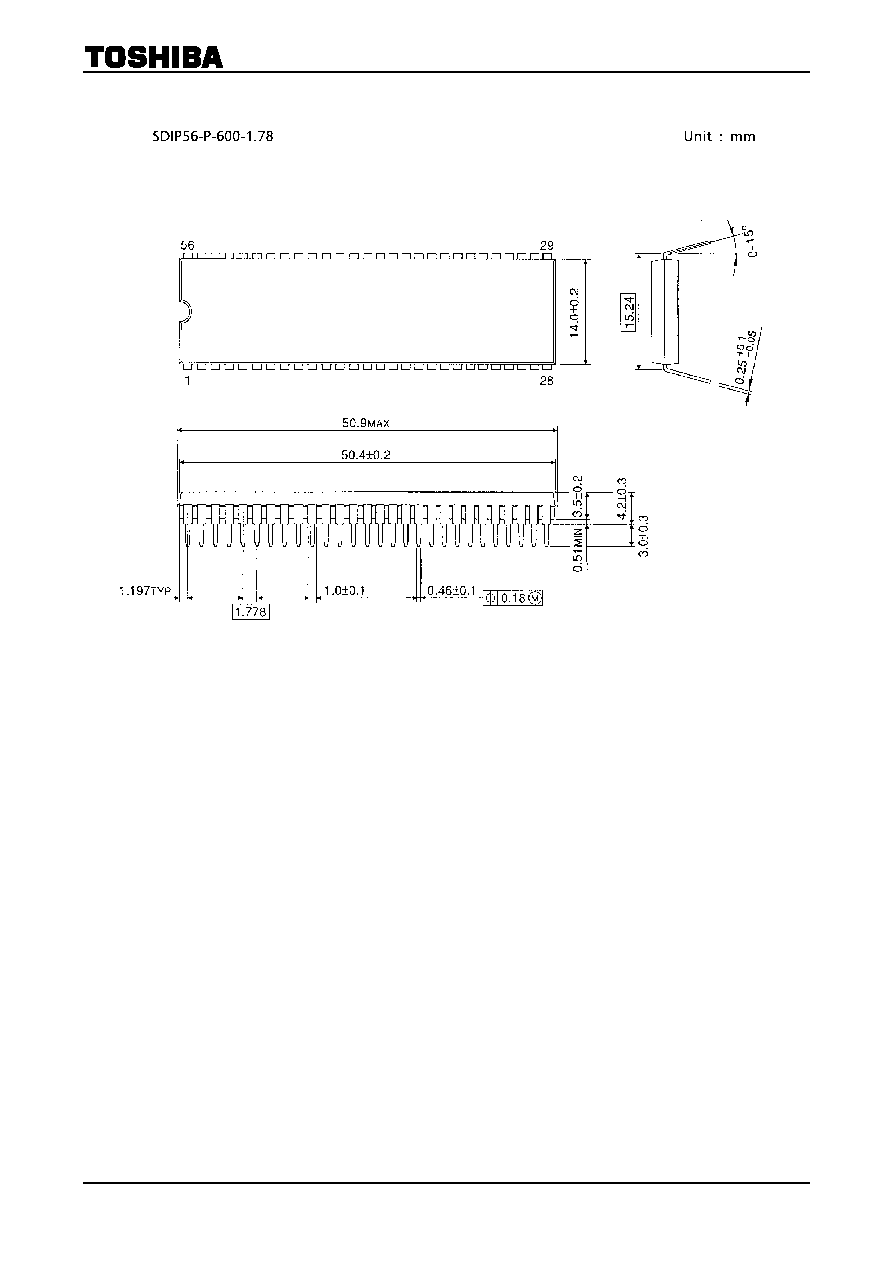

Maximum Ratings

(Ta

=

=

=

= 25∞C)

Rating

Characteristics Symbol

PCB A

PCB B

PCB C

Unit

Power supply voltage

V

CC

max 12

12

12 V

Input pin signal voltage

e

in

max 9

9

9 V

p-p

Power dissipation

P

D

(Note1)

2551

2717

3378

mW

Power dissipation reduction rate

1/

ja

20.4 21.7 27.0

mW/

∞

C

Operating temperature

T

opr

-

20~65

-

20~65

-

20~65

∞

C

Storage temperature

T

stg

-

55~150

-

55~150

-

55~150

∞

C

min 8.5 8.7 8.7

typ. 8.8 9.0 9.0

Power supply voltage

(Pins 19, 40, 55)

max 9.1 9.3 9.3

V

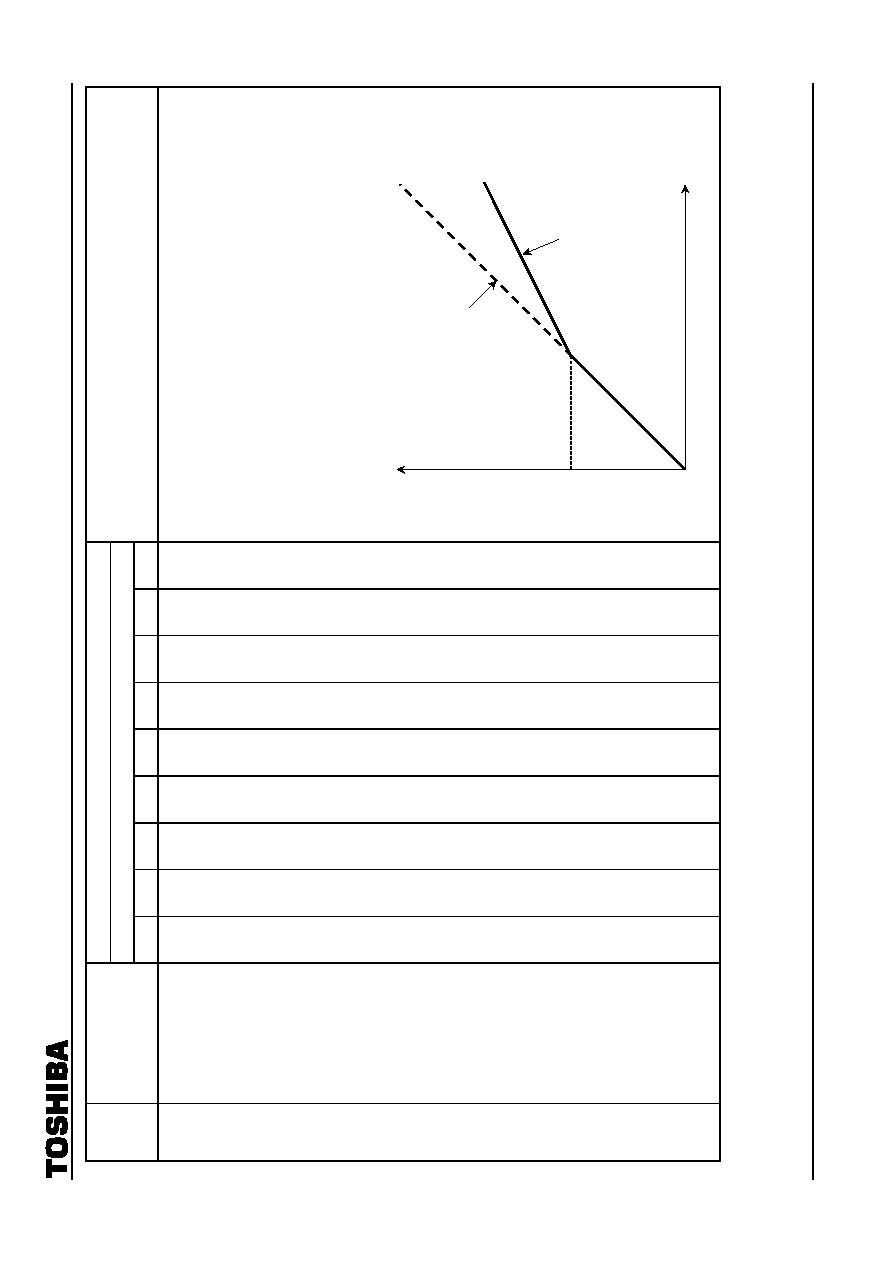

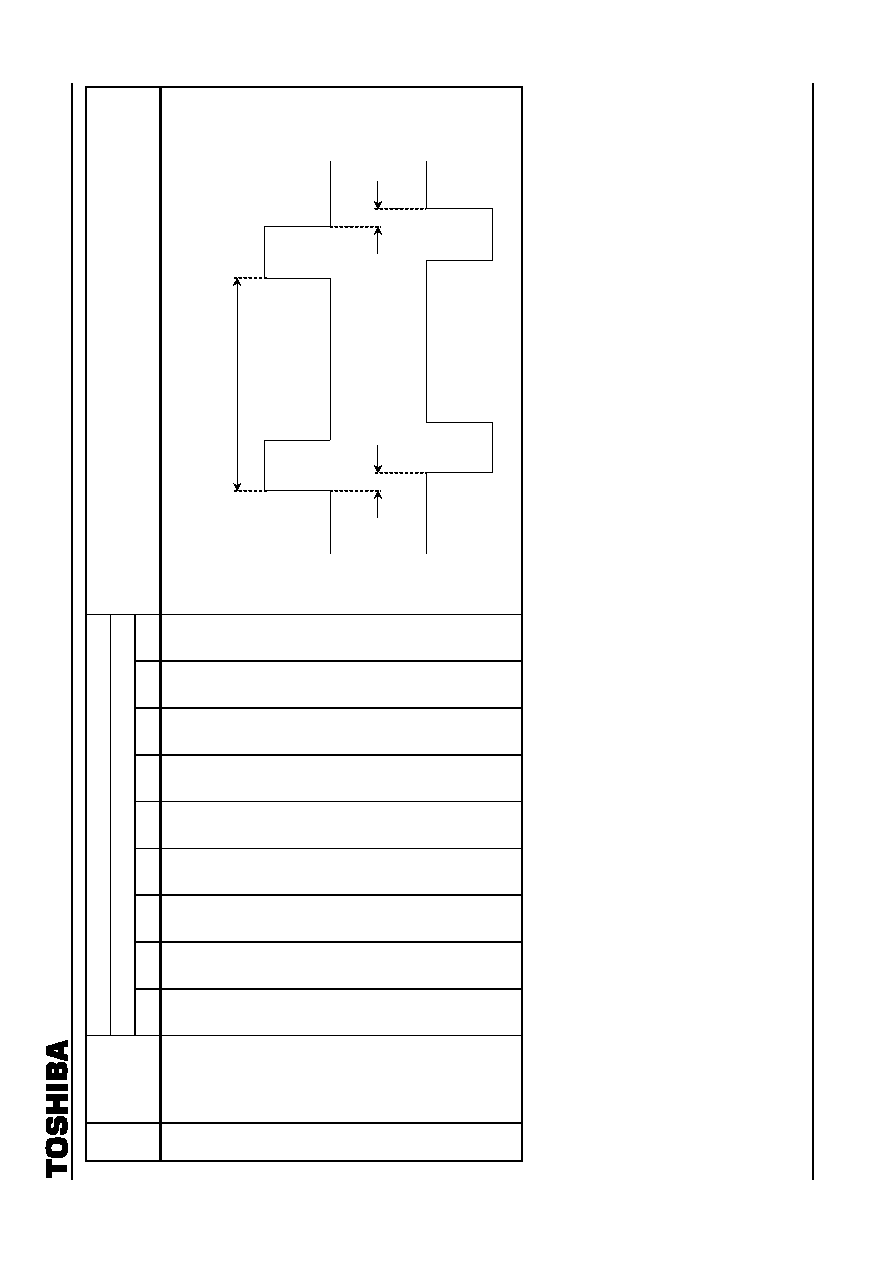

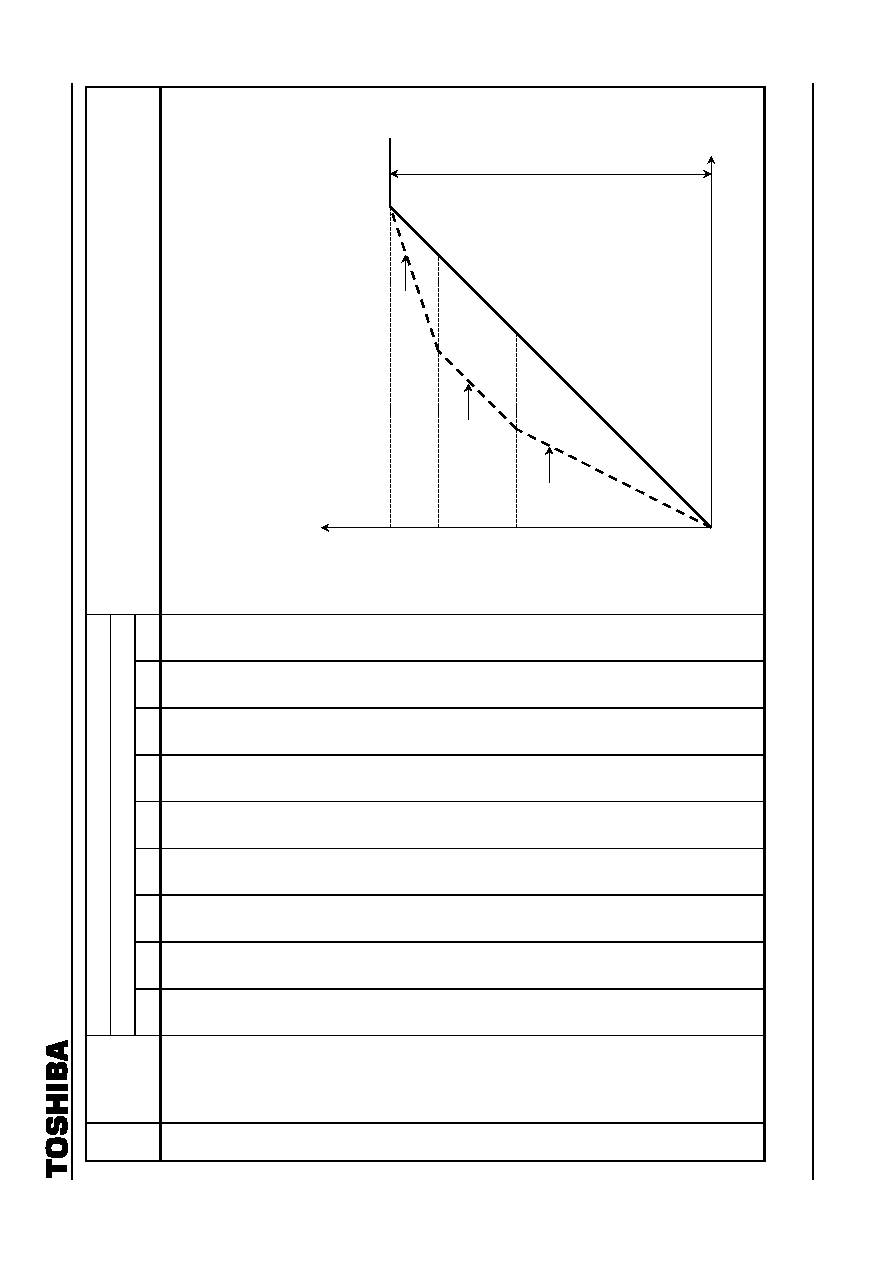

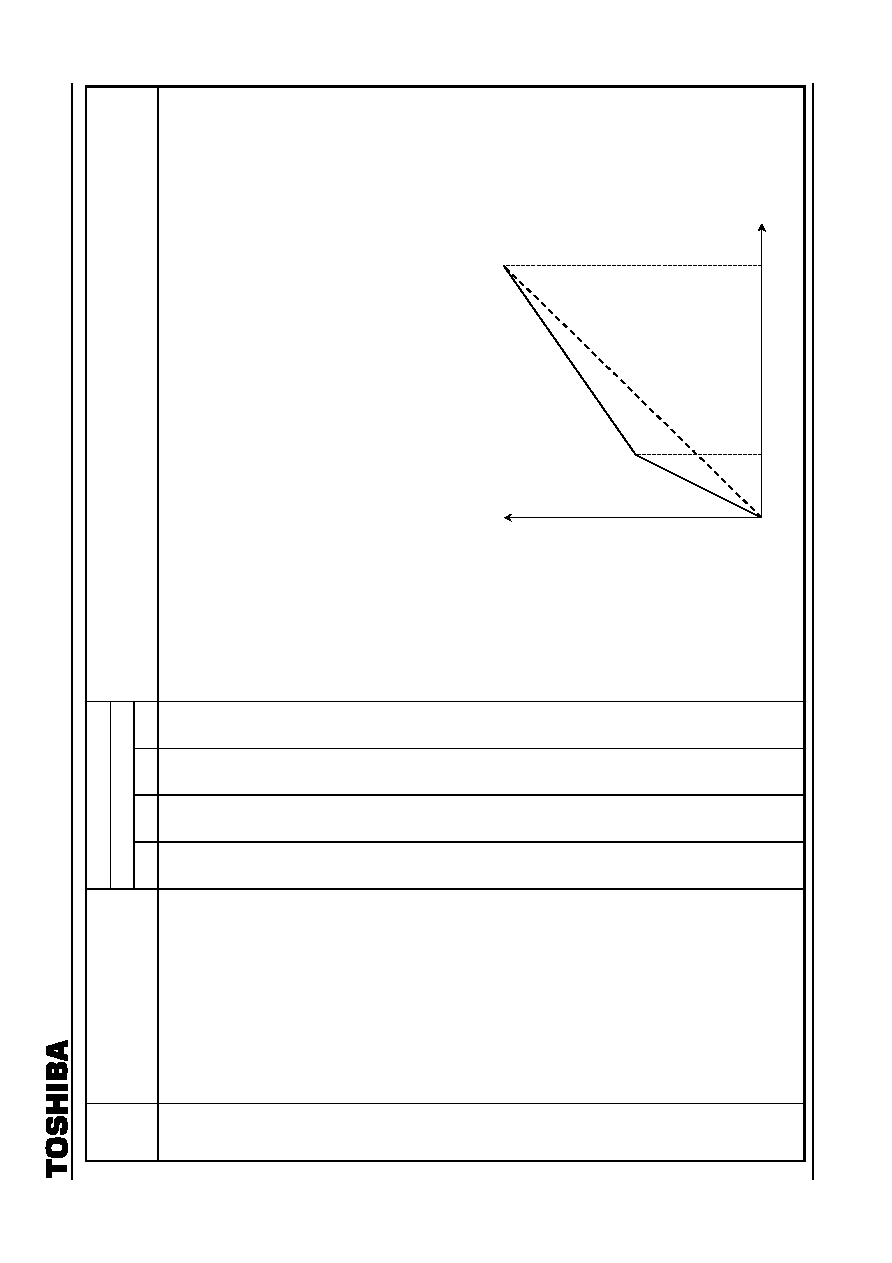

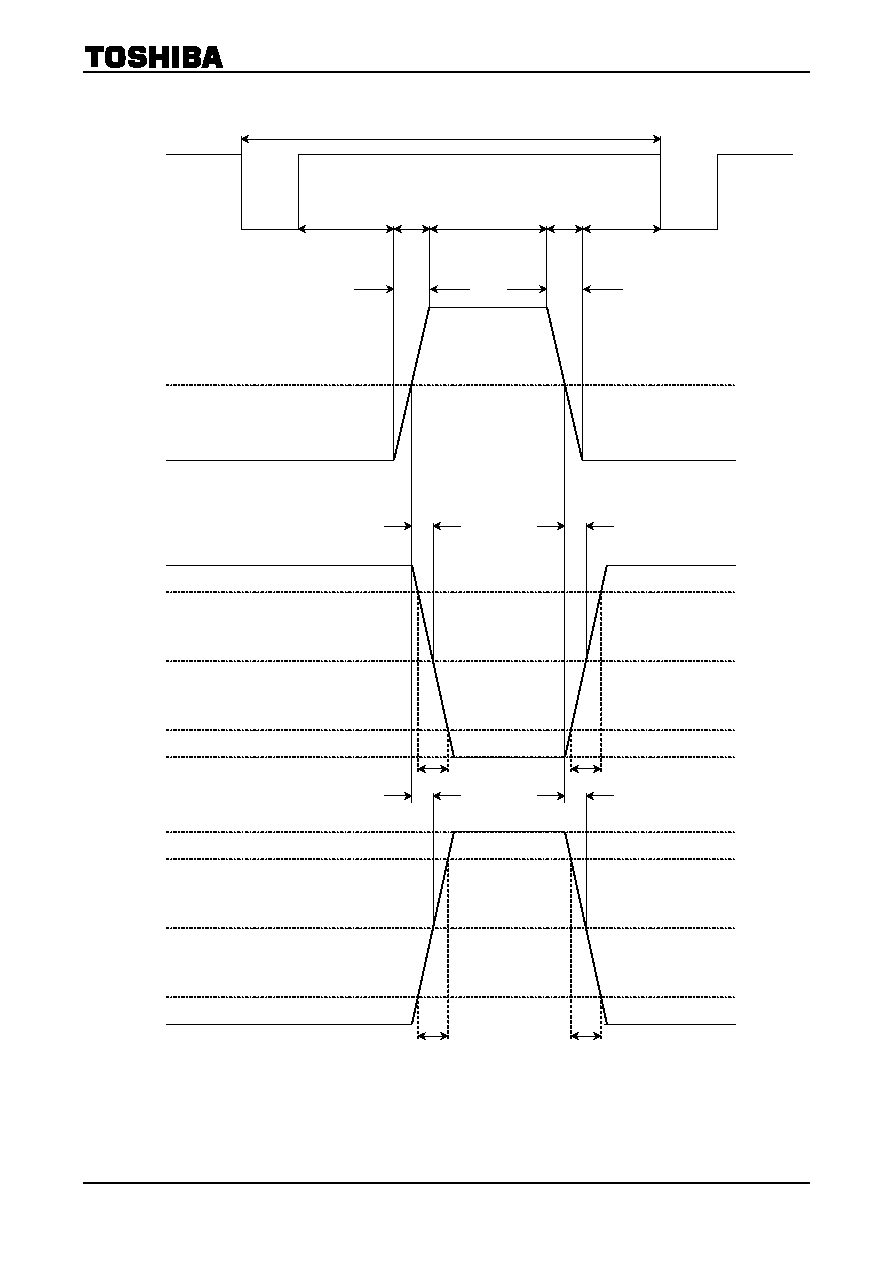

Note 1: Please see the following Figure.

Note, however, that the conditions apply only to the case where the device is mounted on board A (180 mm

◊

125 mm

◊

1.6 mm, one-sided); board B (329 mm

◊

249 mm

◊

1.6 mm, two-sided); or board C (276 mm

◊

192 mm

◊

1.6 mm, six-layered). When mounting the IC, select boards no smaller than these. When using

under the conditions of board A, set the IC's power supply voltage (pins 19, 40, 55) to 8.8 V (

±

0.3 V)

Because the IC's thermal capacity margin is narrow, when designing a set, incorporate heat discharge

features into the design. Note that the power dissipation varies widely depending on the board mounting

conditions.

Note 2: Pins 3, 4, 5, 7, 8, 9, 10, 11, 20, 21, 22, 23, 30, 31, 33, 34, 36, 39, 45, 46, 49, 50, 51, 52 and 53 are

susceptible to damage from surge voltages and should thus be handled with extreme care.

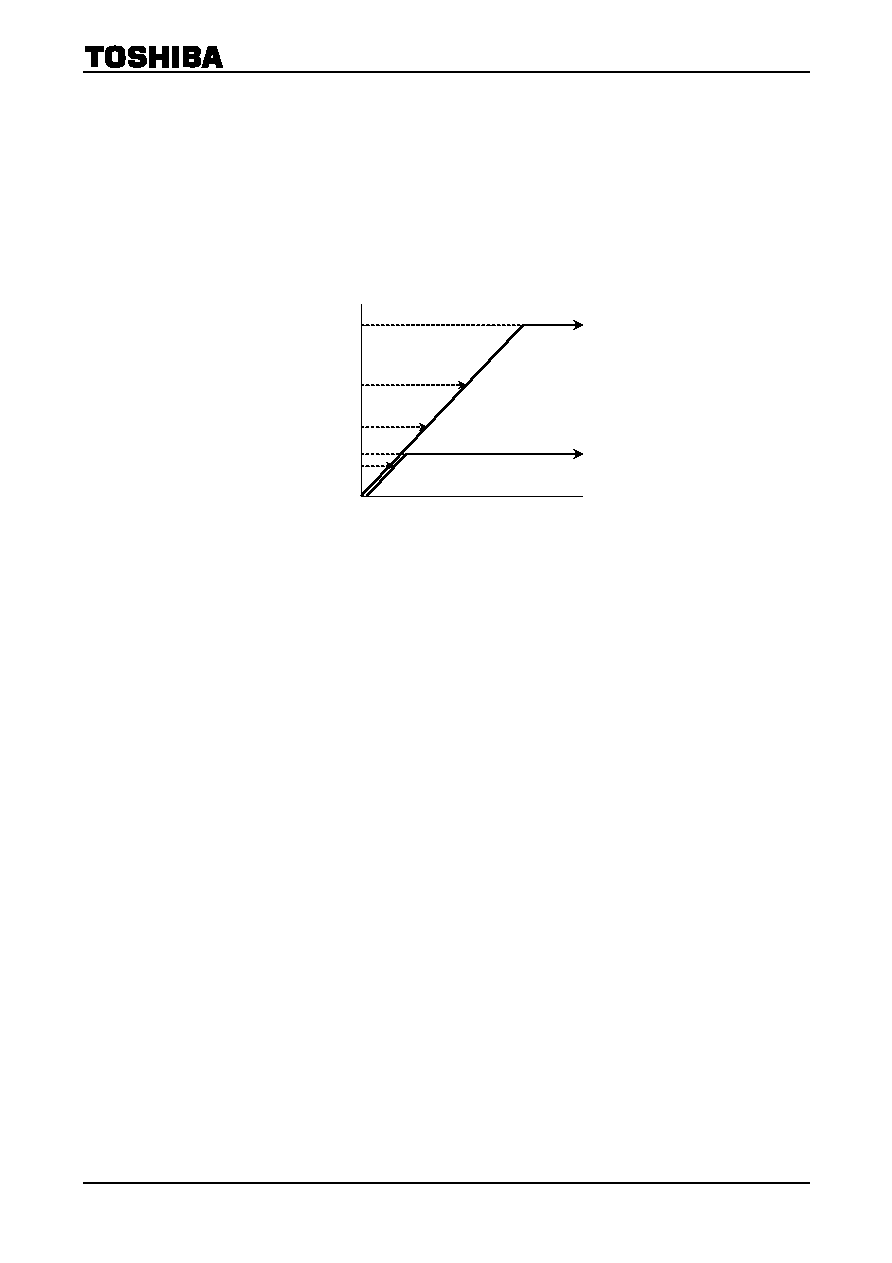

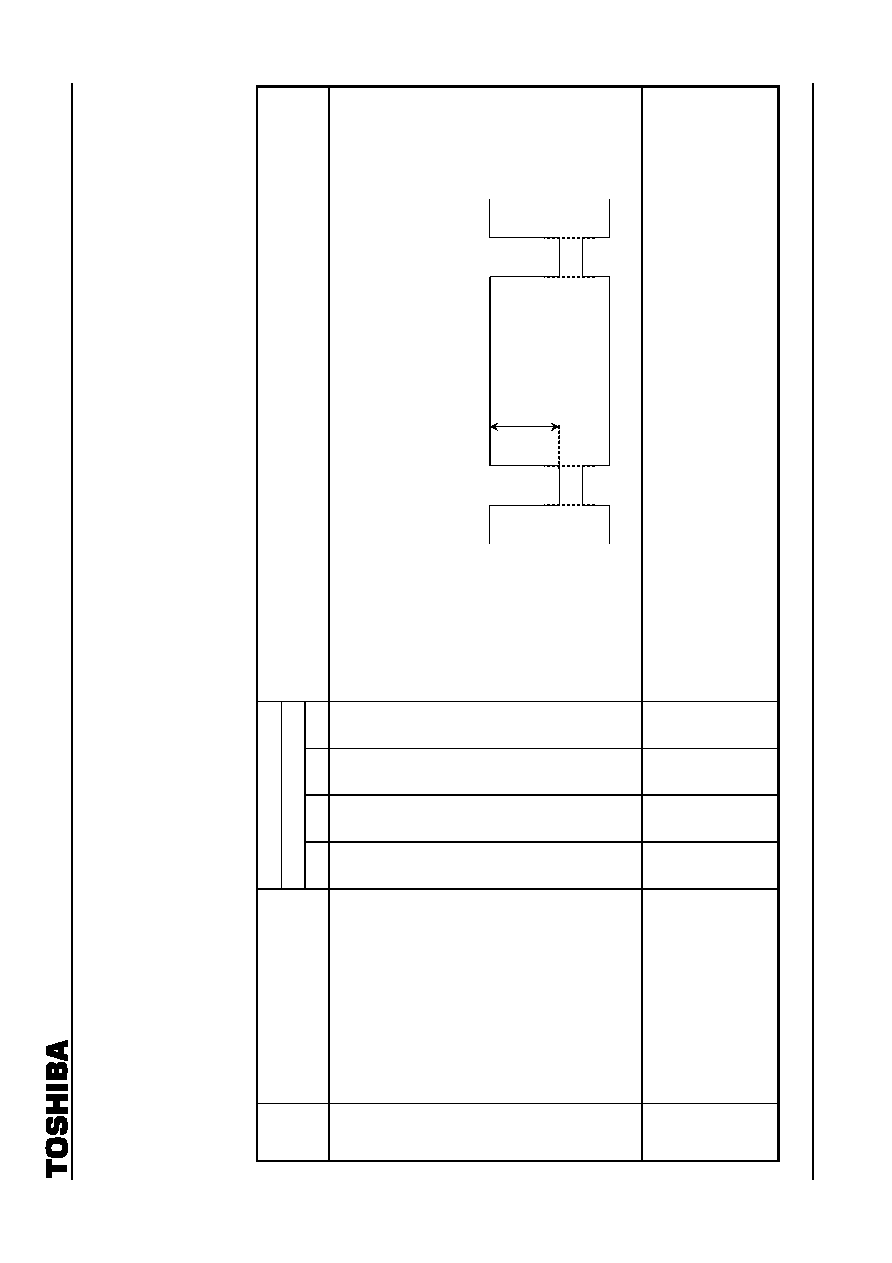

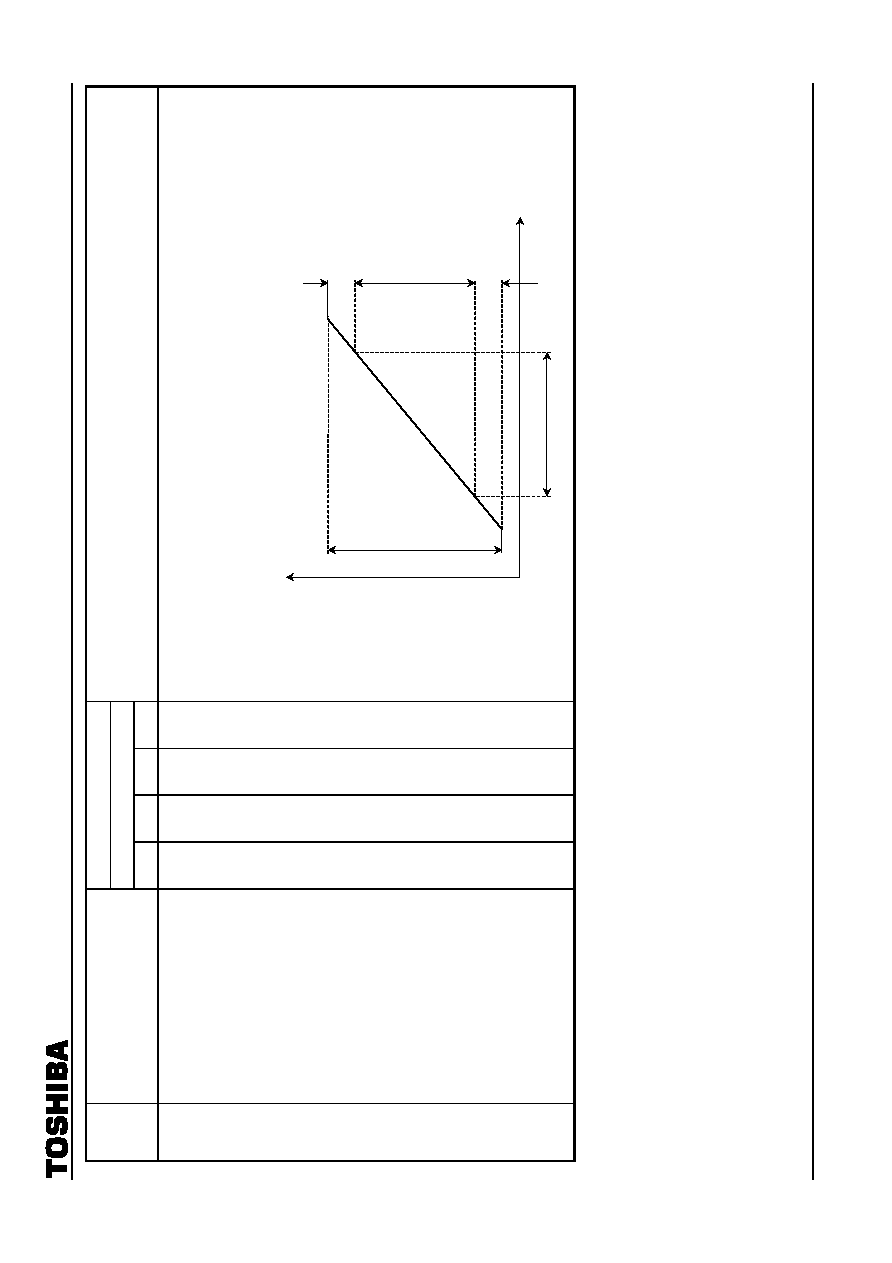

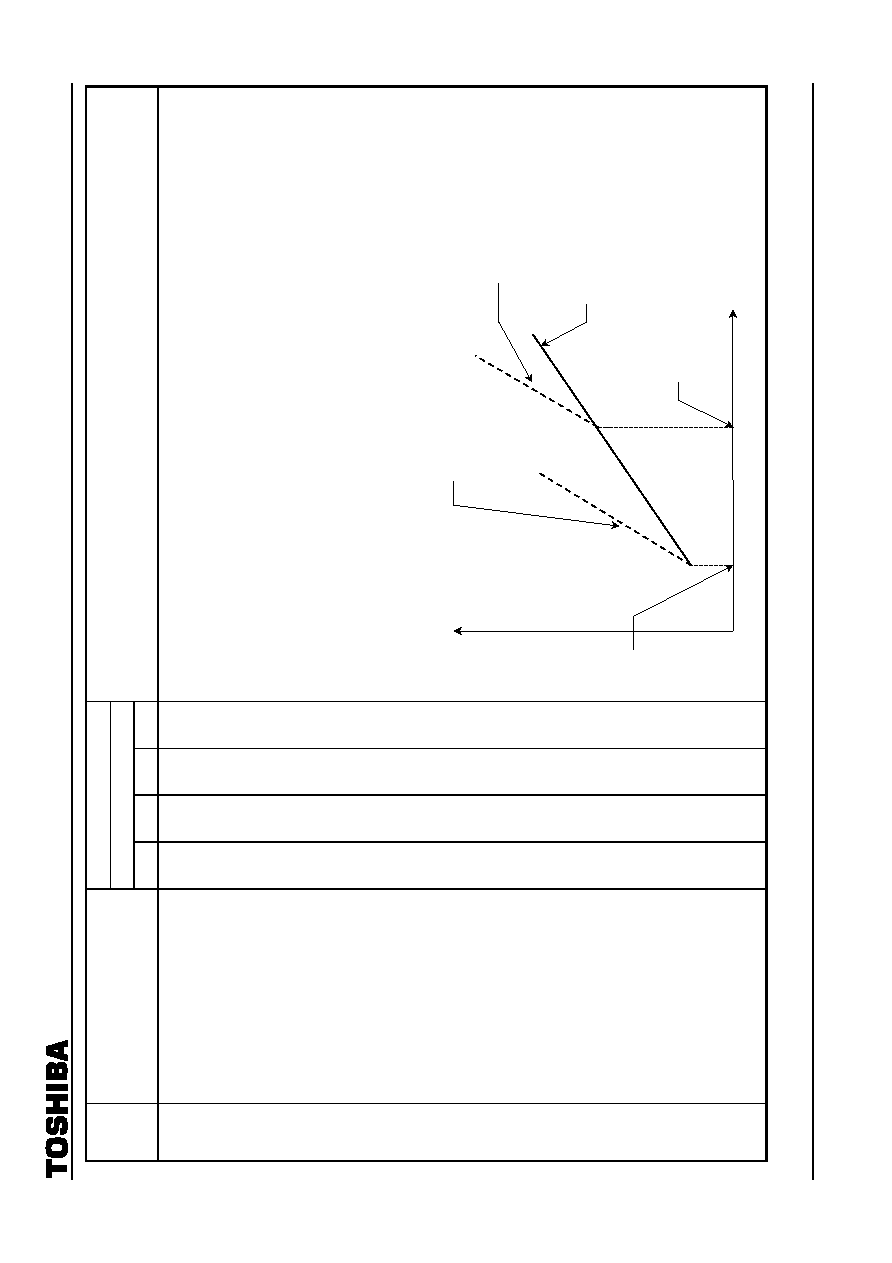

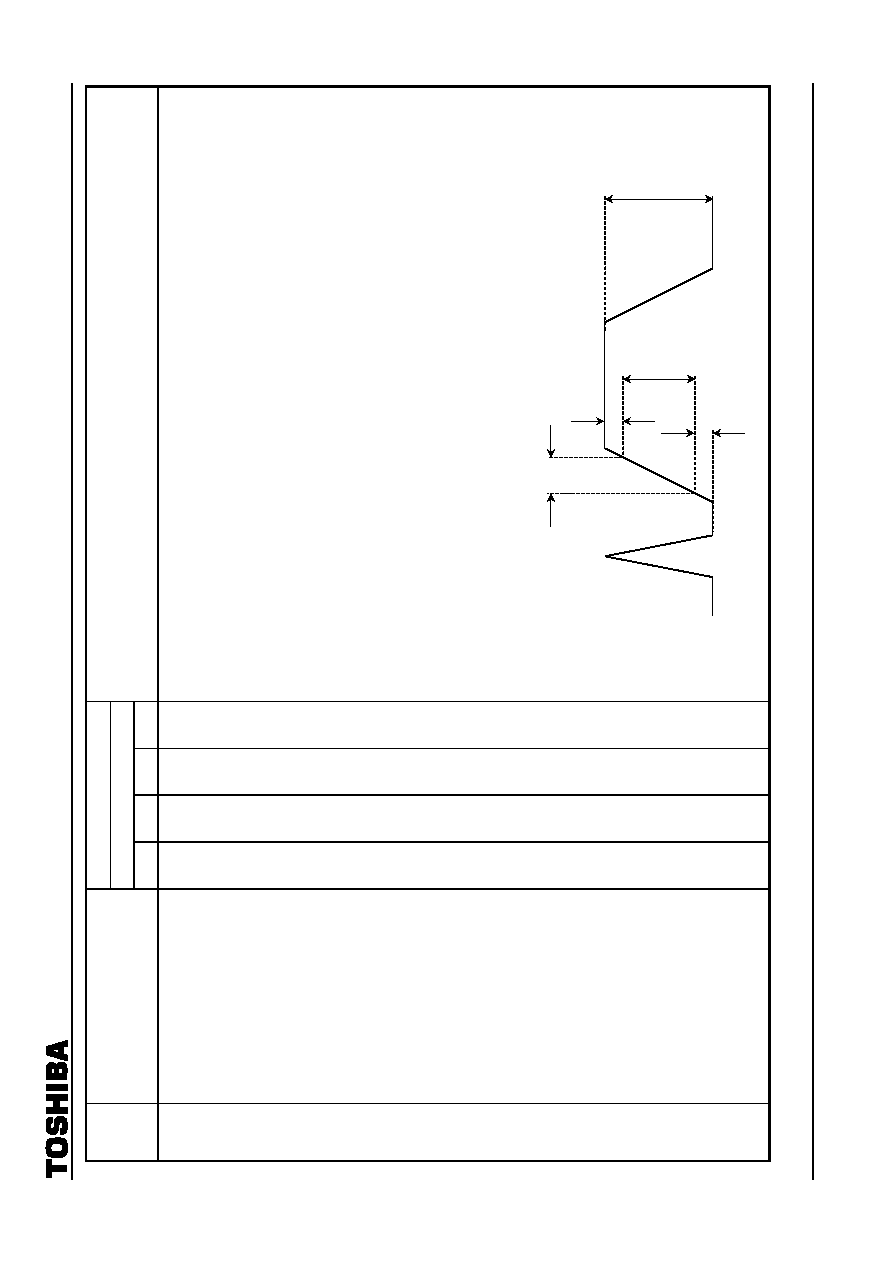

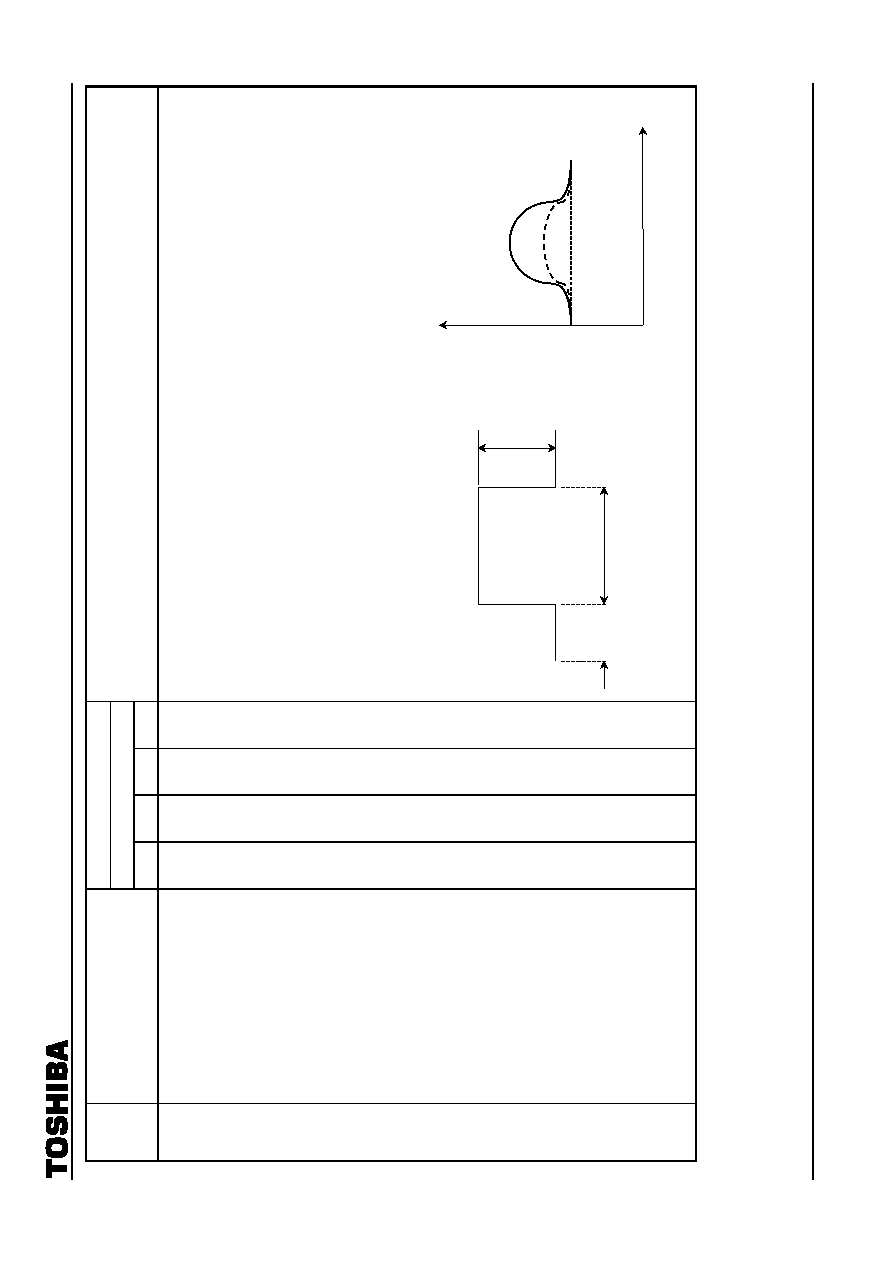

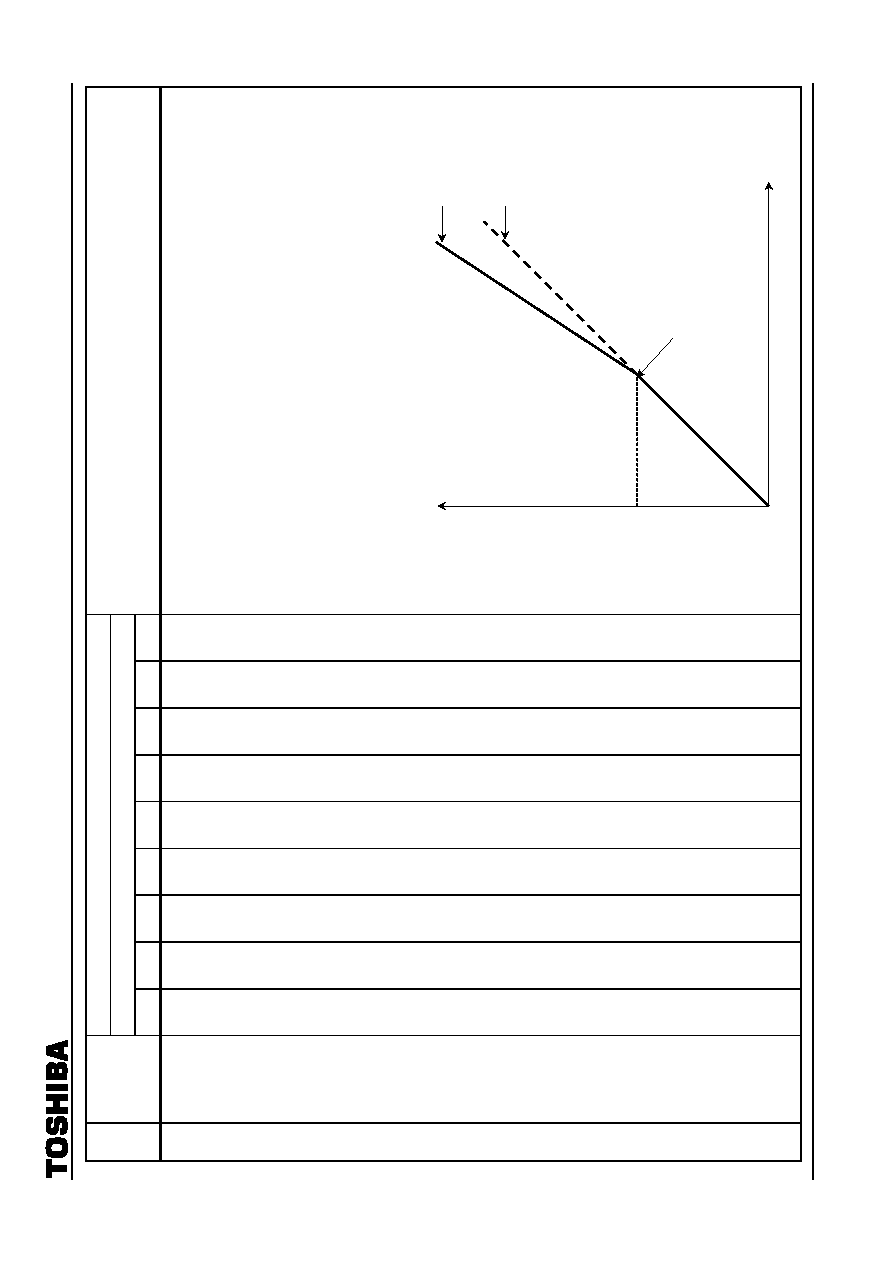

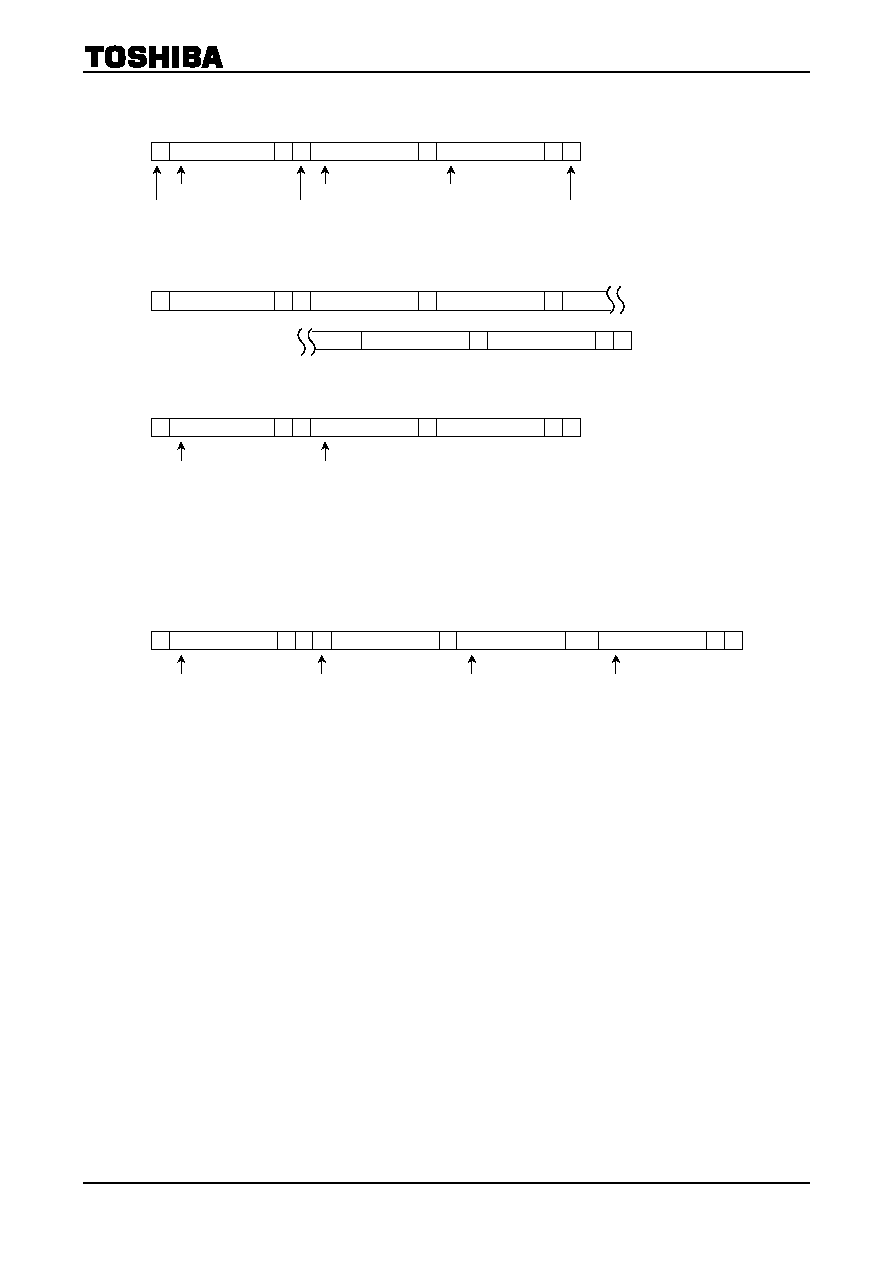

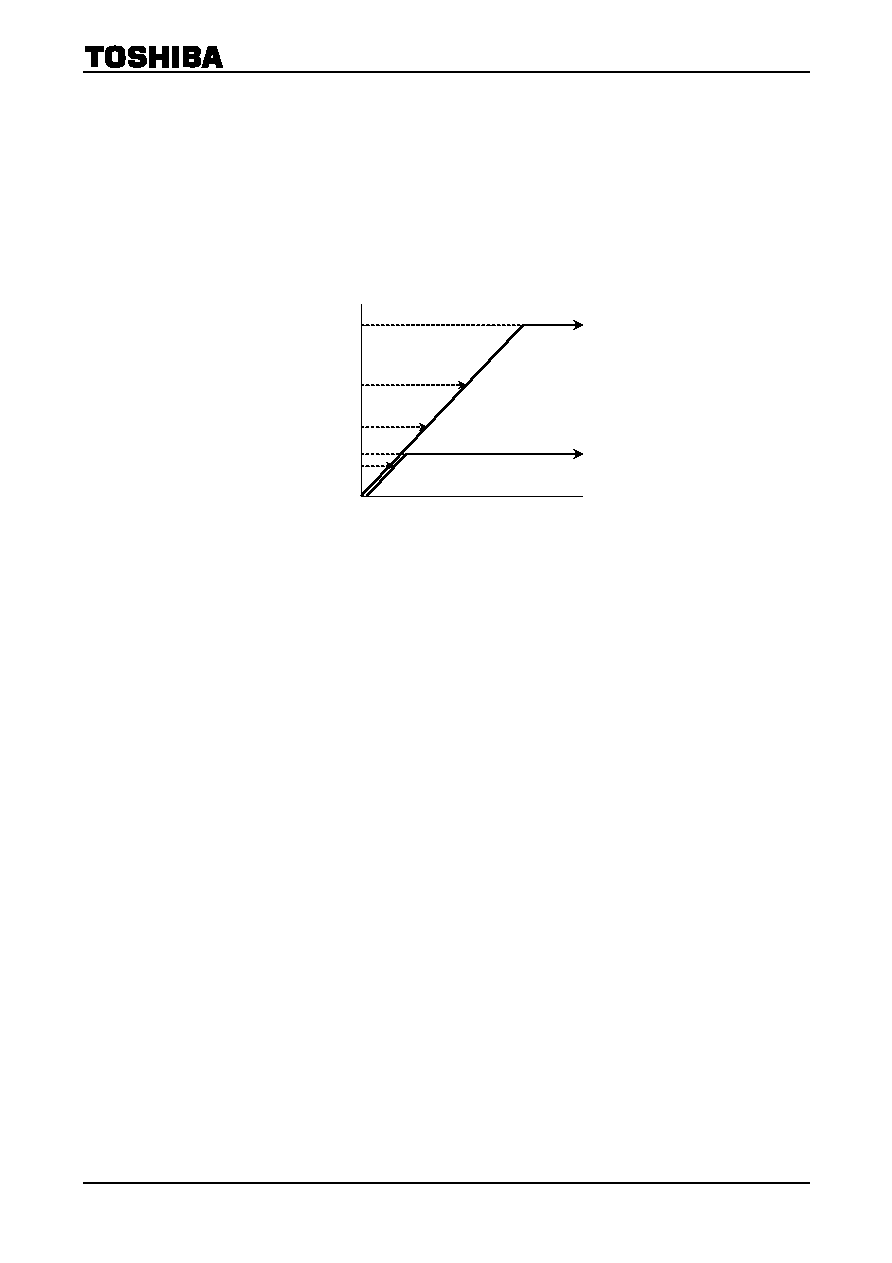

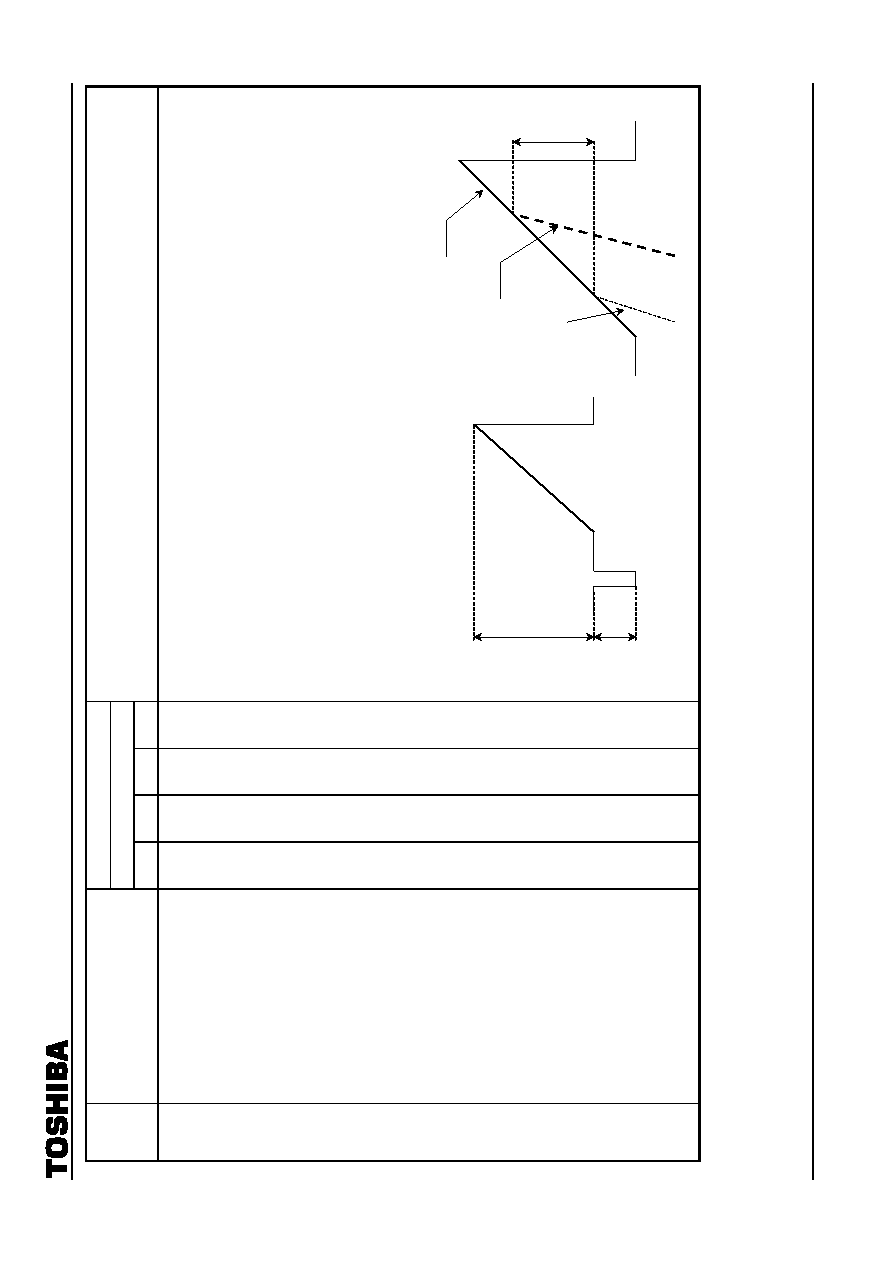

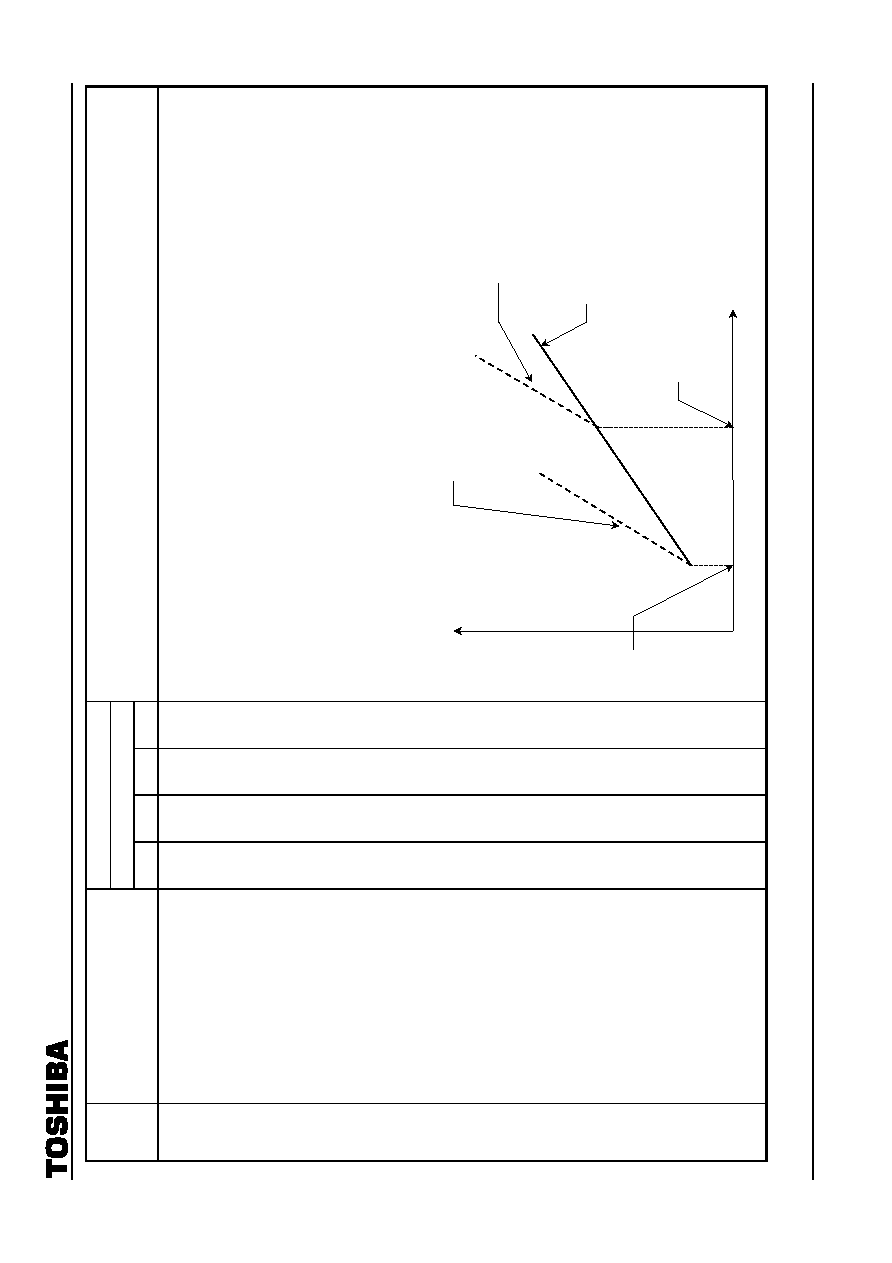

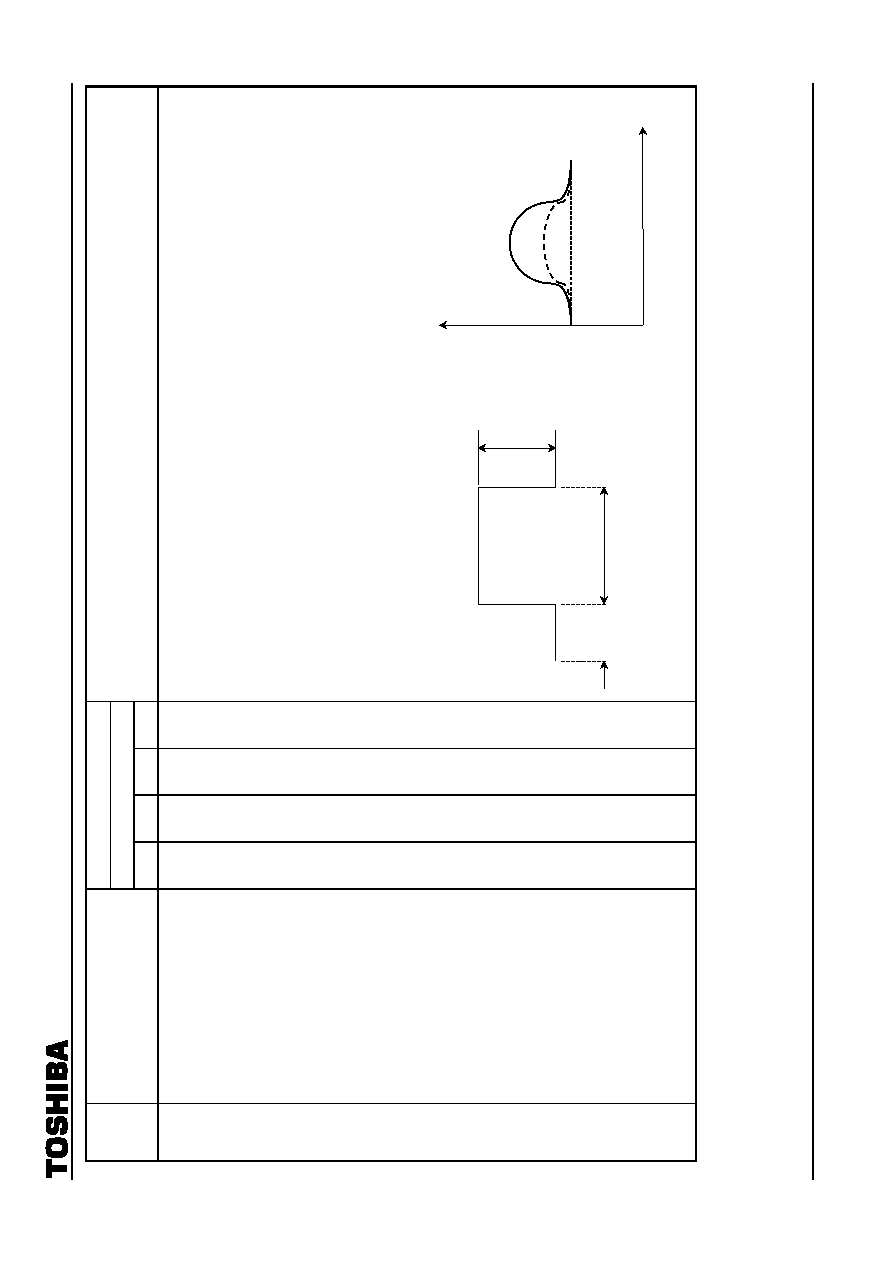

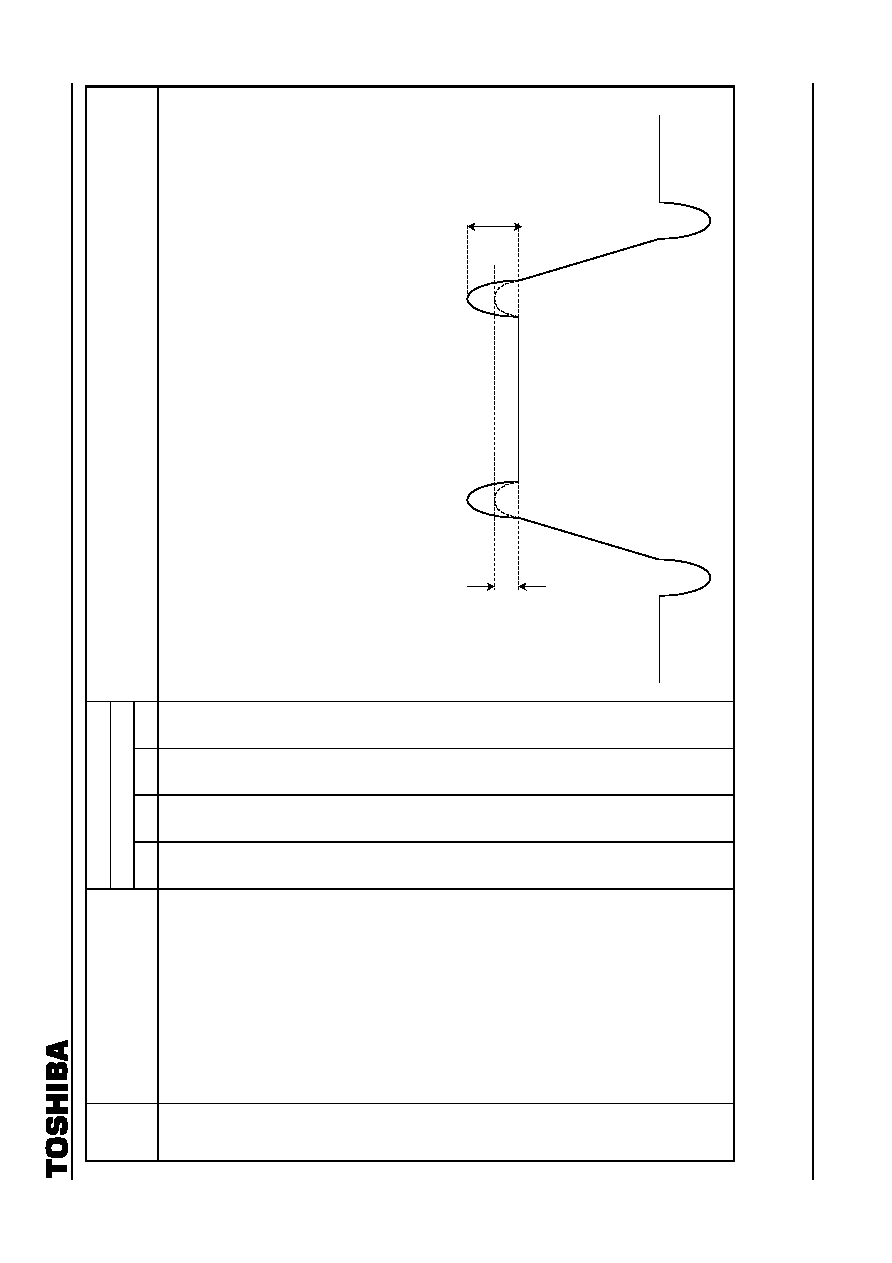

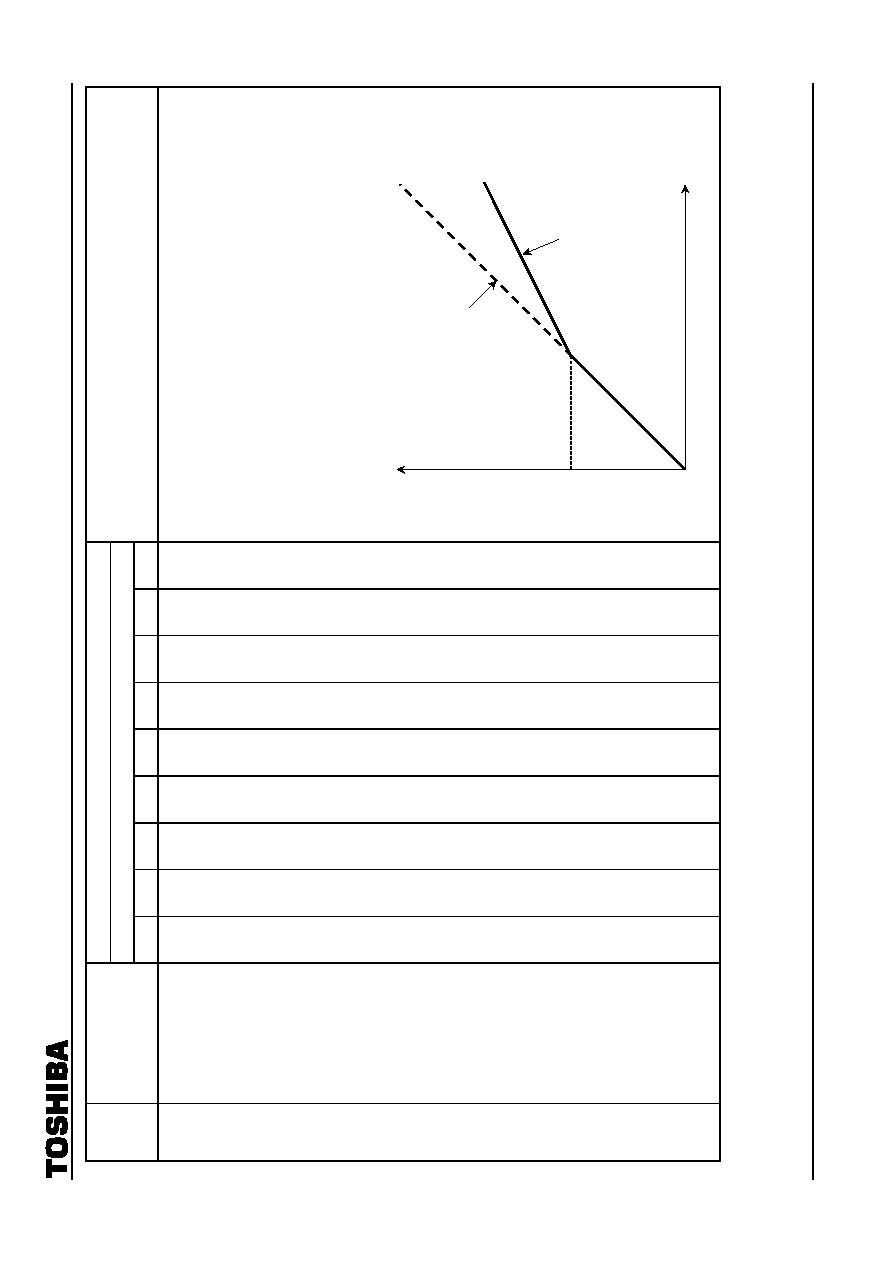

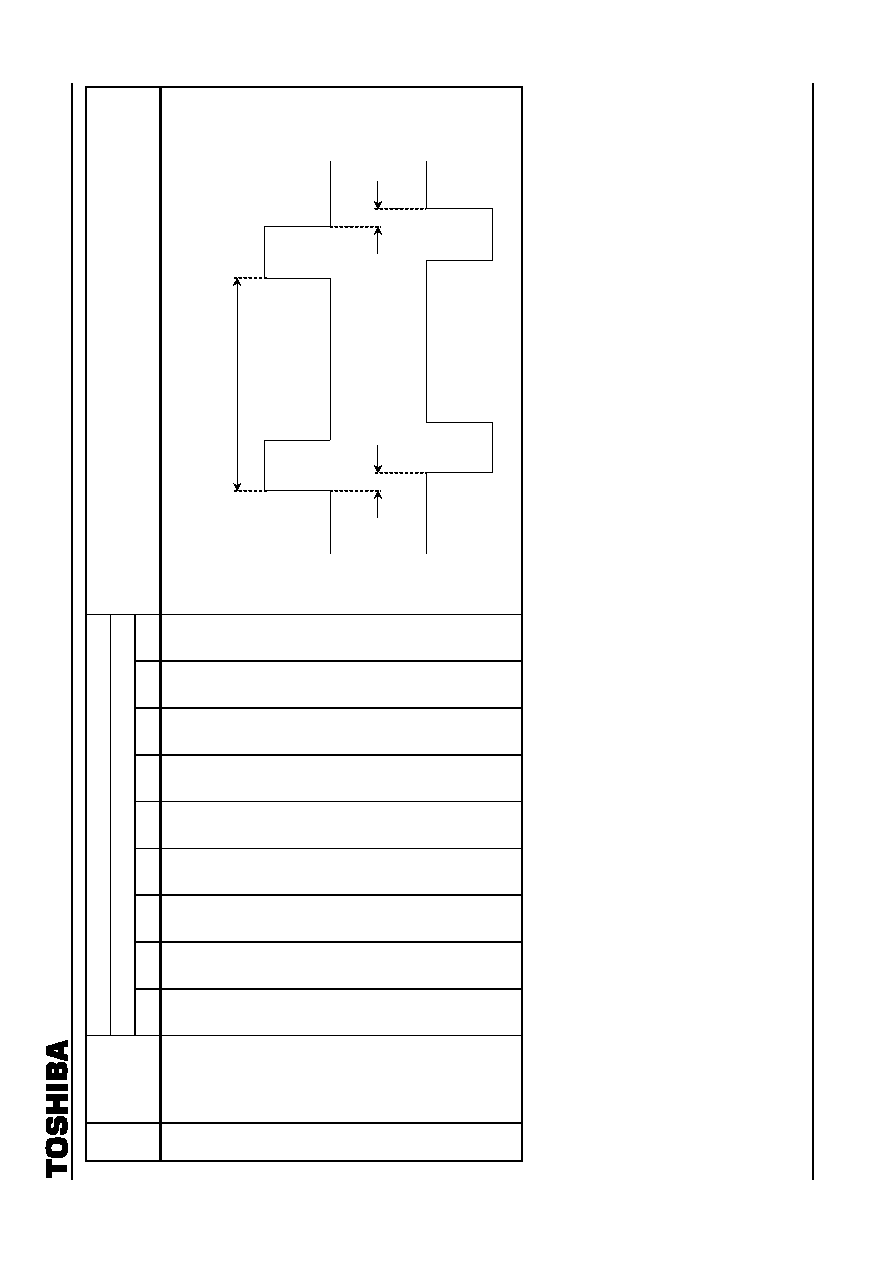

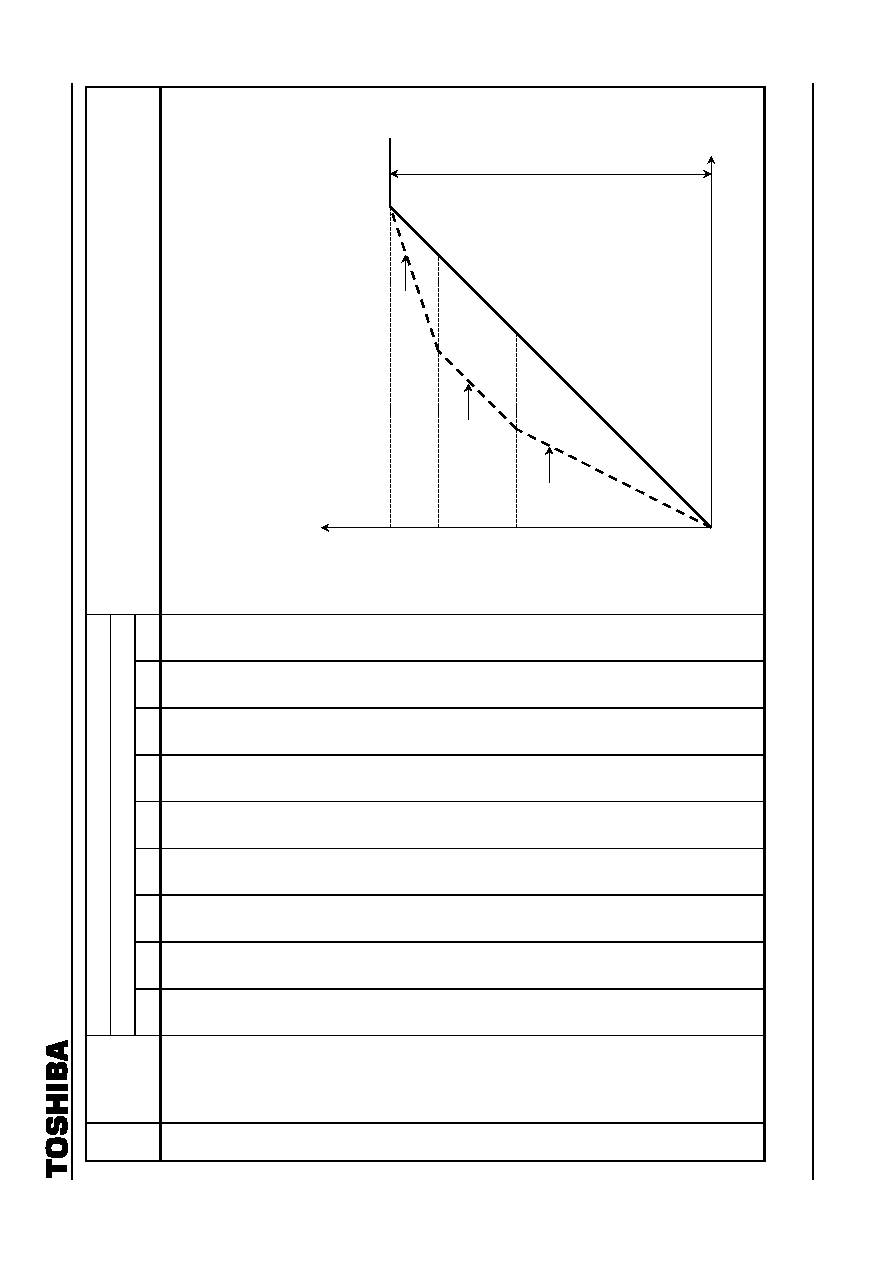

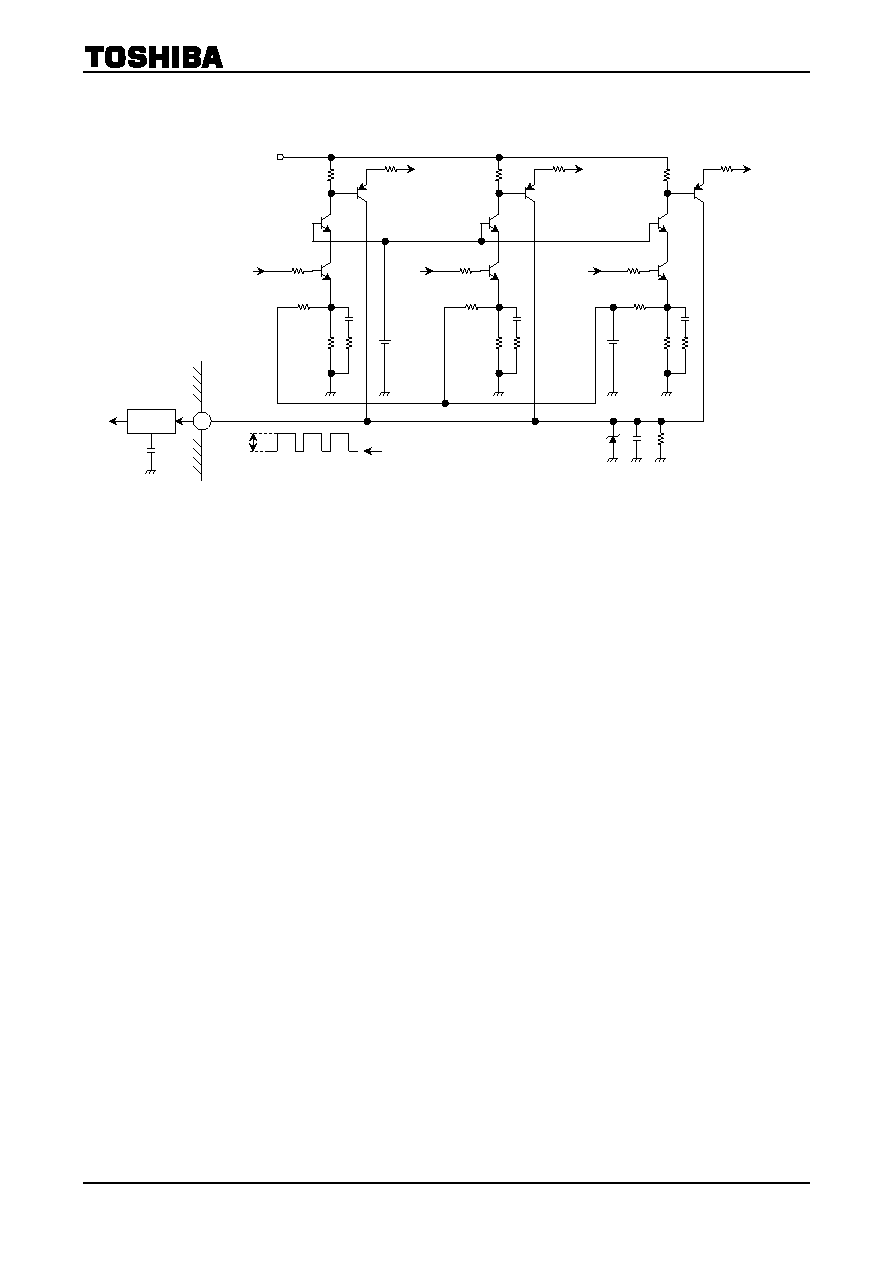

Figure 1 Characteristics of decrease in power dissipation

Ambient temperature Ta (∞C)

P

o

wer

dissi

pati

on P

D

(mW

)

2717

0

150

25 65

1848

0

2297

3378

Printed circuit board B

Printed

circuit

board A

2551

1735

Printed circuit board C

TA1316AN

2002-10-04

34

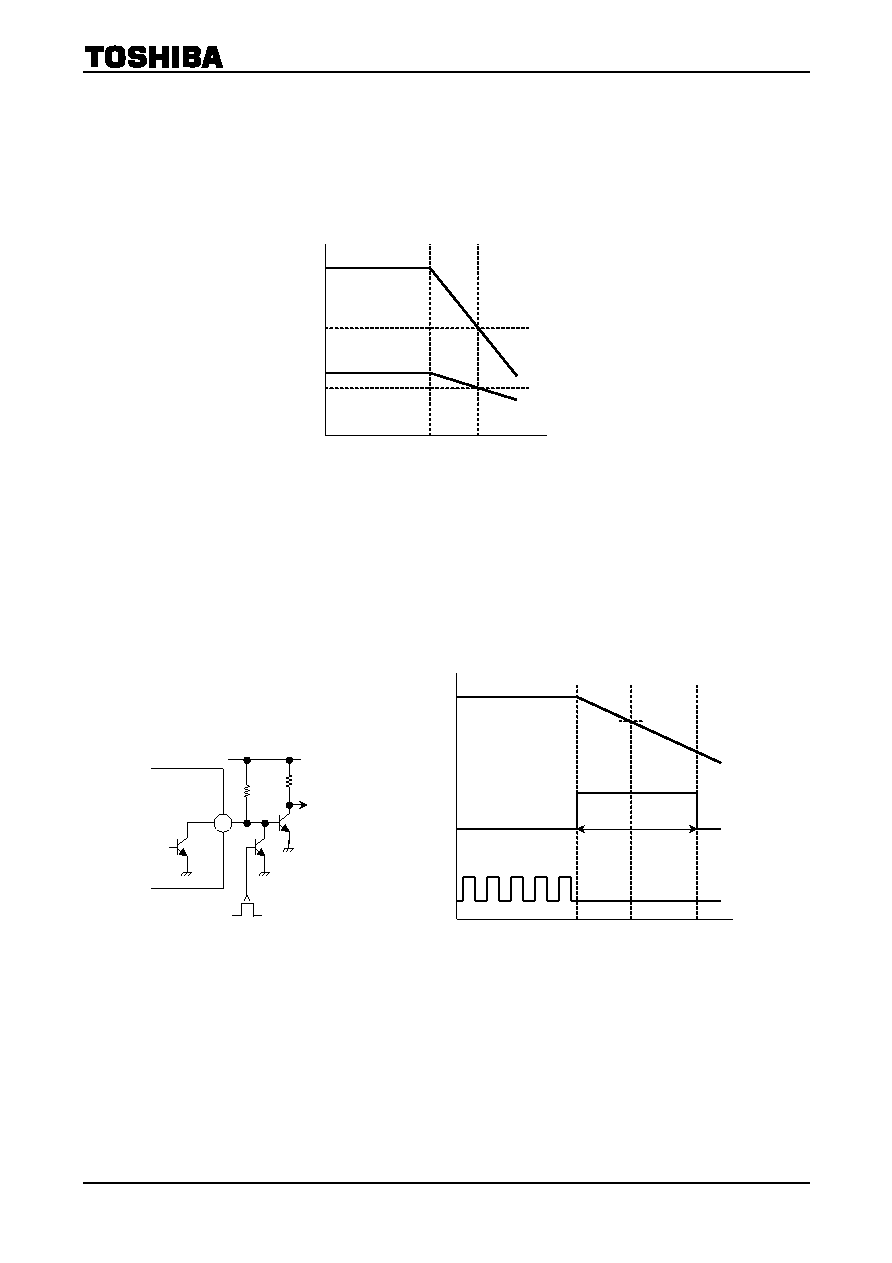

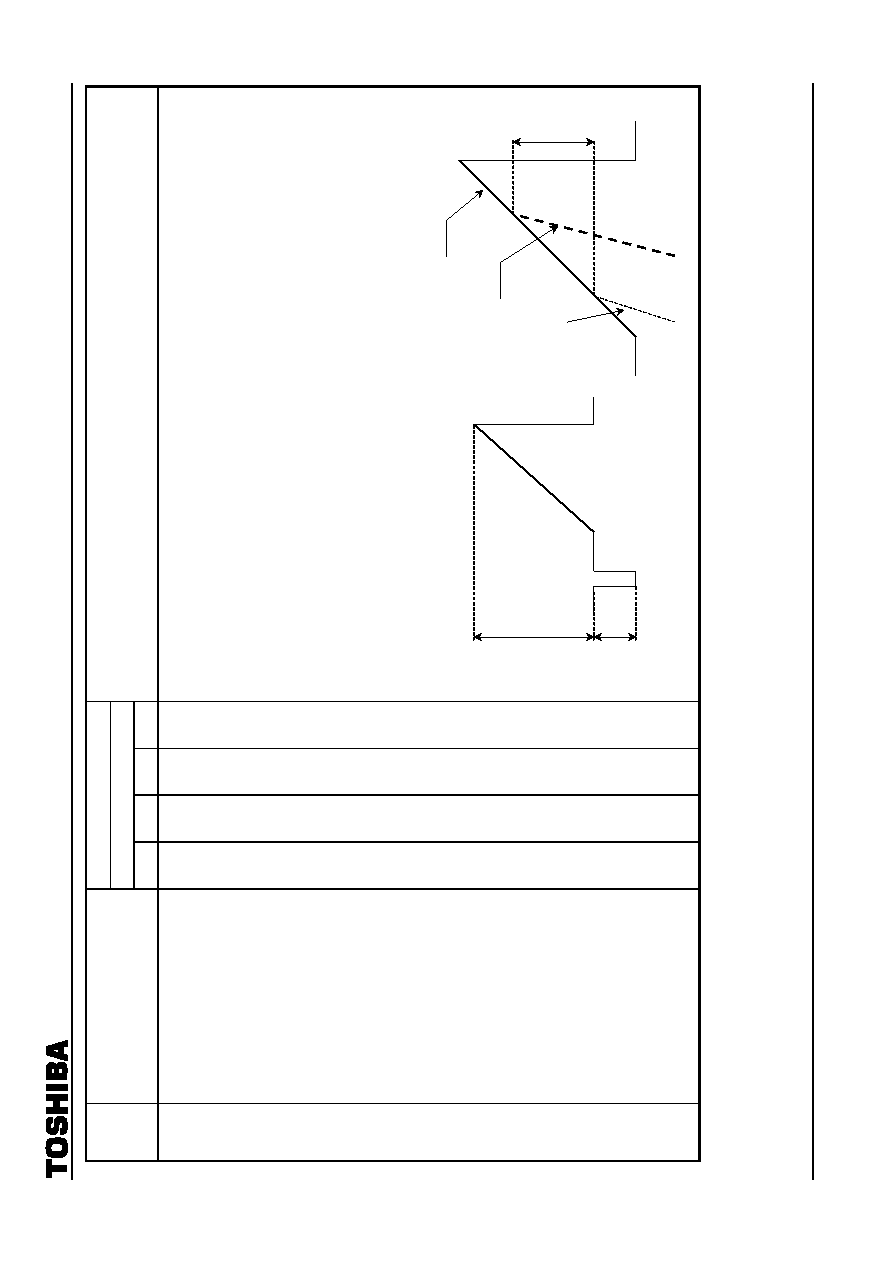

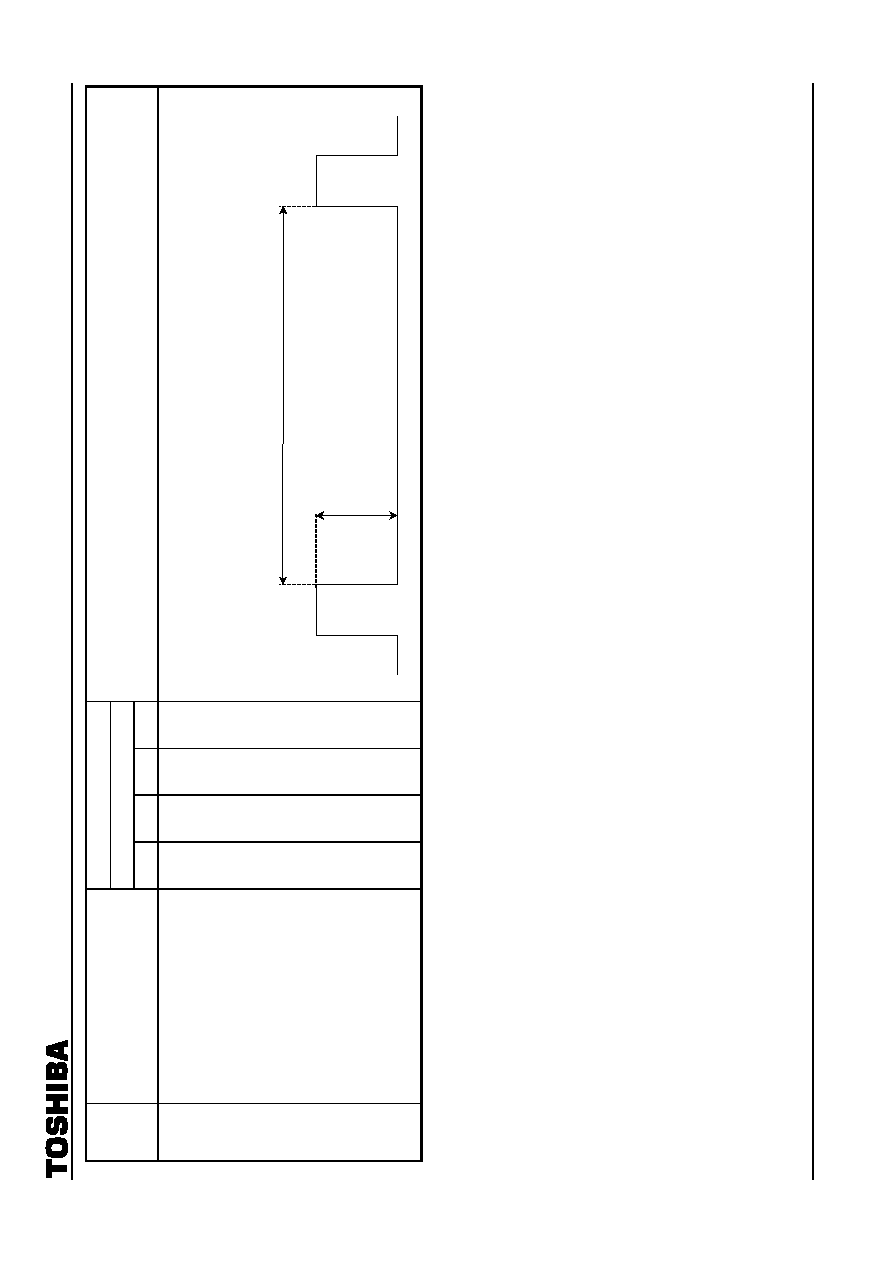

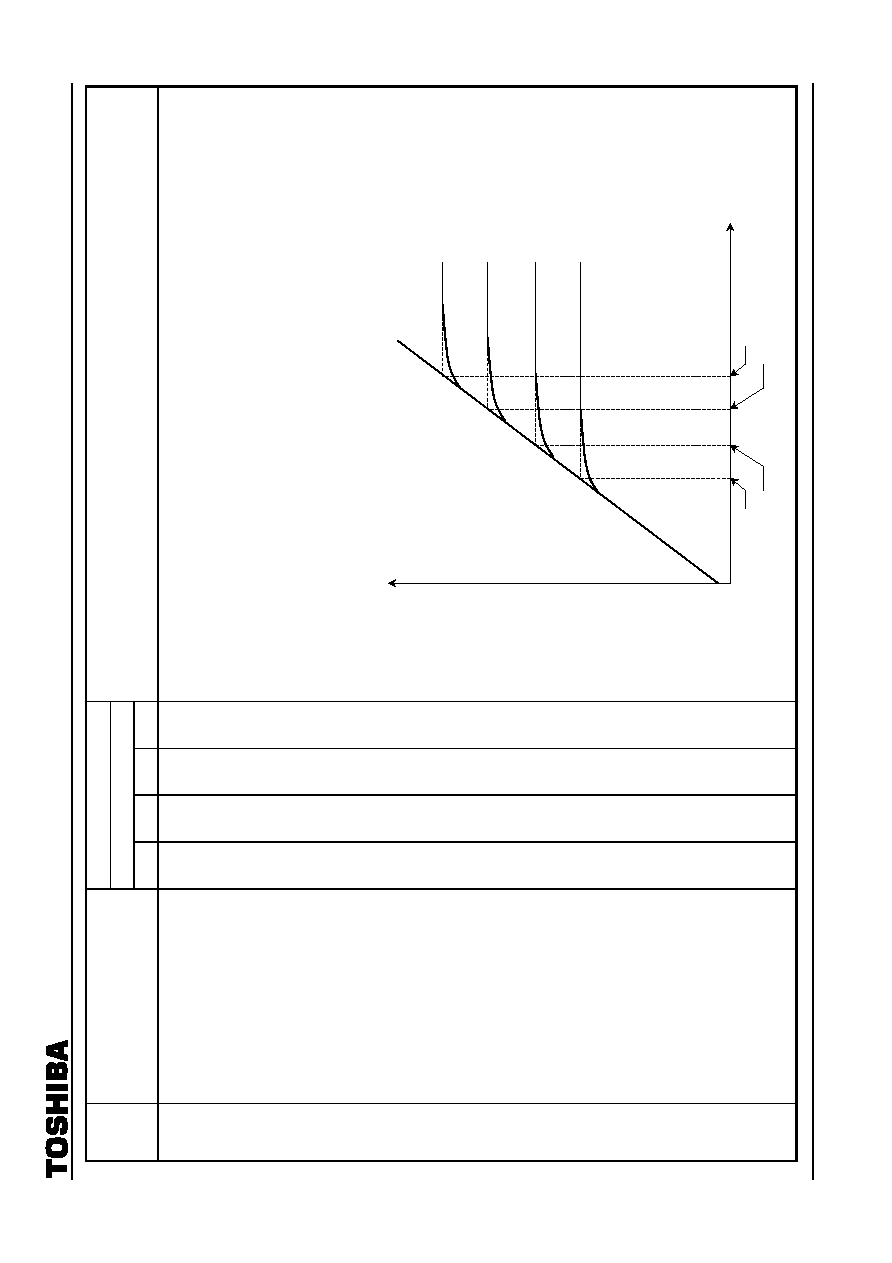

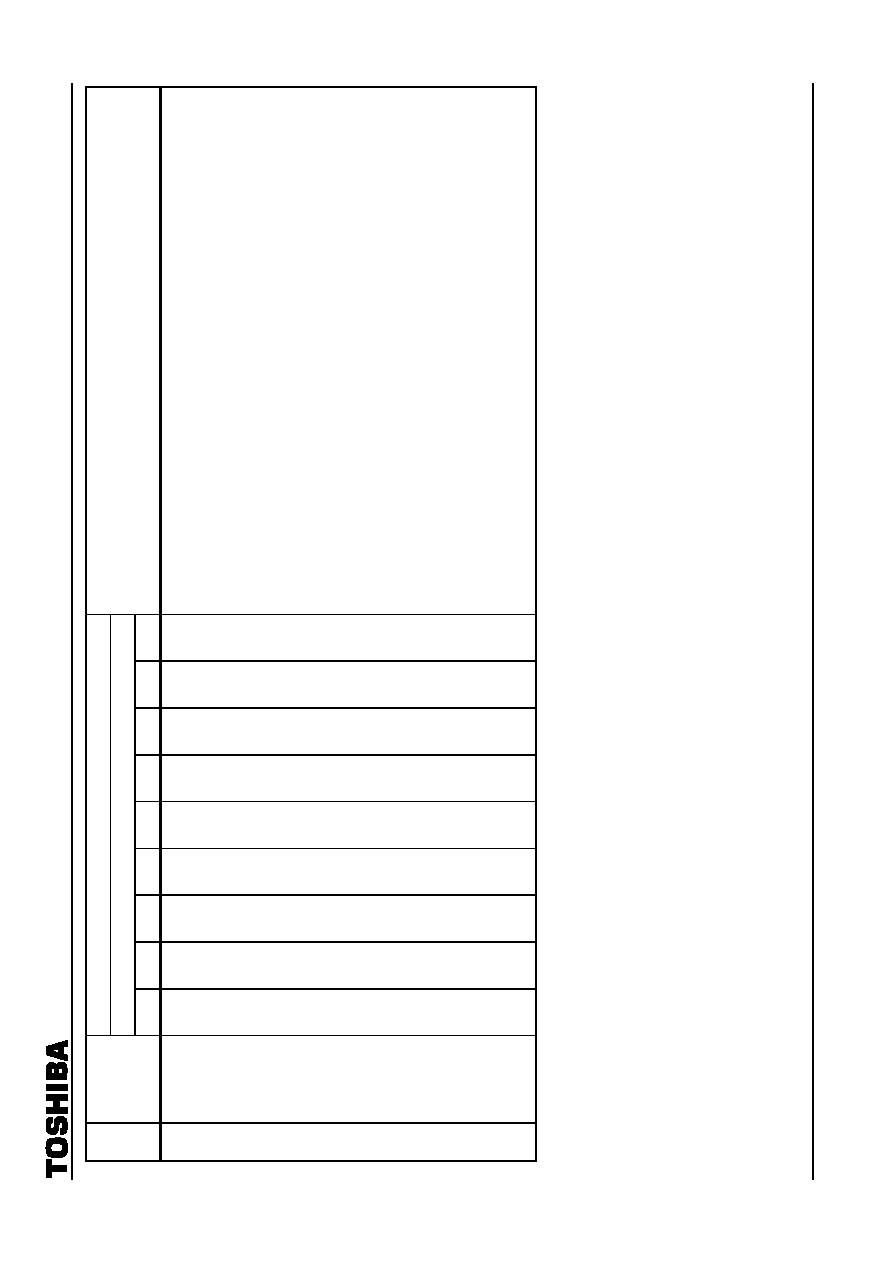

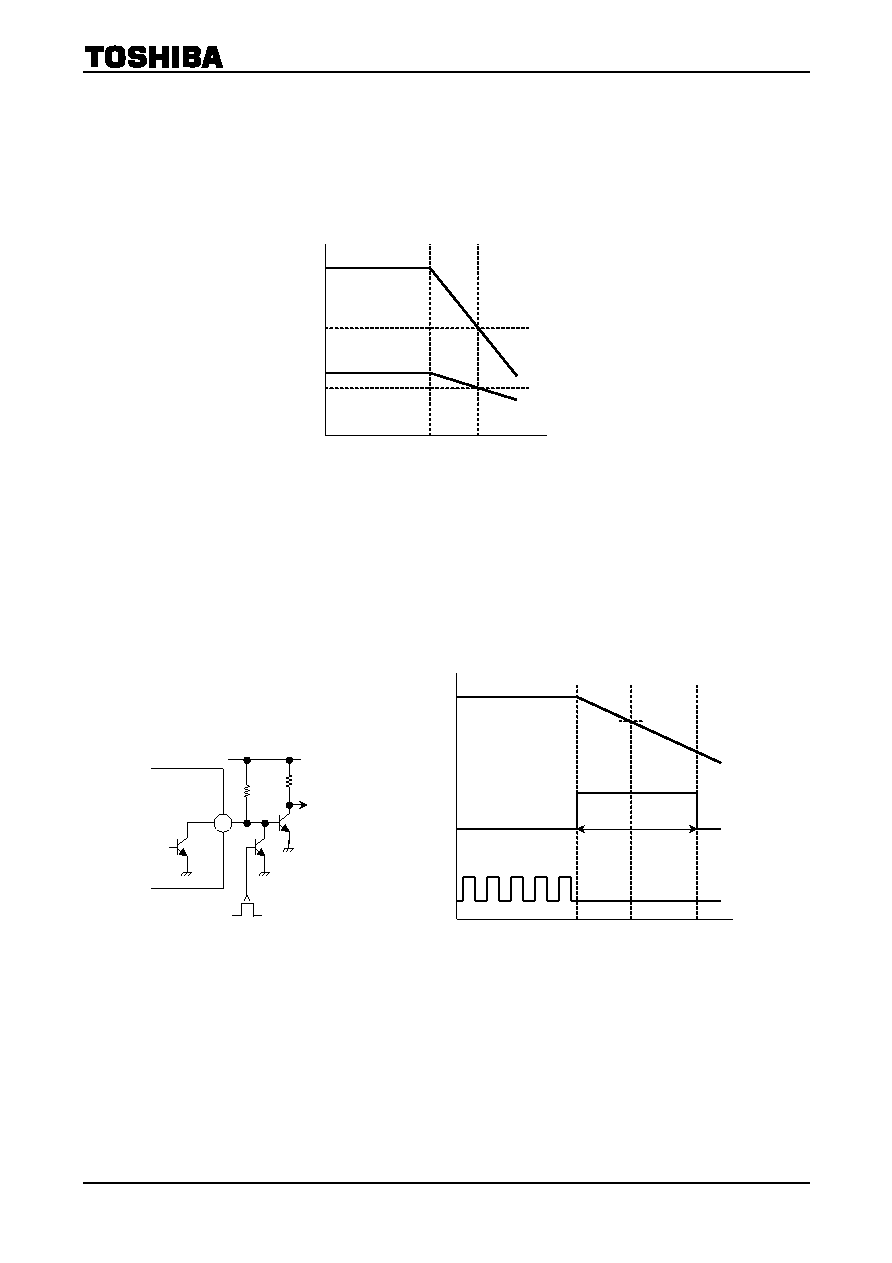

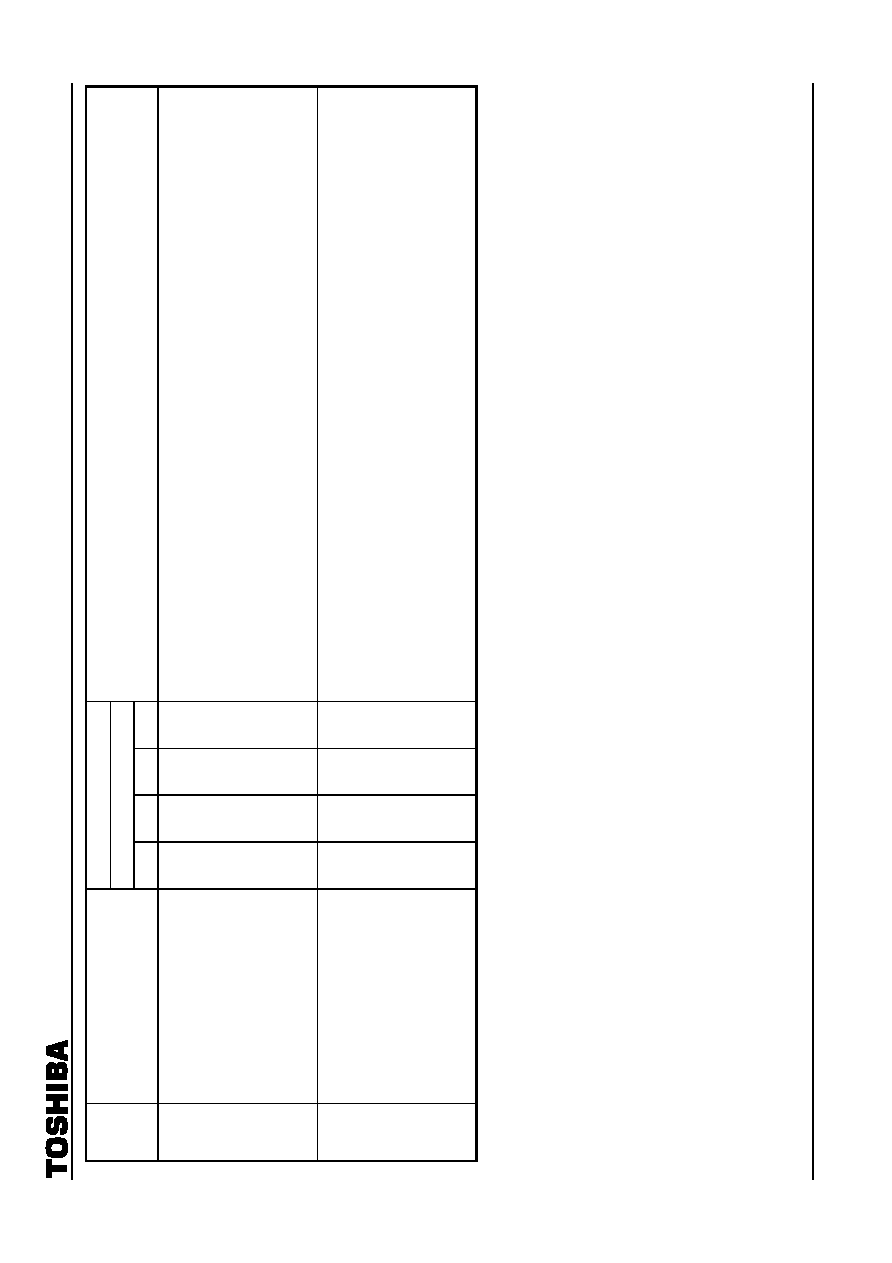

Note 3: Power supply sequence

At power-on, power should be supplied to the IC's power supply pins according to the following sequence:

first to pin 29 (I

2

L V

DD

), then to pin 19 (DEF/DAC V

CC

), and finally to pin 40/pin 55 (RGB V

CC

/YC V

CC

).

Power to pin 29 should be supplied from pin 19 via zener diode through resister.

If power is not supplied to all the power pins or if power is not supplied in the above sequence, BUS preset

will be unsettled and the IC may not function properly.

Especially, when the frequency of H-out (pin 26) will be unsettled, H deflection output transistor may be

broken.

When this IC will be used on CRT, the frequency of H-out should be controlled by pin 22.

t

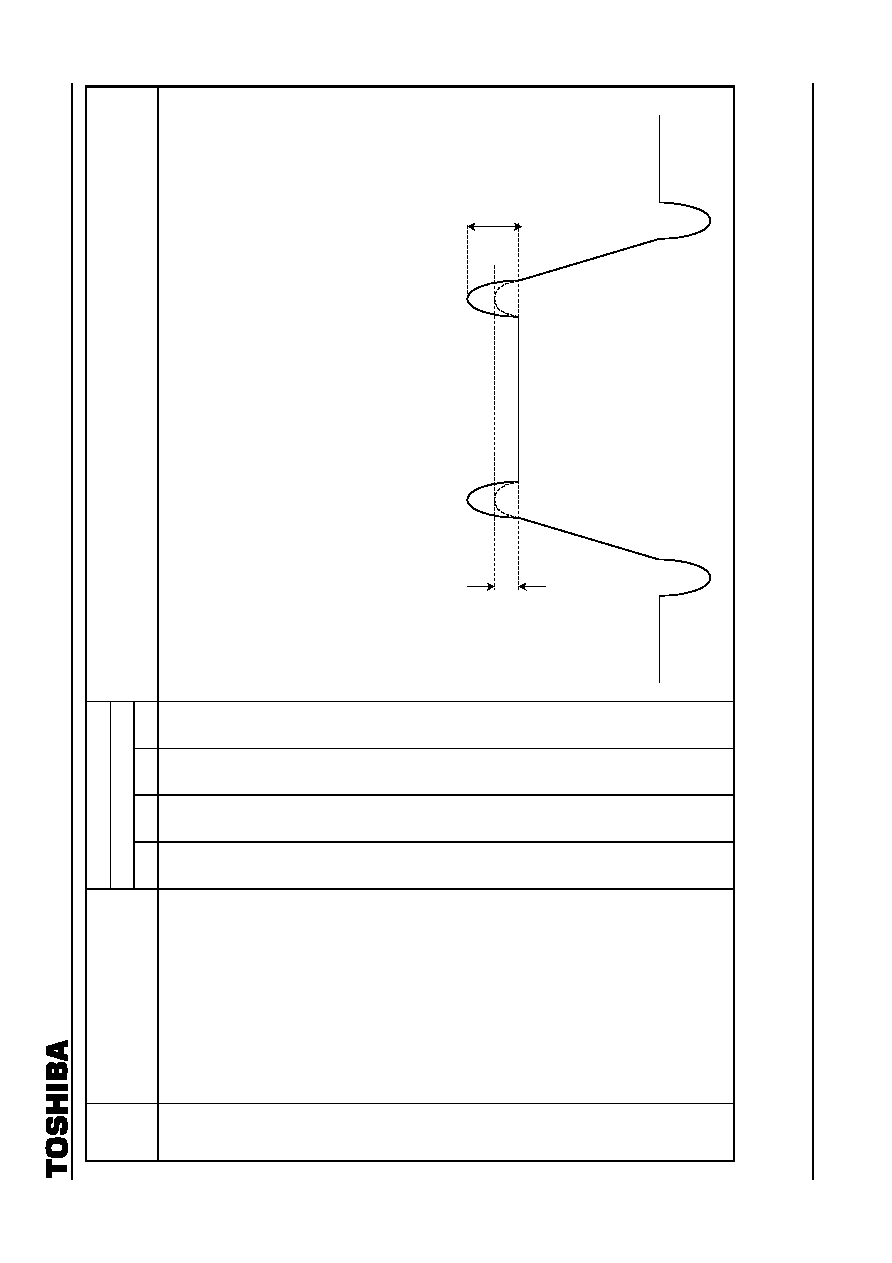

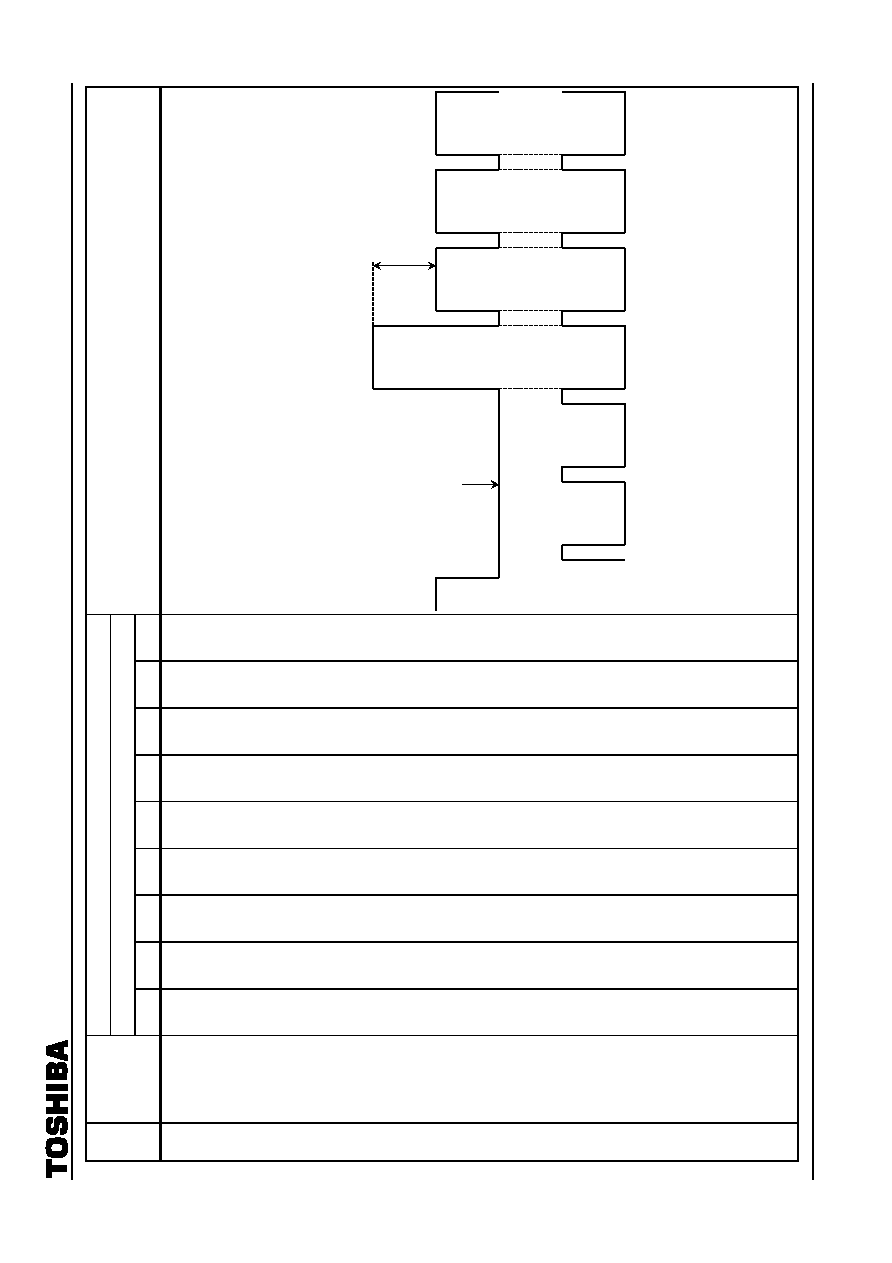

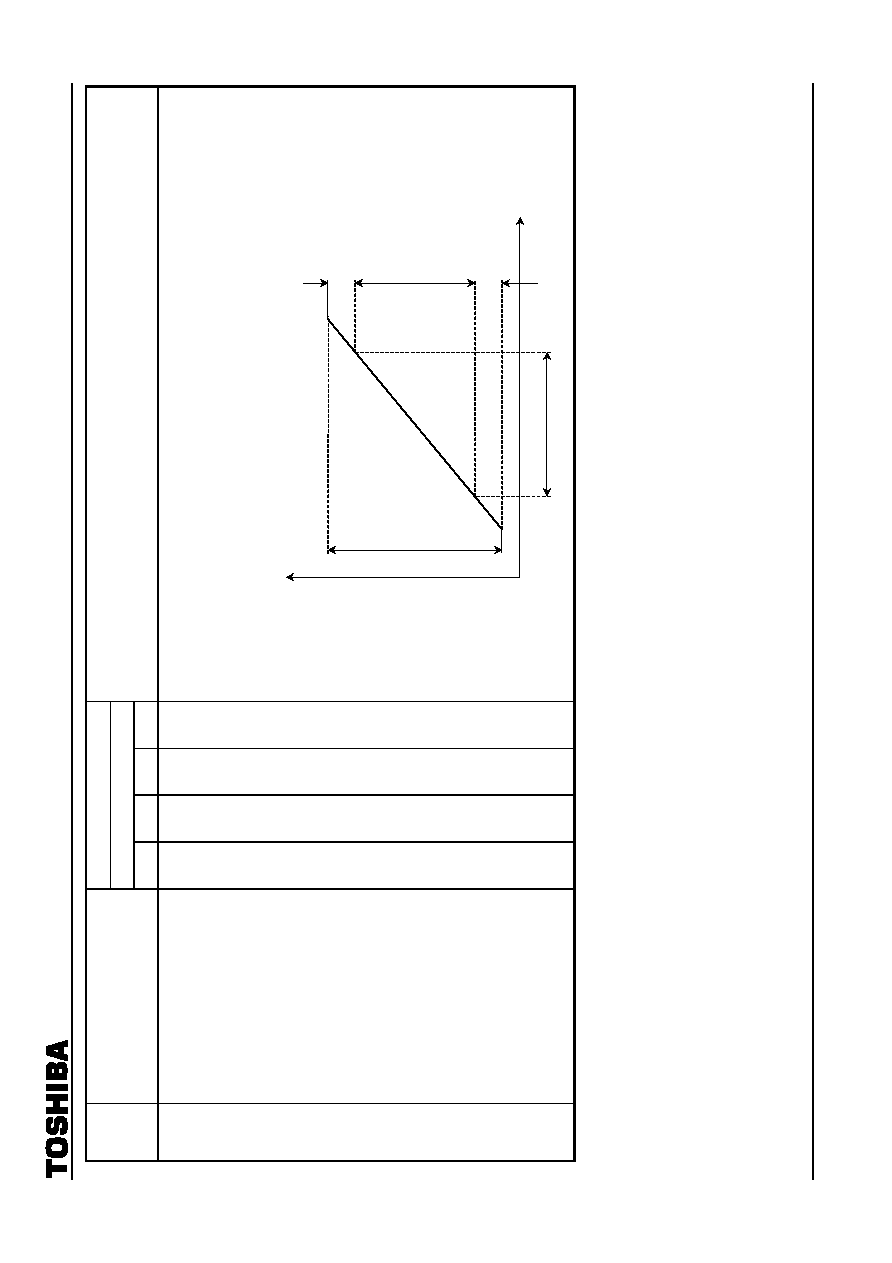

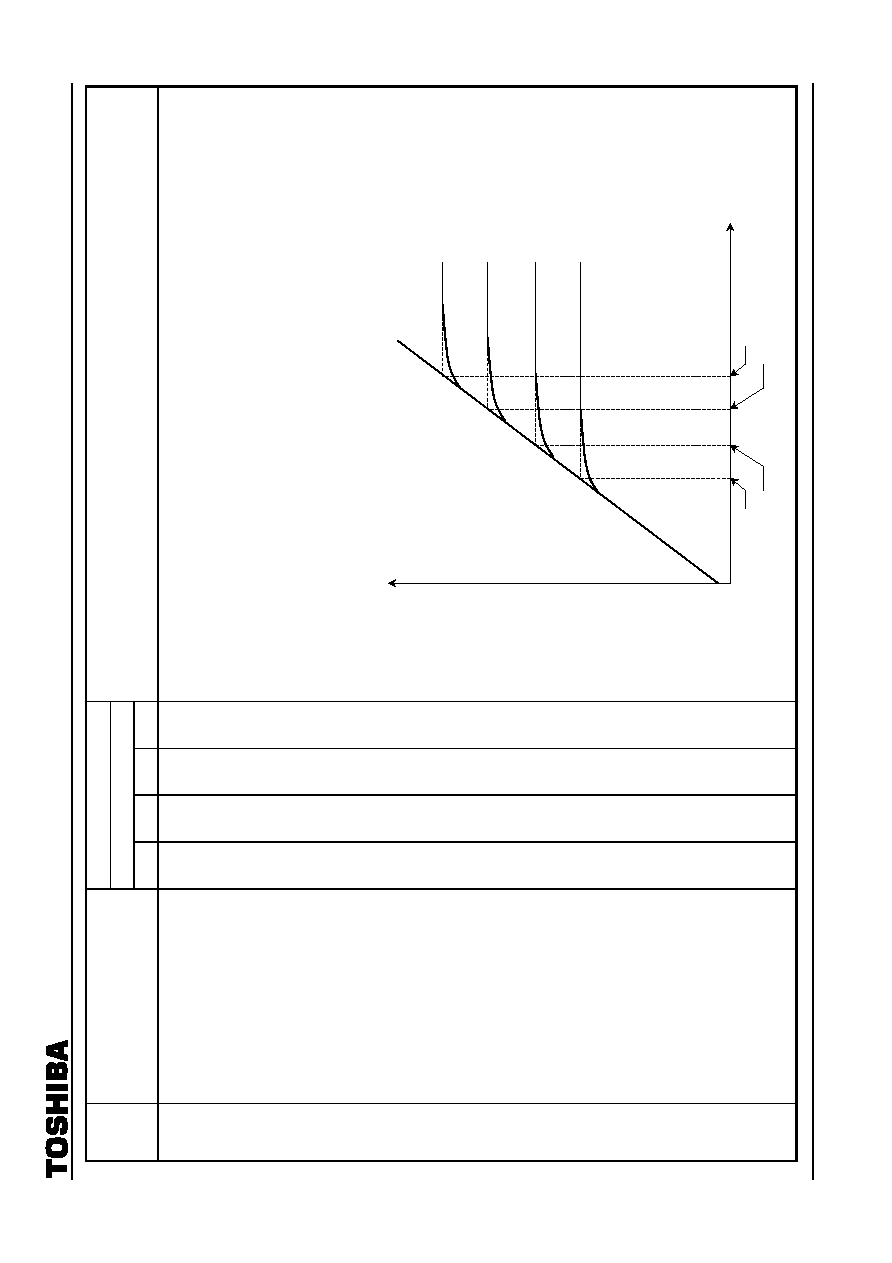

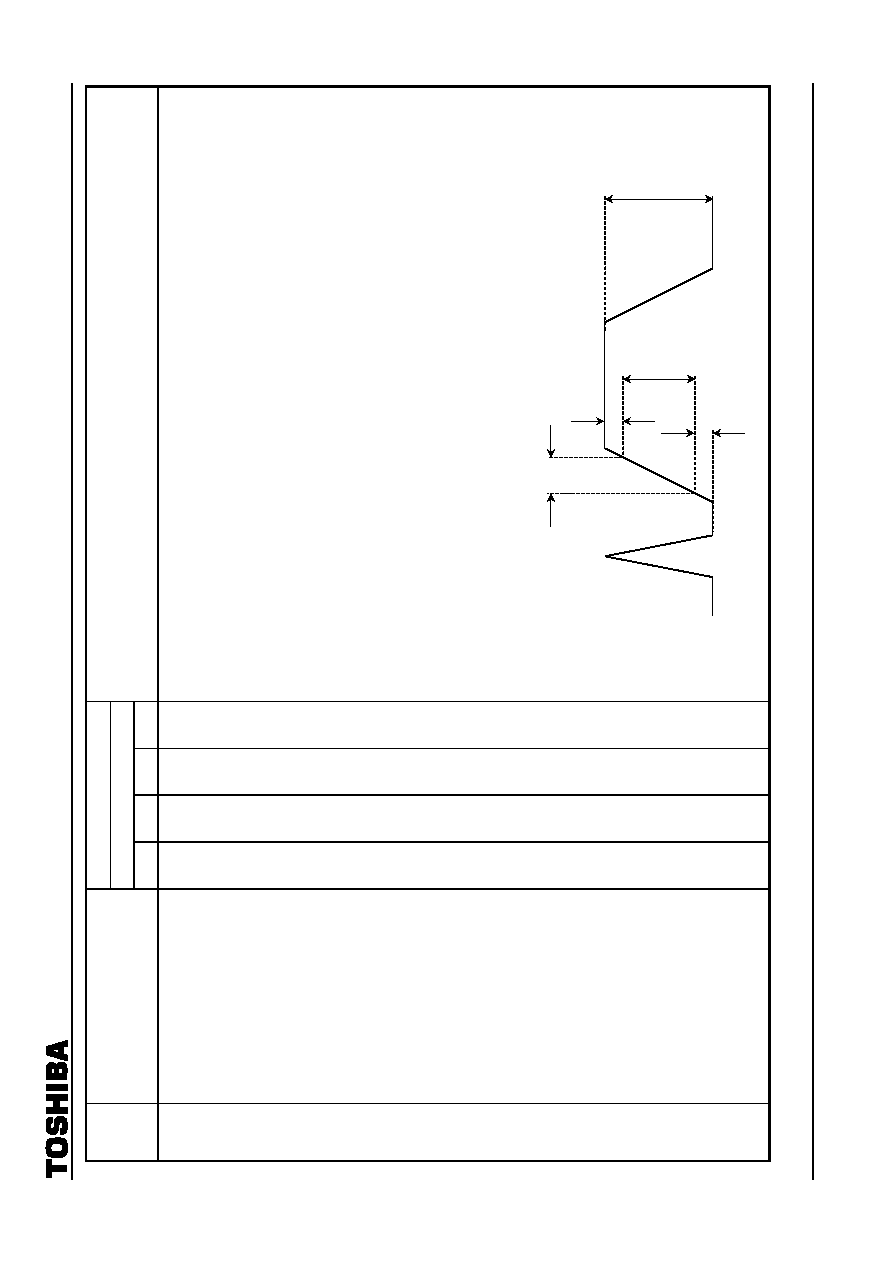

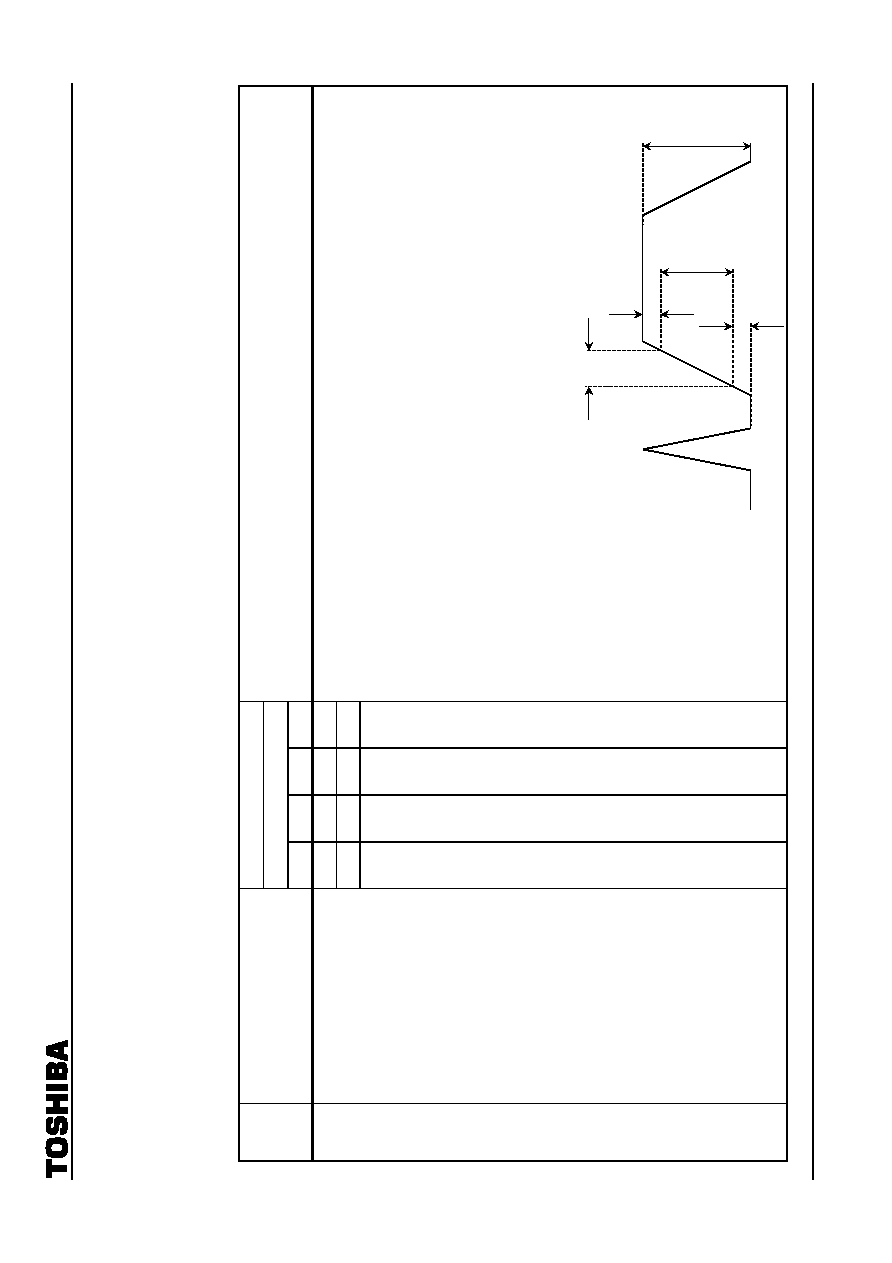

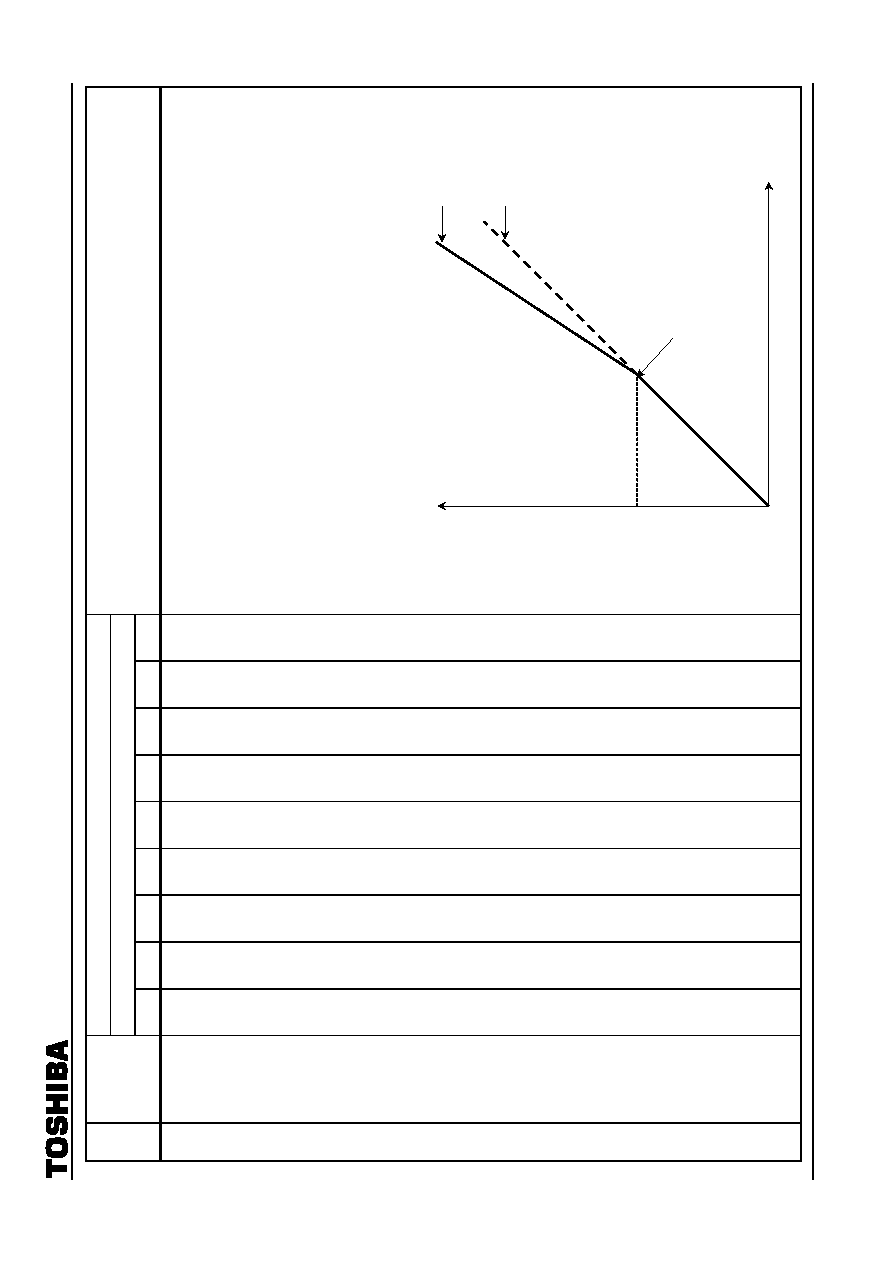

Figure (Note 3) Timing from immediately after power-on to time

at which H-out is output (at Ta

=

=

=

= 25∞∞∞∞C)

I

2

L V

DD

Logic operation 1.5 V (typ.)

Power-on reset (POR) threshold voltage

for bus operation 3.3 V (typ.)

H-out output 5.2 V (typ.)

V DEF/DAC

V

CC

TA1316AN

2002-10-04

35

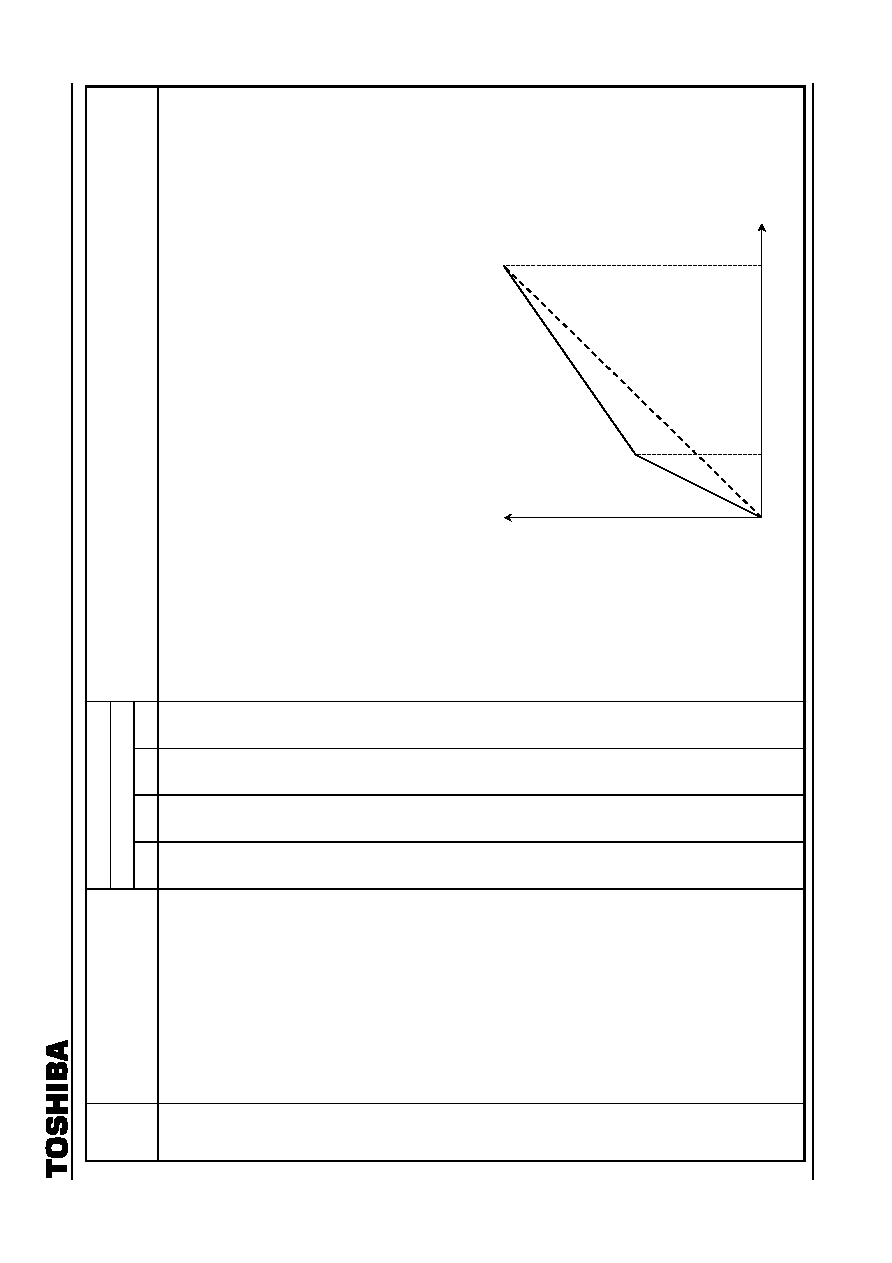

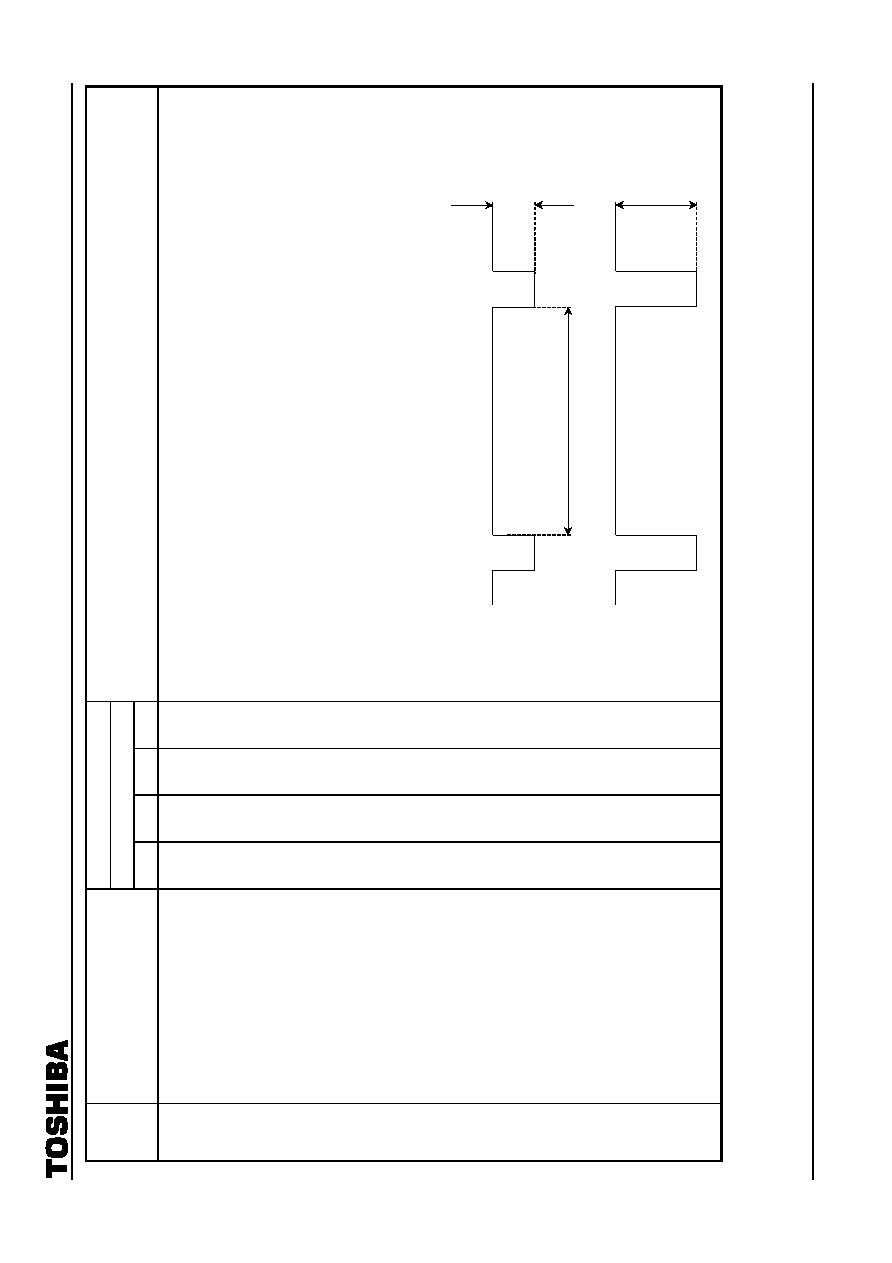

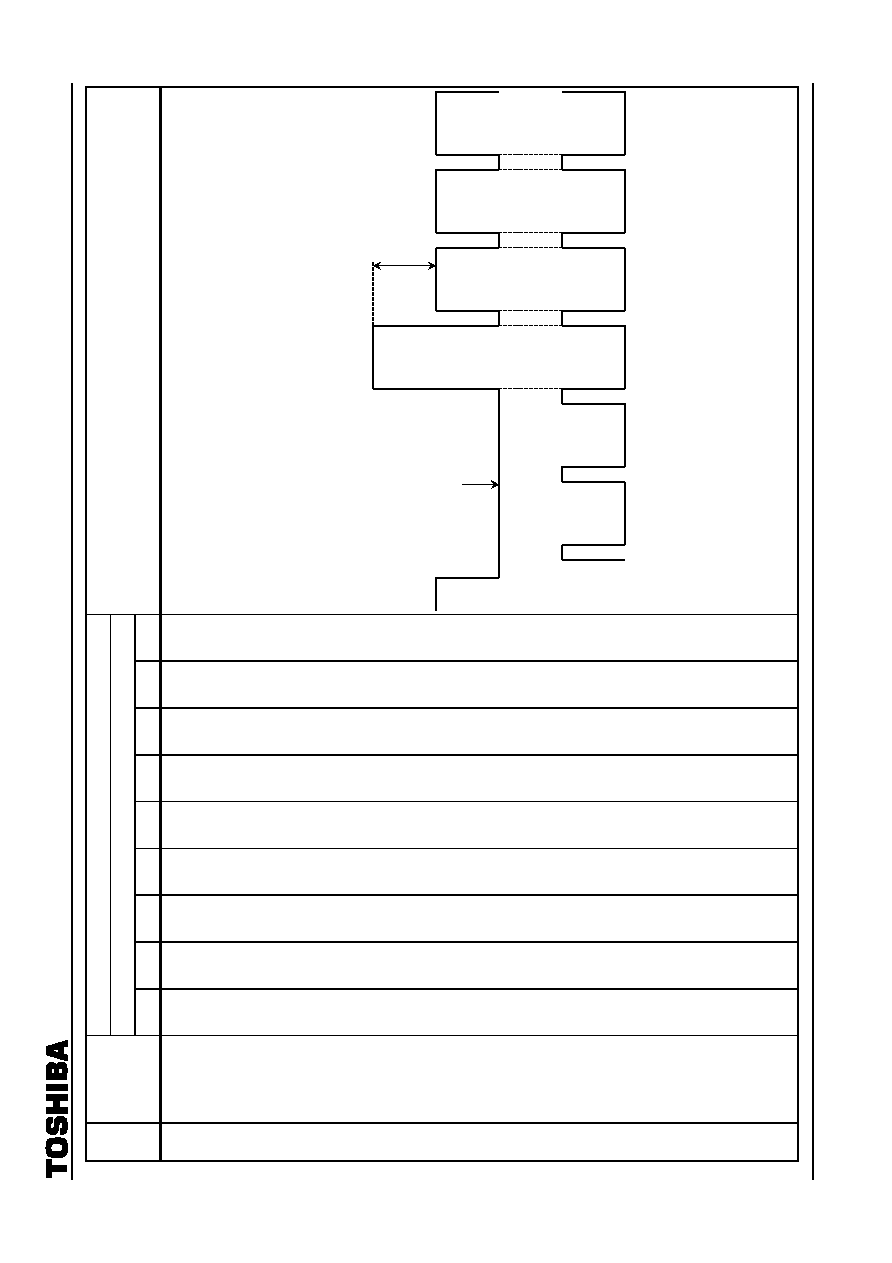

Note 4: V

CC

condition at Power-OFF

At power-off, the last pulse of H-out (pin 26) will become unknown, if I

2

L V

DD

(pin 29) is over 1.7 V at the

timing of H-out stop.

I

2

L V

DD

should be below 1.7 V when DEF/DAC V

CC

(pin 19) will be 6.2 V, which is the maximum voltage

when H-out stops.

Refer to Figure (Note 4-1).

If it is not in the condition of Figure (Note 4-1), it is recommended that H-out will be made LOW at power-off

by external control like micro-processor ang so on. Refer to Figure (Note 4-2).

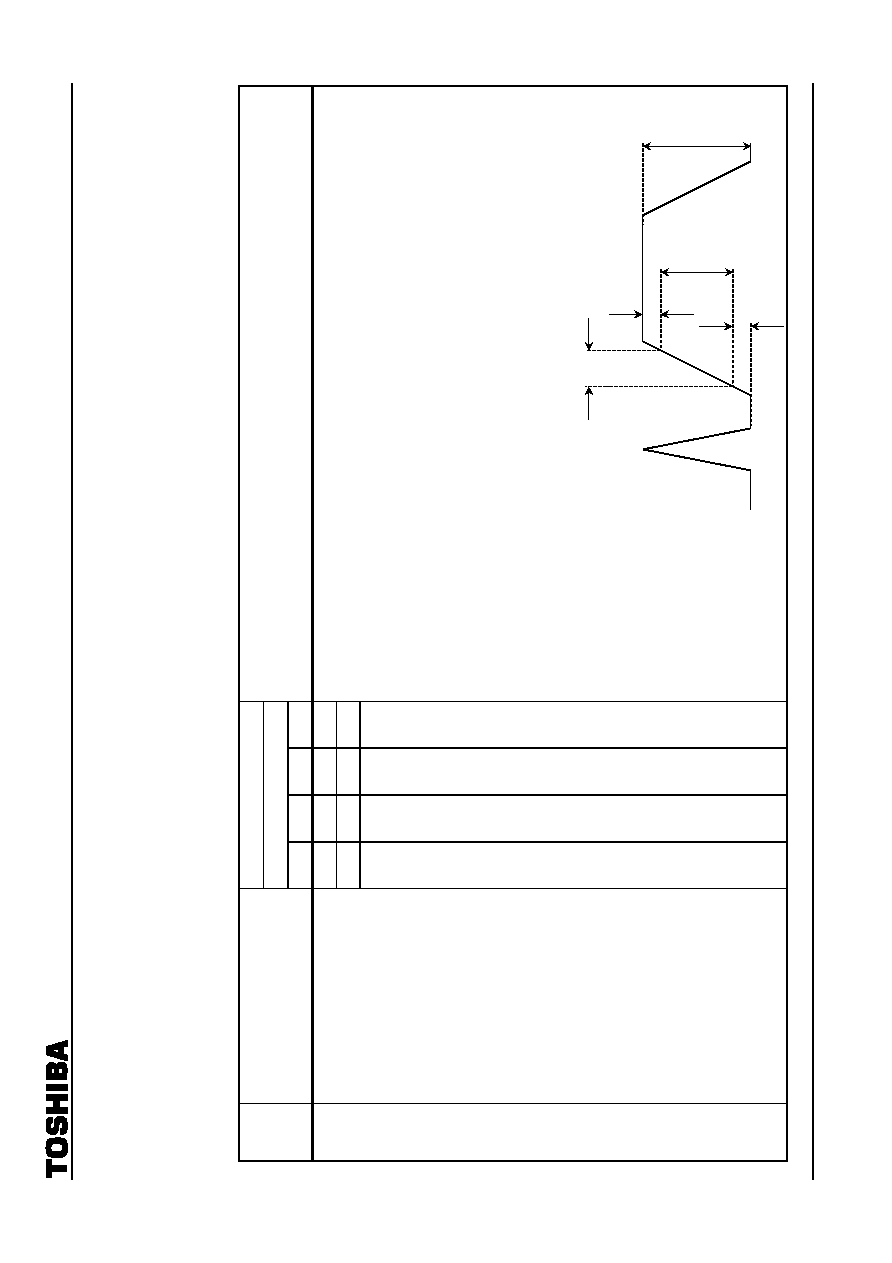

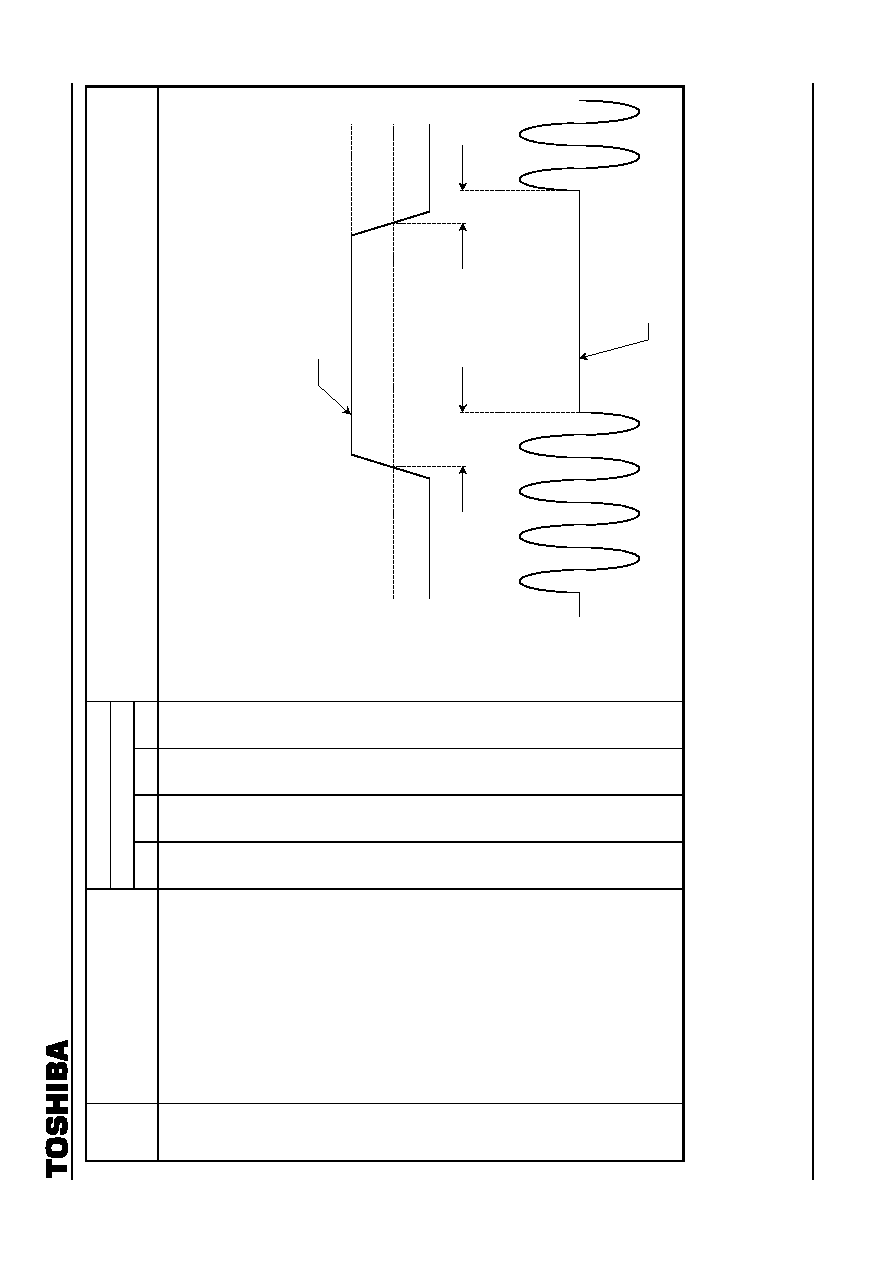

Figure (Note 4-1) V

CC

condition at power-off

6.2 V

t

I

2

L V

DD

(pin 29)

V DEF/DAC V

CC

(pin 19)

H-out stop voltage (max)

below 1.7 V

Po

w

e

r

o

f

f

H-out

st

op

TA1316

26

DEF V

CC

H-out

Control signal by

micro-processor and so on.

H-out waveform

Approximately ten

milli seconds or more

Control signal by micro-processor and so on.

6.2 V

DFF/DAC V

CC

(Pin 19)

Po

w

e

r

O

F

F

H-out

st

op

t

Figure (Note 4-2) Example how to stop H-out

TA1316AN

2002-10-04

36

Recommended Operating Conditions

Characteristics Description

Min

Typ.

Max

Unit

Board

A

(Note1)

8.5 8.8 9.1

Pins 19, 40 and 55

Boards B and C (Note1)

8.7

9.0

9.3

Supply voltage (V

CC

)

Pin

29

1.8 2.0 2.2

V

Y input level

Pins 3 and 8: 100% color bar, including sync (picture

signal: 0.7 V

p-p

)

1.0

Color difference signal input level

Pins 4, 5, 9 and 10: 100% color bar, no sync

0.7

V

p-p

Matrix switching voltage

Pin 7

2.0

3.0

5.0

V

HD/VD input level

Pins 12, 13, 15 and 16

2.0

5.0

9.0

SYNC input level

Pin 14: 100% color bar, including sync

0.9

1.0

1.1

V

p-p

CP

4.7 5.0 9.0

SCP input level

Pin 17

BPP

2.2 2.5 2.8

15.75

kHz

8.0 9.0 9.0

31.5

kHz

5.0 6.0 7.0

33.75

kHz

2.0 3.0 4.0

Horizontal frequency switching

voltage

Pin 22

45 kHz

0

0

1.0

H-AFC

4.0 5.0 9.0

FBP input level

Pin 24

H-BLK 1.7

2.25

2.8

V

H-OUT input current

Pin 26

9.0 15.0

DAC input current

Pins 28 and 36

0.3 1.0

mA

SCL/SDA pull-up voltage

Pins 30 and 31

3.3

5.0

9.0

V

SDA input current

Pin 31

2 mA

Analog RGB input level

Pins 35, 34 and 33: White 100%

0.7

Analog OSD input level

Pins 37, 38 and 39: White 100%

0.7

V

p-p

Y

S

3

switching

voltage

Pin

49

1.5 5.0 9.0

OSD

2.9 5.0 9.0

Y

S

1/2 switching voltage

Pins 51 and

50

VSM

MUTE

1.1 1.5 1.7

BLK

7.0 9.0 9.0

P-MUTE

2.7 3.2 4.0

Y

M

switching voltage

Pin 52

HALF

TONE

1.2 1.5 1.8

V

External V-BLK input current

Pin 27

0.78

1 mA

Note1: For the parameter values for boards A, B and C, please refer to the table entitled Maximum Ratings.

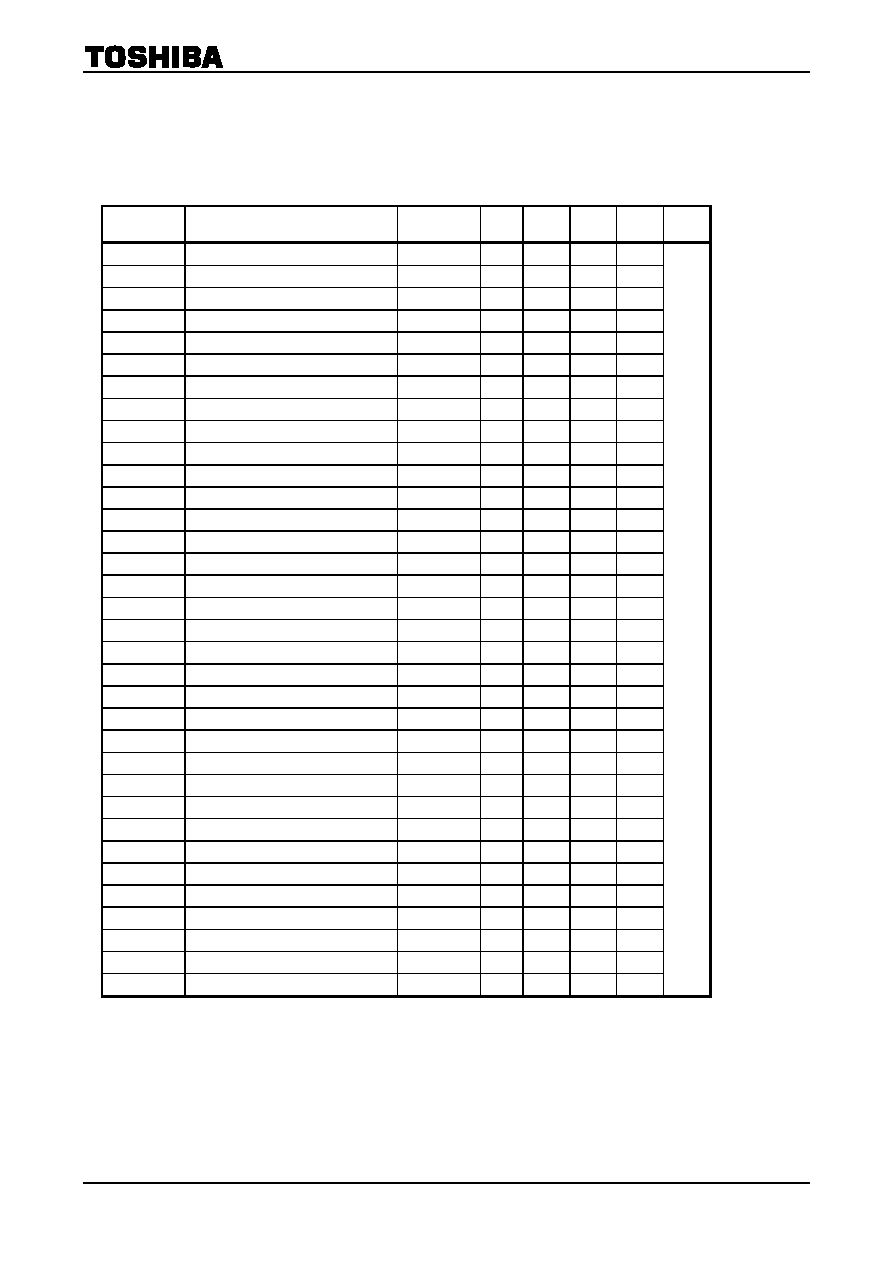

Electrical Characteristics

(V

CC

=

=

=

= 9 V/2 V, Ta ==== 25∞C, unless otherwise specified)

Current Dissipation

Pin Name

Symbol

Test

Circuit

Min Typ. Max Unit

DEF/DAC V

CC

I

CC1

21.0 24.2 26.9

RGB V

CC

I

CC2

55.3 63.6 70.8

I

2

L V

DD

I

CC3

21.0 24.1 26.8

Y/C V

CC

I

CC4

39.3 45.3 50.3

mA

TA1316AN

2002-10-04

37

Pin Voltage

Test Condition

(1) BUS

= Preset

(2) SW1

= B, SW2 = B, SW3 = C, SW4 = B, SW5 = B, SW7 = A, SW8~10 = B, SW14 = B, SW20 = ON,

SW23 = B, SW24 = A, SW26 = A, SW33~35 = A, SW37~39 = A, SW54 = OFF, SW56 = ON

Pin No.

Pin Name

Symbol

Test

Circuit

Min Typ. Max Unit

2 BPH

FILTER

V

2

5.5 5.8 6.1

3 Y1

IN

V

3

4.7 5.0 5.3

4 Cb/Pb1

IN

V

4

4.7 5.0 5.3

5 Cr/Pr1

IN

V

5

4.7 5.0 5.3

7 MATRIX

SW

V

7

2.0 3.0 4.0

8 Y2

IN

V

8

4.7 5.0 5.3

9 Cb/Pb2

IN

V

9

4.7 5.0 5.3

10 Cr/Pr2

IN

V

10

4.7 5.0 5.3

11 COLOR

LIMITER

V

11

6.65 6.9 7.15

12 VD2

IN

V

12

0 0 0.3

13 HD2

IN

V

13

0 0 0.3

14 SYNC

IN

V

14

1.6 2.0 2.4

15 VD1

IN

V

15

0 0 0.3

16 HD1

IN

V

16

0 0 0.3

17 SCP

IN

V

17

3.9 4.4 4.9

20 AFC

FILTER

V

20

5.8 6.5 7.2

21 HVCO

V

21

5.0 5.3 5.6

23 H

CURVE

CORRECTION

V

23

2.2 2.5 2.8

33

ANALOG B IN

V

33

3.65 3.95 4.25

34 ANALOG

G

IN

V

34

3.65 3.95 4.25

35 ANALOG

R

IN

V

35

3.65 3.95 4.25

37

ANALOG OSD B IN

V

37

3.65 3.95 4.25

38 ANALOG

OSD

G

IN

V

38

3.65 3.95 4.25

39

ANALOG OSD R IN

V

39

3.65 3.95 4.25

46 B

S/H

V

46

3.5 4.0 4.5

47 G

S/H

V

47

3.5 4.0 4.5

48 R

S/H

V

48

3.5 4.0 4.5

49 Y

S

3 V

49

0.0 0.1 0.2

50 Y

S

2 V

50

0.0 0.1 0.2

51 Y

S

1 V

51

0.0 0.1 0.2

52 Y

M

V

52

0.0 0.1 0.2

53 ABCL

IN

V

53

5.85 6.1 6.35

54 VSM

OUT

V

54

4.2 4.4 4.6

56 APL

FILTER

V

56

4.8 5.0 5.2

V

TA1316AN

2002-10-04

38

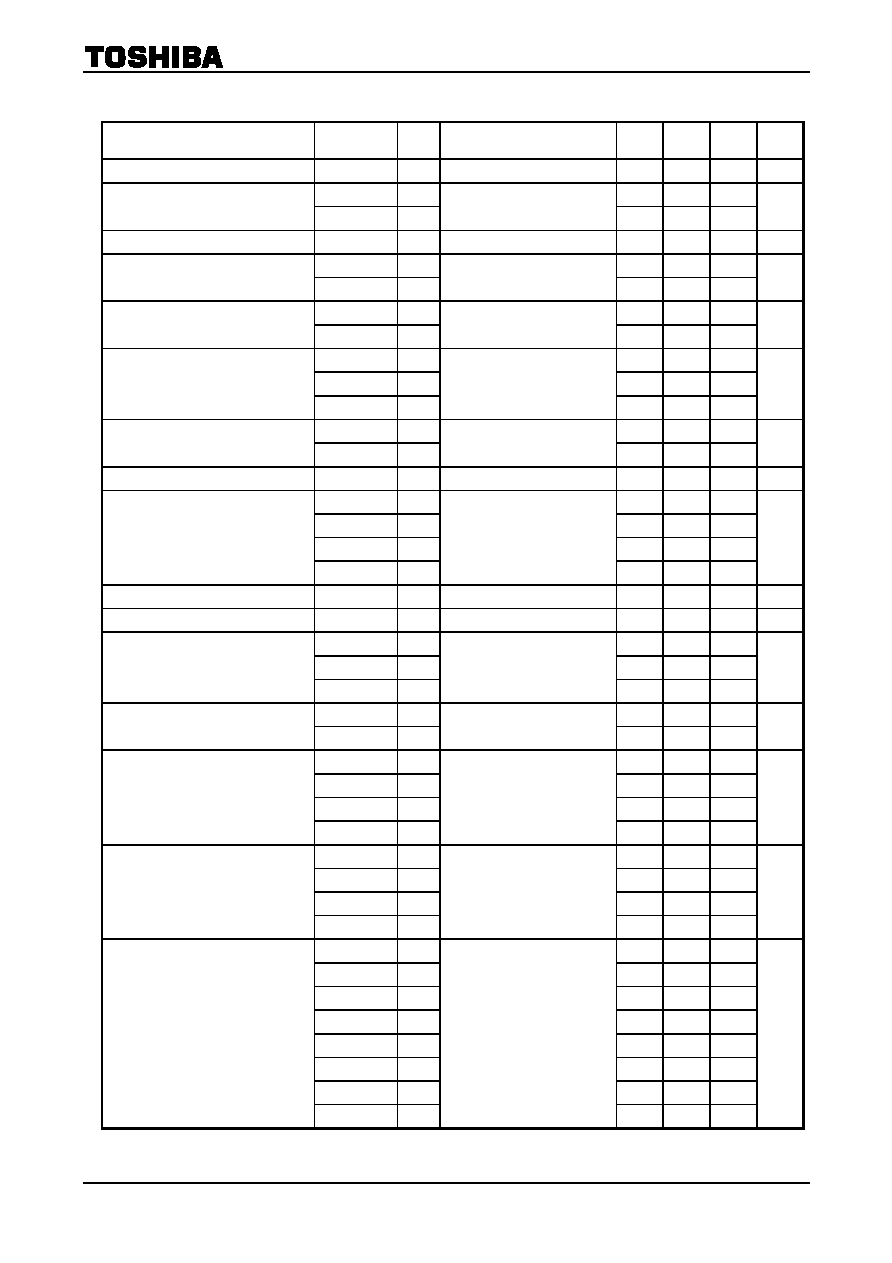

Luminance Block

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

Y input dynamic range

D

RY

0.7

1.0

1.5

V

p-p

V

B

-15

-5

5

Black detection level shift

V

B3

(Note P01)

35

45

55

mV

Black stretch amplifier maximum gain

G

BS

(Note P02)

2.5

3.0

3.5

dB

P

BST1

31

34

37

Black stretch start point 1

P

BST2

(Note P03)

50

53

56

IRE

P

BS1

0

5

10

Black stretch start point 2

P

BS2

(Note P04)

19

24

29

IRE

DV

001

30

50

70

DV

010

80

100

120

Dynamic ABL detection voltage

DV

100

(Note P05)

190

220

250

mV

S

DAMIN

0.005

0.02

Dynamic ABL sensitivity

S

DAMAX

(Note P06)

0.29

0.32

0.35

V/V

Black level correction

BLC

(Note P07)

7.0

8.5

10

IRE

P

DGP00

17

20

23

P

DGPA

0.5

1.5

2.5

P

DGPB

2

3.5

5

Dynamic Y

correction point

P

DGPC

(Note P08)

3

5

7

IRE

Dynamic Y

gain

G

DG

(Note P09)

2

3

4

dB

Static Y

dark area gain

G

SG

(Note P10)

1.3

1.7

2.2

dB

ADT

100

0.9

1.1

1.2

ADT

135

1.2

1.35

1.5

DC restoration gain

ADT

65

(Note P11)

0.55

0.7

0.85

times

V

DT0

-5

0

5

DC restoration start point

V

DT1

(Note P12)

47

51

55

%

P

DTL11

54

57

61

P

DTL10

67

71

75

P

DTL01

74

78

82

DC restoration limit point

P

DTL00

(Note P13)

74

78

82

%

F

AP00

12.2

13.5

14.9

F

AP01

8.5

9.5

10.5

F

AP10

6.5

7.3

8.1

Sharpness control peak frequency

F

AP11

4.2

4.7

5.2

MHz

G

MAX00

13

16

18

G

MIN00

-15

-8

-4

G

MAX01

14

17

19

G

MIN01

-20

-14

-7

G

MAX10

14

17

19

G

MIN10

-25

-16

-7

G

MAX11

14

18

20

Sharpness control range

G

MIN11

(Note P14)

-30

-20

-8

dB

TA1316AN

2002-10-04

39

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

G

CEN00

7.5

10

12.5

G

CEN01

8

11

13

G

CEN10

8

11

13

Sharpness control center

characteristic

G

CEN11

(Note P15)

9

12

14

dB

G

YNRT00

-15

-8

-4

G

YNRF00

-3

-1

1

G

YNRT01

-20

-12

-8

G

YNRF01

-3

-1

1

G

YNRT10

-20

-13

-8

G

YNRF10

-2

-0.5

1.5

G

YNRT11

-25

-12

-8

YNR characteristic

G

YNRF11

(Note P16)

-2

0

2

dB

T

SRT00

0.05

0.4

0.7

T

SRT01

0.5

1

2

T

SRT10

1.5

2

4

Control of SRT response to 2T pulse

input

T

SRT11

(Note P17)

3.5

5

7

dB

VSM peak frequency

F

VSM

15

19

22.8

MHz

G

V000

-39

-35

G

V001

2

3

4

G

V010

5.5

6.5

7.5

G

V011

9.5

11

12

G

V100

12.5

13.8

15

G

V101

14.5

16

17.5

G

V110

15.5

16.8

18.5

VSM gain

G

V111

(Note P18)

17.5

18.6

19.5

dB

V

SR49

0.62

0.72

0.85

V

SR50

0.62

0.72

0.85

Threshold voltage of VSM muting

V

SR51

Pins 49, 50 and 51

0.62

0.72

0.85

V

T

VM49A

0

30

100

T

VM49B

0

30

100

T

VM50A

0

30

100

T

VM50B

0

30

100

T

VM51A

0

30

100

Response time for VSM muting

T

VM51B

(Note P19)

0

30

100

ns

V

LU

0.58

0.65

0.75

VSM limit

V

LD

(Note P20)

0.55

0.62

0.75

V

p-p

Delay time from Y input to R output

T

YR

(Note P21)

96

120

144

ns

YDLA

3

5

7

YDLB

7

10

13

Y delay time switch

YDLC

(Note P22)

11

15

19

ns

G

AMIN

-5

-3.2

-2.0

G

BMIN

1

2

3.5

G

AMAX

0.3

1.0

1.7

Transfer distortion correction

G

BMA X

(Note P23)

-3.0

-1.5

-1.0

dB

TA1316AN

2002-10-04

40

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

G

CDE00

5.5

6.8

8

G

CDE01

5.5

6.8

8

G

CDE10

5.5

6.8

8

Color detail enhancer

G

CDE11

(Note P24)

5.5

6.8

8

dB

F

YD00

4.4

5.5

6.6

F

YD01

2.9

3.7

4.5

F

YD10

11.6

14.5

17.4

Y detail frequency

F

YD11

8

10

12

MHz

G

YDMAX00

6

9

12

G

YDMAX01

7

10

13

G

YDMAX10

2.5

5.5

8.5

G

YDMAX11

3

6

9

G

YDCEN00

3.5

6.5

9.5

G

YDCEN01

4

7

10

G

YDCEN10

-2

0.8

2

G

YDCEN11

-1

1

2

G

YDMIN00

0

1.5

3

G

YDMIN01

0

2

4

G

YDMIN10

-8

-5

-2

Y detail control range

G

YDMIN11

(Note P25)

-18

-15

-12

dB

G

WPL1

-10

-7

-4

G

WPL2

-7

-4.8

-2

APACON white peak limiter

G

WPL3

(Note P26)

-5

-2.3

-0.5

dB

TA1316AN

2002-10-04

41

Color Difference 1/YUV Input and Matrix Block

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

D

BB

0.7

0.9

1

Color difference signal input dynamic

range

D

RR

0.7

0.9

1

V

p-p

T

RMAX

25

29

33

T

RMIN

-37

-33

-29

T

BMAX

27

31

35

Color difference signal tint control

characteristic

T

BMIN

-36

-32

-28

∞

Matrix fast SW threshold voltage

V

MSW

Pin 7

0.65

0.72

0.8

V

F

B00

3.6

4.5

5.4

F

B01

4.6

5.8

7.0

F

B10

6.8

8.5

10.2

F

R00

3.6

4.5

5.4

F

R01

4.6

5.8

7.0

Color SRT peak frequency

F

R10

6.8

8.5

10.2

MHz

GS

B00CEN

5

8

11

GS

B00MAX

9

12

15

GS

B01CEN

2

5

8

GS

B01MAX

5

8

11

GS

B10CEN

1

2

5

GS

B10MAX

1

3

6

GS

R00CEN

5

8

11

GS

R00MAX

9

12

15

GS

R01CEN

2

5

8

GS

R01MAX

5

8

11

GS

R10CEN

1

2

5

Color SRT gain

GS

R10MAX

(Note S01)

1

3

6

dB

Delay time from Cb1 input to B output

T

B

104

130

156

Delay time from Cr1 input to R output

T

R

104

130

156

ns

TA1316AN

2002-10-04

42

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

GC

BDY1

0.3

0.5

0.7

GC

BDY2

0.7

1.0

1.3

GC

BDY3

0.7

1.0

1.3

GC

BBS1

0.2

0.4

0.6

GC

BBS2

-1.0

-0.6

-0.5

GC

BBS3

-3.6

-3.3

-3.0

GC

RDY1

0.3

0.5

0.7

GC

RDY2

1.4

1.6

1.8

GC

RDY3

1.4

1.6

1.8

GC

RBS1

0.1

0.3

0.5

GC

RBS2

-1.2

-1.0

-0.8

Color difference signal amplitude

correction

GC

RBS3

(Note S02)

-3.7

-3.3

-2.9

dB

G

Y00

4.5

5.5

6

G

Y01

4.5

5.5

6

G

Y10

4.5

5.5

6

G

Y11

4.5

5.5

6

G

BA

0.2

0.4

0.5

G

BB

1.0

1.1

1.3

G

BC

1.0

1.1

1.3

G

RA

0.8

1.0

1.2

G

RB

-1.6

-1.4

-1.2

YUV gain

G

RC

(Note S03)

-3.4

-3.2

-3.0

dB

TA1316AN

2002-10-04

43

Color Difference 2 Block

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

Color difference signal contrast

adjustment characteristic

V

uCY

(Note A01)

15.5

17.0

18.5

dB

v

cCY

+

3.6

4.6

5.6

Color adjustment characteristic

vcCY-

(Note A02)

-35

-25

-18

dB

RMAX

109

111.5

114

RCNT

98.5

101

103.5

RMIN

88

90

92

∞

V

R

/V

BMAX

0.82

0.85

0.88

V

R

/V

BCNT

0.68

0.71

0.74

R-Y relative phase and amplitude

V

R

/V

BMIN

0.51

0.54

0.57

times

GMAX

253

256

259

GCNT

245

248

251

GMIN

229

232

235

∞

V

G

/v

BMAX

0.35

0.38

0.41

V

G

/v

BCNT

0.30

0.33

0.36

G-Y relative phase and amplitude

V

G

/v

BMIN

0.25

0.28

0.31

times

GHT

RY

0.47

0.50

0.53

GHT

GY

0.47

0.50

0.53

Color difference signal half-tone

characteristic

GHT

BY

(Note A03)

0.47

0.50

0.53

times

V

1

0.09

0.23

0.37

V

2

0.26

0.40

0.54

V

3

0.44

0.58

0.72

V

p-p

Color

characteristic

(Note A04)

0.60

0.70

0.80

CLT

0

1.45

1.65

1.85

Color limiter characteristic

CLT

1

(Note A05)

1.80

2.00

2.20

V

p-p

High bright color gain

HBC

1

(Note A06)

0.02

0.04

0.06

times

TA1316AN

2002-10-04

44

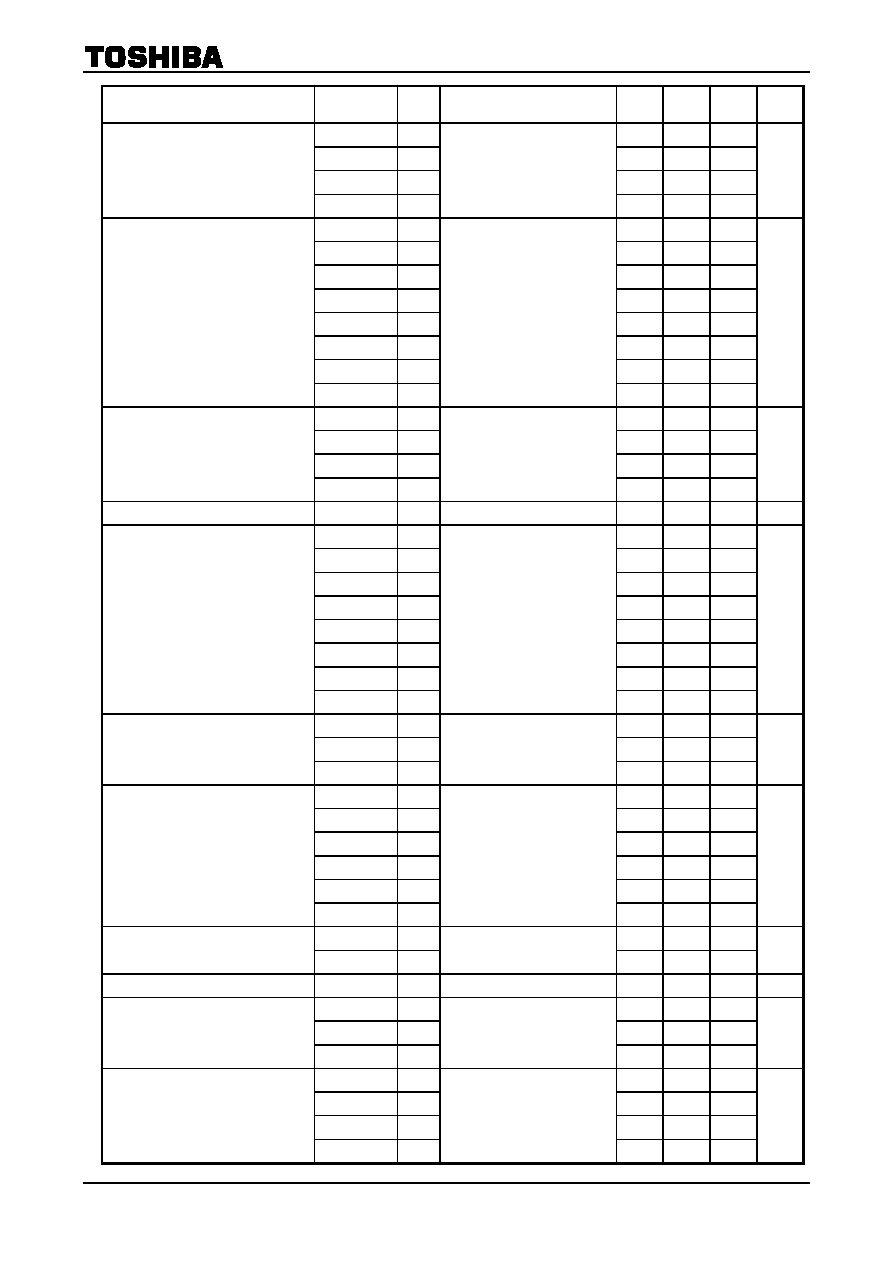

Text Block

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

G

R

3.39

3.80

4.28

G

G

3.39

3.80

4.28

AC gain

(Y1in~R/G/B out)

G

B

(Note T01)

3.39

3.80

4.28

times

G

G/R

0.94

1.00

1.06

AC gain axial difference

G

B/R

0.94

1.00

1.06

G

fR

24

30

G

fG

24

30

Frequency characteristic

(Y1in~R/G/B out)

G

fB

Flat gain

(-3 dB point at 10 MHz)

24

30

MHz

G

fCb

11

14.5

Frequency characteristics

(Cb1/Cr1in~R/G/B out)

G

fCr

11

14.5

MHz

Unicolor adjustment characteristic

V

u

(Note T02)

15.5

16.5

17.5

dB

V

brMAX

4.10

4.45

4.80

V

brCNT

3.05

3.40

3.75

Brightness adjustment characteristic

V

brMIN

(Note T03)

1.95

2.30

2.65

V

V

wps1

2.30

2.45

2.65

White peak slice level

V

wps2

(Note T04)

2.70

2.90

3.10

V

p-p

Black peak slice level

V

bps

(Note T05)

1.05

1.20

1.35

V

N

41

-55

-49

N

42

-55

-49

RGB output S/N

N

43

(Note T06)

-55

-49

dB

G

HT1

0.45

0.50

0.55

Half-tone characteristic

G

HT2

(Note T07)

0.45

0.50

0.55

times

Half-tone ON voltage

V

HT

Pin 52

0.65

0.85

1.05

V

V

VR

0.30

0.80

1.30

V

VG

0.30

0.80

1.30

Vertical blanking pulse output level

V

VB

0.30

0.80

1.30

V

V

HR

0.30

0.80

1.30

V

HG

0.30

0.80

1.30

Horizontal blanking pulse output level

V

HB

0.30

0.80

1.30

V

td

ON

0.00

0.30

Blanking pulse delay time

td

OFF

(Note T08)

0.08

0.30

µs

v

su

+

2.1

2.6

3.1

Sub-contrast variable range

v

su

-

-4.0

-3.5

-3.0

dB

CUT

+

0.42

0.47

0.52

Cutoff voltage variable range

CUT

-

0.42

0.47

0.52

V

TA1316AN

2002-10-04

45

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

DR

R1

+

2.5

3.0

3.5

DR

R1

-

-5.5

-5.0

-4.5

DR

R2

+

2.5

3.0

3.5

DR

R2

-

-5.5

-5.0

-4.5

DR

G1

+

2.5

3.0

3.5

DR

G1

-

-5.5

-5.0

-4.5

DR

G2

+

2.5

3.0

3.5

DR

G2

-

-5.5

-5.0

-4.5

DR

G3

+

2.5

3.0

3.5

DR

G3

-

-5.5

-5.0

-4.5

DR

B1

+

2.5

3.0

3.5

DR

B1

-

-5.5

-5.0

-4.5

DR

B2

+

2.5

3.0

3.5

DR

B2

-

-5.5

-5.0

-4.5

DR

B3

+

2.5

3.0

3.5

Drive adjustment variable range

DR

B3

-

(Note T09)

-5.5

-5.0

-4.5

dB

MU

RD

1.5

1.7

1.9

MU

GD

1.5

1.7

1.9

Output voltage at picture muting

MU

BD

1.5

1.7

1.9

V

P mute ON voltage

V

MUTE

Pin 52

1.90

2.15

2.40

V

BB

R

1.0

1.2

1.4

BB

G

1.0

1.2

1.4

V

Output voltage at blue back

BB

B

1.1

1.25

1.4

V

p-p

Pin 53 input impedance

Zin

(Note T10)

24

30

36

k

ACL

1

-7.5

-5.5

-3.5

ACL characteristic

ACL

2

(Note T11)

-16.0 -14.5 -12.0

dB

ABL

P1

0.10

0.15

0.20

ABL

P2

-0.01 0.04

0.09

ABL

P3

-0.07 -0.02 0.03

ABL

P4

-0.17 -0.12 -0.07

ABL

P5

-0.27 -0.22 -0.17

ABL

P6

-0.36 -0.31 -0.26

ABL

P7

-0.44 -0.39 -0.34

ABL point

ABL

P8

(Note T12)

-0.50 -0.45 -0.40

V

ABL

G1

-0.06 -0.02 0.00

ABL

G2

-0.17 -0.12 -0.07

ABL

G3

-0.34 -0.29 -0.24

ABL

G4

-0.52 -0.47 -0.42

ABL

G5

-0.68 -0.63 -0.59

ABL

G6

-0.85 -0.80 -0.75

ABL

G7

-1.01 -0.96 -0.91

ABL gain

ABL

G8

(Note T13)

-1.09 -1.04 -0.99

V

TA1316AN

2002-10-04

46

Characteristics

Symbol

Test

Circuit

Test Condition

Min

Typ.

Max

Unit

V

43R

2.15

2.40

2.65

V

42R

0.30

0.80

1.30

V

41R

0.30

0.80

1.30

V

43G

0.30

0.80

1.30

V

42G

2.15

2.40

2.65

V

41G

0.30

0.80

1.30

V

43B

0.30

0.80

1.30

V

42B

0.30

0.80

1.30

RGB output mode

V

41B

(Note T14)

2.15

2.40

2.65

V

1

56

66

76

2

72

82

92

IRE

1

0.49

1.24

1.99

2

-1.67 -0.92 -0.17

Y-OUT

characteristic

3

(Note T15)

-4.59 -3.84 -3.09

dB

BS

Pmin

55.0

60.0

65.0

BS

Pcnt

92.5

97.5

102.5

BS

Pmax

107

112

117

IRE

BS

Gmin

1.75

2.25

2.75

BS

Gcnt

6.4

7.4

8.4

Blue stretch circuit characteristic

BS

Gmax

(Note T16)

9

10

11

dB

Forced blanking input threshold

voltage

V

BLKIN

Pin 52

5.50

6.00

6.50

V

ACBR

1

ACBG

2

ACBB

3

H

V

ACB1R

0.04

0.07

0.10

V

ACB1G

0.04

0.07

0.10

V

ACB1B

0.04

0.07

0.10

V

ACB2R

0.16

0.21

0.26

V

ACB2G

0.16

0.21

0.26

V

ACB2B

0.16

0.21

0.26

V

ACB3R

0.41

0.46

0.51

V

ACB3G

0.41

0.46

0.51

ACB pulse phase and amplitude

V

ACB3B

(Note T17)

0.41

0.46

0.51

V

p-p

IK

R

0.73

0.93

1.13

IK

G

0.73

0.93

1.13

IK input amplitude

IK

B