| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TK2051 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

1

TK2051 ≠ SB/1.0/8-02

TK2051

STEREO 50W (8

) CLASS-TTM DIGITAL AUDIO AMPLIFIER

DRIVER USING DIGITAL POWER PROCESSING (DPPTM)

TECHNOLOGY

T e c h n i c a l I n f o r m a t i o n R e v i s i o n 1 . 1 ≠ A u g u s t 2 0 0 2

G E N E R A L D E S C R I P T I O N

T h e T K 2 0 5 1 ( T C 2 0 0 0 / T P 2 0 5 1 c h i p s e t ) i s a 5 0 W c o n t i n u o u s a v e r a g e p o w e r p e r

c h a n n e l , C l a s s - T D i g i t a l A u d i o P o w e r A m p l i f i e r u s i n g T r i p a t h ' s p r o p r i e t a r y D i g i t a l

P o w e r P r o c e s s i n g

T M

t e c h n o l o g y . C l a s s - T a m p l i f i e r s o f f e r b o t h t h e a u d i o f i d e l i t y o f

C l a s s - A B a n d t h e p o w e r e f f i c i e n c y o f C l a s s - D a m p l i f i e r s .

A P P L I C A T I O N S

5.1-Channel DVD

Mini/Micro Component Systems

Home Theater

Stereo applications (6 / 8)

Mono applications (4)

B E N E F I T S

Single Supply Operation

Very High Efficiency

Wide Dynamic Range

Compact layout

F E A T U R E S

Class-T Architecture

High Output power

35W @ 6

, < 1% THD+N

50W @ 8

, < 3% THD+N

117W @ 4

, < 10.0% THD+N

(paralleled outputs)

Audiophile Quality Sound

0.007% THD+N @ 30W 8

0.005% THD+N @ 70W 4

(paralleled outputs)

High Efficiency

92% @ 60W 8

85% @ 46W 6

89% @ 117W 4

(paralleled outputs)

Dynamic Range >100 dB

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

2

TK2051 ≠ SB/1.0/8-02

A B S O L U T E M A X I M U M R A T I N G S ≠ T C 2 0 0 0

(Note 1)

SYMBOL PARAMETER

Value

UNITS

V

5

5V Power Supply

6

V

Vlogic Input

Logic

Level

V

5

+0.3V V

TA

Operating Free-air Temperature Range

-40 to 85

∞C

T

STORE

Storage Temperature Range

-55 to 150

∞C

T

JMAX

Maximum Junction Temperature

150

∞C

ESD

HB

ESD Susceptibility ≠ Human Body Model (Note 2), all pins

2000

V

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

See the table below for Operating Conditions.

Note 2: Human body model, 100pF discharged through a 1.5K

resistor.

A B S O L U T E M A X I M U M R A T I N G S ≠ T P 2 0 5 1

(Note 1)

SYMBOL PARAMETER

Value

UNITS

V

CC

Power Supply

40

V

Vlogic Input

Logic

Level

5.5

V

TA

Operating Free-air Temperature Range

0 to 70

∞C

T

STORE

Storage Temperature Range

-40 to 150

∞C

T

JMAX

Maximum Junction Temperature

150

∞C

ESD

HB

ESD Susceptibility ≠ Human Body Model (Note 2), all pins

2000

V

O P E R A T I N G C O N D I T I O N S ≠ T C 2 0 0 0

(Note 1)

SYMBOL PARAMETER MIN.

TYP.

MAX.

UNITS

V5

Supply Voltage

4.5

5

5.5

V

V

HI

Logic Input High

V5-1.0

V

V

LO

Logic Input Low

1

V

T

A

Operating Temperature Range

-40

25

85

∞C

O P E R A T I N G C O N D I T I O N S ≠ T P 2 0 5 1

(Note 1)

SYMBOL PARAMETER

MIN.

TYP.

MAX.

UNITS

V

CC

Power Supply

10

36

V

V

HI

Logic Input High

Ibias/10 + 500mV

V

V

LO

Logic Input Low

Ibias/5 + 1V

V

T

A

Operating Temperature Range

0

25

70

∞C

T H E R M A L C H A R A C T E R I S T I C S

TC2000

SYMBOL PARAMETER

Value

UNITS

JA

Junction-to-ambient Thermal Resistance (still air)

80

∞C/W

TP2051

SYMBOL PARAMETER

Value

UNITS

JC

Junction-to-case Thermal Resistance

2.5

∞C/W

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

3

TK2051 ≠ SB/1.0/8-02

E L E C T R I C A L C H A R A C T E R I S T I C S ≠ T C 2 0 0 0

SYMBOL PARAMETER MIN.

TYP.

MAX.

UNITS

I5

Supply Current

60

mA

fsw Switching

Frequency

650

kHz

V

IN

Input

Sensitivity

0

1.5

V

V

OUTHI

High

Output

Voltage

V5-0.5

V

V

OUTLO

Low

Output

Voltage

100 mV

R

IN

Input

Impedance

2

k

Input

DC

Bias

2.5

V

E L E C T R I C A L C H A R A C T E R I S T I C S ≠ T P 2 0 5 1

T

A

= 25

∞C. See Application/Test Circuit. Unless otherwise noted, the supply voltage is V

CC

= 28V.

SYMBOL PARAMETER

CONDITIONS MIN.

TYP.

MAX.

UNITS

I

q

Quiescent Current

(No load, Mute = 0V)

V

CC

= +28V

V5 = 5V

125

27

60

mA

mA

I

MUTE

Mute Supply Current

(No load, Mute = 5V)

V

CC

= +31V

V5 = 5V

28

7

mA

mA

V

IH

High-level input voltage (MUTE)

I

IH

= See Mute Control Section

3.5

V

V

IL

Low-level input voltage (MUTE)

I

IL

= See Mute Control Section

1.0

V

I

SC

Short circuit current limit

V

CC

= +30V, T=25

o

C 3.5

5

6.5

A

P E R F O R M A N C E C H A R A C T E R I S T I C S ≠ T K 2 0 5 1

T

A

= 25

∞C. Unless otherwise noted, V

CC

= 30V, f=1kHz, and the measurement bandwidth is 20kHz.

SYMBOL PARAMETER

CONDITIONS MIN.

TYP.

MAX.

UNITS

P

OUT

Output Power

(Continuous Average/Channel)

(Note 13)

V

CC

= +30V, R

L

= 8

THD+N < 0.01%

THD+N < 3.0%

THD+N < 10.0%

V

CC

= +23.5V, R

L

= 6

THD+N < 0.05%

THD+N < 5.0%

THD+N < 10.0%

V

CC

= +30V, R

L

= 4

(par. output)

THD+N < 0.01%

THD+N < 10%

30

50

60

30

40

45

75

117

W

W

W

W

W

W

W

W

THD + N Total Harmonic Distortion Plus

Noise

P

OUT

= 40W/Channel, R

L

= 8

V

CC

= +30V

P

OUT

= 30W/Channel, R

L

= 6

V

CC

= +23.5V

0.03

0.03

%

%

IHF-IM

IHF Intermodulation Distortion

19kHz, 20kHz, 1:1 (IHF), R

L

= 8

P

OUT

= 30W/Channel

0.05 %

SNR Signal-to-Noise

Ratio

A-Weighted

0dB = 50W/Channel, R

L

= 8

103

dB

CS Channel

Separation

0dB = 10W, R

L

= 8

, f=1kHz

95 dB

A

V

Amplifier

Gain

P

OUT

= 10W/Channel, R

L

= 8

,

See Application / Test Circuit

15 V/V

A

VERROR

Channel to Channel Gain Error

P

OUT

= 10W/Channel, R

L

= 8

See Application / Test Circuit

0.5

dB

Power Efficiency

P

OUT

= 60W/Channel, R

L

= 8

P

OUT

= 45W/Channel, R

L

= 6

92

85

%

%

e

N

Output Noise Voltage

A-Weighted, input AC grounded

135

µV

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

4

TK2051 ≠ SB/1.0/8-02

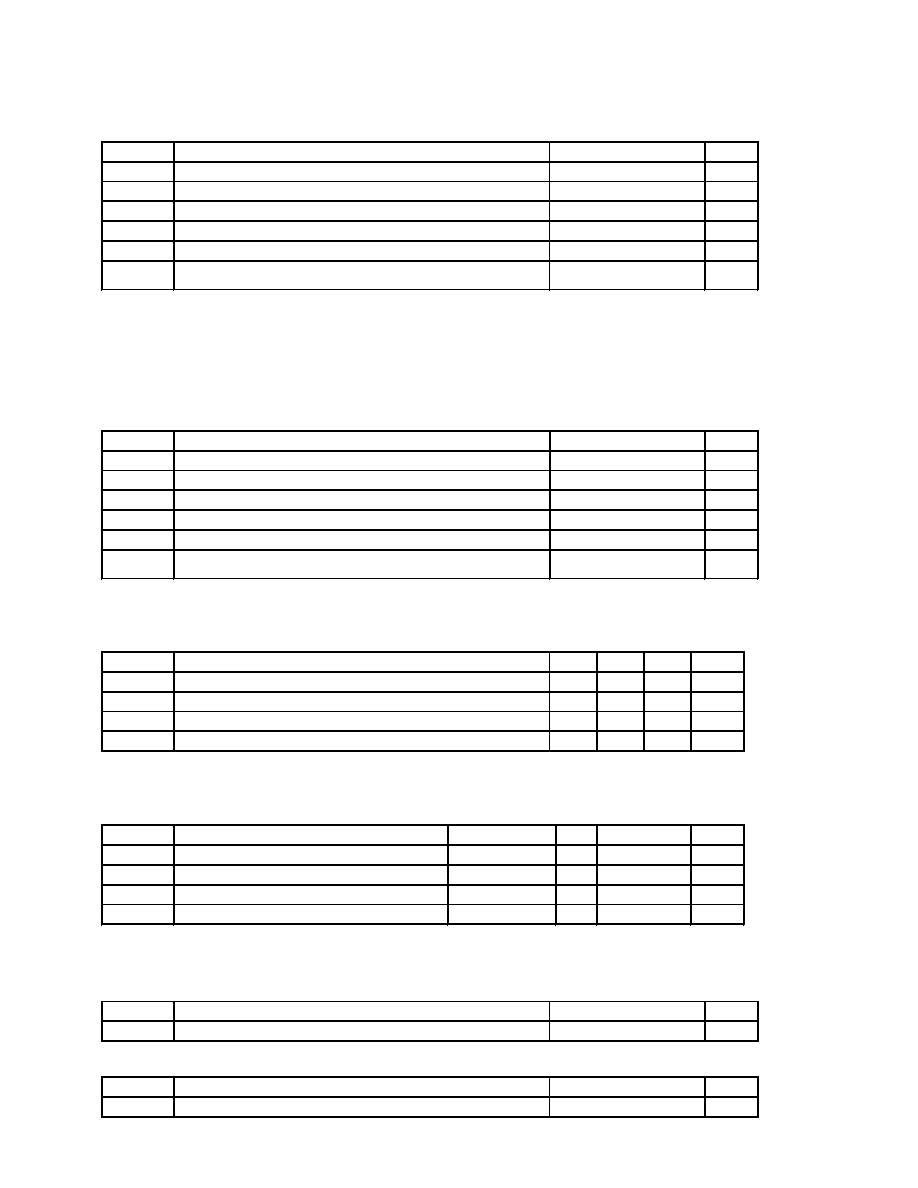

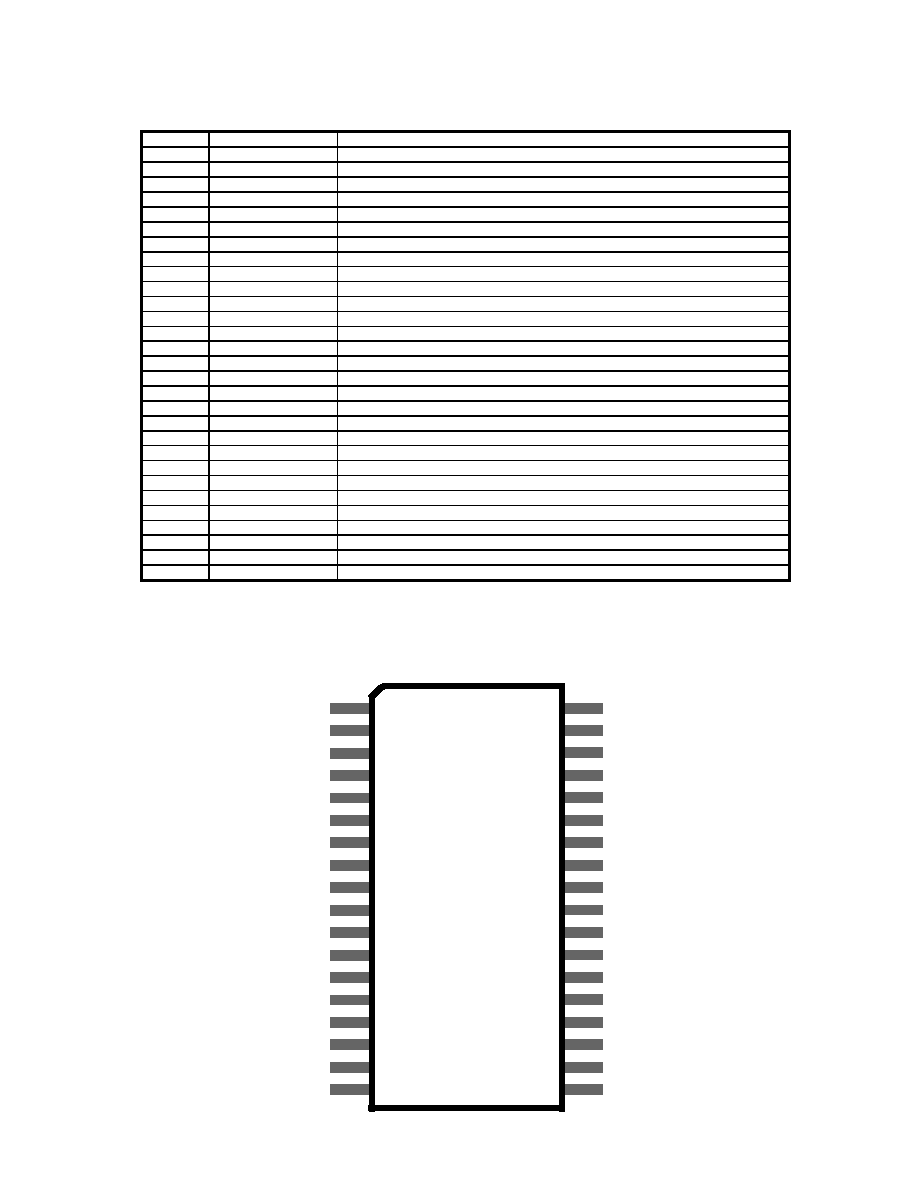

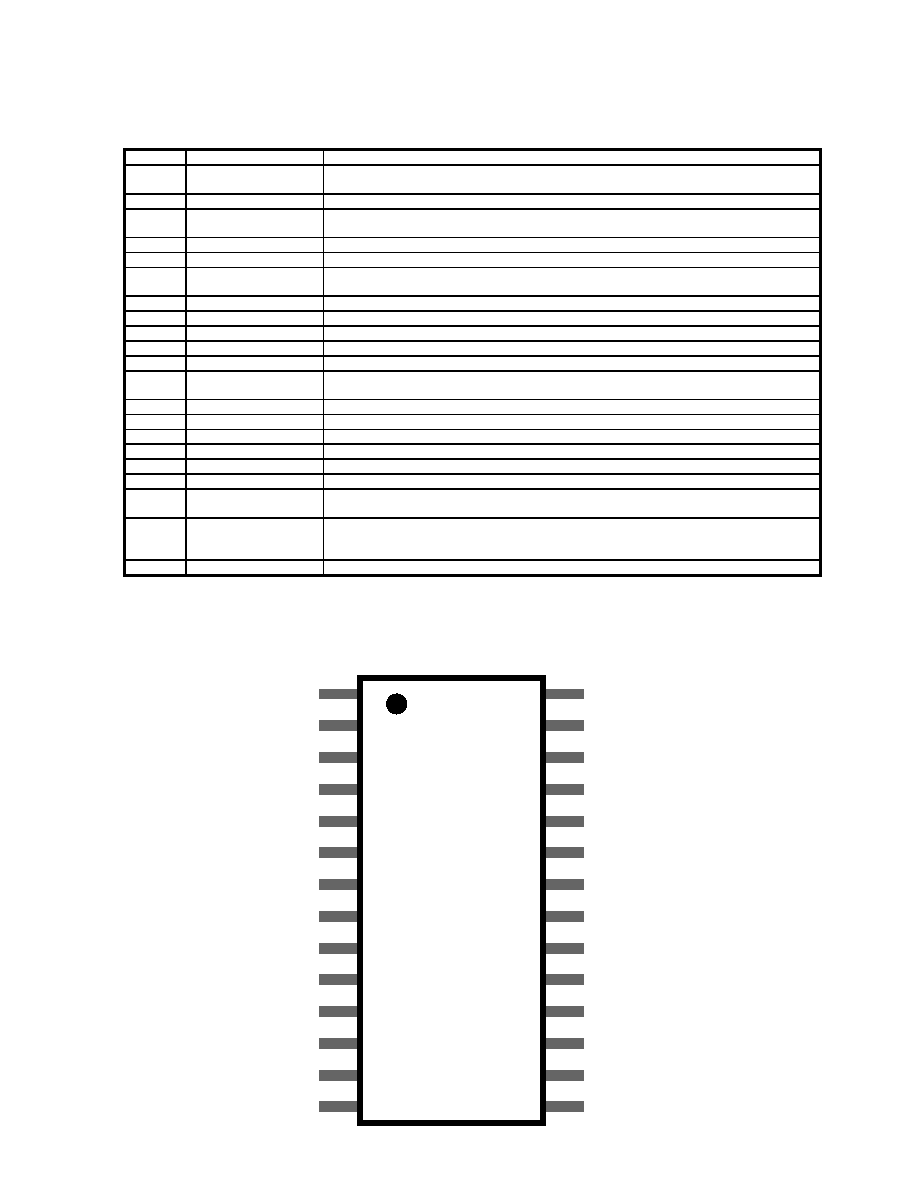

T C 2 0 0 0 A U D I O S I G N A L P R O C E S S O R P I N D E S C R I P T I O N S

Pin Function

Description

1 BIASCAP

Bandgap reference times two (typically 2.5VDC). Used to set the common mode voltage

for the input op amps. This pin is not capable of driving external circuitry.

2, 6

FDBKP2, FDBKP1

Positive switching feedback.

3 DCMP

Internal mode selection. This pin must be grounded for proper device

operation.

4, 7

FDBKN2, FDBKN1

Negative switching feedback.

5

VPWR

Test pin. Must be left floating.

8 HMUTE

Logic output. A logic high indicates both amplifiers are muted, due to the mute pin state, or

a "fault".

9, 12

Y1, Y2

Non-inverted switching modulator outputs.

10, 11

Y1B, Y2B

Inverted switching modulator outputs.

13 NC

No

connect

14

OCD2

Over Current Detect.

15

REF

Internal reference voltage; approximately 1.2 VDC.

16 OCD1

Over Current Detect. This pin must be grounded for proper device

operation.

17

VnnSense

Negative power stage over/under supply voltage sense resistor tie point.

18

OVRLDB

A logic low output indicates the input signal has overloaded the amplifier.

19

VppSense

Positive power stage over/under supply voltage sense resistor tie point.

20 AGND

Ground

21

V5

5 Volt power supply input.

22, 27

Oaout1, Oaout2

Input stage output pins.

23, 28

Inv1, Inv2

Single-ended inputs. Inputs are a "virtual" ground of an inverting opamp with

approximately 2.4VDC bias.

24 MUTE

When set to logic high, both amplifiers are muted and in idle mode. When low (grounded),

both amplifiers are fully operational. If left floating, the device stays in the mute mode.

Ground if not used.

25, 26

BBM0, BBM1

Break-before-make timing control to prevent shoot-through in the output FETs.

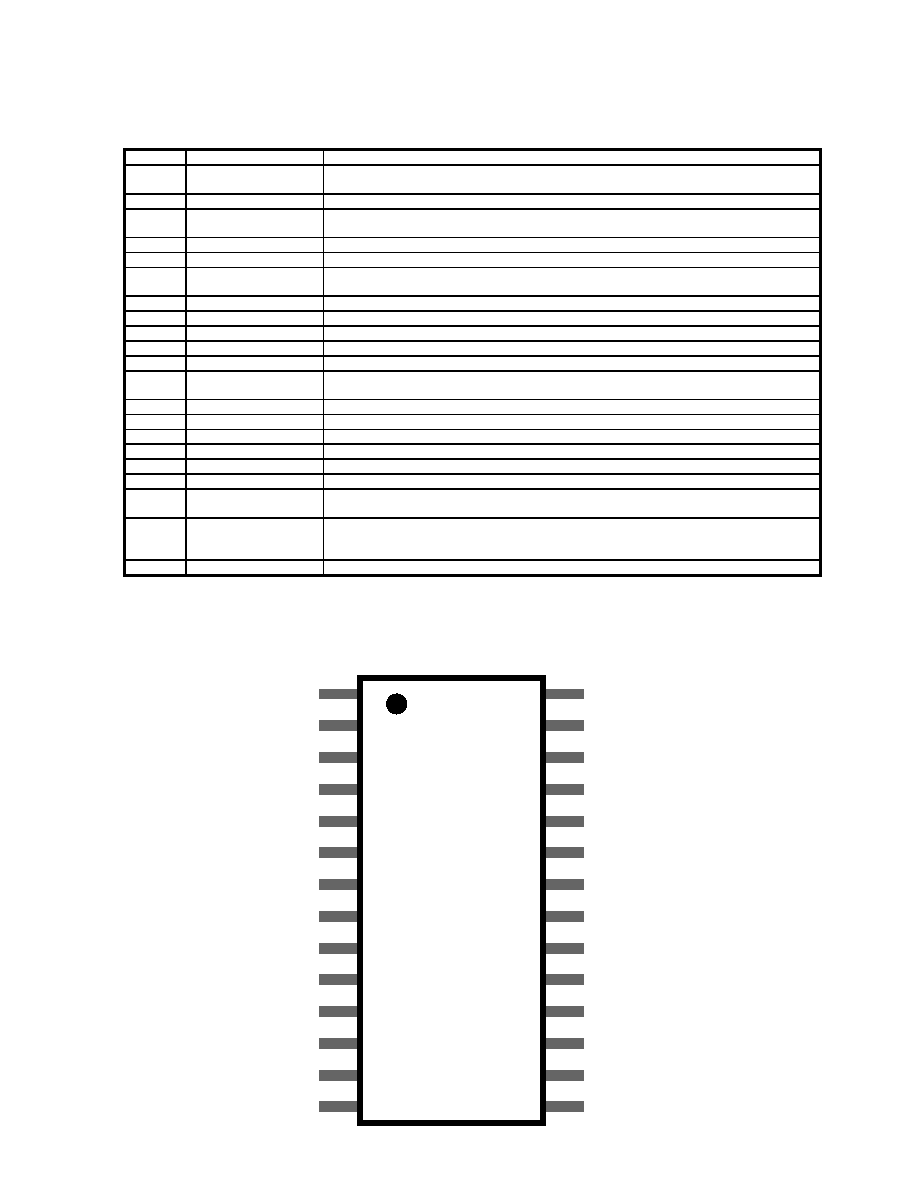

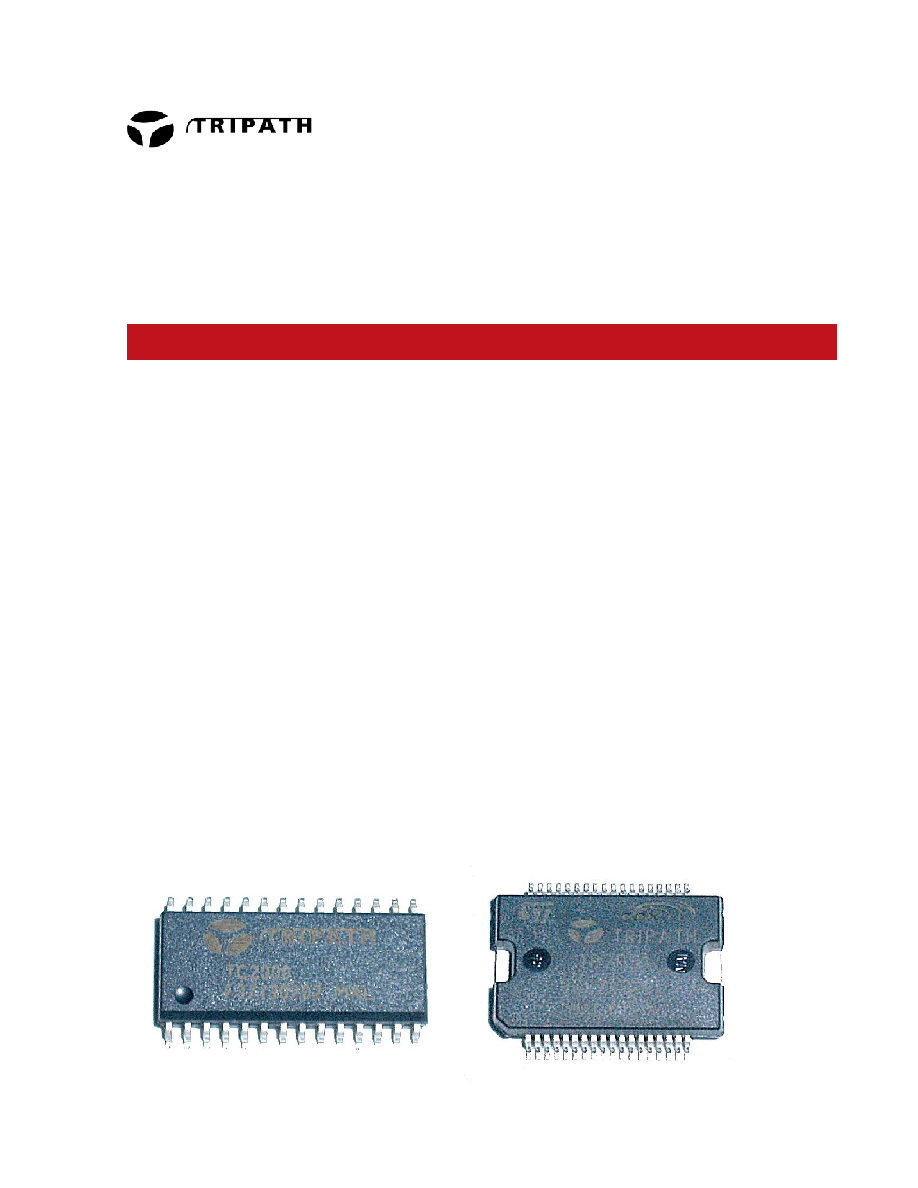

T C 2 0 0 0 A U D I O S I G N A L P R O C E S S O R P I N O U T

BIASCAP

FDBKP2

DCMP

FDBKN2

VPWR

FDBKP1

FDBKN1

HMUTE

Y1

Y1B

Y2B

Y2

NC

OCD2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

REF

OCD1

VnnSENSE

OVRLDB

VppSENSE

AGND

V5

OAout1

INv1

MUTE

BBM1

BBM0

OAout2

INv2

T r i p a t h T e c h n o l o g y, I n c . - T e c h n i c a l I n f o r m a t i o n

5

TK2051 ≠ SB/1.0/8-02

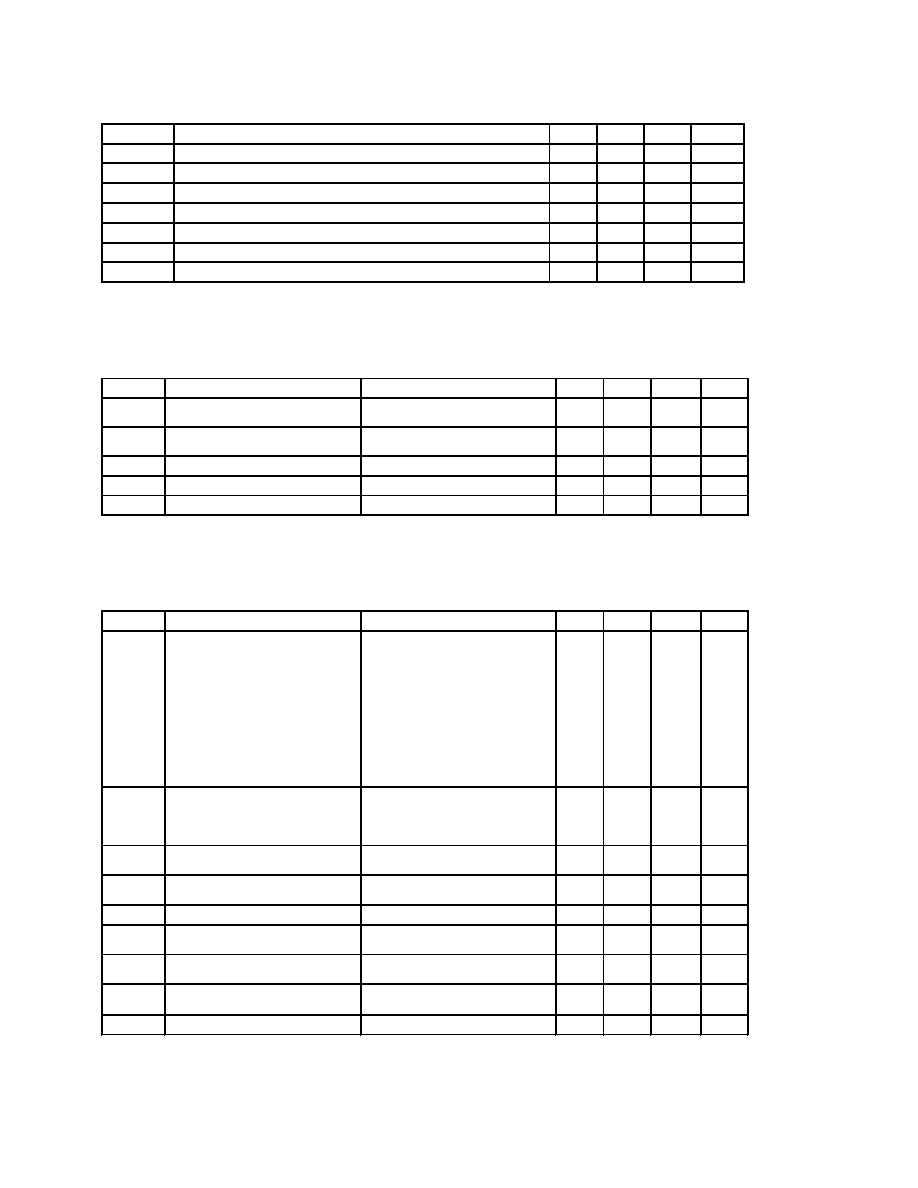

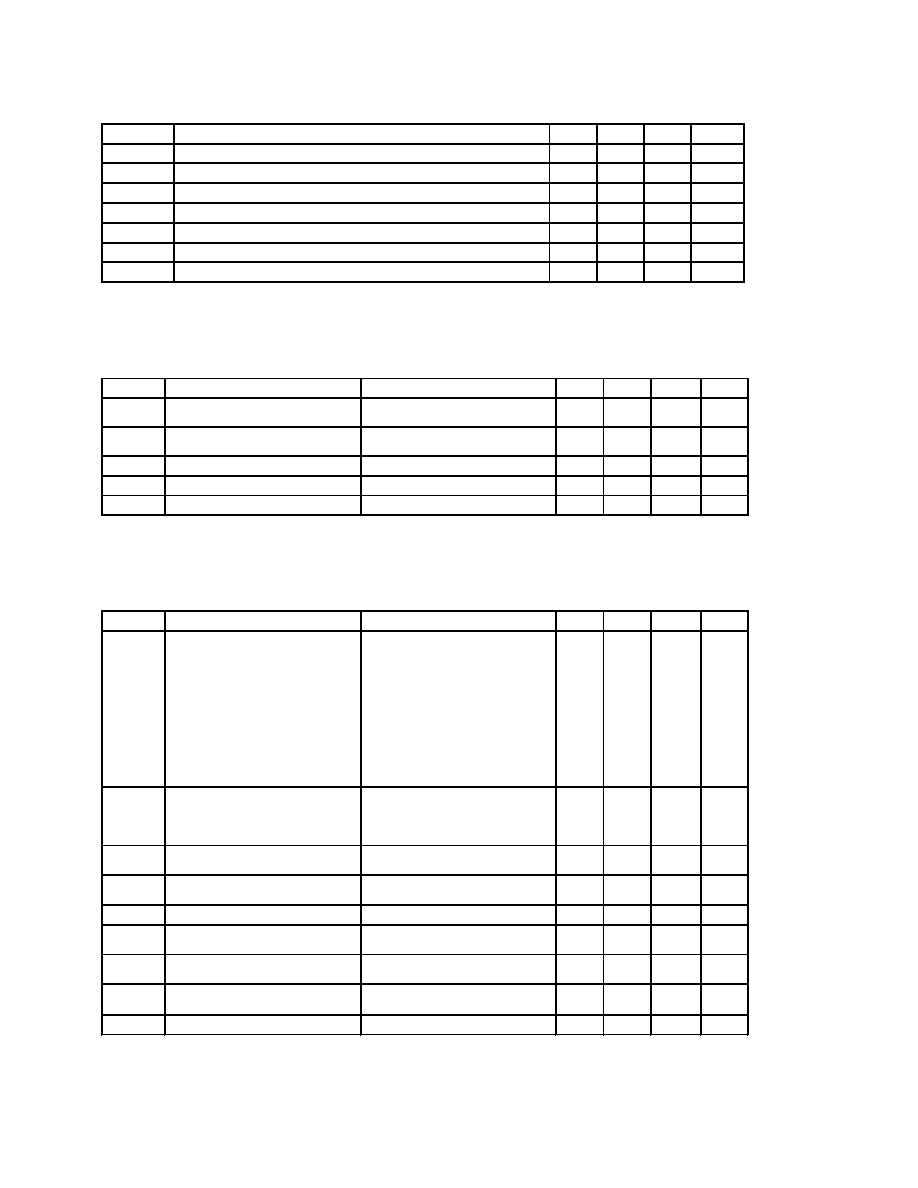

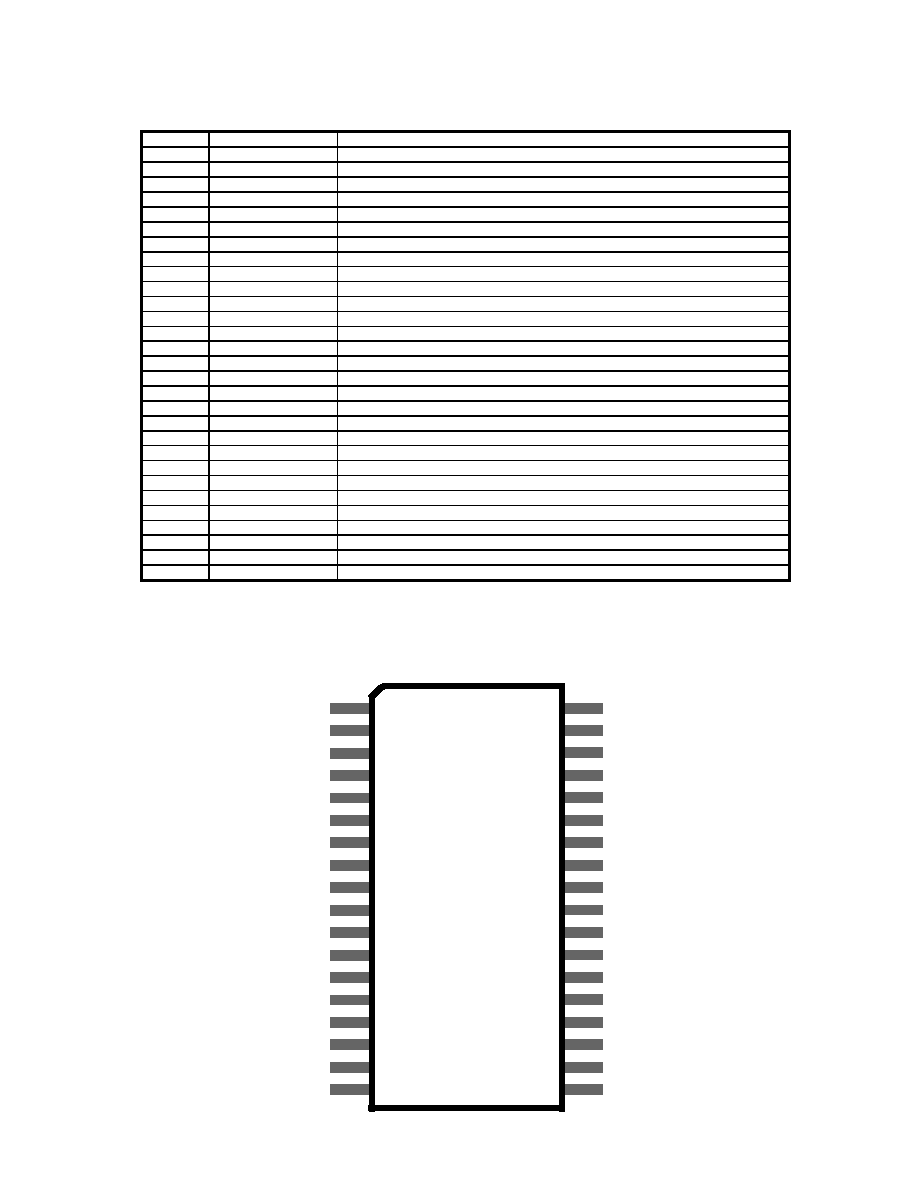

T P 2 0 5 1 P O W E R S T A G E P I N D E S C R I P T I O N S

Pin Function

Description

1 GND-SUB

Substrate

ground

35,36

VccSign

Signal positive supply

15 Vcc1A

Positive

supply

12 Vcc1B

Positive

supply

7 Vcc2A

Positive

supply

4 Vcc2B

Positive

supply

14 GND1A

Negative

supply

13 GND1B

Negative

supply

6 GND2A

Negative

supply

5 GND2B

Negative

supply

16,17

OUT1A

Output half bridge 1A

10,11

OUT1B

Output half bridge 1B

8,9

OUT2A

Output half bridge 2A

2,3

OUT2B

Output half bridge 2B

29

IN1A

Input of half bridge 1A

30

IN1B

Input of half bridge 1B

31

IN2A

Input of half bridge 2A

32

IN2B

Input of half bridge 2B

21,22

Vdd

5V regulator referenced to ground

33,34

Vss

5V regulator referenced to Vcc

25 PWRDN

Stand-by

pin

26 TRI-STATE

Hi-Z

pin

27 FAULT

Fault

output

24 CONFIG

Config

input

28

TH-WAR

Thermal warning output

19 GND-clean

Logic

ground

23

IBIAS

Logic high voltage

18 NC

Not

connected

20

GND-Reg

Ground for Vdd regulator

T P 2 0 5 1 P O W E R S T A G E P I N O U T

(Top view with heat slug down)

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

GNDCLEAN

GNDREG

IBIAS

CONFIG

PWRDN

TRISTATE

FAULT

TH_WAR

IN1A

IN1B

IN2A

IN2B

VSS

VSS

V

CC

SIGN

V

DD

V

DD

V

CC

SIGN

OUT2B

OUT2B

GNDSUB

VCC2B

GND2B

GND2A

VCC2A

OUT2A

OUT2A

OUT1B

OUT1B

VCC1B

GND1B

GND1A

VCC1A

OUT1A

OUT1A

NC