| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TQ8101C | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

T

R

I Q

U

I

N

T

S E M I C O N D U C T O R , I N C .

TELECOM

PRODUCTS

1

For additional information and latest specifications, see our website: www.triquint.com

TQ8101C

622/155 Mb/s

SONET/SDH MDFP

Features

∑ Byte-wide Multiplexing,

Demultiplexing, Framing, and

PLL (MDFP) in one device

∑ Choice of STS-12/STM-4 or

STS-3/STM-1 transmission rates

∑ Configurable master or slave

reference clock generation and

PLL bypass for external clocking

∑ 77.76 MHz or 19.44 MHz output

for the multiplexer; 77.76 MHz or

19.44 MHz and 51.84 MHz

output for the demultiplexer

∑ External RC loop filter

∑ Pass-through mode and three

loopback modes for enhanced

filed diagnostics

∑ Frame-synchronous and byte-

aligned demultiplexer output,

compliant with SONET and SDH

∑ Search, detect, and recovery of

framing on out-of-frame input

∑ Standard TTL and differential or

single-ended ECL I/O (except TXCK)

∑ Tristate TTL output for factory

circuit-board testability

∑ 68-pin TriQuint MLC controlled-Z

surface-mount package with

integral heat spreader

∑ Dual-supply operation (+5V, ≠5.2V)

∑ Low power dissipation (2.3W nom.)

The TQ8101C is a SONET/SDH transceiver that integrates Multiplexing,

Demultiplexing, SONET/SDH Framing, clock synthesis PLL (MDFP), and

loopback functions in a single monolithic integrated circuit. Implementation

with the TQ8101C requires only a simple external RC loop filter and standard

TTL and ECL power supplies. For optimal performance, the TQ8101C MDFP

is packaged in a 68-pin multilayer ceramic (MLC) surface-mount package

with an integral CuW heat spreader. The TQ8101C provides an integrated

solution for physical interfaces intended for use in STS-12/STM-4

(622.08-Mb/s) and STS-3/STM-1 (155.52-Mb/s) SONET/SDH systems.

The TQ8101C meets ANSI, Bellcore, and ITU requirements for a SONET/

SDH device. With a 51.84-MHz reference clock, the phase-locked loop

(PLL) provides 77.76-MHz or 19.44-MHz output for the multiplexer and

77.76-MHz or 19.44-MHz and 51.84-MHz output for the demultiplexer.

Typical SONET/SDH system applications for the TQ8101C include:

∑ Transmission system transport cards

∑ Switch and cross-connect line cards

∑ Repeaters

∑ ATM physical layer interfaces

∑ Test equipment

∑ Add/drop multiplexers

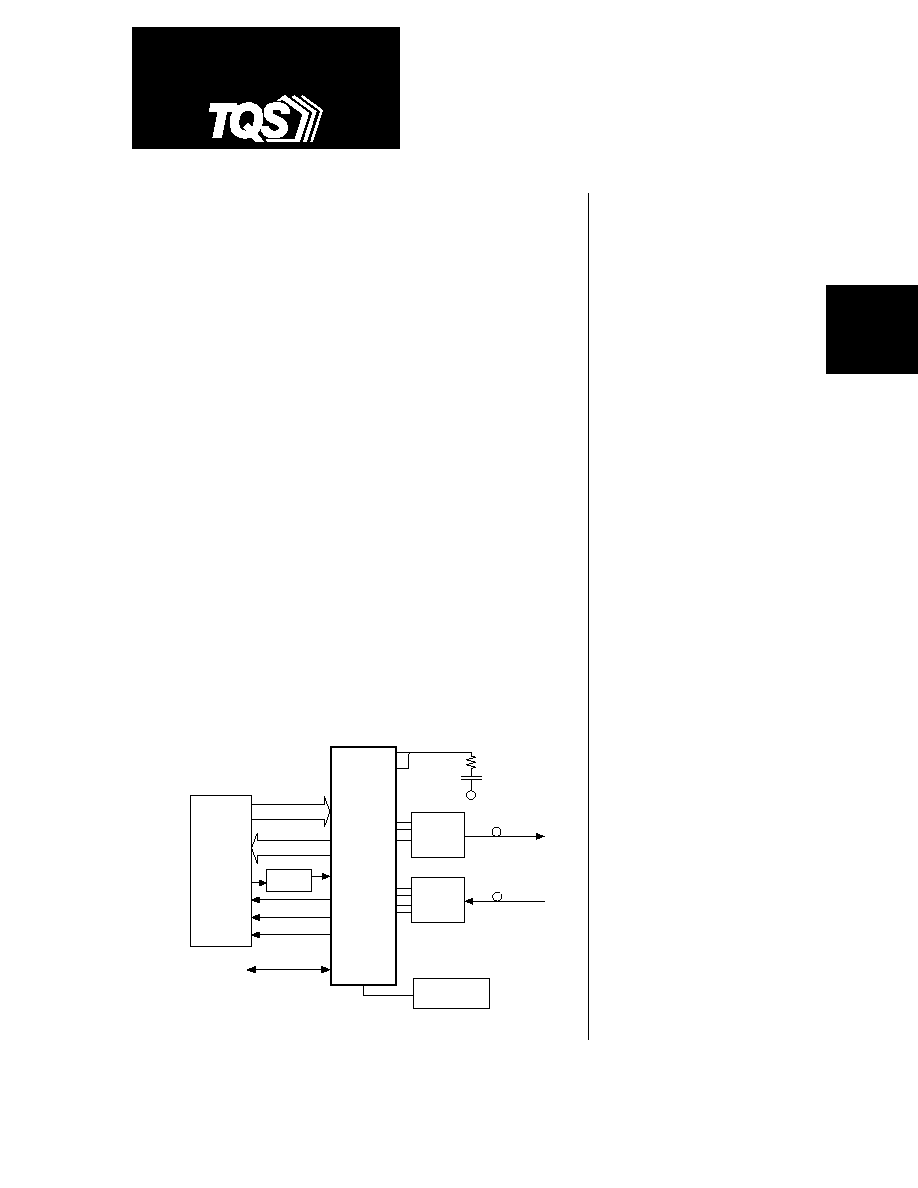

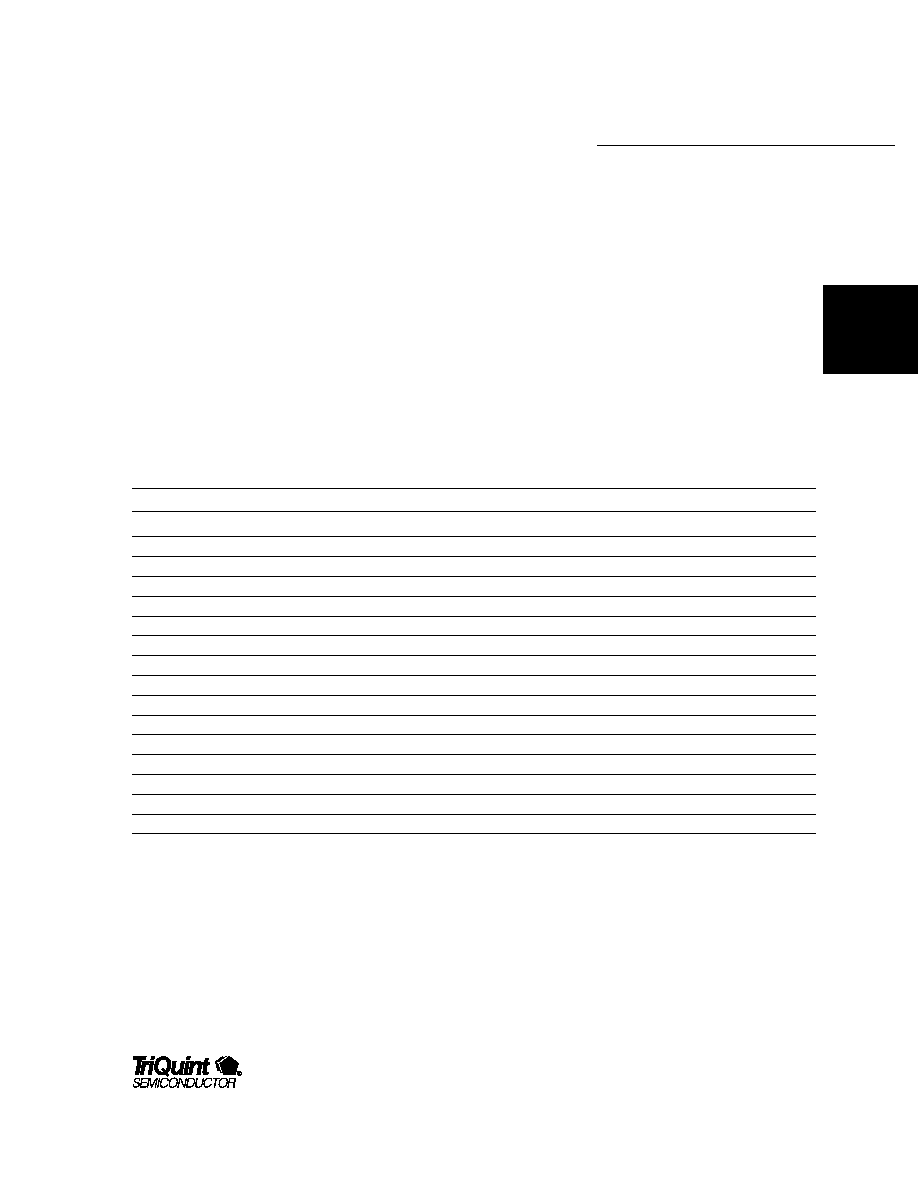

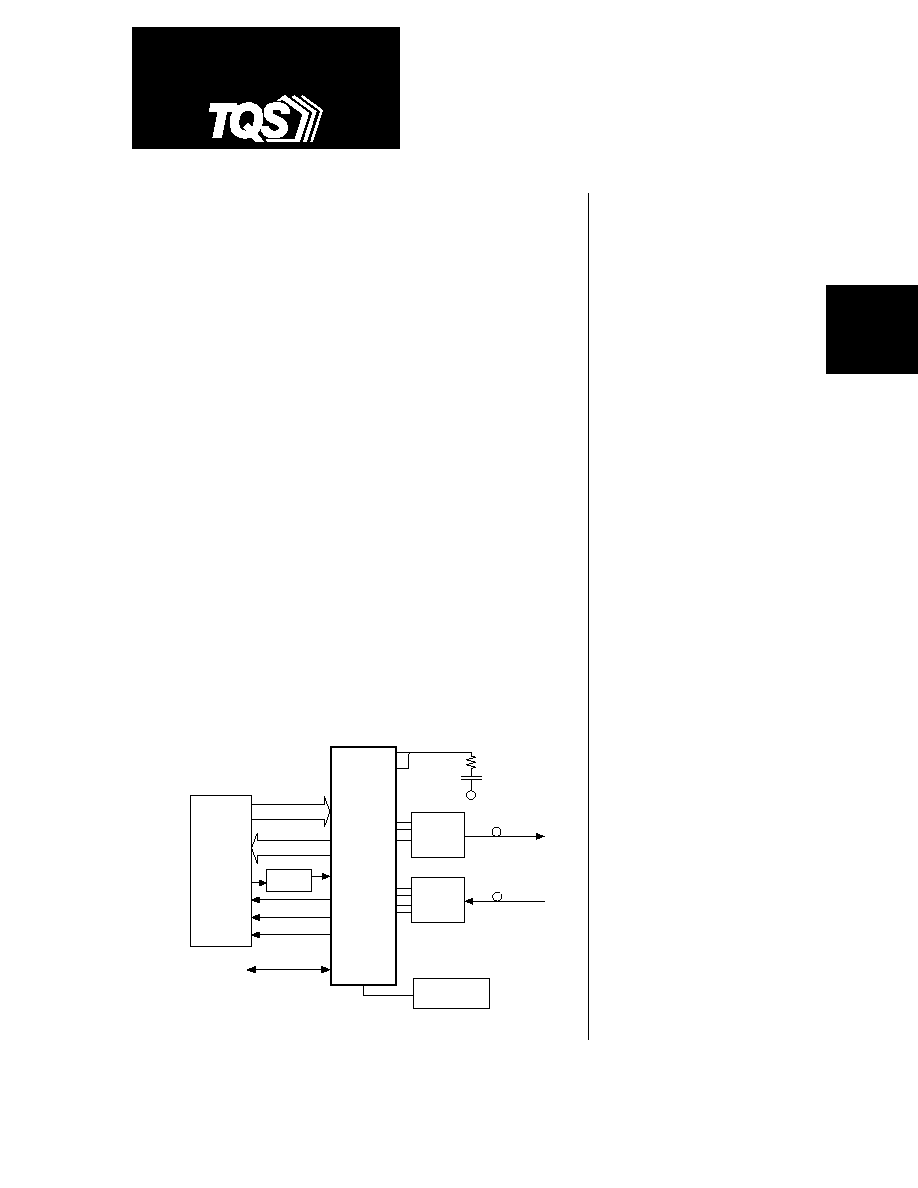

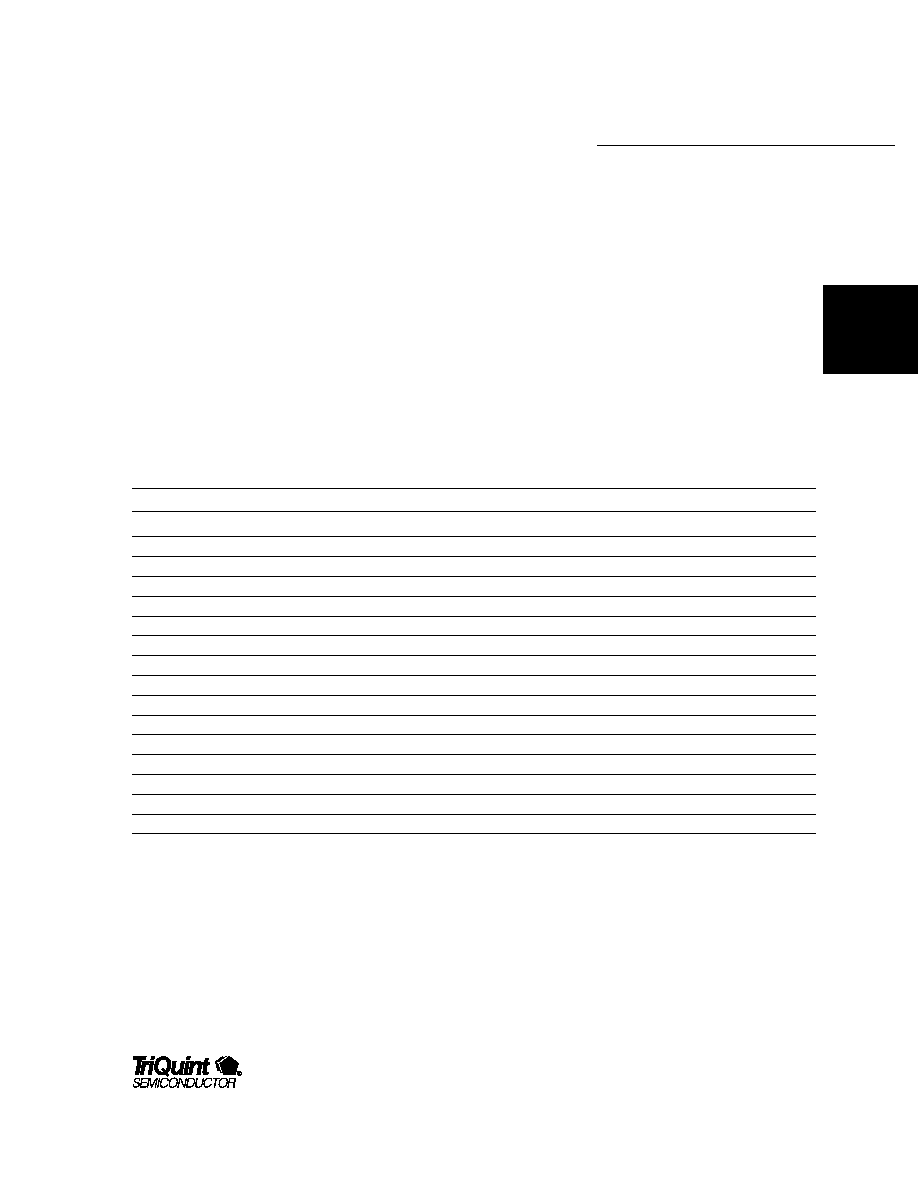

Figure 1. Logical Application

TQ8101C

MDFP

PM5312 or PM5355

STTX

S/UNI-622

Driver

and

LASER

O/E Rx +

TQ8103

CDR

TOUT(7:0)

OOF

TCLK

RIFP

RICLK

CNTL(3:0)

51.84 MHz

CMOS OSC

MXDT(7:0)

OOF

MXCK0

DXSYNC

DXCK

8-bit data

OC-3 or OC-12

OC-3 or OC-12

RIN(7:0)

MXDT(7:0)

DXDT(7:0)

8-bit data

600

0.68

µ

F

V

EE

OHFP

OOF fix*

*Contact PMC-Sierra for

application note.

TQ8101C

2

For additional information and latest specifications, see our website: www.triquint.com

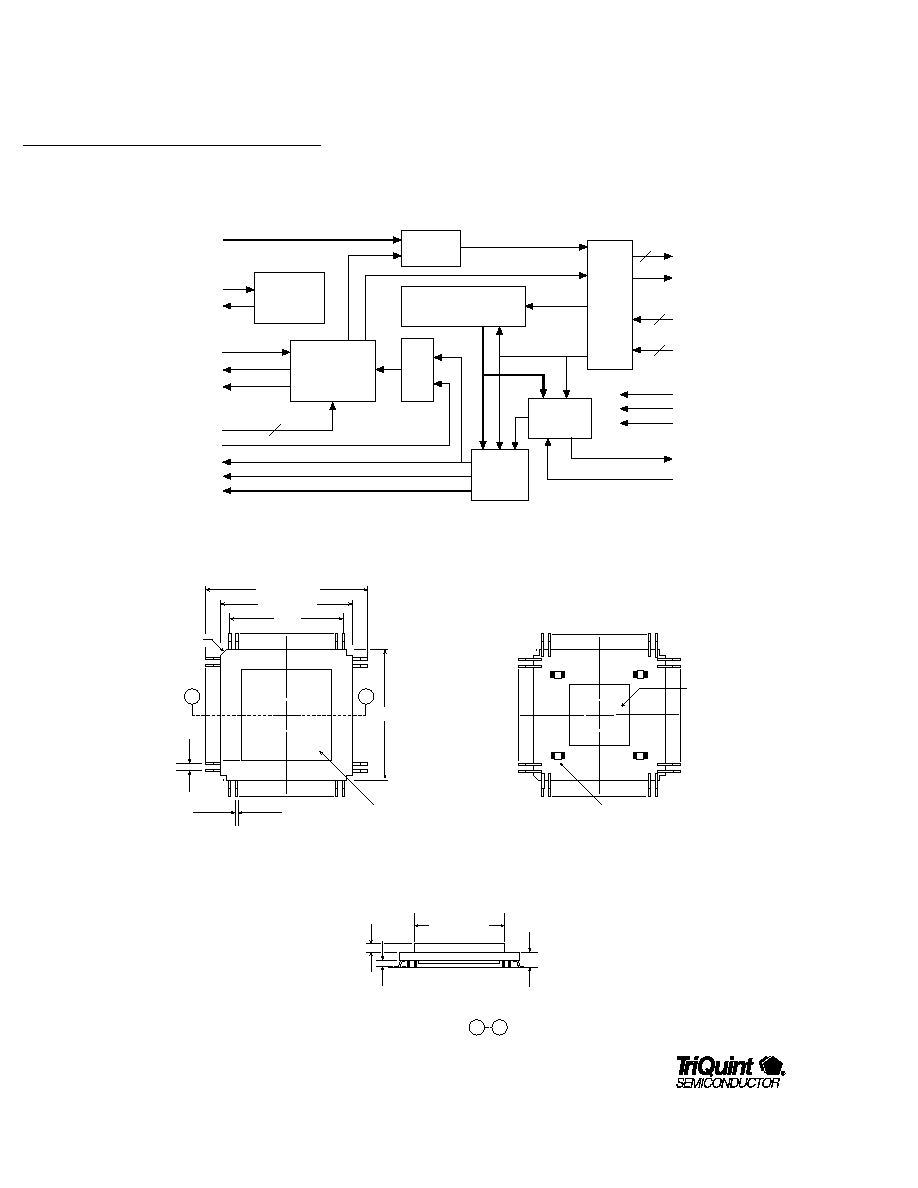

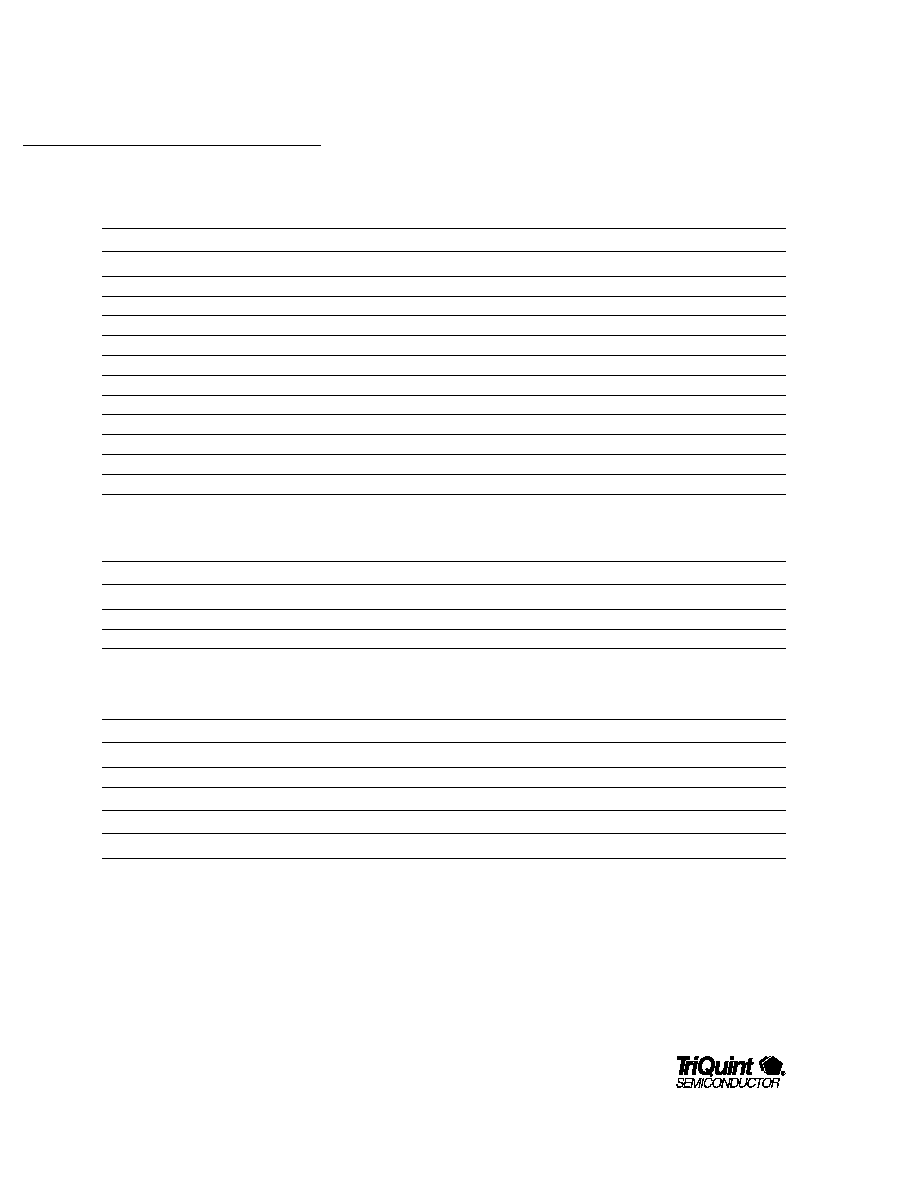

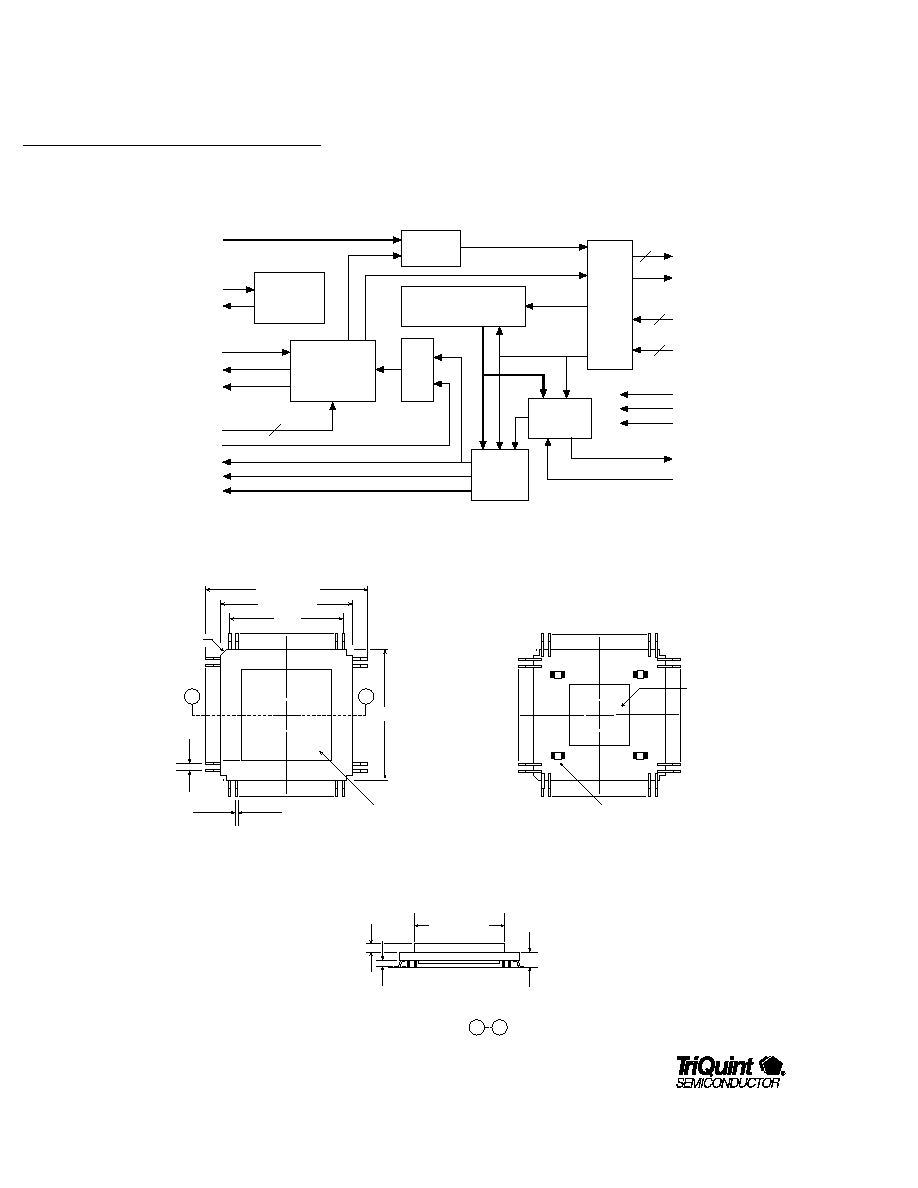

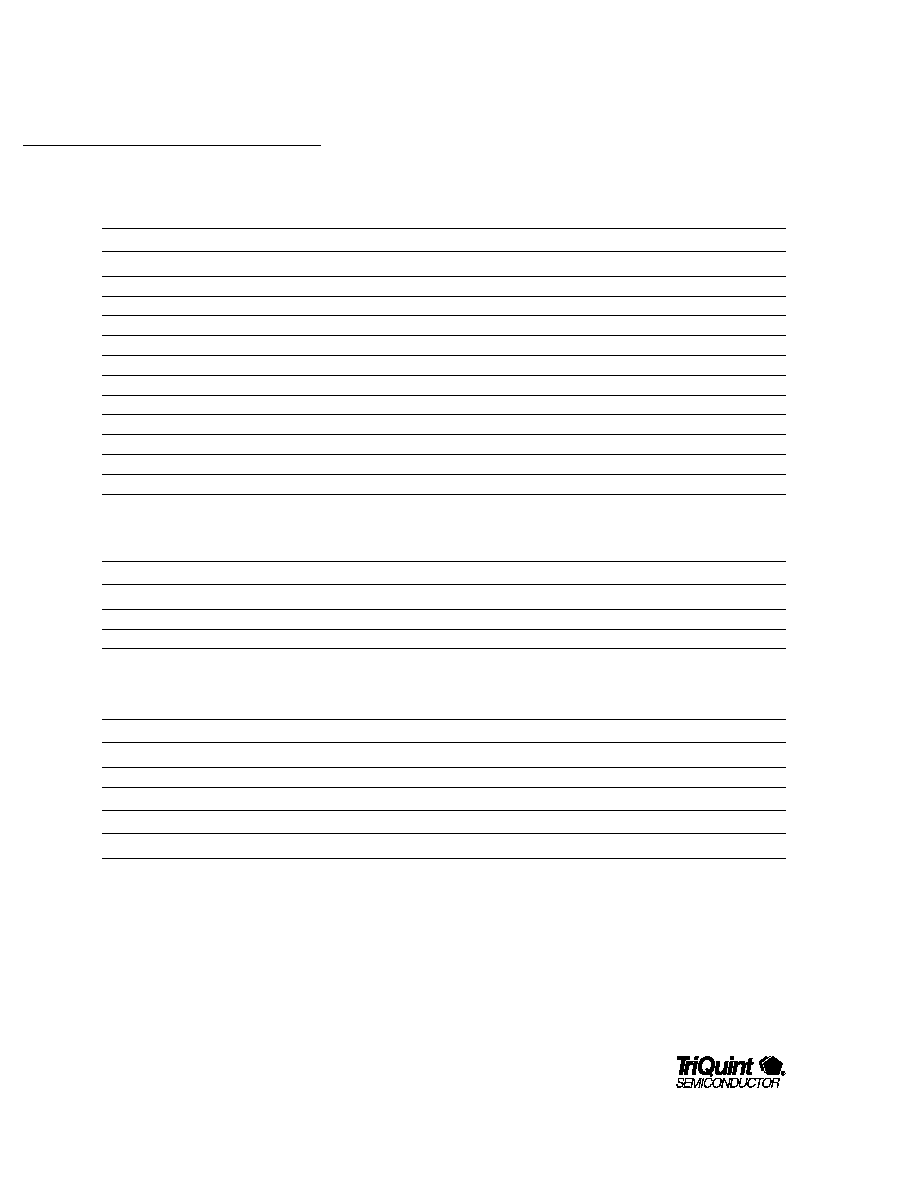

Figure 2. TQ8101C Block Diagram

Figure 3. TQ8101C Package--68-pin MLC

Control

Block

Mux

Serial-to-Parallel

Converter

Loop-

back

Block

PLL Clock

Synthesizer

Mux

Framer

Demux

TXDT

TXCK

RXDT

RXCK

2

2

MXDT(7:0)

CNTL(3:0)

MO

TUNE

IOUT

MXCK(2:0)

MXHC

MXLRC

DXRCK

DXCK

DXDT(7:0)

OOF

DXSYNC

+5V

GND

≠5.2V

2

2

T

OP

V

IEW

1.170

±

.006

.950

±

.010

.800

4 plcs

Pin 1 index

.050

.016

n-4 plcs

n plcs

CuW heat

spreader

1

2

2

3

3

4

A

A

.950

±

.010

S

ECTION

A

A

.050

.060

±

.005

.125

.650

±

.005

B

OTTOM

V

IEW

Chip capacitor

4 plcs

Ceramic

or metal

lid

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

3

For additional information and latest specifications, see our website: www.triquint.com

Functional Description

Figure 2 shows a block diagram of the TQ8101C

multiplexer, demultiplexer, framer, and PLL clock

synthesizer (MDFP). The primary purpose of TQ8101C

is to integrate the conversion of serial and parallel

SONET/SDH data with bit alignment and clock

synthesis in a single device.

Multiplexing

Byte-wide input data on MXDT(7:0)

1

is continuously

strobed into the multiplexer on the rising edge of the

multiplexer clock output, MXCK(2:0).

2

Any of these

three MXCK pins may be used as a reference point for

relative timing. (See Table 8 for setup, hold, and skew

times. See Table 1 for clock selection options.)

Either an on-chip synthesized clock (see "PLL Clock

Synthesis") or an external high-speed multiplexer

Notes:

1. MXDT(0) is defined as the least significant bit.

2. MXCK(2:0) nominally runs at 77.76 MHz in STS-12/STM-4 mode,

and at 19.44 MHz in STS-3/STM-1 mode.

3. Internal signal. See Figure 5, "TQ8101C Loopback Modes."

4. DXDT (0) is defined as the least significant bit.

Frame Detection

and Recovery

Shift

Register

Parallel

Register

1/3

1/8

1/2

1/2

1/3

Mux

DXDTIN

DXHSCK

XFD

OOF

RT

DXDT(7:0)

DXSYNC

DXCK

DXRCK

clock, MXHC, serializes the input data bytes. In the

normal mode of operation, the serial data is then

buffered as ECL-compatible output on TXDT. An ECL

output is provided for the transmit clock, TXCK.

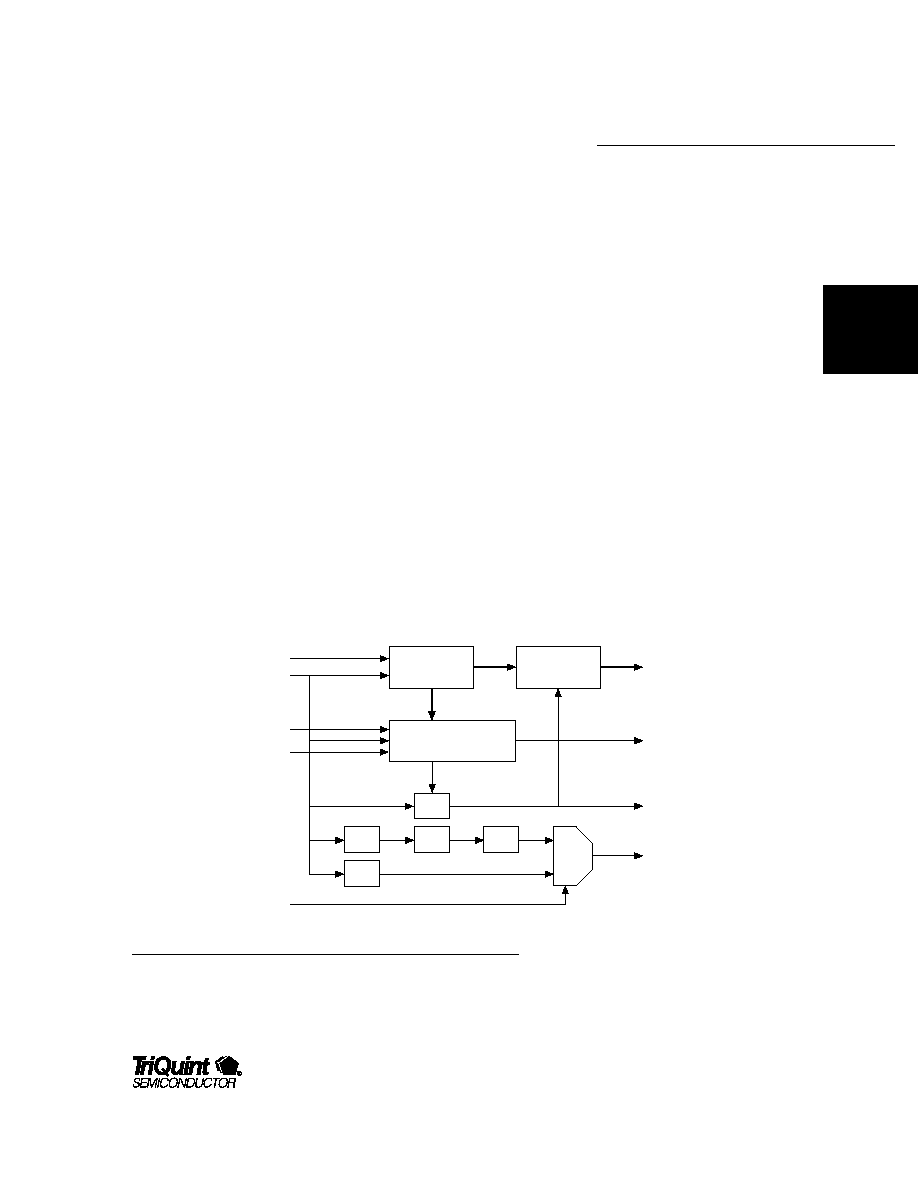

Demultiplexing

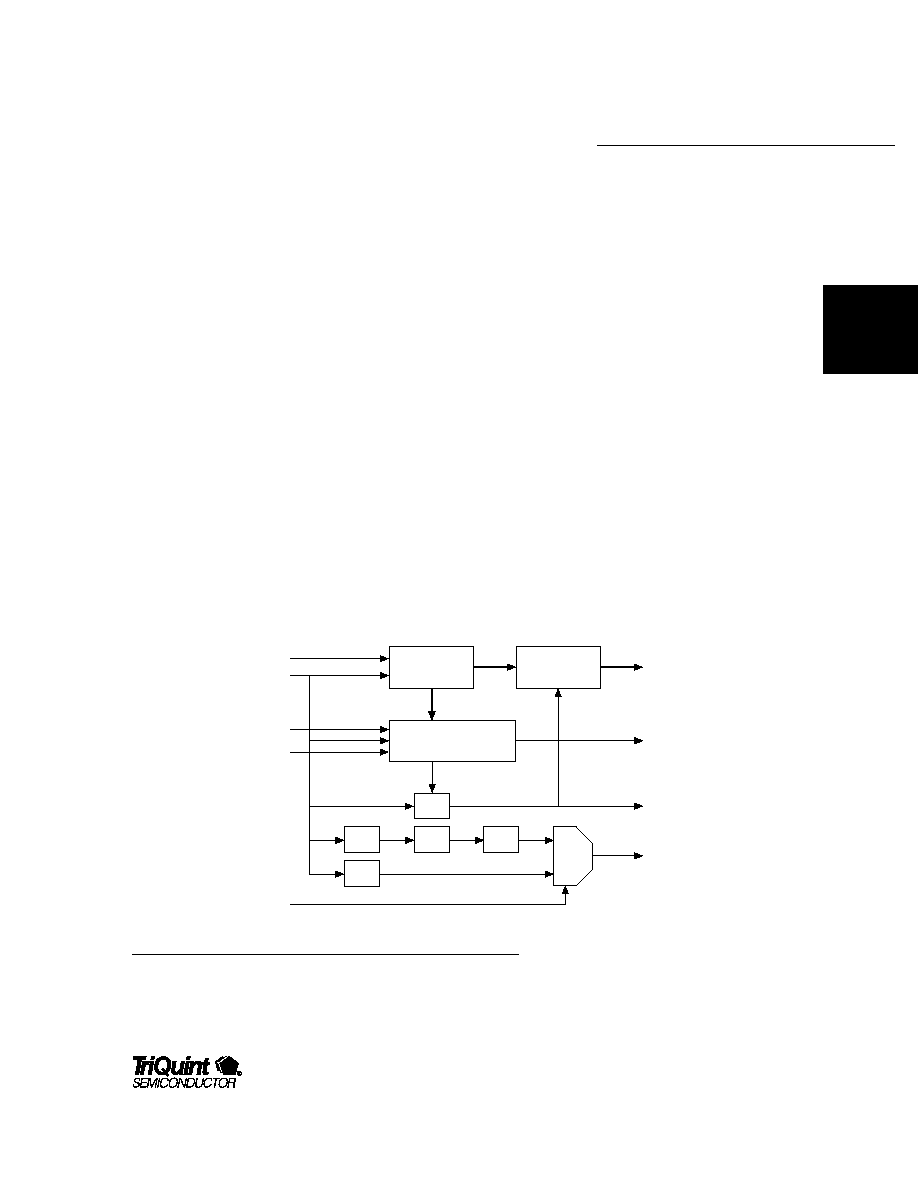

As shown in Figure 4, The demultiplexer block converts

incoming serial data on DXDTIN

3

. Byte-wide output

data is presented on DXDT(7:0)

4

slightly after the

falling edge of the output demultiplexer clock, DXCK.

(See Table 8 for setup, hold, and skew times.)

The demultiplexer block also includes clock divider

circuitry, which is used by the demultiplexer to control

divide-by-8 output on DXCK. The MDFP provides a

divide-by-3 or divide-by-12 output, DXRCK.

(See Table 1 for mode selection options.)

Figure 4. Demultiplexer Functional Block

TQ8101C

4

For additional information and latest specifications, see our website: www.triquint.com

Framing

The demultiplexer block (see Figure 2) includes a

frame-detection and recovery block. Regardless of the

state of the OOF input signal, this block takes DXSYNC

high for one period of DXCK whenever it detects a

pattern of three "A1" bytes followed by three "A2"

bytes.

Frame recovery is initiated by the rising edge of the

OOF input signal. The recovery process involves a

search for a bit rotation that satisfies the three-"A1"≠

three-"A2" byte pattern specified for SONET/SDH. Once

the pattern is found, DXSYNC goes high and the bit

rotation is synchronized to the correct byte boundaries.

No further byte boundary adjustments are made,

regardless of "A1"-"A2" indication, unless they have

been preceded by an OOF rising edge.

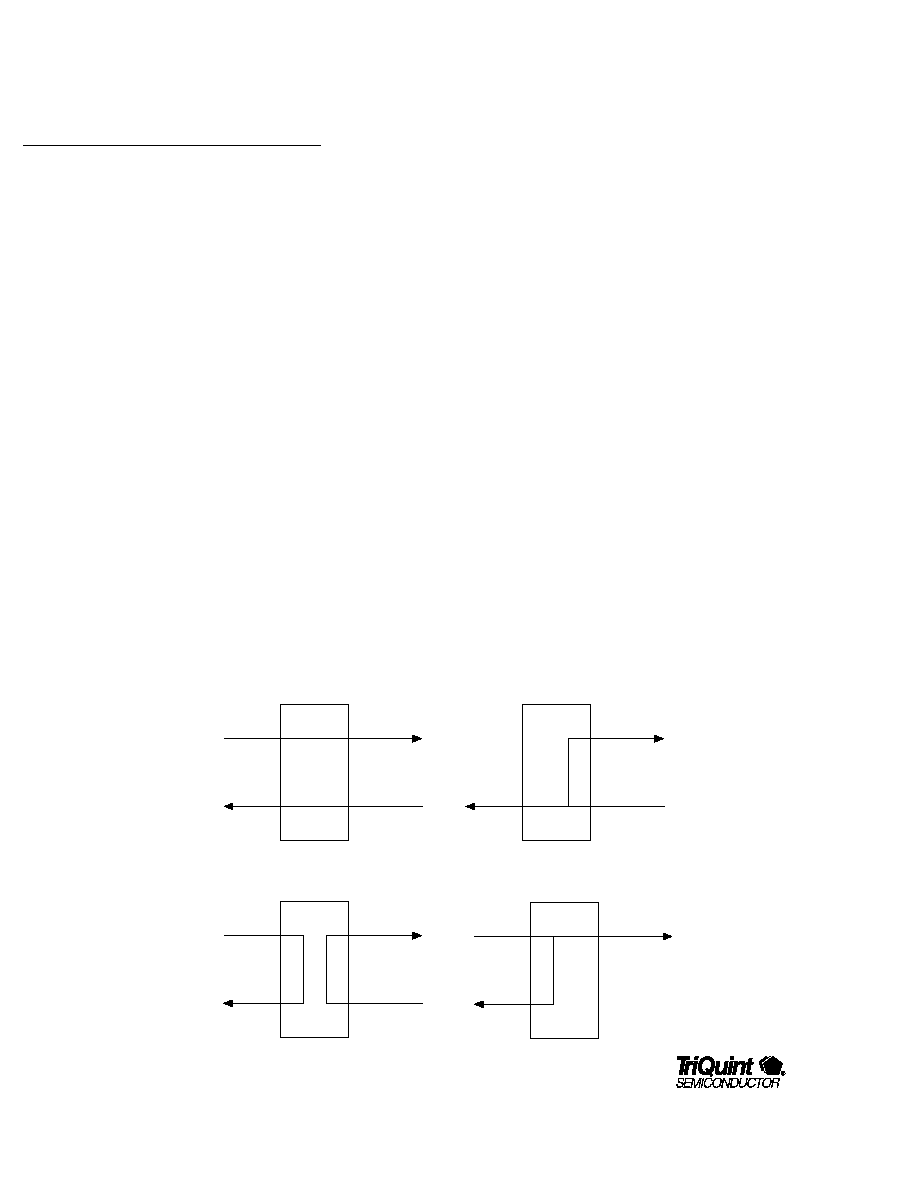

Normal

RXDT

RXCK

TXDT

TXCK

DXDTIN

DXHSCK

MXDTOUT

MXHSCK

Equipment Loopback

TXDT

TXCK

DXDTIN

DXHSCK

MXDTOUT

MXHSCK

Facility Loopback

RXDT

RXCK

TXDT

TXCK

DXDTIN

DXHSCK

Split Loopback

RXDT

RXCK

TXDT

TXCK

DXDTIN

DXHSCK

MXDTOUT

MXHSCK

PLL Clock Synthesis

The PLL utilizes a monolithic voltage-controlled

oscillator with a typical tuning constant of 50 to 100

MHz per volt on the TUNE input. This configuration

provides jitter performance superior to other

technologies. In a typical SONET/SDH application the

TUNE input and charge pump output IOUT are

connected and tied to V

EE

through a 600-ohm resistor

and 0.68-

µ

F capacitor.

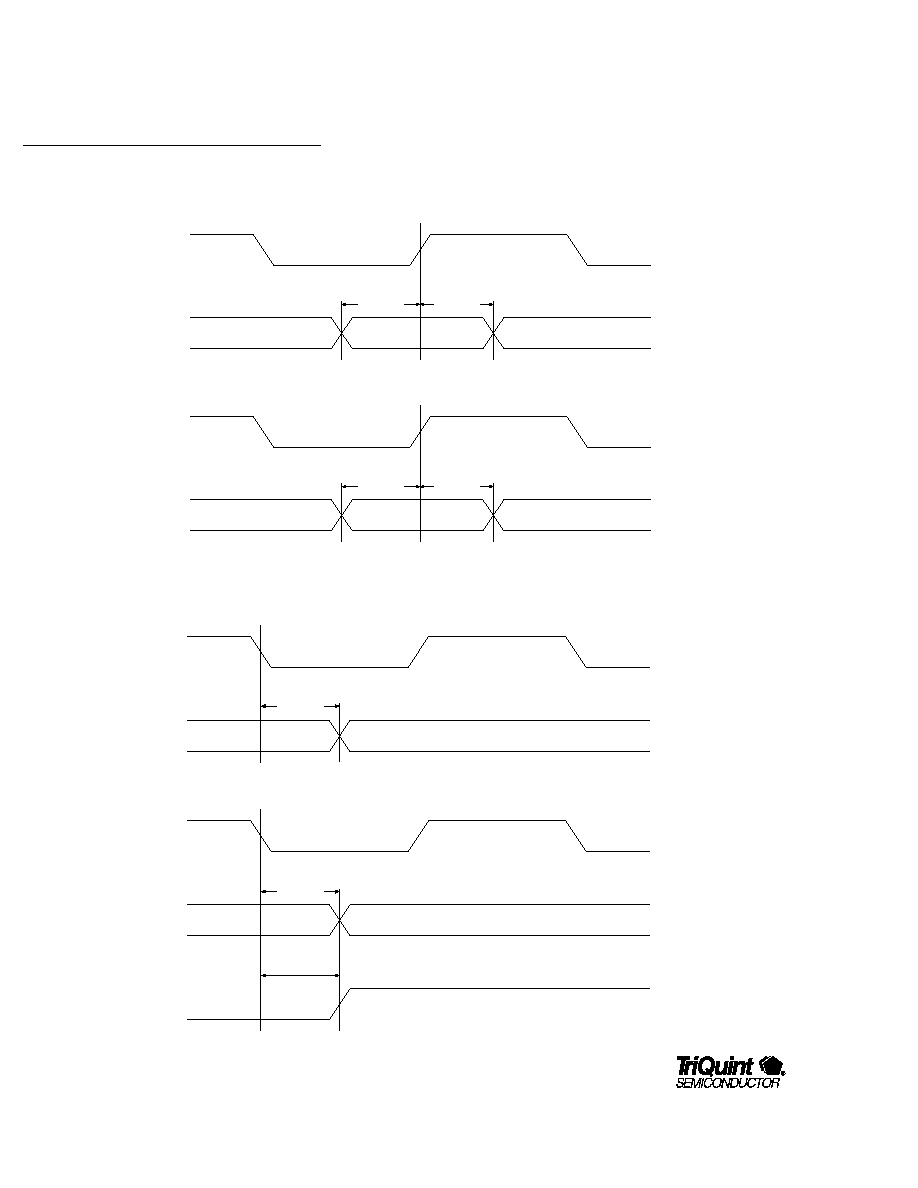

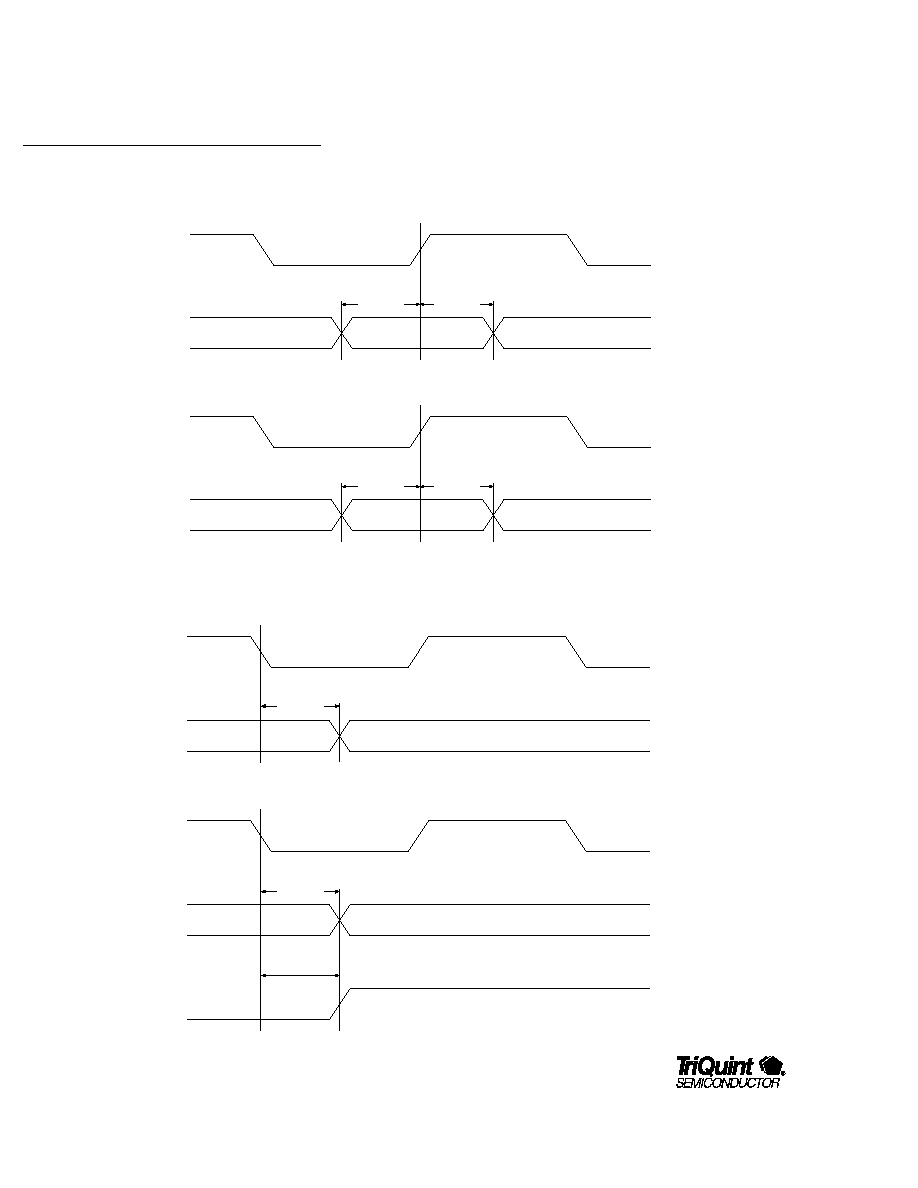

Loopback

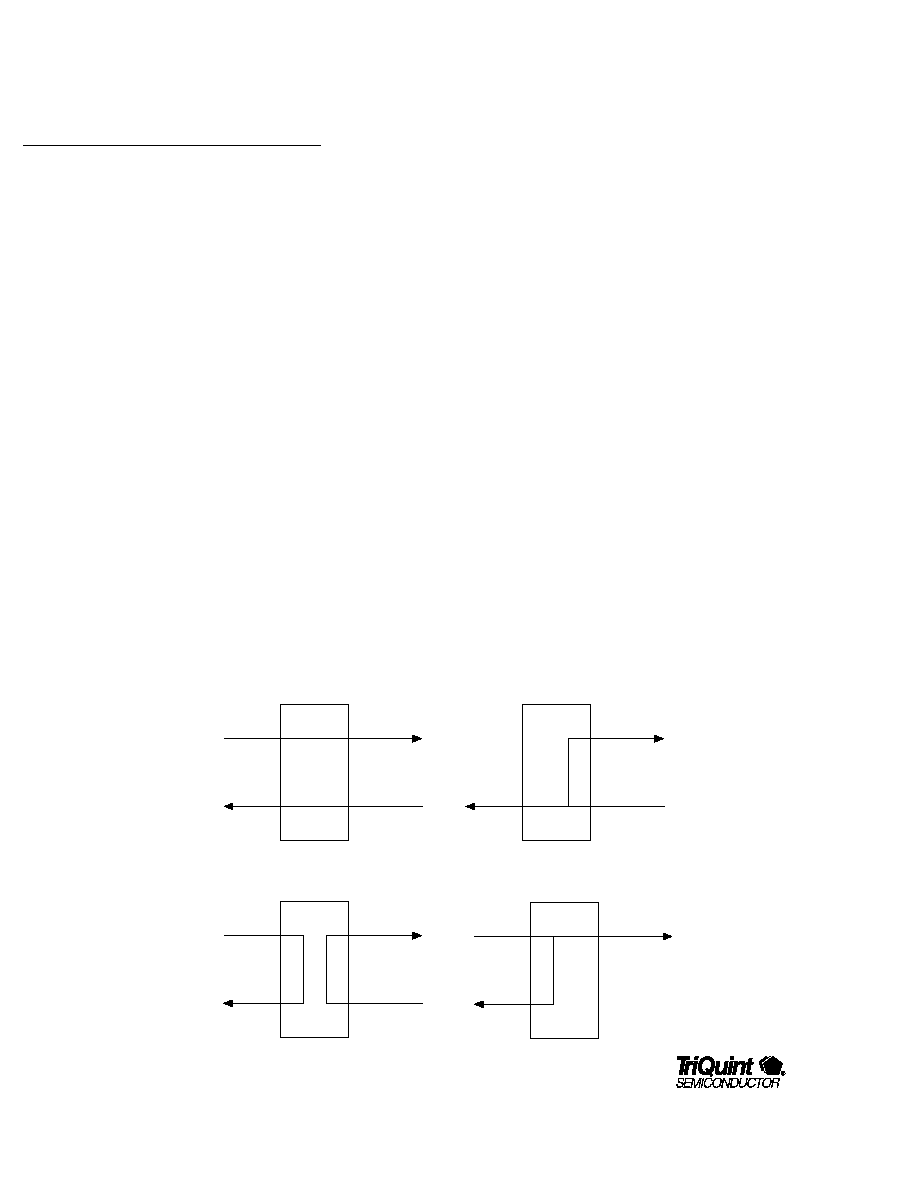

The TQ8101C features four loopback modes: normal

(pass-through), equipment loopback, split loopback,

and facility loopback. Loopback modes are controlled

by pins CNTL(3:0). Note that the loopback mode does

not affect the latched selection of clock modes and

rates. Note that the RXCK input is directly connected to

the TXCK output in most loopback modes (see below).

Figure 5. TQ8101C Loopback Modes

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

5

For additional information and latest specifications, see our website: www.triquint.com

Control

The signals on pins CNTL(3:0) can be used to control

the clock rate, clock mode, loopback scheme, and

tristate pins. Also, the internal PLL high-speed clock

may be disabled, allowing an external clock source to

be used on the MXHCN and MXHCP pins.

Note that the NAND tree enable normally is used only

for device testing of the V

IH

and V

IL

parameters.

Table 1. Modes of Operation

CNTL(3:0)

Modes of operation

0h

Reset

1h

Tristate all TTL outputs except DXRCK and MO

2h

NAND-tree test all TTL inputs except CNTL(3:0)

3h

DXRCK tristate

4h

Frame recovery disable

5h

Equipment loopback

6h

Facility loopback

7h

Split loopback

8h

Bypass, slave, internal VCO disabled, STS-3 rate

9h

Bypass, master, internal VCO disabled, STS-3 rate

Ah

Bypass, slave, internal VCO disabled, STS-12 rate

Bh

Bypass, master, internal VCO disabled, STS-12 rate

Ch

Normal, slave, internal VCO enabled, STS-3 rate

Dh

Normal, master, internal VCO enabled, STS-3 rate

Eh

Normal, slave, internal VCO enabled, STS-12 rate

Fh

Normal, master, internal VCO enabled, STS-12 rate

Notes: ∑ "Bypass" indicates the use of the external high-speed clock in lieu of the internal transmit PLL.

∑ "Normal" indicates use of the internal transmit PLL.

∑ "Master" derives PLL timing from the reference 51.84-MHz oscillator input, MXLRC

∑ "Slave" derives PLL timing from the demultiplexer clock input, RXCK.

At power-up or during initialization, CNTL(3) should

be set to logic 1. During reset, all internal counters,

dividers, and loopback states, and the phase-

frequency detector, are reset or deactivated. Note that

frame search is initiated only by a rising edge on OOF.

TQ8101C

6

For additional information and latest specifications, see our website: www.triquint.com

Table 2. Absolute Maximum Ratings

Parameter

Symbol

Level

Minimum

Maximum

Unit

Positive supply

V

CC

--

0

7

V

Negative supply

V

EE

--

≠7

0

V

Output voltage

V

O

ECL

V

EE

≠ 0.5

+0.5

V

Output current

I

O

ECL

--

40

mA

Input voltage

V

I

ECL

V

EE

≠ 0.5

+0.5

V

Input current

I

I

ECL

≠1

1

mA

Output voltage

V

O

TTL

≠0.5

V

CC

+ 0.5

V

Output current

I

O

TTL

--

20

mA

Input voltage

V

I

TTL

≠0.5

V

CC

+ 0.5

V

Input current

I

I

TTL

≠1

1

mA

Junction temperature

T

J

--

≠55

+150

∞C

Storage temperature

T

S

--

≠65

+175

∞C

Table 3. Recommended Operating Conditions

Parameter

Symbol

Minimum

Nominal

Maximum

Unit

Positive supply

V

CC

4.75

5

5.25

V

Negative supply

V

EE

≠5.5

≠5.2

≠4.75

V

Operating ambient temperature

T

O

0

70

∞C

Table 4. Power Consumption

Function

+5 V supply

≠5.2 V supply

Unit

Nominal

40

320

mA

Max

55

420

mA

Parameter

Symbol

Level

Minimum

Maximum

Unit

Thermal resistance, junction-case

JC

4

∞C / W

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

7

For additional information and latest specifications, see our website: www.triquint.com

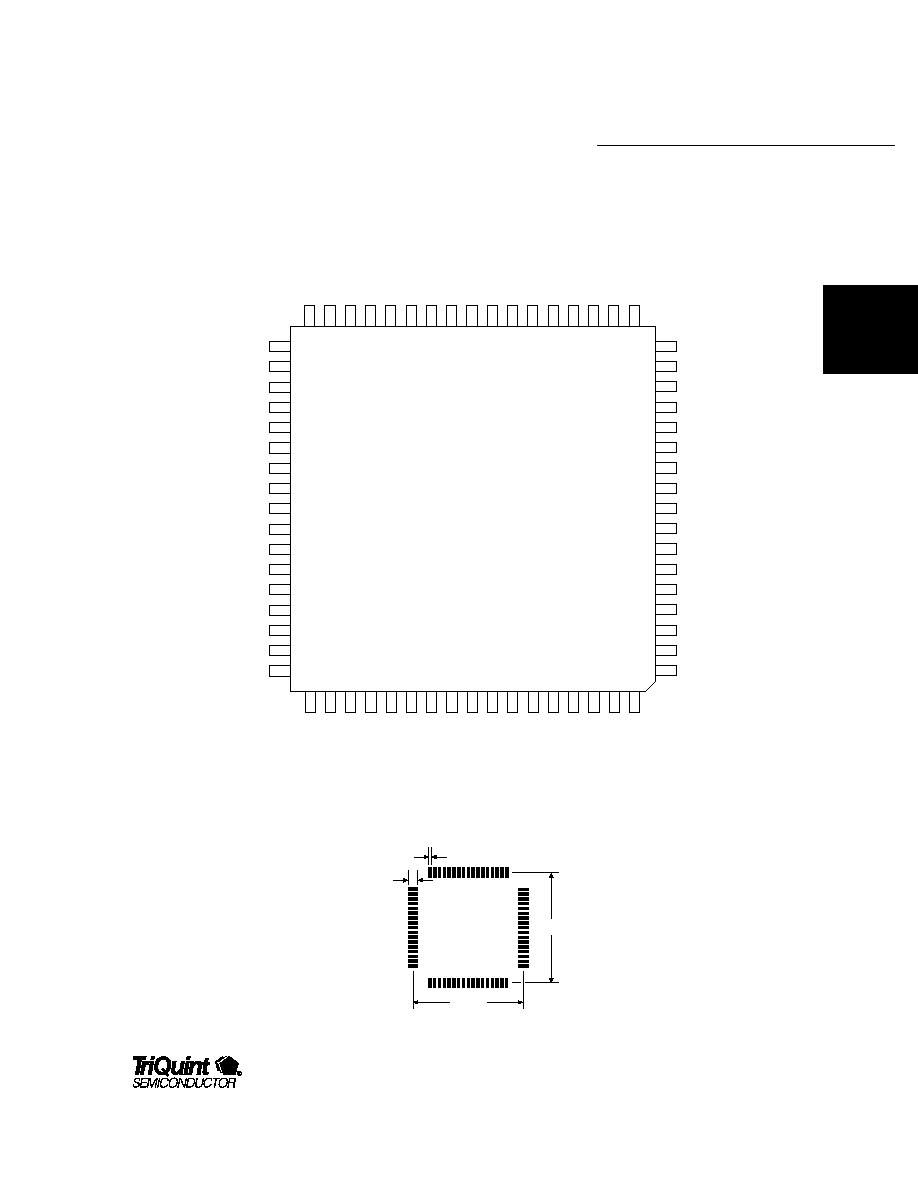

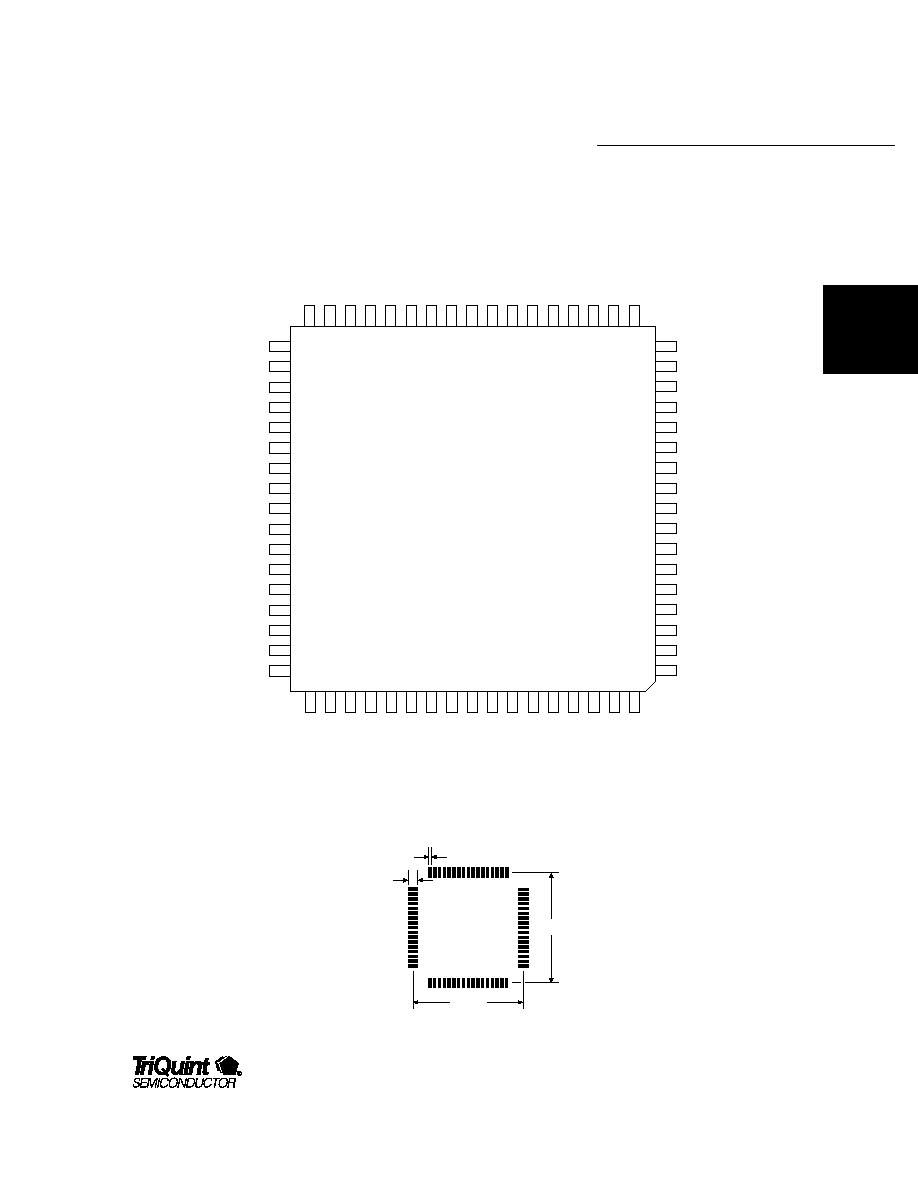

Figure 6. Pinout Diagram

(heat spreader side--top view)

Figure 7. Recommended Package Footprint

1 V

EE

2 GND

3 RXCKP

4 RXCKN

5 GND

6 RXDTN

7 RXDTP

8 GND

9 TXCK

10 TXDTP

11 GND

12 TXDTN

13 MO

14 GND

15 OOF

16 DXRC

17 GND

68 GND

67 CNTL0

66 CNTL1

65 GND

64 CNTL2

63

TUNE

62 GND

61 IOUT

60 CNTL3

59 GND

58 MXHCP

57 MXHCN

56 GND

55 MXLRC

54 MXCK0

53 GND

52 V

CC

18 V

CC

19 GND

20 DXDT7

21 DXDT6

22 GND

23 DXDT5

24 DXDT4

25 GND

26 DXDT3

27 DXDT2

28 GND

29 DXDT1

30 DXDT0

31 GND

32 DXCK

33 DXSYN

34 GND

51 GND

50 MXCK1

49 MXCK2

48 GND

47 MXDT0

46 MXDT1

45 GND

44 MXDT2

43 MXDT3

42 GND

41 MXDT4

40 MXDT5

39 GND

38 MXDT6

37 MXDT7

36 GND

35 V

EE

TQ8101C

MDFP

1.150

1.150

.026

.096

TQ8101C

8

For additional information and latest specifications, see our website: www.triquint.com

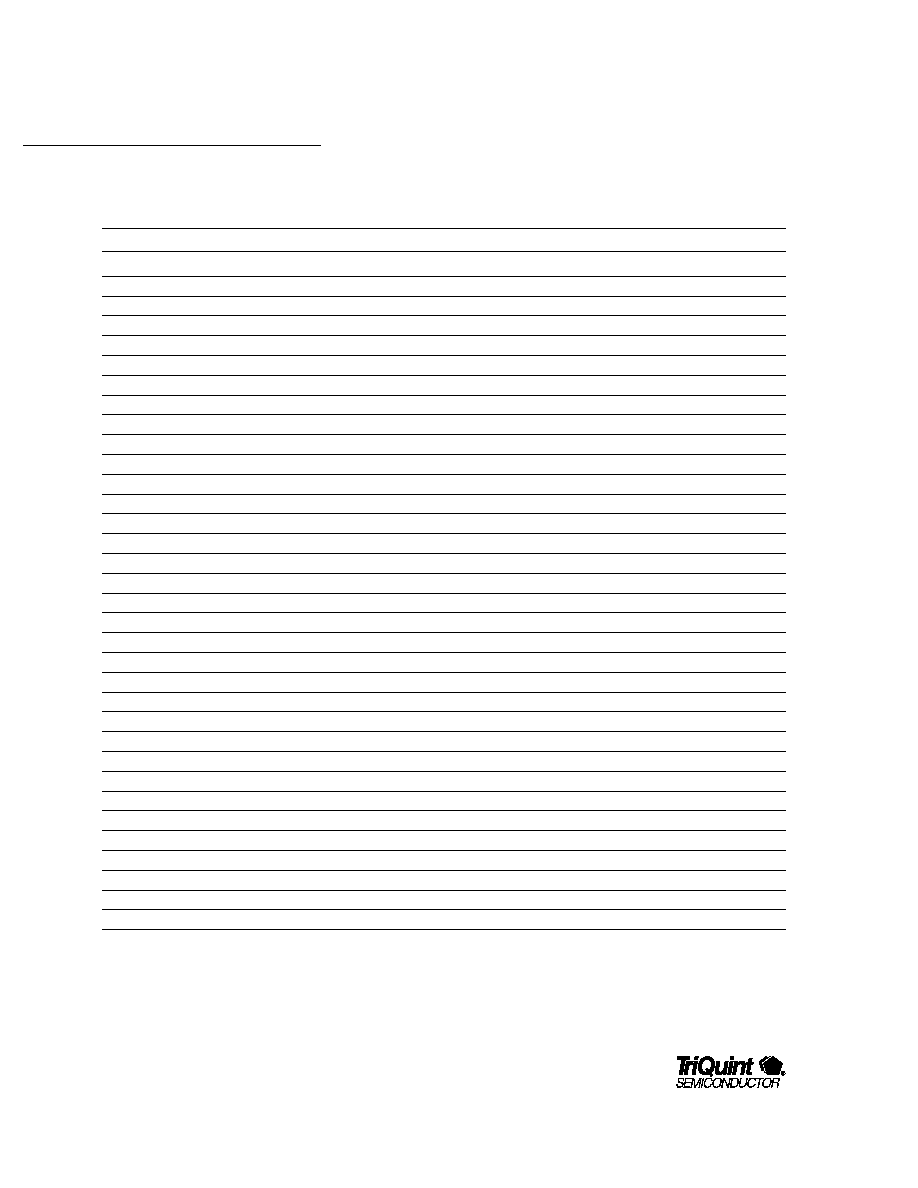

Table 5. Signal Descriptions

Pin

Signal

Type

Description

1

V

EE

Negative power supply input (≠5.2V)

2

GND

Ground

3

RXCKP

In

Receive bit-serial clock; differential ECL, positive

4

RXCKN

In

Receive bit-serial clock; differential ECL, negative

5

GND

Ground

6

RXDTN

In

Receive bit-serial data (MSB first); differential ECL, negative

7

RXDTP

In

Receive bit-serial data (MSB first); differential ECL, positive

8

GND

Ground

9

TXCK

Out

Transmit bit-serial clock; single-ended ECL level

10

TXDTP

Out

Transmit bit-serial data (MSB first); differential ECL, positive

11

GND

Ground

12

TXDTN

Out

Transmit bit-serial data (MSB first); differential ECL, negative

13

MO

Out

NAND tree monitor output; TTL level

14

GND

Ground

15

OOF

In

Out of frame; TTL level; rising-edge initiated frame search

16

DXRCK

Tri Out

Demultiplexer reference clock; TTL level; 50-pF backplane driving capacity

17

GND

Ground

18

V

CC

Positive power supply input (+5.0V)

19

GND

Ground

20

DXDT7

Tri Out

Demultiplexer byte-serial data (bit 7); TTL level

21

DXDT6

Tri Out

Demultiplexer byte-serial data (bit 6); TTL level

22

GND

Ground

23

DXDT5

Tri Out

Demultiplexer byte-serial data (bit 5); TTL level

24

DXDT4

Tri Out

Demultiplexer byte-serial data (bit 4); TTL level

25

GND

Ground

26

DXDT3

Tri Out

Demultiplexer byte-serial data (bit 3); TTL level

27

DXDT2

Tri Out

Demultiplexer byte-serial data (bit 2); TTL level

28

GND

Ground

29

DXDT1

Tri Out

Demultiplexer byte-serial data (bit 1); TTL level

30

DXDT0

Tri Out

Demultiplexer byte-serial date (bit 0); TTL level

31

GND

Ground

32

DXCK

Tri Out

Demultiplexer byte-serial clock; TTL level

33

DXSYNC

Tri Out

Demultiplexer synchronization; TTL level

34

GND

Ground

(Continues on next page)

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

9

For additional information and latest specifications, see our website: www.triquint.com

Table 5. Signal Descriptions (continued)

Pin

Signal

Type

Description

35

V

EE

Negative power supply input (≠5.2V)

36

GND

Ground

37

MXDT7

In

Multiplexer byte-serial data (bit 7); TTL level

38

MXDT6

In

Multiplexer byte-serial data (bit 6); TTL level

39

GND

Ground

40

MXDT5

In

Multiplexer byte-serial data (bit 5); TTL level

41

MXDT4

In

Multiplexer byte-serial data (bit 4); TTL level

42

GND

Ground

43

MXDT3

In

Multiplexer byte-serial data (bit 3); TTL level

44

MXDT2

In

Multiplexer byte-serial data (bit 2); TTL level

45

GND

Ground

46

MXDT1

In

Multiplexer byte-serial data (bit 1); TTL level

47

MXDT0

In

Multiplexer byte-serial data (bit 0); TTL level

48

GND

Ground

49

MXCK2

Tri Out

Multiplexer byte-serial clock (bit 2); TTL level. See Table 1 for output rate.

50

MXCK1

Tri Out

Multiplexer byte-serial clock (bit 1); TTL level. See Table 1 for output rate.

51

GND

Ground

52

V

CC

Positive power supply input (+5.0V)

53

GND

Ground

54

MXCK0

Tri Out

Multiplexer byte-serial clock (bit 0); TTL level. See Table 1 for output rate.

55

MXLRC

In

Multiplexer low-speed reference clock (51.84 MHz); TTL level

56

GND

Ground

57

MXHCN

In

Multiplexer high-speed reference clock (max. 640 MHz); differential ECL, negative

58

MXHCP

In

Multiplexer high-speed reference clock (max. 640 MHz); differential ECL, positive

59

GND

Ground

60

CNTL3

In

Control (bit 3); TTL level

61

IOUT

Out

Tristate charge pump output (analog); connect to pin 63

62

GND

Ground

63

TUNE

In

VCO tune (analog); connect to external loop filter and pin 61

64

CNTL2

In

Control (bit 2); TTL level

65

GND

Ground

66

CNTL1

In

Control (bit 1); TTL level

67

CNTL0

In

Control (bit 0); TTL level

68

GND

Ground

TQ8101C

10

For additional information and latest specifications, see our website: www.triquint.com

Table 6. DC Characteristics--ECL I/O

(1)

Parameter

Condition

Symbol

Minimum

Nominal

Maximum

Unit

Internal ECL reference

(2)

V

REF

--

0.26 V

EE

mV

Common mode voltage

(3)

V

COM

≠1500

--

≠1100

mV

Differential voltage

(3)

V

DIFF

200

--

1200

mV

Input HIGH voltage

(4)

V

IH

≠1100

--

≠400

mV

Input LOW voltage

V

IL

V

EE

--

≠1500

mV

Output HIGH voltage

(5)

V

OH

≠1000

0

≠500

mV

Output LOW voltage

(5)

V

OL

V

TT

≠ 100

--

≠1600

mV

Input HIGH current

V

IH (MAX)

I

IH

--

--

30

mA

Input LOW current

V

IL (MIN)

I

IL

--

--

≠30

mA

Output HIGH current

(6)

I

OH

20

23

30

mA

Output LOW current

(6)

I

OL

≠2

5

8

mA

Input capacitance

C

IN

--

3

--

pF

Output capacitance

C

OUT

--

3

--

pF

ESD breakdown

(1)

V

ESD

500

--

--

V

Table 7. DC Characteristics--TTL I/O

(1)

Parameter

Condition

Symbol

Minimum

Nominal

Maximum

Unit

Input HIGH voltage

V

IH

2.0

--

V

CC

V

Input LOW voltage

V

IL

0

--

0.8

V

Input HIGH current

V

IH (MAX)

I

IH

--

--

100

mA

Input LOW current

V

IL (MIN)

I

IL

≠100

--

--

mA

Output HIGH voltage

I

OH

= 3 mA

V

OH

2.4

--

V

CC

V

Output LOW voltage

I

OL

= ≠1 mA

V

OL

0

--

0.4

V

Tristate current

I

OZ

≠100

--

100

mA

Input capacitance

C

IN

--

8

--

pF

Output capacitance

C

OUT

--

10

--

pF

ESD breakdown

(1)

V

ESD

1000

--

--

V

Notes (tables 6 and 7):

1. Specifications apply over recommended operating ranges.

2. Single-ended inputs

3. Differential inputs

4. V

REF

= ≠1300 mV

5. R

LOAD

= 50 ohms to V

TT

= ≠2.0V

6. Not tested; consistent with V

OH

and V

OL

tests

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

11

For additional information and latest specifications, see our website: www.triquint.com

Table 8. AC Characteristics

Parameter

Symbol

Minimum

Nominal

Maximum

Unit

RXCK clock period

T

C(RXCK)

1.6

--

--

ns

MXHC clock period

T

C(MXHC)

1.6

--

--

ns

TXCK clock period

T

C(TXCK)

1.6

--

--

ns

MXCK clock period

T

C(MXCK)

12.8

--

--

ns

DXCK clock period

T

C(DXCK)

12.8

--

--

ns

MXLRC clock period

T

C(MXTRC)

18.87

19.29

19.61

ns

DXRCK clock period

T

C(DXRCK)

4.80

19.29

--

ns

RXCK clock duty cycle

T

DC(RXCK)

30

50

70

%

MXHC clock duty cycle

T

DC(MXHC)

30

50

70

%

TXCK clock duty cycle

T

DC(TXCK)

40

50

60

%

MXCK clock duty cycle

T

DC(MXCK)

40

50

60

%

DXCK clock duty cycle

T

DC(DXCK)

40

50

60

%

MXLRC clock duty cycle

T

DC(MXIRC)

30

50

70

%

DXRCK clock duty cycle

T

DC(DXRCK)

40

50

60

%

High-speed rise/fall time

1

(more than 79 MHz)

T

H(R/F)

--

--

320

ps

Low-speed rise/fall time

1

(less than 79 MHz)

T

L(R/F)

--

--

2.56

ns

CNTL(2:0) Setup Time to CNTL(3)

T

S(CNTL)

5500

--

--

ps

CNTL(2:0) Hold Time to CNTL(3)

T

H(CNTL)

2000

--

--

ps

RXDT setup time to RXCK

T

S(RXDT)

225

--

--

ps

RXDT hold time to RXCK

T

H(RXDT)

125

--

--

ps

OOF rising edge before A1 changes to A2

T

(OOFH)

51.44

--

--

ns

OOF pulse width

T

(OOFPW)

12.86

--

--

ns

DXSYNC rising edge from parallel

T

(DSYNC)

--

25.72

--

ns

data output change from A1 to A2

DXSYNC pulse width

T

(DXSYNCPW)

12.86

--

--

ns

DXCK falling edge to valid parallel data output

T

P(DXDT)

T

C(RXCK)

T

C(RXCK)

+ 0.5

T

C(RSCK)

+ 1.5

ns

MXDT(0:7) setup time to MXCK

T

S(MXDT)

4500

--

--

ps

MXDT(0:7) hold time to MXCK

T

H(MXDT)

≠2000

--

--

ps

TXCK falling edge to TXDT

T

P(TXDT)

--

--

500

ps

Notes:

1. 20% to 80% of min V

OH

and max V

OL

levels.

TQ8101C

12

For additional information and latest specifications, see our website: www.triquint.com

Figure 8. Input Timing

Figure 9. Output Timing

RXCKP

RXDT

T

S(RXDT)

T

H(RXDT)

MXCK(2:0)

MXDT(7:0)

T

S(MXDT)

T

H(MXDT)

DXCK

DXDT(7:0)

T

P(DXDT)

DXSYNC

T

P(DXSYNC)

TXCK

TXDT

T

P(TXDT)

TQ8101C

SONET/SDH/A

TM

TELECOM

PRODUCTS

13

For additional information and latest specifications, see our website: www.triquint.com

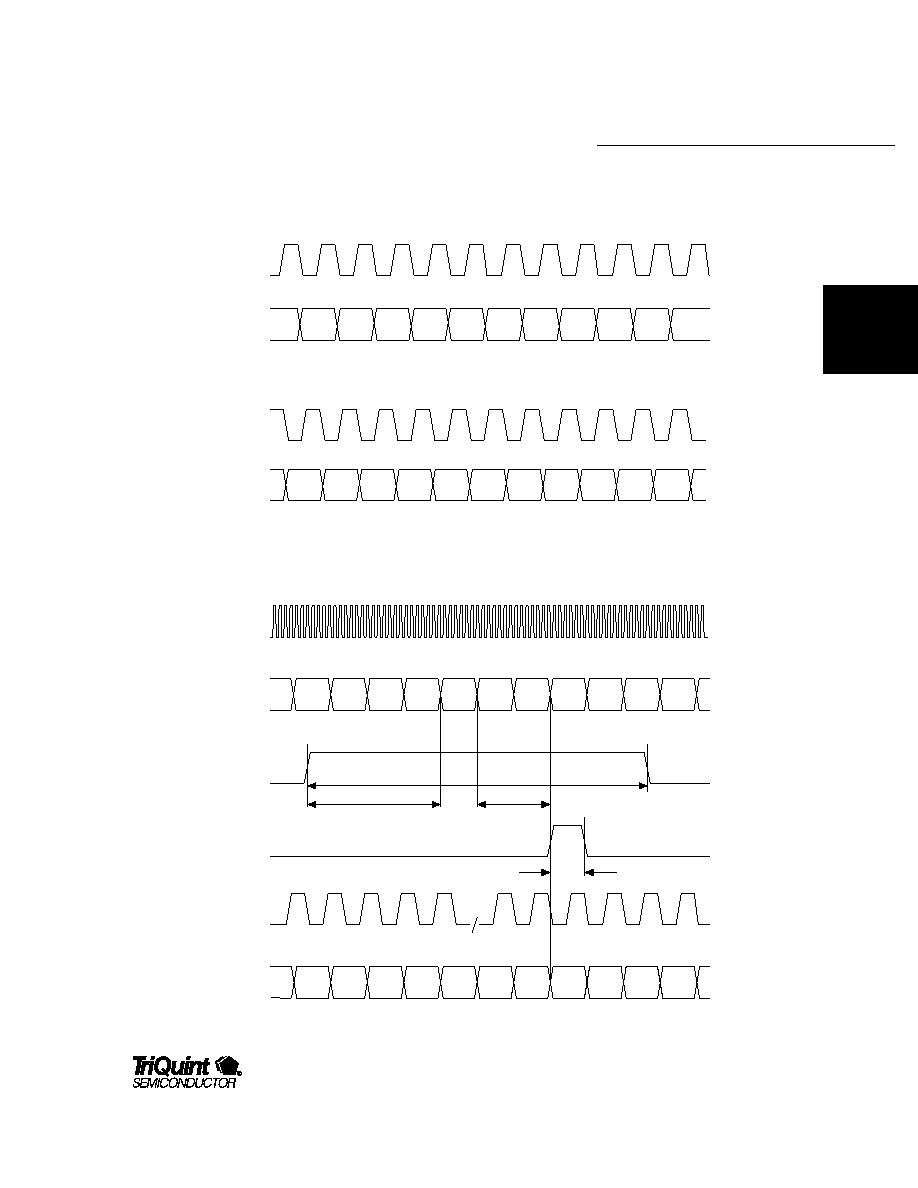

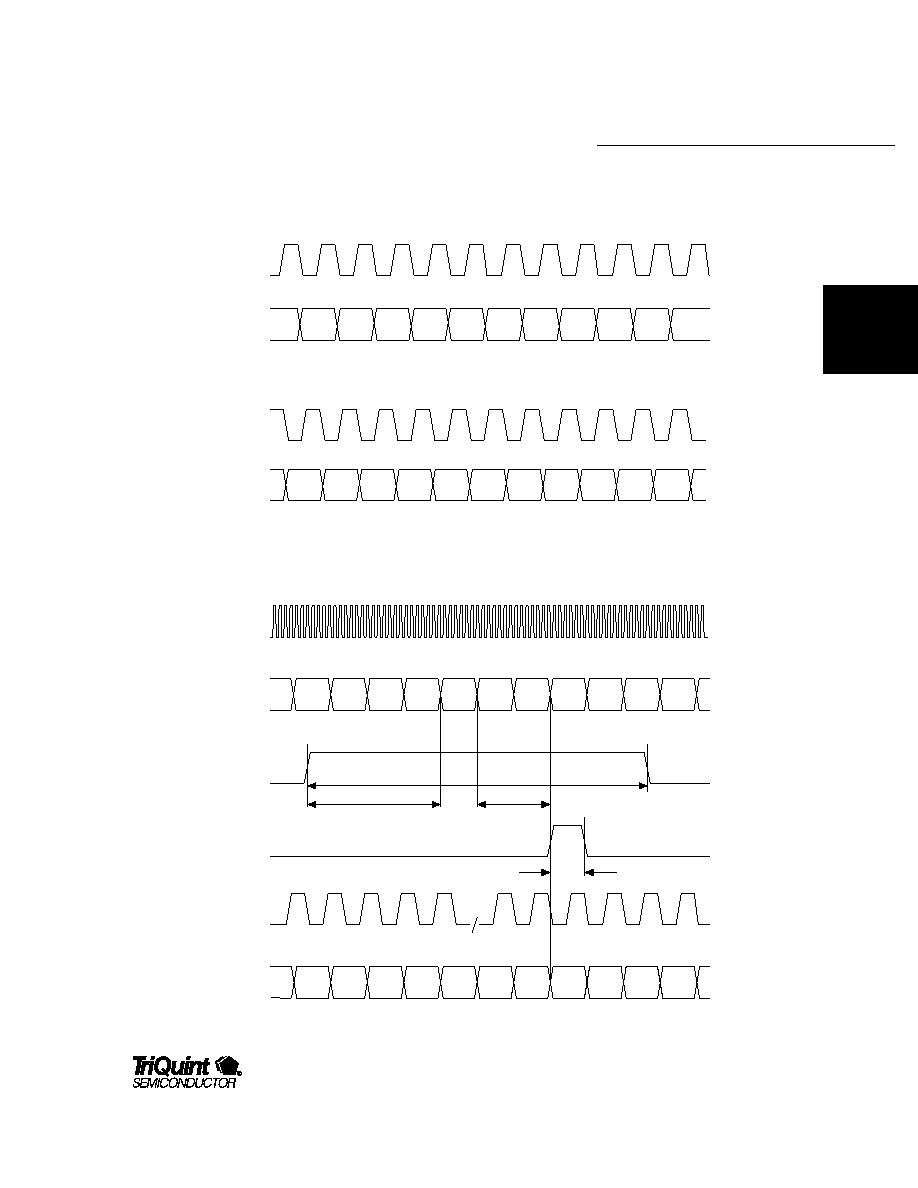

Figure 10. Multiplexer Timing

TXCK

TXDT

MXCK(2:0)

MXDT(7:0)

OOF

DXSYNC

RXDT

DXCK

DXDT(7:0)

RXCK

DXCK Resync

T

(DXSYNCPW)

T

(OOFH)

T

(DXSYNC)

T

(OOFPW)

A1

#1

A1

#2

A1

#

n

A2

#1

A2

#2

A2

#3

A1

#1

A1

#2

A1

#

n

A2

#1

A2

#2

A2

#3

Figure 11. Demultiplexer Timing

TQ8101C

14

For additional information and latest specifications, see our website: www.triquint.com

SONET/SDH Considerations

Jitter Tolerance

This measurement does not apply to the TQ8101C,

since data is transmitted from the input parallel bus

relative to a TQ8101C-generated clock output

(MXCK[2:0]). The user must meet setup and hold time

requirements in order to ensure that data tracking is

maintained.

Ordering Information

TQ8101-M

SONET/SDH MDFP

Evaluation Board

Please contact a TriQuint representative or the factory

for availability and pricing.

Additional Information

For latest specifications, additional product information,

worldwide sales and distribution locations, and information about TriQuint:

Web: www.triquint.com

Tel: (503) 615-9000

Email: sales@tqs.com

Fax: (503) 615-8900

For technical questions and additional information on specific applications:

Email: applications@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or

omissions. TriQuint assumes no responsibility for the use of this information, and all such information

shall be entirely at the user's own risk. Prices and specifications are subject to change without notice.

No patent rights or licenses to any of the circuits described herein are implied or granted to any third party.

TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

Copyright © 1997 TriQuint Semiconductor, Inc. All rights reserved.

Revision 1.1.A

November 1997

Jitter Generation

By exploiting material characteristics, fully differential

SCFL logic, and on-chip reactive elements, the

TQ8101C typically has a jitter generation of 0.008 UI

RMS (where 1 UI is 1/622.08E06) using recommended

loop filter component values.