| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TQ9147B | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

WIRELESS COMMUNICATIONS DIVISION

For additional information and latest specifications, see our website:

www.triquint.com

1

Electrical Characteristics

TQ9147B

DATA SHEET

2-Stage AMPS

Power Amplifier IC

Features

ß

High Efficiency

ß

+32 dBm Output Power

ß

50

Matched Input

ß

SO-16 Plastic Package

ß

Monolithic Power Amp

Applications

ß

AMPS Mobile Phones

ß

CDPD Modems

ß

General ISM Band Applications

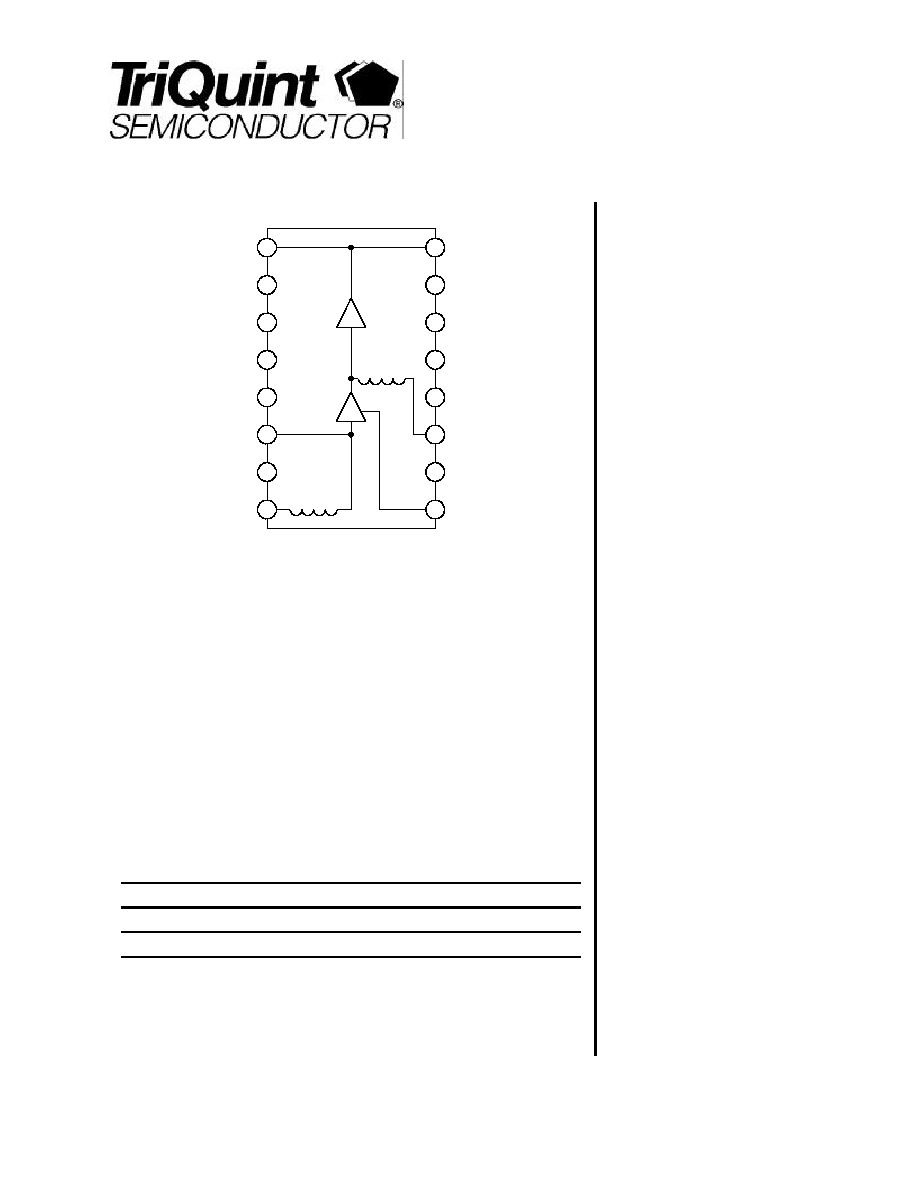

1

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

RF

OUT

RF

OUT

GND

GND

GND

RF

IN

GND

GND

GND

GND

GND

GND

GND

V

G1

V

G2

V

D1

Product Description

The TQ9147 is a high efficiency two stage GaAs MESFET power amplifier IC

intended for use in AMPS (IS-19) applications that operate in the US Cellular (824 -

849 MHz) band. The TQ9147 requires minimal external RF circuitry and operates

from a 4.8-Volt supply. With its flexible, off-chip, single component output matching

circuit, the TQ9147 is suitable for use in other applications near the cellular band,

such as 900 MHz ISM applications.

The TQ9147 utilizes a space saving SO-16 plastic package that minimizes board

area and cost.

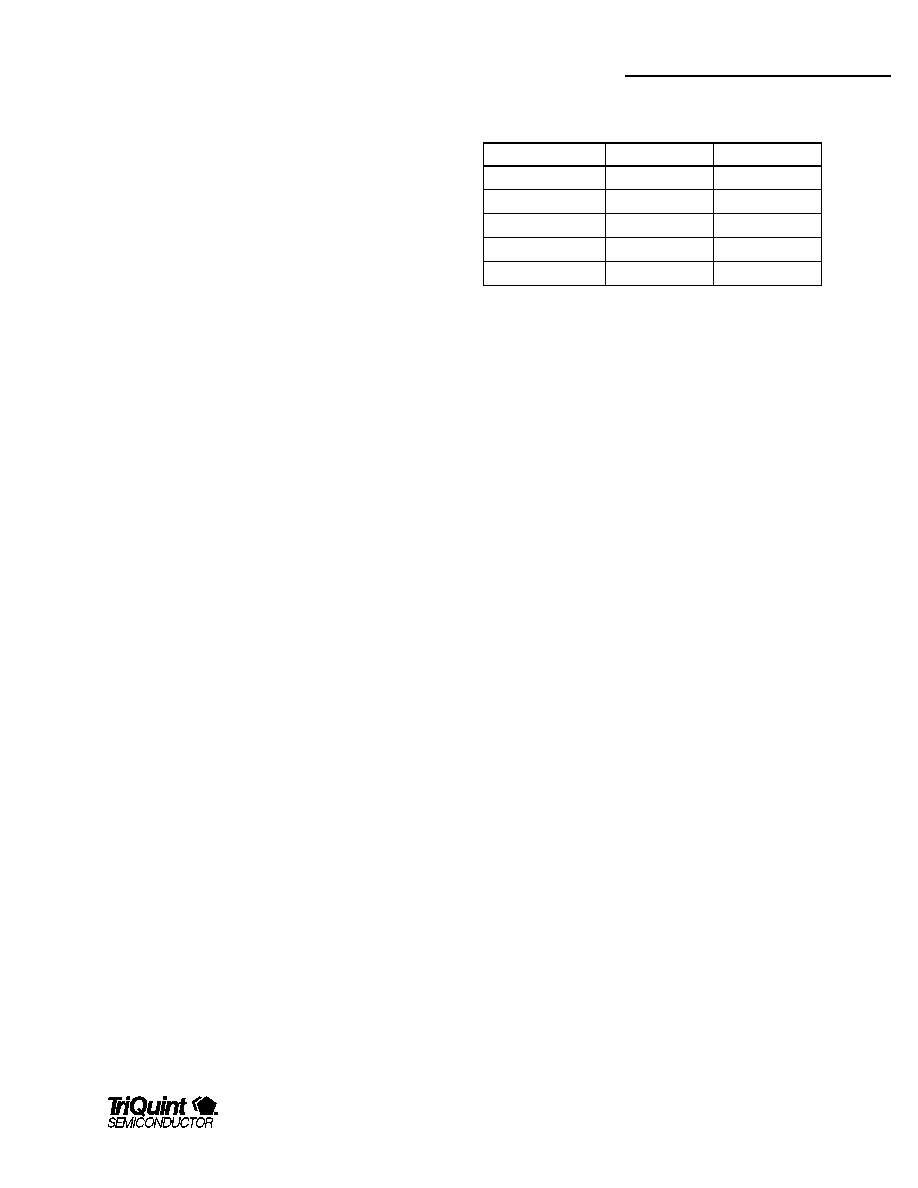

Electrical Specifications

1

Parameter

Min

Typ

Max

Units

Output Power

+31.5

+32

dBm

Efficiency

55

60

%

Note 1: Test Conditions: V

DD

= 4.8 V, P

IN

= +7 dBm,

Freq. = 824 & 849 MHz,

T

C

= 25

∞

C,

Min/max values 100% production tested.

TQ9147B

Data Sheet

2

For additional information and latest specifications, see our website:

www.triquint.com

Electrical Characteristics

Parameter

1

Conditions

Min

Typ/Nom

Max

Units

Frequency

tuned for cellular band

824

849

MHz

Supply Voltage (V

DD

)

2.7

4.8

6.0

V

Temperature

measured at case

-40

25

+110

o

C

P

OUT

V

DD

= 4.8 V

V

DD

= 4.3 V

31.5

32

30

dBm

dBm

Efficiency

55

60

%

Rx band Noise

2

P

IN

= -30 to +7 dBm

-90

dBm

Small Signal Gain

P

IN

= -10 dBm

32

dB

Power Gain

P

OUT

= 32 dBm (typ)

25

dB

Input Return Loss

P

IN

= -30 to +7 dBm

10

dB

Harmonics

2nd Harmonic

3rd Harmonic

4th Harmonic

-30

-35

-35

dBc

dBc

dBc

Spurious (Stability)

P

IN

= -30 to +7 dBm

-70

dBc/30 kHz

RF Off Isolation

20

dBc

Ruggedness

V

DD

at burnout

6.5

V

Note 1: Test Conditions: V

DD

= 4.8 V, P

IN

= +7 dBm, Freq. = 824 & 849 MHz, V

GG

= 3.5 V, T

C

= 25

∞

C.

Note 2: Noise power is measured in 30 kHz band width at the transmit frequency plus 45 MHz

Note 3: Load is set to 50 ohms, output power measured at nominal test conditions. Load VSWR is set to 10:1 and the angle is varied 360 degrees over 5 seconds.

Load set to 50 ohms, output power remeasured and compared with the first measurement to check for no degradation from the first measurement.

Absolute Maximum Ratings

Parameter

Value

Units

DC Power Supply

1

8.0

V

DC Gate Voltage

-5.0

V

RF Input Power

20

dBm

Storage Temperature

-55 to 150

∞

C

Operating Temperature (case)

-40 to 110

∞

C

Note 1: Into a 10:1 mismatch.

TQ9147B

Data Sheet

For additional information and latest specifications, see our website:

www.triquint.com

3

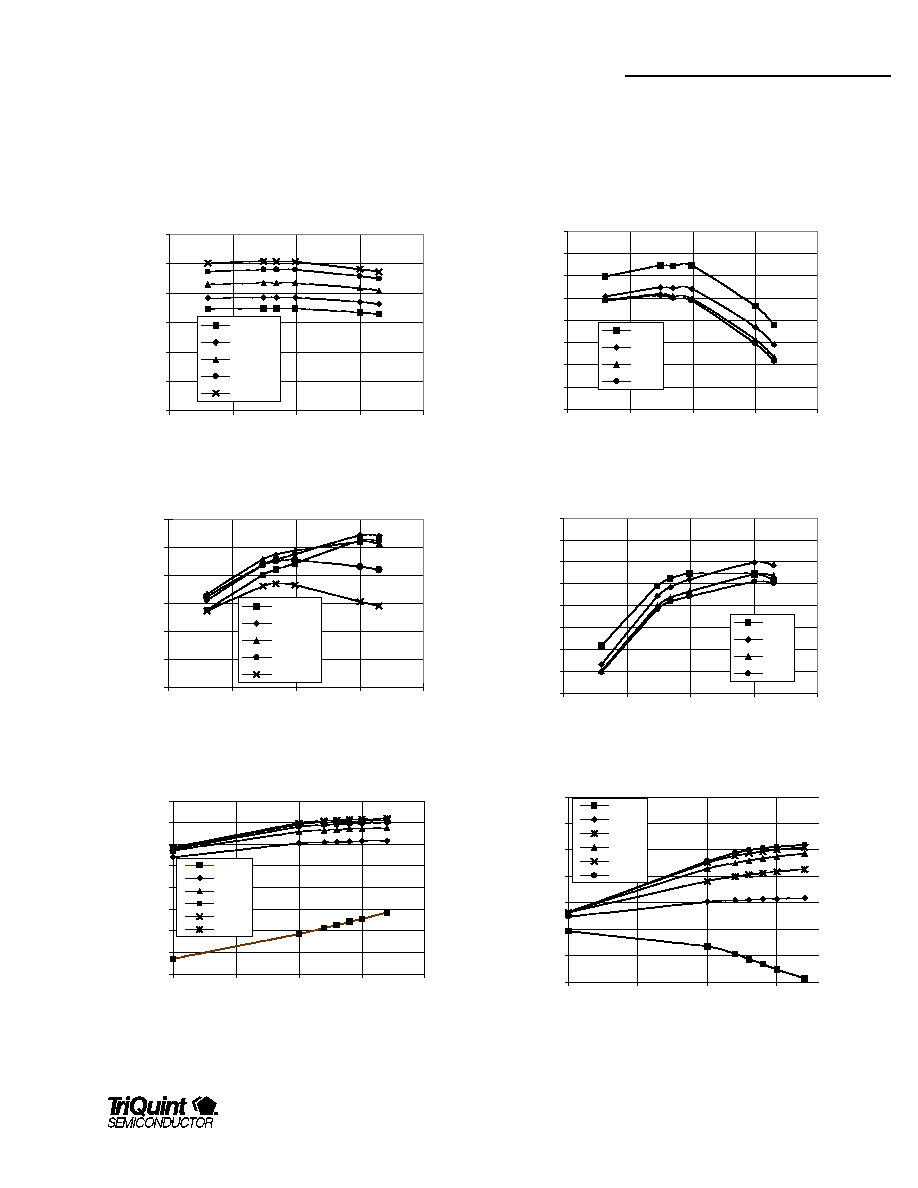

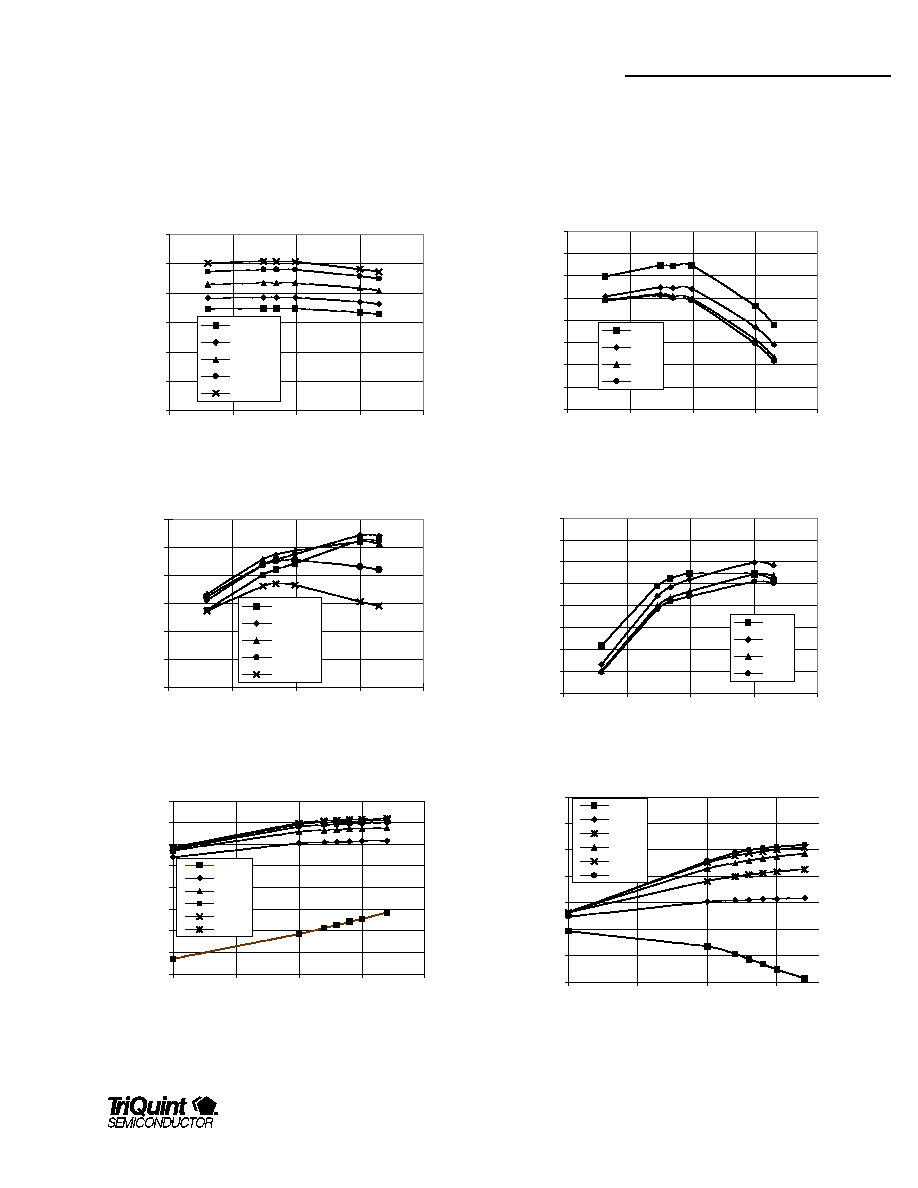

Typical Performance

Test Conditions (Unless Otherwise Specified): V

DD

= 4.8 V, P

IN

= +7 dBm, F

req. = 824 & 849 MHz,

T

C

= 25

∞

C, constant gate

voltages: V

G1

= -1.5 V, V

G2

= -2.2 V.

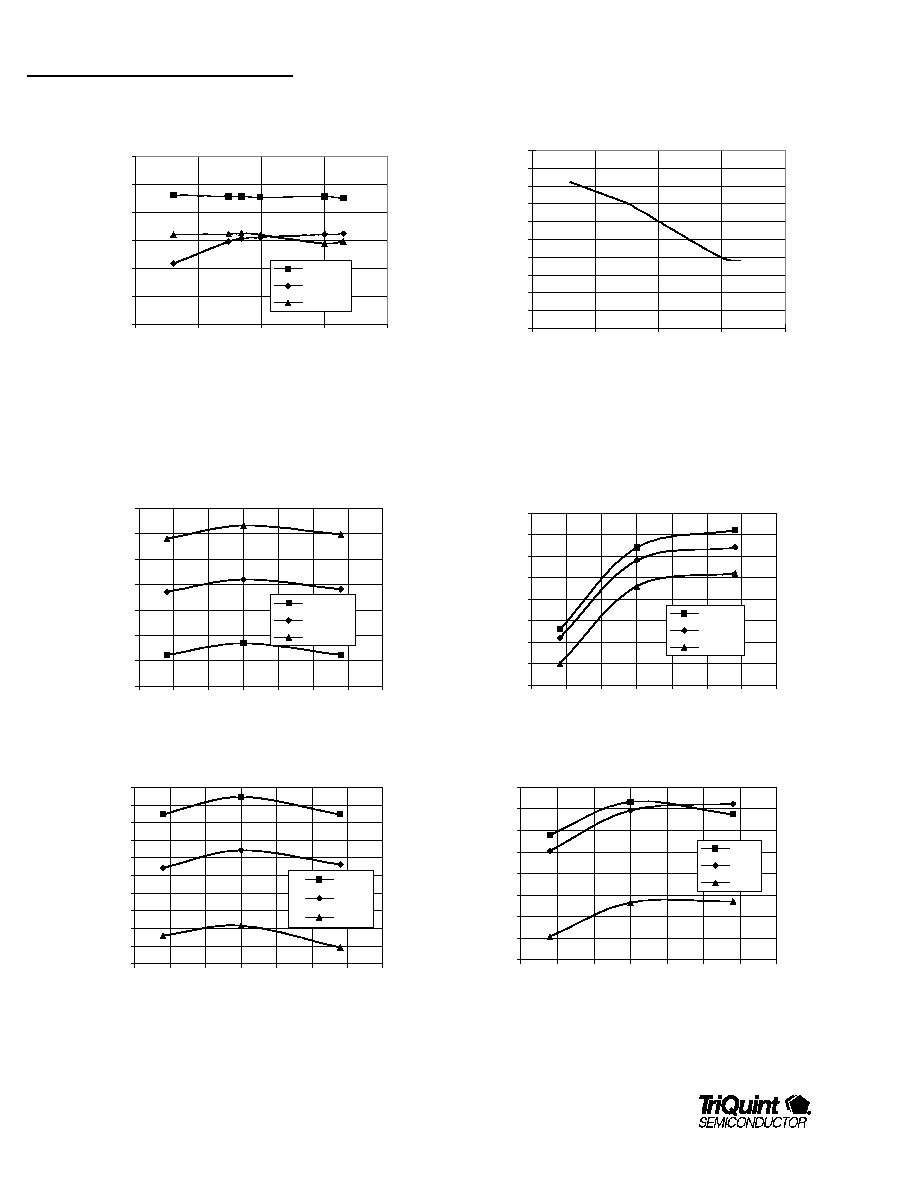

Output Power vs. Frequency and VDD

10

15

20

25

30

35

40

750

800

850

900

950

Frequency (MHz)

POUT (dBm)

VDD=3.0 V

VDD=3.6 V

VDD=4.6 V

VDD=5.8 V

VDD=7.0 V

Efficiency vs. Frequency and VDD

40

45

50

55

60

65

70

750

800

850

900

950

Frequency (MHz)

Efficiency (%)

VDD=3.0 V

VDD=3.6 V

VDD=4.6 V

VDD=5.8 V

VDD=7.0 V

Output Power vs. Input Power vs. VD1

-40

-30

-20

-10

0

10

20

30

40

-10

-5

0

5

10

P

IN

(dBm)

POUT (dBm)

Vd1=0V

Vd1=1V

Vd1=2V

Vd1=3V

Vd1=4V

Vd1=5V

Output Power vs. Frequency vs. Temp.

29.0

29.5

30.0

30.5

31.0

31.5

32.0

32.5

33.0

750

800

850

900

950

Frequency (MHz)

Pout (dBm)

-30 C

25 C

85 C

110 C

Efficiency vs. Frequency vs. Temp

54

56

58

60

62

64

66

68

70

750

800

850

900

950

Freq ( MHz )

Efficiency ( % )

-30 C

25 C

85 C

110 C

Efficiency vs. Input Power vs. Vd1

-40

-20

0

20

40

60

80

100

-10

-5

0

5

P

IN

(dBm)

Efficiency (%)

Vd1=0V

Vd1=1V

Vd1=2V

Vd1=3V

Vd1=4V

Vd1=5V

TQ9147B

Data Sheet

4

For additional information and latest specifications, see our website:

www.triquint.com

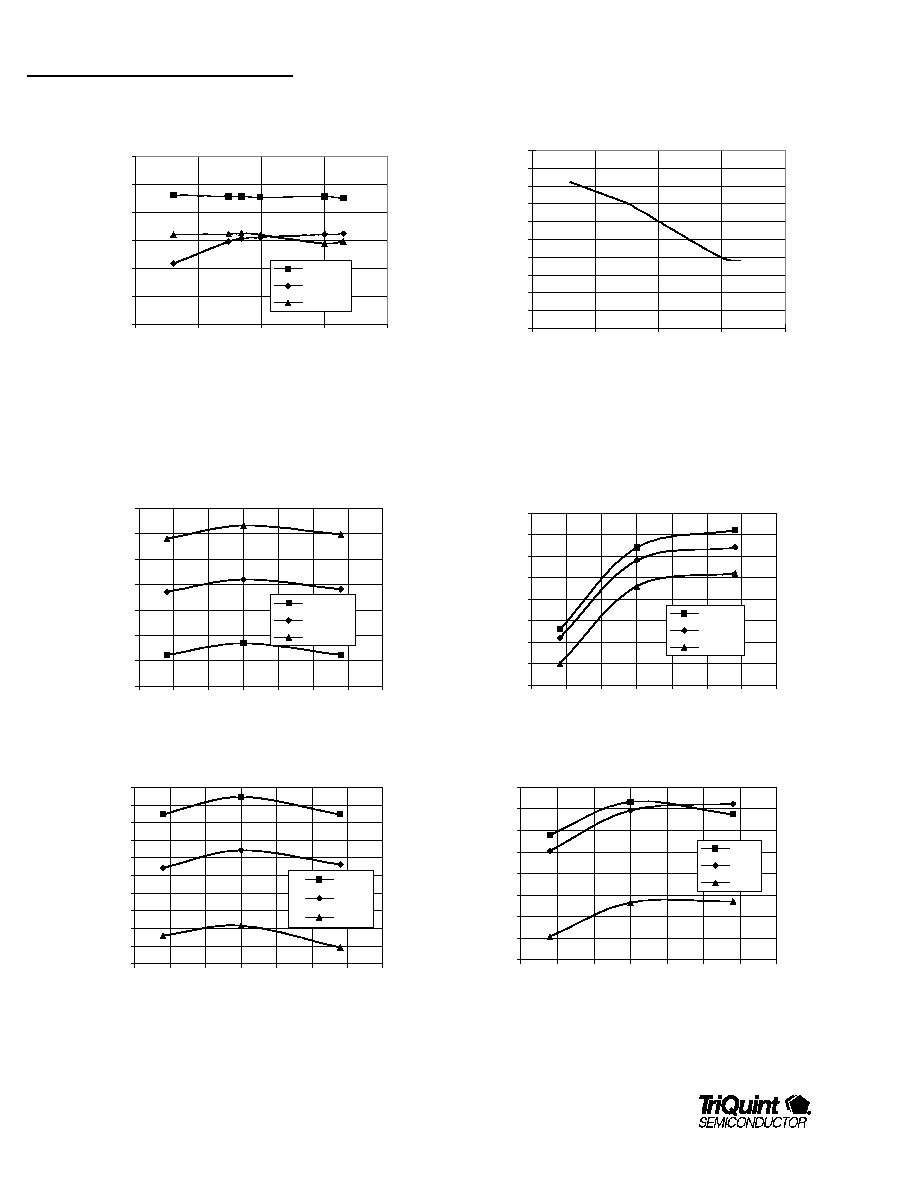

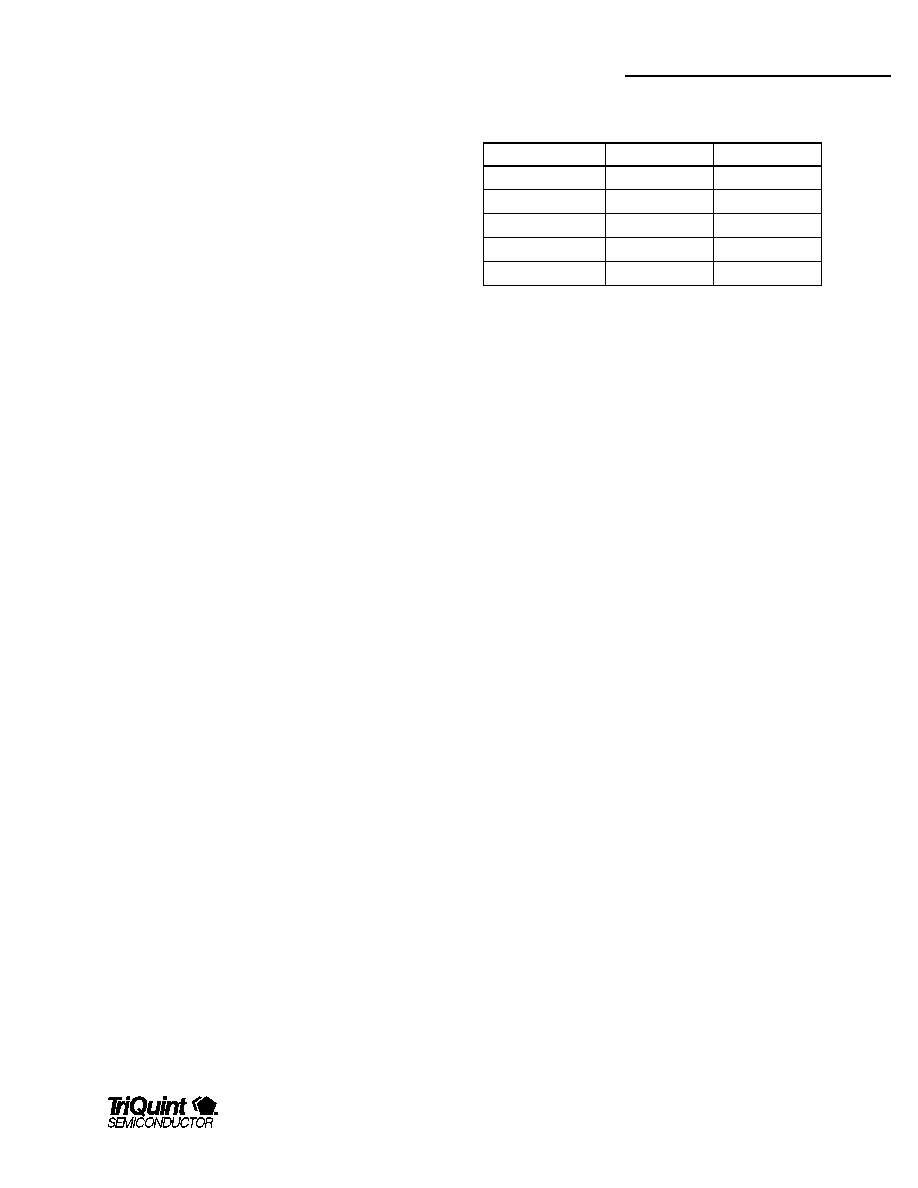

Harmonics vs. Frequency @ T = 25 C

-80

-70

-60

-50

-40

-30

-20

750

800

850

900

950

Frequency (MHz)

Level (dBc)

2nd Harm.

3rd Harm.

4th Harm.

S11 vs. Frequency

-25

-23

-21

-19

-17

-15

-13

-11

-9

-7

-5

750

800

850

900

950

Frequency (MHz)

S11 (dB)

Test Conditions (Unless Otherwise Specified): V

DD

= 5 V, P

IN

= +7 dBm, V

GG

= -3.5 V, F

req. = 824 & 849 MHz,

T

C

= 25

∞

C, Gate

voltage determined by the recommended bias circuit

Output Power vs. Frequency vs. VDD

31.8

32.0

32.2

32.4

32.6

32.8

33.0

33.2

820

825

830

835

840

845

850

855

Frequency (MHz)

P

OUT

(dBm)

VDD=4.75V

VDD=5V

VDD=5.25V

Output Power vs. Frequency vs. Temperature

32.0

32.1

32.2

32.3

32.4

32.5

32.6

32.7

32.8

32.9

33.0

820

825

830

835

840

845

850

855

Frequency (MHz)

Pout (dBm)

-30 C

25 C

110 C

Efficiency vs. Frequency vs. VDD

56.0

56.5

57.0

57.5

58.0

58.5

59.0

59.5

60.0

820

825

830

835

840

845

850

855

Frequency (MHz)

Efficiency (%)

Eff, 4.75V

Eff, 5V

Eff, 5.25V

Efficiency vs. Frequency vs. Temperature

52

53

54

55

56

57

58

59

60

820

825

830

835

840

845

850

855

Frequency (MHz)

Efficiency (%)

-30 C

25 C

110 C

.

TQ9147B

Data Sheet

For additional information and latest specifications, see our website:

www.triquint.com

5

Test Conditions (Unless Otherwise Specified): V

DD

= 5 V, P

IN

= +7 dBm, V

GG

= -3.5 V, F

req. = 824 & 849 MHz,

T

C

= 25

∞

C, Gate

voltage determined by the recommended bias circuit

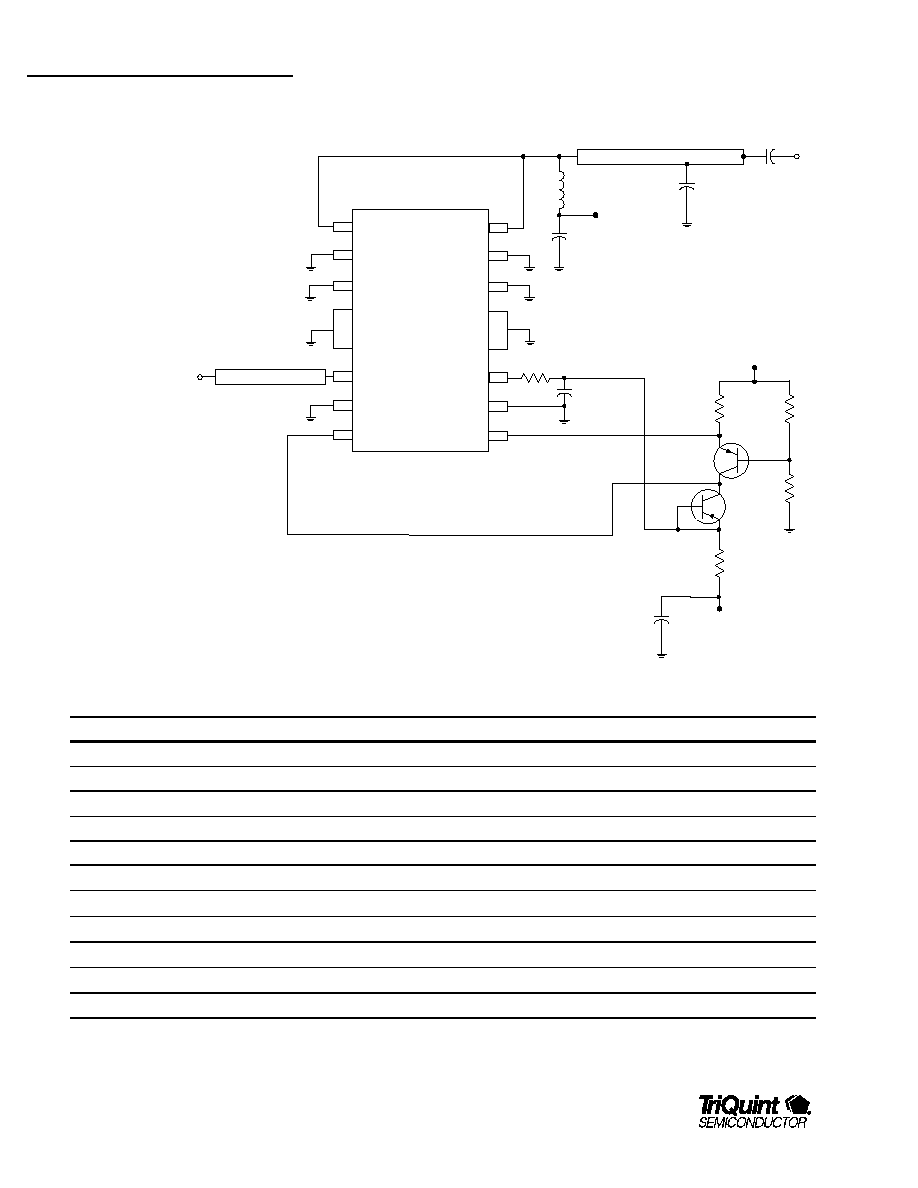

Output Power vs. Frequency vs. Input Power

30.0

30.5

31.0

31.5

32.0

32.5

33.0

820

825

830

835

840

845

850

855

Frequency (MHz)

P

OUT

(dBm)

P in=7dBm

P in=3dBm

P in=-2dBm

Efficiency vs. Frequency vs. Input Power

30

35

40

45

50

55

60

65

820

825

830

835

840

845

850

855

Frequency (MHz)

Efficiency (%)

Pin=7 dBm

Pin=3 dBm

Pin=-2 dBm

TQ9147B

Data Sheet

6

For additional information and latest specifications, see our website:

www.triquint.com

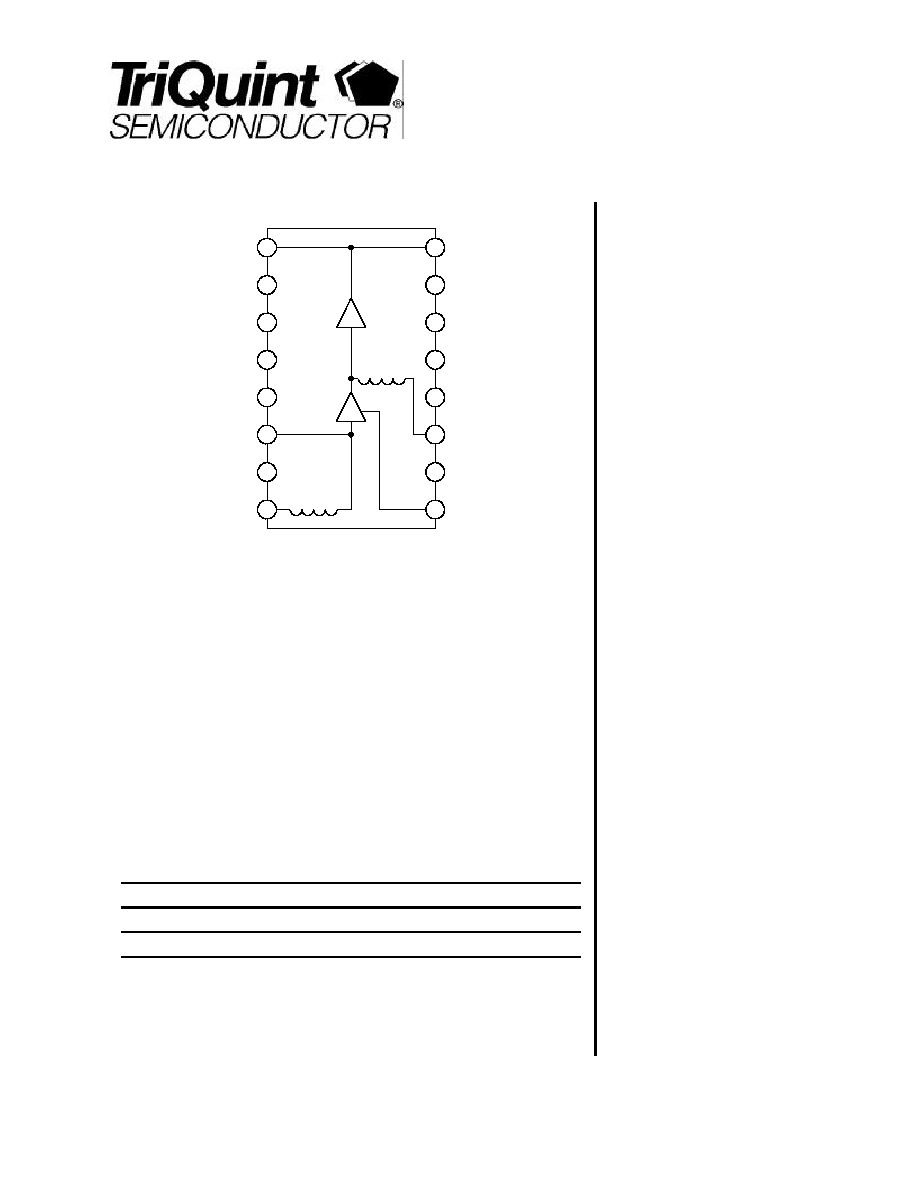

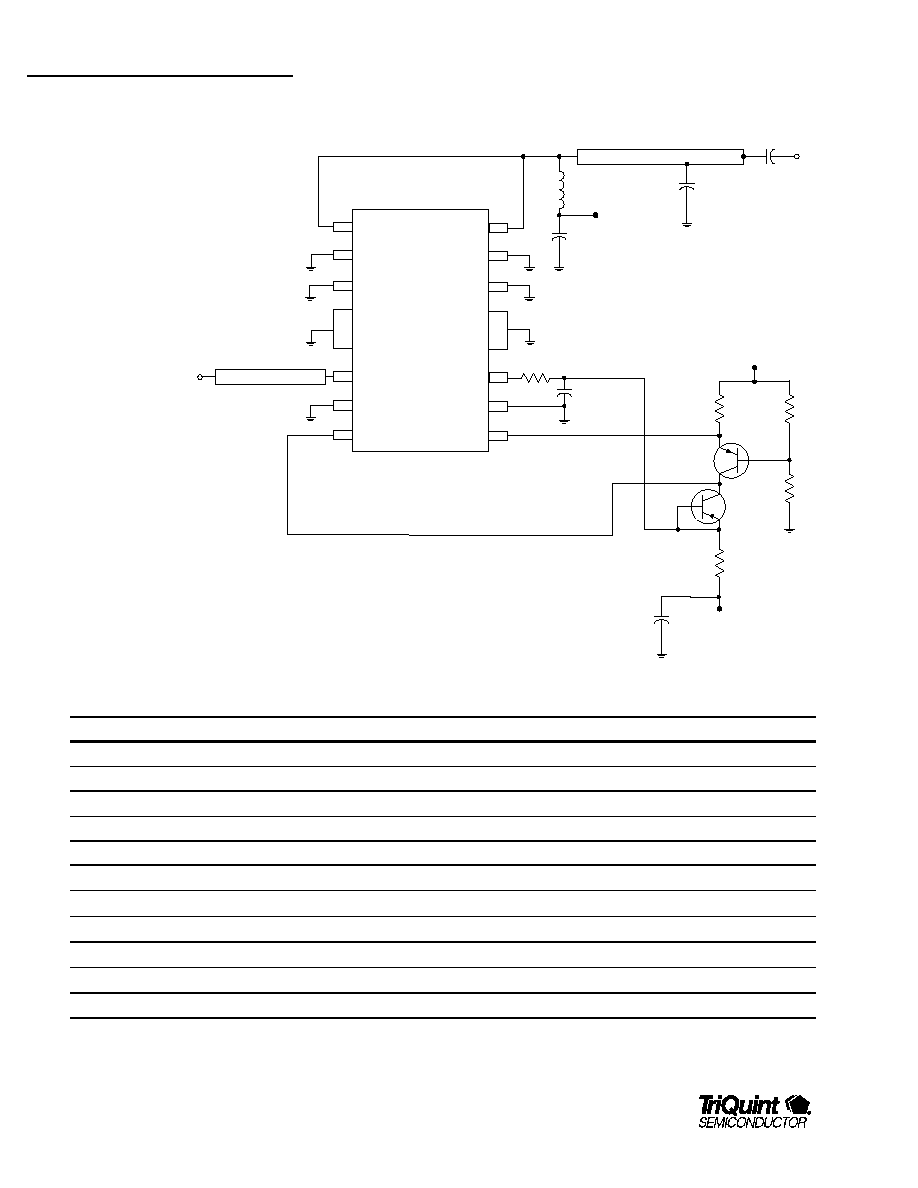

Application/Test Circuit

50

Transmission Line

C2

C3

L1

C1

V

D2

= 4.8 V

50

Transmission Line

R1

13

R4

R3

5

C4

V

D1

= 4.8 V

V

GG

= -3.5 V

R5

R2

Q1

Q2

C5

TQ9147B

RF

OUT

RF

OUT

GND

GND

GND

GND

RF

IN

GND

GND

GND

GND

V

G1

V

D1

V

G2

1

7

2

9

3

4

6

8

10

11

14

15

16

12

Bill of Material for TQ9147B Power Amplifier Application/Test Circuit

Component

Reference Designator

Part Number

Value

Size

Manufacturer

Power Amplifier IC

U1

TQ9147B

TSSOP-20

TriQuint Semiconductor

PNP Transistor

Q1, Q2

2N3906

Capacitor

C1, C4, C5

MCH182F104ZK

0.1

µ

F

0603

Rohm

Capacitor

C2,

MCH155A8R2CK

8.2 pF

0402

Rohm

Capacitor

C3

MCH155A680JK

68 pF

0402

Rohm

Resistor

R1

MCR01JW510

51

0402

Rohm

Resistor

R2

MCR01JW100

10

0402

Rohm

Resistor

R3

MCR01JW621

620

0402

Rohm

Resistor

R4

MCR01JW202

2 k

0402

Rohm

Resistor

R5

MCR01JW391

390

0402

Rohm

Inductor

L1

0805CS470

47 nH

Coilcraft

TQ9147B

Data Sheet

For additional information and latest specifications, see our website:

www.triquint.com

7

Product Description

The TQ9147 is a high efficiency two stage GaAs MESFET

power amplifier IC intended for use in AMPS (IS-19)

applications that operate in the US Cellular (824 - 849 MHz)

band. The TQ9147 requires minimal external RF circuitry and

operates from a 4.8-Volt supply. With its flexible, off-chip, single

component output matching circuit, the TQ9147 is suitable for

use in other applications near the cellular band, such as 900

MHz ISM applications.

The TQ9147 utilizes a space saving SO-16 plastic package that

minimizes board area and cost.

Operation

Please refer to the application circuit above.

Gate Biasing and Bypassing

The TQ9147 is a dual-supply power amplifier (PA). Because it

utilizes depletion-mode MESFETs, a negative bias voltage must

be supplied to the gate of each FET. There are several

excellent choices of negative voltage bias supplies (charge

pumps) on the market, such as the Maxim MAX881R, or the

Harris ILC7660S. A simple resistor divider circuit is the most

inexpensive way to bias the gates of each stage from the charge

pump. However, due to fabrication tolerances and the large

window of main supply voltages under which the device can

function, the active bias method shown in the application circuit

is recommended.

This bias technique accurately sets the bias point for each stage

and optimizes the quiescent current and efficiency over a wide

range of supply voltages and output power levels. The following

table lists the nominal values of gate voltage and quiescent

current when this bias method is used. It is important to

remember that the negative gate voltage must be supplied first

in order to protect the device from inadvertent high drain

currents. If the drains are turned on before the gate bias is set,

the IC can be damaged or destroyed.

Gate Bias Voltages and Drain Quiescent Current

Parameter

Value

Units

V

DD

4.8

V

V

G1

-1.5

V

V

G2

-2.2

V

I

DQ1

50

MA

I

DQ2

0-100

mA

The gate of each FET in the IC is RF bypassed on chip.

However, additional low frequency filtering and noise

suppression must be done externally. This is accomplished with

a 51 Ohm resistor (R1) and 0.1

µ

F cap (C4) from pin 11 (Vg2).

This capacitor and resistor combination also ensures device

stability under all conditions.

Drain Bypassing

C1 (0.1

µ

F) provides RF bypassing for the high impedance side

of the RF choke (L1).

Input Match

The device input is internally matched to 50 Ohms. A 50-Ohm

transmission line is all that is required between the PA and the

driver amp.

Output Match and High Power Bias Injection

Pins 1 and 16 are dual-purpose pins, providing for both the RF

output and the high power DC input for the drain of the second

stage FET. As such, these pins are connected to a 50-Ohm

transmission line. Locating C2 (8.2 pF) approximately 200 mils

from the device along this transmission line acts as a shorted

stub tuner that transforms the low output impedance (~ 7.5

Ohms) of the power stage to 50 Ohms. Varying the position of

C2 along the line can alter the output match in order to optimize

either power output or efficiency. In general, the farther away

C2 is from the pins the higher the efficiency at the expense of

power output. The closer the cap is, the higher the output

power at the expense of efficiency. By varying the value and

position of C2, the device can be easily tuned for a different

frequency range such as the 902 ≠ 928 MHz ISM band. C3 (68

pF) is a DC blocking cap.

TQ9147B

Data Sheet

8

For additional information and latest specifications, see our website:

www.triquint.com

Drain current for the second stage is injected through L1 (47

nH), which acts as an RF choke on the high power DC feed line.

As stated above, C1 is the bypass cap for the high impedance

side of L1.

Power down Function

To fully turn off the PA when not transmitting, a PMOS FET

(PFET) switch can be used to control the drain bias to the PA.

There are several acceptable models available on the market,

such as the IRF7604 from International Rectifier, or any device

with low R

DSon

. An added benefit of incorporating a switch of

this type is that it protects the PA from inadvertently powering up

the device incorrectly. Since depletion-mode FETs are used in

the PA, care must be taken to insure that the gate bias is fully

stabilized before drain bias is applied. If not, the full value of I

Dss

will flow, which could damage or destroy the IC. A feature

included in the Maxim charge pump allows for a separate

control output to run the PFET. This control line holds the PFET

off until the gate bias voltage has stabilized.

RF Power Control

There are three methods of controlling the output power from

the TQ9147. All three methods can provide a minimum 25 dB of

control range for the device, which exceeds the requirements of

IS-19.

The first method is to vary the gate bias voltages. Though this

approach has the advantage of increased efficiency at lower

output power levels, it is hampered by two problems. First, both

gate voltages must be varied. Since each stage typically

requires a different bias point, the control circuit must monitor

both bias points, thereby complicating the design.

The second drawback is that most charge pumps, including

those recommended above, require large capacitors on the

output for filtering and stability. Such large cap values may not

allow full compliance with the required 20 mS transition spec

between any two power levels.

The second method is to vary the input power level. Though

this can be done with a simple attenuator between the driver

amp and the PA, the response is very non-linear, as the PA

must first come out of saturation before the output power can

change. Once out of saturation, the first stage is class A biased,

which means that the drain current is constant regardless of

power settings. The addition of an attenuator also adds to the

expense of the parts list and to the board size equation, and

increases the insertion loss the driver amp must overcome.

The third, and preferred, method is to vary the drain supply

voltage to the first stage. By forcing the first stage bias lower,

the first stage is always heavily saturated, thus saving battery

power. Since the second stage is biased class AB, drain current

to that stage lowers as the drive level decreases. This method

optimizes battery savings over the other approaches. The

simplest implementation of this technique would be to

incorporate a second PFET to control the first stage drain. This

circuit can be realized buy utilizing a dual PFET such as the

International Rectifier IRF7314, which has two low R

DSon

FETs in

a single SO-8 package. By cascoding the two FETs, one

implements a master on/off function while the second controls

only the first stage drain bias. This technique also fits very well

with the active gate biasing circuit that was recommended

previously.

TQ9147B

Data Sheet

Revision A

A

J

une 30

November

, 1998

TQS Wireless Communications

∑

2300 NE Brookwood Parkway

∑

Hillsboro, OR 97124

∑

(503) 615-9000

∑

FAX:(503) 615-

8900

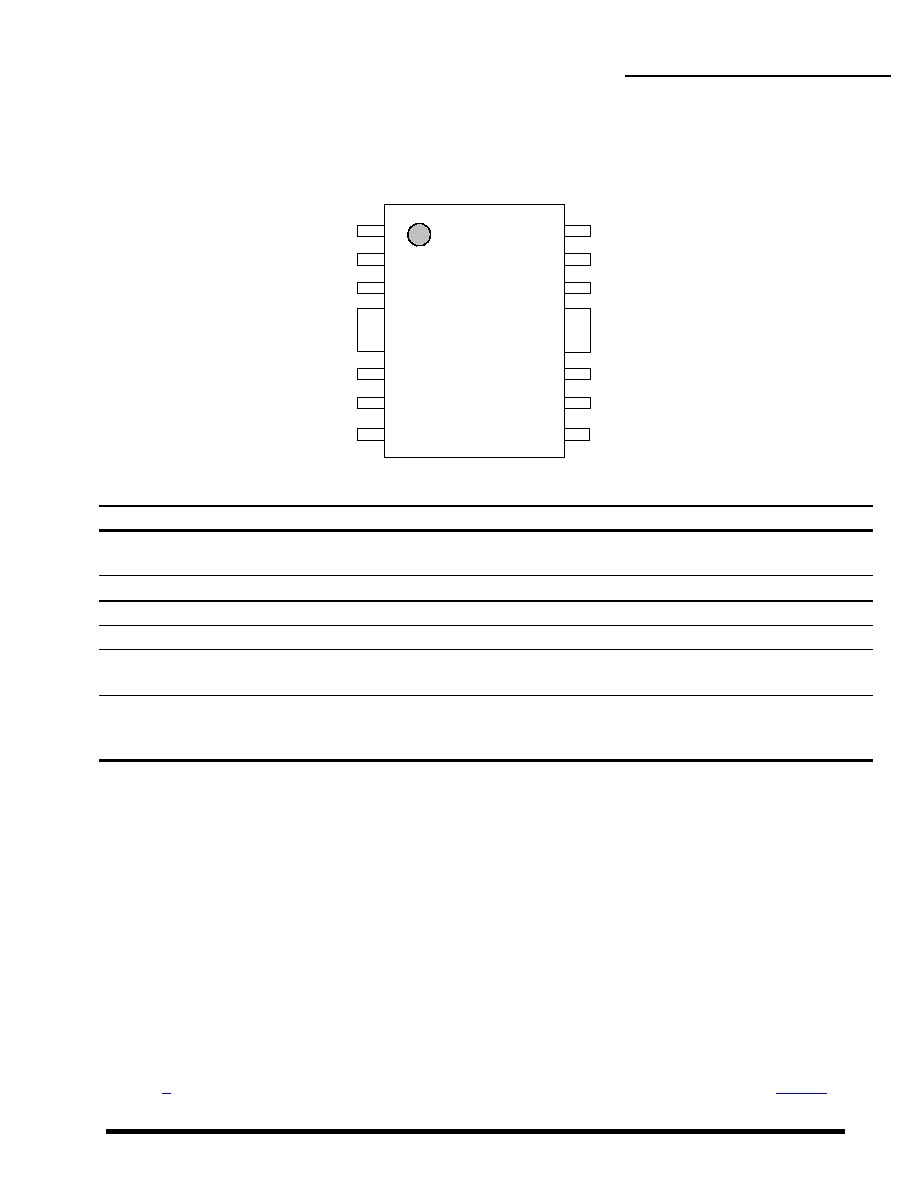

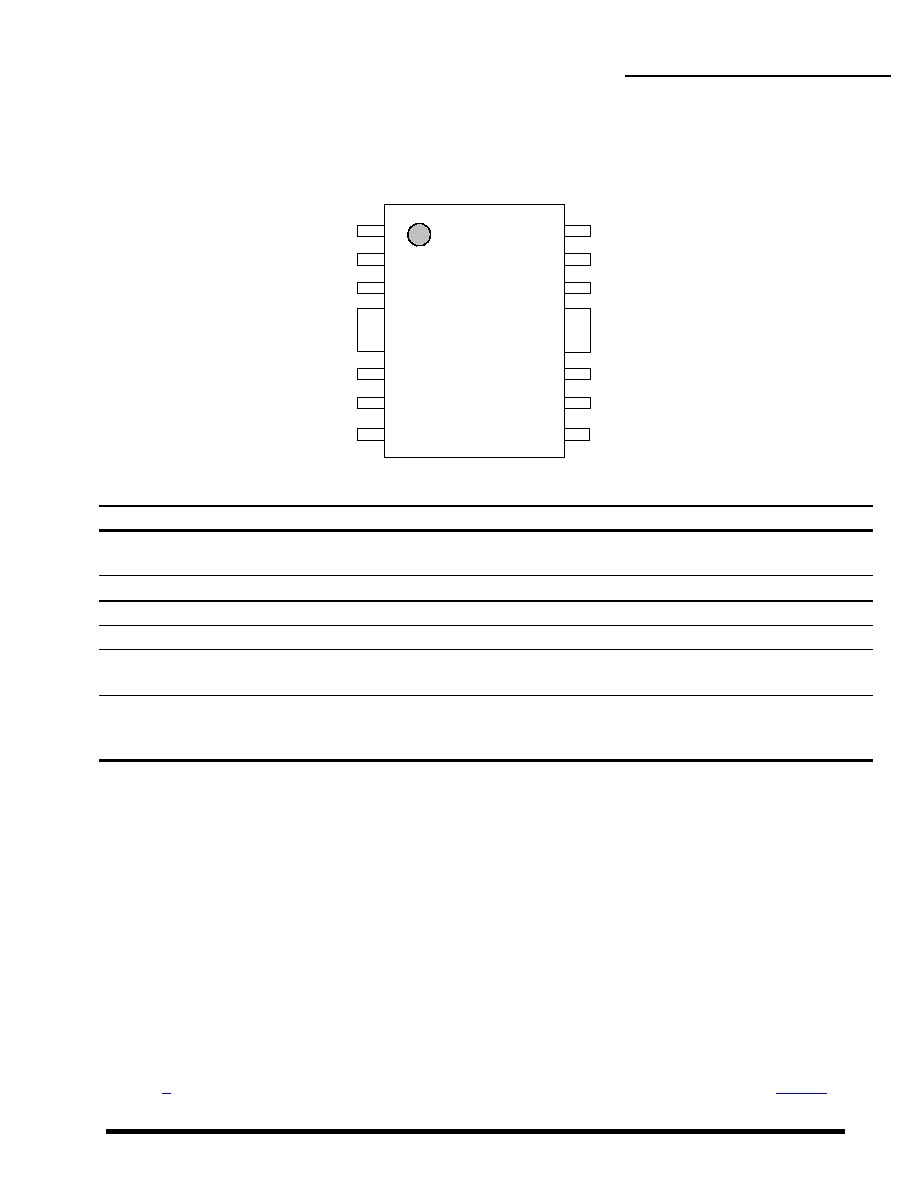

Package Pinout

7

6

8

5

4

3

2

1

9

10

11

14

15

16

V

G1

GND

RF

OUT

RF

OUT

V

G2

V

D1

GND

RF

IN

GND

GND

GND

V

D2

GND

V

G3

TQ9147B

13

12

Pin Descriptions

Pin Name

Pin #

Description and Usage

RF

OUT

1,16

Power Amplifier output and second-stage supply voltage. Critical, but simple, matching circuit required. Bias choke for V

D2

required, local bypass cap recommend, and DC blocking capacitor required.

RF

IN

6

RF input to power amplifier. Matched to 50

. Internal DC block.

V

G1

8

First stage gate voltage. Local bypass cap needed. Set V

G1

= -1.5 V or use bias stabilization circuit.

V

D1

9

First stage supply voltage. Local bypass cap recommended. Use same voltage as V

D2

or use bias stabilization circuit.

V

G2

11

Second stage gate voltage. Local bypass cap needed. Required 50

series resistor near device for stability. Set

V

G2

= -2.2 V or use bias stabilization circuit.

GND

2, 3, 4, 5, 7,

10, 12, 13,

14, 15

Ground connections. Provide thermal path for heat dissipation and RF grounding. Very important to place multiple via holes

immediately adjacent to the pins.

TQ9147B

Data Sheet

Additional Information

For latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: www.triquint.com

Tel: (503) 615-9000

Email: info_wireless@tqs.com

Fax: (503) 615-8900

For technical questions and additional information on specific applications:

Email: info_wireless@tqs.com

The information provided herein is believed to be reliable; TriQuint assumes no liability for inaccuracies or omissions. TriQuint assumes no responsibility for the use of

this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or

licenses to any of the circuits described herein are implied or granted to any third party.

TriQuint does not authorize or warrant any TriQuint product for use in life-support devices and/or systems.

Copyright © 1998 TriQuint Semiconductor, Inc. All rights reserved.

Revision B, March 18, 1999

10

For additional information and latest specifications, see our website:

www.triquint.com

Package Type: SOIC-16 Plastic Package with Thermal Tabs