| ÐлекÑÑоннÑй компоненÑ: CHV2243 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

CHV2243

Ref. : DSCHV22431074 -15-Mar.-01

1/6

Specifications subject to change without notice

united monolithic semiconductors S.A.S.

Route Départementale 128 - B.P.46 - 91401 Orsay Cedex France

Tel. : +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09

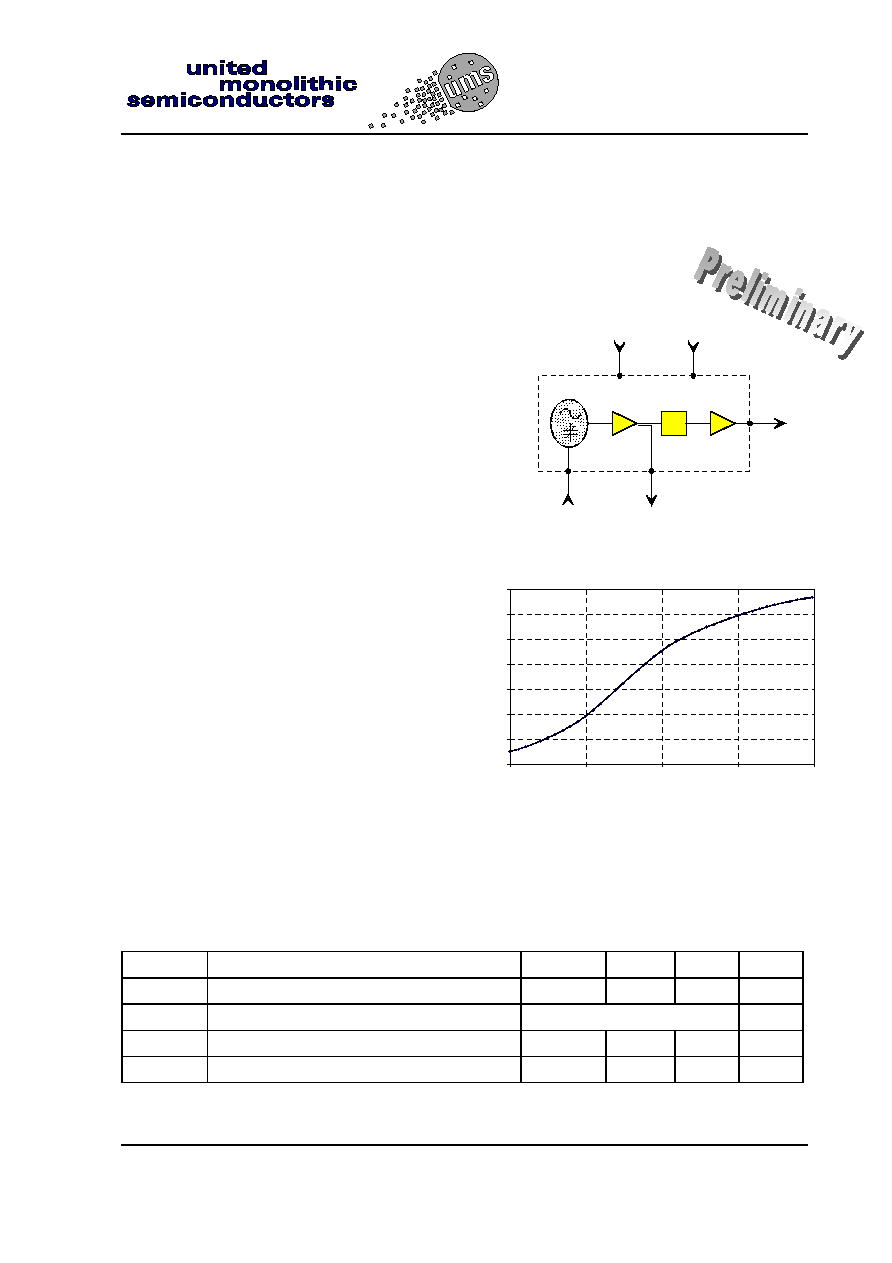

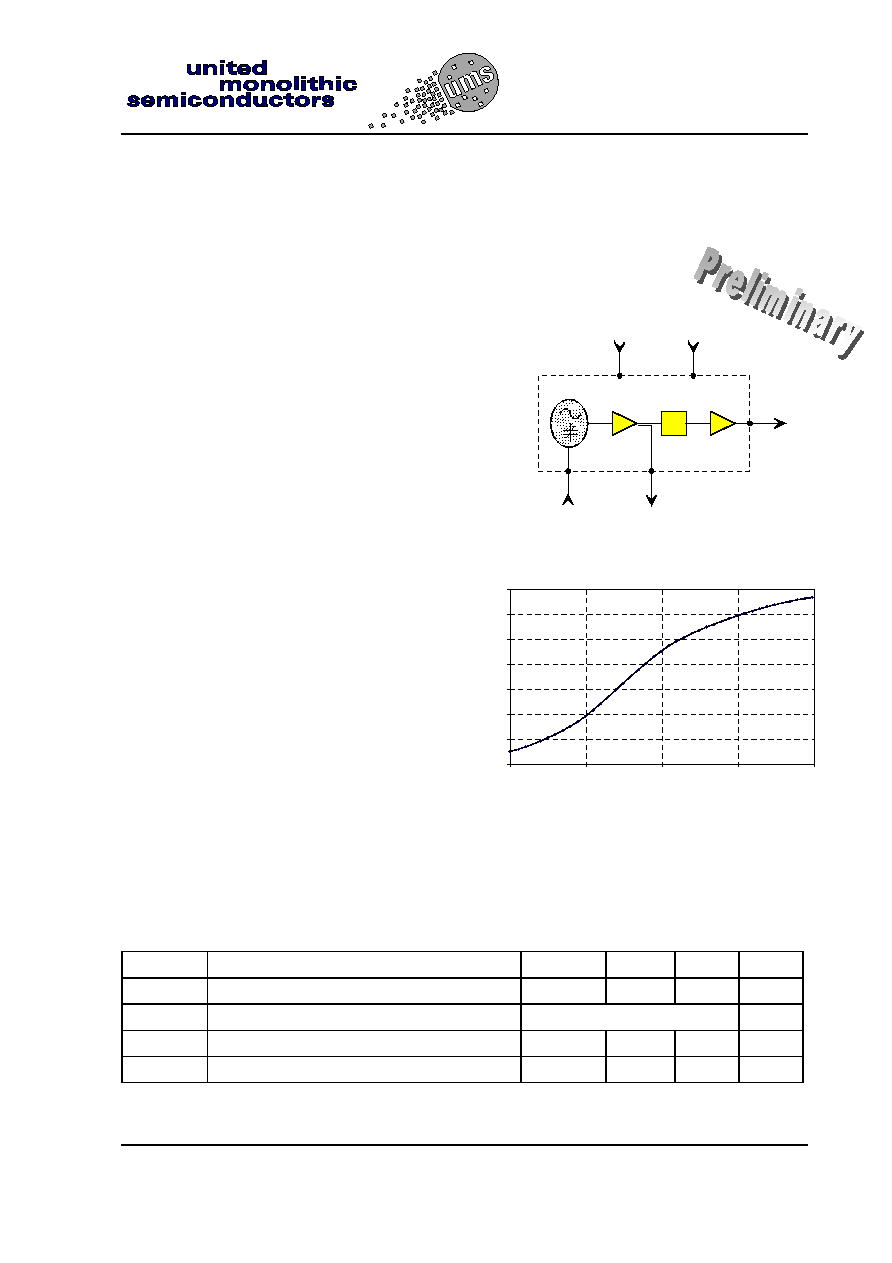

Fully Integrated Q-band VCO

based on Ku-band Oscillator and Q-band Multiplier

GaAs Monolithic Microwave IC

Description

The CHV2243 is a monolithic multifunction

for frequency generation. It integrates a

Ku-band oscillator with frequency control

(VCO), a Q-band frequency multiplier and

buffer amplifiers. The VCO is fully

integrated. On chip P-HEMT based

Schottky diode is used as varactor. All the

active devices are internally self biased.

The circuit is manufactured with the P-

HEMT process : 0.25µm gate length, via

holes through the substrate, air bridges

and electron beam gate lithography.

It is available in chip form.

Main Features

n

Ku-band VCO + Q-band multiplier

n

Fully integrated VCO

n

Wide frequency tuning range

n

PLL

oriented

n

Auxiliary output at VCO frequency

n

High temperature range

n

On-chip self biasing

n

Automatic assembly oriented

n

Chip size 2.41 x 1.18 x 0.1 mm

(F_out)

F_VCO = F_out/3

x3

RF_out

V_tune

+V

-V

VCO_out_aux

Multifunction block diagram

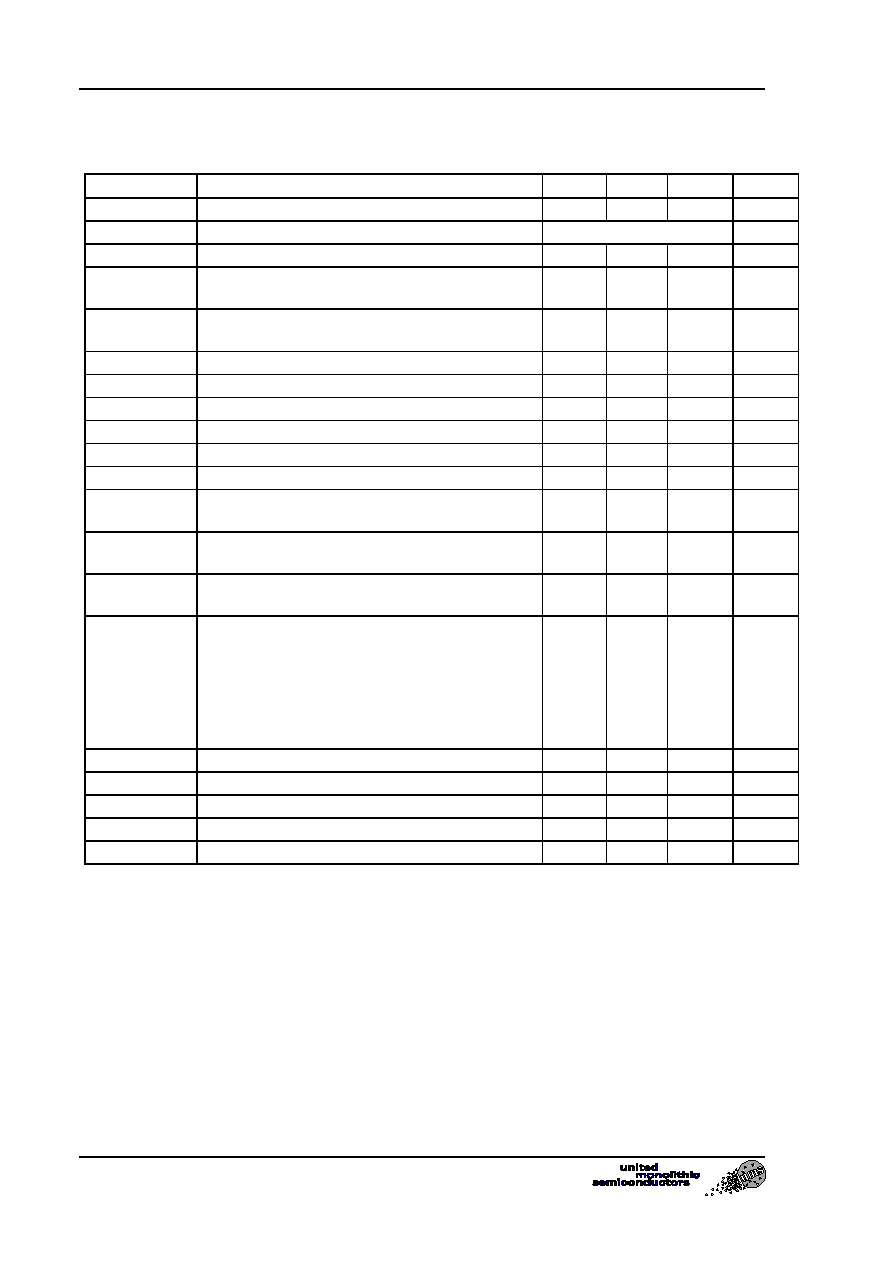

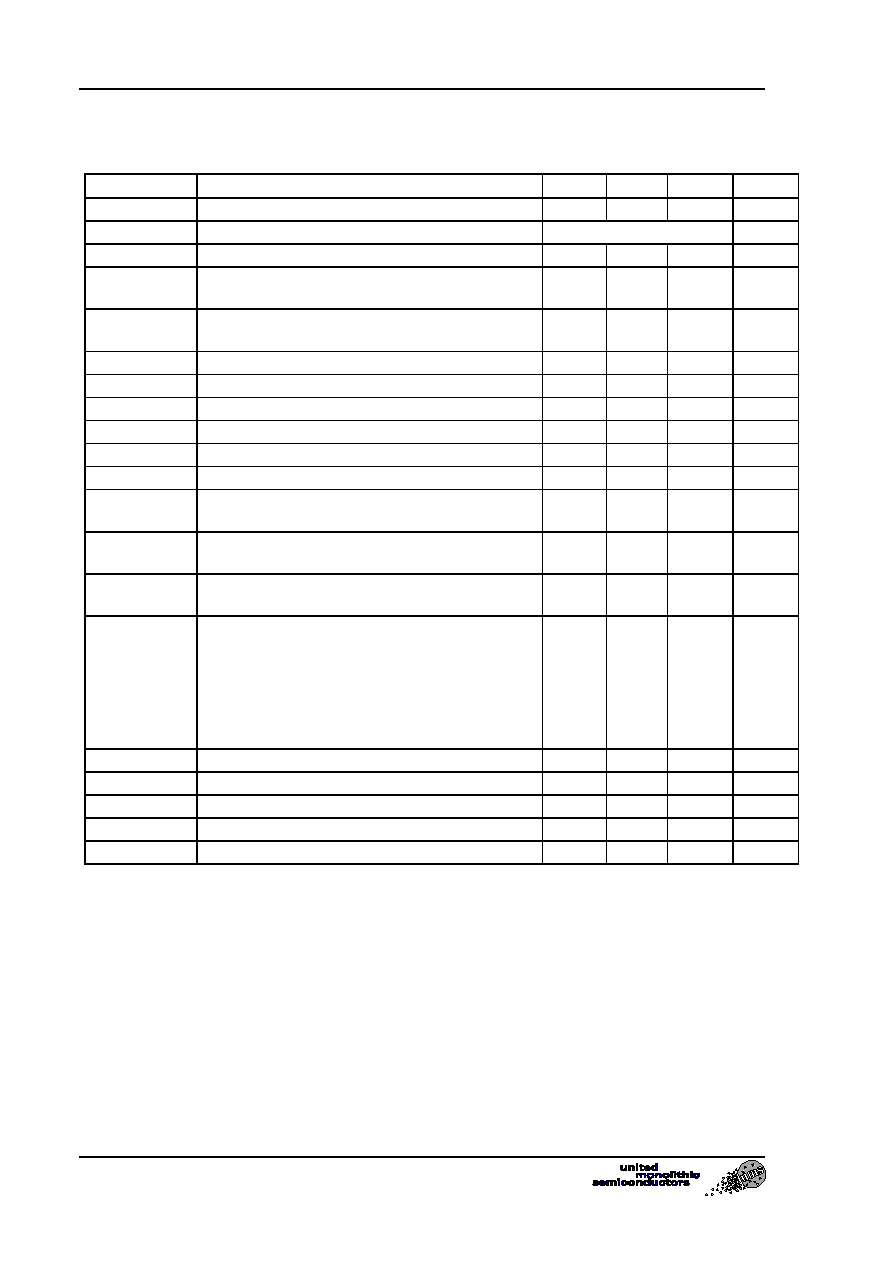

36,5

37

37,5

38

38,5

39

39,5

40

0

0,5

1

1,5

2

Tuning voltage (V)

Out

put

f

r

e

que

nc

y

(

G

H

z

)

Typical tuning characteristic

Main Characteristics

Tamb = +25°C

Symbol

Parameter

Min

Typ

Max

Unit

F_out

Output centre frequency

38

38.25

38.5

GHz

F_vco

Oscillator frequency

F_out/3

F_tune1

Output frequency tuning range

1.5

3

GHz

Pout

Output power

5

7

dBm

ESD Protections : Electrostatic discharge sensitive device observe handling precautions !

CHV2243

Q-band VCO

Ref. : DSCHV22431074 -15-Mar.-01

2/6

Specifications subject to change without notice

Route Départementale 128 , B.P.46 - 91401 ORSAY Cedex - FRANCE

Tel.: +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09

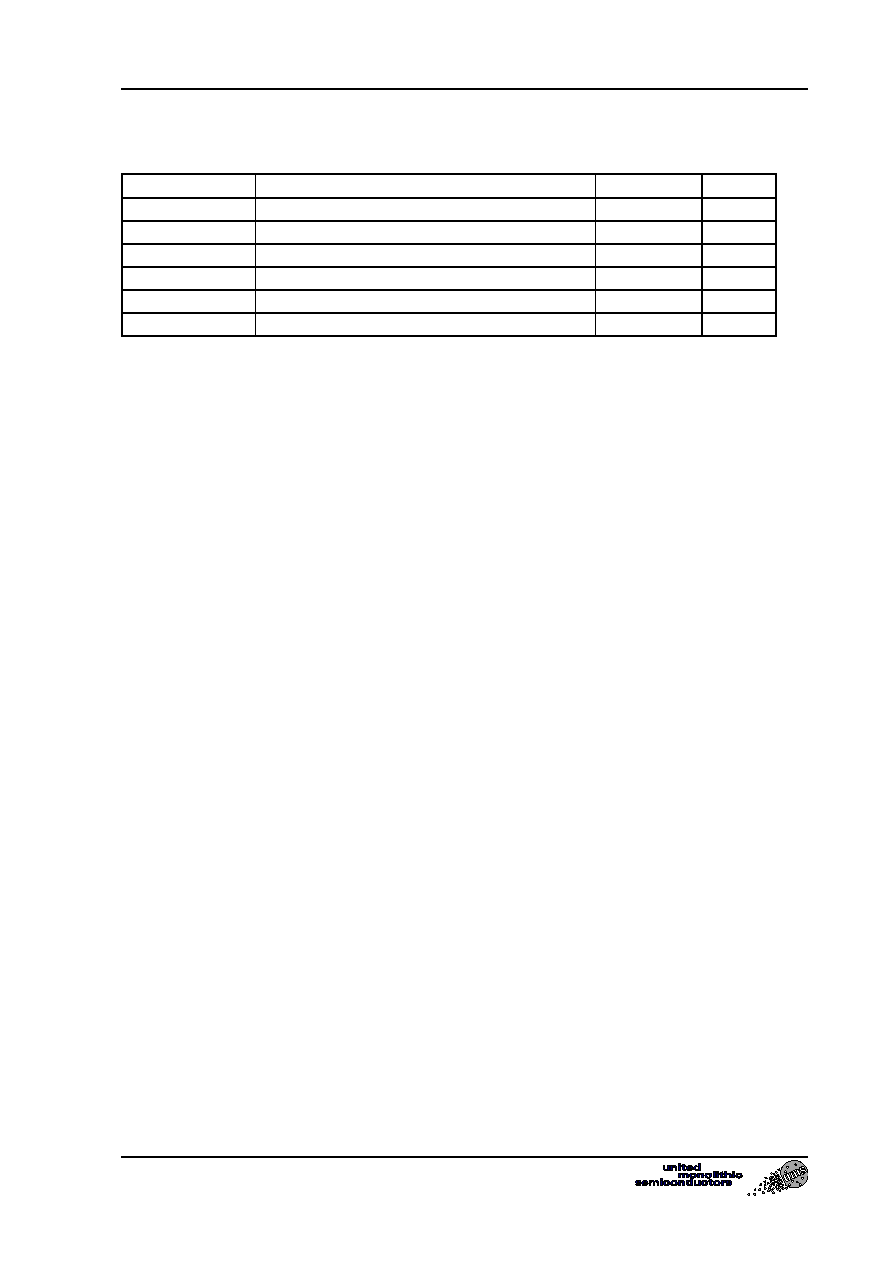

Electrical Characteristics

Full temperature range, used according to section "Typical assembly and bias configuration"

Symbol

Parameter

Min

Typ

Max

Unit

F_out

Output centre frequency

38

38.25

38.5

GHz

F_vco

VCO frequency

F_out/3

F_tune1

Maximum frequency tuning range (@ F_out)

1.5

3

4

GHz

F_tune2

Specified frequency tuning range (@ F_out)

(1)

200

300

500

MHz

F_tune2(T)

Maximum variation of Frequency over

temperature (2)

-300

+300

MHz

P_out

Output power on RF_out port

5

7

12

dBm

H1

Sub-harmonics rejection (Fout/3) (2)

-16

-11

dBc

H2

Sub-harmonics rejection (2*Fout/3) (2)

-17

-12

dBc

P_VCO

VCO output power on VCO_out_aux port (4)

tbd

V_tune

Control voltage range

0.5-1

0 - 2

V

F_slope

Frequency tuning slope (2)

1000

2800

4500

MHz/v

F_slope(T)

Maximum variation of Frequency tuning

slope over temperature (2)

-26

+34

%

P_V+

Frequency pushing vs positive supply

voltage (2)

150

450

MHz/v

P_V-

Frequency pushing vs negative supply

voltage (2)

80

250

MHz/v

PN

Phase noise (given at F_out) (2)

@ 1kHz

@ 10kHz

@ 100kHz

@ 200kHz

@ 1MHz

-5

-35

-65

-73

-92

+5

-25

-55

-63

-82

dBc/Hz

+V

Positive supply voltage (3)

4.4

4.5

4.6

V

+I

Positive supply current

130

180

mA

-V

Negative supply voltage (3)

-4.6

-4.5

-4.4

V

-I

Negative supply current

4

8

mA

Top

Operating temperature range

-40

+100

°C

(1) F_tune2 is the frequency tuning range relative to the specified parameters, this

frequency tuning range has to be inside 38 to 38.5GHz.

(2) Specified within F_tune2

(3) Negative supply voltage must be applied at least 1µs before positive supply

voltage

(4) This output is optional, it can be not connected

Q-band VCO

CHV2243

Ref. : DSCHV22431074 -15-Mar.-01

3/6

Specifications subject to change without notice

Route Départementale 128 , B.P.46 - 91401 ORSAY Cedex - FRANCE

Tel.: +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09

Absolute Maximum Ratings (1)

Symbol

Parameter

Values

Unit

V_tune

Tuning voltage

2.5

V

+V

Positive supply voltage

5

V

-V

Negative supply voltage

-5

V

+I

Positive supply current

250

mA

-I

Negative supply current

15

mA

Tstg

Storage temperature range

-55 to +155

°C

(1)

Operation of this device above anyone of these parameters may cause permanent damage.

CHV2243

Q-band VCO

Ref. : DSCHV22431074 -15-Mar.-01

4/6

Specifications subject to change without notice

Route Départementale 128 , B.P.46 - 91401 ORSAY Cedex - FRANCE

Tel.: +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09

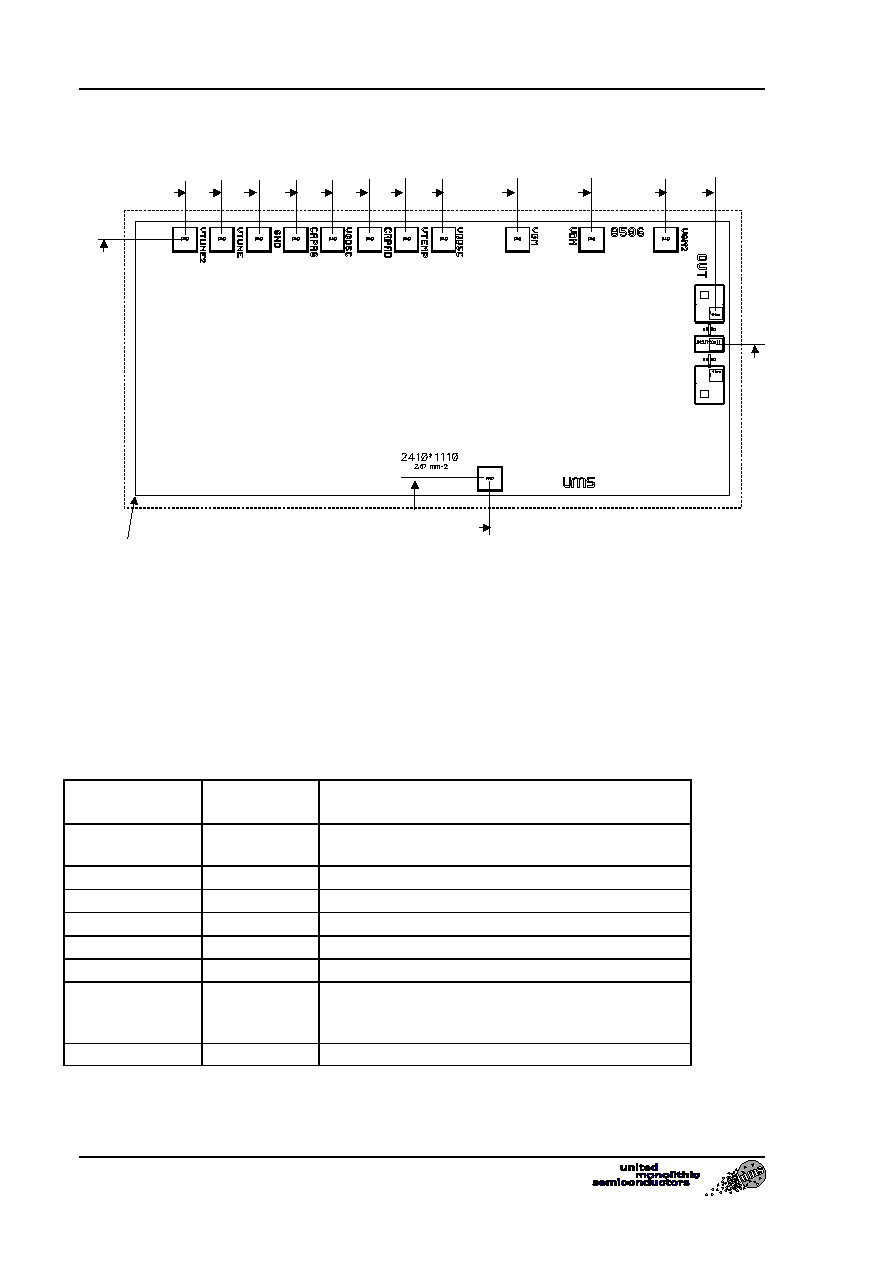

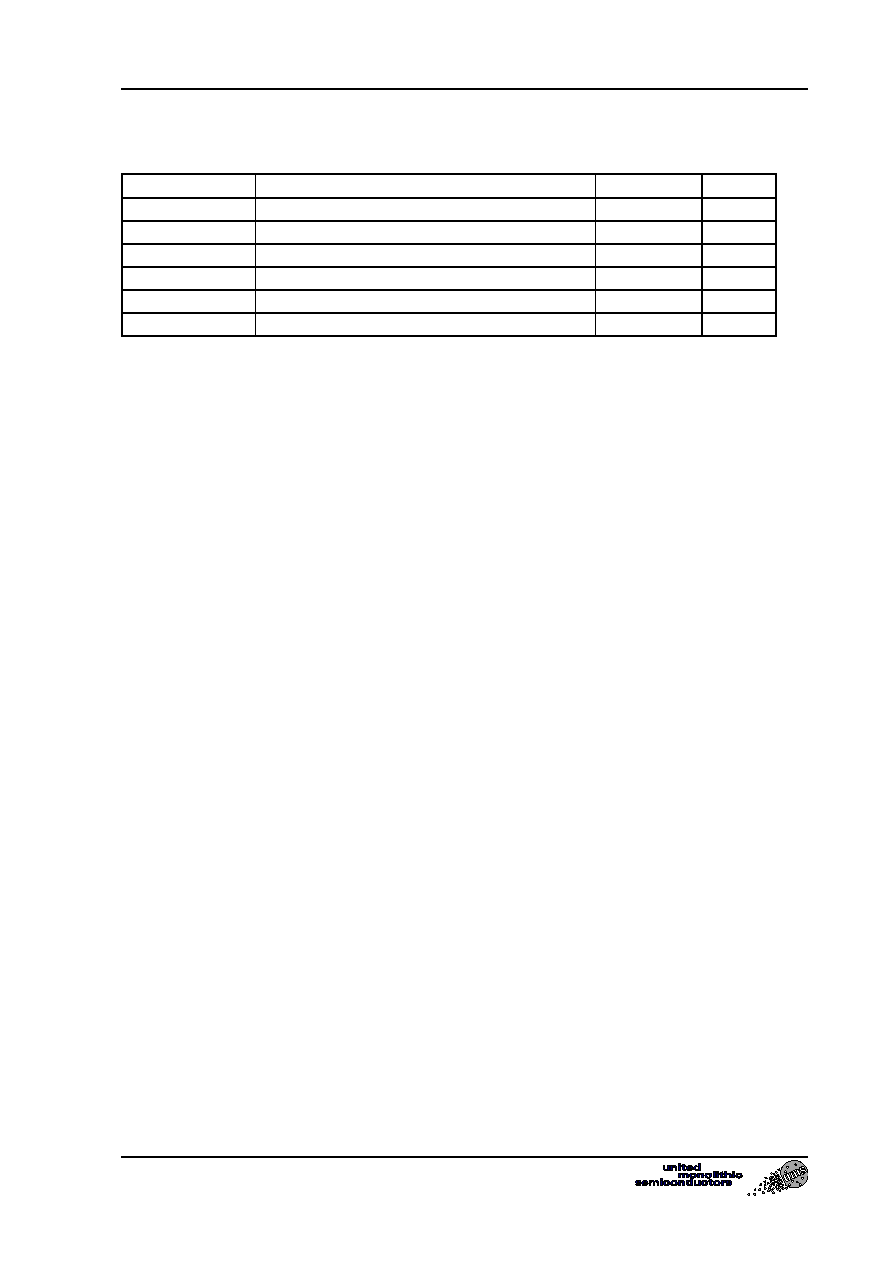

Chip Mechanical Data and Pin References

Origin 0,0

Layout 2410X1110

1

2

3

4

5

6

7

8

9

10

11

15

12

13

14

200

10

40

70

1440

350

500

650

800

950

1100

1250

1550

1850

2150

2355

61

5

Unit = µm

External chip size (including saw streets) = 2480 x 1180 +/- 35

Chip thickness = 100 +/- 10

HF Pads (13) = 68 x 118

VCO_out_aux Pad = 100 x 100

DC/IF Pads = 100 x 100

Pin number

Pin name

Description

12, 14

Ground: should not be bonded. If required,

please ask for more information.

3

Ground (optional)

13

RF_out

RF output port @38GHz

8, 10

+V

Positive supply voltage

5, 9

-V

Negative supply voltage

4, 6, 7, 11

NC

1, 2

V-tune

Tuning voltage input ports (should be connected

together, see typical assembly and bias

configuration)

15

VCO_out_aux Auxiliary VCO output at 12.7GHz (F_out / 3) (optional)

Q-band VCO

CHV2243

Ref. : DSCHV22431074 -15-Mar.-01

5/6

Specifications subject to change without notice

Route Départementale 128 , B.P.46 - 91401 ORSAY Cedex - FRANCE

Tel.: +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09

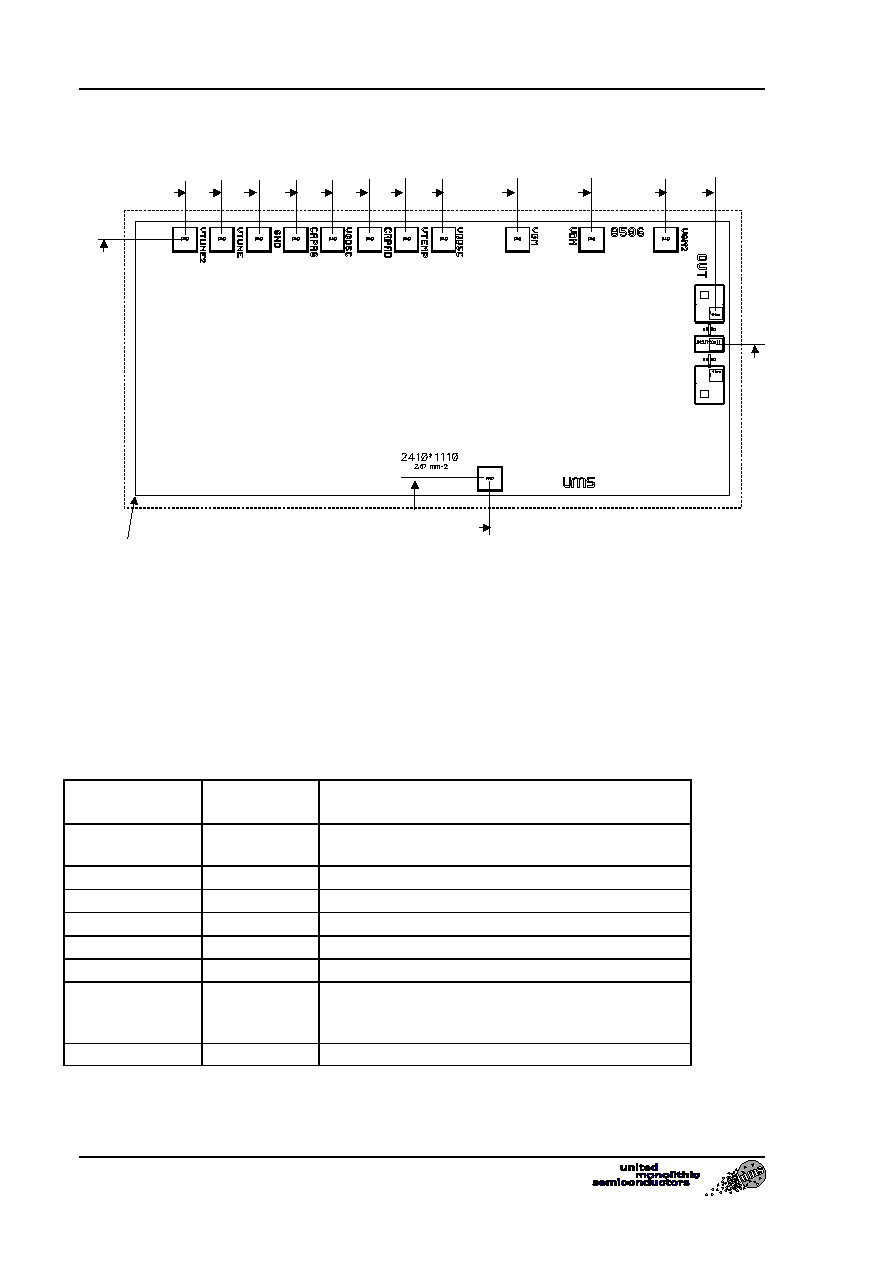

Typical Assembly and Bias Configuration

1

2

3

4

5

6

7

8

9

10

11

15

12

13

14

L_aux

µ-strip line

L_out

µ-strip line

-V

+V

V-tune

DC and control lines

>= 120pF

This drawing shows an example of assembly and bias configuration. All the

transistors are internally self biased. The positive and negative voltages can be

respectively connected together (see drawing) according to the recommended

values given in the electrical characteristics table.

For the RF pads the equivalent wire bonding inductance (diameter=25µm) has to

be according to the following recommendation.

Port

Equivalent inductance

(nH)

Approximated wire

length (mm)

RF_out (13)

L_out = 0.28

0.35

VCO_out_aux (15)

L_aux = 0.4

0.5

For a micro-strip configuration a hole in the substrate is recommended for chip

assembly.

Document Outline