| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: UTC4066 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

1

QW-R502-009,A

QUAD BILATERAL SWITCH

DESCRIPTION

The 4066 is a quad bilateral swith intended for the

Transmission or multiplexing of analog or digtal signals.It is

pin≠for-pin compatible with the 4066,but has a much

olwer "ON" resistance,and "ON" resistance is relatively

constant over the input-signal range.

FEATURES

*Wide supply voltage range : 3V ~ 15V.

*High noise immunity : 0.45V

DD

(typ.)

*Wide range of digital and ± 7.5V

PEAK

analog switching

*"ON" resistance for 15V operation : 80

*Matched "ON" resistance : R

ON

=5(typ.)

over 15V signal input

*"ON" resistance flat over peak-to-peak signal range

*High "ON" / "OFF" : 65 dB(typ.)

output voltage ratio @fis=10kHz,R

L

=10k

*High degree linearity : 0.1% distortion(typ.).

@f

is

=1kHz,V

is

=5Vp-p.

*

V

DD

-V

SS

=10V,R

L

=10k

*Extremely low "OFF" : 0.1nA(typ.)

*

switch leakage @V

DD

-V

SS

=10V,T

A

=25

*Extremely high control input impedance : 10

12

(typ.)

*Low crosstalk : ≠50dB(typ.)

*

between switches @f

is

=0.9MHz,R

L

=1k

*Frequency response,switch "ON" : 40MHz(typ.)

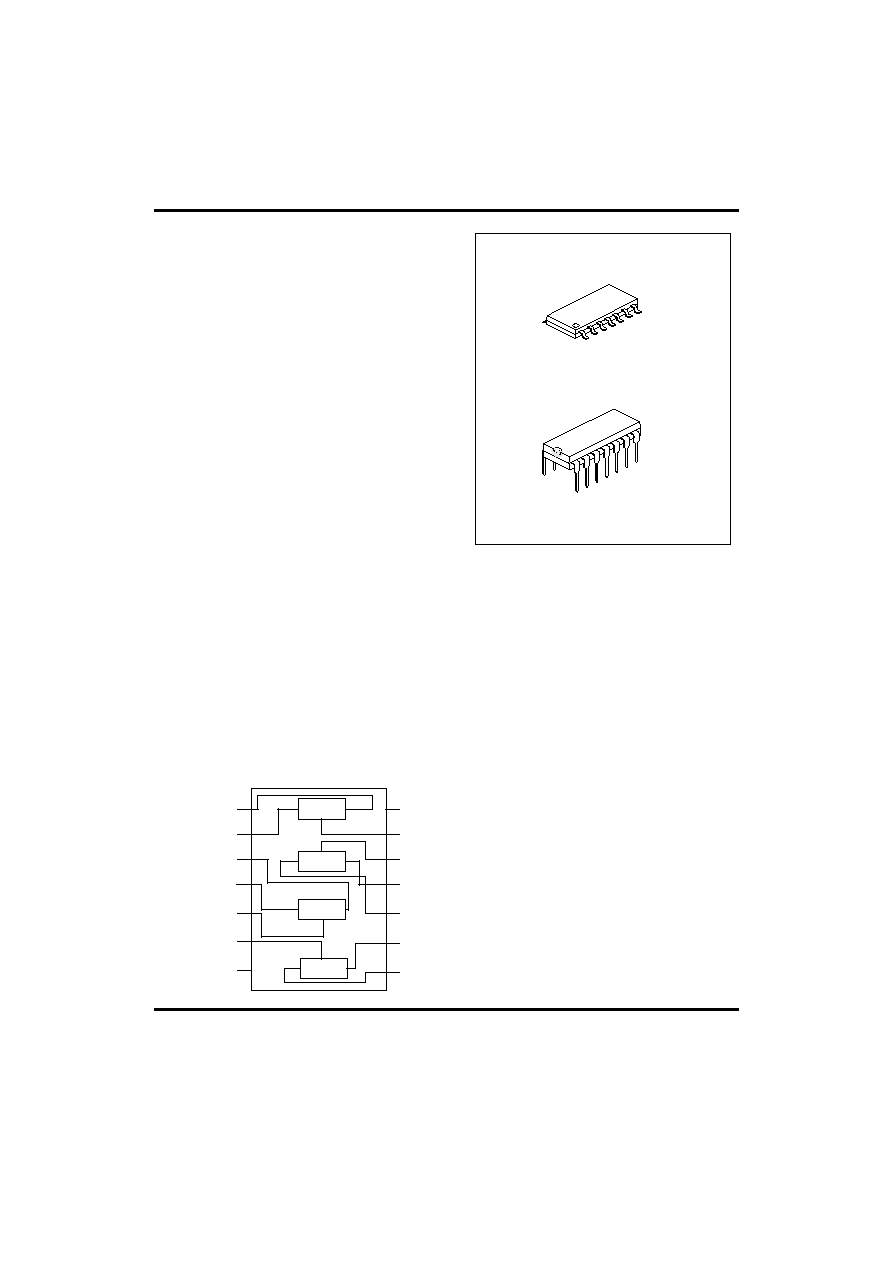

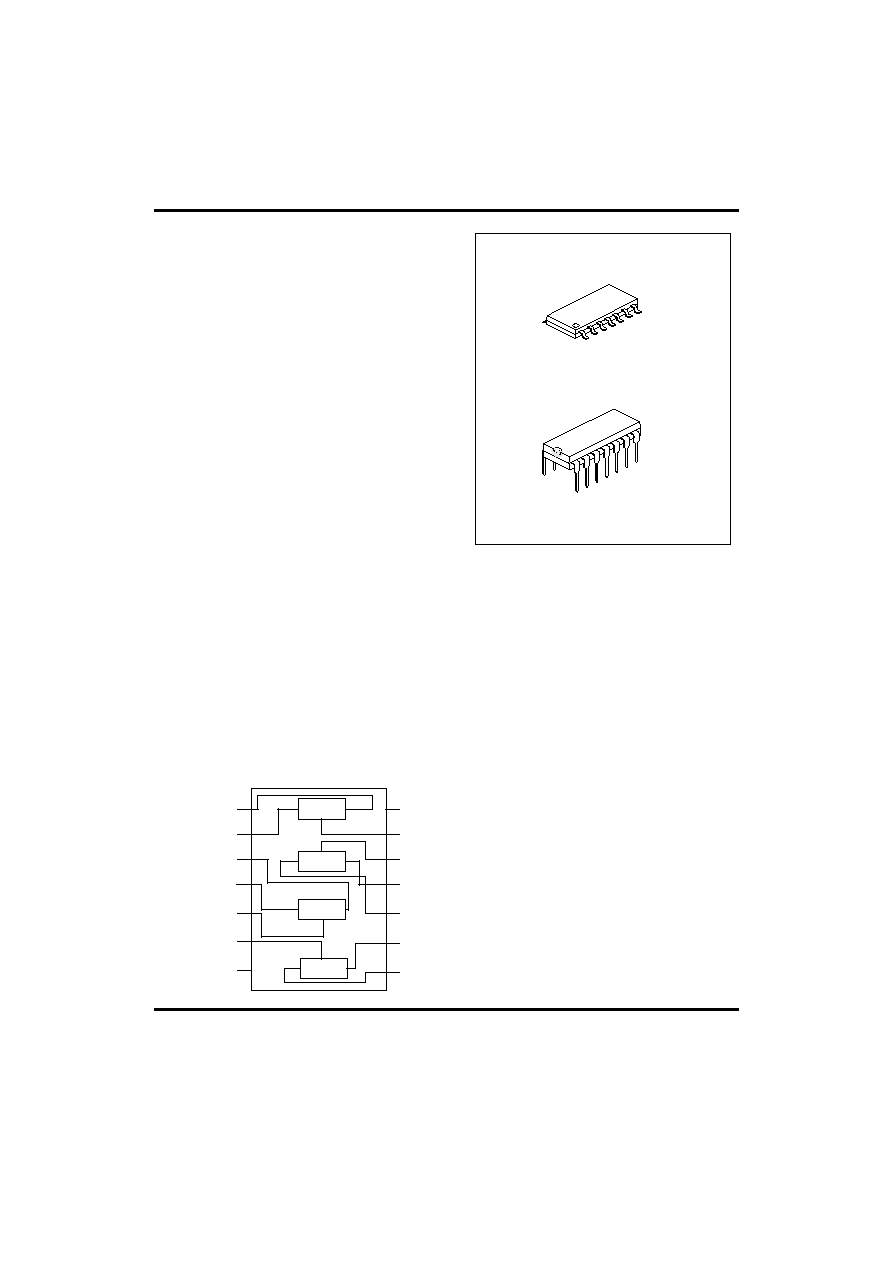

DIP-14

SOP-14

APPLICATIONS

*Analog signal switching/multiplexing

*Signal gating

*Squelch control

*Chopper

*Modulator/Demodulator

*Commutating switch

*Digital signal switching/multiplexing

*CMOS logic implementation

*Analog-to-digital/digital-to-analog conversion

*Digital control of frequency,impedance,phase,and

analog-signal-gain.

PIN CONFIGURATION

IN / OUT

OUT / IN

OUT / IN

IN / OUT

CONTROL B

CONTROL C

Vss

IN / OUT

OUT / IN

OUT / IN

IN / OUT

CONTROL C

CONTROL A

V

DD

1

14

7

6

5

4

3

2

8

9

10

11

12

13

SW A

SW C

SW B

SW D

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

2

QW-R502-009,A

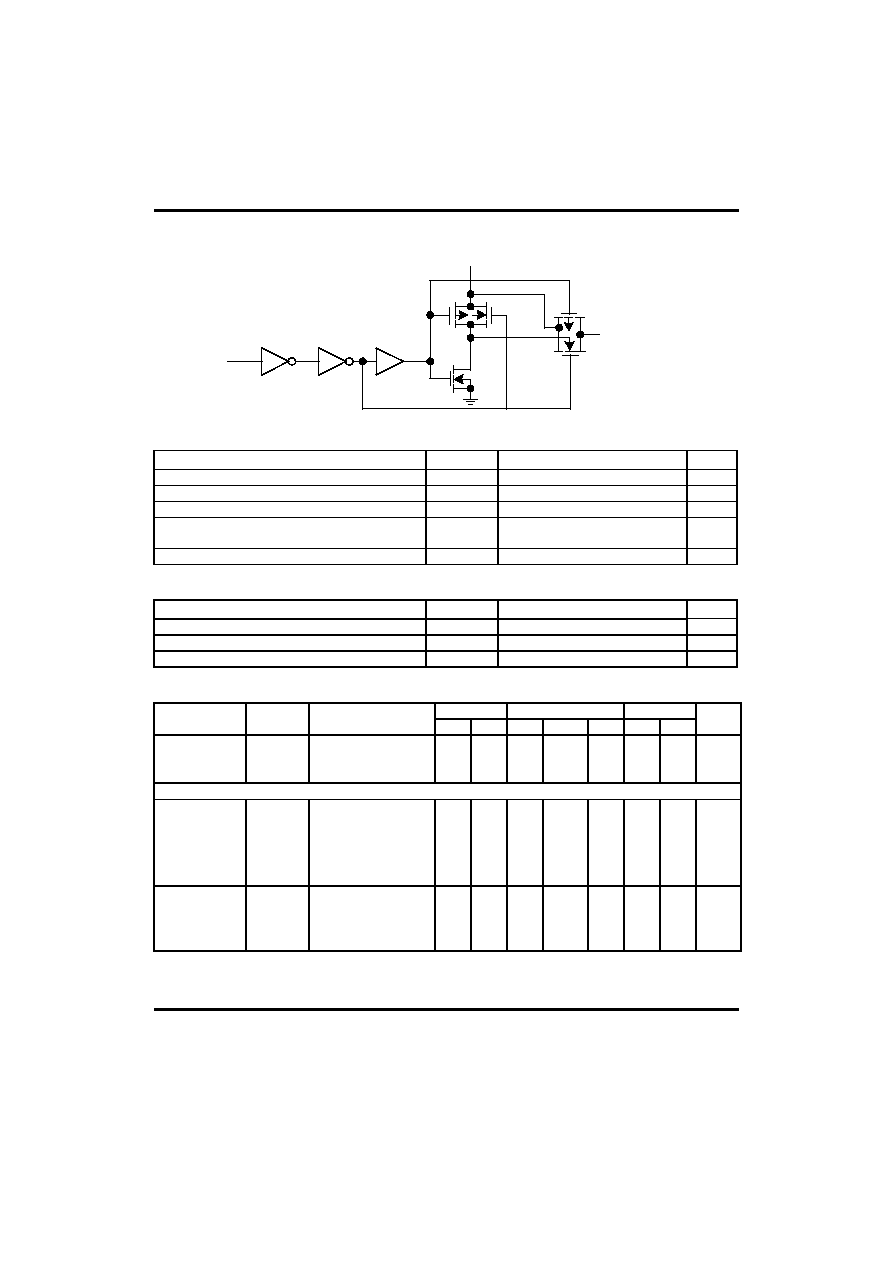

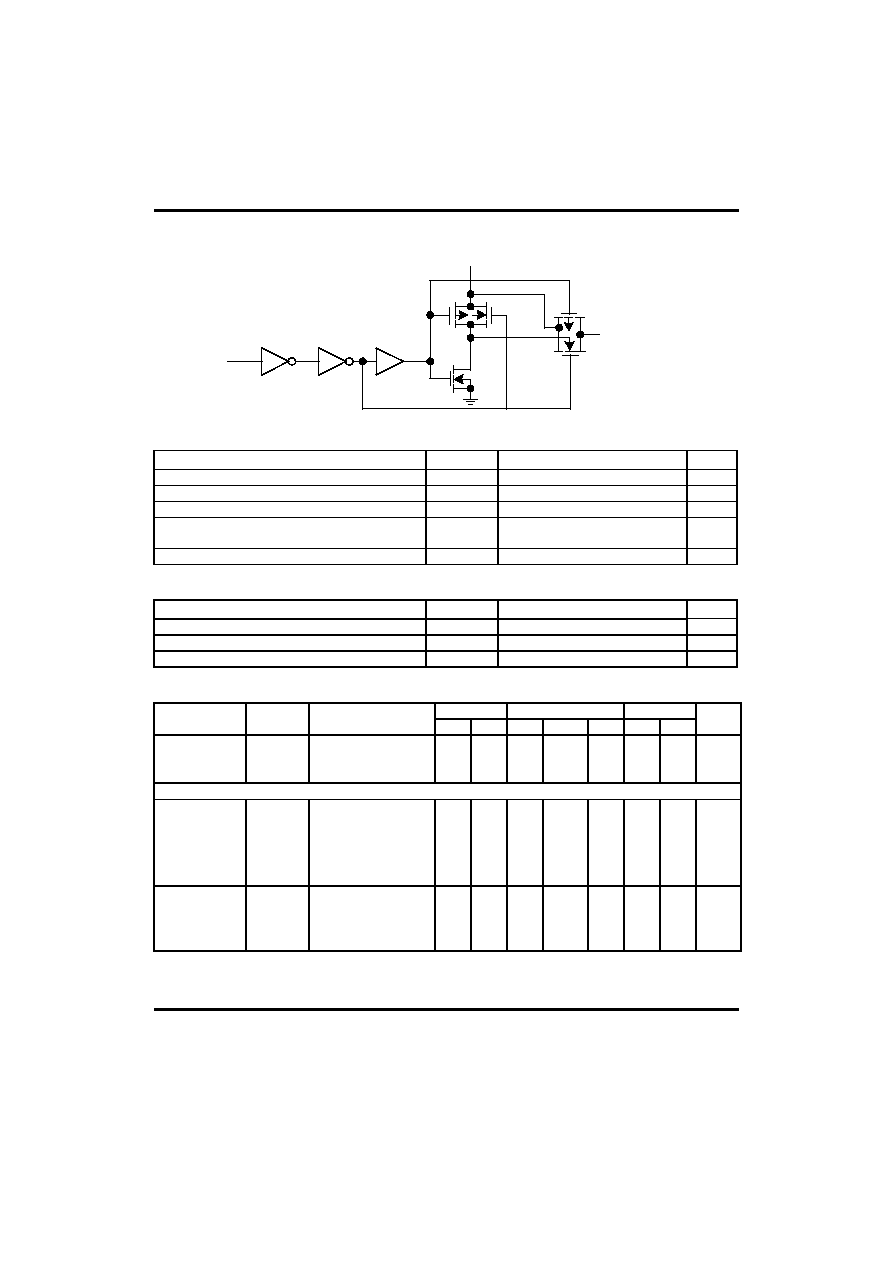

SCHEMATIC DIAGRAM

I N / OUT

CONTROL

OUT/ I N

Vss

ABSOLUTE MAXIMUM RATINGS

(Vss=0V, unless otherwise specified)

PARAMETER SYMBOL

RATING

UNIT

Supply Voltage

V

DD

-0.5 ~ +18

V

Input Voltage

V

IN

-0.5 ~ Vcc+0.5

V

Storage Temperature Range

Tstg

-65 ~ +150

∞C

Power Dissipation DIP-14

SOP-14

P

D

700

500

mW

Lead Temperature (Soldering,10 seconds)

T

lead

300

∞C

RECOMMENDED OPERATING CONDITIONS

(Vss=0V, unless otherwise specified)

PARAMETER SYMBOL

RATING

UNIT

Supply Voltage

V

DD

3 ~ 15

V

Input Voltage

V

IN

0 ~ V

DD

V

Operating Temperature Range

Topr

-40 ~ +85

∞C

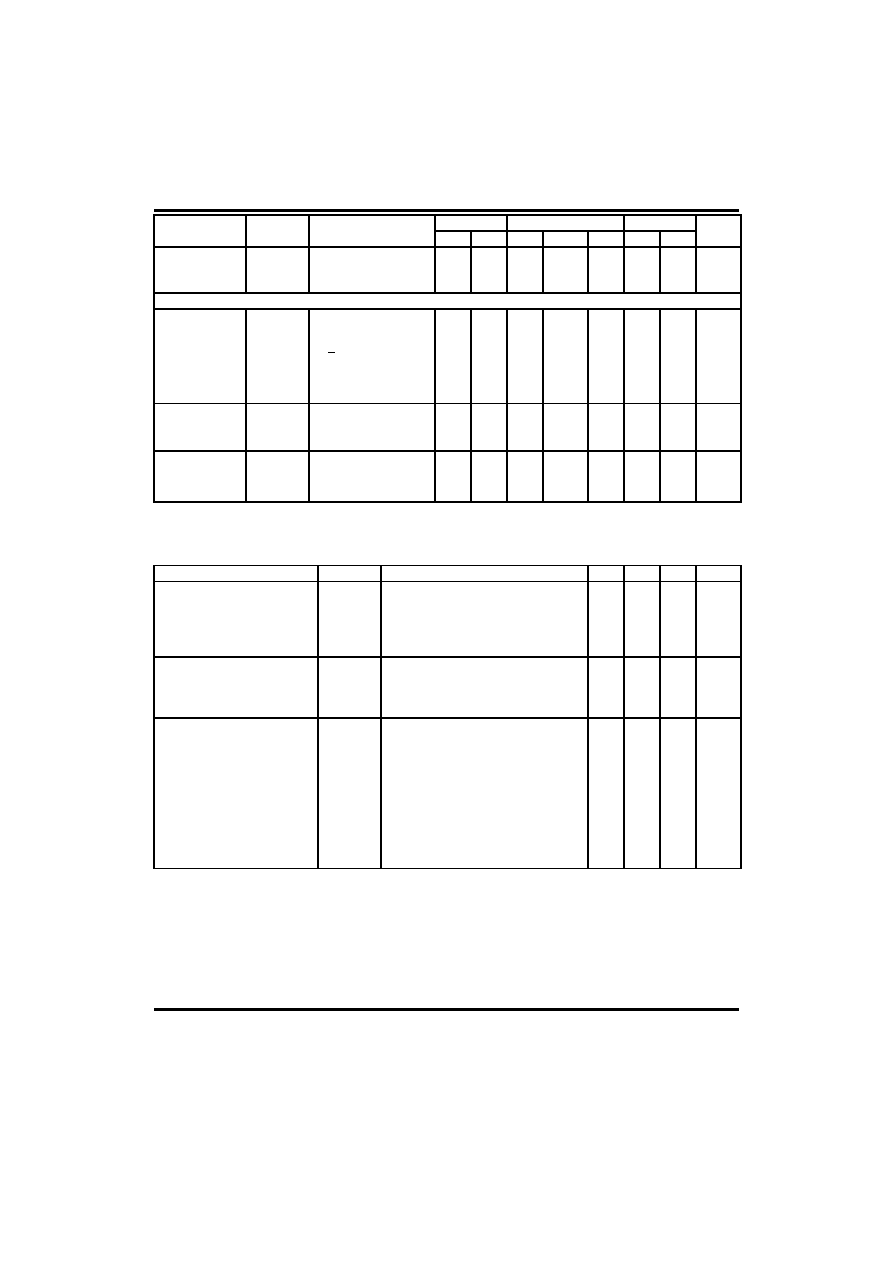

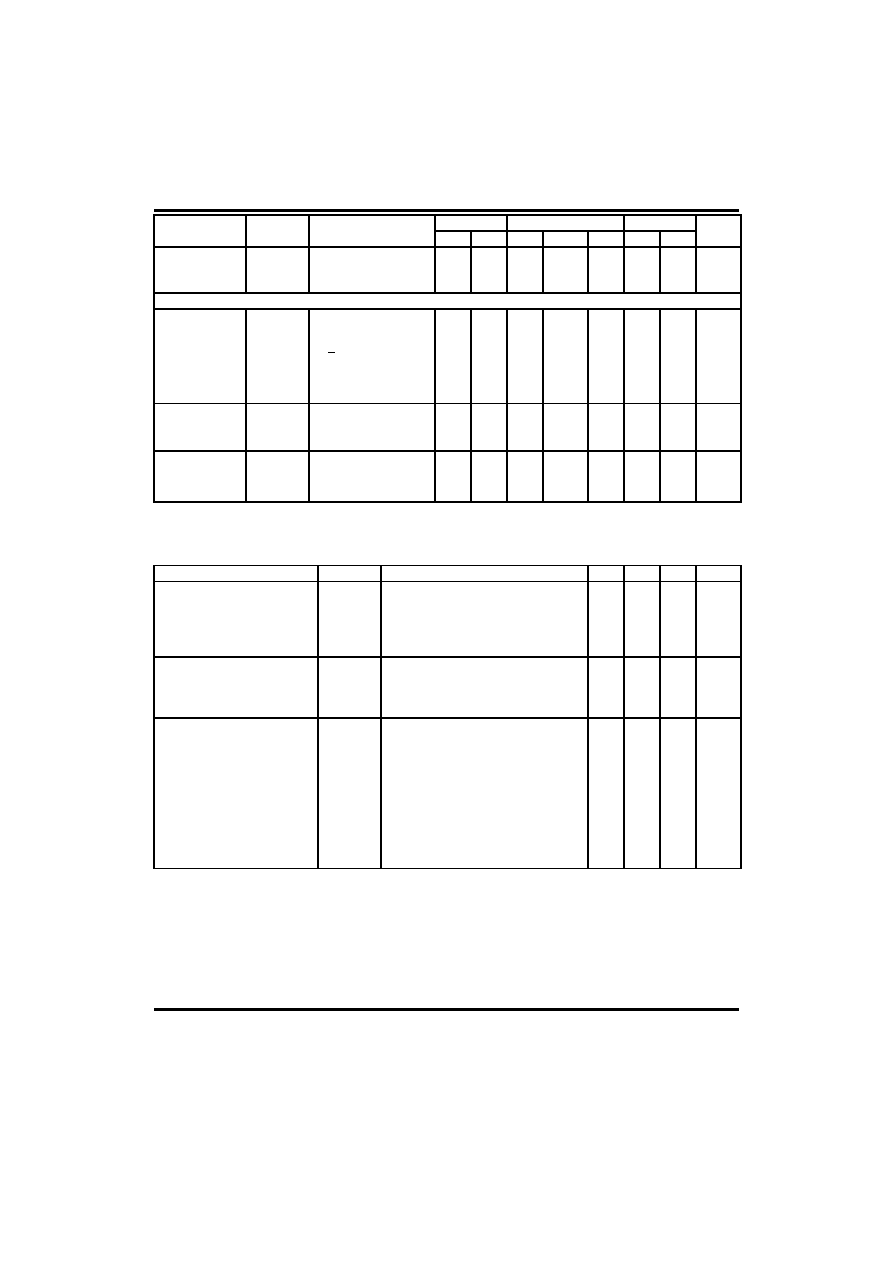

DC ELECTRICAL CHARACTERISTICS

(Vss=0V, unless otherwise specified)

-40∞C +25∞C +85∞C

PARAMETER SYMBOL

CONDITIONS

MIN MAX

MIN TYP MAX

MIN MAX

UNITS

Quiescent

Device Current

I

DD

V

DD

=5V

V

DD

=10V

V

DD

=15V

1.0

2.0

4.0

0.01

0.01

0.01

1.0

2.0

4.0

7.5

15

30

A

A

A

SIGNAL INPUTS AND OUTPUTS

"ON"Resistance R

ON

R

L

=10kto (V

DD

-V

SS

/2)

Vc=V

DD

,V

SS

to V

DD

V

DD

=5V

V

DD

=10V

V

DD

=15V

850

330

210

270

120

80

1050

400

240

1200

520

300

"ON"

Resistance

Between Any 2

of 4 Swiches

R

ON

R

L

=10kto (V

DD

-V

SS

/2)

Vc=V

DD

,V

IS

=V

SS

to V

DD

V

DD

=10V

V

DD

=15V

10

5

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

3

QW-R502-009,A

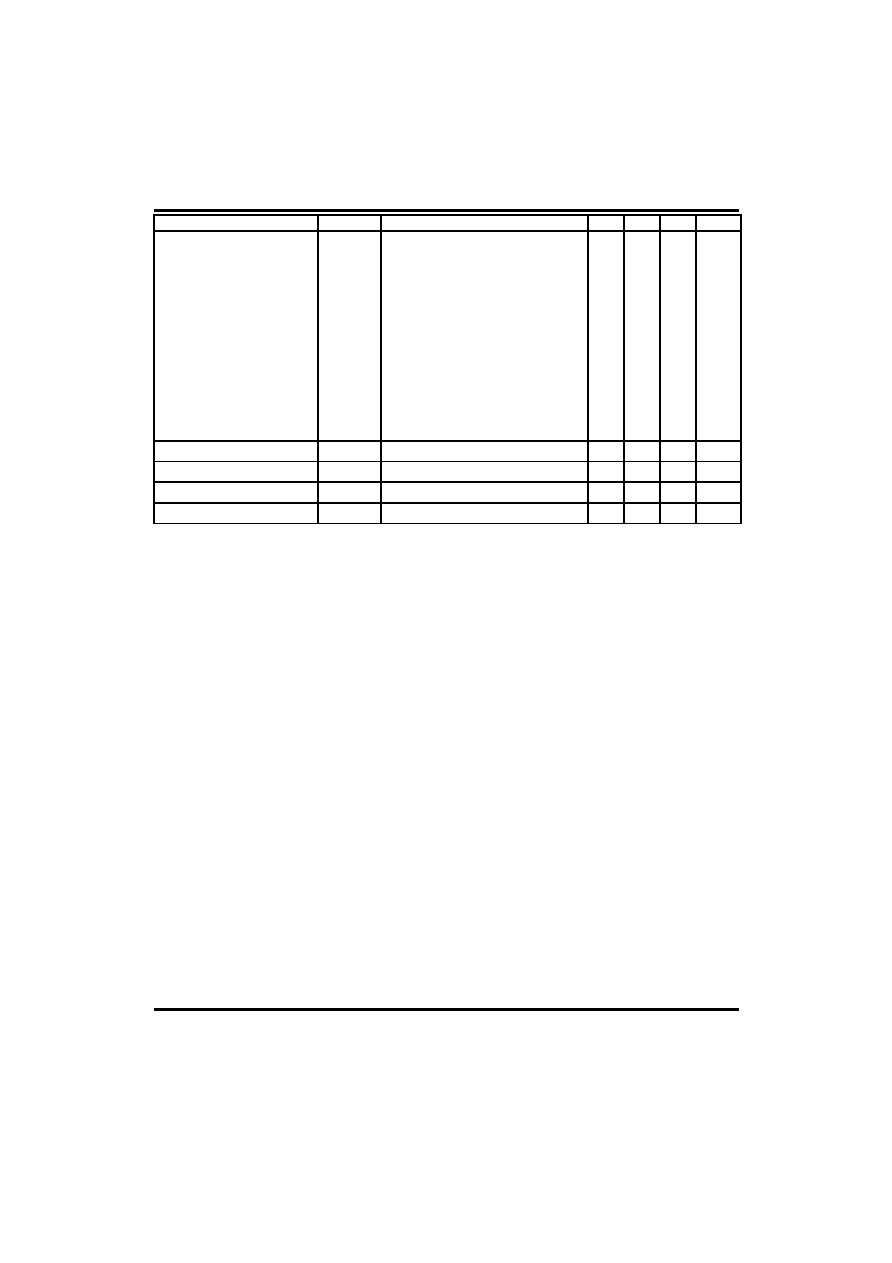

-40∞C +25∞C +85∞C

PARAMETER SYMBOL

CONDITIONS

MIN MAX

MIN TYP MAX

MIN MAX

UNITS

Input or Output

Leakage

Switch"OFF"

I

IS

Vc=0

±50 ±0.1

±50 ±200 nA

CONTROL INPUTS

Low Level Input

Voltage

V

ILC

V

IS

=Vss and V

DD

Vos=V

DD

and Vss

I

IS

=+10A

V

DD

=5V

V

DD

=10V

V

DD

=15V

1.5

3.0

4.0

2.25

4.5

6.75

1.5

3.0

4.0

1.5

3.0

4.0

V

V

V

HIGH Level Input

Voltage

V

IHC

V

DD

=5V

V

DD

=10V (Note 4)

V

DD

=15V

3.5

7.0

11.0

3.5

7.0

11.0

2.75

5.5

8.25

3.5

7.0

11.0

V

V

V

Input Current

I

IN

V

DD

-V

SS

=15V

V

DD

VISVss

V

DD

VcVss

±0.3 ±10

-5

±0.3 ±1.0 A

AC ELECTRICAL CHARACTERISTICS

(AC Parameters are guaranteed by DC correlated testing)

(T

A

=25,tr=tf=20 ns and Vss=0V unless otherwise)

PARAMETER SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Propagation Delay Time Signal

Input to Signal Output

T

PHL

,T

PLH

Vc=V

DD

,C

L

=50pF,(Figure1)

R

L

=200k

V

DD

=5V

V

DD

=10V

V

DD

=15V

25

15

10

55

35

25

ns

ns

ns

Propagation Delay Time

Control Input to Signal

Output High Impedance to

Logical Level

t

PZH

,t

PLZ

R

L

=1.0k,C

L

=50pF,(Figure2,Figure3)

V

DD

=5V

V

DD

=10V

V

DD

=15V

125

60

50

ns

ns

ns

Propagation Delay Time

Control Input to Signal

Output Logical Level to

High Impedance

Sine Wave Distortion

Frequency Response-Switch

"ON"(Frequency at-3dB)

t

PHZ

,t

PLZ

R

L

=1.0k,C

L

=50pF,(Figure2,Figure3)

V

DD

=5V

V

DD

=10V

V

DD

=15V

Vc=V

DD

=5V,Vss=-5V

R

L

=10k,V

IS

=5Vp-p,f=1kHz,(Figure 4)

Vc=V

DD

=5V,Vss=-5V

R

L

=1k,V

IS

=5Vp-p

20 Log10 V

OS

/V

OS

(1kHz)-dB

(Figure4)

0.1

40

125

60

50

ns

ns

ns

%

MHz

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

4

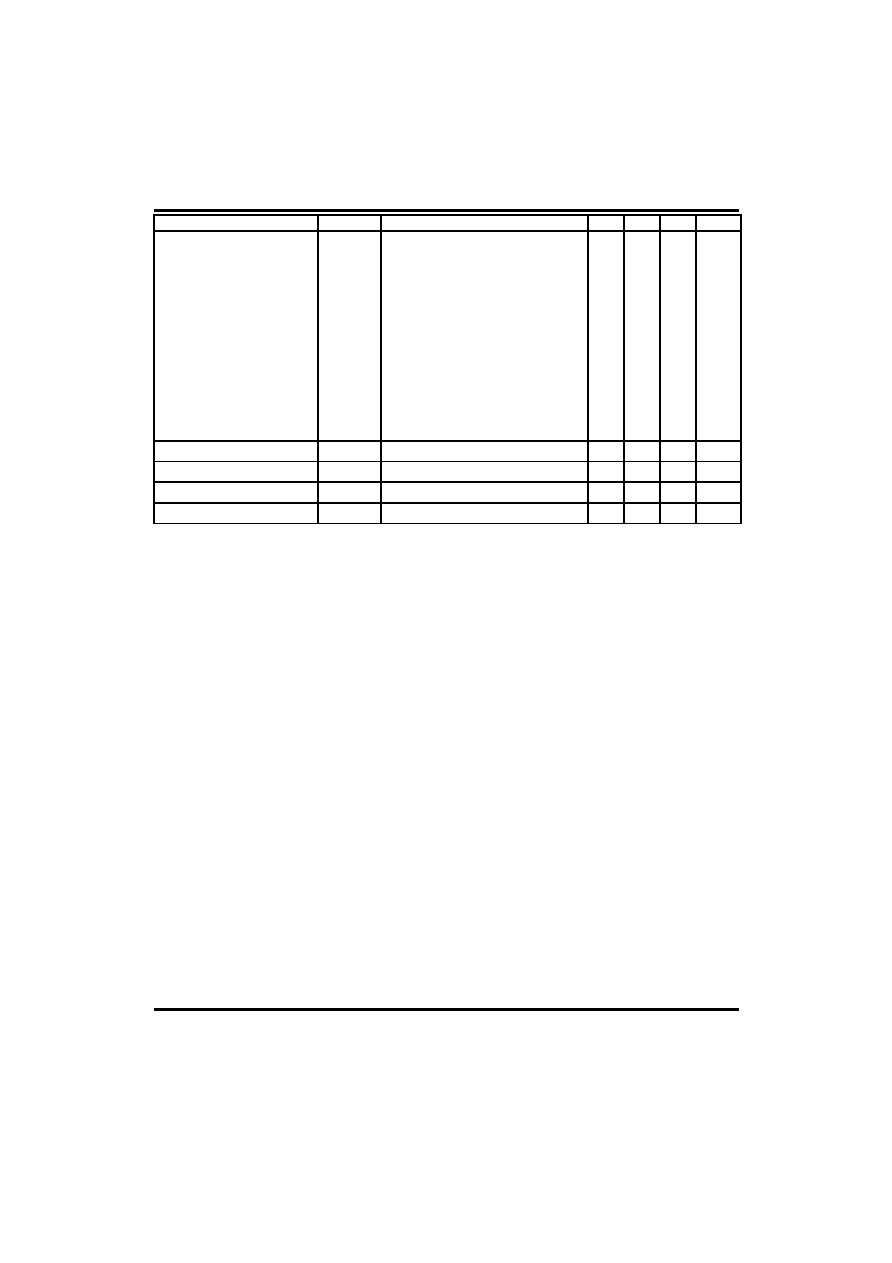

QW-R502-009,A

PARAMETER SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Feedthrough-Switch "OFF"

(Frequency at ≠50 dB)

Crosstalk Between Any Two

Switches(Frequency at-50dB)

Crosstalk;Control Input to

Signal Output

Maximum Control Input

V

DD

=5.0V,Vcc=Vss=-5.0V,

R

L

=1k,V

IS

=5.0Vp-p,20Log

10

,

Vos/Vis=-50dB,(Figure 4)

V

DD

=VC(A)=5.0V;Vss=Vc(B)=5.0V,

R

L

1k,V

IS

(A)=5.0Vp-p,20Log

10

,

Vos(B)/V

IS

(A)=-50dB(Figure5)

V

DD

=10V,R

L

=10k,R

IN

=1.0k

Vcc=10V Square Wave,C

L

=50pF

(Figure 6)

R

L

=1.0k,C

L

=50pF,(Figure7)

Vos(f)=1/2Vos(1.0kHz)

V

DD

=5.0V

V

DD

=10V

V

DD

=15V

1.25

0.9

150

6.0

8.0

8.5

MHz

mVp-p

MHz

MHz

MHz

Signal Inut Capacitance

C

IS

8.0 pF

Signal Output Capacitance

C

OS

V

DD

=10V

8.0

pF

Feedthrough Capacitance

C

IOS

V

C

=0V

0.5

pF

Controllnput Capacitance

C

IN

5.0 7.5 pF

Note 1:These devices should not be connected to circuits with th power "ON"

Note 2:In all cases,these is approximately 5pF of probe and jig capacitance in the output;however,this capacitance is

induded in C

L

wherever it is specified.

Note 3:Vis is the voltage at the in/out pin and Vos is the voltage at the out/in pin.Vc is the voltage at the control input.

Note 4:Conditions for V

IHC

:(a) V

IS

=V

DD

,Ios=standard B series I

OH

. (b) V

IS

=0V,I

OL

=standard B series Io

L

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

5

QW-R502-009,A

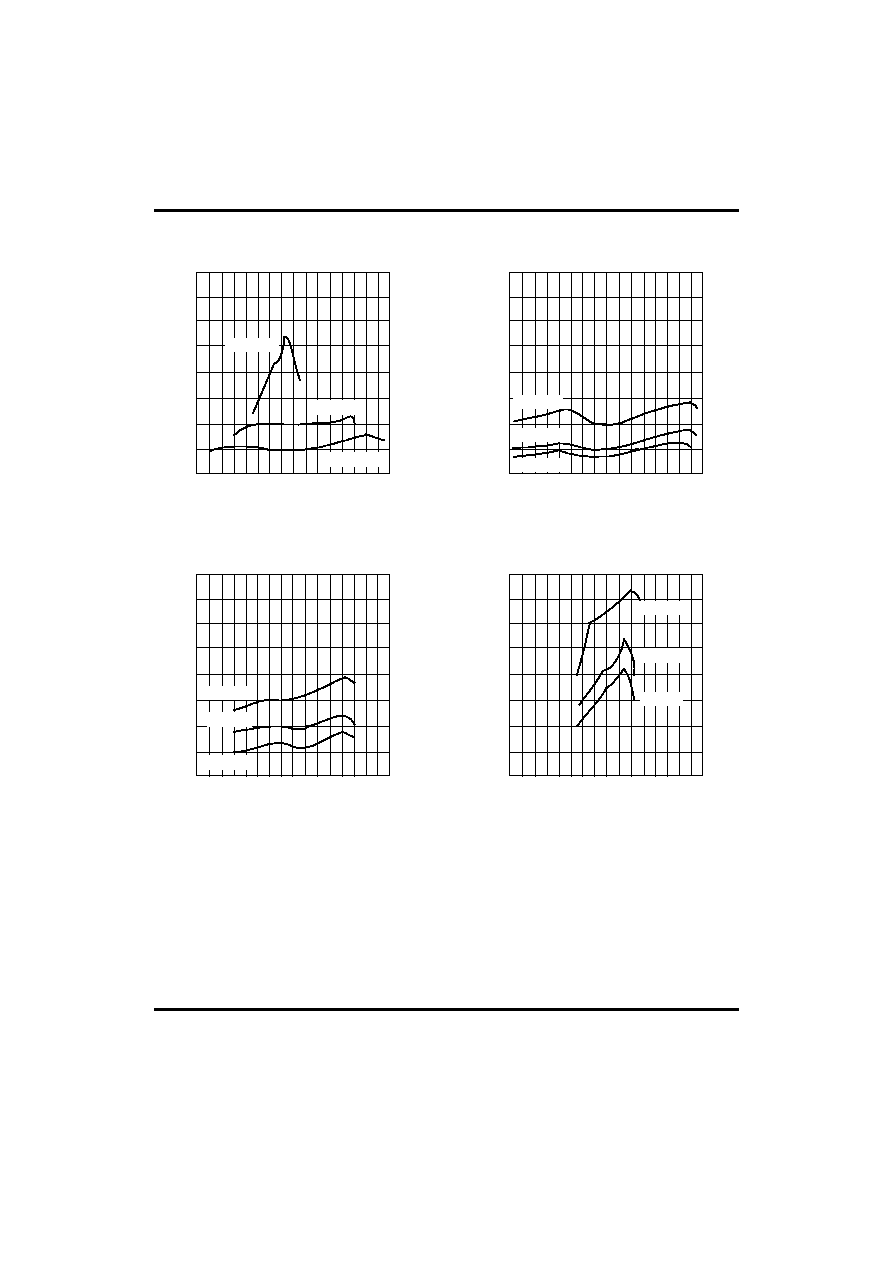

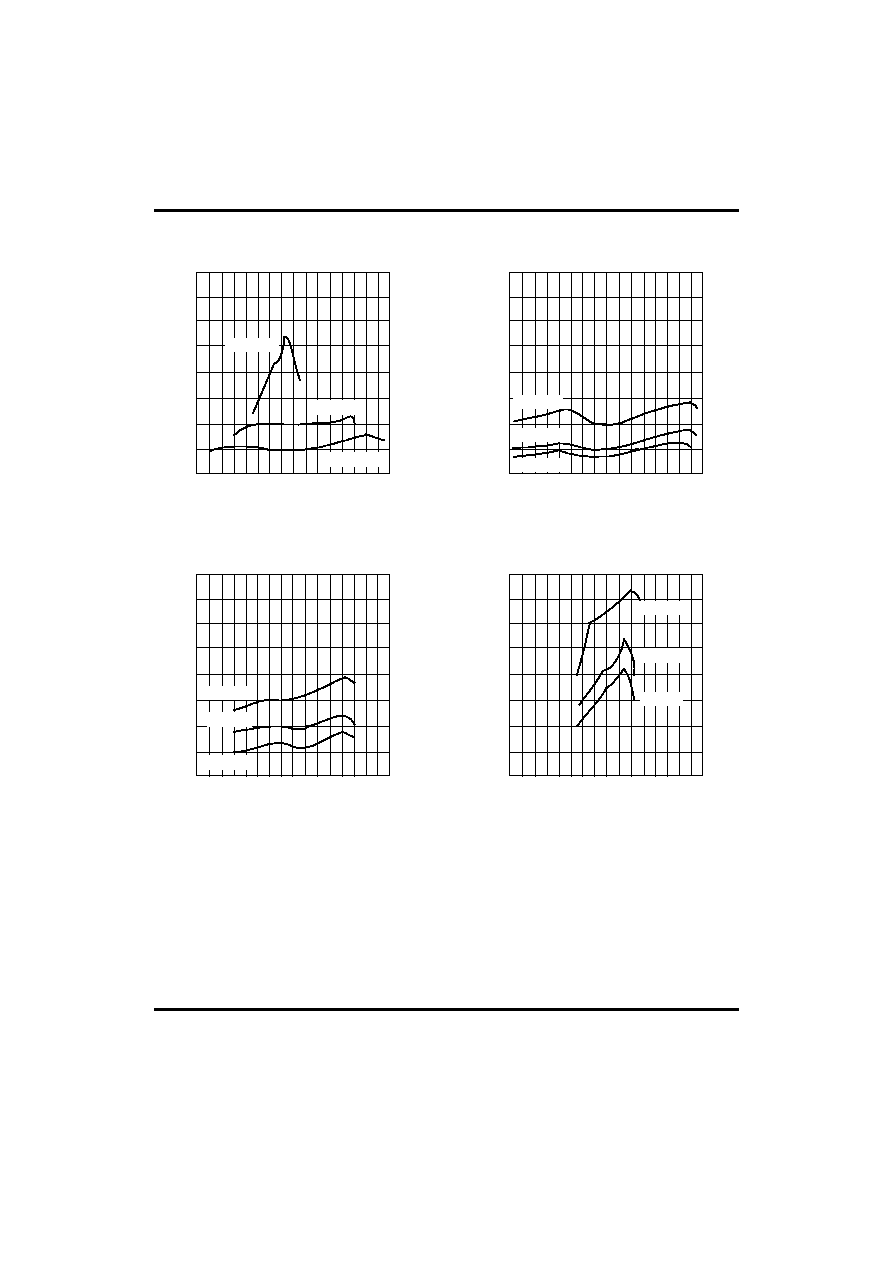

TYPICAL PERFORMANCE CHARACTERISTICS

0

0

"ON"Resistance vs Signal Voltage for T

A

=25

400

350

300

250

200

150

100

50

-8

-6

-4

-2

2

4

6

8

SIGNAL VOLTAGE (V

IS

) (V)

C

H

A

N

N

E

L

"

O

N

"

R

E

S

I

S

T

A

N

C

E

(

R

O

N

)

(

)

0

0

"ON"Resistance as a Function of emperature for

V

DD

-V

SS

=15V

400

350

300

250

200

150

100

50

-8

-6

-4

-2

2

4

6

8

SIGNAL VOLTAGE (V

IS

) (V)

C

H

A

N

N

E

L

"

O

N

"

R

E

S

I

S

T

A

N

C

E

(

R

O

N

)

(

)

0

0

400

350

300

250

200

150

100

50

-8

-6

-4

-2

2

4

6

8

SIGNAL VOLTAGE (V

IS

) (V)

C

H

A

N

N

E

L

"

O

N

"

R

E

S

I

S

T

A

N

C

E

(

R

O

N

)

(

)

0

0

400

350

300

250

200

150

100

50

-8

-6

-4

-2

2

4

6

8

SIGNAL VOLTAGE (V

IS

) (V)

C

H

A

N

N

E

L

"

O

N

"

R

E

S

I

S

T

A

N

C

E

(

R

O

N

)

(

)

V

DD

-V

SS

=5V

V

DD

-V

SS

=10V

V

DD

-V

SS

=15V

TA=+125

TA=+25

TA=-55

"ON"Resistance as a Function of Temperature for

V

DD

-V

SS

=10V

TA=+125

TA=+25

TA=-55

"ON"Resistance as a Function of Temperature for

V

DD

-V

SS

=15V

TA=+125

TA=+25

TA=-55

SPECIAL CONSIDERATIONS

In applications where separate power sources are used to drive V

DD

and the signal input,the V

DD

current capability

should exceed V

DD

/R

L

(R

L

=effective extermal load of the 4066 bilateral switches).This provision avoids any

permanent current flow or clamp action of the V

DD

supply when power is applied or removed from UTCCD4066.

In certain applications,the external load-resistor current may include both V

DD

and Signal-line components.To

avoid drawing V

DD

current when switch current flows into terminals 1,4,8 or 11,the voltage drop across the

bidirectional swith must not exceed 0.6V at T

A

25,or 0.4V at T

A

>25(calculated from R

ON

vlues shown).

NO V

DD

current will flow through R

L

if the switch current flows into terminals2,3,9 or 10.

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

6

QW-R502-009,A

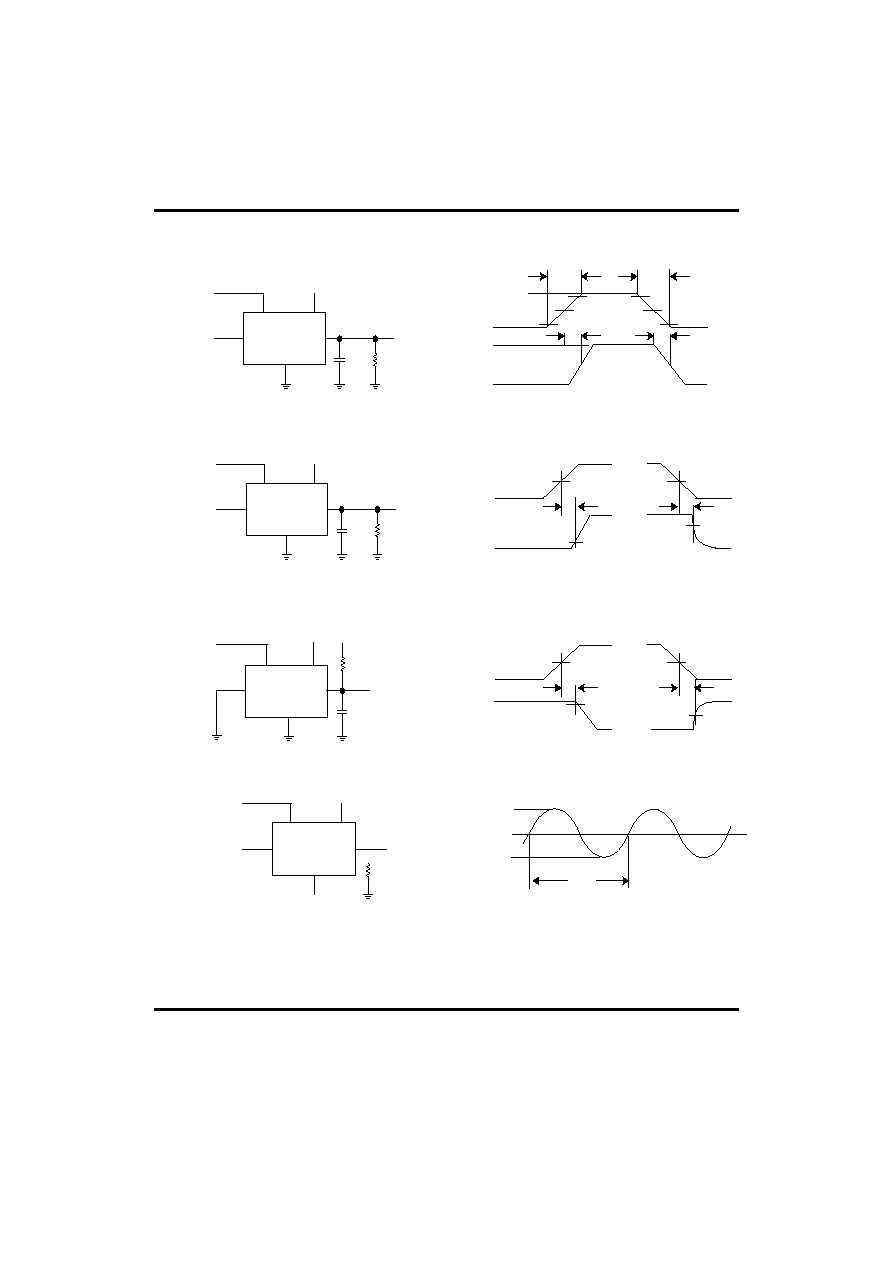

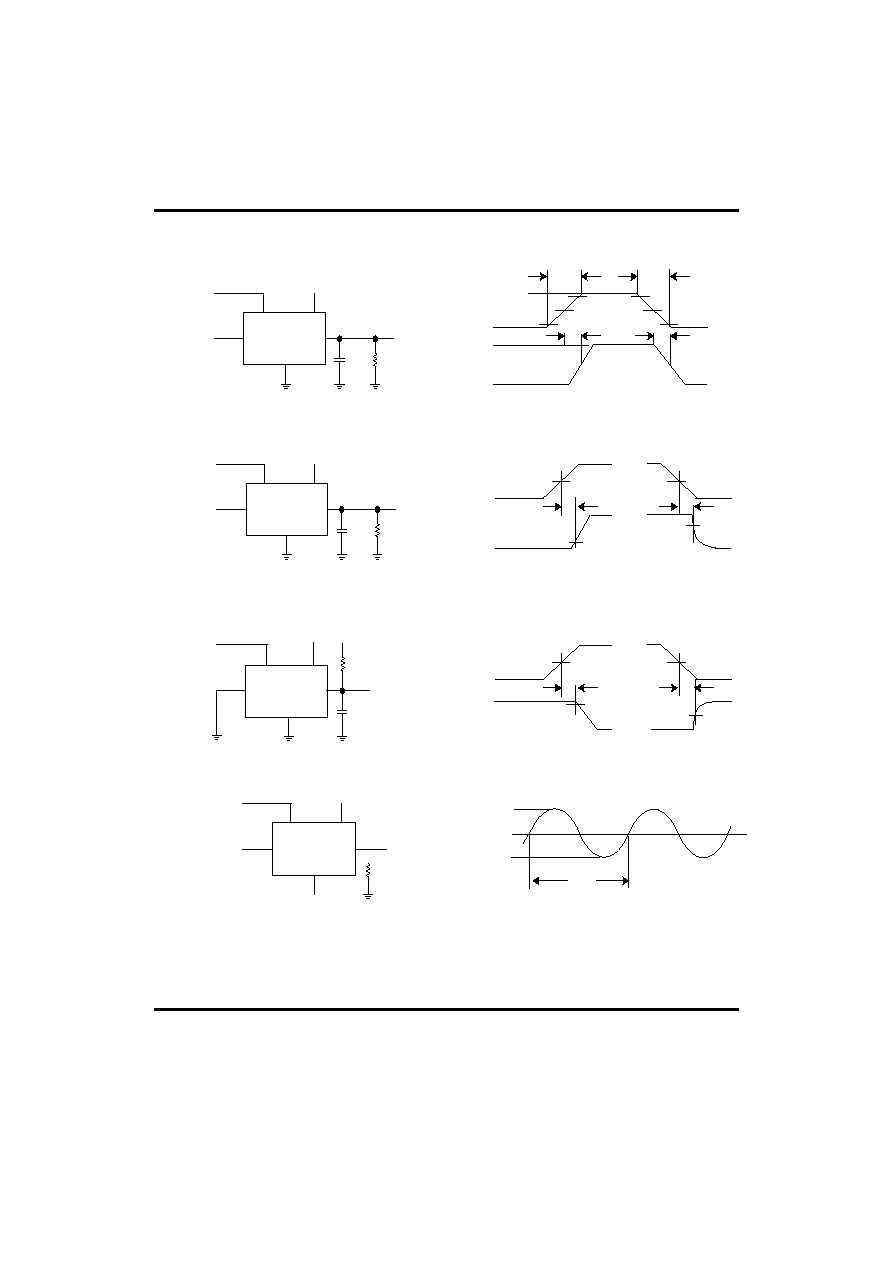

AC TEST CIRCUITS AND SWITCHING TIME WAVEFORMS

OUT/IN

V

C

=V

DD

V

IS

V

DD

V

OS

RL

200K

CL

50F

90%

50%

10%

V

DD

0V

V

DD

0V

V

OS

V

IS

tf

tf

t

PLN

t

PNL

50%

FIGURE 1.t

PHL

,t

PLH

Propagation Delay Time Signal Input to Signal Output

V

C

V

DD

V

OS

RL

1K

50%

10%

V

DD

0V

V

OH

0V

t

PHZ

FIGURE 2.t

PZH

,t

PHZ

Propagation Delay Time Control to Signal Output

V

IS

=V

DD

t

PZH

V

DD

0V

V

OH

0V

50%

90%

V

DD

t

PZH

t

PHZ

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

V

C

V

DD

V

OS

RL

1K

50%

V

DD

0V

V

DD

V

OL

t

PLZ

FIGURE 3.t

PZL

,t

PLZ

Propagation Delay Time Control to Signal Output

V

IS

=0V

t

PZL

V

DD

0V

50%

t

PZL

t

PLZ

V

DD

90%

10%

V

DD

V

OL

CL

50F

CL

50F

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

CONTROL

V

DD

IN/OUT

Vss

1 OF 4

SWITCHES

OUT/IN

V

C

5V

V

OS

RL

FIGURE 4.Sine Wave Distortion,Frequency Response and Feedthrough

V

IS

-5V

Vc=VDD for distortion and frequency response tests

Vc=Vss for feedthrough test

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

1/ f

2.5V

V

IS

0V

-2.5V

UTC 4066

CMOS

UTC

UNISONIC TECHNOLOGIES CO. LTD

7

QW-R502-009,A

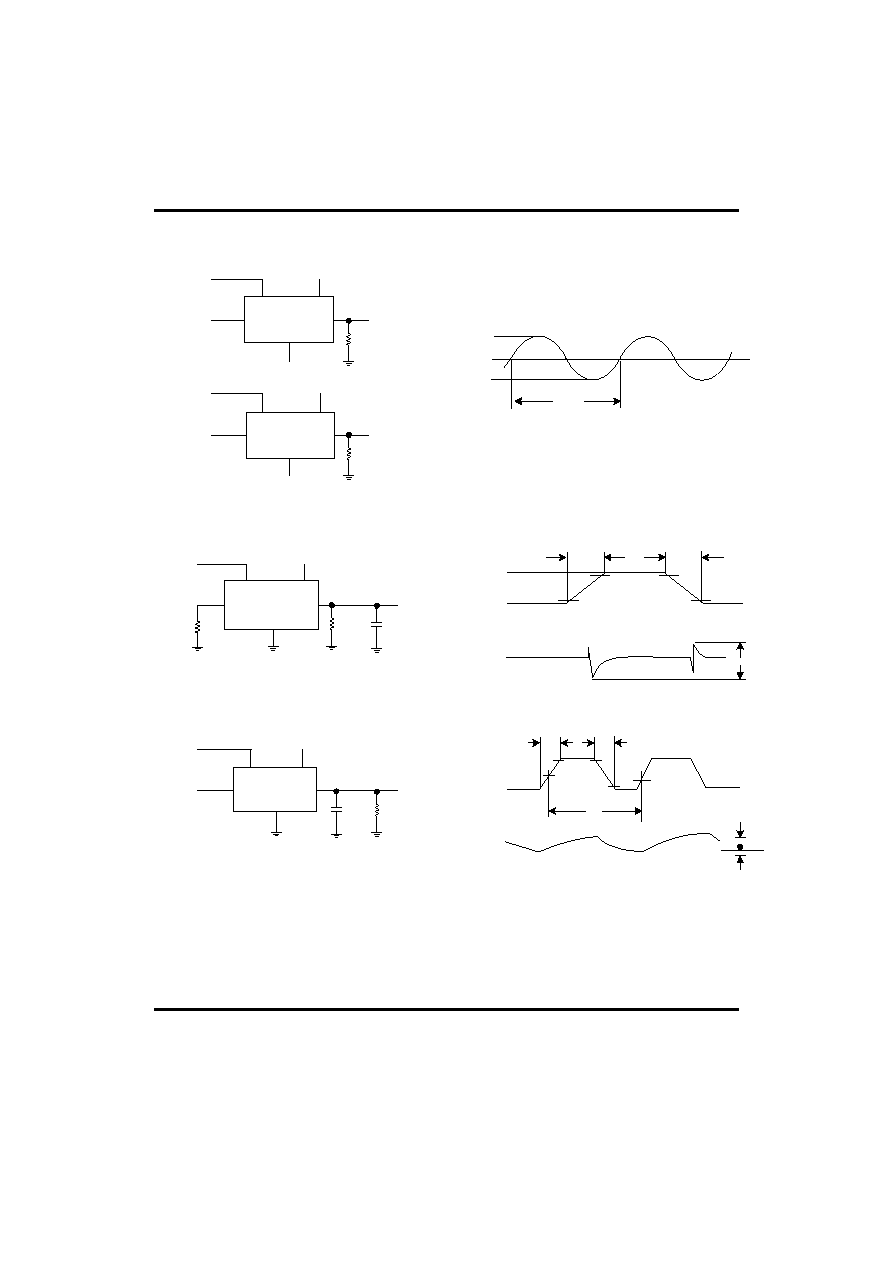

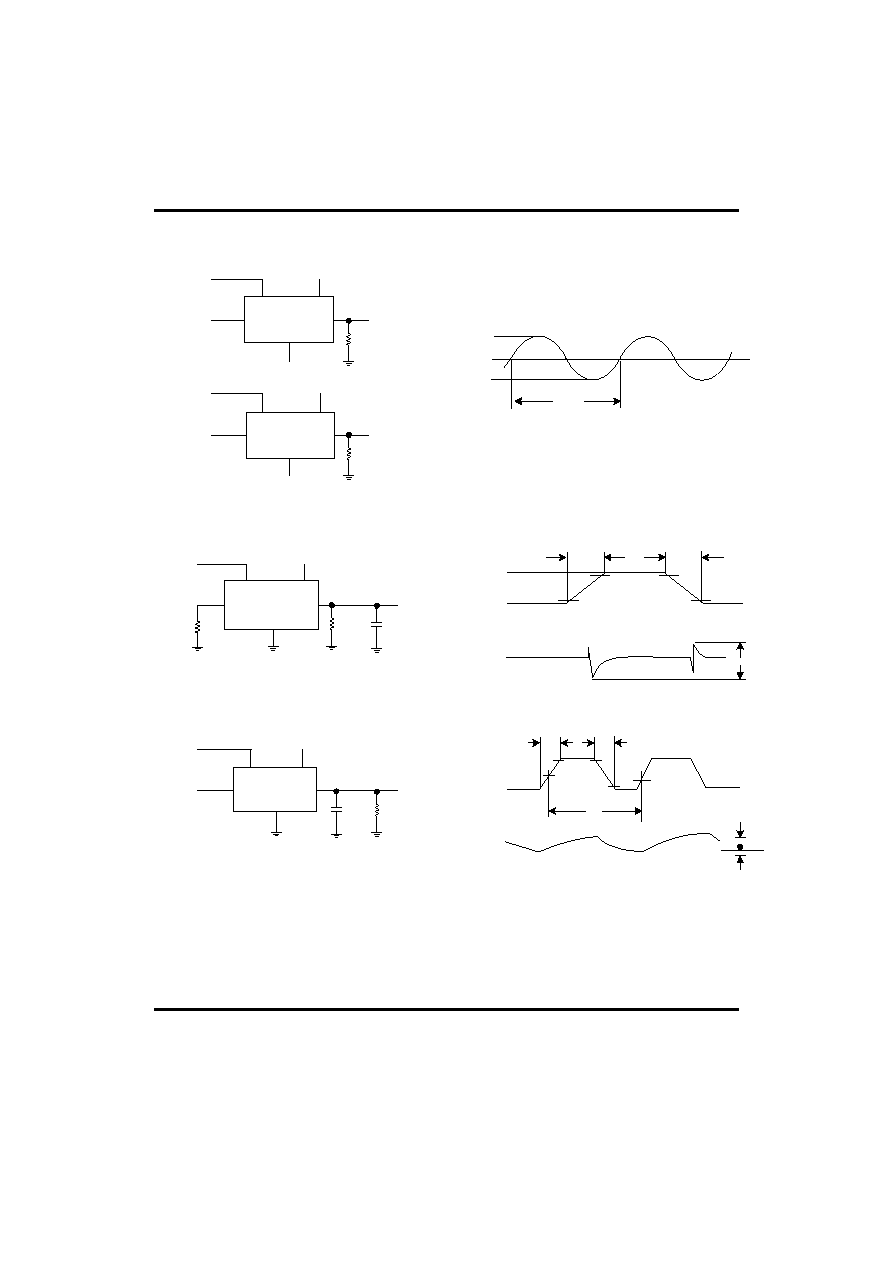

AC TEST CIRCUITS AND SWITCHING TIME WAVEFORMS

(CONTINUED)

V

C(1)

=V

DD

5V

V

OS(1)

RL

1k

FIGURE 5.Crosstalk Between Any T wo Switches

V

IS(1)

-5V

V

C(2)

=Vss

5V

V

OS(2)

RL

1k

-5V

V

IS(2)

=0V

90%

10%

V

DD

0V

VC

V

OS

tf=20ns

V

DD

OUT/IN

Vc

10V

V

OS

RL

10k

V

IS

CL

50 F

R

IN

1k

FIGURE 6.Crosstalk :Control Input to Signal Output

tf=20ns

CROSSTALK

V

DD

0V

VC

V

OS

Vc

V

OS

RL

1k

V

IS

=V

DD

CL

50 F

FIGURE 7.Maximum Control Input Frequenc y

V

DD

tf

tf

90%

50%

50%

10%

10%

1/f

V

OS

1kHz

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

CONTROL

IN/OUT

Vss

1 OF 4

SWITCHES

V

DD

OUT/IN

CONTROL

V

DD

IN/OUT

OUT/IN

Vss

1 OF 4

SWITCHES

1/ f

2.5V

V

IS

0V

-2.5V