'HOLYHULQJ

9DOXH

9,$ 7HFKQRORJLHV

97

$SROOR093

0+]

6LQJOH&KLS6RFNHW6XSHU1RUWK%ULGJH

ZLWK3&,6\VWHP%XV

,QWHJUDWHG$*3''*UDSKLFV$FFHOHUDWRU

DQG$GYDQFHG(&&0HPRU\&RQWUROOHU

VXSSRUWLQJ3&6'5$0

9LUWXDO&KDQQHO6'5$0('2DQG)3*'5$0

5HYLVLRQ

)HEUXDU\

9,$7(&+12/2*,(6,1&

&RS\ULJKW1RWLFH

&RS\ULJKW

9,$ 7HFKQRORJLHV ,QFRUSRUDWHG 3ULQWHG LQ WKH 8QLWHG 6WDWHV $

//

5

,*+76

5

(6(59('

1R SDUW RI WKLV GRFXPHQW PD\ EH UHSURGXFHG WUDQVPLWWHG WUDQVFULEHG VWRUHG LQ D UHWULHYDO V\VWHP RU WUDQVODWHG LQWR

DQ\ ODQJXDJH LQ DQ\ IRUP RU E\ DQ\ PHDQV HOHFWURQLF PHFKDQLFDO PDJQHWLF RSWLFDO FKHPLFDO PDQXDO RU RWKHUZLVH

ZLWKRXW WKH SULRU ZULWWHQ SHUPLVVLRQ RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

97&% 97&% 97&$ 97 0RELOH 6RXWK 6XSHU 6RXWK $SROOR 093 $SROOR 093 $SROOR 3UR

$SROOR 3UR DQG $SROOR 3UR0HGLD PD\ RQO\ EH XVHG WR LGHQWLI\ SURGXFWV RI 9,$ 7HFKQRORJLHV

36

%

LV D UHJLVWHUHG WUDGHPDUN RI ,QWHUQDWLRQDO %XVLQHVV 0DFKLQHV &RUS

3HQWLXP

%

3HQWLXP,,

%

3HQWLXP,,,

%

00;

%

DQG ,QWHO

%

DUH UHJLVWHUHG WUDGHPDUNV RI ,QWHO &RUS

&\UL[

;

%

LV D UHJLVWHUHG WUDGHPDUN RI &\UL[ &RUS

$0'

.

%

$0'.

%

DQG $0'.

%

DUH UHJLVWHUHG WUDGHPDUNV RI $GYDQFHG 0LFUR 'HYLFHV &RUS

:LQGRZV

%

DQG 3OXJ DQG 3OD\

%

DUH UHJLVWHUHG WUDGHPDUNV RI 0LFURVRIW &RUS

3&,

%

LV D UHJLVWHUHG WUDGHPDUN RI WKH 3&, 6SHFLDO ,QWHUHVW *URXS

$OO WUDGHPDUNV DUH WKH SURSHUWLHV RI WKHLU UHVSHFWLYH RZQHUV

'LVFODLPHU1RWLFH

1R OLFHQVH LV JUDQWHG LPSOLHG RU RWKHUZLVH XQGHU DQ\ SDWHQW RU SDWHQW ULJKWV RI 9,$ 7HFKQRORJLHV 9,$ 7HFKQRORJLHV

PDNHV QR ZDUUDQWLHV LPSOLHG RU RWKHUZLVH LQ UHJDUG WR WKLV GRFXPHQW DQG WR WKH SURGXFWV GHVFULEHG LQ WKLV GRFXPHQW

7KH LQIRUPDWLRQ SURYLGHG E\ WKLV GRFXPHQW LV EHOLHYHG WR EH DFFXUDWH DQG UHOLDEOH WR WKH SXEOLFDWLRQ GDWH RI WKLV

GRFXPHQW +RZHYHU 9,$ 7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU DQ\ HUURUV LQ WKLV GRFXPHQW )XUWKHUPRUH 9,$

7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU WKH XVH RU PLVXVH RI WKH LQIRUPDWLRQ LQ WKLV GRFXPHQW DQG IRU DQ\ SDWHQW

LQIULQJHPHQWV WKDW PD\ DULVH IURP WKH XVH RI WKLV GRFXPHQW 7KH LQIRUPDWLRQ DQG SURGXFW VSHFLILFDWLRQV ZLWKLQ WKLV

GRFXPHQW DUH VXEMHFW WR FKDQJH DW DQ\ WLPH ZLWKRXW QRWLFH DQG ZLWKRXW REOLJDWLRQ WR QRWLI\ DQ\ SHUVRQ RI VXFK FKDQJH

2IILFHV

86$ 2IILFH

7DLSHL 2IILFH

0LVVLRQ &RXUW

WK

)ORRU 1R

)UHPRQW &$

&KXQJ&KHQJ 5RDG +VLQ7LHQ

86$

7DLSHL 7DLZDQ 52&

7HO �

7HO �

)D[ �

)D[ �

2QOLQH6HUYLFHV

+RPH 3DJH

http://www.via.com.tw

7DLZDQ� �RU

http://www.viatech.com

86$�

)73 6HUYHU

ftp.via.com.tw

7DLZDQ�

%%6

VT8501 Apollo MVP4

Revision 1.3 February 1, 2000

-i-

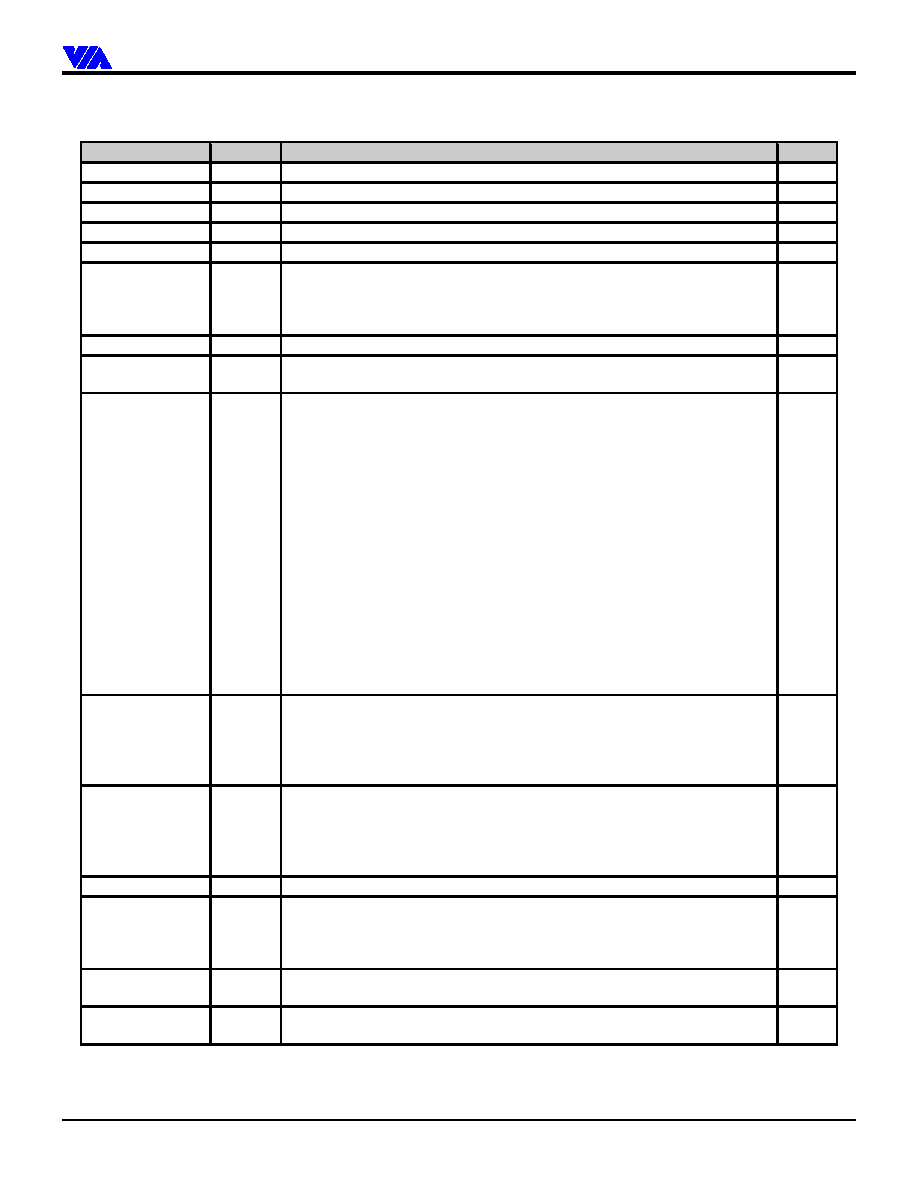

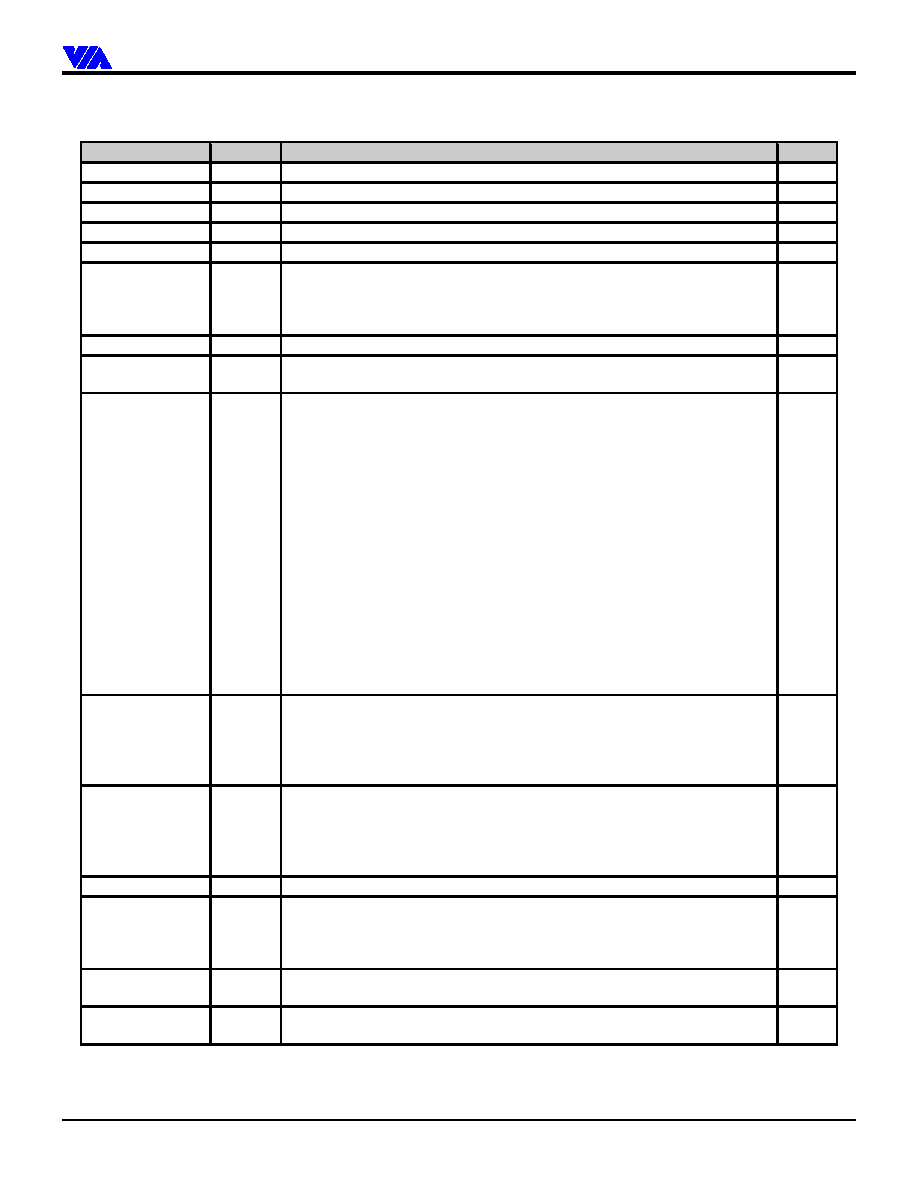

Revision History

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

R

EVISION

H

ISTORY

Document Release

Date

Revision

Initials

0.1

Initial internal release based on Apollo MVP3 specification & Porsche HRM

GH

0.2

Updated/corrected signal list; added power signal detail, corrected misc features

GH

0.3

Added FP description, AC/DC tables, pin placement diagram; Fixed misc typos

GH

0.4

7/298

Reconciled with target spec: changed pinouts & poweron config, added registers

EC

0.5

7/27/98

Changed pinout; added pin descriptions; changed p/n to VT82C501; reformatted

DH

0.6

8/21/98

Changed pinouts TVD[0-2], TVHS, TVCLK per 7/30/98 rev 1.1 ballout

Changed PD[9-11,13-14,18-19], TVD[0-2,6-7], VIDCLK per 8/13, 1.3 ballout

Changed name of REQ4# / GNT4# to REQX# / GNTX# to match VT82C231

Added VGA and Graphics Accelerator registers

DH

0.7

8/24/98

Added remaining Graphics Engine registers

DH

0.8

9/11/98

Changed pinouts to match internal pinout document revision 1.5:

HCLK, MCLKI, MCLKO, GNDA, VCC2A, MD16-28, MD50-60

DH

0.9

10/15/98

Updated Feature Bullets

Changed pins F1, G1, G3, N2, and N4 to "Reserved, Do Not Connect"

Changed ADS#, M/IO#, W/R#, D/C#, BE[7-0]# to inputs, BRDY# to output

Added descriptions to VLF1 and VLF2 pins

Changed VSUS2 and VSUS3 to VSUS and corrected description

Changed VCC2 definition to 2.5V

Updated Register Definitions:

- Device 0 Rx68[1-0] changed; Rx78[5] & Rx88[0] reserved; Rx79 added

- Device 1 Rx41[1] reserved, Rx42[2] changed

- Default values added to 3D8, GR5, E-F, 20-22, 24-28, 2A, 2C, 2F, SR8-9, B-

12, 18-1B, 20-21, 24, 37-38, 96-99, 9E, BE, CE, and CR0-18, 1A-1C, 20, 21,

25, 27-2F, 34-3C, 52, 55, 56, 5E, 5F, 62, & 63

- CR11[6] reserved, CR17[4] extended function added, SRC[6] note added,

SRD[3].new reserved, SRD[7-4].new redefined, SR12[7-4, 3-0] redefined,

SR16-17 removed, CR1A-1C redefined, CR28/2C/2E deleted, CR2A[3-2]

reserved, CR62[3-0] redefined

Updated Functional Descriptions: corrected DFP config & deleted test modes

DH

0.91

10/21/98

Changed power / ground pin names to match design guide

Replaced ENPVDD (F1) and ENPVEE (G1) required for DFP interface

Moved CKE functions from MECC to RAS4-5#, SRASC#, SCASC#

Fixed error in numerical pin list AD15-AD18

Updated block diagram

DH

0.92

11/4/98

Changed part # to VT8501, changed VT82C686 to 686A & VT82C596 to 596A

Updated register definitions: Device 0 Rx51[4], 52[3,1], 53[3-0], 59-58[15-13],

MA Mapping Table, 69[7], 6B[3-1], 6C[7,3], 6D[4], 70[5,0], 73[4], 74[4-0],

76[3-0], 78[2], 79[7-0], 88[2], AC[6-4,0], AD, F0-FF, Device 1 Rx41[0],

42[3-2]; Fixed Device 1 bus #

DH

1.0

12/9/98

Fixed typographical error in pin lists: VCC3 pin # was W7, should be W21

DH

1.1

6/1/99

Fixed miscellaneous typographical errors and updated feature bullets

Changed defaults for Device 0 RxAC and RxAD

Changed device 0 Rx6[6], 52[3], 69[1] (VGA Ena Guard Bit), 79[1-0], FB[7]

Added missing device 1 registers Rx43, 44, and 47-46

DH

1.2

10/8/99

Fixed Bus 0 Device 1 Rx7-6[13-12] changed from WC to RO

Fixed Bus 1 Device 0 Rx3-0 Vendor & Device ID

DH

1.3

2/1/00

Added DSTN panel tables in intro/overview; added note to Device 0 Rx78[6]

Updated document logos; fixed ambient/case temp specs

DH

VT8501 Apollo MVP4

Revision 1.3 February 1, 2000

-ii-

Table of Contents

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

T

ABLE OF

C

ONTENTS

REVISION HISTORY........................................................................................................................................................................I

TABLE OF CONTENTS .................................................................................................................................................................. II

LIST OF FIGURES..........................................................................................................................................................................IV

LIST OF TABLES ...........................................................................................................................................................................IV

APOLLO MVP4................................................................................................................................................................................. 1

SYSTEM OVERVIEW...................................................................................................................................................................... 6

A

POLLO

MVP4 C

ORE

L

OGIC

O

VERVIEW

.................................................................................................................................... 7

A

POLLO

MVP4 G

RAPHICS

C

ONTROLLER

O

VERVIEW

................................................................................................................ 8

Capability Overview ............................................................................................................................................................... 8

System Capabilities................................................................................................................................................................. 9

High Performance 64-bit 2D GUI.......................................................................................................................................... 9

Highly Integrated RAMDAC

TM

& Clock Synthesizer......................................................................................................... 9

Full Feature High Performance 3D Engine .......................................................................................................................... 9

Video Processor..................................................................................................................................................................... 10

Video Capture and DVD ...................................................................................................................................................... 10

Versatile Frame Buffer Interface ........................................................................................................................................ 10

Hi-Res and Hi-Ref Display Support .................................................................................................................................... 10

CRT Power Management (VESA DPMS) .......................................................................................................................... 11

Digital Flat Panel (DFP) Interface ...................................................................................................................................... 11

Video Capture Interface / ZV Port...................................................................................................................................... 11

Complete Hardware Compatibility ..................................................................................................................................... 11

PINOUTS .......................................................................................................................................................................................... 12

PIN DESCRIPTIONS ...................................................................................................................................................................... 15

REGISTERS ..................................................................................................................................................................................... 24

R

EGISTER

O

VERVIEW

................................................................................................................................................................. 24

M

ISCELLANEOUS

I/O................................................................................................................................................................... 34

C

ONFIGURATION

S

PACE

I/O ....................................................................................................................................................... 34

R

EGISTER

D

ESCRIPTIONS

............................................................................................................................................................ 35

Bus 0 Device 0 Header Registers - Host Bridge.................................................................................................................. 35

Device 0 Configuration Registers - Host Bridge ................................................................................................................ 37

Cache Control ....................................................................................................................................................................................... 37

DRAM Control ..................................................................................................................................................................................... 39

PCI Bus Control.................................................................................................................................................................................... 46

GART / Graphics Aperture Control ...................................................................................................................................................... 50

AGP Control ......................................................................................................................................................................................... 52

Bus 0 Device 1 Header Registers - PCI-to-PCI Bridge...................................................................................................... 54

Device 1 Configuration Registers - PCI-to-AGP Bridge ................................................................................................... 57

AGP Bus Control .................................................................................................................................................................................. 57

Bus 1 Device 0 - 2D / 3D Graphics Accelerator Registers ................................................................................................. 59

PCI Configuration Registers � Graphics Accelerator............................................................................................................................ 59

PCI Device-Specific Config Regs � Graphics Accelerator ................................................................................................................... 62

Graphics Accelerator PCI Bus Master Registers................................................................................................................................... 63

VGA Standard Registers - Introduction ................................................................................................................................................ 69

Capture / ZV Port Registers .................................................................................................................................................................. 70

DVD Registers ...................................................................................................................................................................................... 71

Attribute Controller Registers (AR) ...................................................................................................................................................... 74

VT8501 Apollo MVP4

Revision 1.3 February 1, 2000

-iii-

Table of Contents

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

VGA Status / Enable Registers ............................................................................................................................................................. 74

VGA Sequencer Registers (SR) ............................................................................................................................................................ 75

VGA RAMDAC Registers .................................................................................................................................................................... 75

VGA Graphics Controller Registers (GR)............................................................................................................................................. 76

VGA CRT Controller Registers (CR) .................................................................................................................................................. 77

Extended Registers � Non-Indexed I/O Ports ....................................................................................................................................... 78

Extended Registers � VGA Sequencer Indexed .................................................................................................................................... 79

Extended Registers � VGA Graphics Controller Indexed ..................................................................................................................... 89

Extended Registers � VGA CRT Controller Indexed............................................................................................................................ 95

Extended Registers � CRTC Shadow.................................................................................................................................................. 109

3D Graphics Engine Registers ........................................................................................................................................... 110

Operational Concept ........................................................................................................................................................................... 110

Drawing............................................................................................................................................................................................... 111

Geometry Primitives............................................................................................................................................................................ 112

Synchronization .................................................................................................................................................................................. 115

Functional Blocks ............................................................................................................................................................................... 115

Bus Interface ....................................................................................................................................................................................... 115

Span Engine......................................................................................................................................................................... 116

Graphics Engine Core ........................................................................................................................................................ 117

Graphics Engine Organization ............................................................................................................................................................ 120

Setup Engine Registers ....................................................................................................................................................................... 121

Vertex Registers .................................................................................................................................................................................. 122

Rasterization Engine Registers............................................................................................................................................................ 123

Pixel Engine Registers ........................................................................................................................................................................ 130

Texture Engine Registers .................................................................................................................................................................... 136

Memory Interface Registers ................................................................................................................................................................ 138

Data Port Area..................................................................................................................................................................................... 138

FUNCTIONAL DESCRIPTIONS ................................................................................................................................................ 139

S

YSTEM

C

ONFIGURATION

......................................................................................................................................................... 139

DFP Interface Configuration ............................................................................................................................................. 139

G

RAPHICS

C

ONTROLLER

P

OWER

M

ANAGEMENT

................................................................................................................... 140

Power Management States................................................................................................................................................. 140

Power Management Clock Control ................................................................................................................................... 140

Power Management Registers ........................................................................................................................................... 140

ELECTRICAL SPECIFICATIONS ............................................................................................................................................. 141

A

BSOLUTE

M

AXIMUM

R

ATINGS

............................................................................................................................................... 141

DC C

HARACTERISTICS

.............................................................................................................................................................. 141

AC T

IMING

S

PECIFICATIONS

.................................................................................................................................................... 141

MECHANICAL SPECIFICATIONS ........................................................................................................................................... 147