H

FRQQHFW

Z

97&

97&$7

$SROOR93

6LQJOH&KLS1RUWK%ULGJH

IRU3HQWLXP6RFNHW

ZLWK$*3DQG3&,

SOXV$GYDQFHG(&&0HPRU\&RQWUROOHU

VXSSRUWLQJ''56'5$0,,

6'5$0('2DQG)3*

5HYLVLRQ

2FWREHU

9,$7(&+12/2*,(6,1&

&RS\ULJKW1RWLFH

&RS\ULJKW

9,$ 7HFKQRORJLHV ,QFRUSRUDWHG 3ULQWHG LQ WKH 8QLWHG 6WDWHV $

//

5

,*+76

5

(6(59('

1R SDUW RI WKLV GRFXPHQW PD\ EH UHSURGXFHG WUDQVPLWWHG WUDQVFULEHG VWRUHG LQ D UHWULHYDO V\VWHP RU WUDQVODWHG LQWR

DQ\ ODQJXDJH LQ DQ\ IRUP RU E\ DQ\ PHDQV HOHFWURQLF PHFKDQLFDO PDJQHWLF RSWLFDO FKHPLFDO PDQXDO RU RWKHUZLVH

ZLWKRXW WKH SULRU ZULWWHQ SHUPLVVLRQ RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

97& 97&% DQG $SROOR 93 PD\ RQO\ EH XVHG WR LGHQWLI\ SURGXFWV RI 9,$ 7HFKQRORJLHV

36

%

LV D UHJLVWHUHG WUDGHPDUN RI ,QWHUQDWLRQDO %XVLQHVV 0DFKLQHV &RUS

3HQWLXP

%

3&

%

3&

%

DQG 00;

%

DUH UHJLVWHUHG WUDGHPDUNV RI ,QWHO &RUS

&\UL[

;

%

LV D UHJLVWHUHG WUDGHPDUN RI &\UL[ &RUS

$0'

.

%

$0'

.

%

$0'.

%

DQG $0'.

%

DUH UHJLVWHUHG WUDGHPDUNV RI $GYDQFHG 0LFUR 'HYLFHV &RUS

:LQGRZV

%

DQG 3OXJ DQG 3OD\

%

DUH UHJLVWHUHG WUDGHPDUNV RI 0LFURVRIW &RUS

3&,

%

LV D UHJLVWHUHG WUDGHPDUN RI WKH 3&, 6SHFLDO ,QWHUHVW *URXS

9(6$ LV D WUDGHPDUN RI WKH 9LGHR (OHFWURQLFV 6WDQGDUGV $VVRFLDWLRQ

$OO WUDGHPDUNV DUH WKH SURSHUWLHV RI WKHLU UHVSHFWLYH RZQHUV

'LVFODLPHU1RWLFH

1R OLFHQVH LV JUDQWHG LPSOLHG RU RWKHUZLVH XQGHU DQ\ SDWHQW RU SDWHQW ULJKWV RI 9,$ 7HFKQRORJLHV 9,$ 7HFKQRORJLHV

PDNHV QR ZDUUDQWLHV LPSOLHG RU RWKHUZLVH LQ UHJDUG WR WKLV GRFXPHQW DQG WR WKH SURGXFWV GHVFULEHG LQ WKLV GRFXPHQW

7KH LQIRUPDWLRQ SURYLGHG E\ WKLV GRFXPHQW LV EHOLHYHG WR EH DFFXUDWH DQG UHOLDEOH WR WKH SXEOLFDWLRQ GDWH RI WKLV

GRFXPHQW +RZHYHU 9,$ 7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU DQ\ HUURUV LQ WKLV GRFXPHQW )XUWKHUPRUH 9,$

7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU WKH XVH RU PLVXVH RI WKH LQIRUPDWLRQ LQ WKLV GRFXPHQW DQG IRU DQ\ SDWHQW

LQIULQJHPHQWV WKDW PD\ DULVH IURP WKH XVH RI WKLV GRFXPHQW 7KH LQIRUPDWLRQ DQG SURGXFW VSHFLILFDWLRQV ZLWKLQ WKLV

GRFXPHQW DUH VXEMHFW WR FKDQJH DW DQ\ WLPH ZLWKRXW QRWLFH DQG ZLWKRXW REOLJDWLRQ WR QRWLI\ DQ\ SHUVRQ RI VXFK FKDQJH

2IILFHV

86$ 2IILFH

7DLSHL 2IILFH

0LVVLRQ &RXUW

WK

)ORRU 1R

)UHPRQW &$

&KXQJ&KHQJ 5RDG +VLQ7LHQ

86$

7DLSHL 7DLZDQ 52&

7HO �

7HO �

)D[ �

)D[ �

2QOLQH6HUYLFHV

+RPH 3DJH

http://www.via.com.tw

7DLZDQ� RU

http://www.viatech.com

86$�

)73 6HUYHU

ftp.via.com.tw

7DLZDQ�

%%6

VT82C597 / VT82C597AT

Revision 1.0 October 3, 1997

-i-

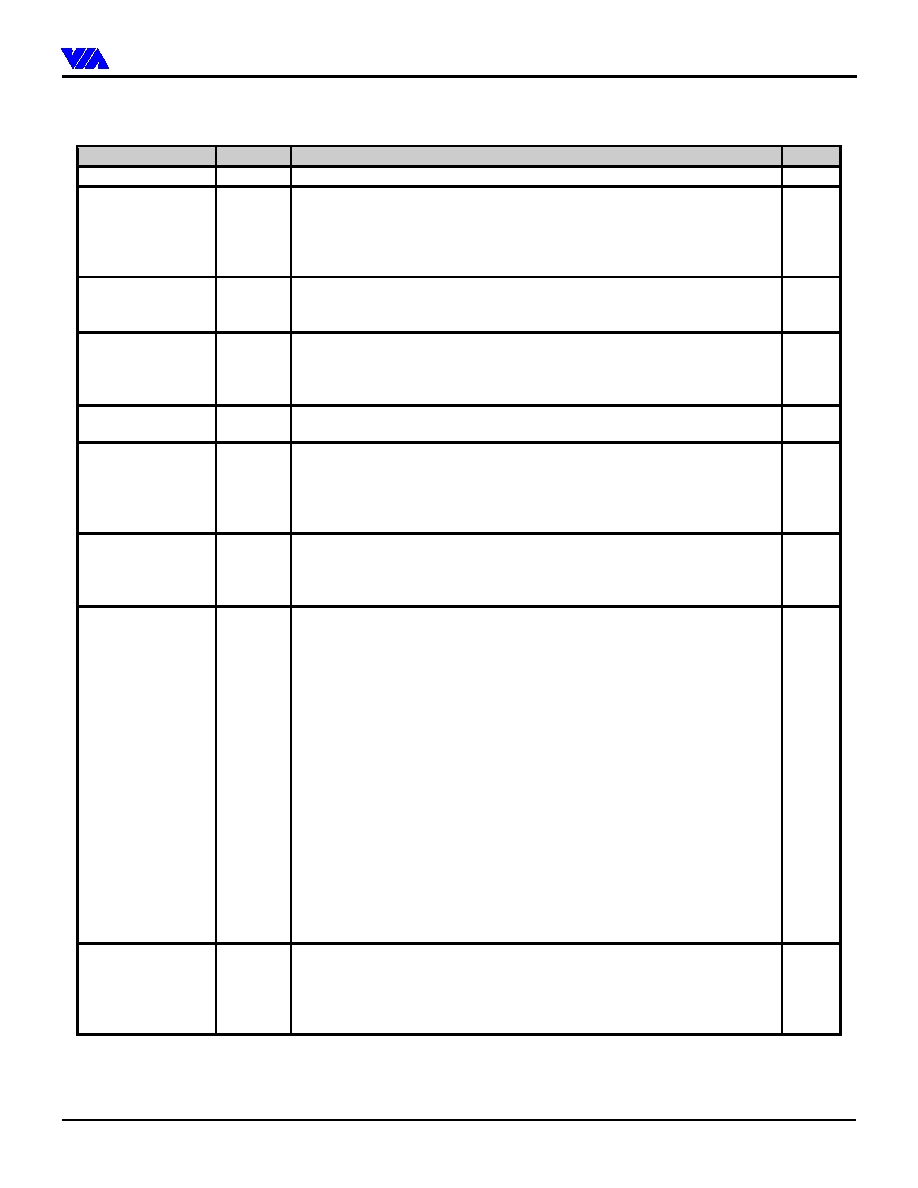

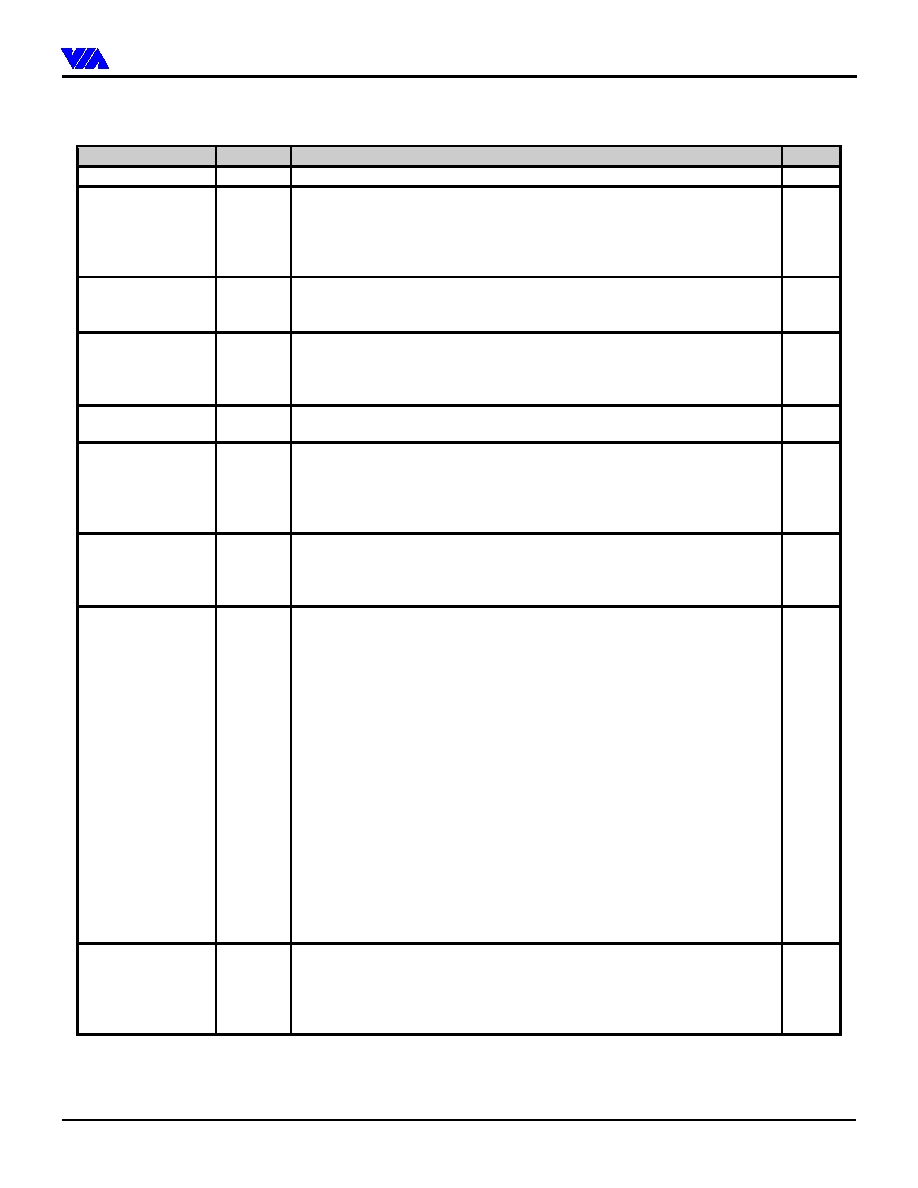

Revision History

7HFKQRORJLHV ,QF

:H &

:H &RRQQQQHFW

HFW

R

EVISION

H

ISTORY

Document Release

Date

Revision

Initials

0.1

3/28/97

Original release (VIA internal review only)

DH

0.2

4/1/97

Changed memory technologies supported to FP,EDO,SDRAM,SDRAM-II

Fixed Introduction and Feature bullets per engineering review

Rearranged registers to clarify that registers 50-8F are device 0

Added pin descriptions for DS[3:0], GGNT#, and clocks

Fixed miscellaneous register bit descriptions per engineering review

DH

0.3

4/29/97

Added 456-pin BGA Mechanical Specification drawing

Rearranged pin groupings and changed pinouts per PCB floorplanning

Updated register definitions to reflect internal spec Rev 0.5 (4/15/97)

DH

0.4

5/14/97

Updated pinouts to reflect final pinout after chip layout / pad placement

Updated Feature Bullets and Overview to reflect final chip design

Updated pin descriptions per engineering input and final chip design

Updated register descriptions per engineering input and final chip design

DH

0.5

5/15/97

Updated pinouts (MD, MPD, & CAS pin swaps). Per 5/15/97 engg spec

Added pin descriptions for GVREF, MVREF, AVCC, AGND

DH

0.6

5/21/97

Changed package from 456-pin to 472-pin BGA - updated mechanical spec

Updated pinouts: added 16 grounds in package center

Updated pinouts: changed 4 GND pins to CVCC (supply for internal logic)

Updated pinouts: changed 2 HVCC pins to MVCC

Updated pin descriptions for clock pins

DH

0.7

6/16/97

Removed "NDA Required" watermark (product announced at Computex)

Moved ground balls from M9-M10 to N9-N10 (fixed pinouts and mechanical)

Added central-DQ support (feature bullets and register bits)

Fixed typos (block diagram BGA ball count, and alpha pin list J18)

DH

0.8

9/22/97

Fixed feature bullets in AGP and memory controller sections

Fixed Pinouts & Pin Definitions:

597 pinout error: CAS1 swapped with CAS2; CAS5 swapped with CAS6

Added 82C597AT pinouts

Updated pin definitions and signal names (SBS#, ADS0-1#)

Removed COE2# and CCS2# functionality from TA8-9 (not implemented)

Added MWEA# and MWEB# function on SWEA# and SWEB#

Added AGP PCB layout notes

Changed AGP clock (GCLK) to grounded input (generated internally)

Fixed Register Descriptions:

Added Chip Revision info to Device 0 Rx08

Fixed typos in Device 0 Rx10, Rx58, and RxAC

Updated bit definitions in Device 0 Rx64, 68, 6C, 70, 71, 76, 80, 88, and AC

Added Device 0 Rx6B DRAM Arbitration Control

Added Device 0 Rx74 PCI Master Control 2

Added Device 0 Rx77 Chip Test, Rx7E DLL/DLL4 Test, Rx7F DLL4 Test

Added Device 1 Rx3E PCI-to-PCI Bridge Control

Updated bit definitions in Device 1 Rx40 and 42

Added Electrical Specifications & Timing Diagrams

DH

1.0

10/3/97

Timing Diagrams redrawn to reduce final PDF file size

Timing Specification AC Timing numbers rounded to one decimal place

Timing Specification AC Timing Table 8 numbers updated

Changed name of ADS[1-0]# to GDS[1-0]# reduce confusion with ADS#

Added new VIA logos and removed "Preliminary" from document revision

DH

VT82C597 / VT82C597AT

Revision 1.0 October 3, 1997

-ii-

Table of Contents

7HFKQRORJLHV ,QF

:H &

:H &RRQQQQHFW

HFW

T

ABLE OF

C

ONTENTS

REVISION HISTORY........................................................................................................................................................................I

TABLE OF CONTENTS .................................................................................................................................................................. II

LIST OF FIGURES..........................................................................................................................................................................III

LIST OF TABLES ...........................................................................................................................................................................IV

OVERVIEW ....................................................................................................................................................................................... 4

PINOUTS ............................................................................................................................................................................................ 5

PINOUTS ............................................................................................................................................................................................ 8

REGISTERS ..................................................................................................................................................................................... 19

R

EGISTER

O

VERVIEW

................................................................................................................................................................. 19

C

ONFIGURATION

S

PACE

I/O ....................................................................................................................................................... 20

R

EGISTER

D

ESCRIPTIONS

............................................................................................................................................................ 21

Device 0 Header Registers - Host Bridge ............................................................................................................................ 21

Device 0 Configuration Registers - Host Bridge ................................................................................................................ 23

Cache Control ....................................................................................................................................................................................... 23

DRAM Control ..................................................................................................................................................................................... 25

PCI Bus #1 Control............................................................................................................................................................................... 30

GART / Graphics Aperture Control ...................................................................................................................................................... 33

AGP Control ......................................................................................................................................................................................... 35

Device 1 Header Registers - PCI-to-PCI Bridge ................................................................................................................ 36

Device 1 Configuration Registers - PCI-to-PCI Bridge..................................................................................................... 38

PCI Bus #2 Control............................................................................................................................................................................... 38

ELECTRICAL SPECIFICATIONS ............................................................................................................................................... 39

A

BSOLUTE

M

AXIMUM

R

ATINGS

................................................................................................................................................. 39

DC C

HARACTERISTICS

................................................................................................................................................................ 39

AC T

IMING

S

PECIFICATIONS

...................................................................................................................................................... 39

MECHANICAL SPECIFICATIONS ............................................................................................................................................. 74

VT82C597 / VT82C597AT

Revision 1.0 October 3, 1997

-iii-

List of Figures

7HFKQRORJLHV ,QF

:H &

:H &RRQQQQHFW

HFW

L

IST OF

F

IGURES

FIGURE 1. APOLLO VP3 SYSTEM BLOCK DIAGRAM.......................................................................................................... 4

FIGURE 2. VT82C597 BALL DIAGRAM (TOP VIEW).............................................................................................................. 5

FIGURE 3. VT82C597 PIN LIST (NUMERICAL ORDER) ........................................................................................................ 6

FIGURE 4. VT82C597 PIN LIST (ALPHABETICAL ORDER).................................................................................................. 7

FIGURE 5. VT82C597AT BALL DIAGRAM (TOP VIEW) ........................................................................................................ 8

FIGURE 6. VT82C597AT PIN LIST (NUMERICAL ORDER)................................................................................................... 9

FIGURE 7. VT82C597AT PIN LIST (ALPHABETICAL ORDER) .......................................................................................... 10

FIGURE 8. GRAPHICS APERTURE ADDRESS TRANSLATION ......................................................................................... 33

FIGURE 6. AGP MEMORY ACCESS (LPR).............................................................................................................................. 45

FIGURE 7. 2-BANK PBSRAM READ 3111-2111 ....................................................................................................................... 46

FIGURE 8. PCI-66 CONFIGURATION CYCLE........................................................................................................................ 47

FIGURE 9. AGP READ SDRAM (2L) 1X PIPE MODE............................................................................................................. 48

FIGURE 10. AGP READ EDO 1X PIPE MODE......................................................................................................................... 49

FIGURE 11. AGP READ EDO PIPE 2X MODE......................................................................................................................... 50

FIGURE 12. AGP SIDEBAND ADDRESS 2X WRITE SDRAM ............................................................................................... 51

FIGURE 13. AGP SIDEBAND ADDRESS 2X READ SDRAM (2L) ......................................................................................... 52

FIGURE 14. AGP SIDEBAND ADDRESS 1X READ SDRAM (2L) ......................................................................................... 53

FIGURE 15. AGP SIDEBAND ADDRESS 1X WRITE SDRAM ............................................................................................... 54

FIGURE 16. POST WRITE 3111, EDO DRAM 2222 ................................................................................................................. 55

FIGURE 17. PIPELINE READ EDO DRAM 6222, 3222 ........................................................................................................... 56

FIGURE 18. CPU WRITE HIT SRAM 3111................................................................................................................................ 57

FIGURE 19. CPU READ HIT SRAM 3111 .................................................................................................................................. 58

FIGURE 20. CPU READ MISS FILL SYNCHRONOUS SRAM .............................................................................................. 59

FIGURE 21. CPU WRITE PCI SLAVE WRITE BUFFER ON FAST BACK-TO-BACK...................................................... 60

FIGURE 22. CPU READ PCI SLAVE .......................................................................................................................................... 61

FIGURE 23. PCI MASTER READ L1 SNOOP TO DRAM ....................................................................................................... 62

FIGURE 24. PCI MASTER READ HIT L2 ................................................................................................................................. 63

FIGURE 25. PCI MASTER READ L1 SNOOP TO L2............................................................................................................... 64

FIGURE 26. SDRAM READ CYCLE (BANK INTERLEAVE, CAS LATENCY 3) ............................................................... 65

FIGURE 27. SDRAM WRITE CYCLE (BANK INTERLEAVE) .............................................................................................. 66

FIGURE 28. PCI MASTER READ HIT DRAM.......................................................................................................................... 67

FIGURE 29. PCI MASTER WRITE DRAM ............................................................................................................................... 68

FIGURE 30. PCI MASTER WRITE HIT L1 SNOOP TO DRAM ............................................................................................ 69

FIGURE 31. PCI MASTER WRITE HIT L2 ............................................................................................................................... 70

FIGURE 32. PCI MASTER WRITE HIT L2, L1 HITM ............................................................................................................ 71

FIGURE 33. PCI MASTER WRITE HIT L2 & DIRTY ............................................................................................................. 72

FIGURE 34. CPU READ MISS DIRTY L2 WRITE BACK FILL............................................................................................. 73

FIGURE 39. MECHANICAL SPECIFICATIONS - 472-PIN BALL GRID ARRAY PACKAGE ......................................... 74