Document:1G5-0126

Rev.1

Page 1

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Description

The device is CMOS Dynamic RAM organized as 4,194,304 words x 4 bits. It is fabricated with an

advanced submicron CMOS technology and designed to operate from a single 5V only or 3.3V only power

supply. Low voltage operation is more suitable to be used on battery backup, portable electronic application.

A new refresh feature called " self-refresh " is supported and very slow CBR cycles are being performed. It is

packaged in JEDEC standard 26/24 - pin plastic SOJ or TSOP (II).

Features

∑ Single 5V (

%) or 3.3V (

%) only power supply

∑ High speed t

RAC

access time : 50/60 ns

∑ Low power dissipation

- Active mode : 5V version 605/550 mW (Max.)

3.3V version 396/360 mW (Max.)

- Standby mode : 5V version 1.375 mW (Max.)

3.3V version 0.54 mW (Max.)

∑ Fast Page Mode access

∑ I/O level : TTL compatible (Vcc = 5V)

LVTTL compatible (Vcc = 3.3V)

∑ 2048 refresh cycles in 32 ms (Std) or 128ms (S - version)

∑ 4 refresh mode :

- RAS only refresh

- CAS-before-RAS refresh

- Hidden refresh

- Self - refresh (S - version)

10

±

10

±

Document:1G5-0126

Rev.1

Page 2

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Pin Description

Pin Name

Function

A0 - A10

Address inputs

- Row address A0 - A10

- Column address A0 - A10

- Refresh address A0 - A10

DQ1 ~ DQ4

Data - in/data - out

RAS

Row address strobe

CAS

Column address strobe

WE

Write enable

OE

Output enable

V

cc

Power (+ 5V or + 3.3V)

V

ss

Ground

V

G

2

6

(

v

)

(

S

)

1

7

4

0

0

D

J

DQ1

WE

V

SS

DQ4

A

2

A

3

V

CC

A

0

A

1

A

10

V

CC

A

8

A

7

A

6

A

5

A

4

V

SS

1

2

3

4

5

6

CAS

OE

A

9

26

25

24

23

22

21

8

9

10

11

12

13

19

18

17

16

15

14

RAS

DQ3

NC

DQ2

V

G

2

6

(

v

)

(

S

)

1

7

4

0

0

D

J

DQ1

WE

V

SS

DQ4

A

2

A

3

V

CC

A

0

A

1

A

10

V

CC

A

8

A

7

A

6

A

5

A

4

V

SS

1

2

3

4

5

6

CAS

OE

A

9

26

25

24

23

22

21

8

9

10

11

12

13

19

18

17

16

15

14

RAS

DQ3

NC

DQ2

Pin configuration

26/24 - PIN 300mil Plastic TSOP (II)

Pin configuration

26/24 - PIN 300mil Plastic SOP

Document:1G5-0126

Rev.1

Page 3

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

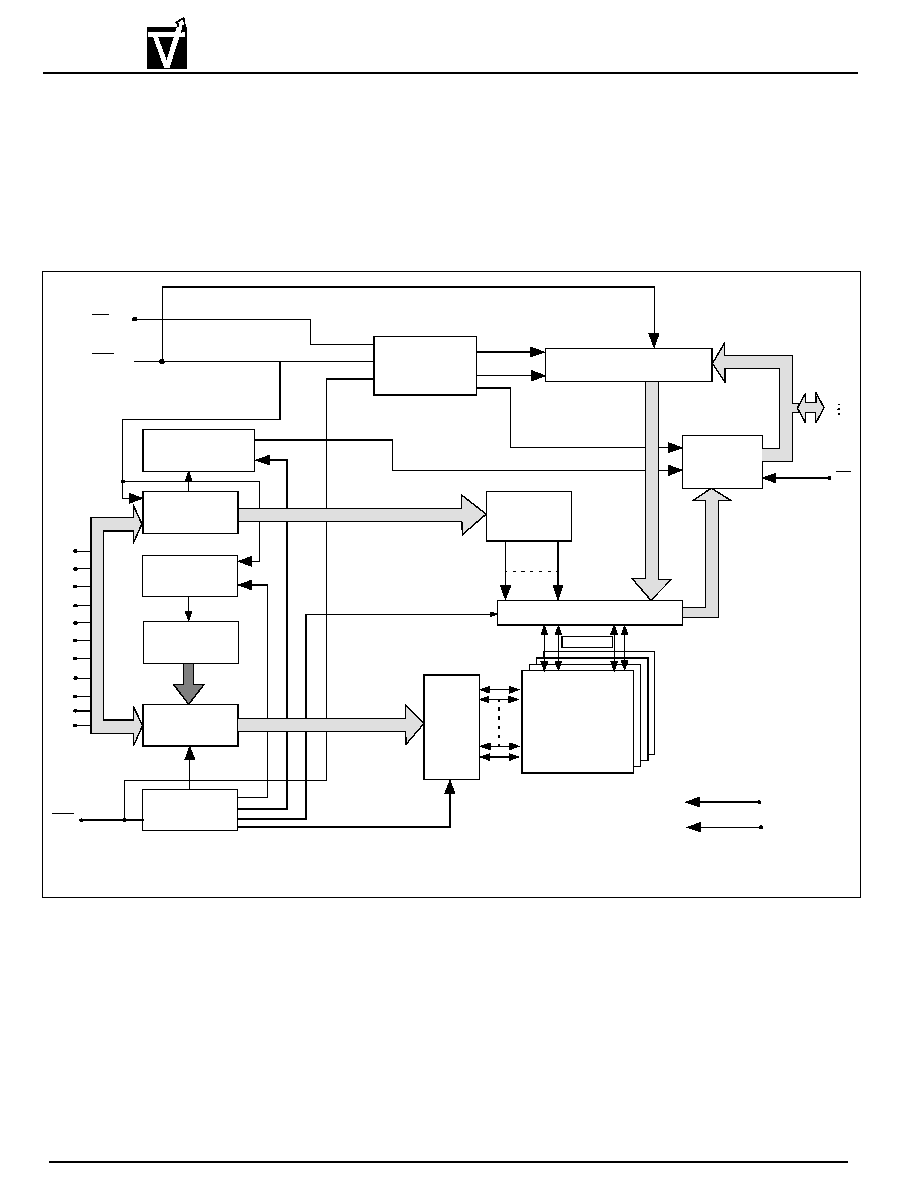

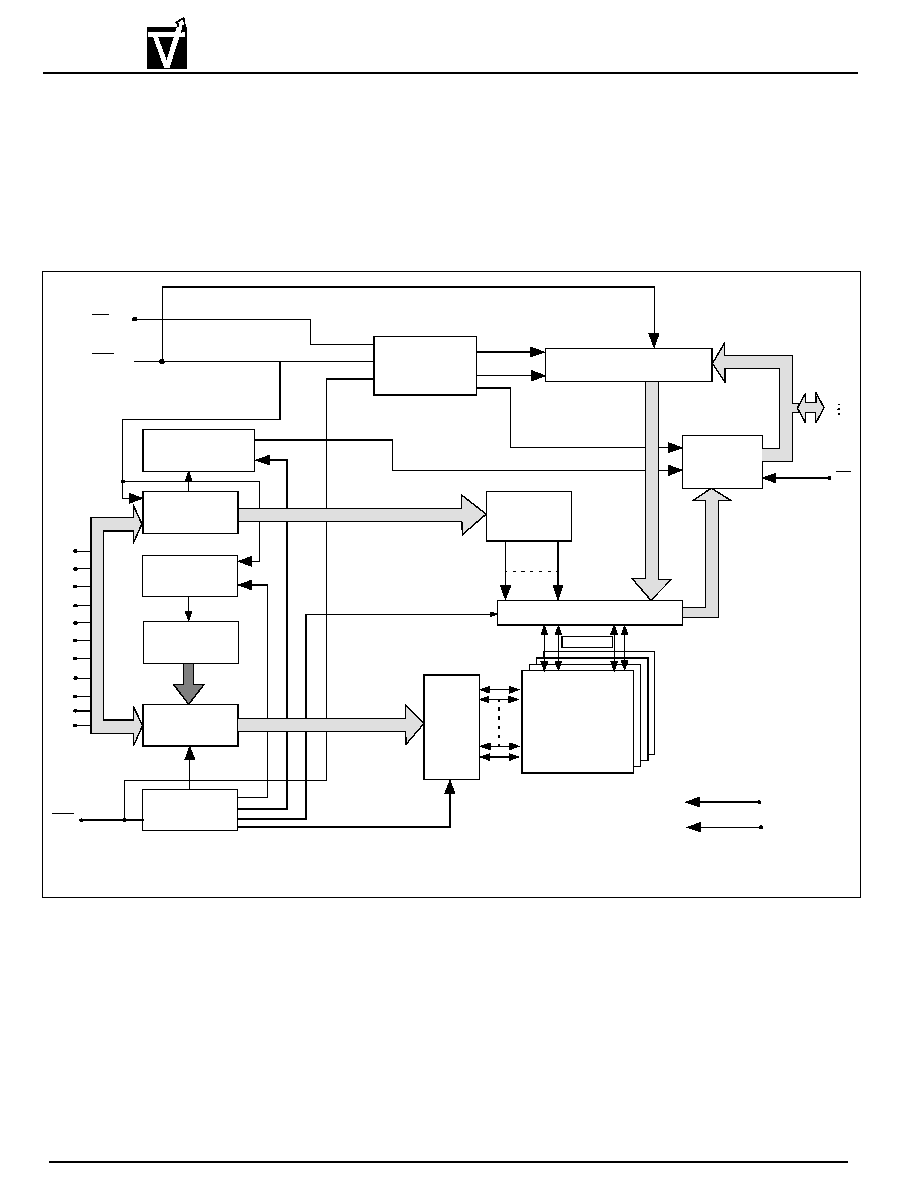

WE

GENERATOR

COLUMN-

ADDRESS

BUFFERS (11)

REFRESH

CONTROLLER

REFRESH

COUNTER

BUFFERS (11)

ADDRESS

ROW

NO. 1 CLOCK

GENERATOR

A0

RAS

A1

A2

A3

A4

A5

A6

A7

A8

CONTROL

LOGIC

DATA - IN BUFFER

DATA - OUT

BUFFER

OE

DQ1

DQ4

COLUMN

DECODER

2048

SENSE AMPLIFIERS

I/O GATING

2048 x 4

2048 x 2048 x 4

MEMORY

ARRAY

2

0

4

8

R

O

W

D

E

C

O

D

E

R

Vcc

Vss

Block Diagram

CAS

A9

A10

NO. 2 CLOCK

Document:1G5-0126

Rev.1

Page 4

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

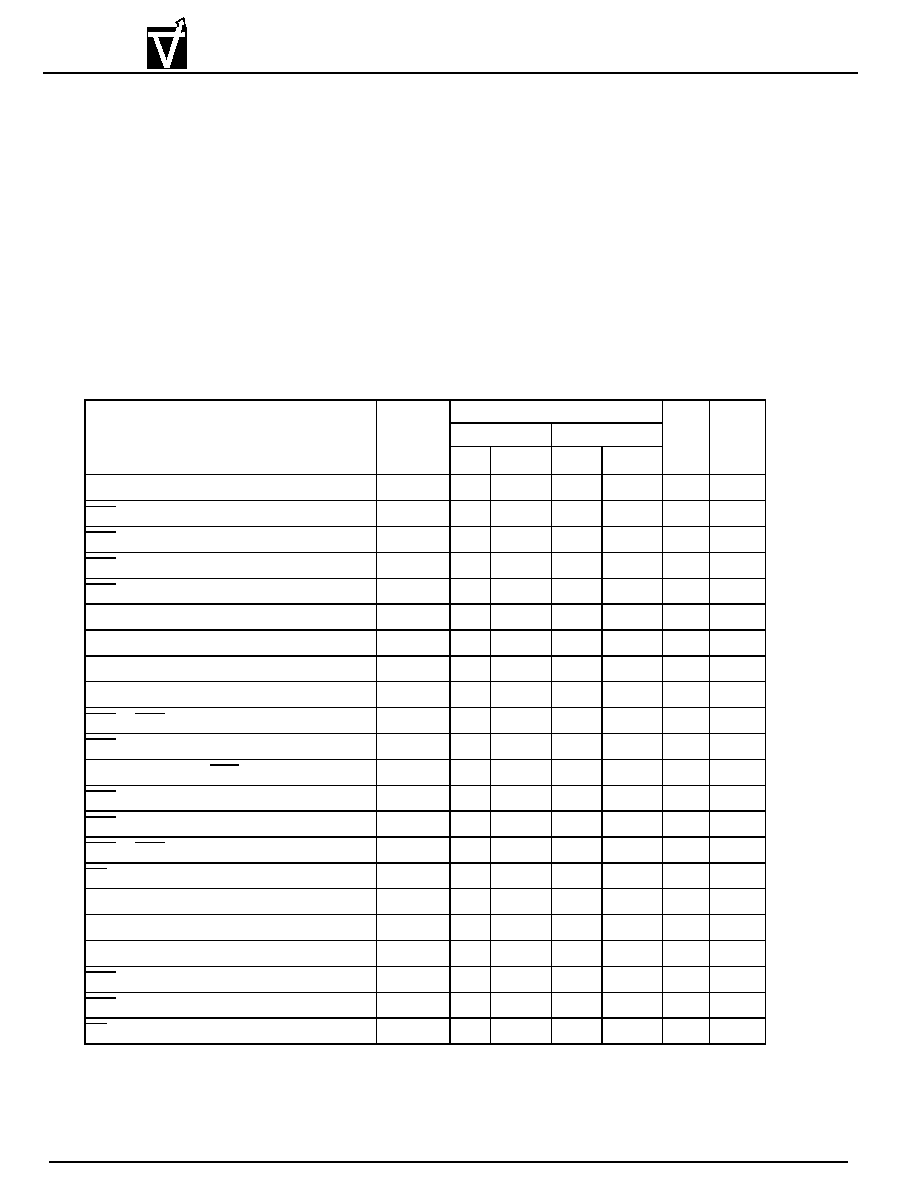

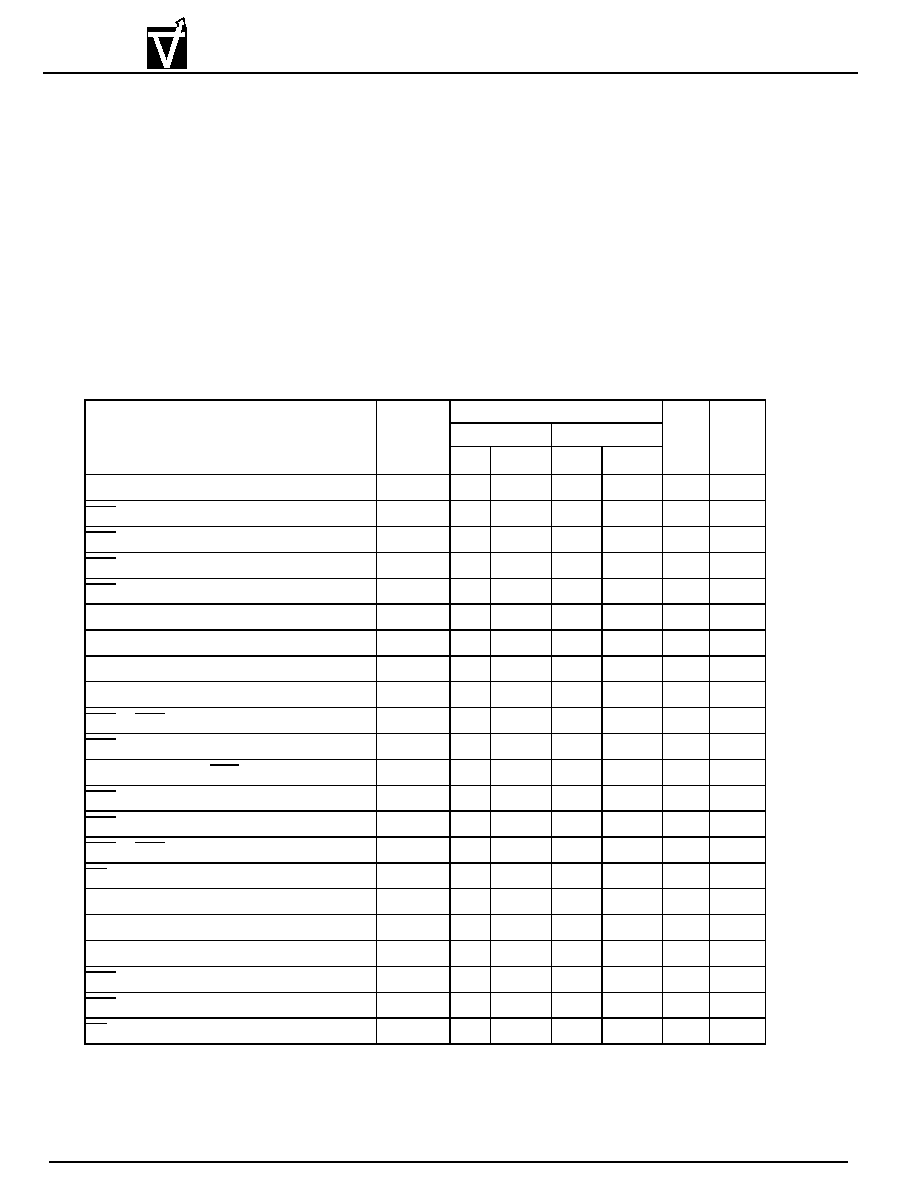

Truth Table

Notes : 1. EARLY WRITE only.

FUNCTION

RAS

CAS

WE

OE

ADDRESSES

DQ

S

Notes

ROW

COL

STANDBY

H

X

X

X

X

High - Z

READ

L

L

H

L

ROW

COL Data - Out

WRITE : (EARLY

WRITE)

L

L

L

X

ROW

COL Data - In

READ WRITE

L

L

ROW

COL Data - Out, Data - In

PAGE -

MODE READ

1st Cycle

L

H

L

ROW

COL Data - Out

2st

Cycle

L

H

L

n/a

COL Data - Out

PAGE -

MODE WRITE

1st Cycle

L

L

X

ROW

COL Data - In

2st

Cycle

L

L

X

n/a

COL Data - In

PAGE - MODE

READ - WRITE

1st Cycle

L

ROW

COL Data - Out, Data - In

2st

Cycle

L

n/a

COL Data - Out, Data - In

HIDDEN

REFRESH

READ

L

H

L

ROW

COL Data - Out

WRITE

L

L

X

ROW

COL Data - In

1

RAS - ONLY REFRESH

L

H

X

X

ROW

n/a

High - Z

CBR REFRESH

L

H

X

X

X

High - Z

H

X

H

L

L

H

H

L

H

L

H

L

H

L

H

L

H

L

L

H

H

L

H

L

L

H

L

H

L

L

H

L

H

L

Document:1G5-0126

Rev.1

Page 5

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

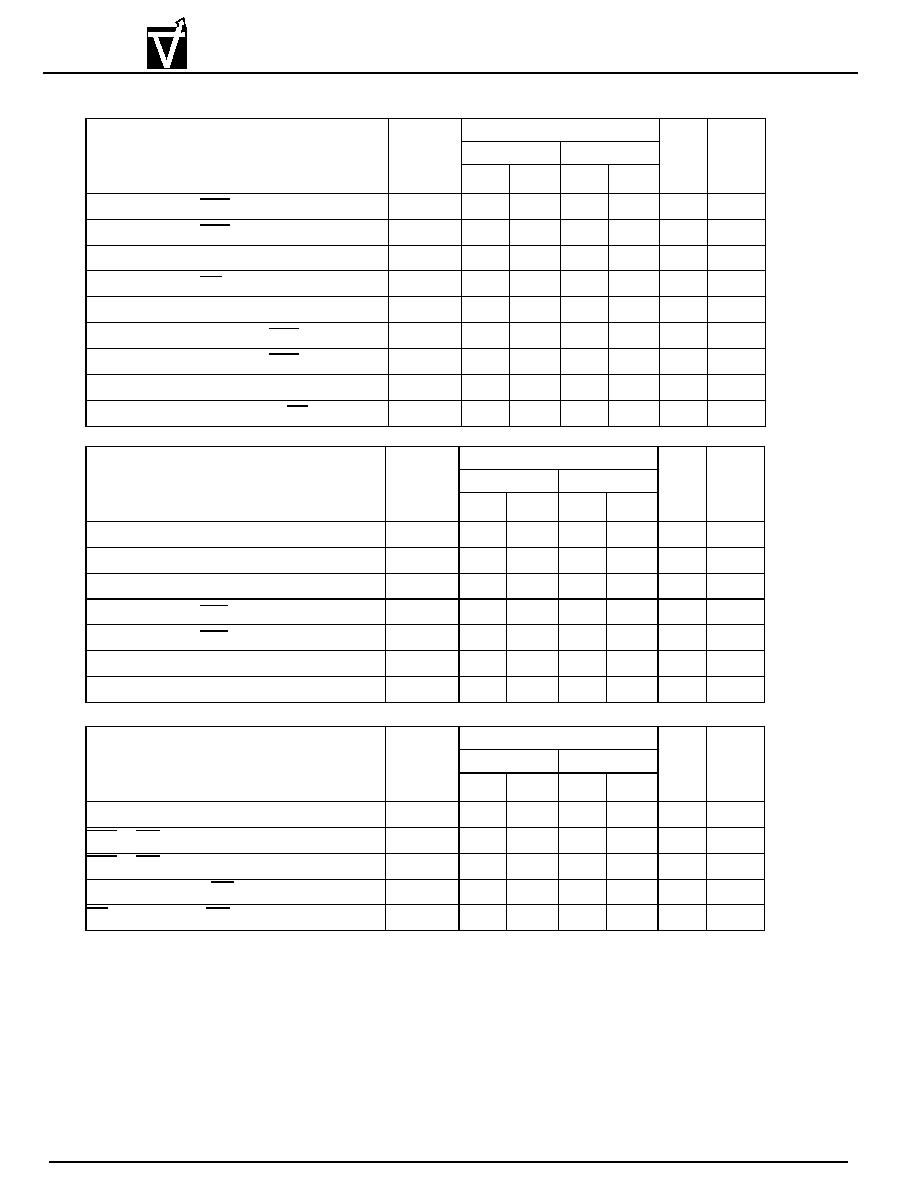

Absolute Maximum Rating

Recommended DC Operating Conditions

Capacitance

Ta = 25∞C, V

CC

= % or %, f = 1MHz

Note : 1. Capacitance measured with effective capacitance measuring method.

2. CAS = V

IH

to disable Dout.

Parameter

Symbol

Value

Unit

Voltage on any pin relative to Vss 5V

3.3V

V

T

-1.0 to + 7.0

-0.5 to + 4.6

V

Supply voltage relative to Vss 5V

3.3V

V

cc

-1.0 to + 7.0

-0.5 to + 4.6

V

Short circuit output current

I

OUT

50

mA

Power dissipation

P

D

1.0

W

Operating temperature

T

OPT

0 to + 70

∞C

Storage temperature

T

STG

-55 to + 125

∞C

Parameter/Condition

Symbol

5 Volt Version

3.3 Volt Version

Unit

Min

Typ

Max

Min

Typ

Max

Supply Voltage

V

cc

4.5

5.0

5.5

3.0

3.3

3.6

V

Input High Voltage, all inputs

V

IH

2.4

-

V

CC

+ 1.0

2.0

-

V

CC

+ 0.3

V

Input Low Voltage, all inputs

V

IL

-1.0

-

0.8

-0.3

-

0.8

V

Parameter

Symbol

Typ

Max

Unit

Note

Input capacitance (Address)

C

l1

-

5

pF

1

Input capacitance

(RAS, CAS, OE, WE)

C

l2

-

7

pF

1

Output capacitance

(Data - in, Data - out)

C

I/O

-

7

pF

1,2

5V 10

±

3.3V 10

±

Document:1G5-0126

Rev.1

Page 6

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

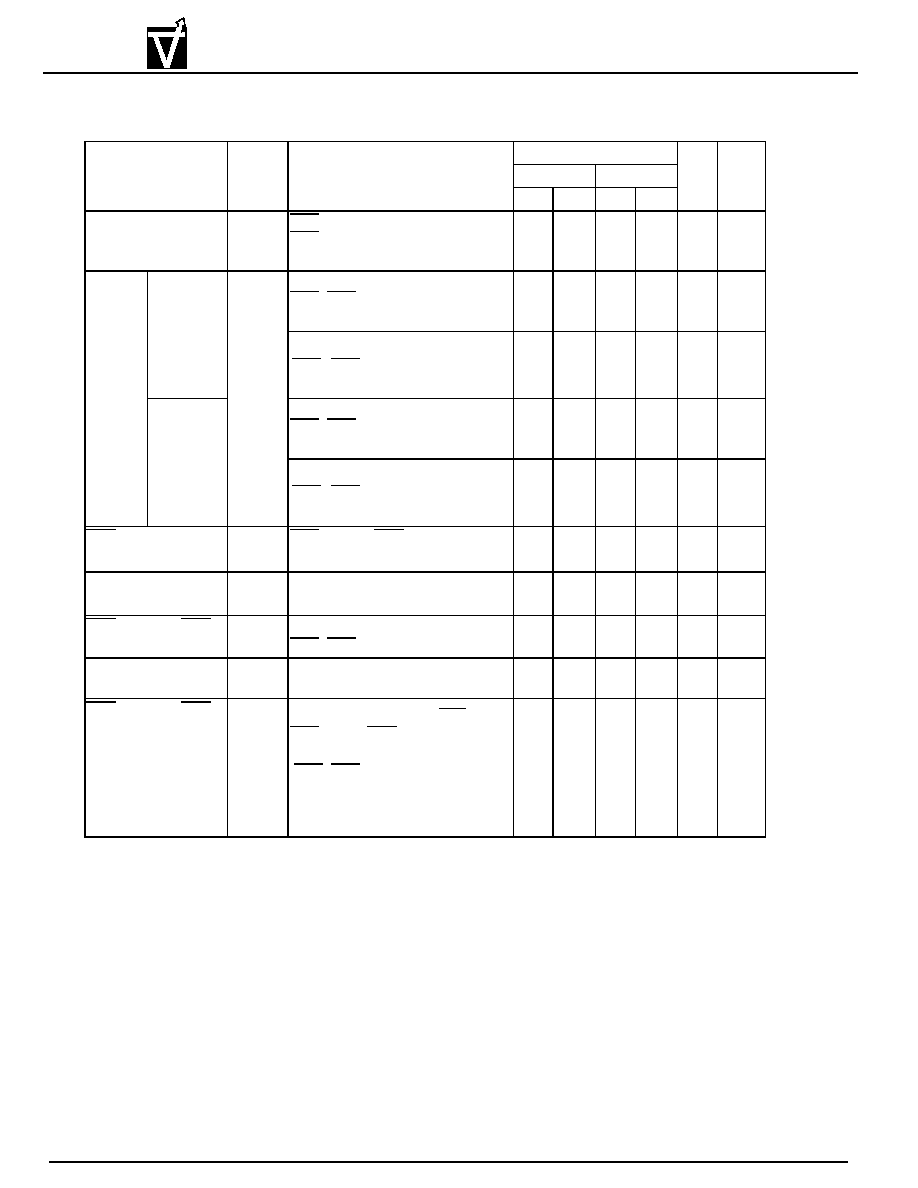

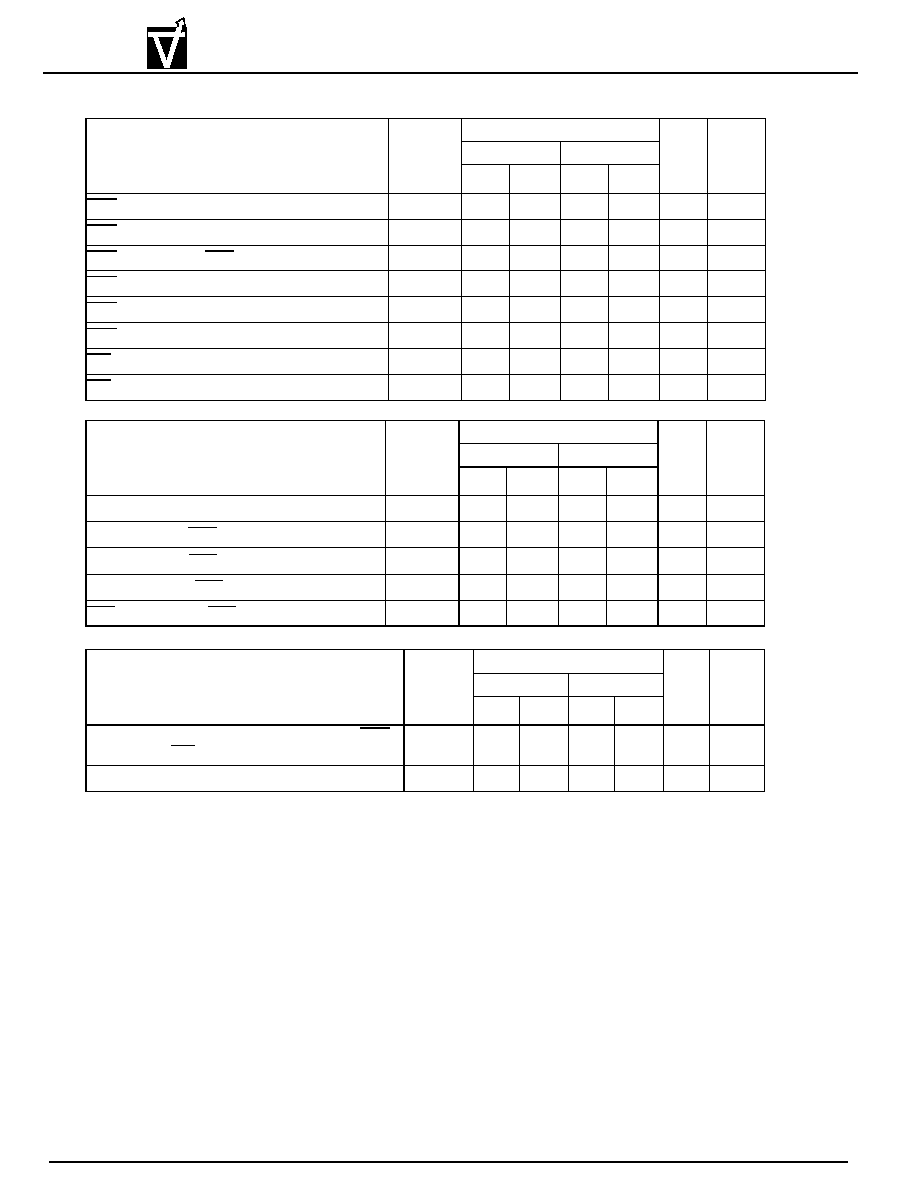

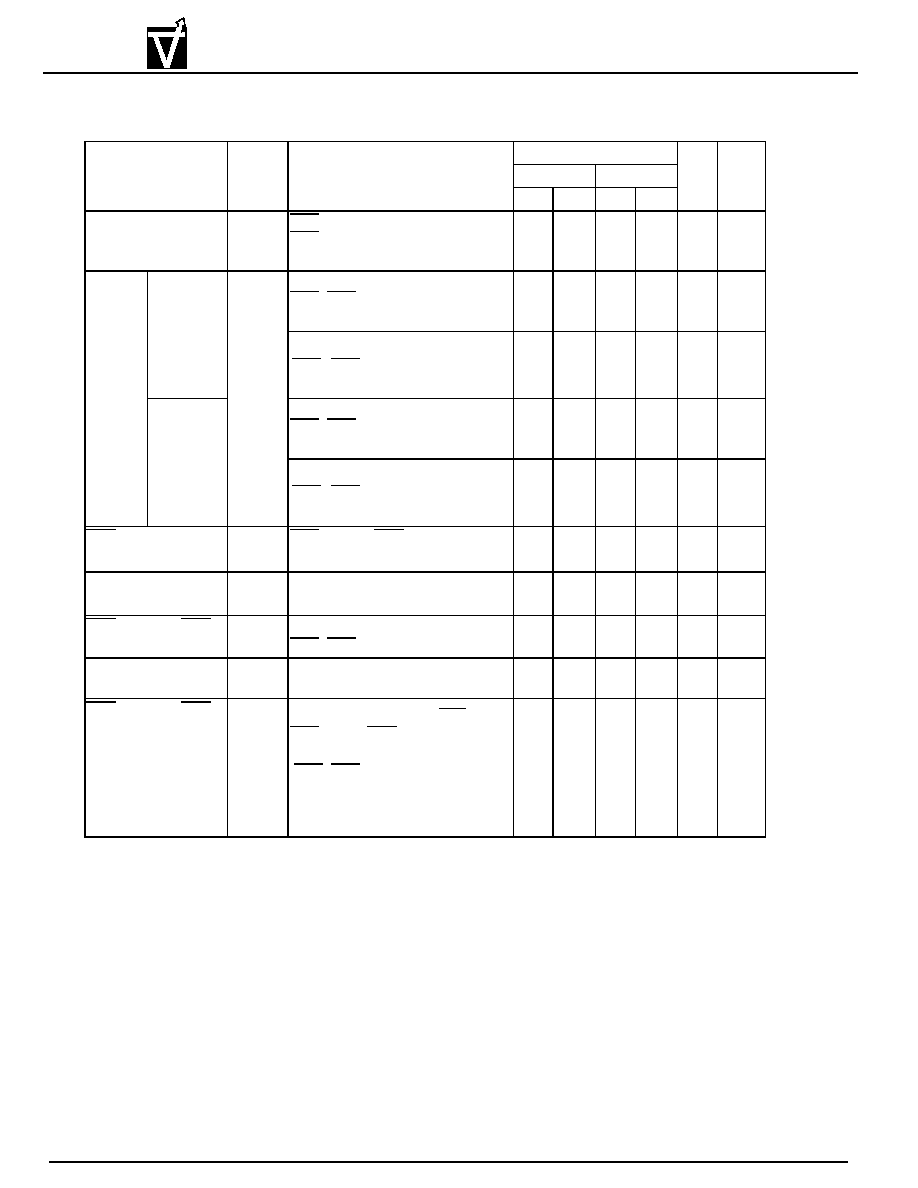

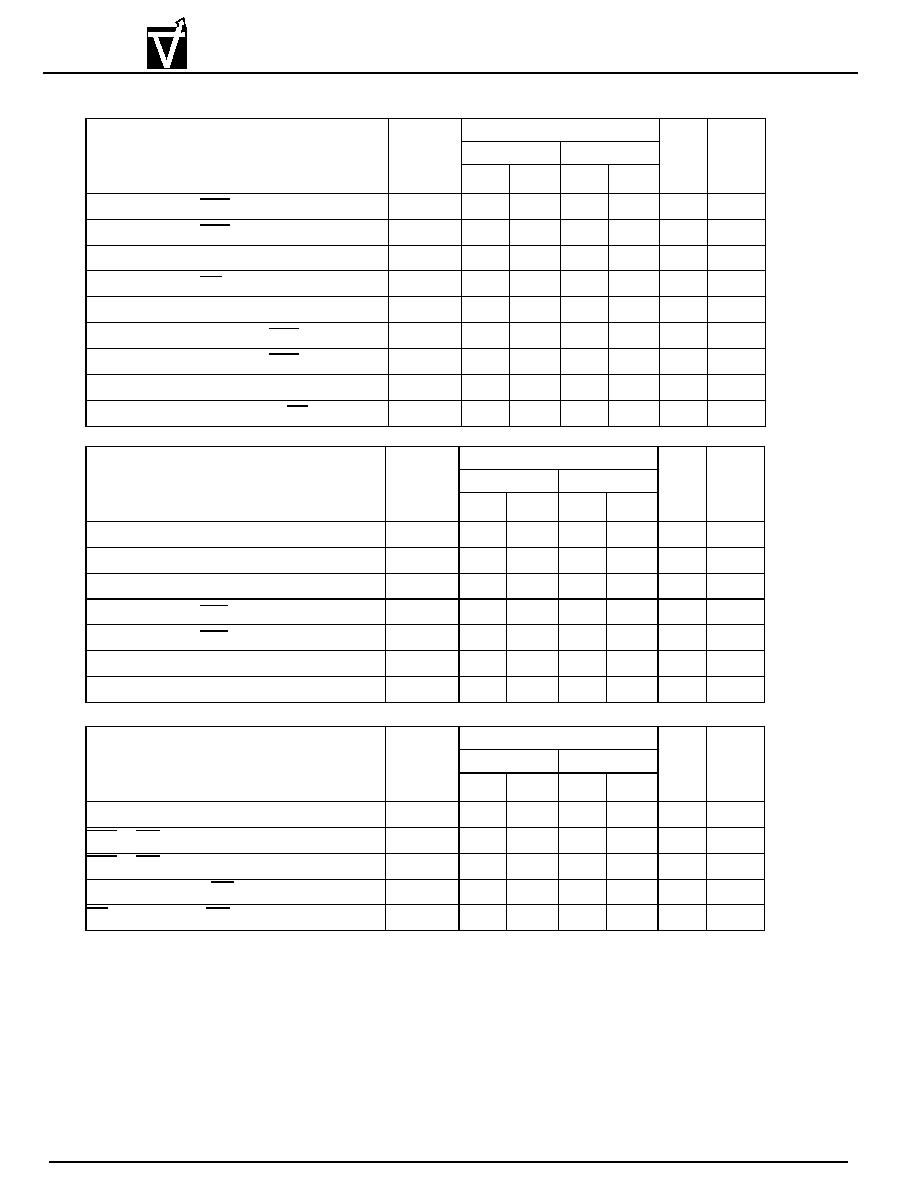

DC Characteristics; 5 - Volt verion

(T

a

= 0 to 70∞C, V

CC

= + 5V 10%, V

ss

= 0V)

Parameter

Symbol

Test Conditions

VG26 (V) (S) 17400D

Unit Notes

-5

-6

Min

Max

Min

Max

Operating

current

I

CC1

RAS cycling

CAS cycling

t

RC

= min.

-

110

-

100 mA

1, 2

Standby

Current

Low

power

S - version

I

CC2

TTL interface

RAS, CAS = V

IH

Dout = high - Z

-

2

-

2

mA

CMOS interface

- 0.2V

Dout = high - Z

-

0.25

-

0.25

mA

Standard

power

version

TTL interface

RAS, CAS = V

IH

Dout = high - Z

-

2

-

2

mA

CMOS interface

- 0.2V

Dout = high - Z

-

1

-

1

mA

RAS - only

refresh current

I

CC3

RAS cycling, CAS = V

IH

t

RC

= min.

-

110

-

100

mA

1, 2

Fast page mode

current

I

CC4

t

PC

= min.

-

80

-

70

mA

1,3

CAS - before - RAS

refresh current

I

CC5

t

RC

= min.

RAS, CAS cycling

-

110

-

100

mA

1, 2

Self - refresh currant

(S - Version)

I

CC8

-

350

-

350

CAS - before - RAS

long refresh

current (S - Version)

I

CC9

Standby : V

CC

-

CAS before RAS refresh :

2048 cycles/128ms

RAS, RAS :

V

CC

- (Max)

Dout = high - Z,

-

500

-

500

±

RAS CAS

,

V

CC

RAS CAS

,

V

CC

t

RASS

100

µ

S

µ

A

0.2V

RAS

0V

V

IL

0.2V

0.2V

V

IH

V

IH

t

RAS

300ns

µ

A

Document:1G5-0126

Rev.1

Page 7

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

DC Characteristics ; 5 - Volt Version (cont.)

(T

a

= 0 to 70∞C, V

CC

= + 5V 10%, V

ss

= 0V)

Notes :

1. l

CC

is specified as an average current. It depends on output loading condition and cycle rate when

the device is selected. l

CC

max is specified at the output open condition.

2. Address can be changed once or less while RAS = V

IL

.

3. For l

CC4

, address can be changed once or less within one Fast page mode cycle time.

Parameter

Symbol

Test Conditions

VG26 (V) (S) 17400D

Unit Notes

-5

-6

Min

Max

Min

Max

lnput leakage

current

I

LI

+ 0.5V

-5

5

-5

5

Output leakage

current

I

LO

+ 0.5V

Dout = Disable

-5

5

-5

5

Output high

voltage

V

OH

l

OH

= -5mA

2.4

-

2.4

-

V

Output low

voltage

V

OL

l

OL

= + 4.2mA

-

0.4

-

0.4

V

±

0V

Vin

V

CC

µ

A

0V

Vout

V

C C

µ

A

Document:1G5-0126

Rev.1

Page 8

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

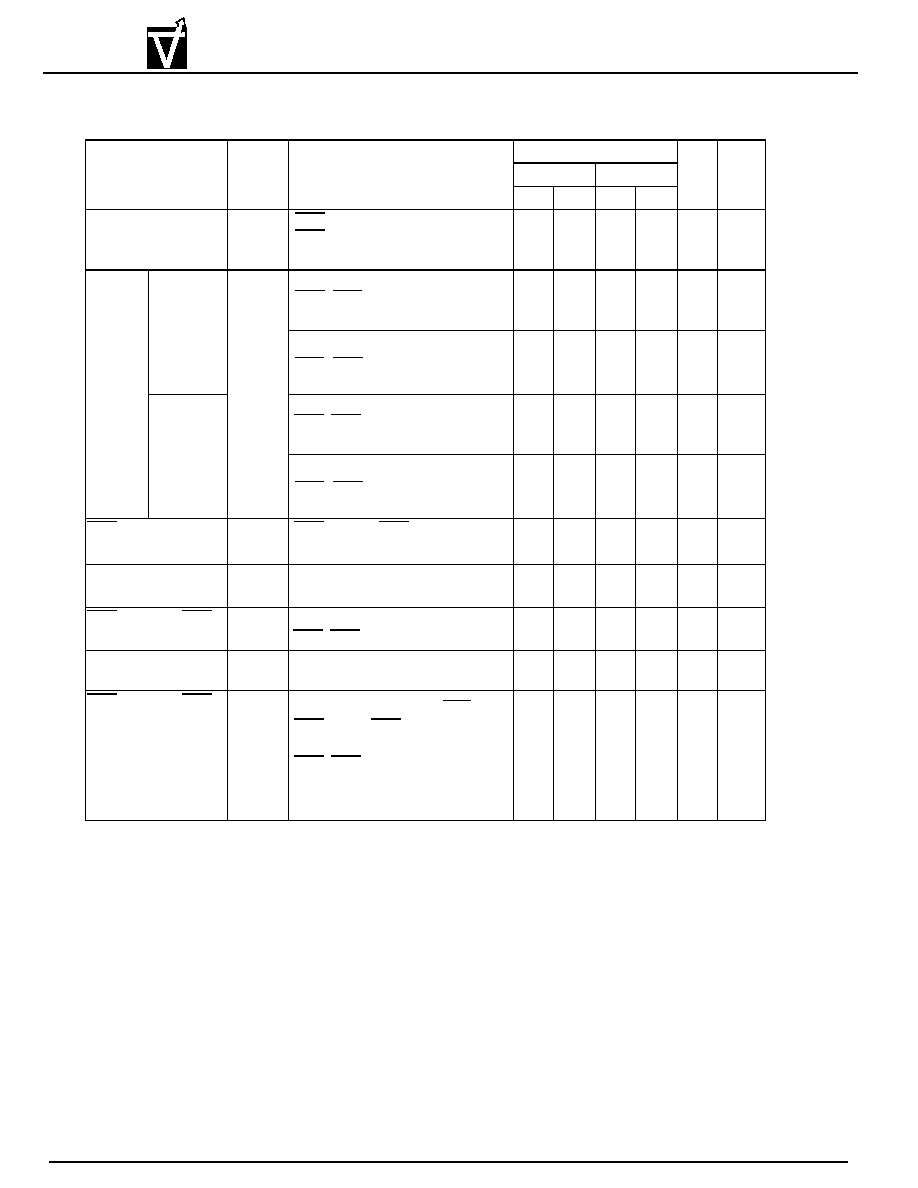

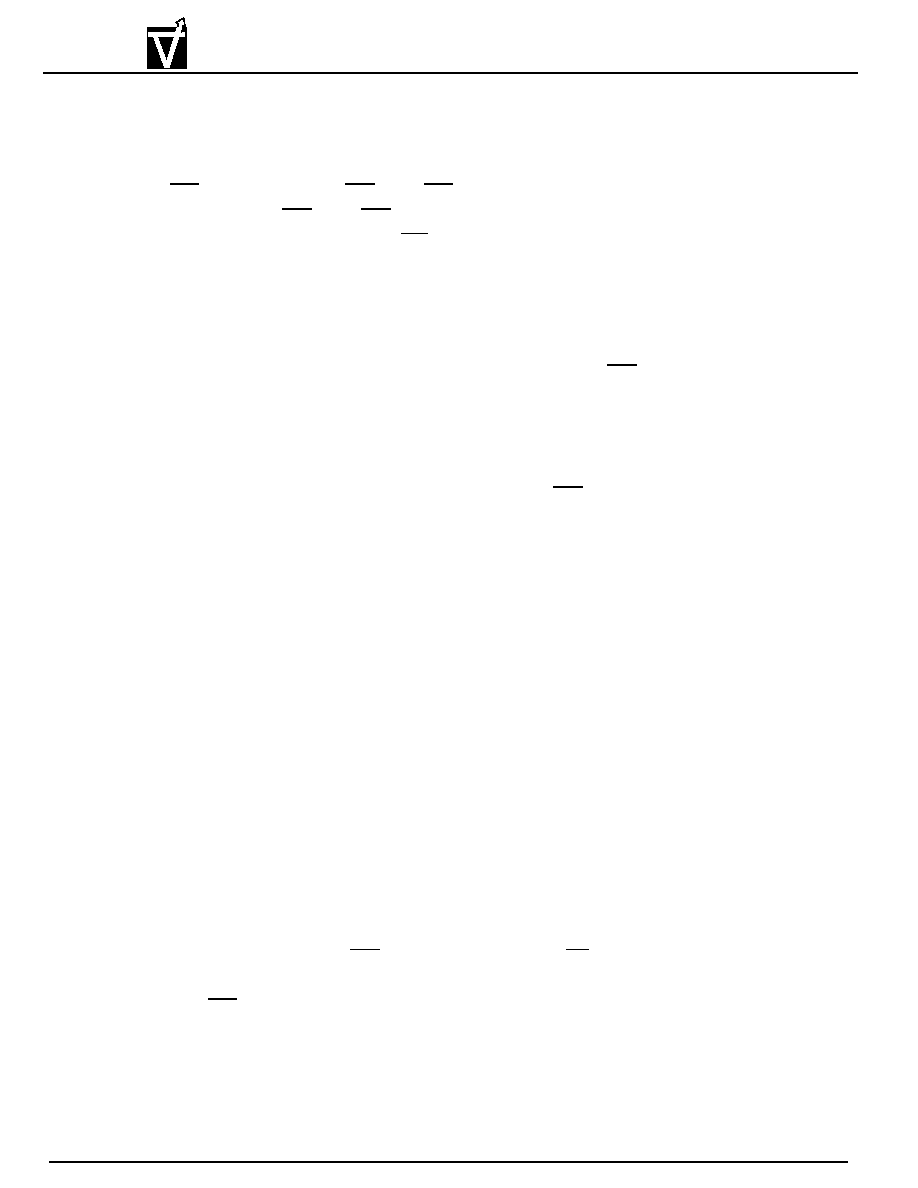

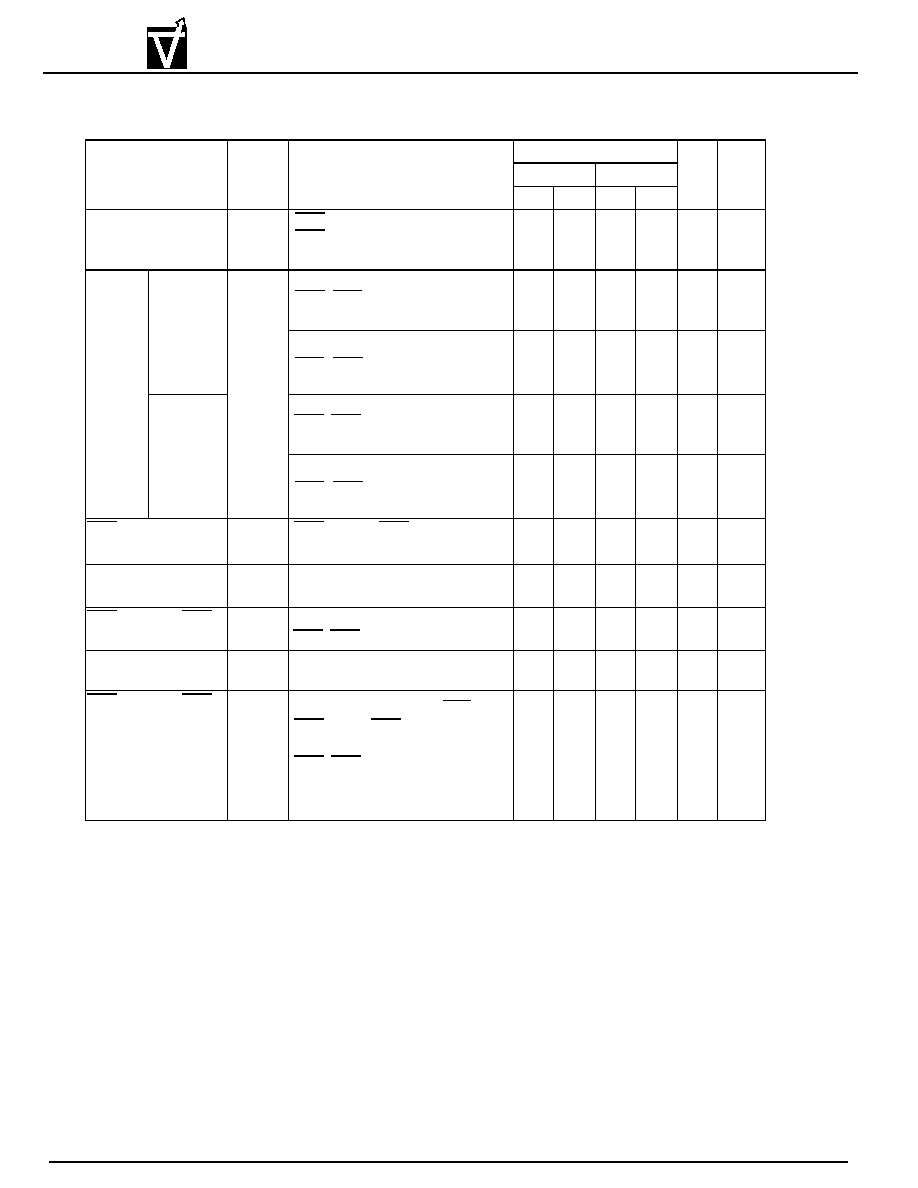

DC Characteristics ; 3.3 - Volt Verion

(T

a

= 0 to 70∞C, V

CC

= + 3.3V 10%, V

ss

= 0V)

Parameter

Symbol

Test Conditions

VG26 (V) (S) 17400D

Unit Notes

-5

-6

Min

Max

Min

Max

Operating

current

I

CC1

RAS cycling

CAS cycling

t

RC

= min.

-

110

-

100 mA

1, 2

Standby

Current

Low

power

S - version

I

CC2

LVTTL interface

RAS, CAS = V

IH

Dout = high - Z

-

0.5

-

0.5

mA

CMOS interface

- 0.2V

Dout = high - Z

-

0.25

-

0.25

mA

Standard

power

version

LVTTL interface

RAS, CAS = V

IH

Dout = high - Z

-

2

-

2

mA

CMOS interface

- 0.2V

Dout = high - Z

-

0.5

-

0.5

mA

RAS - only

refresh current

I

CC3

RAS cycling, CAS = V

IH

t

RC

= min.

-

110

-

100

mA

1, 2

Fast page mode

current

I

CC4

t

PC

= min.

-

80

-

70

mA

1,3

CAS - before - RAS

refresh current

I

CC5

t

RC

= min.

RAS, CAS cycling

-

110

-

100

mA

1, 2

Self - refresh currant

(S - Version)

I

CC8

-

250

-

250

CAS - before - RAS

long refresh

current (S - Version)

I

CC9

Standby : V

CC

-

CAS before RAS refresh :

2048 cycles/128ms

RAS, RAS :

V

CC

- (Max)

Dout = high - Z,

-

300

-

300

±

RAS CAS

,

V

CC

RAS CAS

,

V

CC

t

RASS

100

µ

S

µ

A

0.2V

RAS

0V

V

I L

0.2V

0.2V

V

IH

V

IH

t

RAS

300ns

µ

A

Document:1G5-0126

Rev.1

Page 9

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

DC Characteristics ; 3.3 - Volt Version (cont.)

(T

a

= 0 to 70∞C, V

CC

= + 3.3V 10%, V

SS

= 0V)

Notes :

1. l

CC

is specified as an average current. It depends on output loading condition and cycle rate when

the device is selected. l

CC

max is specified at the output open condition.

2. Address can be changed once or less while RAS = V

IL

.

3. For l

CC4

, address can be changed once or less within one Fast page mode cycle time.

Parameter

Symbol

Test Conditions

VG26 (V) (S) 17400D

Unit Notes

-5

-6

Min

Max

Min

Max

Input leakage

current

I

LI

+ 0.3V

-5

5

-5

5

Output leakage

current

I

LO

+ 0.3V

Dout = Disable

-5

5

-5

5

Output high

voltage

V

OH

l

OH

= -2mA

2.4

-

2.4

-

V

Output low

voltage

V

OL

l

OL

= + 2mA

-

0.4

-

0.4

V

±

0V

Vin

V

CC

µ

A

0V

Vout

V

C C

µ

A

Document:1G5-0126

Rev.1

Page 10

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

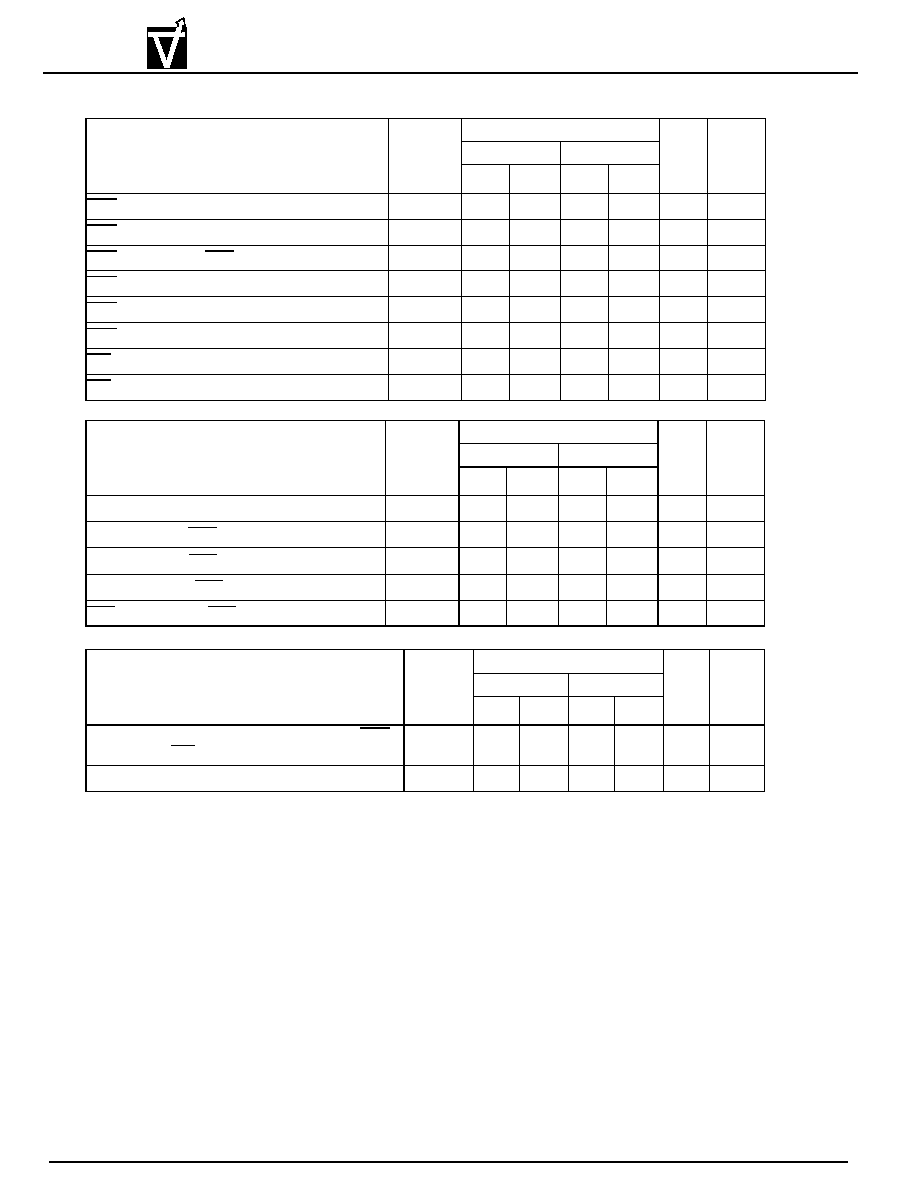

AC Characteristics

(Ta = 0 to + 70∞C, V

CC

= 5V

10% or 3.3V

10%, V

SS

= 0V) * 1, * 2, * 3, * 4

Test conditions

∑ Output load : two TTL Loads and 100pF(V

CC

= 5.0V 10%)

one TTL Load and 100pF(V

CC

= 3.3V 10%)

∑ Input timing reference levels :

V

IH

= 2.4V, V

lL

= 0.8V (V

CC

= 5.0V 10%); V

IH

= 2.0V, V

lL

= 0.8V (V

CC

= 3.3V 10%)

∑ Output timing reference levels :

V

OH

= 2.0V, V

OL

= 0.8V (V

CC

= 5V 10%, 3.3V 10%)

Read, Write, Read - Modify - Write and Refresh Cycles

(Common Parameters)

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Random read or write cycle time

t

RC

90

-

110

-

ns

RAS precharge time

t

RP

30

-

40

-

ns

CAS precharge time in normal mode

t

CPN

10

-

10

-

ns

RAS pulse width

t

RAS

50

10000

60

10000

ns

5

CAS pulse width

t

CAS

12

10000

15

10000

ns

6

Row address setup time

t

ASR

0

-

0

-

ns

Row address hold time

t

RAH

8

-

10

-

ns

Column address setup time

t

ASC

0

-

0

-

ns

7

Column address hold time

t

CAH

8

-

10

-

ns

RAS to CAS delay time

t

RCD

12

37

14

45

ns

8

RAS to column address delay time

t

RAD

10

25

12

30

ns

9

Column address to RAS lead time

t

RAL

25

-

30

-

ns

RAS hold time

t

RSH

13

-

15

-

ns

CAS hold time

t

CSH

50

-

60

-

ns

CAS to RAS precharge time

t

CRP

5

-

5

-

ns

10

OE to Din delay time

t

OED

12

-

15

-

ns

Transition time (rise and fall)

t

T

1

50

1

50

ns

11

Refresh period

t

REF

-

32

-

32

ms

Refresh period (S - Version)

t

REF

-

128

-

128

ms

CAS to output in Low-Z

t

CLZ

0

-

0

-

ns

CAS delay time from Din

t

DZC

0

-

0

-

ns

OE delay time from Din

t

DZO

0

-

0

-

ns

±

±

±

±

±

±

±

±

Document:1G5-0126

Rev.1

Page 11

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Read Cycle

Write Cycle

Read - Modigy - Write Cycle

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Access time from RAS

t

RAC

-

50

-

60

ns

12

Access time from CAS

t

CAC

-

13

-

15

ns

13,14

Access time from column address

t

AA

-

25

-

30

ns

14,15

Access time from OE

t

OEA

-

13

-

15

ns

Read command setup time

t

RCS

0

-

0

-

ns

7

Read command hold time to CAS

t

RCH

0

-

0

-

ns

10,16

Read command hold time to RAS

t

RRH

0

-

0

-

ns

16

Output buffer turn-off time

t

OFF

0

13

0

15

ns

17

Output buffer turn-off time from OE

t

OEZ

0

13

0

15

ns

17

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Write command setup time

t

WCS

0

-

0

-

ns

7,18

Write command hold time

t

WCH

8

-

10

-

ns

Write command pulse width

t

WP

8

-

10

-

ns

Write command to RAS lead time

t

RWL

13

-

15

-

ns

Write command to CAS lead time

t

CWL

8

-

10

-

ns

Data-in setup time

t

DS

0

-

0

-

ns

19

Data-in hold time

t

DH

8

-

10

-

ns

19

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Read - modify - write cycle time

t

RWC

125

-

150

-

ns

RAS to WE delay time

t

RWD

65

-

80

-

ns

18

CAS to WE delay time

t

CWD

30

-

35

-

ns

18

Column address to WE delay time

t

AWD

40

-

50

-

ns

18

OE hold time from WE

t

OEH

8

-

10

-

ns

Document:1G5-0126

Rev.1

Page 12

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

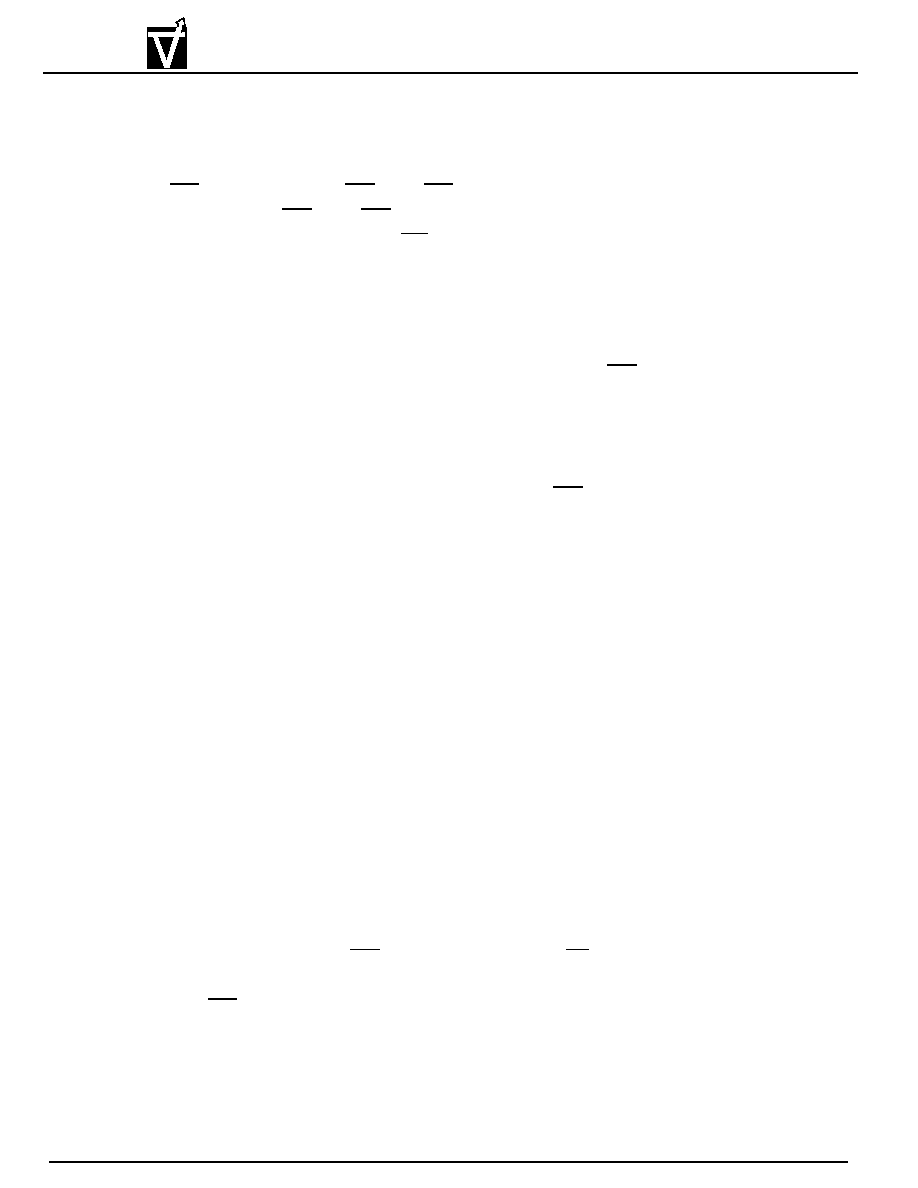

Refresh Cycle

Fast Page Mode Cycle

Fast Page Mode Read Modify Write Cycle

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

CAS setup time (CBR refresh)

t

CSR

10

-

10

-

ns

CAS hold time (CBR refresh)

t

CHR

10

-

10

-

ns

10

RAS precharge to CAS hold time

t

RPC

5

-

5

-

ns

7

RAS pulse width (self refresh)

t

RASS

100

-

100

-

RAS precharge time (self refresh)

t

RPS

90

-

110

-

ns

CAS hold time (CBR self refresh)

t

CHS

-50

-

-50

-

ns

WE setup time

t

WSR

0

-

0

-

ns

WE hold time

t

WHR

10

-

10

-

ns

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Fast page mode cycle time

t

PC

35

-

40

-

ns

Fast page mode CAS

Precharge

time

t

CP

10

-

10

-

ns

Fast page

mode RAS pulse width

t

RASP

50

10

5

60

10

5

ns

20

Access time from CAS

precharge

t

CPA

-

30

-

35

ns

10,14

RAS hold time from CAS precharge

t

CPRH

30

-

35

-

ns

Parameter

Symbol

VG26 (V) (S) 17400D

Unit

Notes

-5

-6

Min

Max

Min

Max

Fast page mode read - modify - write cycle CAS

precharge to WE delay time

t

CPW

45

-

55

-

ns

11

Fast page mode read - modify - write cycle time

t

PRWC

70

-

80

-

ns

µ

s

Document:1G5-0126

Rev.1

Page 13

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Notes :

1. AC measurements assume t

T

= 5ns.

2. An initial pause of 100 is required after power up, and it followed by a minimum of eight initialization

cycles (RAS-only refresh cycle or CAS-before-RAS refresh cycle). If the internal refresh counter is

used, a minimum of eight CAS-before-RAS refresh cycles are required.

3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to

the device.

4. All the V

CC

and V

SS

pins shall be supplied with the same voltage.

5. t

RAS

(min) = t

RWD

(min) + t

RWL

(min) + t

T

in read - modify-write cycle.

6. t

CAS

(min) = t

CWD

(min) + t

CWL

(min) + t

T

in read - modify-write cycle.

7

.

t

ASC

(min), t

RCS

(min), t

WCS

(min) and t

RPC

are determined by the falling edge of CAS.

8. t

RCD

(max) is specified as a reference point only, and t

RAC

(max) can be met with the t

RCD

(max) limit.

Otherwise, t

RAC

is controlled exclusively by t

CAC

if t

RCD

is greater than the specified t

RCD

(max) limit.

9. t

RAD

(max) is specified as a reference point only, and t

RAC

(max) can be met with the t

RAD

(max) limit.

Otherwise, t

RAC

is controlled exclusively by t

AA

if t

RAD

is greater than the specified t

RAD

(max) limit.

10. t

CRP

, t

CHR

, t

RCH

, t

CPA

and t

CPW

are determined by the rising edge of CAS.

11. V

IH

(min) and V

IL

(max) are reference levels for measuring timing or input signals. Therefore, transition

time is measured between V

IH

and V

IL

.

12. Assumes that t

RCD

t

RCD

(max) and t

RAD

t

RAD

(max). If t

RCD

or t

RAD

is greater than the maximum

recommended value shown in this table, t

RAC

exceeds the value shown.

13. Assumes that t

RCD

t

RCD

(max) and t

RAD

t

RAD

(max).

14. Access time is determined by the maximum among t

AA

, t

CAC

, t

CPA

.

15. Assumes that t

RCD

t

RCD

(max) and t

RAD

t

RAD

(max).

16. Either t

RCH

or t

RRH

must be satisfied for a read cycle.

17. t

OFF

(max) and t

OEZ

(max) define the time at which the output achieves the open circuit condition (

high impedance).

18. t

WCS

, t

RWD

, t

CWD

, and t

AWD

are not restrictive operating parameters. They are included in the data

sheet as electrical characteristics only. If t

WCS

t

WCS

(min), the cycle is an early write cycle and the

data output will remain open circuit (high impedance) throughout the entire cycle. If t

RWD

t

RWD

(min),

t

CWD

t

CWD

(min), t

AWD

t

AWD

(min), and t

CPW

t

CPW

(min), the cycle is a read-modify-write and the

data output will contain data read from the selected cell. If neither of the above sets of conditions is

satisfied, the condition of the data output (at access time) is indeterminate.

19. These parameters are referenced to CAS in an early write cycle and to WE edge in a delayed write or a

read-modify-write cycle.

20. t

RASP

defines RAS pulse width in Fast page mode cycles.

µ

s

Document:1G5-0126

Rev.1

Page 14

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

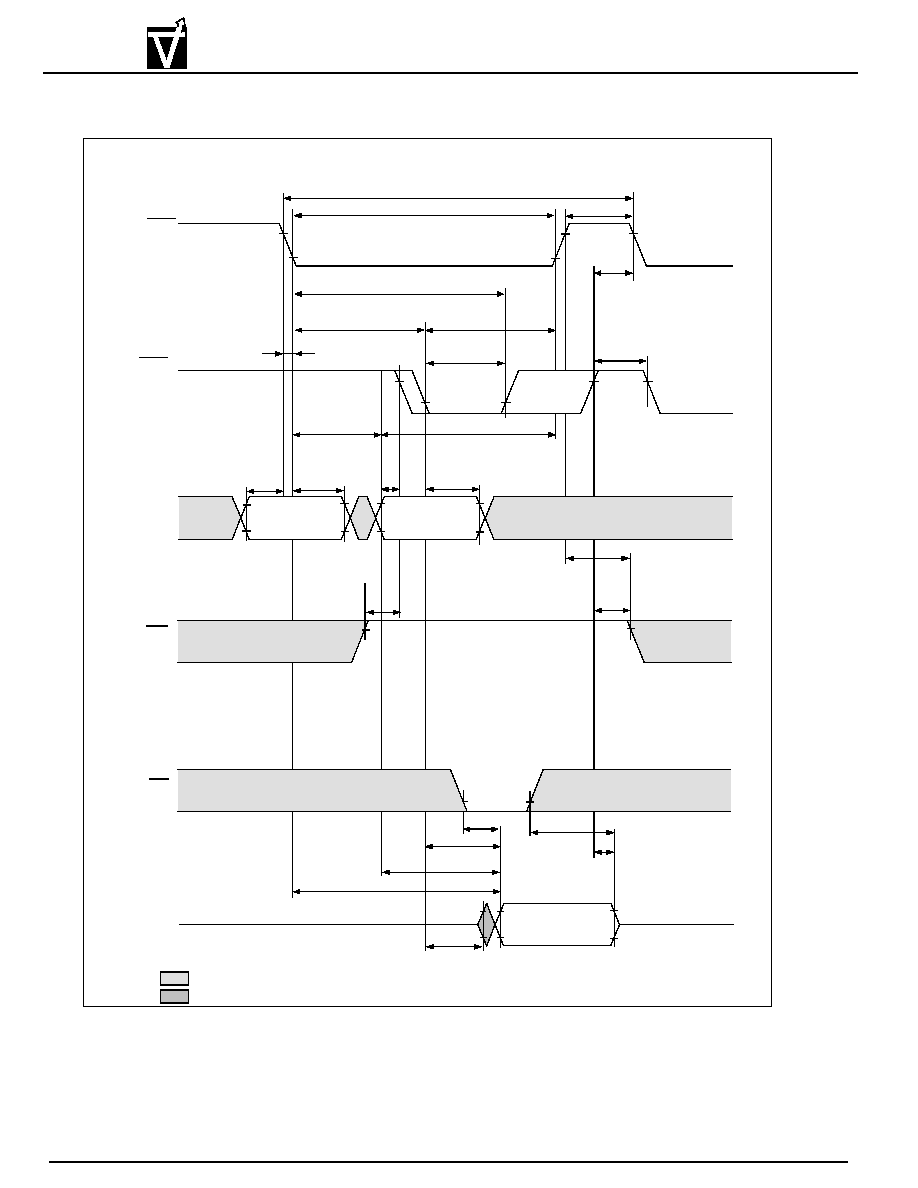

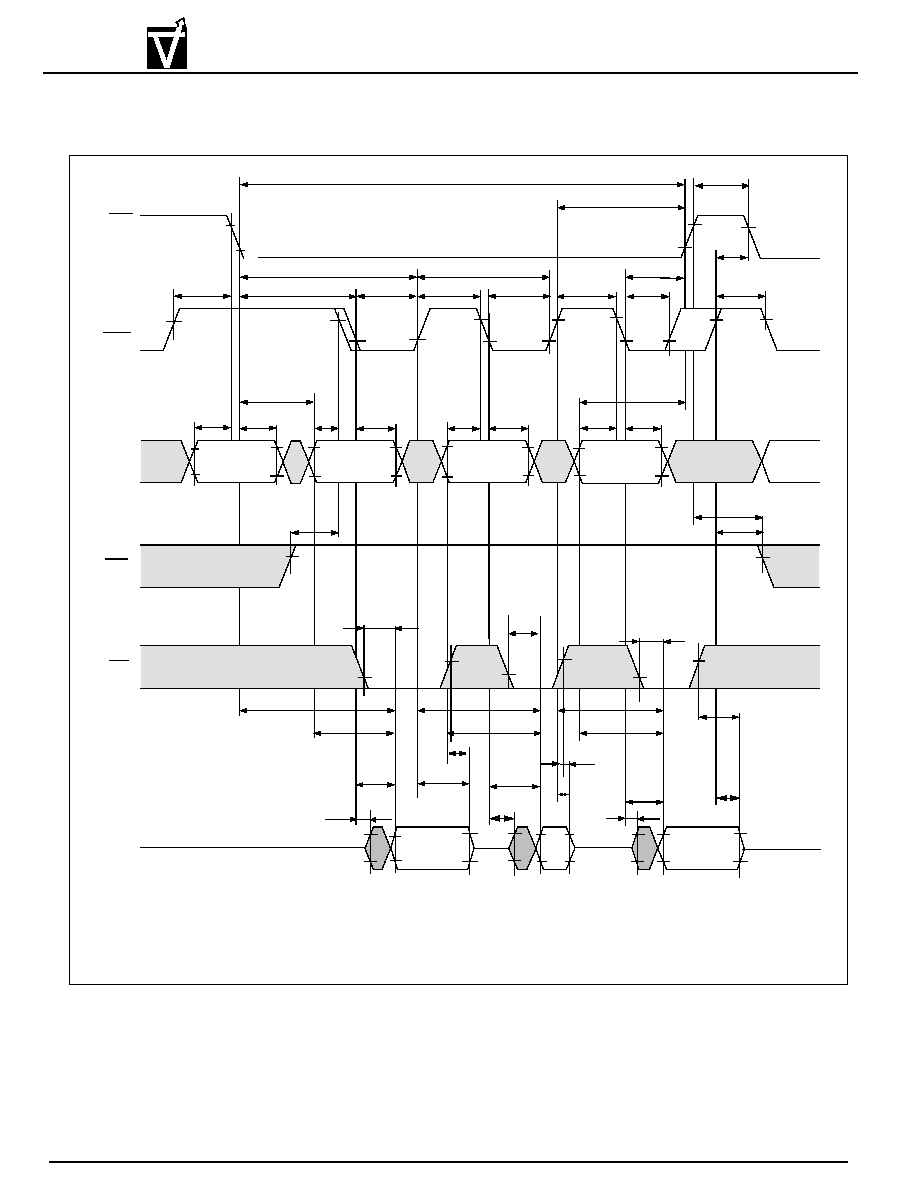

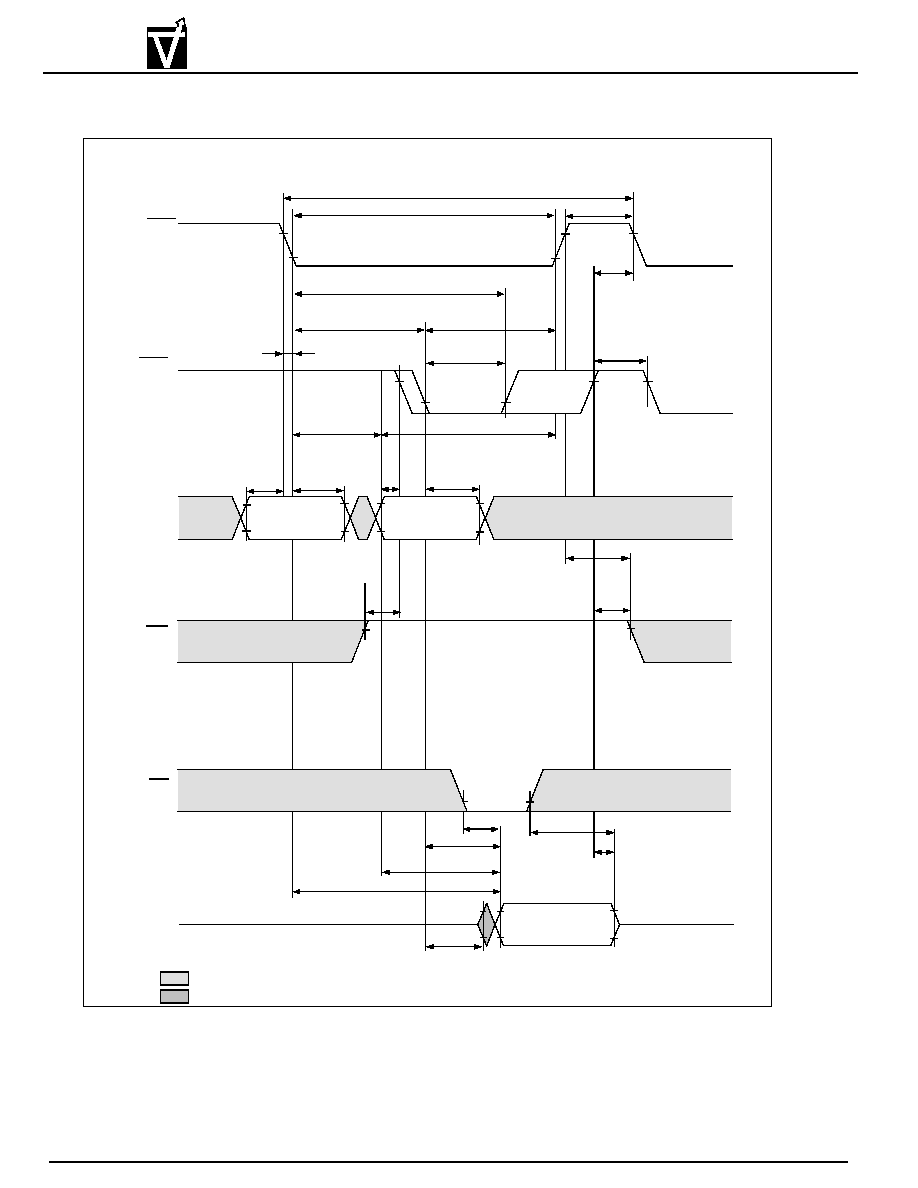

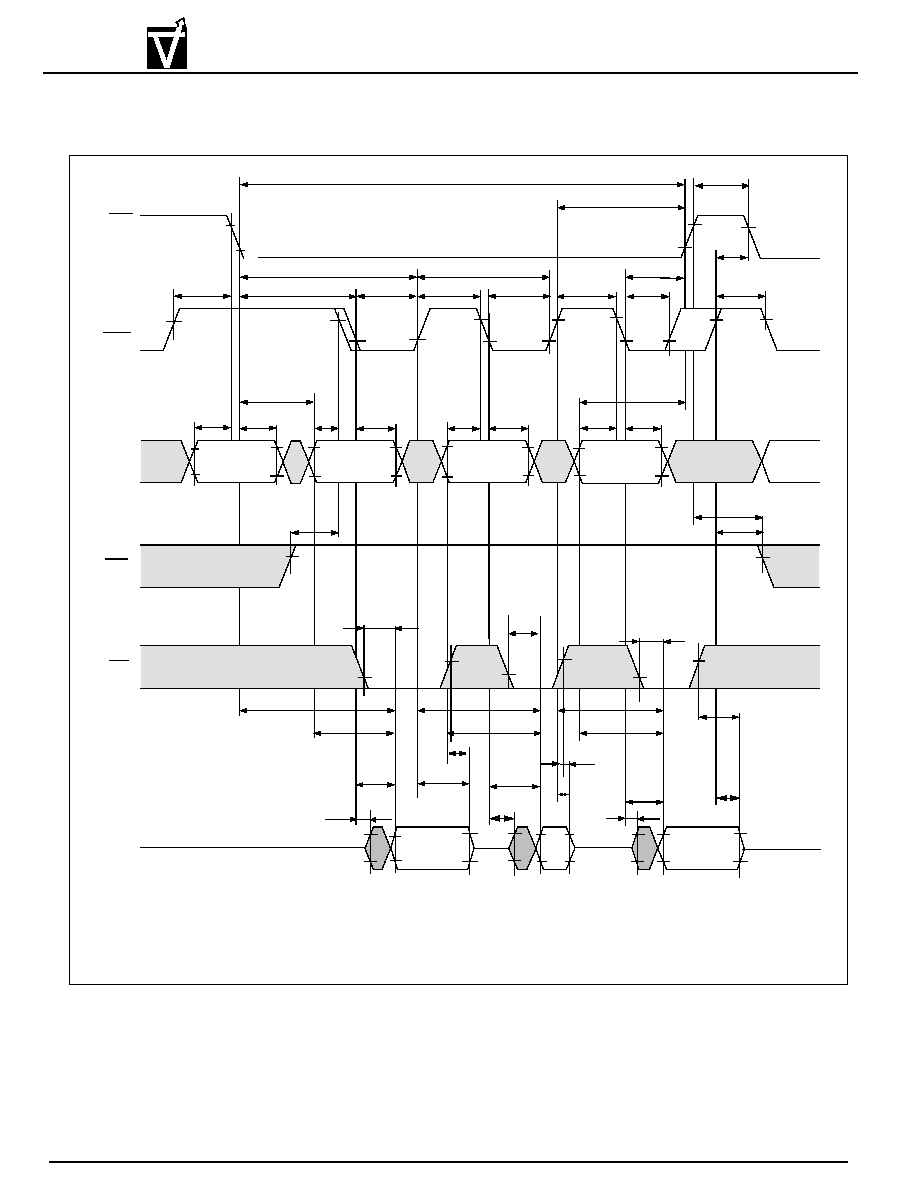

Timing Waveforms

∑ Read Cycle

t

RC

t

RAS

t

RP

t

CRP

t

CPN

t

RRH

t

RCH

t

OEZ

t

OFF

t

OEA

t

CAC

t

AA

t

RAC

t

CLZ

D

OUT

t

RCS

t

ASR

t

RAH

t

ASC

t

CAH

t

RAD

t

RAL

t

CAS

t

RSH

t

RCD

t

T

t

CSH

RAS

ADDRESS

DQ1 ~ DQ4

Note : = don't care

Row

Column

CAS

WE

OE

= Invalid Dout

Document:1G5-0126

Rev.1

Page 15

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

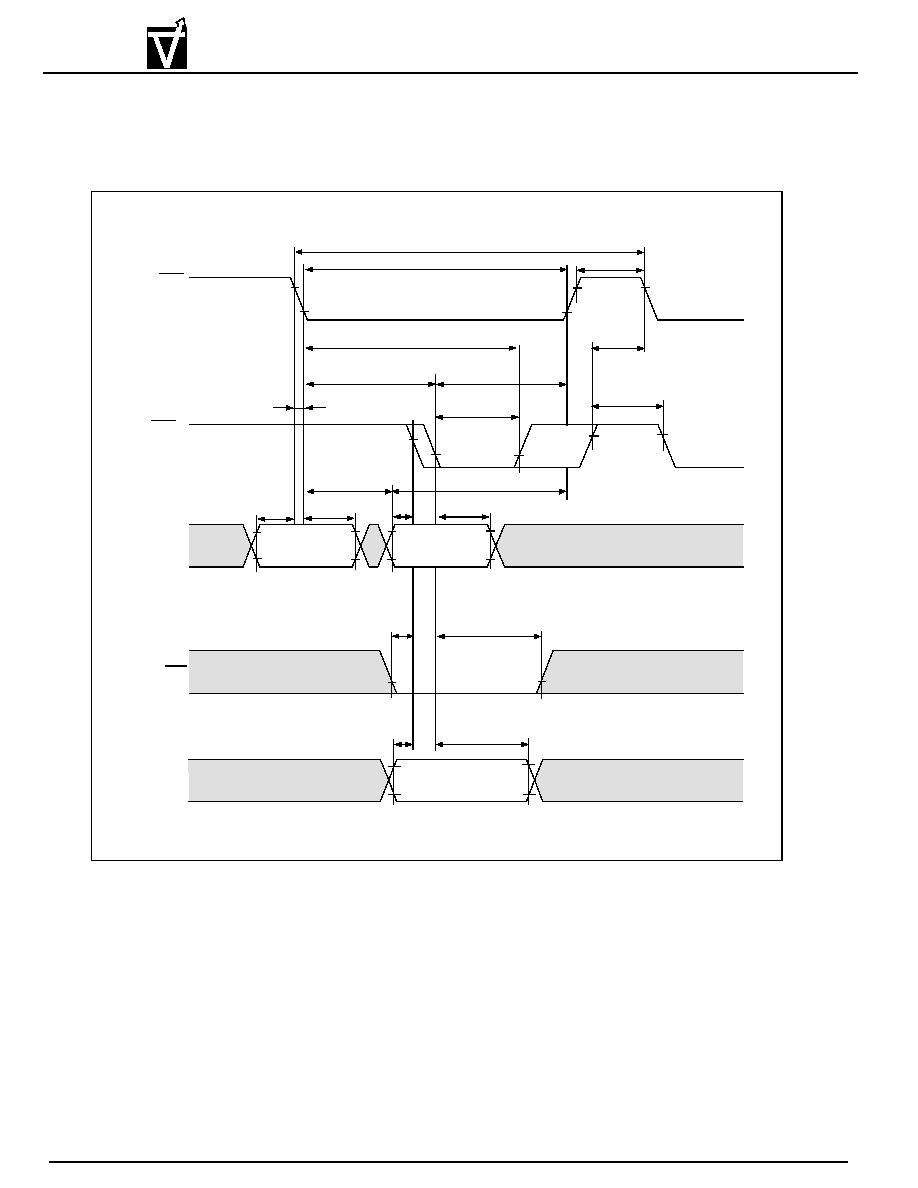

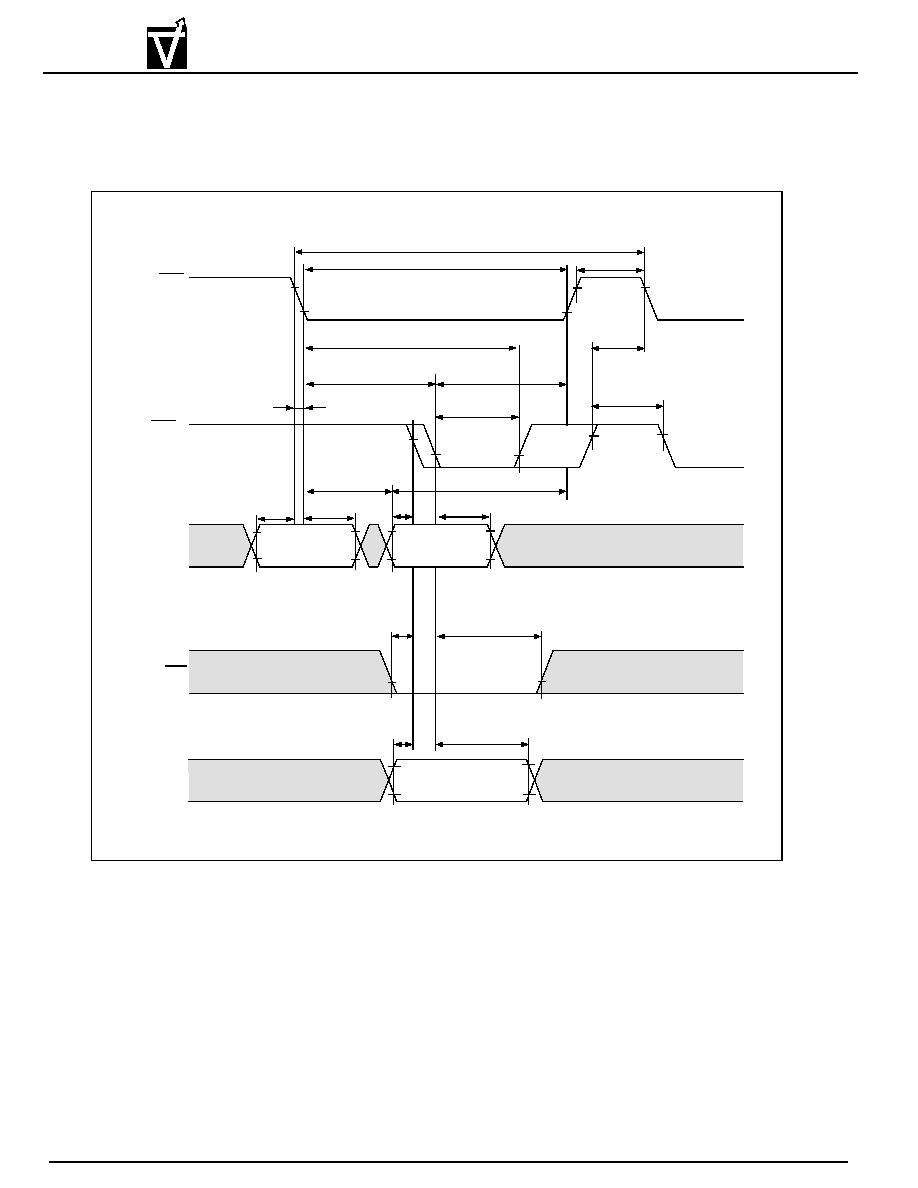

∑Early Write Cycle

t

RC

t

RAS

t

RP

t WCH

t

DS

t

DH

tWCS

t

RAL

t

CAS

t

RSH

t

RCD

t

T

t

CSH

RAS

CAS

WE

DQ1 ~ DQ4

t

CRP

t

ASR

t

RAH

t

ASC

t

CAH

ADDRESS

Column

Row

t

CPN

DIN

t

RAD

t

RAL

Document:1G5-0126

Rev.1

Page 16

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

∑ Delayed Write Cycle

t

RC

t

RAS

t

RP

t RWL

t RCS

t

CAS

t

RSH

t

RCD

t

T

t

CSH

RAS

CAS

t

ASR

t

RAH

t

CAH

ADDRESS

Column

Row

t

ASC

D

IN

DQ1 ~ DQ4

WE

t

CRP

t

CPN

t

DH

t

DS

t OEH

t OED

OE

t

DS

OPEN

t WP

tCWL

Document:1G5-0126

Rev.1

Page 17

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

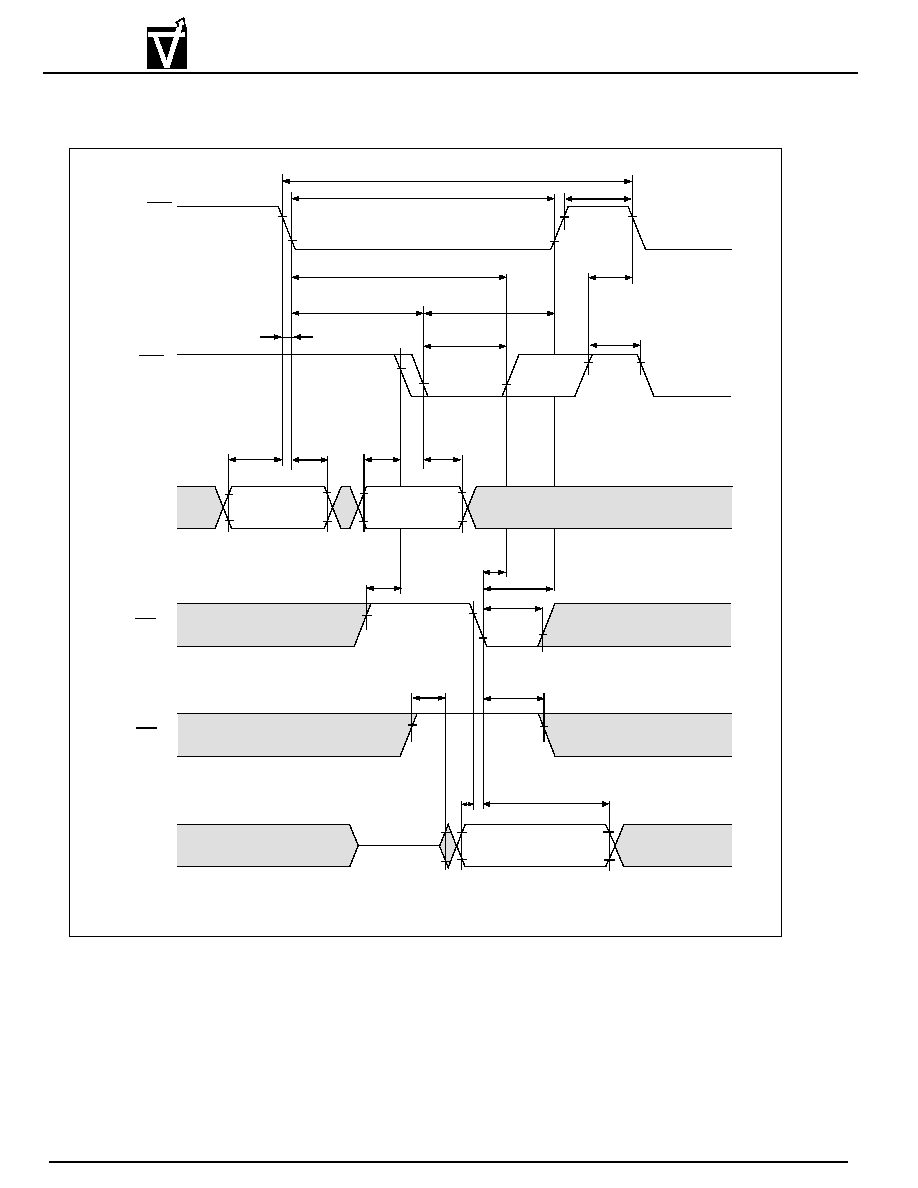

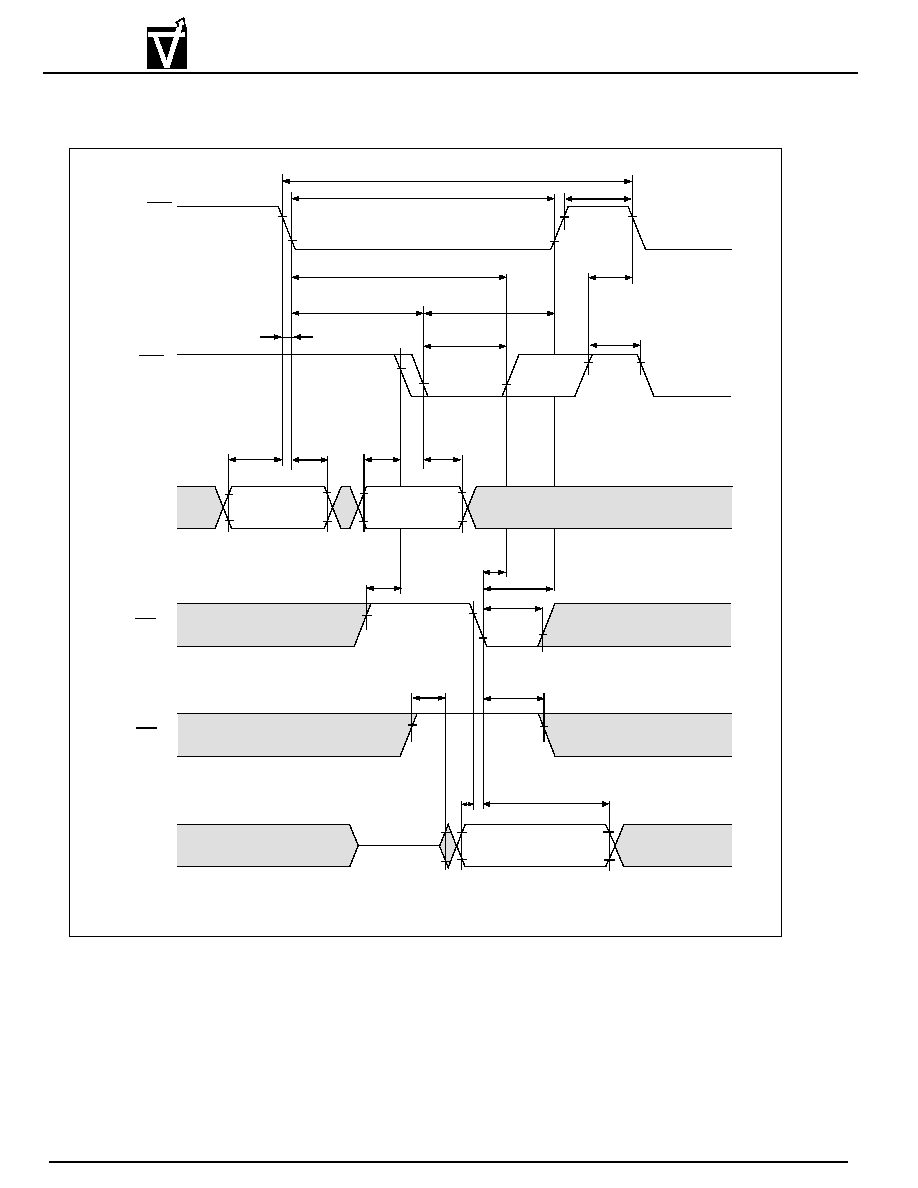

∑ Read - Modify - Write Cycle

t

RWC

t

RAS

tRP

t

RWD

t

WP

t

RAD

t

RWL

t

CAS

t

CWL

t

RCD

t

T

t

CPN

RAS

CAS

WE

t

CRP

t

ASR

t

RAH

t

ASC

t

CAH

ADDRESS

Column

Row

DQ1 ~ DQ4

t

DH

tDS

OE

t

RCS

t

AWD

t

CWD

D

IN

tOED

tOEH

tOEZ

tOEA

tCAC

tRAC

tAA

DQ1 ~ DQ4

DOUT

OPEN

tDZO

tDZC

Document:1G5-0126

Rev.1

Page 18

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

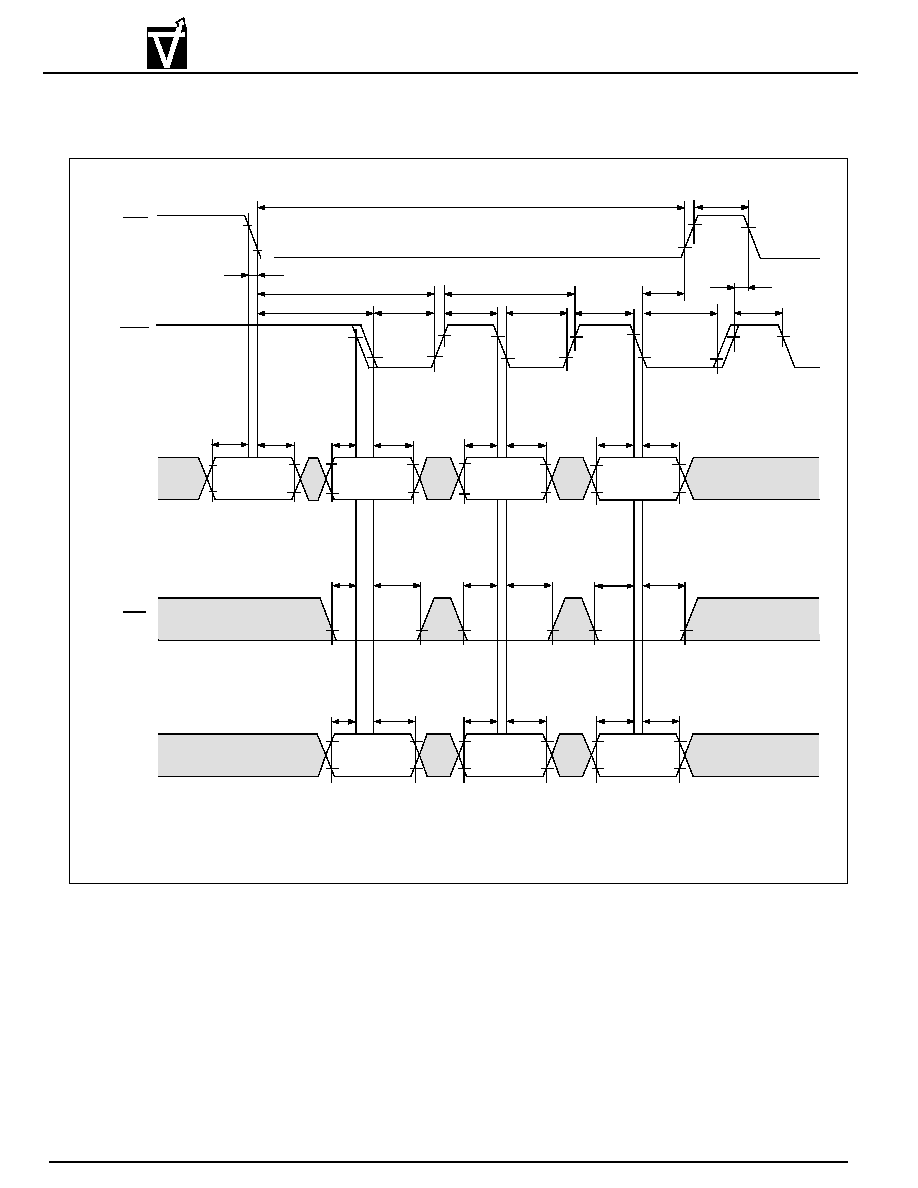

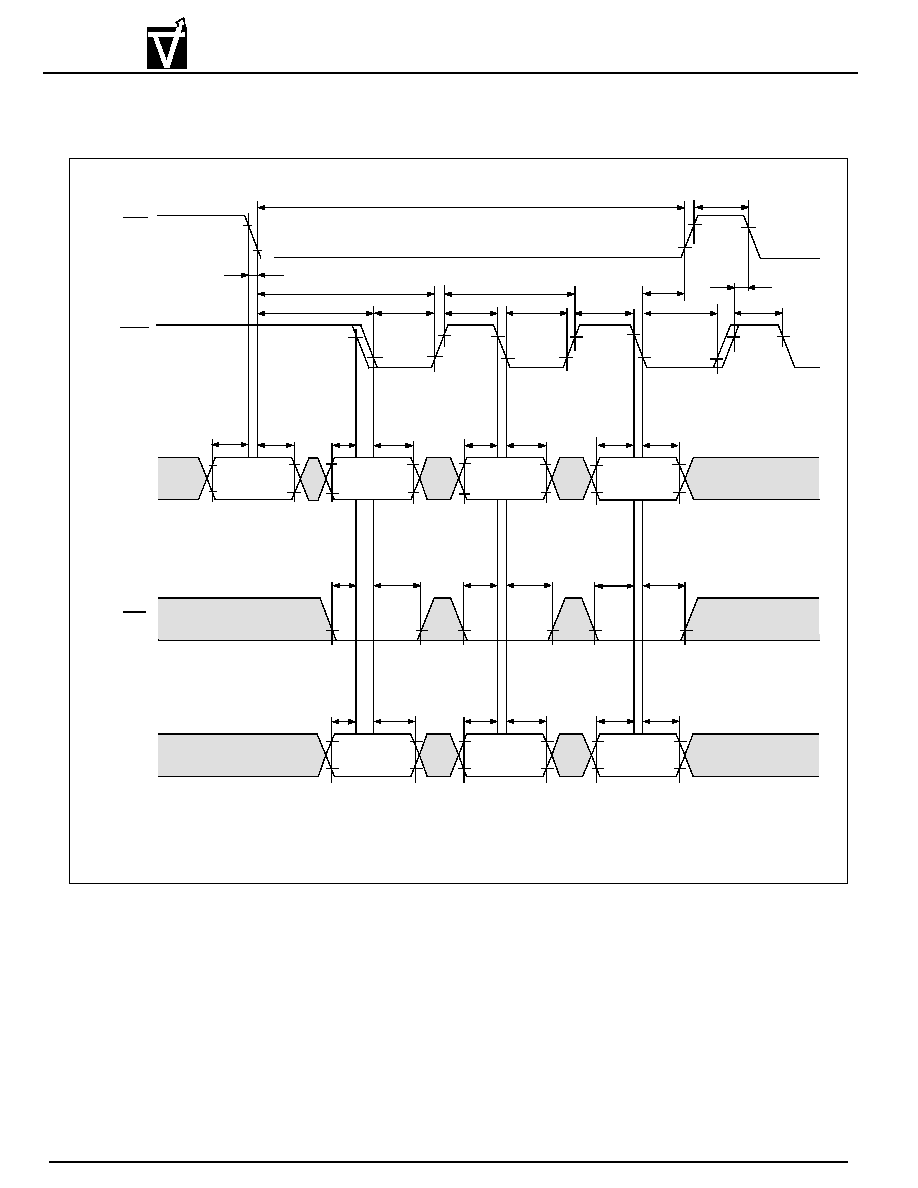

∑ Fast Page Mode Read Cycle

t

RASP

t

CPRH

tRCS

t

CAS

t

RSH

t

RCD

tOEA

t

CSH

RAS

CAS

t

ASR

t

RAH

t

CAH

ADDRESS

t

CAS

WE

t

CRP

t CP

OE

DQ1 ~ DQ4

OPEN

D

OUT 1

t

PC

t

CP

t

CAS

t

CPN

t

CRP

t

RAD

t

CAH

t

ASC

t

ASC

t

CAH

t

ASC

t

RAL

Row

Column 1

t

RRH

t

RCH

tRAC

tAA

tAA

tAA

tCPA

tCPA

tOEZ

tOFF

tCAC

tOEZ

tCAC

tCAC

tCLZ

D

OUT N

WE

OE

Column 2

Column N

Row

t

RP

tOEA

tOEA

tCLZ

tOEZ

tCLZ

D

OUT 2

tOFF

tOFF

Document:1G5-0126

Rev.1

Page 19

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

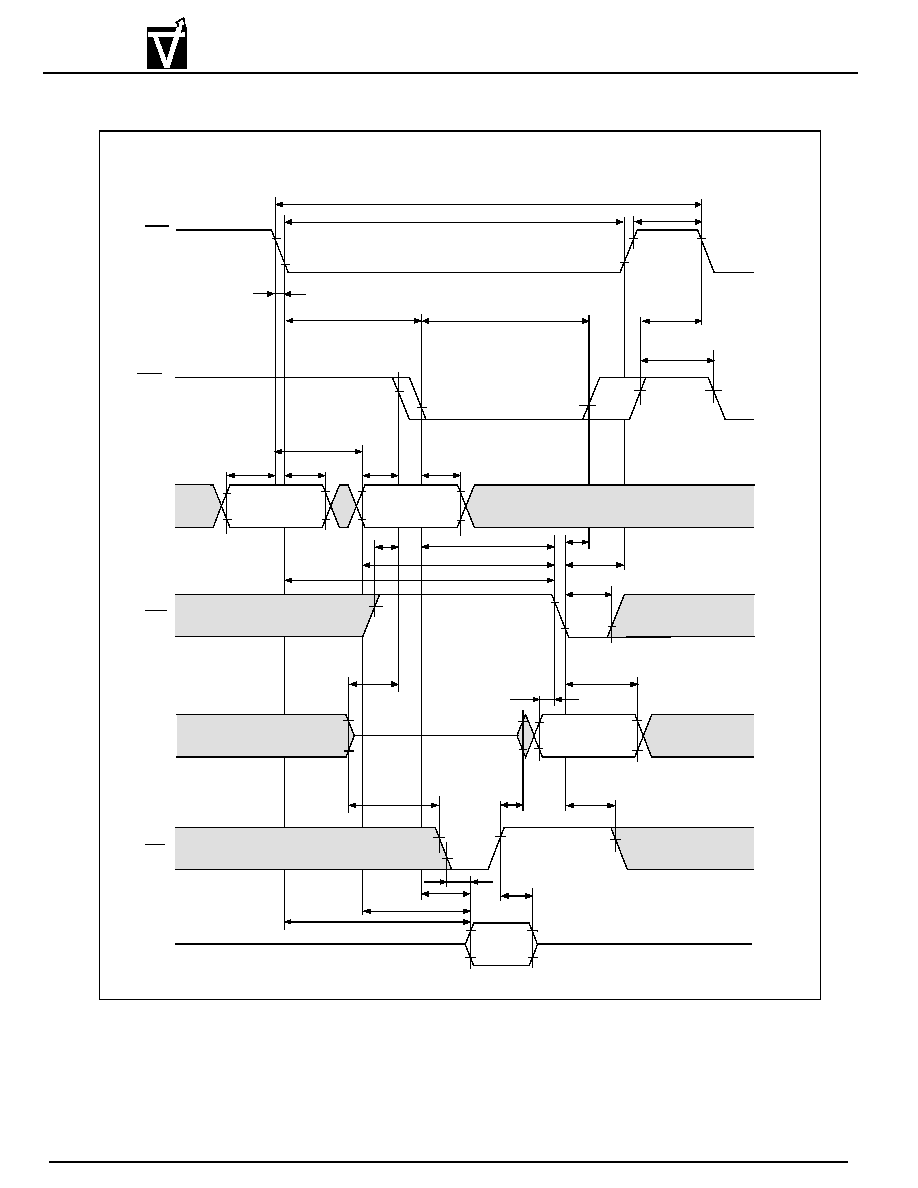

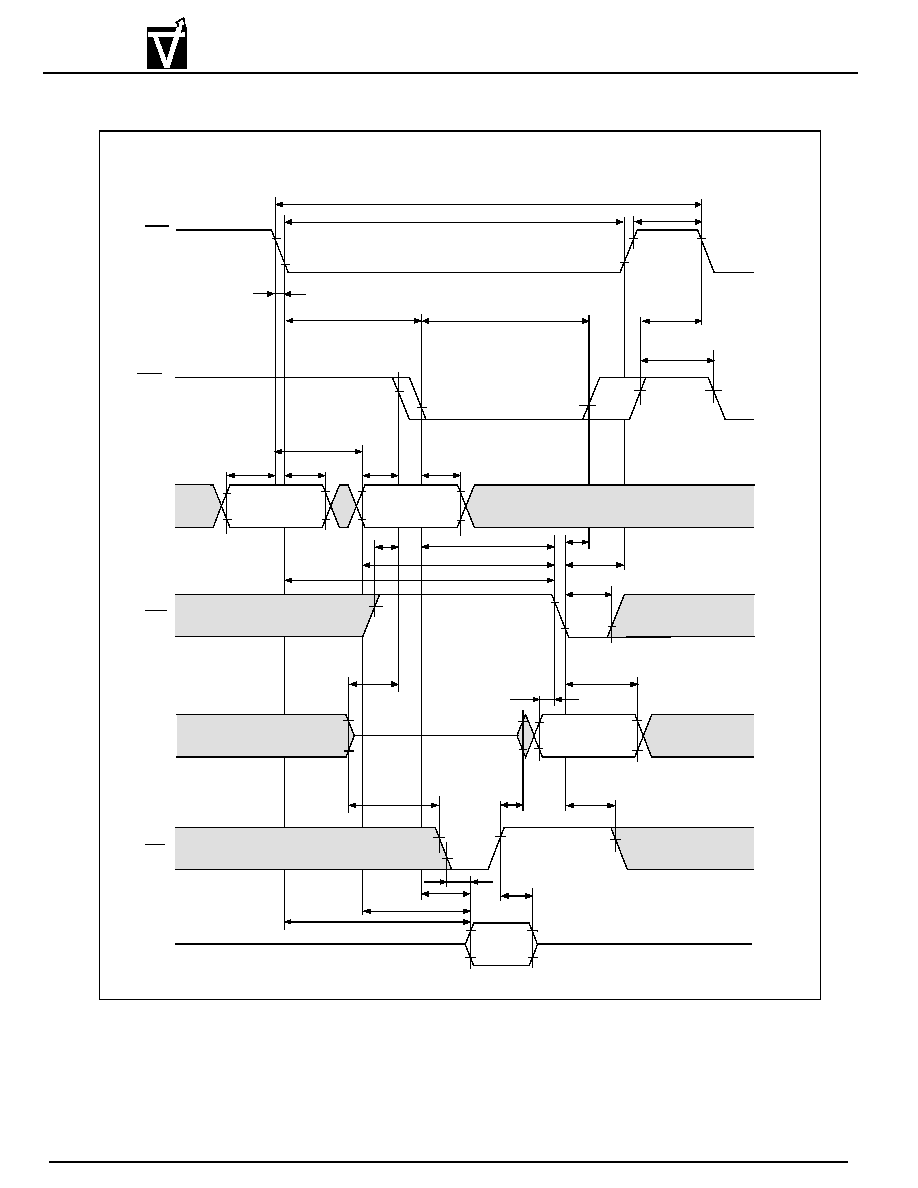

∑ Fast Page Mode Early Write Cycle

t

RASP

t

RP

tWCS

t

CAS

t

RSH

t

RCD

RAS

CAS

t

ASR

t

RAH

t

CAH

ADDRESS

t

CAS

WE

t CP

DQ1 ~ DQ4

t

PC

t

CP

t

CAS

t

CPN

t

CRP

t

CAH

t

ASC

t

ASC

t

CAH

t

ASC

Row

Column 1

tDS

WE

Column 2

Column N

tWCH

tWCS

tWCH

tWCS

tWCH

tDH

tDS

tDH

tDS

tDH

D

IN

1

D

IN

2

D

IN

N

tT

t

CSH

Document:1G5-0126

Rev.1

Page 20

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

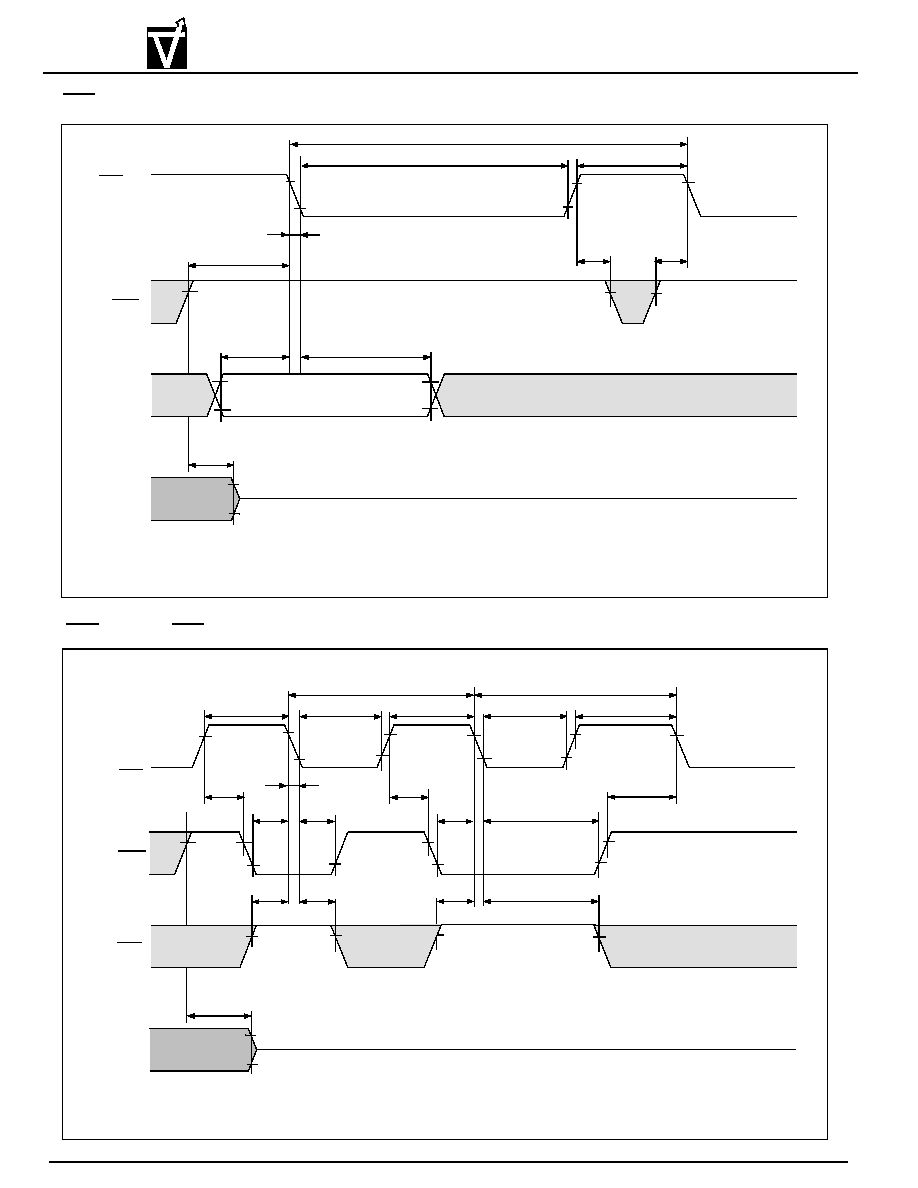

∑ Fast Page Mode Delayed Write Cycle

tRASP

tCPRH

tRCS

t

CAS

tWP

RAS

CAS

t

ASR

t

RAH

t

CAH

ADDRESS

t

CAS

WE

t

RCD

t

RSH

t

CAS

t

CRP

t

RAD

t

CAH

t

ASC

t

ASC

t

CAH

t

ASC

Row

Column 1

t

RWL

t

RCS

tOED

WE

OE

tRP

t

T

Column N

Column 2

Column 1

t

CWL

t

RCS

t

CWL

t

CWL

tOED

tOED

tOEH

tOEH

tOEH

tDS

tDH

tWP

tDS

tDH

tWP

tDS

tDH

OPEN

OPEN

OPEN

D

IN

1

D

IN

N

D

IN

2

DQ1 ~ DQ4

t

CP

t

CP

t

CSH

t

PC

tDZC

tDZO

tDZC

tDZO

tDZC

tDZO

Document:1G5-0126

Rev.1

Page 21

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

∑ Fast Page Mode Read - Modify - Write Cycle

tRASP

tCPRH

tRCS

t

CAS

tWP

RAS

CAS

t

ASR

t

RAH

t

CAH

ADDRESS

t

CAS

WE

t

RCD

CP

DQ1 ~ DQ4

t

PRWC

t

CP

t

CAS

t

CRP

t

RAD

t

CAH

t

ASC

t

ASC

t

CAH

t

ASC

Row

Column 1

t

RWL

t

RCS

tOED

tCPA

tCAC

WE

OE

tRP

D

OUT 2

D

OUT N

D

OUT 1

t

T

t

Column N

Column 2

Column 1

t

RWD

t

AWD

t

CWD

t

CWL

t

RCS

t

CWD

t

AWD

t

CPW

t

CWL

t

CPW

t

AWD

t

CWD

t

CWL

tOED

tOED

tOEH

tOEH

tOEH

tCAC

tCAC

tAA

tRAC

tOEZ

tOEA

tAA

tCLZ

tOEZ

tAA

tCLZ

tOEZ

tDS

tDH

tWP

tDS

tDH

tWP

tDS

tDH

OPEN

OPEN

D

IN

1

D

IN

N

D

IN

2

DQ1 ~ DQ4

tDZC

tDZC

tOEA

tOEA

tCPA

tOEA

tCLZ

tDZC

tDZO

tDZO

tDZO

Document:1G5-0126

Rev.1

Page 22

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

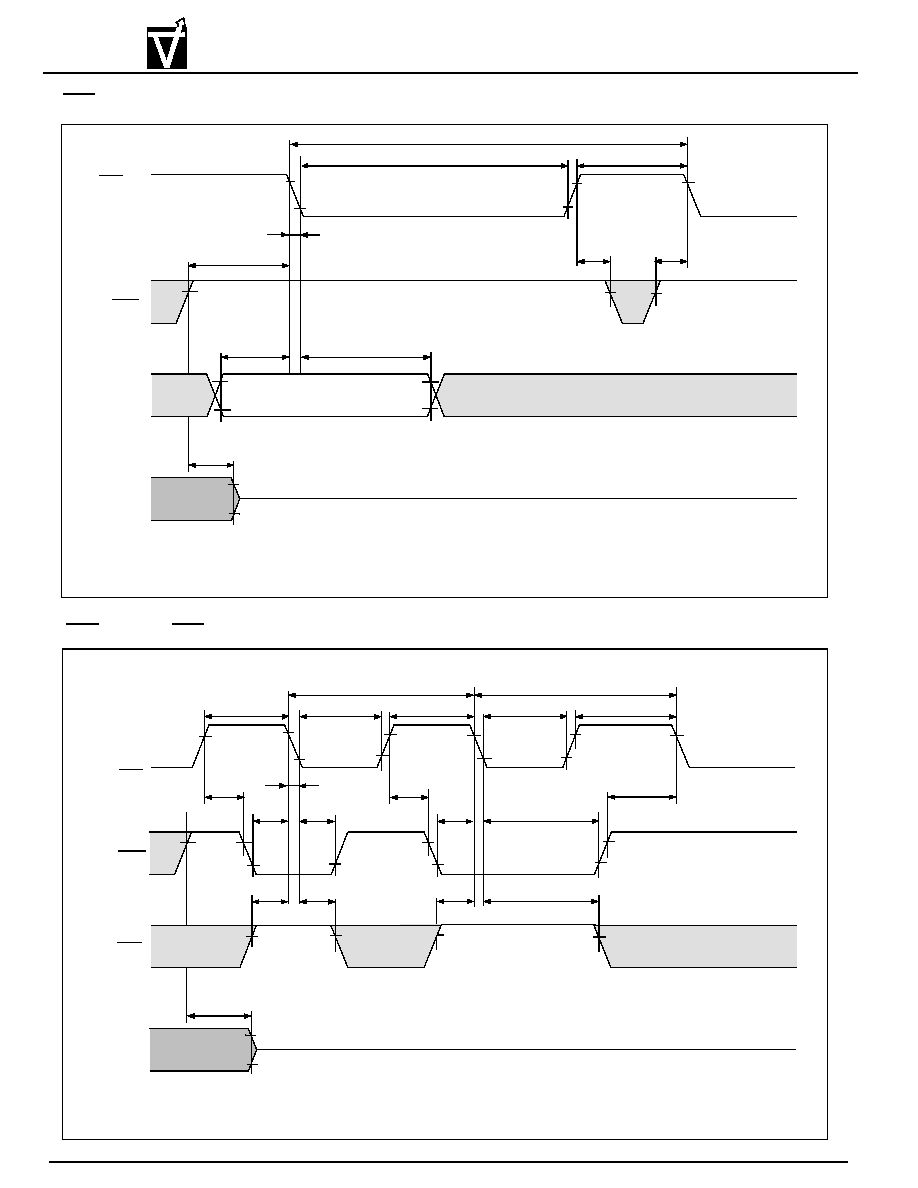

RAS - Only Refresh Cycle

RAS

ADDRESS

tRC

tCRP

tASR

tRAH

tT

tRPC

Row

tOFF

CAS

tRAS

tRP

OPEN

tCRP

DQ1 ~ DQ4

RAS

tCSR

tWSR

tRP

tT

tRPC

tOFF

CAS

tRAS

tRP

OPEN

tCRP

DQ1 ~ DQ4

tRPC

tCHR

tRAS

tRP

tRC

tRC

tCHR

tCSR

tWHR

tWSR

tWHR

WE

CAS - Before - RAS Refresh Cycle

Document:1G5-0126

Rev.1

Page 23

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

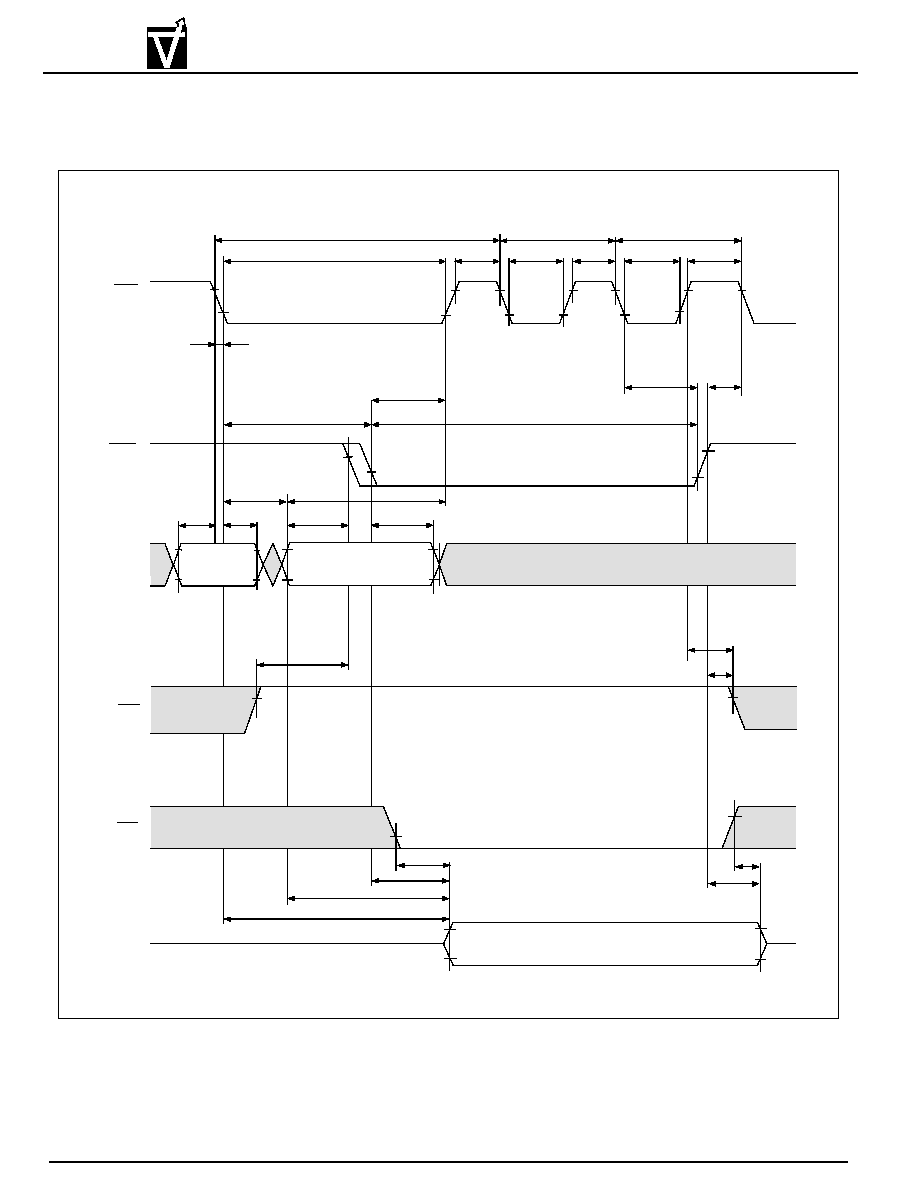

CBR Self - Refesh Cycle

RAS

WE

tRPC

tOFF

tCSR

tCHS

tWSR

CAS

tRASS

tRPS

OPEN

DQ1 - DQ4

tWHR

High lmpedance

Document:1G5-0126

Rev.1

Page 24

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

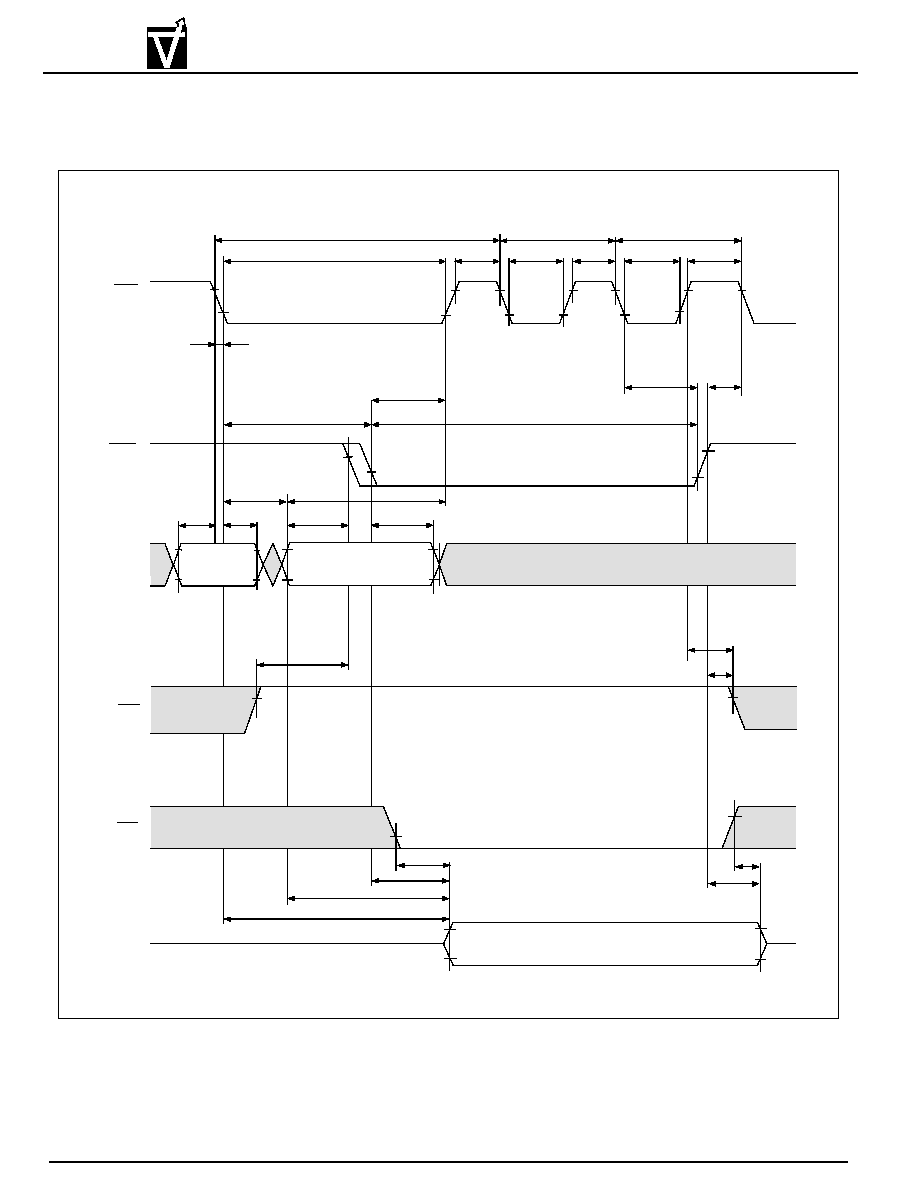

∑ Hidden Refresh Cycle

tRP

tRAS

RAS

tRCD

tCRP

ADDRESS

WE

tCHR

tCAS

tRSH

t RAH

tASR

tASC

tCAH

tRAL

Row

tRCH

tOEZ

CAS

DQ1 ~ DQ4

tT

t RCS

D

tRAS

tRAS

tRP

tRP

tRC

tRC

tRC

t RAD

tRRH

tOFF

t OEA

tCAC

tAA

t RAC

Column

OUT

OE

(READ)

(REFRESH)

(REFRESH)

Document:1G5-0126

Rev.1

Page 25

VIS

VG26(V)(S)17400D

4,194,304 x 4 - Bit

CMOS Dynamic RAM

Ordering information

Part Number

Access Time

Package

VG26 (V) (S) 17400DJ - 5

VG26 (V) (S) 17400DJ - 6

50 ns

60 ns

300mil 26/24 - Pin

Plastic SOJ

∑ VG

∑ 26

∑ V

∑ S

∑ 17400

∑ D

∑ J

∑5

∑ VIS Memory Product

∑ Technology

∑ 3.3V version

∑ Self refresh

∑ Device Type and Configuration

∑ Revision

∑ Package Type (J : SOJ , T : TSOJ II)

∑ Speed (5 : 50 ns, 6 : 60 ns)

VG26 (V) (S) 17400DJ - 5

Packaging information

Packaging information

∑

300 mil, 26/24-Pin Plastic SOJ

SEATING PLANE

4-e

e

b

b2

0.007"M

C

L

0.025" MIN.

0.004"

SECTION B-B

E2

A

RAD R1

A1

B

B

D

26

21

E

E1

19

14

BASE METAL

WITH PLATING

c1 c

b1

b

0.267 BASIC

0.335 BASIC

0.050 BASIC

R1

e

E1

E2

6.78 BASIC

1.27 BASIC

0.76

---

7.49

7.62

1.02

0.030

7.75

0.295

17.02

b

D

E

c1

b2

c

b1

A1

A

DIM

0.51

0.41

0.016

8.51 BASIC

0.18

17.15

---

0.66

0.18

0.41

---

---

0.46

17.27

0.28

0.670

0.007

0.81

0.30

0.48

0.007

0.026

0.016

MILLIMETERS

MIN.

NOM.

2.08

3.25

---

---

3.51

MAX.

MIN.

---

3.76

0.082

0.128

0.305

0.040

---

0.300

0.020

0.032

0.019

0.012

0.680

0.011

0.675

---

0.018

---

---

MAX.

0.148

---

NOM.

---

0.138

---

INCHES

2. DIMENSION D DOES NOT INCLUDE MOLD PROTRUSION.

DIMENSION E1 DOES NOT INCLUDE INTERLEAD PROTRUSION.

MOLD PROTRUSION SHALL NOT EXCEED 0.006"(0.15mm) PER SIDE.

INTERLEAD PROTRUSION SHALL NOT EXCEED 0.01"(0.25mm) PER SIDE.

1. CONTROLLING DIMENSION : INCHES

NOTE:

3. DIMENSION b2 DOES NOT INCLUDE DAMBAR PROTRUSION OR

TO LESS THAN 0.001"(0.025mm) BELOW b2 MIN.

DAMBAR INTRUSION SHALL NOT REDUCE THE SHOULDER WIDTH

SHOULDER WIDTH TO EXCEED b2 MAX BY MORE THAN 0.005"(0.127mm)

INTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE

1

6

8

13

A2

A2

2.54 REF.

0.100 REF.