1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Sept. 2002 Rev. 4A

ECO #15528

EDI7F33512C

EDI7F33512C-BNC: 512Kx32 80 PIN SIMM

512Kx32, 2x512Kx32 and 4x512Kx32 Densities

Based on AMDs - AM290F040 Flash Device

Fast Read Access Time - 80-150ns

5- Volt-Only Reprogramming

Sector Erase Architecture

Uniform sectors of 64 Kbytes each

Any combination of sectors can be erased

Also supports full chip erase

Sector Protection

Hardware method that disables any combination of sectors

from write or erase operations

Embedded Erase Algorithms

Automatically preprograms and erases the chip or any com-

bination of sectors

Embedded Program Algorithms

Automatically programs and verifies data at specified ad-

dress

Data Polling and Toggle Bit feature for detection of program or

erase cycle completion

Low Power Dissipation

40mA per Device Active Current

10µA per Device CMOS Standby Current

Typical Endurance >100,000 Cycles

Single 5 Volt ±10% Supply

CMOS and TTL Compatible Inputs and Outputs

Commercial and Industrial Temperature Range

Package

80 Pin SIMM (JEDEC)

The EDI7F33512, EDI7F233512 and EDI7F433512 are organized

as 512Kx32 and 2x512Kx32 and 4x512Kx32 respectively. The

modules are based on AMD's AM29F040 - 512Kx8 Flash Device

in TSOP packages which are mounted on an FR4 substrate.

The modules offer access times between 80 and 150ns allowing

for operation of high-speed microprocessors without wait states.

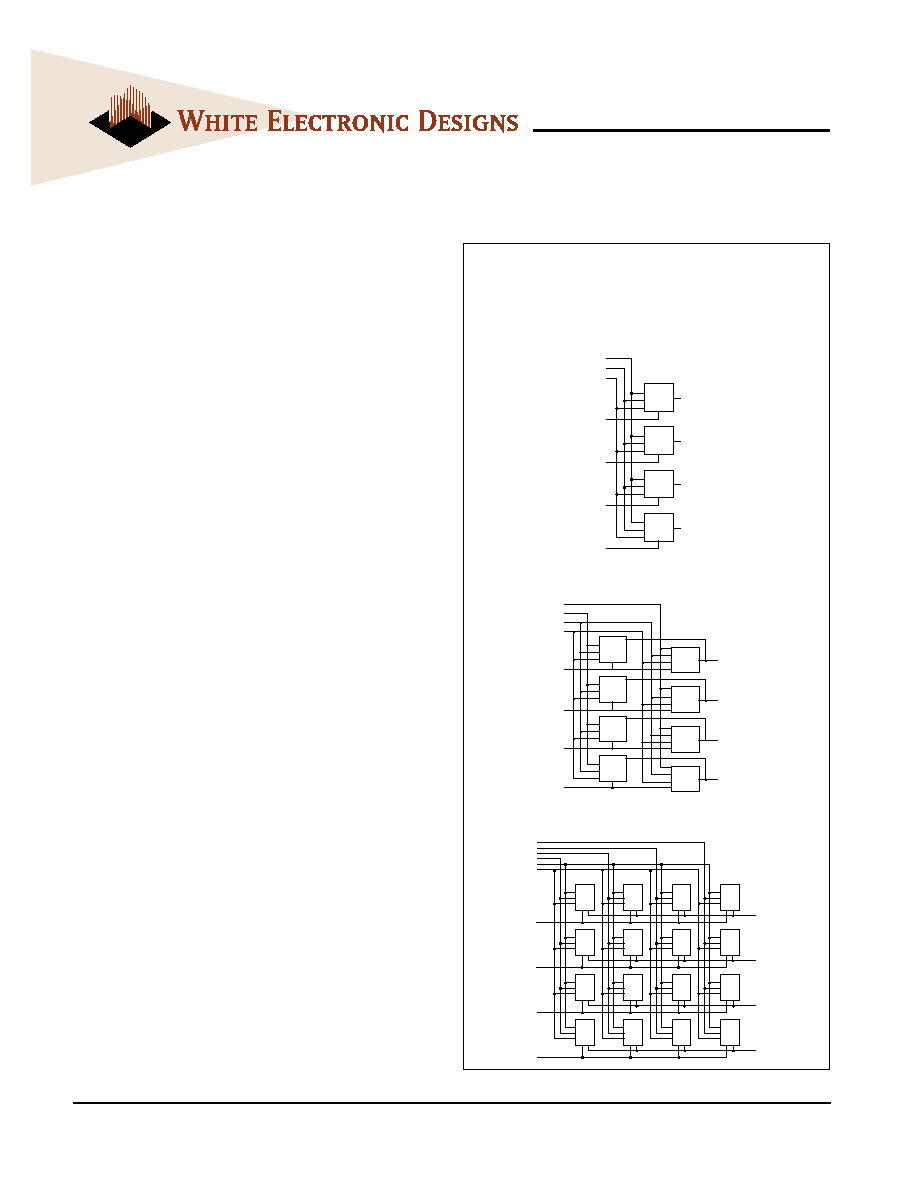

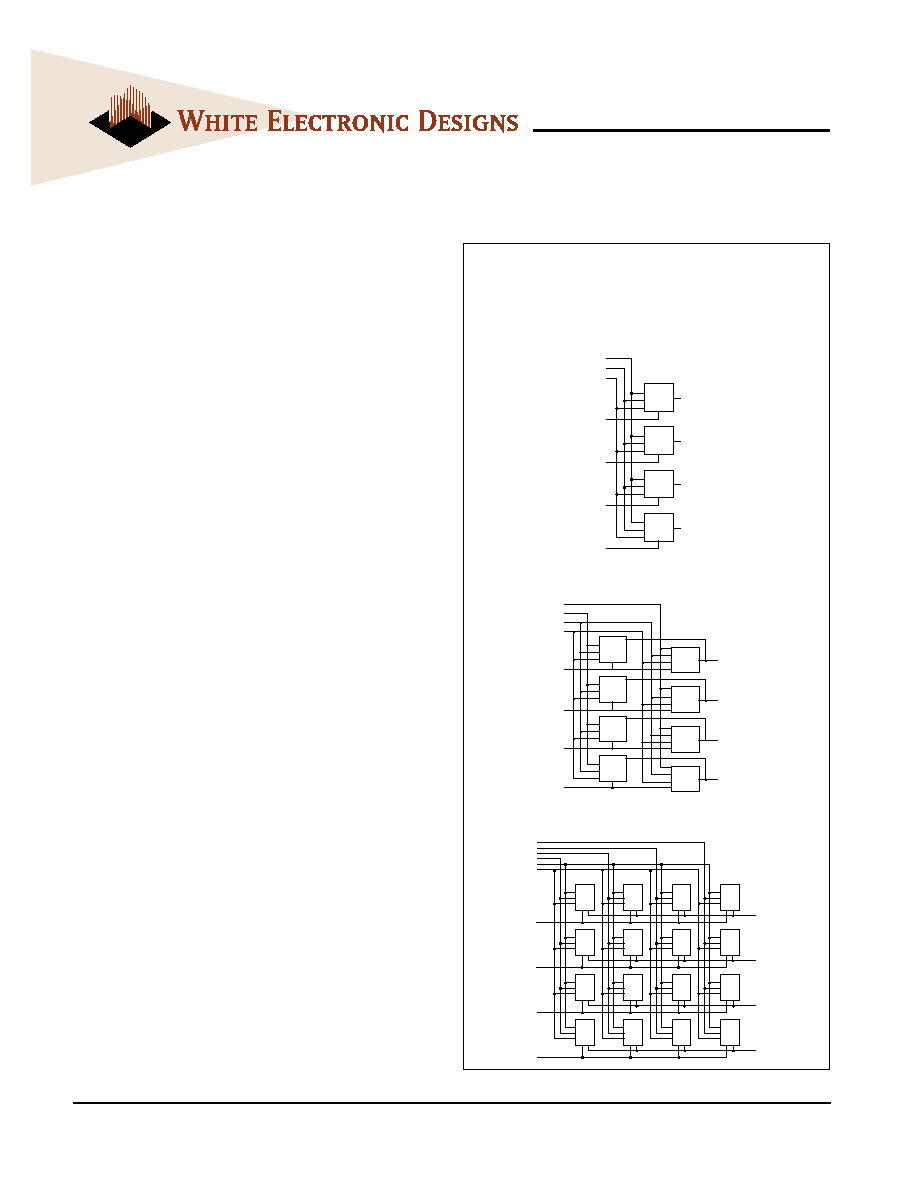

BLOCK DIAGRAMS

EDI7F433512C-BNC: 4x512Kx32 80 PIN SIMM

EDI7F233512C-BNC: 2x512Kx32 80 PIN SIMM

512Kx32 Flash

DESCRIPTION

FEATURES

FIG. 1

512K

X 8

DQ0-DQ7

DQ8-DQ15

DQ16-DQ23

DQ24-DQ31

512K

512K

512K

512K

512K

512K

512K

X 8

X 8

X 8

X 8

X 8

X 8

X 8

G\

W1\

W2\

W3\

A0-A18

E1\

E0\

W0\

512K

X 8

DQ0-DQ7

DQ8-DQ15

DQ16-DQ23

DQ24-DQ31

Eÿ\

G

W0

W1

W2

W3

512K

512K

512K

X 8

X 8

X 8

\

\

\

\

\

A0-A18

A0-A18

G\

W1\

W2\

W3\

X8

512K

X8

512K

X8

512K

X8

512K

DQ0-DQ7

X8

512K

X8

512K

X8

512K

X8

512K

X8

512K

X8

512K

X8

512K

X8

512K

DQ8-DQ15

DQ16-DQ23

DQ24-DQ31

X8

512K

X8

512K

X8

512K

X8

512K

E3\

E2\

E1\

E0\

W0\

DATASHEET APPROVALS

ECO#

EDI PART NO.

NEW REV

DATE

APPROVAL:

INITIAL

DATE

CORRECTION ON PAGES

JUAN GUZMAN

MUKESH TRIVEDI

PAUL MARIEN

LARRY WINROTH

DAVE KELLY

MARK DOWNEY

DAVE HARRISON

TONY LEE

BOB KHEDERIAN

LUIS ESTELLA

YES

NO

LINE

:________

WILL THIS DATASHEET GO ON THE WEB?

FAMILY:

____________

PROD.TYPE:

________

ORG:___________

IS THIS A NEW DATASHEET?

DENSITY:________

SPEED:__________

WILL THIS DATASHEET REPLACE AN EXISTING

PKG:____________

DATASHEET THAT'S ALREADY ON THE WEB?

VOLTAGE:________

IF YES, WHAT DATASHEET IS IT REPLACING?

WHAT SECTION SHOULD THIS DATASHEET BE

PLACED IN ON THE WEB?

AFTER REVIEWING OR MAKING CORRECTIONS ON THE DATASHEET (S)

PLEASE SIGN-OFF ON THIS SHEET AND ,MAKE YOUR CORRECTIONS ≠ON

THE ORIGINAL COPY(S).

AFTER REVIEWING THE DATA SHEET, TEST ENGINEERING WILL COMPLETE THE SECTION BELOW.

TEST PROGRAM CHANGE REQUIRED:

YES:_________NO____________DATE:___________

TEST ENGINEER SIGNATURE___________________

IF YES, DO NOT RELEASE DATA SHEET UNTIL TEST PROGRAM CHANGE IS COMPLETED.

TEST PROGRAM CHANGE COMPLETION DATE:__________

TEST PROGRAM NAME AND REVISION_________________

TEST ENGINEER SIGNATURE__________________________

FO-00342R1.DOC

ECO# 14942

SHEET 1 OF

1

9/25/02

9/26/02

9/27/02

L.K.

M.A.

EDI7F33512C

15528

4A

9/24/02