1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

July 2002 Rev. 13A

ECO #15405

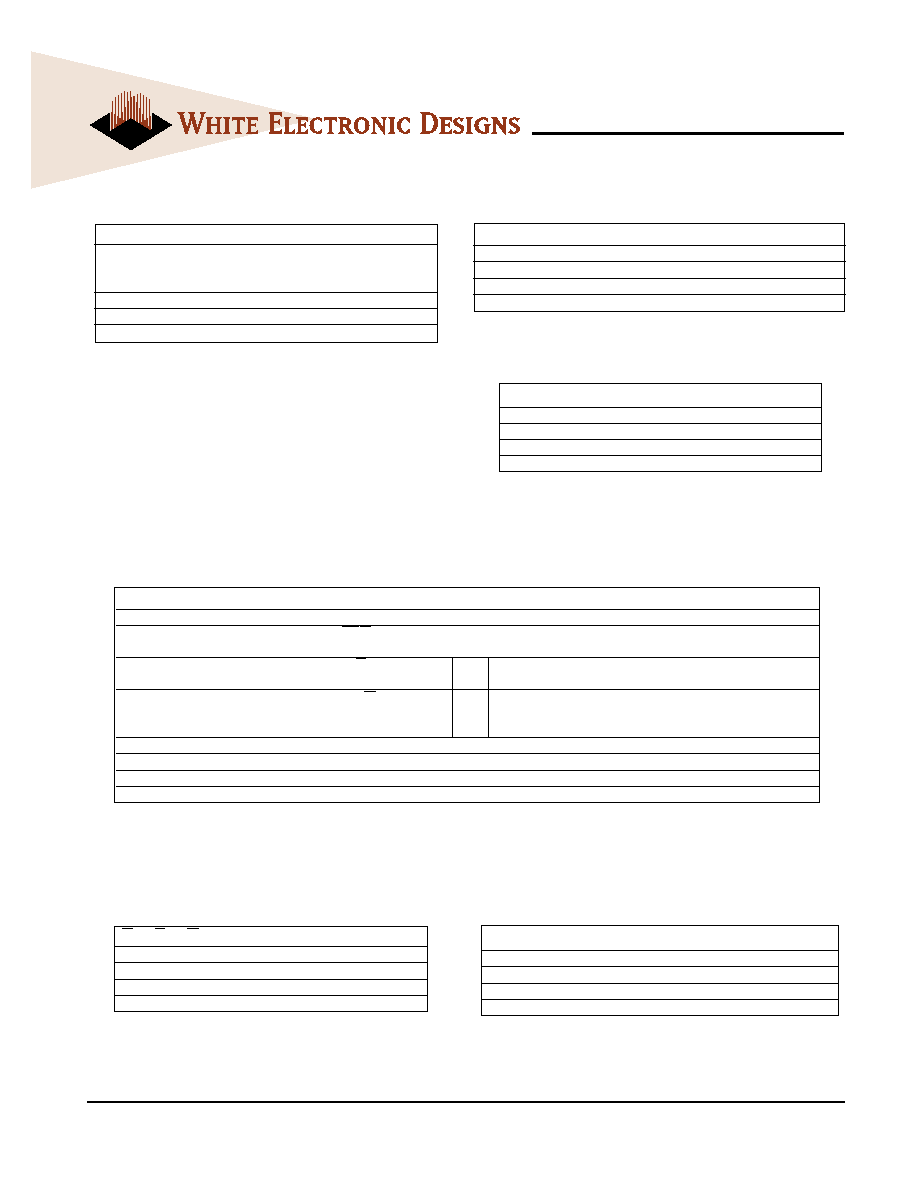

EDI8F8512C

P

IN

C

ONFIGURATIONS

AND

B

LOCK

D

IAGRAM

FEATURES

n 512Kx8 bit CMOS Static

n Random Access Memory

Access Times 20 through 100ns

Data Retention Function (EDI8F8512LP)

TTL Compatible Inputs and Outputs

Fully Static, No Clocks

n High Density Packaging

36 Pin SIP, No. 63

32 Pin DIP, JEDEC Pinout, No. 91 (55-100ns)

32 Pin DIP, JEDEC Pinout, No. 183 (20-35ns)

n Single +5V (±10%) Supply Operation

20-55ns

P

IN

N

AMES

The EDI8F8512C is a 4096K bit CMOS Static RAM based on four

128Kx8 or 256Kx4 (high speed) Static RAMs mounted on a multi-

layered epoxy laminate (FR4) substrate.

Functional equivalence to the monolithic four megabit Static

RAM is achieved by utilization of an on-board decoder that

interprets the higher order address(es) to select one of the128Kx8

or 256Kx4 Static RAMs.

The 32 pin DIP pinout adheres to the JEDEC standard for the four

megabit device, to ensure compatibility with future monolithics.

A low power version with data retention (EDI8F8512LP) is also

available.

All inputs and outputs are TTL compatible and operate from a

single 5V supply. Fully asynchronous, the EDI8F8512C requires

no clocks or refreshing for operation.

55-100ns

20-35ns

512Kx8 STATIC RAM CMOS, MODULE

DESCRIPTION

Aÿ-A18

Address Inputs

E

Chip Enable

W

Write Enable

G

Output Enable

DQÿ-DQ7

Common Data Input/Output

VCC

Power (+5V±10%)

VSS

Ground

NC

No Connection

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

NC

VCC

W

DQ2

DQ3

DQ0

A1

A2

A3

A4

VSS

DQ5

A10

A11

A5

A13

A14

NC

E

A15

A16

A12

A18

A6

DQ1

VSS

A0

A7

A8

A9

DQ7

DQ4

DQ6

A17

VCC

G

8F8512C Pin Config.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

A18

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ1

DQ2

VSS

8F8512C Pin Config

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

VCC

A15

A17

W

A13

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5

DQ4

DQ3

DQ

0-7

128K x 8

128K x 8

128K x 8

128K x 8

A

0-16

W

G

A

17-A18

E

DECODER

8F8512C Blk Dia

DQ

4-7

256K x 4

256K x 4

256K x 4

256K x 4

A

0-17

W

G

A18

E

DECODER

8F8512C Blk Dia2

DQ

0-3

FIG. 1

2

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

July 2002 Rev. 13A

ECO #15405

EDI8F8512C

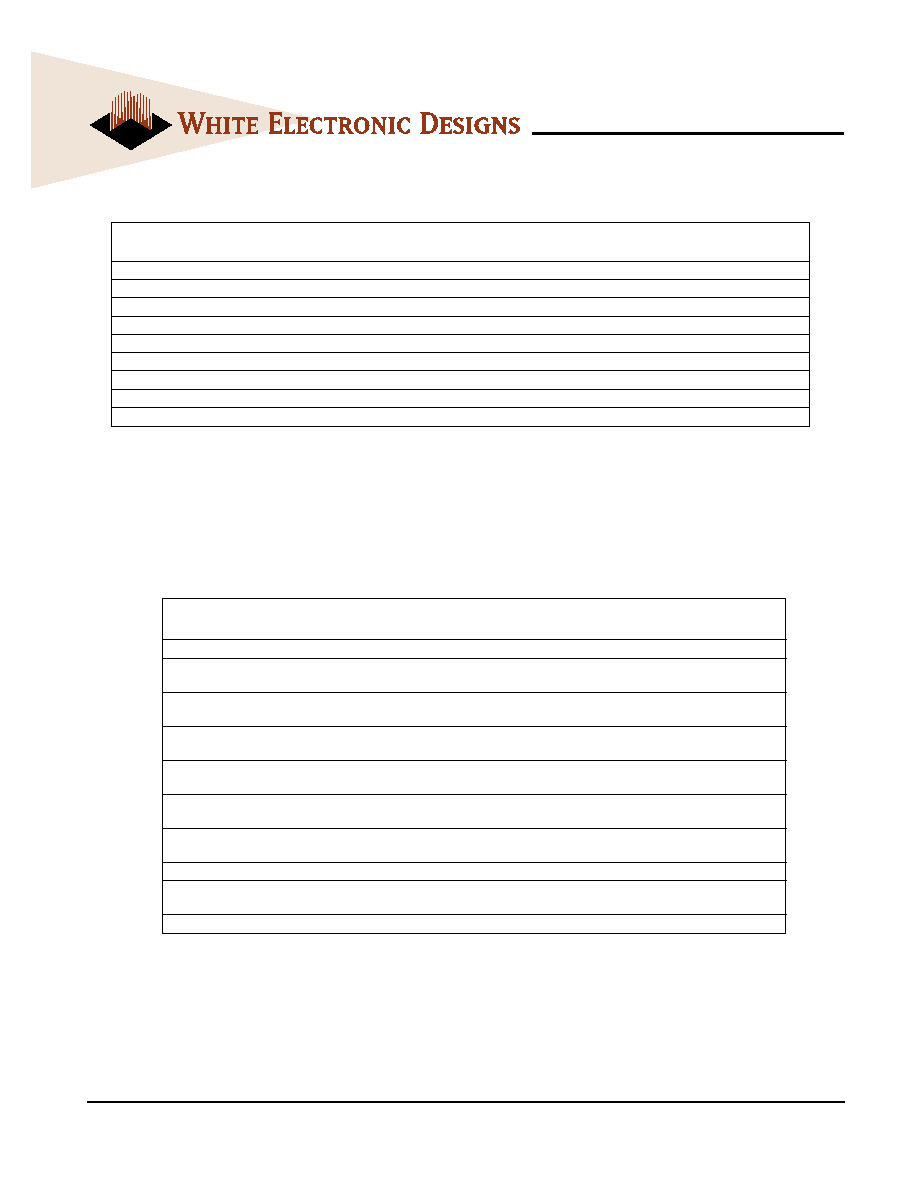

A

BSOLUTE

M

AXIMUM

R

ATINGS

*

R

ECOMMENDED

DC O

PERATING

C

ONDITIONS

DC E

LECTRICAL

C

HARACTERISTICS

*Typical: TA=25∞C, VCC=5.0V

C

APACITANCE

T

RUTH

T

ABLE

(f=1.0MHz, VIN=VCC or VSS)

AC T

EST

C

ONDITIONS

(note: For TEHQZ,TGHQZ and TWLQZ, CL = 5pF)

These parameters are sampled, not 100% tested.

*Stress greater than those listed under "Absolute Maximum Ratings" may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions greater than those indicated in the

operational sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect reliability.

Voltage on any pin relative to VSS

-0.5V to 7.0V

Operating Temperature TA (Ambient)

Commercial

0∞C to +70∞C

Industrial

-40∞C to +85∞C

Storage Temperature

-55∞C to +125∞C

Power Dissipation

4 Watts

Output Current

20 mA

Parameter

Sym

Min

Typ

Max

Units

Supply Voltage

VCC

4.5

5.0

5.5

V

Supply Voltage

VSS

0

0

0

V

Input High Voltage

VIH

2.2

--

6.0

V

Input Low Voltage

VIL

-0.3

--

0.8

V

Input Pulse Levels

VSS to 3.0V

Input Rise and Fall Times

5ns

Input and Output Timing Levels

1.5V

Output Load 20-35ns

1TTL = 30pF

70-100ns

1TTL, CL =100pF

G

E

W

Mode

Output

Power

X

H

X

Standby

High Z

ICC2, ICC3

H

L

H

Output Deselect High Z

ICC1

L

L

H

Read

DOUT

ICC1

X

L

L

Write

DIN

ICC1

Parameter

Sym

Max

Unit

Address Lines

CI

30

pF

Data Lines

CD/Q

43

pF

Chip Enable Line

CC

10

pF

Write and Output Enable Lines

CW

32

pF

Parameter

Sym

Conditions

Min

Typ*

Max

Units

[35

·55 20-25 35 55-100

ns

Operating Power

ICC1 W, E = VIL, II/O = 0mA,

--

340

70

570 390 130

mA

Supply Current

Min Cycle

Standby (TTL) Power

ICC2

E · VIH, VIN VIL

DIP

--

50

10

85

85

55

mA

Supply Current

VIN · VIH

SIP

--

--

--

--

--

65

mA

Full Standby Power

ICC3

E · VCC-0.2V

C

--

5

2

40

40

5

mA

Supply Current (CMOS)

VIN · VCC-0.2V or

LP

--

--

40

--

--

400

µA

VIN [ 0.2V

Input Leakage Current

ILI

VIN = 0V to VCC

--

--

--

±10 ±10 ±10

µA

Output Leakage Current

ILO

V I/O = 0V to VCC

--

--

--

±10 ±10 ±10

µA

Output High Voltage

VOH IOH=-1.0mA (·70),or -4.0([35)

2.4

--

--

--

--

--

V

Output Low Voltage

VOL IOL = 2.1mA (·70),or 8.0mA([35) --

--

--

0.4

0.4 0.4

V

3

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

July 2002 Rev. 13A

ECO #15405

EDI8F8512C

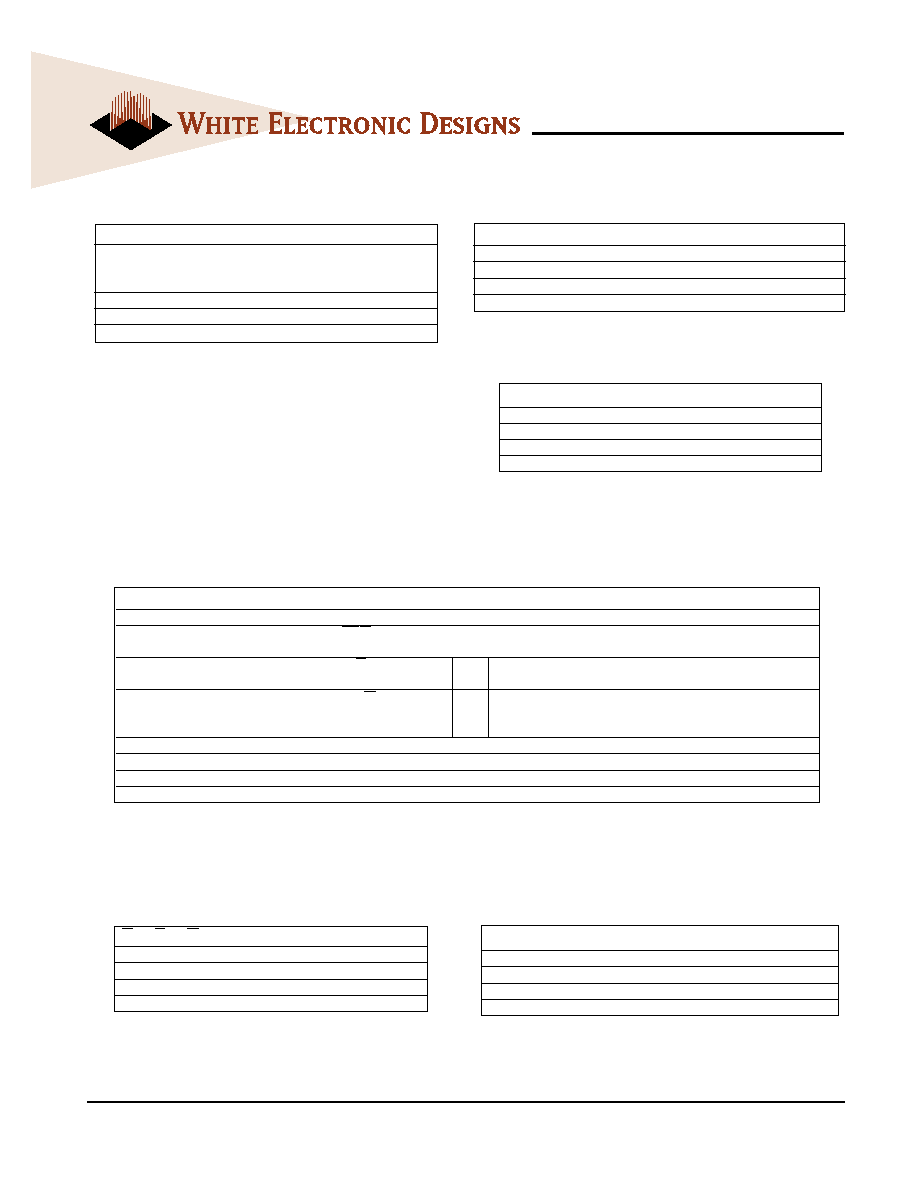

AC C

HARACTERISTICS

R

EAD

C

YCLE

R

EAD

C

YCLE

2 - W H

IGH

Symbol20ns

25ns

35ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Min

Max

Units

Read Cycle Time

TAVAV

TRC

20

25

35

ns

Address Access Time

TAVQV

TAA

20

25

35

ns

Chip Enable Access Time

TELQVTACS

20

25

35

ns

Chip Enable to Output in Low Z (1)

TELQX

TCLZ

3

3

3

ns

Chip Disable to Output in High Z (1)

TEHQZ

TCHZ

10

12

15

ns

Output Hold from Address Change

TAVQX

TOH

3

3

3

ns

Output Enable to Output Valid

TGLQV

TOE

13

15

20

ns

Output Enable to Output in Low Z (1) TGLQX

TOLZ

0

0

0

ns

Output Disable to Output in High Z(1) TGHQZ

TOHZ

8

10

12

ns

Note 1: Parameter guaranteed, but not tested.

R

EAD

C

YCLE

1 - W H

IGH

, G, E L

OW

FIG. 2

FIG. 3

ADDRESS 1

ADDRESS 2

TAVAV

DATA 1

DATA 2

TAVQV

TAVQX

8F8512C Rd Cyc1

A

Q

TGHQZ

TELQV

TELQX

E

G

Q

TEHQZ

A

TAVAV

TGLQV

TGLQX

TAVQV

8F8512C Rd Cyc2

4

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

July 2002 Rev. 13A

ECO #15405

EDI8F8512C

AC C

HARACTERISTICS

R

EAD

C

YCLE

Symbol55ns

70ns

85ns

100ns

Parameter

JEDEC

Alt.

Min

Max

Min Max

Min Max

Min Max

Units

Read Cycle Time

TAVAV

TRC

55

70

85

100

ns

Address Access Time

TAVQV

TAA

55

70

85

100

ns

Chip Enable Access Time

TELQVTACS

55

70

85

100

ns

Chip Enable to Output in Low Z (1)

TELQX

TCLZ

5

5

5

5

ns

Chip Disable to Output in High Z (1)

TEHQZ

TCHZ

30

30

35

40

ns

Output Hold from Address Change

TAVQX

TOH

3

3

3

3

ns

Output Enable to Output Valid

TGLQV

TOE

40

40

45

50

ns

Output Enable to Output in Low Z (1) TGLQX

TOLZ

0

0

0

0

ns

Output Disable to Output in High Z(1) TGHQZ

TOHZ

30

30

35

40

ns

Note 1: Parameter guaranteed, but not tested.

Note 1: Parameter guaranteed, but not tested.

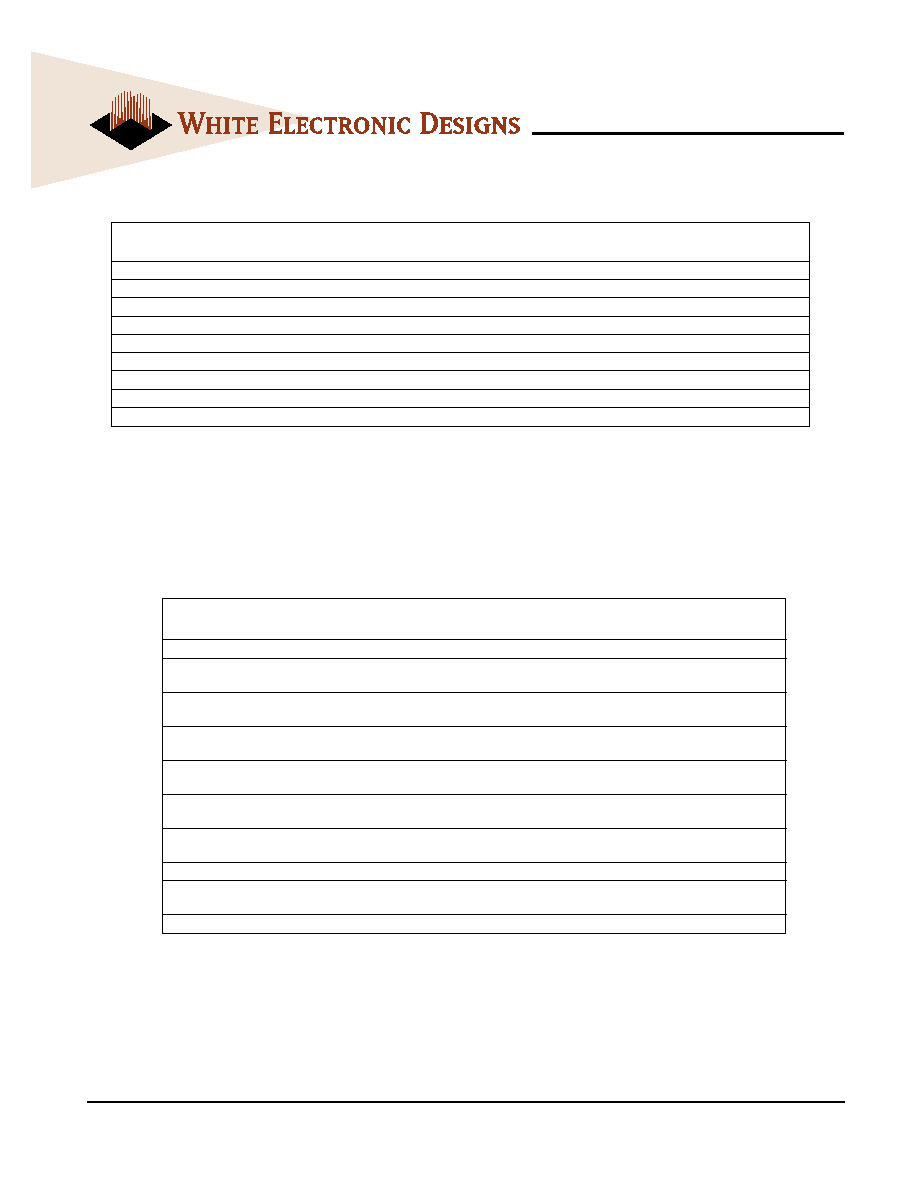

AC C

HARACTERISTICS

W

RITE

C

YCLE

Write Cycle

Symbol

20ns

25ns

35ns

Parameter

JEDEC

Alt

Min

Max

Min Max

Min Max

Units

Write Cycle Time

TAVAV

TWC

20

25

35

ns

Chip Enable to End of Write

TELWH

TCW

15

20

30

ns

TELEH

TCW

15

20

30

ns

Address Setup Time

TAVWL

TAS

0

0

0

ns

TAVEL

TAS

0

0

0

ns

Address Valid to End of Write

TAVWH

TAW

15

20

30

ns

TAVEH

TAW

15

20

30

ns

Write Pulse Width

TWLWH

TWP

15

20

25

ns

TWLEH

TWP

15

20

25

ns

Write Recovery Time

TWHAX

TWR

0

0

0

ns

TEHAX

TWR

0

0

0

ns

Data Hold Time

TWHDX

TDH

3

3

3

ns

TEHDX

TDH

3

3

3

ns

Write to Output in High Z (1)

TWLQZ

TWHZ

0

10

0

12

0

15

ns

Data to Write Time

TDVWH

TDW

12

15

20

ns

TDVEH

TDW

12

15

20

ns

Output Active from End of Write (1)

TWHQX

TWLZ

3

3

3

ns

5

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

July 2002 Rev. 13A

ECO #15405

EDI8F8512C

Symbol55NS

70ns

85n

100ns

Parameter

JEDEC

Alt.

Min

Max

Min

Max

Min Max

Min Max

Units

Write Cycle Time

TAVAV

TWC

55

70

85

100

ns

Chip Enable to End of Write

TELWH

TCW

50

65

70

80

ns

TELEH

TCW

50

65

70

80

ns

Address Setup Time

TAVWL

TAS

0

0

0

0

ns

TAVEL

TAS

0

0

0

0

ns

Address Valid to End of Write

TAVWH

TAW

50

65

70

80

ns

TAVEH

TAW

50

65

70

80

ns

Write Pulse Width

TWLWH

TWP

50

65

70

80

ns

TWLEH

TWP

50

65

70

80

ns

Write Recovery Time

TWHAX

TWR

0

0

0

0

ns

TEHAX

TWR

0

0

0

0

ns

Data Hold Time

TWHDX

TDH

0

0

0

0

ns

TEHDX

TDH

0

0

0

0

ns

Write to Output in High Z (1)

TWLQZ

TWHZ

0

30

0

30

0

35

0

40

ns

Data to Write Time

TDVWH

TDW

30

30

35

40

ns

TDVEH

TDW

30

30

35

40

ns

Output Active from End of Write (1)

TWHQX

TWLZ

5

5

5

5

ns

Note 1: Parameter guaranteed, but not tested.

AC C

HARACTERISTICS

W

RITE

C

YCLE

W

RITE

C

YCLE

1 - W C

ONTROLLED

FIG. 6

E

A

TAVAV

TELWH

TAVWH

TWLWH

TAVWL

TWHAX

W

HIGH Z

DATA VALID

TWLQZ

TWHQX

TDVWH

TWHDX

Q

D

8F8512C Write Cyc1