W3E32M72S-XBX

1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

32Mx72 DDR SDRAM

FEATURES

Data rate = 200, 250, 266, 333Mbs

Package:

∑ 219 Plastic Ball Grid Array (PBGA), 32 x 25mm

2.5V ±0.2V core power supply

2.5V I/O (SSTL_2 compatible)

Differential clock in puts (CK and CK#)

Commands entered on each positive CK edge

Internal pipelined double-data-rate (DDR)

ar chi tec ture; two data accesses per clock cy cle

Programmable Burst length: 2,4 or 8

Bidirectional data strobe (DQS) transmitted/

re ceived with data, i.e., source-syn chro nous data

capture (one per byte)

DQS edge-aligned with data for READs; center-

aligned with data for WRITEs

DLL to align DQ and DQS transitions with CK

Four internal banks for concurrent operation

Data mask (DM) pins for masking write data

(one per byte)

Programmable

IOL/IOH

option

Auto precharge option

Auto Refresh and Self Refresh Modes

Commercial, Industrial and Military

TemperatureRang es

Organized as 32M x 72

Weight: W3E32M72S-XBX ≠ 3.0 grams typical

* This product is subject to change without notice.

BENEFITS

40%

SPACE

SAVINGS

vs.

TSOP

Re

duced part count

34% I/O reduction vs TSOP

Re

duced trace lengths for low er par a sit ic

ca pac i tance

Suit

able for hi-re li abil i ty ap pli ca tions

Lam

i nate in ter pos er for op ti mum TCE match

GENERAL DESCRIPTION

The 256MByte (2Gb) DDR SDRAM is a high-speed CMOS,

dy nam ic ran dom-access, memory using 5 chips containing

536,870,912 bits. Each chip is internally configured as a

quad-bank DRAM.

The 256MB DDR SDRAM uses a double data rate

ar chi tec ture to achieve high-speed operation. The

double data rate ar chi tec ture is essentially a 2n-prefetch

architecture with an in ter face designed to transfer two data

words per clock cycle at the I/O pins. A single read or write

access for the 256MB DDR SDRAM effectively consists

of a single 2n-bit wide, one-clock-cycle data tansfer at the

internal DRAM core and two cor re spond ing n-bit wide,

one-half-clock-cycle data transfers at the I/O pins.

A bi-directional data strobe (DQS) is transmitted

externally, along with data, for use in data capture at the

receiver.strobe transmitted by the DDR SDRAM during

READs and by the memory contoller during WRITEs. DQS

is edge-aligned with data for READs and center-aligned

with data for WRITEs. Each chip has two data strobes, one

for the lower byte and one for the upper byte.

The 256MB DDR SDRAM operates from a differential clock

(CK and CK#); the crossing of CK going HIGH and CK#

going LOW will be referred to as the positive edge of CK.

Com mands (ad dress and control signals) are registered

at every positive edge of CK. Input data is registered on

both edg es of DQS, and out put data is ref er enced to both

edges of DQS, as well as to both edges of CK.

W3E32M72S-XBX

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

DENSITY COMPARISONS

Read and write accesses to the DDR SDRAM are burst

ori ent ed; accesses start at a selected location and continue

for a pro grammed number of locations in a programmed

sequence. Accesses begin with the registration of an

AC TIVE command, which is then followed by a READ or

WRITE command. The address bits registered coincident

with the ACTIVE command are used to select the bank

and row to be accessed. The ad dress bits registered

coincident with the READ or WRITE com mand are used

to select the bank and the starting column location for the

burst access.

The DDR SDRAM provides for programmable READ

or WRITE burst lengths of 2, 4, or 8 locations. An auto

precharge func tion may be enabled to provide a self-

timed row precharge that is initiated at the end of the

burst access.

The pipelined, multibank architecture of DDR SDRAMs al lows

for concurrent operation, thereby providing high ef fec tive

band width by hiding row precharge and activation time.

An auto refresh mode is provided, along with a power-

saving power-down mode. All inputs are compatible with

the Jedec Standard for SSTL_2. All full drive options

outputs are SSTL_2, Class II compatible.

Area

5 x 265mm

2

= 1325mm

2

800mm

2

40%

5 x 66 pins = 330 pins

219 Balls

34%

S

A

V

I

N

G

S

I/O

Count

TSOP Approach (mm)

22.3

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

11.9

66

TSOP

Actual Size

W3E32M72S-XBX

22

16

FUNCTIONAL DE SCRIP TION

Read and write accesses to the DDR SDRAM are burst

ori ent ed; accesses start at a selected location and continue

for a pro grammed number of locations in a pro grammed

se quence. Ac cess es begin with the registration of an

AC TIVE com mand which is then followed by a READ or

WRITE com mand. The address bits registered coincident

with the AC TIVE command are used to select the bank and

row to be accessed (BA0 and BA1 select the bank, A0-12

select the row). The address bits registered coincident

with the READ or WRITE com mand are used to select the

start ing column location for the burst access.

Prior to normal operation, the DDR SDRAM must be

initialized. The following sections provide detailed

information cov er ing device initialization, register defi nition,

command de scrip tions and de vice operation.

INITIALIZATION

DDR SDRAMs must be powered up and initialized in a

pre defi ned manner. Operational procedures other than

those specifi ed may result in undefi ned operation. Power

must fi rst be applied to V

CC

and V

CCQ

simultaneously, and

then to V

REF

(and to the system V

TT

). V

TT

must be applied

W3E32M72S-XBX

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

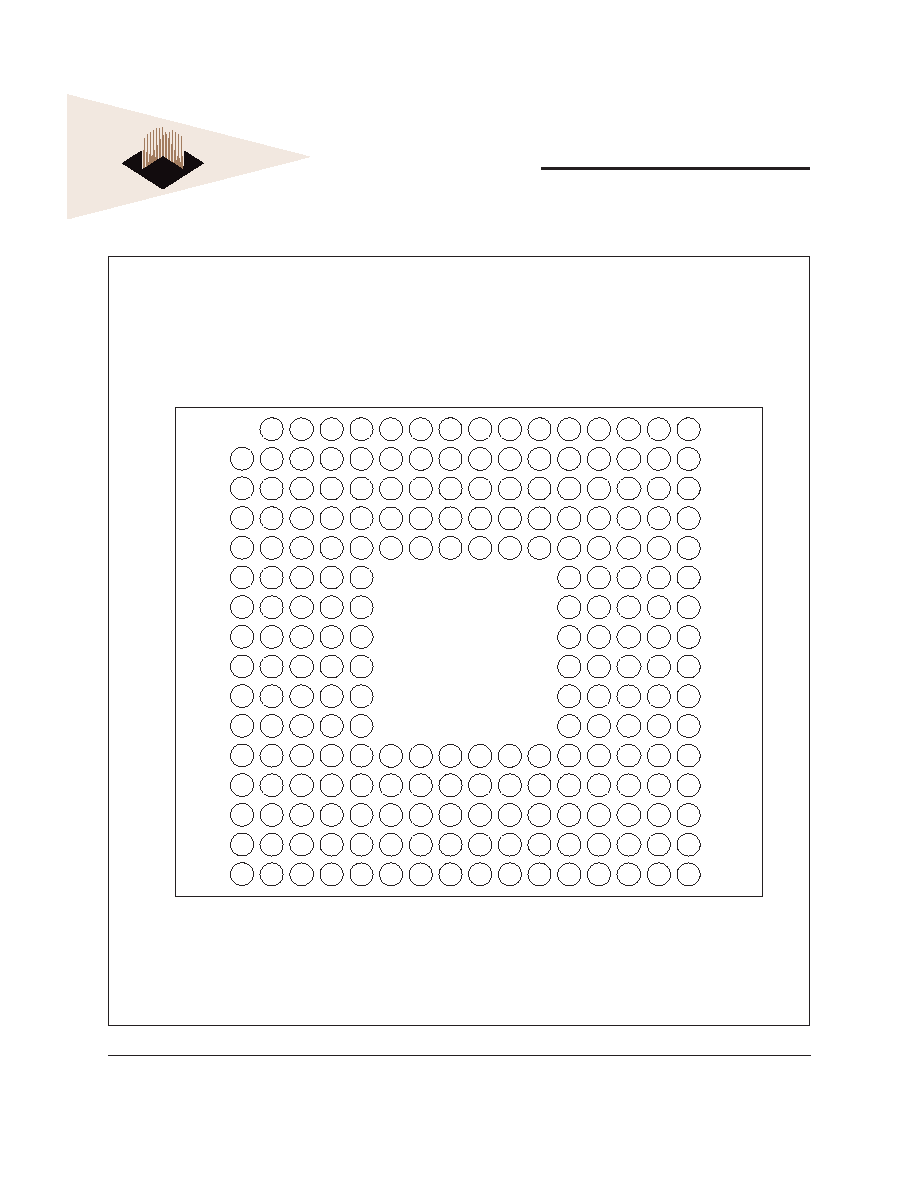

FIGURE 1 ≠ PIN CONFIGURATION

NOTE: DNU = Do Not Use.

Top View

1

2

3

4

5

6

7

8

9 10

11 12 13 14

15 16

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

DQ1

DQ3

DQ6

DQ7

CAS0#

CS0#

V

SS

V

SS

CLK3#

NC

DQ56

DQ57

DQ60

DQ62

V

SS

V

SS

DQ30

DQ28

DQ25

DQ24

CLK1

CKE1

V

CC

V

CC

CS2#

CAS2#

DQ39

DQ38

DQ35

DQ33

V

CC

DQ0

DQ2

DQ4

DQ5

DQML0

WE0#

RAS0#

V

SS

V

SS

CKE3

CLK3

DQMH3

DQ58

DQ59

DQ61

DQ63

DQ31

DQ29

DQ27

DQ26

NC

DQMH1

CLK1#

V

CCQ

V

CCQ

RAS2#

WE2#

DQML2

DQ37

DQ36

DQ34

DQ32

DQ14

DQ12

DQ10

DQ8

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

DQ55

DQ53

DQ51

DQ49

DQ17

DQ19

DQ21

DQ23

V

SS

V

SS

V

SS

Vss

V

SS

V

SS

V

SS

V

SS

DQ40

DQ42

DQ44

DQ46

DQ15

DQ13

DQ11

DQ9

DQMH0

CLK0

CKE0

V

CCQ

V

CCQ

CS3#

CAS3#

WE3#

DQ54

DQ52

DQ50

DQ48

DQ16

DQ18

DQ20

DQ22

DQML1

WE1#

CS1#

V

SS

V

SS

CKE2

CLK2

DQMH2

DQ41

DQ43

DQ45

DQ47

V

SS

V

SS

V

CC

V

CCQ

DQSH3

DQSL3

CLK0#

V

SS

V

SS

DQSL4

RAS3#

DQML3

DQSH4

V

SS

V

CC

V

CCQ

V

CCQ

V

CC

V

SS

V

SS

V

REF

RAS1#

CAS1#

V

CC

V

CC

CLK2#

DQSL2

CS4#

DQSH2

V

CC

V

SS

V

SS

A9

A0

A2

A12

DQSH0

DQMH4

DQ73

DQ75

DQ77

DQ79

A8

A1

A3

DNU

DQSL1

WE4#

DQ70

DQ68

DQ66

DQ64

A10

A7

A5

DNU

BA0

CLK4

DQ72

DQ74

DQ76

DQ78

A11

A6

A4

DNU

BA1

CAS4#

DQ71

DQ69

DQ67

DQ65

V

SS

V

SS

V

CC

V

CCQ

DQSL0

CKE4

CLK4#

V

SS

V

CC

V

CCQ

V

CCQ

V

CC

V

SS

V

SS

DQSH1

RAS4#

DQML4

V

CC

V

SS

V

SS

W3E32M72S-XBX

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

A

0-12

BA

0-1

CK

0

#

CK#

DQ

0

DQ

15

CKE

B

CKE

DM

0

DQML

DM

1

DQMH

DQ

0

DQ

15

U1

A

0-12

BA

0-1

CK

1

#

CK#

16

DQ

31

RAS

B

#

WE

B

#

CAS

B

#

DQ

0

DQ

15

U0

CKE

B

CKE

DM

2

DQML

DM

3

DQMH

DQ

0

DQ

15

U2

A

0-12

BA

0-1

CK

2

#

CK#

DQ

32

DQ

47

CKE

B

CKE

DM

4

DQML

DM

5

DQMH

DQ

0

DQ

15

U3

A

0-12

BA

0-1

CK

3

#

CK#

DQ

48

DQ

63

CKE

B

CKE

DQS

6

DQSL

DQS

7

DQSH

DQ

0

DQ

15

U4

A

0-12

BA

0-1

CK

4

#

CK#

DQ

64

DQ

79

CKE

B

CKE

DQS

8

DQSL

DQS

9

DQSH

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

DQ

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

Y

=

CK

4

CK

V

REF

CK

3

CK

V

REF

DQS

4

DQSL

DQS

5

DQSH

V

REF

DQS

2

DQSL

DQS

3

DQSH

V

REF

DQS

0

DQSL

DQS

1

DQSH

V

REF

CK

2

CK

CK

1

CK

CK

0

CK

V

REF

DM

6

DQML

DM

7

DQMH

DM

8

DM

9

DQML

DQMH

A

0-12

BA

0

-

1

CS

B

#

CAS#

WE# RAS#

CS#

CAS#

WE# RAS#

CS#

CAS#

WE# RAS#

CS#

CAS#

WE# RAS#

CS#

CAS#

WE# RAS#

CS#

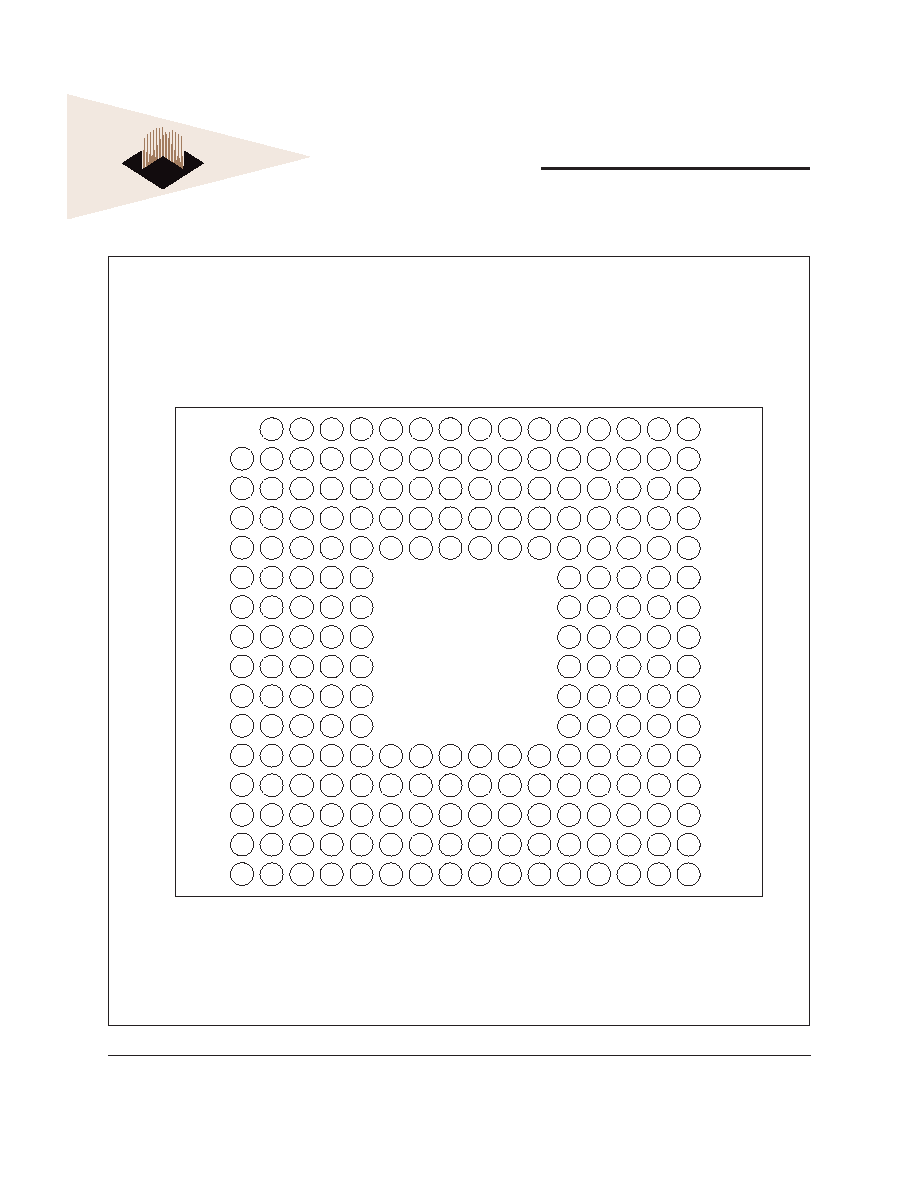

FIGURE 2 ≠ FUNCTIONAL BLOCK DIAGRAM

after V

CCQ

to avoid device latch-up, which may cause

per ma nent dam age to the device. V

REF

can be applied any

time after V

CCQ

but is expected to be nominally coincident

with V

TT

. Except for CKE, inputs are not recognized as

valid until after VREF is applied. CKE is an SSTL_2

input but will detect an LVCMOS LOW level after V

CC

is

applied. After CKE passes through V

IH

, it will transition to

an SSTL_2 signal and remain as such until power is cycled.

Maintaining an LVCMOS LOW level on CKE during power-

up is required to ensure that the DQ and DQS outputs will

be in the High-Z state, where they will remain until driven

in normal operation (by a read ac cess). After all power

supply and reference voltages are stable, and the clock

is stable, the DDR SDRAM requires a 200µs delay prior

to applying an executable com mand.

Once the 200µs delay has been satisfi ed, a DESELECT

or NOP command should be applied, and CKE should

be brought HIGH. Following the NOP command, a

PRECHARGE ALL command should be applied. Next a

LOAD MODE REG IS TER command should be issued for

the extended mode register (BA1 LOW and BA0 HIGH)

to enable the D

LL

, fol lowed by another LOAD MODE

REGISTER command to the mode register (BA0/BA1

both LOW) to reset the D

LL

and to program the operating

parameters. Two-hundred clock cy cles are required

between the DLL reset and any READ command. A

PRECHARGE ALL command should then be applied,

placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must

be performed (t

RFC

must be satisfi ed.) Additionally, a LOAD

MODE REGISTER command for the mode register with

the reset DLL bit deactivated (i.e., to program operating

pa ram e ters without resetting the DLL) is required.

Following these requirements, the DDR SDRAM is ready

for normal op er a tion.

W3E32M72S-XBX

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

REGISTER DEFINITION

MODE REGISTER

The Mode Register is used to defi ne the specifi c mode of

op er a tion of the DDR SDRAM. This defi nition includes the

selection of a burst length, a burst type, a CAS latency,

and an op er at ing mode, as shown in Figure 3. The Mode

Reg is ter is programmed via the MODE REG IS TER SET

command (with BA0 = 0 and BA1 = 0) and will retain

the stored in for ma tion until it is pro grammed again or

the device loses power. (Ex cept for bit A8 which is self

clearing).

Reprogramming the mode register will not alter the contents

of the memory, provided it is performed correctly. The Mode

Reg is ter must be load ed (reloaded) when all banks are

idle and no bursts are in progress, and the con trol ler must

wait the spec i fi ed time be fore ini ti at ing the sub se quent

op er a tion. Vi o lat ing either of these re quire ments will result

in un spec i fi ed operation.

Mode register bits A0-A2 specify the burst length, A3

spec i fi es the type of burst (sequential or in ter leaved),

A4-A6 spec i fy the CAS latency, and A7-A12 specify the

op er at ing mode.

BURST LENGTH

Read and write ac cess es to the DDR SDRAM are burst

ori ent ed, with the burst length being programmable,

as shown in Fig ure 3. The burst length determines

the maximum num ber of column lo ca tions that can be

accessed for a given READ or WRITE command. Burst

lengths of 2, 4 or 8 lo ca tions are avail able for both the

sequential and the in ter leaved burst types.

Reserved states should not be used, as unknown op er a tion

or incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of

col umns equal to the burst length is effectively selected.

All accesses for that burst take place within this block,

mean ing that the burst will wrap within the block if a

boundary is reached. The block is uniquely selected by

A1-Ai when the burst length is set to two; by A2-Ai when the

burst length is set to four (where Ai is the most signifi cant

column address for a given confi guration); and by A3-Ai

when the burst length is set to eight. The remaining (least

sig nifi cant) ad dress bit(s) is (are) used to select the starting

lo ca tion within the block. The pro grammed burst length

ap plies to both READ and WRITE bursts.

BURST TYPE

Accesses within a given burst may be pro grammed to be

either se quen tial or interleaved; this is re ferred to as the

burst type and is selected via bit M3.

The ordering of accesses within a burst is de ter mined by

the burst length, the burst type and the start ing column

address, as shown in Table 1.

READ LATENCY

The READ latency is the delay, in clock cycles, between

the reg is tra tion of a READ command and the avail abil i ty

of the fi rst bit of output data. The latency can be set to 2

or 2.5 clocks.

If a READ command is registered at clock edge n, and the

latency is m clocks, the data will be available by clock edge

n+m. Table 2 below indicates the op er at ing fre quen cies at

which each CAS latency setting can be used.

Reserved states should not be used as unknown operation

or incompatibility with future versions may result.

OPERATING MODE

The normal operating mode is selected by issuing a MODE

REGISTER SET command with bits A7-A12 each set to

zero, and bits A0-A6 set to the desired values. A DLL reset

is initiated by issuing a MODE REGISTER SET command

with bits A7 and A9-A12 each set to zero, bit A8 set to one,

and bits A0-A6 set to the desired values. Although not

re quired, JEDEC specifi cations recommend when a LOAD

MODE REG IS TER command is issued to reset the DLL, it

should always be followed by a LOAD MODE REGISTER

command to se lect nor mal op er at ing mode.

All other combinations of values for A7-A12 are reserved

for future use and/or test modes. Test modes and reserved

states should not be used because unknown operation or

incompatibility with future versions may result.

EXTENDED MODE REGISTER

The extended mode register controls functions beyond

those controlled by the mode register; these additional

functions are DLL enable/disable, output drive strength,

and QFC. These functions are controlled via the bits shown

in Figure 5. The extended mode register is programmed

via the LOAD MODE REGISTER command to the mode

register (with BA0 = 1 and BA1 = 0) and will retain the

stored information until it is programmed again or the