1

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

1GB- 128Mx72 SDRAM, UNBUFFERED W/PLL

n Burst Mode Operation

n Auto and Self Refresh capability

n LVTTL compatible inputs and outputs

n Serial Presence Detect with EEPROM

n Fully synchronous: All signals are registered on the positive

edge of the system clock

n Programmable Burst Lengths: 1, 2, 4, 8 or Full Page

n 3.3 volt 6 0.3v Power Supply

n 144 Pin SO-DIMM JEDEC

The WED3DG72128V is a 128Mx72 synchronous DRAM module

which consists of nine 128Mx8 stack SDRAM components in

TSOP- 11 package, and one 2K EEPROM in an 8- pin TSSOP

package for Serial Presence Detect which are mounted on a 144

Pin SO-DIMM multilayer FR4 Substrate.

DESCRIPTION

FEATURES

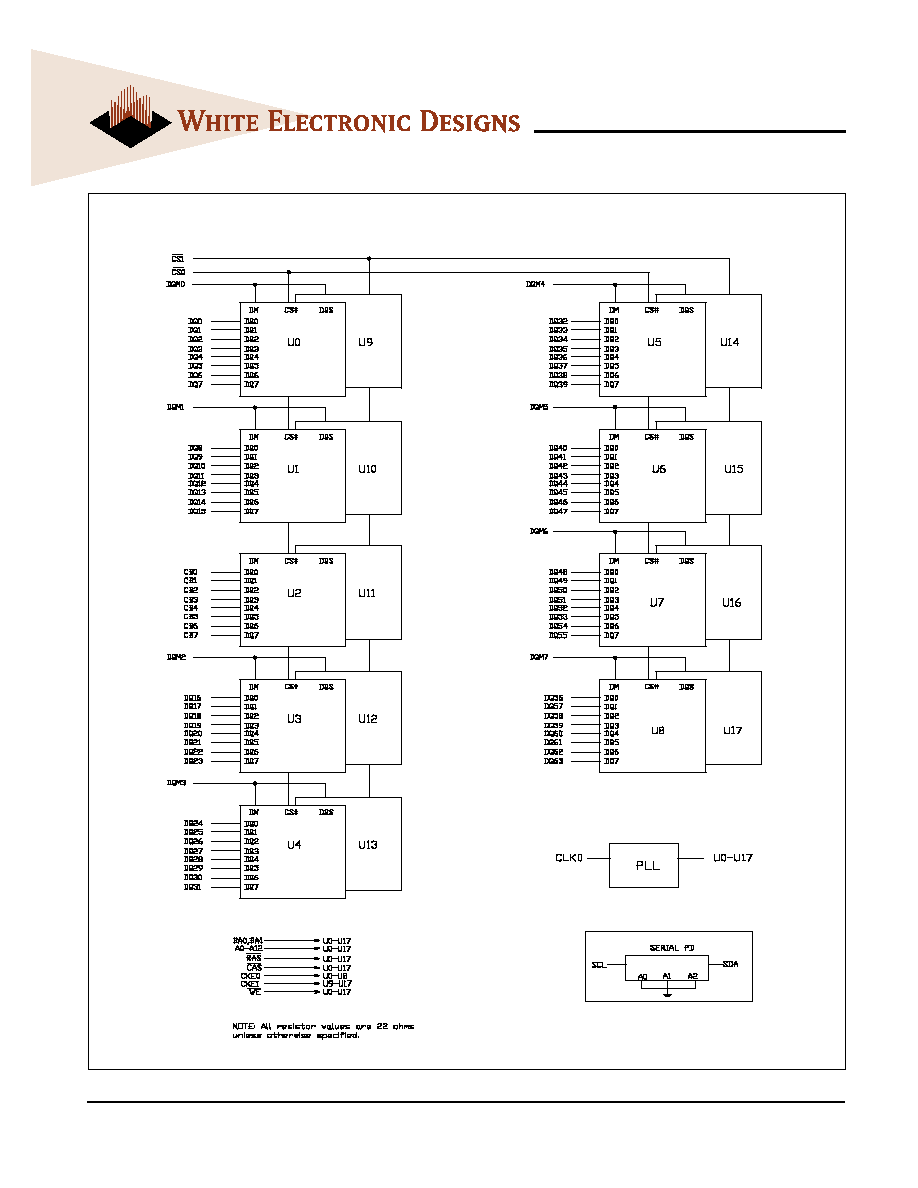

PIN CONFIGURATIONS (FRONT SIDE/BACK SIDE)

PIN NAMES

* These pins are not used in this module.

** These pins should be NC in the system which

does not support SPD.

NC

NC

* This datasheet describes a product that may or may not be under development

and is subject to change or cancellation without notice.

A0 A12Address input (Multiplexed)

BA0-1

Select Bank

DQ0-63

Data Input/Output

CLK0

Clock input

CBO-7

Check bit (Data-In/Data-Out)

CKE0, CKE1

Clock Enable input

CS0, CS1

Chip select Input

RAS

Row Address Strobe

CAS

Column Address Strobe

WE

Write Enable

DQM0-7

DQM

VDD

Power Supply (3.3V)

VSS

Ground

SDA

Serial data I/O

SCL

Serial clock

DNU

Do not use

NC

No Connect

2

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

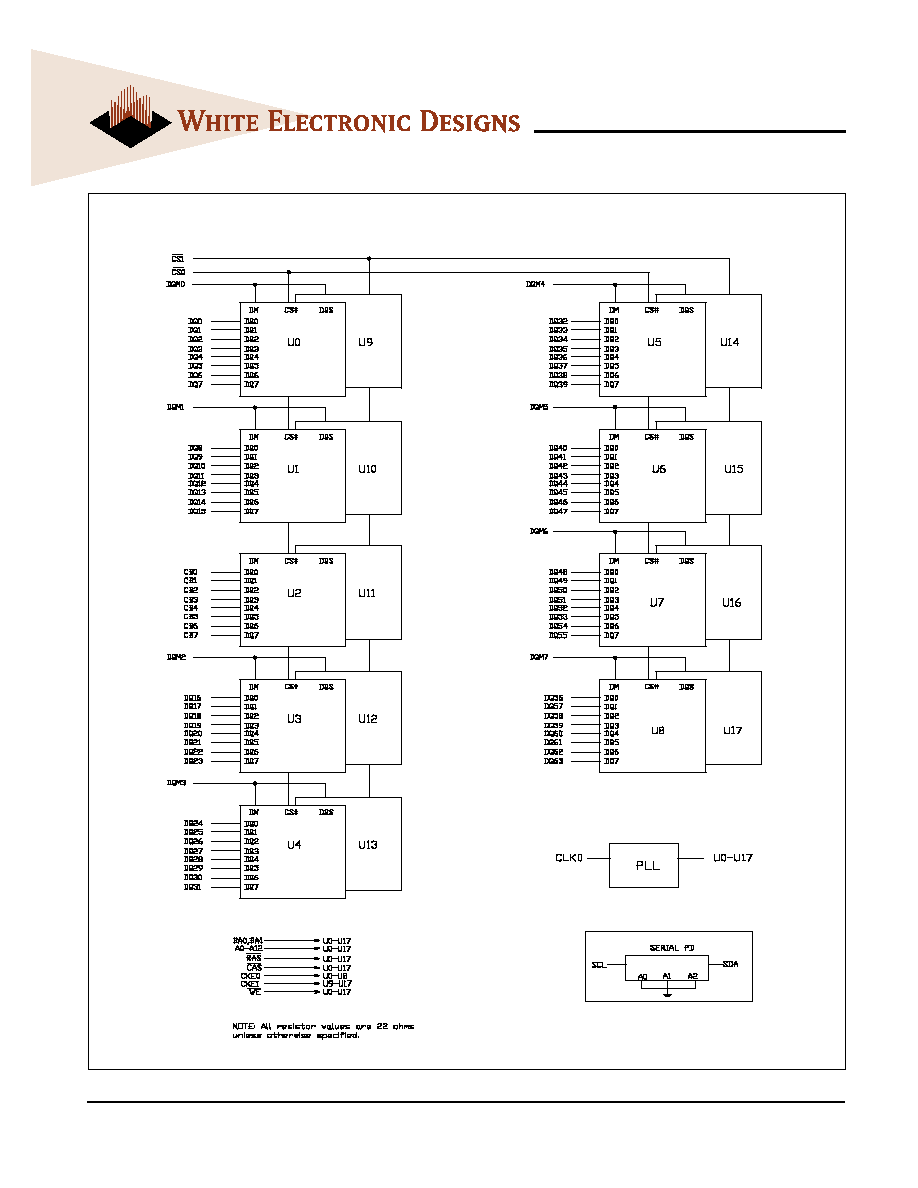

FUNCTIONAL BLOCK DIAGRAM

3

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

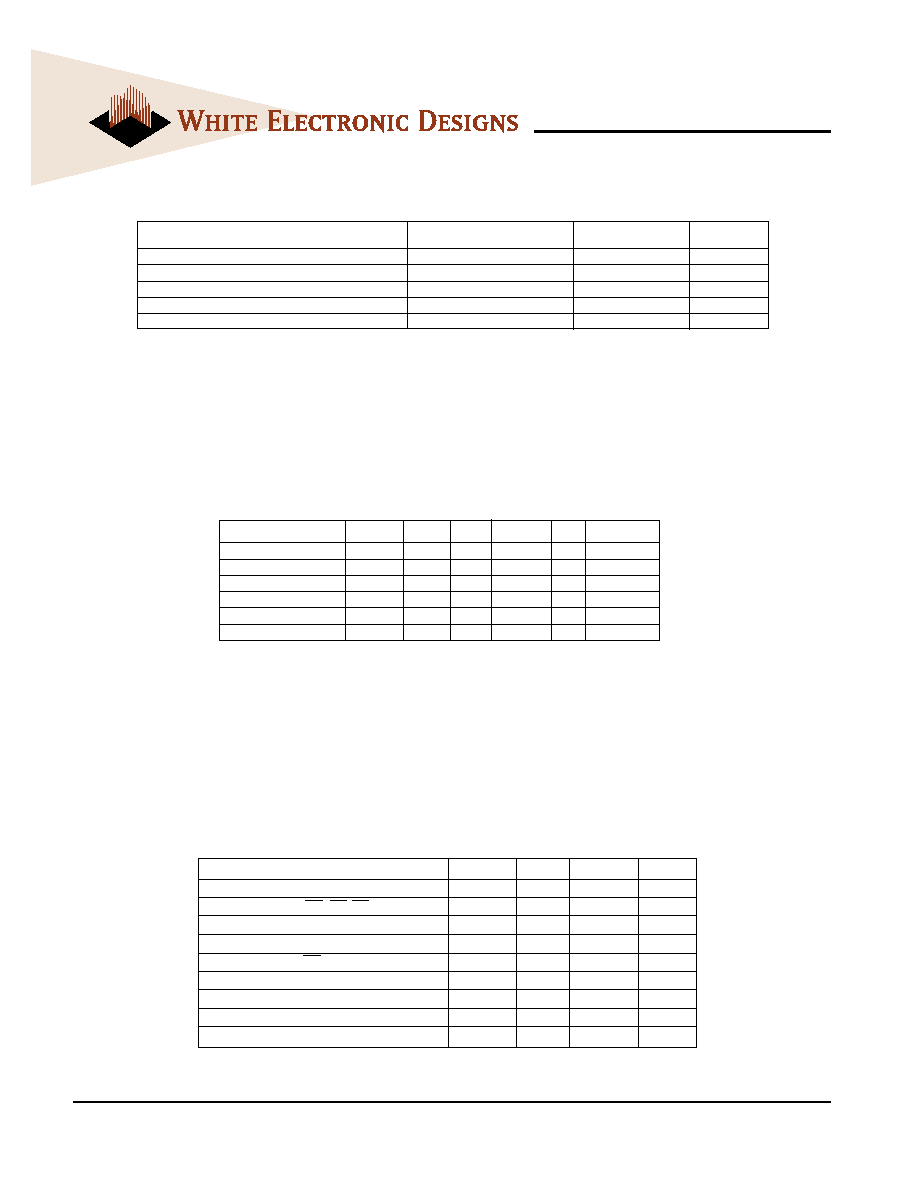

(Voltage Referenced to: V

SS

= 0V, T

A

= 0∞C to +70∞C)

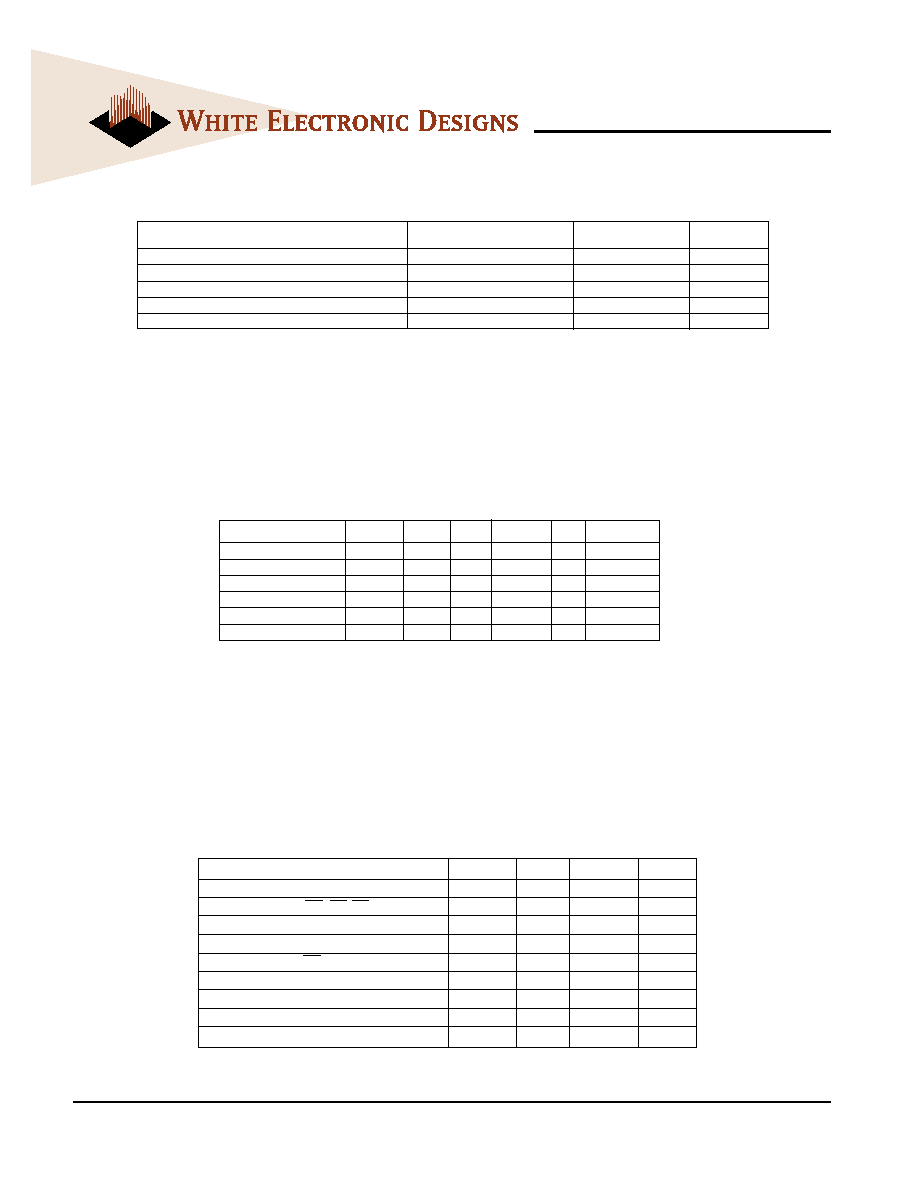

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Value

Units

Voltage on any pin relative to VSS

V

IN

, Vout

-1.0 ~ 4.6

V

Voltage on VDD supply relative to VSS

VDD, VDDQ

-1.0 ~ 4.6

V

Storage Temperature

TSTG

-55 ~ +150 ∞C

Power Dissipation

PD

18

W

Short Circuit Current

IOS

50

mA

Note: Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

RECOMMENDED DC OPERATING CONDITIONS

Parameter

Symbol

Min

Typ

Max

Unit

Note

Supply Voltage

VDD

3.0

3.3

3.6

V

Input High Voltage

VIH

2.0

3.0 VDDQ+0.3 V

1

Input Low Voltage

VIL

-0.3

0.8

V

2

Output High Voltage

VOH

2.4

V

IOH= -2mA

Output Low Voltage

VOL

0.4

V

IOL= -2mA

Input Leakage Current

ILI

-10

10

µA

3

Note: 1. VIH (max)= 5.6V AC. The overshoot voltage duration is £ 3ns.

2. VIL (min)= -2.0V AC. The undershoot voltage duration is £ 3ns.

3. Any input 0V £ VIN £ VDDQ

Input leakage currents include Hi-Z output leakage for all bi-directional buffers with Tri-State

outputs.

CAPACITANCE

(T

A

= 23∞C, f = 1MHz, V

DD

= 3.3V, VREF=1.4V 6200mV)

Parameter

Symbol

Min

Max

Unit

Input Capacitance (A0-A12)

CIN1

-

15

pF

Input Capacitance (RAS,CAS,WE)

CIN2

-

15

pF

Input Capacitance (CKE0)

CIN3

-

15

pF

Input Capacitance (CLK0)

CIN4

-

20

pF

Input Capacitance (CS0)

CIN5

-

15

pF

Input Capacitance (DQM0-DQM7)

CIN6

-

15

pF

Input Capacitance (BA0-BA1)

CIN7

-

15

pF

Data input/output capacitance (DQ0-DQ63)

Cout

-

22

pF

Data input/output capacitance (CB0-7)

Cout 1

-

22

pF

4

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

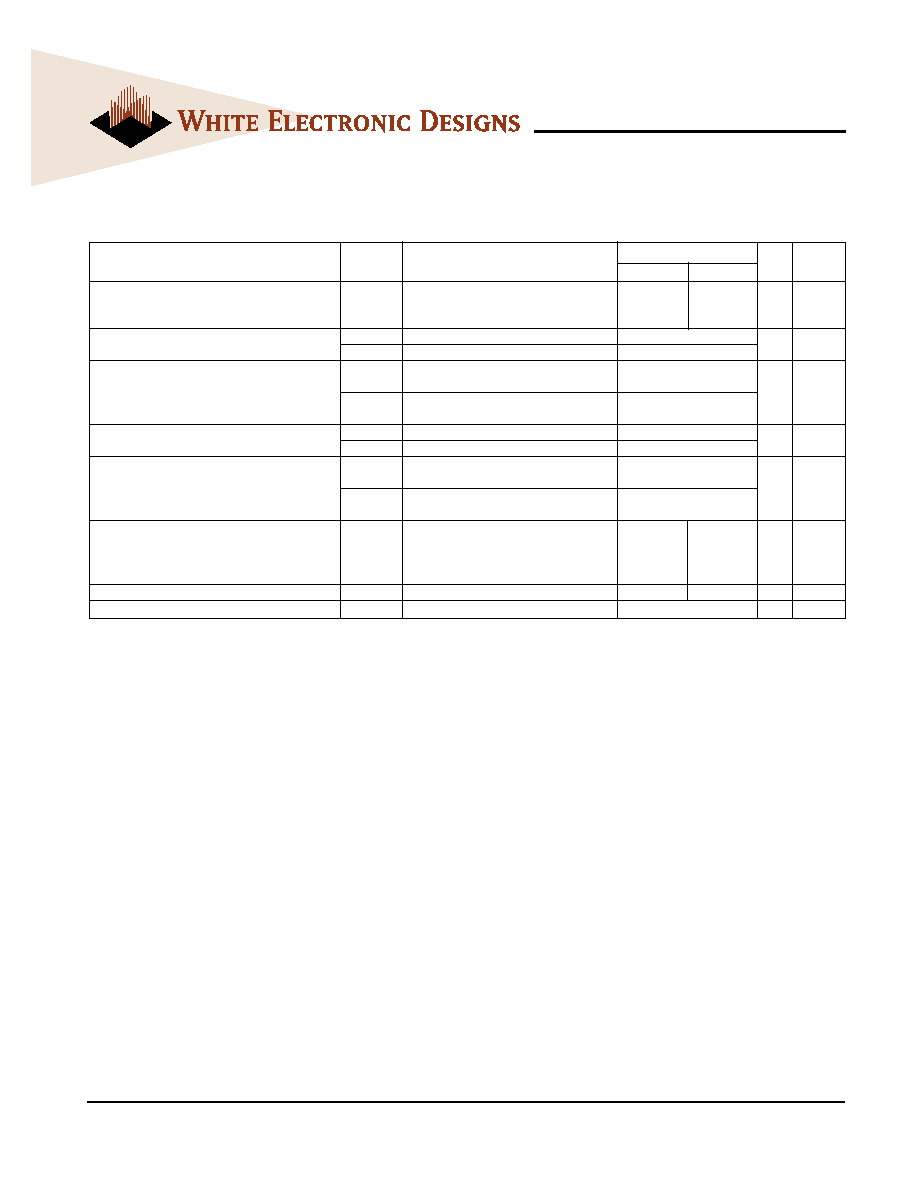

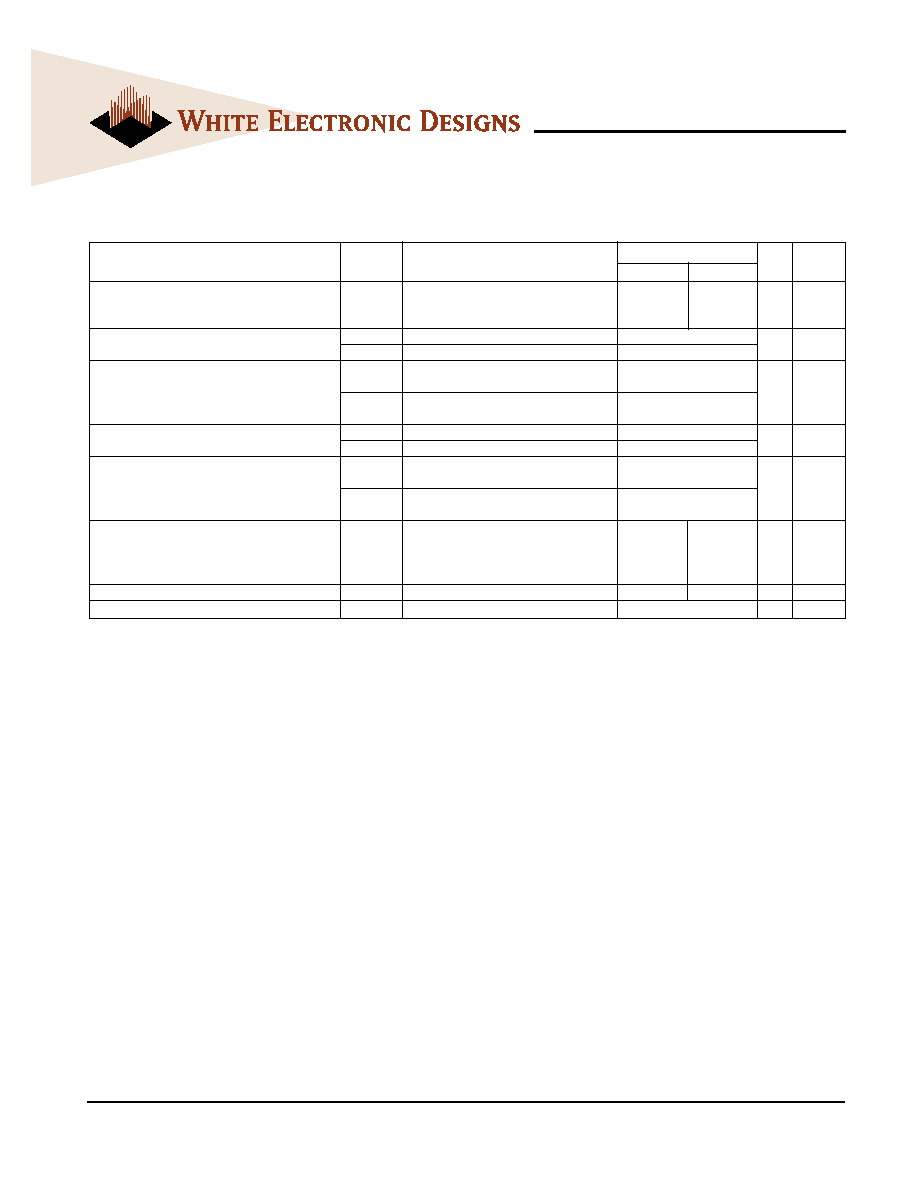

OPERATING CURRENT CHARACTERISTICS

(V

CC

= 3.3V, T

A

= 0∞C to +70∞C)

Notes: 1. Measured with outputs open.

2. Refresh period is 64ms.

3. Unless otherwise noticed, input swing level is CMOS (VIH/VIL = VDDQ/VssQ)

Version

Parameter

Symbol

Conditions

133

100

Units Note

Operating Current

ICC1

Burst Length = 1

1,890

1,710

mA

1

(One bank active)

tRC ≥ tRC(min)

IOL = 0mA

Precharge Standby Current

ICC2P

CKE £ VIL(max), tCC = 10ns

145

mA

in Power Down Mode

ICC2PS

CKE & CLK £ VIL(max), tCC = •

135

Icc2N

CKE ≥ VIH(min), CS ≥ VIH(min), tcc = 10ns

Precharge Standby Current

Input signals are charged one time during 20

360

in Non-Power Down Mode

Icc2NS

CKE ≥ VIH(min), CLK £ VIL(max), tcc = •

mA

Input signals are stable

180

Active standby current in

ICC3P

CKE ≥ VIL(max), tCC = 10ns

180

mA

power-down mode

ICC3PS

CKE & CLK £ VIL(max), tcc = •

130

ICC3N

CKE ≥ VIH(min), CS ≥ VIH(min), tcc = 10ns

Active standby current in

Input signals are changed one time during 20ns 540

mA

non power-down mode

ICC3NS

CKE ≥ VIH(min), CLK £ VIL(max), tcc = •

input signals are stable

405

mA

Io = mA

Operating current (Burst mode)

ICC4

Page burst

1,890

1,620

mA

1

4 Banks activated

tCCD = 2CLK

Refresh current

ICC5

tRC ≥ tRC(min)

3,060

2,880

mA

2

Self refresh current

ICC6

CKE £ 0.2V

130

mA

5

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

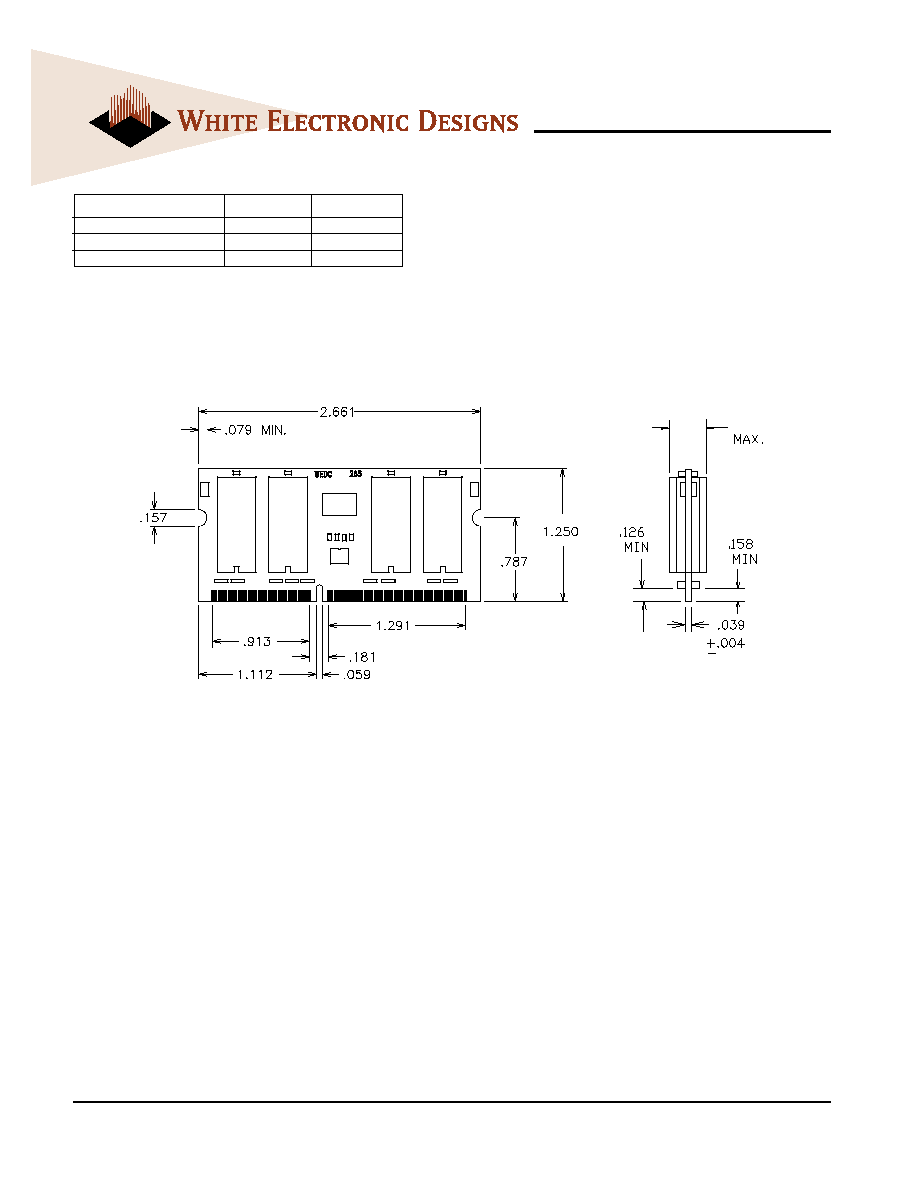

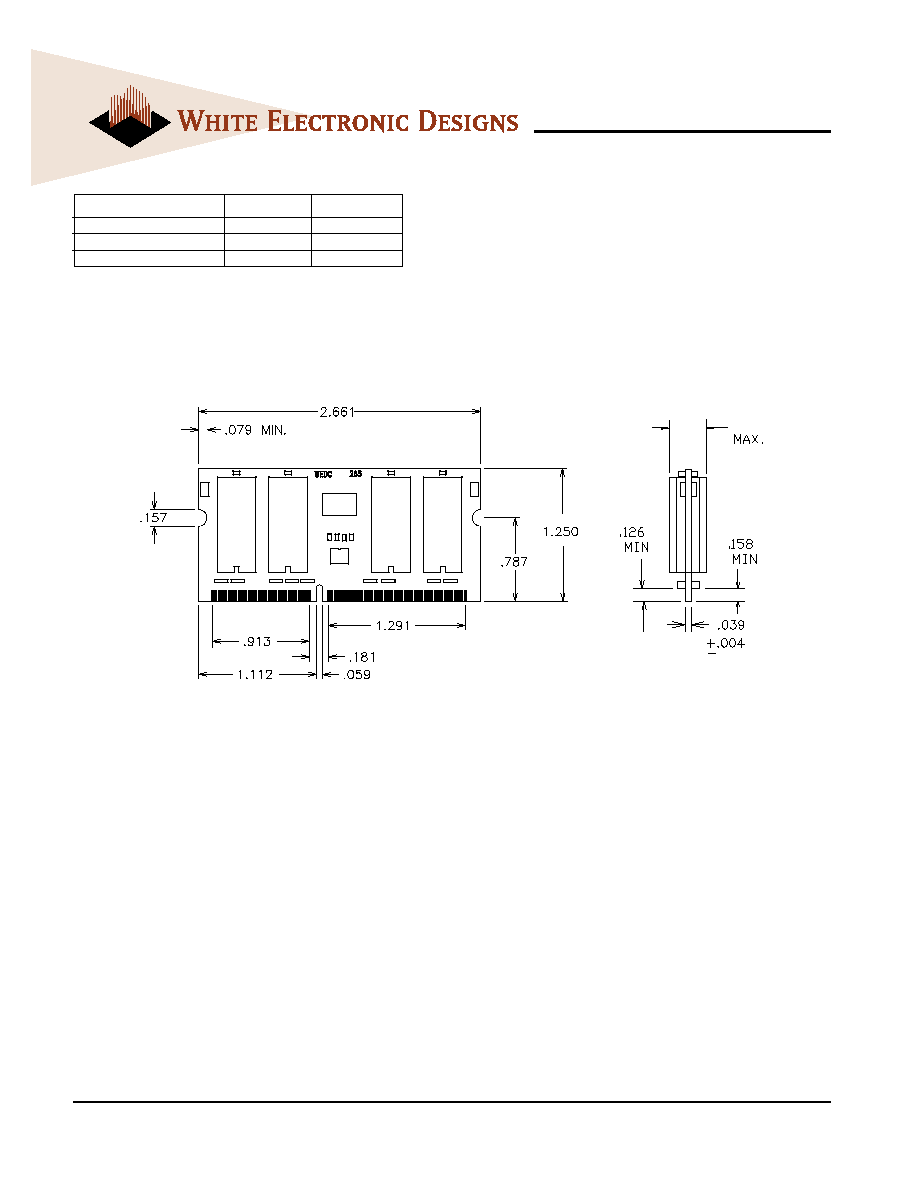

ALL DIMENSIONS ARE IN INCHES

PACKAGE DIMENSIONS

Ordering Information

Speed

Cas Latency

WED3DG72128V10D1

100MHz

CL=2

WED3DG72128V7D1

133MHz

CL=2

WED3DG72128V75D1

133MHz

CL=3

PLL

.250

6

White Electronic Designs Corporation (508) 366-5151 www.whiteedc.com

Oct. 2002 Rev. 0

ECO #15738

WED3DG72128V-D1

REV.

DATE

REQUESTED BY

DETAILS

A

10-18-02

PAUL MARIEN

CREATED

0

11-6-02

PAUL MARIEN

-CHANGE FROM ADVANCED

TO FINAL

DATASHEET APPROVALS

ECO#

EDI PART NO.

NEW REV

DATE

APPROVAL:

INITIAL

DATE

CORRECTION ON PAGES

JUAN GUZMAN

MUKESH TRIVEDI

PAUL MARIEN

LARRY WINROTH

DAVE KELLY

MARK DOWNEY

DAVE HARRISON

TONY LEE

BOB KHEDERIAN

LUIS ESTELLA

YES

NO

LINE

:________

WILL THIS DATASHEET GO ON THE WEB?

FAMILY:

____________

PROD.TYPE:

________

ORG:___________

IS THIS A NEW DATASHEET?

DENSITY:________

SPEED:__________

WILL THIS DATASHEET REPLACE AN EXISTING

PKG:____________

DATASHEET THAT'S ALREADY ON THE WEB?

VOLTAGE:________

IF YES, WHAT DATASHEET IS IT REPLACING?

WHAT SECTION SHOULD THIS DATASHEET BE

PLACED IN ON THE WEB?

AFTER REVIEWING OR MAKING CORRECTIONS ON THE DATASHEET (S)

PLEASE SIGN-OFF ON THIS SHEET AND ,MAKE YOUR CORRECTIONS ≠ON

THE ORIGINAL COPY(S).

AFTER REVIEWING THE DATA SHEET, TEST ENGINEERING WILL COMPLETE THE SECTION BELOW.

TEST PROGRAM CHANGE REQUIRED:

YES:_________NO____________DATE:___________

TEST ENGINEER SIGNATURE___________________

IF YES, DO NOT RELEASE DATA SHEET UNTIL TEST PROGRAM CHANGE IS COMPLETED.

TEST PROGRAM CHANGE COMPLETION DATE:__________

TEST PROGRAM NAME AND REVISION_________________

TEST ENGINEER SIGNATURE__________________________

FO-00342R1.DOC

ECO# 14942

SHEET 1 OF

1

s

s

11/6/02

11/6/02

11/6/02

11/26/02

Memories - Modules - SDRAM

11/26/02

s

WED3DG72128V-D1

15738

0

11/6/02