1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

FEATURES

ATA

compatibility

Supports 3 variations of mode access

∑ I/O Card Mode

∑ Memory Card Mode

∑ True- IDE Mode

+5.5V / +3.0V single power supply.

Internal Error Correction Logic

∑ Data Interleave to 2 for each 256 Bytes.

∑ Error Correction of 1 Byte random error per 128

Bytes of data.

∑ Automatic on-the-fl y, in-buffer error correction.

Compatible with all PC Card Service and Socket

Service.

Integrated PC Card attribute memory of 256

Bytes(CIS).

4 PC Card function register support.

Supports Host-side Write Protect.

Automatic wake up from power-down on host reset

or command write.

Sector data transfers without microprocessor

intervention.

Operation

Environment

∑ Temperature -- 0∞C ~ 65∞C

∑ Humidity -- 8% ~ 95%

32MB to 4GB Flash Card

DESCRIPTION

The WED7PxxxATA80xxC25 series ATA card is an ATA

interface fl ash memory card based on fl ash technology.

The ATA card is constructed with a fl ash disk controller

chip and NAND-type fl ash memory device. Operates

from a single 5-Volt or 3.3-Volt power source. The card

is available in ATA type-2 form factor from 32MB to 4GB

unformatted capacity. Being able to emulate IDE hard disk

drives, WEDC's ATA card is a perfect choice for solid-state

mass-storage in industrial applications.

* This product is subject to change without notice.

PRODUCT TYPES

Card Density

Model No.

32MB

7P032ATA80xxC25

64MB

7P064ATA80xxC25

128MB

7P128ATA80xxC25

256MB

7P256ATA80xxC25

512MB

7P512ATA80xxC25

1024MB

7P1G0ATA80xxC25

2048MB

7P2G0ATA80xxC25

4096MB

7P4G0ATA80xxC25

xx = Housing

03 = WEDC logo

04 = No logo

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

BLOCK DIAGRAM

D0 to D15

HOST

INTERF

ACE

BVD2/1SPKR/DASP#

A0 to A10

CE1#, CE2#

OE#, ATASEL#

WE#

IORD#

Controller

Control Signal

FCE/7..01

Flash

Memory

Data Bus

FAD [7:0]/FBD[7:0]

IOWR#

REG#

RESET/RESET#

CSEL#

RDY/BSY#/IREQ#/INTRQ

WP/IOIS16#

INPACK#

BVD1/STSCHG#/PDIAG#

WAIT#/IORDY

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

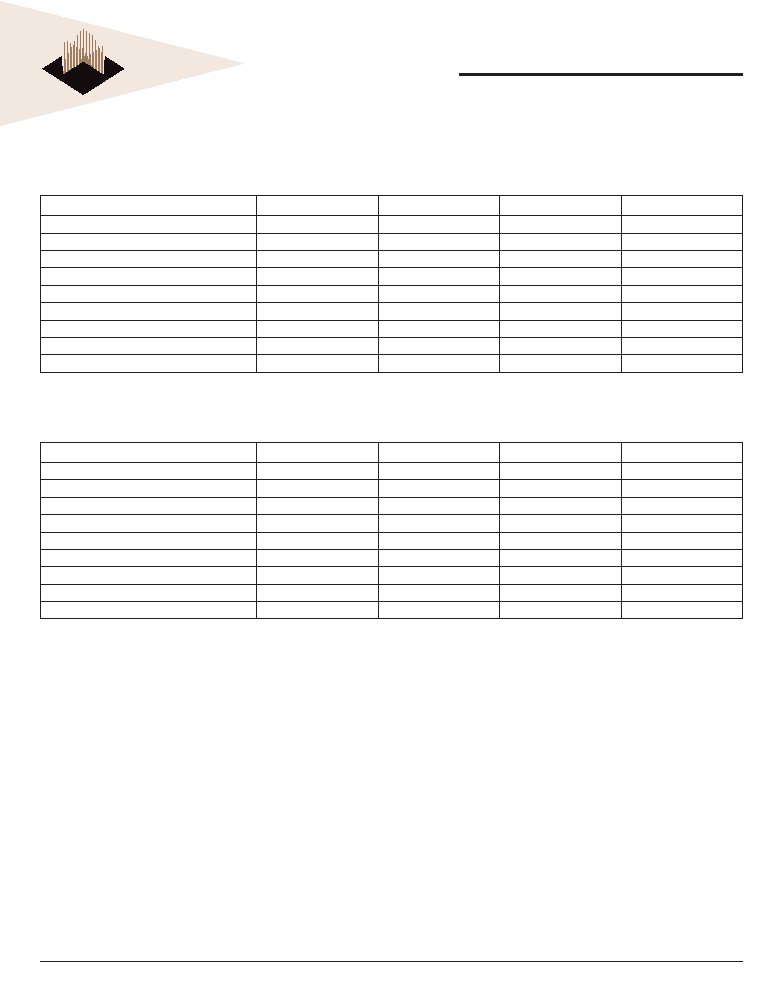

PIN ASSIGNMENTS AND PIN TYPE

Pin #

Memory card mode

I/O Card Mode

True IDE Mode

Signal Name

I/O

Signal Name

I/O

Signal Name

I/O

1

GND

GND

GND

2

D3

I/O

D3

I/O

D3

I/O

3

D4

I/O

D4

I/O

D4

I/O

4

D5

I/O

D5

I/O

D5

I/O

5

D6

I/O

D6

I/O

D6

I/O

6

D7

I/O

D7

I/O

D7

I/O

7

CE1#

I

CE1#

I

CE1#

I

8

A10

I

A10

I

A10

I

9

OE#

I

OE#

I

ATASEL#

I

10

N.C.

≠

N.C.

≠

N.C.

≠

11

A9

I

A9

I

A9

I

12

A8

I

A8

I

A8

I

13

N.C.

≠

N.C.

≠

N.C.

≠

14

N.C.

≠

N.C.

≠

N.C.

≠

15

WE#

I

WE#

I

WE#

I

16

RDY/BSY

O

IREQ#

O

INTRQ

O

17

Vcc

Vcc

Vcc

18

N.C.

≠

N.C.

≠

N.C.

≠

19

N.C.

≠

N.C.

≠

N.C.

≠

20

N.C.

≠

N.C.

≠

N.C.

≠

21

N.C.

≠

N.C.

≠

N.C.

≠

22

A7

I

A7

I

A7

I

23

A6

I

A6

I

A6

I

24

A5

I

A5

I

A5

I

25

A4

I

A4

I

A4

I

26

A3

I

A3

I

A3

I

27

A2

I

A2

I

A2

I

28

A1

I

A1

I

A1

I

29

A0

I

A0

I

A0

I

30

D0

I/O

D0

I/O

D0

I/O

31

D1

I/O

D1

I/O

D1

I/O

32

D2

I/O

D2

I/O

D2

I/O

33

WP

O

IOIS16#

O

IOIS16#

O

34

GND

≠

GND

≠

GND

≠

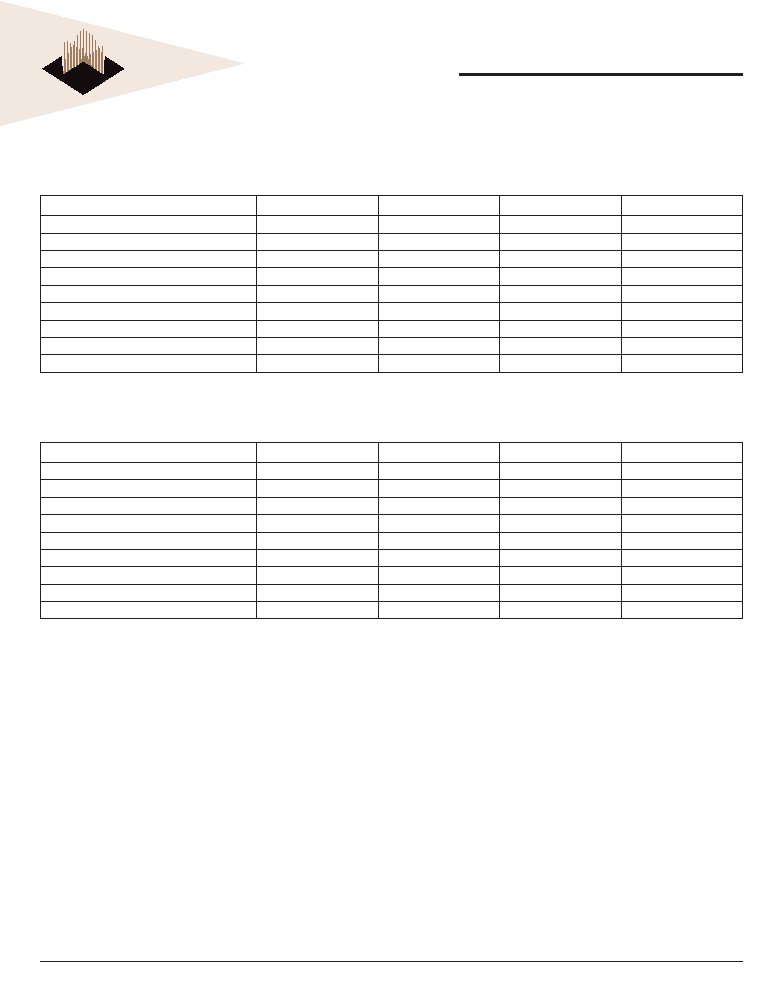

Pin #

Memory card mode

I/O Card Mode

True IDE Mode

Signal Name

I/O

Signal Name

I/O

Signal Name

I/O

35

GND

≠

GND

≠

GND

≠

36

CD1#

O

CD1#

O

CD1#

O

37

D11

I/O

D11

I/O

D11

I/O

38

D12

I/O

D12

I/O

D12

I/O

39

D13

I/O

D13

I/O

D13

I/O

40

D14

I/O

D14

I/O

D14

I/O

41

D15

I

D15

I

D15

I

42

CE2#

I

CE2#

I

CE2#

I

43

VS1

O

VS1

O

VS1

O

44

IORD#

I

IORD#

I

IORD#

I

45

IOWR#

I

IOWR#

I

IOWR#

I

46

NC

≠

NC

≠

NC

≠

47

NC

≠

NC

≠

NC

≠

48

NC

≠

NC

≠

NC

≠

49

NC

≠

NC

≠

NC

≠

50

NC

≠

NC

≠

NC

≠

51

Vcc

≠

Vcc

≠

Vcc

≠

52

NC

≠

NC

≠

NC

≠

53

NC

≠

NC

≠

NC

≠

54

NC

≠

NC

≠

NC

≠

55

NC

≠

NC

≠

NC

≠

56

CSEL#

I

CSEL#

I

CSEL#

I

57

VS2

O

VS2

O

VS2

O

58

RESET

I

RESET

I

RESET#

I

59

Wait#

O

Wait#

O

IORDY

O

60

INPACK#

O

INPACK#

O

INPACK#

O

61

REG#

I

REG#

I

REG#

I

62

BVD2

I/O

SPKR#

I/O

DASP

I/O

63

BVD1

I/O

STSCHG#

I/O

PDIAG#

I/O

64

D8

I/O

D8

I/O

D8

I/O

65

D9

I/O

D9

I/O

D9

I/O

66

D10

O

D10

O

D10

O

67

CD2#

O

CD2#

O

CD2#

O

68

GND

≠

GND

≠

GND

≠

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

ELECTRICAL SPECIFICATIONS

ABSOLUTE MAXIMUM RATING

Symbol

Parameter

Rating

Units

V

CC

Power supply

-0.3 to 6.0

V

V

IN

Input voltage

-0.3 to V

CC

+0.3

V

V

OUT

Output voltage

-0.3 to V

CC

+0.3

V

T

STG

Storage temperature

-40 to 125

∞C

DC CHARACTERISTICS:

I) Recommended Operating Conditions:

Symbol

Parameter

Min.

Max.

Units

V

CC

Power supply

3.0

5.5

V

V

IN

Input voltage

0

V

CC

V

T

OPR

Operating temperature

-20

65

∞C

II) General DC Characteristics:

Symbol

Parameter

Conditions

Min

Typ

Max

Units

I

IL

Input low current

no pull up/down

-1

1

µA

I

IH

Input high current

no pull up/down

-1

1

µA

I

OZ

Tri-state leakage current

-10

10

µA

C

IN

Input capacitance

4

pF

C

OUT

Output capacitance

4

pF

C

BID

Bi-direction capacitance

4

pF

III) DC Electrical Characteristics:

Symbol

Parameter

Min

Typ

Max

Units

V

IL

Input low voltage

0.3V

CC

V

V

IH

Input high voltage

0.7V

CC

V

V

IL

Schmitt input low voltage

1.22

V

V

IH

Schmitt input high voltage

2.08

V

V

OL

Output low voltage

0.4

V

V

OH

Output high voltage

2.3

1

V

R

I

Input pull up/down resistance

75

k

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

AC CHARACTERISTICS:

Attribute Memory Read Timing Specifi cation

Attribute Memory access time is defi ned as 300ns. Detailed timing specs are shown in Table below.

Speed Version

300 ns

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Read Cycle Time

tc(R)

t

AVAV

300

Address Access Time

ta(A)

t

AVQV

300

Card Enable Access Time

ta(CE)

t

ELQV

300

Output Enable Access Time

ta(OE)

t

GLQV

150

Output Disable Time from CE

tdis(CE)

t

EHQZ

100

Output Disable Time from OE

tdis(OE)

t

GHQZ

100

Address Setup Time

tsu(A)

t

AVGL

30

Output Enable Time from CE

ten(CE)

t

ELQNZ

5

Output Enable Time from OE

ten(OE)

t

GLQNZ

5

Data Valid from Address Change

tv(A)

t

AXQX

0

Note: All times are in nanoseconds. The CE# signal or both the OE# signal and the WE# signal must be de-asserted between consecutive cycle operations.

Confi guration Register (Attribute Memory) Write Timing Specifi cation

The Card Confi guration write access time is defi ned as 250ns. Detailed timing specifi cations are shown in Table below.

Speed Version

250 ns

Item

Symbol

IEEE Symbol

Min ns

Max ns

Write Cycle Time

tc(W)

t

AVAV

250

Write Pulse Width

tw(WE)

t

WLWH

150

Address Setup Time

tsu(A)

t

AVWL

30

Write Recovery Time

trec(WE)

t

WMAX

30

Data Setup Time for WE

tsu(D-WEH)

t

DVWH

80

Data Hold Time

th(D)

t

WMDX

30

Note: All times are in nanoseconds.

Common Memory Read Timing Specifi cation

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Output Enable Access Time

ta(OE)

t

GLQV

125

Output Disable Time from OE

tdis(OE)

t

GHQZ

100

Address Setup Time

tsu(A)

t

AVGL

30

Address Hold Time

th(A)

t

GHAX

20

CE Setup before OE

tsu(CE)

t

ELGL

0

CE Hold following OE

th(CE)

t

GHEH

20

Wait Delay Falling from OE

tv(WT-OE)

t

GLWTV

35

Data Setup for Wait Release

tv(WT)

t

QVWTH

0

Wait Width Time

tw(WT)

t

WTLWTH

350 (3000 for CF+)

Note: The maximum load on -WAIT# is 1 LSTTL with 50pF total load. All times are in nanoseconds. The WAIT# signal may be ignored if the OE# cycle to cycle time is greater than

the Wait Width time. The Max Wait Width time can be determined from the Card Information Structure. The Wait Width time meets the PCMCIA specifi cation of 12ps but is

intentionally less in this specifi cation.

6

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

AC CHARACTERISTICS (cont'd):

I/O Input (Read) Timing Specifi cation

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Data Delay after IORD

td(IORD)

t

IGLQV

100

Data Hold following IORD

th(IORD)

t

IGHQX

0

IORD Width Time

tw(IORD)

t

IGLIGH

165

Address Setup before IORD

tsuA(IORD)

t

AVIGL

70

Address Hold following IORD

thA(IORD)

t

IGHAX

20

CE Setup before IORD

tsuCE(IORD)

t

ELIGL

5

CE Hold following IORD

thCE(IORD)

t

IGHEH

20

REG Setup before IORD

tsuREG(IORD)

t

RGLIGL

5

REG Hold following IORD

thREG(IORD)

t

IGHRGH

0

INPACK Delay Falling from IORD

tdfINPACK(IORD)

t

IGLIAL

0

45

INPACK Delay Rising from IORD

tdrINPACK(IORD)

t

IGHIAH

45

IOIS16 Delay Falling from Address

tdfIOIS16(ADR)

t

AVISL

35

IOIS16 Delay Rising from Address

tdrIOIS16(ADR)

t

AVISH

35

Wait Delay Falling from IORD

tdWT(IORD)

t

IGLWTL

35

Data Delay from Wait Rising

td(WT)

t

WTHQV

0

Wait Width Time

tw(WT)

t

WTLWTH

350 (3000 for CF+)

Note: Maximum load on WAIT#, INPACK# and I0IS16# is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from WAIT# high to IORD# high is Onsec, but

minimum IORD# width must still be met. Wait Width time meets PCMCIA specifi cation of 12ps but is intentionally less in this spec.

I/O Output (Write) Timing Specifi cation

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Data Setup before IOWR

tsu(IOWR)

t

DVIWH

60

Data Hold following IOWR

th(IOWR)

t

IWHDX

30

IOWR Width Time

tw(IOWR)

t

IWLIWH

165

Address Setup before IOWR

tsuA(IOWR)

t

AVIWL

70

Address Hold following IOWR

thA(IOWR)

t

IWHAX

20

CE Setup before IOWR

tsuCE(IOWR)

t

ELIWL

5

CE Hold following IOWR

thCE(IOWR)

t

IWHEH

20

REG Setup before IOWR

tsuREG(IOWR)

t

RGLIWL

5

REG Hold following IOWR

thREG(IOWR)

t

IWHRGH

0

IOIS16 Delay Falling from Address

tdfIOIS16(ADR)

t

AVISL

35

IOIS16 Delay Rising from Address

tdrIOIS16(ADR)

t

AVISH

35

Wait Delay Falling from IOWR

tdWT(IOWR)

t

IWLWTL

35

IOWR high from Wait high

tdrIOWR(WT)

t

WTJIWH

0

Wait Width Time

tw(WT)

t

WTLWTH

350 (3000for CF+)

Note: The maximum load on WAIT#, INPACK#, and I0IS16# is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from WAIT# high to IOWR# high is Onsec,

but minimum IOWR# width must still be met. The Wait Width time meets the PCMCIA specifi cation of 12ps but is intentionally less in this specifi cation.

7

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

AC CHARACTERISTICS (cont'd):

True IDE Mode I/O Input (Read) Timing Specifi cation

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Data Delay after IORD

td(IORD)

t

IGLQV

100

Data Hold following IORD

th(IORD)

t

IGHQX

0

IORD Width Time

tw(IORD)

t

IGLIGH

165

Address Setup before IORD

tsuA(IORD)

t

AVIGL

70

Address Hold following IORD

thA(IORD)

t

IGHAX

20

CE Setup before IORD

tsuCE(IORD)

t

ELIGL

5

CE Hold following IORD

thCE(IORD)

t

IGHEH

20

I0IS16 Delay Falling from Address

tdfIOIS16(ADR)

t

AVISL

35

I0IS16 Delay Rising from Address

tdrIOIS16(ADR)

t

AVISH

35

Note: The maximum load on I0IS16# is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from WAIT# high to IORD# high is 0 nsec, but minimum IORD# width

must still be met.

True IDE Mode I/O Output (Write) Timing Specifi cation

Item

Symbol

IEEE Symbol

Min ns.

Max ns.

Data Setup before IOWR

tsu(IOWR)

t

DVIWH

60

Data Hold following IOWR

th(IOWR)

t

IWHDX

30

IOWR Width Time

tw(IOWR)

t

IWLIWH

165

Address Setup before IOWR

tsuA(IOWR)

t

AVIWL

70

Address Hold following IOWR

thA(IOWR)

t

IWHAX

20

CE Setup before IOWR

tsuCE(IOWR)

t

ELIWL

5

CE Hold following IOWR

thCE(IOWR)

t

IWHEH

20

I0IS16 Delay Falling from Address

tdfIOIS16(ADR)

t

AVISL

35

I0IS16 Delay Rising from Address

tdrIOIS16(ADR)

t

AVISH

35

Note: The maximum load on I0IS16# is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from WAIT# high to IOWR# high is 0 nsec, but minimum IOWR#

width must still be met.

8

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

PACKAGE DIMENSIONS

Interconnect area

Substrate area

1.6mm ± 0.05

(0.063")

1.0mm ± 0.05

(0.039")

1.0mm ± 0.05

(0.039")

3.3mm ± 0.10

(0.129")

85.6mm ± 0.20

(3.370")

54.0mm ± 0.10

(2.126")

3.0mm MIN

(0.118")

5.0mm ± T1

(0.197")

10.0mm MIN

(0.400")

Type II

9

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

PART NUMBERING GUIDE

WED 7P xxx ATA 80 xx C 25

WEDC

Flash

Memory Size

ATA Flash

Commercial Flash

Housing:

03 = WEDC Logo

04 = Blank Housing

Commercial Temp

Speed

10

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WED7PxxxATA80xxC25

July 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

Document Title

32MB to 4GB Flash Card

Revision History

Rev #

History

Release Date

Status

Rev 0

Initial Release

March 2005

Final

Rev 1

1.1 Added "ED" to part marking

July 2005

Final