| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: WF2M16-90 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

HI-RELIABILITY PRODUCT

WF2M16-XXX5

August 2001 Rev. 4

2Mx16 FLASH MODULE, SMD 5962-97610

PRELIMINARY*

FEATURES

s Access Times of 90, 120, 150ns

s Packaging:

∑ 56 lead, Hermetic Ceramic, 0.520" CSOP (Package 207).

Fits standard 56 SSOP footprint.

∑ 44 pin Ceramic SOJ (Package 102)**

∑ 44 lead Ceramic Flatpack (Package 208)**

s Sector Architecture

∑ 32 equal size sectors of 64KBytes each

∑ Any combination of sectors can be erased. Also supports

full chip erase.

s Minimum 100,000 Write/Erase Cycles Minimum

s Organized as 2Mx16; User Configurable as 2 x 2Mx8

s Commercial, Industrial, and Military Temperature Ranges

s 5 Volt Read and Write. 5V

±

10% Supply.

s Low Power CMOS

s Data Polling and Toggle Bit feature for detection of program

or erase cycle completion.

s Supports reading or programming data to a sector not being

erased.

s Built-in Decoupling Caps and Multiple Ground Pins for Low

Noise Operation.

s RESET pin resets internal state machine to the read mode.

s Ready/Busy (RY/BY) output for detection of program or

erase cycle completion.

s Multiple Ground Pins for Low Noise Operation

* This data sheet describes a product under development, not fully

characterized, and is subject to change without notice.

* * Package to be developed.

Note: For programming information refer to Flash Programming 16M5

Application Notes.

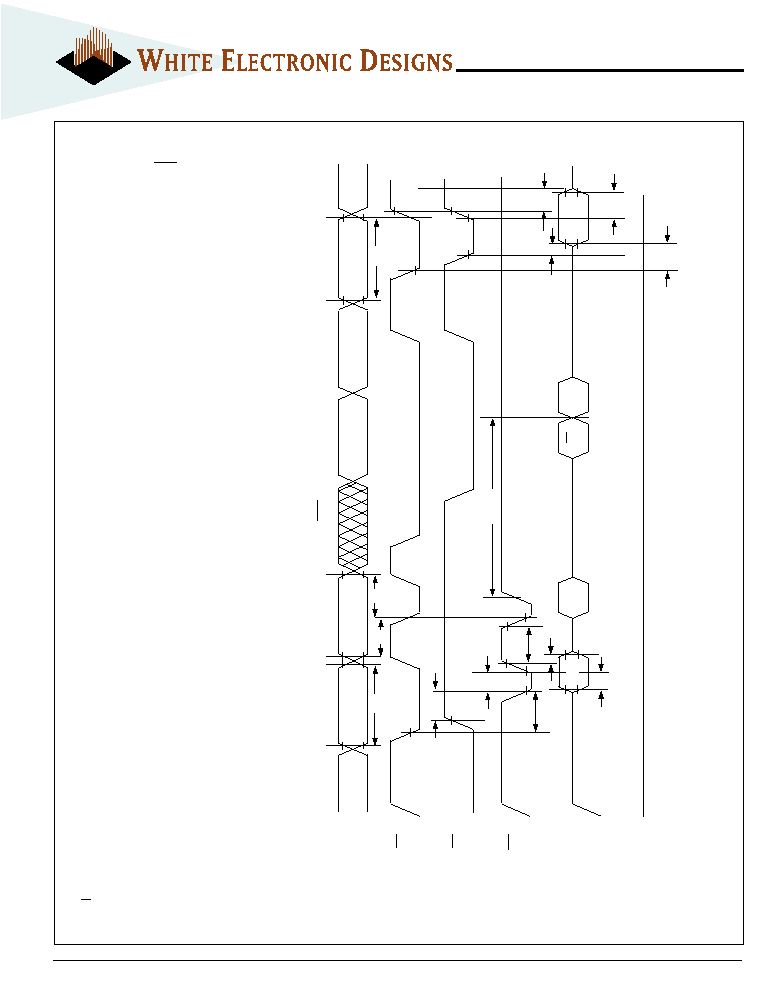

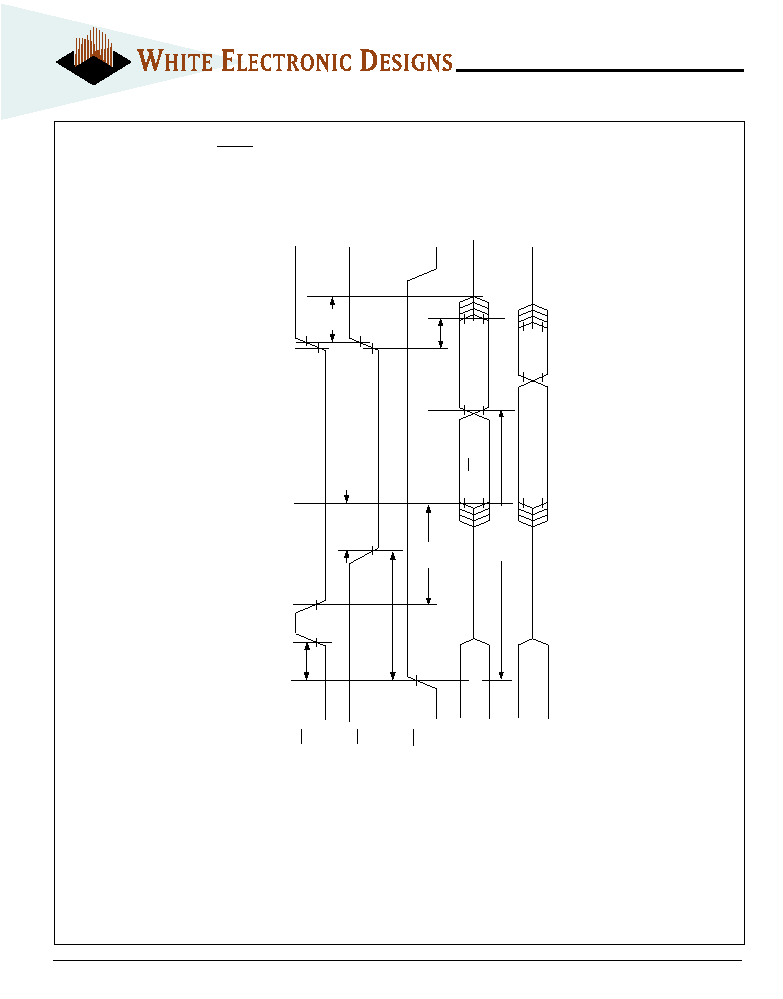

FIG. 1

PIN CONFIGURATIONS

PIN DESCRIPTION

I/O

0-15

Data Inputs/Outputs

A

0-20

Address Inputs

WE

Write Enable

CS

1-2

Chip Select

OE

Output Enable

V

CC

Power Supply

V

SS

Ground

RY/BY

Ready/Busy

RESET

Reset

BLOCK DIAGRAM

NOTE:

1. RY/BY is an open drain output and should be pulled up to Vcc

with an external resistor.

2. Address compatible with Intel 2M8 56 SSOP.

TOP VIEW

WF2M16-XDAX5

56 CSOP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

CS1

A12

A13

A14

A15

NC

CS2

NC

A20

A19

A18

A17

A16

V

CC

GND

I/O6

I/O14

I/O7

I/O15

RY/BY

OE

WE

NC

I/O13

I/O5

I/O12

I/O4

V

CC

NC

RESET

A11

A10

A9

A1

A2

A3

A4

A5

A6

A7

GND

A8

V

CC

I/O9

I/O1

I/O8

I/O0

A0

NC

NC

NC

I/O2

I/O10

I/O3

I/O11

GND

2M x 8

2M x 8

A

0 - 2 0

O E

W E

C S

1

C S

2

I / O

0 - 7

I / O

8 - 1 5

R E S E T

R Y / B Y

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

A15

A14

A13

A12

A11

A10

A9

A8

RESET

CS1

V

CC

V

SS

CS2

RY/BY

A7

A6

A5

A4

A3

A2

A1

A0

A16

A17

A18

A19

A20

OE

I/O7

I/O6

I/O5

I/O4

V

SS

V

CC

I/O3

I/O2

I/O1

I/O0

WE

NC

NC

NC

NC

NC

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

WF2M16-XXX5

44 CSOJ (DL)**

44 FLATPACK (FL)**

** Package to be developed.

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Ratings

Unit

Voltage on Any Pin Relative to V

SS

V

T

-2.0 to +7.0

V

Power Dissipation

P

T

8

W

Storage Temperature

Tstg

-65 to +125

∞

C

Short Circuit Output Current

I

OS

100

mA

Data Retention (Mil Temp)

20

years

Endurance - write/erase cycles

100,000 min.

cycles

(Mil Temp)

RECOMMENDED DC OPERATING CONDITIONS

Parameter

Symbol

Min

Typ

Max

Unit

Supply Voltage

V

CC

4.5

5.0

5.5

V

Ground

V

SS

0

0

0

V

Input High Voltage

V

IH

2.0

-

V

CC

+ 0.5

V

Input Low Voltage

V

IL

-0.5

-

+0.8

V

Operating Temperature (Mil.)

T

A

-55

-

+125

∞

C

Operating Temperature (Ind.)

T

A

-40

-

+85

∞

C

DC CHARACTERISTICS - CMOS COMPATIBLE

(V

CC

= 5.0V, V

SS

= 0V, T

A

= -55

∞

C to +125

∞

C)

NOTES:

1. The Icc current listed includes both the DC operating current and the frequency dependent component (@ 5MHz). The frequency component typically is less than

2mA/MHz, with OE at V

IH

.

2. Icc active while Embedded Algorithm (program or erase) is in progress.

3. DC test conditions V

IL

= 0.3V, V

IH

= V

CC

- 0.3V

Parameter

Symbol

Conditions

Min

Max

Unit

Input Leakage Current

I

LI

V

CC

= 5.5, V

IN

= GND to V

CC

10

µ

A

Output Leakage Current

I

LO

V

CC

= 5.5, V

IN

= GND to V

CC

10

µ

A

V

CC

Active Current for Read (1)

I

CC1

CS = V

IL

, OE = V

IH

, f = 5MHz

80

mA

V

CC

Active Current for Program or Erase (2)

I

CC2

CS = V

IL

, OE = V

IH

120

mA

V

CC

Standby Current

I

CC3

V

CC

= 5.5, CS = V

IH

, f = 5MHz, RESET = Vcc

±

0.3V

4.0

mA

Output Low Voltage

V

OL

I

OL

= 12.0 mA, V

CC

= 4.5

0.45

V

Output High Voltage

V

OH

I

OH

= -2.5 mA, V

CC

= 4.5

0.85xV

cc

V

Low V

CC

Lock-Out Voltage

V

LKO

3.2

4.2

V

CAPACITANCE

(T

A

= +25

∞

C)

Parameter

Symbol

Conditions

Max

Unit

OE capacitance

C

OE

V

IN

= 0 V, f = 1.0 MHz

25

pF

WE capacitance

C

WE

V

IN

= 0 V, f = 1.0 MHz

25

pF

CS capacitance

C

CS

V

IN

= 0 V, f = 1.0 MHz

15

pF

Data I/O capacitance

C

I/O

V

I/O

= 0 V, f = 1.0 MHz

15

pF

Address input capacitance

C

AD

V

IN

= 0 V, f = 1.0 MHz

25

pF

This parameter is guaranteed by design but not tested.

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

AC CHARACTERISTICS ≠ WRITE/ERASE/PROGRAM OPERATIONS - WE CONTROLLED

(V

CC

= 5.0V, T

A

= -55

∞

C to +125

∞

C)

Parameter

Symbol

-90

-120

-150

Unit

Min

Max

Min

Max

Min

Max

Write Cycle Time

t

AVAV

t

WC

90

120

150

ns

Chip Select Setup Time

t

ELWL

t

CS

0

0

0

ns

Write Enable Pulse Width

t

WLWH

t

WP

45

50

50

ns

Address Setup Time

t

AVWL

t

AS

0

0

0

ns

Data Setup Time

t

DVWH

t

DS

45

50

50

ns

Data Hold Time

t

WHDX

t

DH

0

0

0

ns

Address Hold Time

t

WLAX

t

AH

45

50

50

ns

Write Enable Pulse Width High

t

WHWL

t

WPH

20

20

20

ns

Duration of Byte Programming Operation (1)

t

WHWH1

300

300

300

µ

s

Sector Erase (2)

t

WHWH2

15

15

15

sec

Read Recovery Time before Write

t

GHWL

0

0

0

µ

s

V

CC

Setup Time

t

VCS

50

50

50

µ

s

Chip Programming Time

44

44

44

sec

Chip Erase Time (3)

256

256

256

sec

Output Enable Hold Time (4)

t

OEH

10

10

10

ns

RESET Pulse Width

t

RP

500

500

500

ns

NOTES:

1. Typical value for t

WHWH1

is 7

µ

s.

2. Typical value for t

WHWH2

is 1sec.

3. Typical value for Chip Erase Time is 32sec.

4. For Toggle and Data Polling.

AC CHARACTERISTICS ≠ READ-ONLY OPERATIONS

(V

CC

= 5.0V, T

A

= -55

∞

C to +125

∞

C)

Parameter

Symbol

-90

-120

-150

Unit

Min

Max

Min

Max

Min

Max

Read Cycle Time

t

AVAV

t

RC

90

120

150

ns

Address Access Time

t

AVQV

t

ACC

90

120

150

ns

Chip Select Access Time

t

ELQV

t

CE

90

120

150

ns

Output Enable to Output Valid

t

GLQV

t

OE

40

50

55

ns

Chip Select High to Output High Z (1)

t

EHQZ

t

DF

20

30

35

ns

Output Enable High to Output High Z (1)

t

GHQZ

t

DF

20

30

35

ns

Output Hold from Addresses, CS or OE Change,

t

AXQX

t

OH

0

0

0

ns

whichever is First

RESET Low to Read Mode (1)

t

Ready

20

20

20

µ

s

1. Guaranteed by design, not tested.

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

CS

WE

RY/BY

RESET

t

RP

The rising edge of the last WE signal

Entire programming

or erase operations

t

Ready

t

BUSY

AC CHARACTERISTICS ≠ WRITE/ERASE/PROGRAM OPERATIONS,CS CONTROLLED

(V

CC

= 5.0V, V

SS

= 0V, T

A

= -55

∞

C to +125

∞

C)

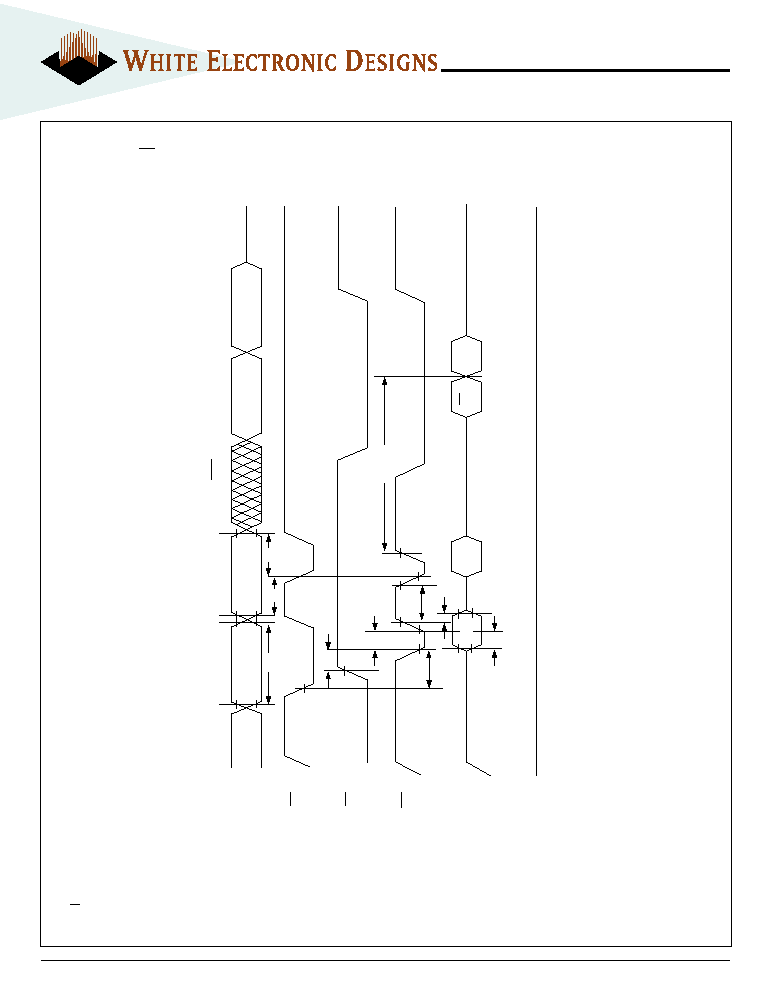

FIG. 2

AC TEST CIRCUIT

AC TEST CONDITIONS

NOTES:

V

Z

is programmable from -2V to +7V.

I

OL

& I

OH

programmable from 0 to 16mA.

Tester Impedance Z

0

= 75

.

V

Z

is typically the midpoint of V

OH

and V

OL

.

I

OL

& I

OH

are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

Parameter

Typ

Unit

Input Pulse Levels

V

IL

= 0, V

IH

= 3.0

V

Input Rise and Fall

5

ns

Input and Output Reference Level

1.5

V

Output Timing Reference Level

1.5

V

I

Current Source

D.U.T.

C = 50 pf

eff

I

OL

V

1.5V

(Bipolar Supply)

Z

Current Source

OH

Parameter

Symbol

-90

-120

-150

Unit

Min

Max

Min

Max

Min

Max

Write Cycle Time

t

AVAV

t

WC

90

120

150

ns

Write Enable Setup Time

t

WLEL

t

WS

0

0

0

ns

Chip Select Pulse Width

t

ELEH

t

CP

45

50

50

ns

Address Setup Time

t

AVEL

t

AS

0

0

0

ns

Data Setup Time

t

DVEH

t

DS

45

50

50

ns

Data Hold Time

t

EHDX

t

DH

0

0

0

ns

Address Hold Time

t

ELAX

t

AH

45

50

50

ns

Chip Select Pulse Width High

t

EHEL

t

CPH

20

20

20

ns

Duration of Byte Programming Operation (1)

t

WHWH1

300

300

300

µ

s

Sector Erase Time (2)

t

WHWH2

15

15

15

sec

Read Recovery Time

t

GHEL

0

0

0

µ

s

Chip Programming Time

44

44

44

sec

Chip Erase Time (3)

256

256

256

sec

Output Enable Hold Time (4)

t

OEH

10

10

10

ns

NOTES:

1. Typical value for t

WHWH1

is 7

µ

s.

2. Typical value for t

WHWH2

is 1sec.

3. Typical value for Chip Erase Time is 32sec.

4. For Toggle and Data Polling.

FIG. 3

RESET TIMING DIAGRAM

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

FIG. 3

AC WAVEFORMS FOR READ OPERATIONS

Addresses

FCS1/FCS2

FDx

FDx

FOE

FWE

Outputs

High Z

Addresses Stable

t

OE

t

RC

Output Valid

t

CE

t

ACC

t

OH

High Z

t

DF

6

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

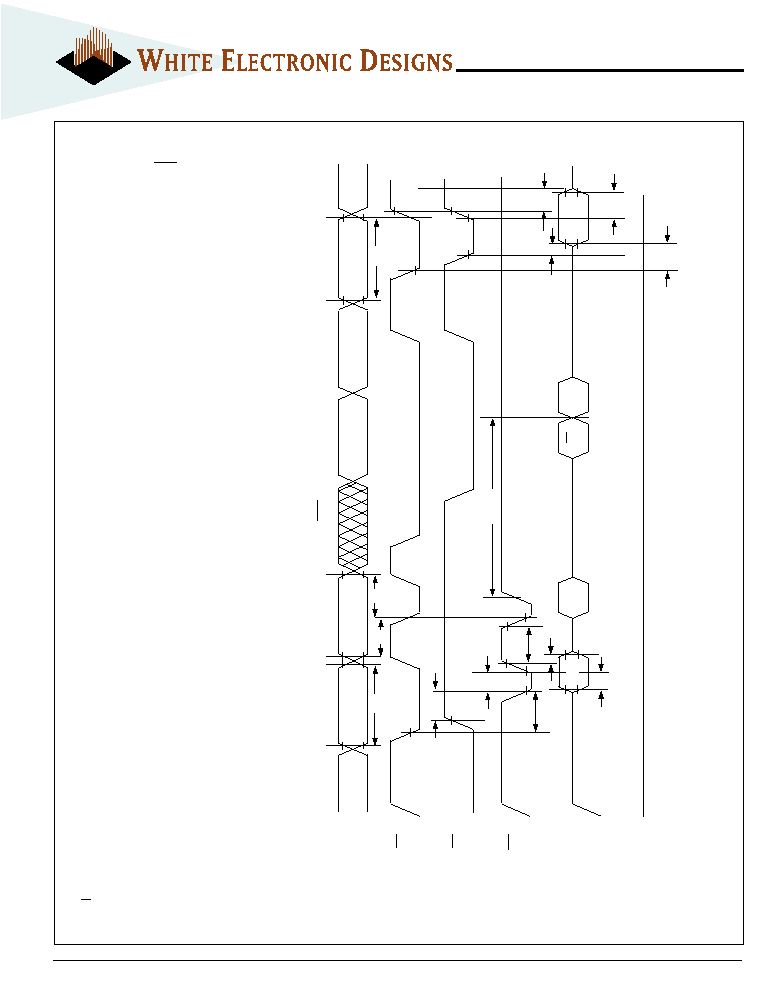

NOTES:

1. PA is the address of the memory location to be programmed.

2. PD is the data to be programmed at byte address.

3. D

7

is the output of the complement of the data written to the device.

4. D

OUT

is the output of the data written to the device.

5. Figure indicates last two bus cycles of four bus cycle sequence.

FIG. 4

WRITE/ERASE/PROGRAM

OPERATION, WE CONTROLLED

Addresses

CS

OE

WE

Data

5.0 V

5555H

PA

PA

t

WC

t

CS

PD

D

7

D

OUT

t

AH

t

WPH

t

DH

t

DS

Data Polling

t

AS

t

RC

t

WP

A0H

t

OE

t

DF

t

OH

t

CE

t

GHWL

t

WHWH1

7

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

FIG. 5

AC WAVEFORMS CHIP/SECTOR

ERASE OPERATIONS

NOTE:

1. SA is the sector address for Sector Erase.

Addresses

CS

OE

WE

Data

V

CC

5555H

2AAAH

2AAAH

SA

5555H

5555H

t

WP

t

CS

t

VCS

10H/30H

55H

80H

55H

AAH

AAH

t

AH

t

GHWL

t

WPH

t

DH

t

DS

t

AS

8

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

FIG. 6

AC WAVEFORMS FOR DATA POLLING

DURING EMBEDDED ALGORITHM OPERATIONS

CS

OE

WE

t

OE

t

CE

t

CH

t

OH

D7

D7 =

Valid Data

High Z

D0-D6 = Invalid

D0-D7

Valid Data

t

DF

D7

D0-D6

t

OEH

t

WHWH 1 or 2

Data

9

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

NOTES:

1. PA represents the address of the memory location to be programmed.

2. PD represents the data to be programmed at byte address.

3. D

7

is the output of the complement of the data written to the device.

4. D

OUT

is the output of the data written to the device.

5. Figure indicates the last two bus cycles of a four bus cycle sequence.

Addresses

WE

OE

CS

Data

5.0 V

5555H

PA

PA

t

WC

t

WS

PD

D

7

D

OUT

t

AH

t

CPH

t

CP

t

DH

t

DS

Data Polling

t

AS

t

GHEL

A0H

t

WHWH1

FIG. 7

ALTERNATE CS CONTROLLED

PROGRAMMING OPERATION TIMINGS

10

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

PACKAGE 208:

44 LEAD, CERAMIC FLAT PACK**

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

28.45 (1.120)

±

0.26 (0.010)

32.64 (1.285) TYP

12.95 (0.510)

±

0.13 (0.005)

3.81 (0.150)

TYP

3.18 (0.125)

MAX

0.13 (0.005)

±

0.05 (0.002)

PIN 1

IDENTIFIER

1.27 (0.050) TYP

9.90 (0.390)

±

0.13 (0.005)

26.67 (1.050) TYP

43.17 (1.699)

±

0.39 (0.015)

12.70 (0.500)

±

0.51 (0.020)

5.08 (0.200)

±

0.25 (0.010)

0.43 (0.017)

±

0.05 (0.002)

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

PACKAGE 102:

44 LEAD, CERAMIC SOJ**

1.27 (0.050) TYP

28.70 (1.13)

±

0.25 (0.010)

PIN 1 IDENTIFIER

26.7 (1.050) TYP

11.3 (0.446)

±

0.2 (0.009)

3.96 (0.156) MAX

0.2 (0.008)

±

0.05 (0.002)

9.55 (0.376)

±

0.25 (0.010)

1.27 (0.050)

±

0.25 (0.010)

0.89 (0.035)

Radius TYP

** Package to be developed.

** Package to be developed.

11

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

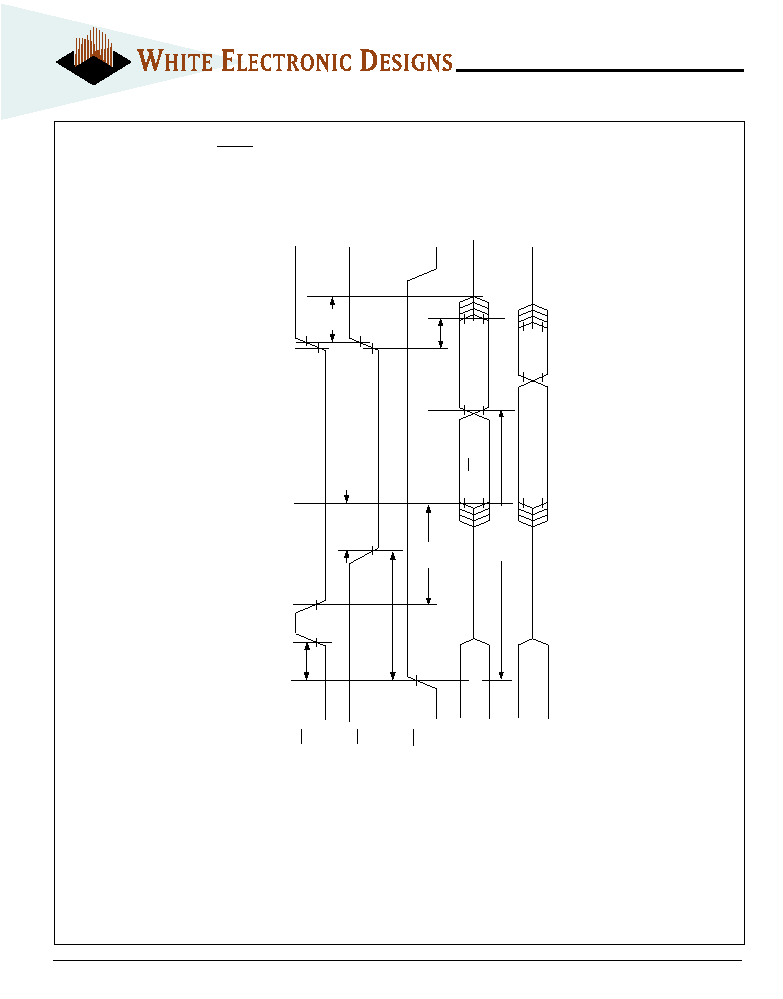

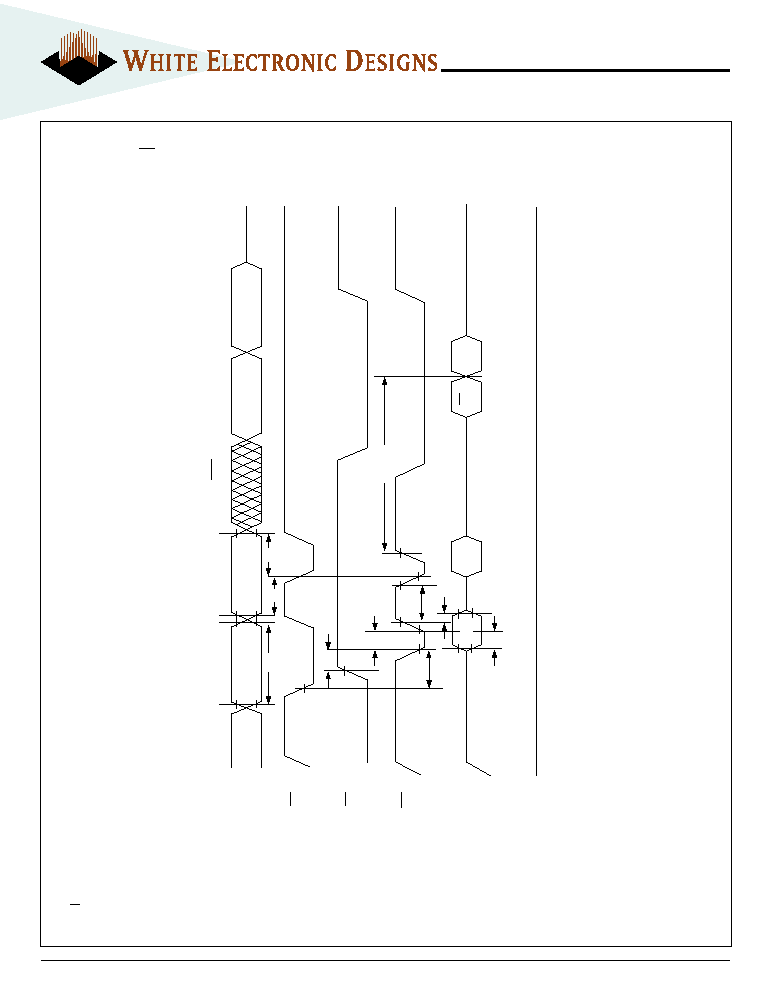

FIG. 8

ALTERNATE PIN CONFIGURATION FOR WF2M16W-XDAX5

PIN DESCRIPTION

I/O

0-15

Data Inputs/Outputs

A

1-21

Address Inputs

WE

Write Enable

CS

1-2

Chip Select

OE

Output Enable

V

CC

Power Supply

V

SS

Ground

RY/BY

Ready/Busy

RESET

Reset

BLOCK DIAGRAM

NOTE:

1. RY/BY is an open drain output and should be pulled up to Vcc with

an external resistor.

2. Address compatible with Intel 1M16 56 SSOP.

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

CS1

A12

A13

A14

A15

NC

CS2

A21

A20

A19

A18

A17

A16

V

CC

GND

I/O6

I/O14

I/O7

I/O15

RY/BY

OE

WE

NC

I/O13

I/O5

I/O12

I/O4

V

CC

NC

RESET

A11

A10

A9

A1

A2

A3

A4

A5

A6

A7

GND

A8

V

CC

I/O9

I/O1

I/O8

I/O0

NC

NC

NC

NC

I/O2

I/O10

I/O3

I/O11

GND

56 CSOP

2M x 8

2M x 8

A

1 - 2 1

O E

W E

C S

1

C S

2

I / O

0 - 7

I / O

8 - 1 5

R E S E T

R Y / B Y

PACKAGE 207:

56 LEAD, CERAMIC SOP*

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

* Package Dimensions subject to change

23.63 (0.930)

±

0.25 (0.010)

12.96 (0.510)

±

0.15 (0.006)

0.18 (0.007)

±

0.05 (0.002)

21.59 (0.850) TYP

16.13 (0.635)

±

0.13 (0.005)

0.25 (0.010)

±

0.05 (0.002)

0.80 (0.031) TYP

4.06 (0.160)

MAX

PIN 1 IDENTIFIER

0

∞

/ -4

∞

0.51 (0.020) TYP

DETAIL "A"

SEE DETAIL "A"

+

1.02 (0.040)

±

0.18 (0.007)

+

1.60 (0.063) TYP

2.87 (0.113)

MAX

R = 0.18 (0.007) TYP

12

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.whiteedc.com

WF2M16-XXX5

W F 2M16 X - XXX X X 5 X

LEAD FINISH:

Blank = Gold plated leads

A = Solder dip leads

V

PP

PROGRAMMING VOLTAGE

5 = 5V

DEVICE GRADE:

M = Military, 883 Screened -55

∞

C to +125

∞

C

I = Industrial

-40

∞

C to +85

∞

C

C = Commercial

0

∞

C to +70

∞

C

PACKAGE TYPE:

DA = 56 Lead CSOP (Package 207)

fits standard 56 SSOP footprint

DL = 44 Lead Ceramic SOJ (Package 102)*

FL = 44 Lead Ceramic Flatpack (Package 208)*

ACCESS TIME (ns)

IMPROVEMENT MARK:

∑ Address Pinout for 56 CSOP Package

W = Word Wide Applications

ORGANIZATION of 2M x 16

User configurable as 2 x 2M x 8

Flash

WHITE ELECTRONIC DESIGNS CORP.

ORDERING INFORMATION

* Package to be developed.

DEVICE TYPE

SECTOR SIZE

SPEED

PACKAGE

SMD NO.

2M x 16 5V Flash Module

64KByte

150ns

56 lead CSOP (DA)

5962-97610 01HXX

2M x 16 5V Flash Module

64KByte

120ns

56 lead CSOP (DA)

5962-97610 02HXX

2M x 16 5V Flash Module

64KByte

90ns

56 lead CSOP (DA)

5962-97610 03HXX