1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WS128K32-XG2TXE

December 2000

Rev. 0

ADVANCED*

128Kx32 SRAM MULTICHIP PACKAGE, RADIATION TOLLERANT

TTL Compatible Inputs and Outputs

Built in Decoupling Caps and Multiple Ground Pins

for Low Noise Operation

Weight

WS128K32-XG2TXE ≠ 8 grams typical

Radiation tolerant with epitaxial layer on die.

6T memory cells provide excellent protection

against soft errors

* This product is under development, is not qualifi ed or characterized and is subject to

change or cancellation without notice.

FEATURES

Access Times of 35, 45, 55ns

Packaging

∑ 68 lead, 22.4mm CQFP (G2T), 4.57mm (0.180"),

(Package 509)

Organized as 128Kx32; User Confi gurable as

256Kx16 or 512Kx8

Low Power Data Retention

Commercial,

Industrial

and

Military

Temperature

Ranges

5V

Power

Supply

Low

Power

CMOS

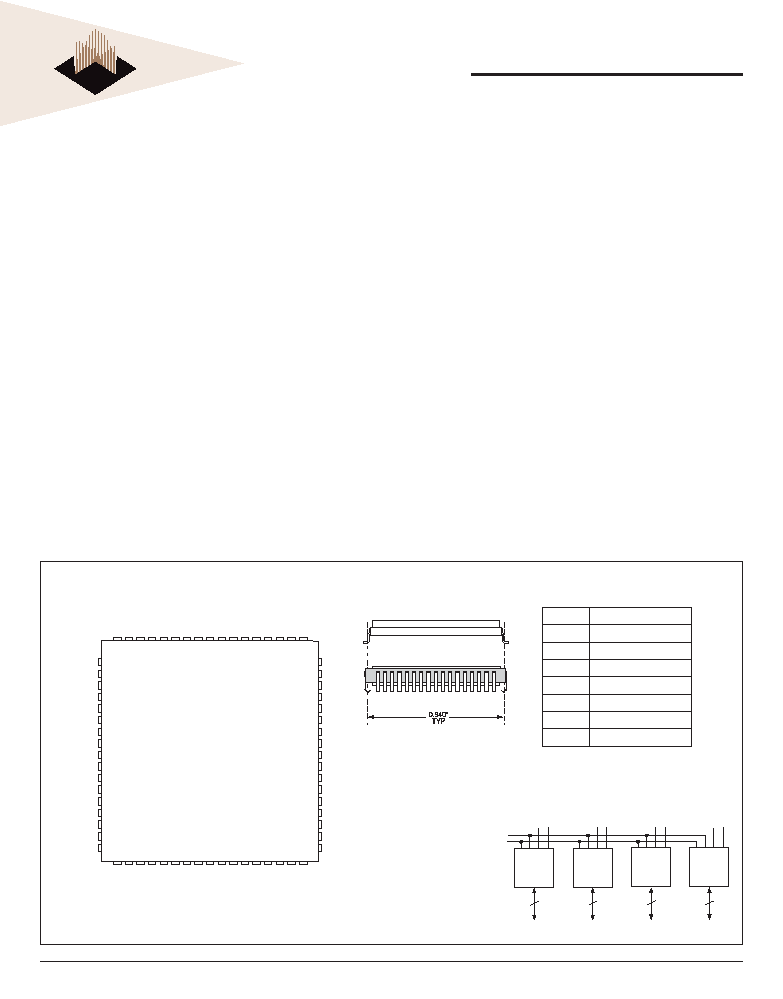

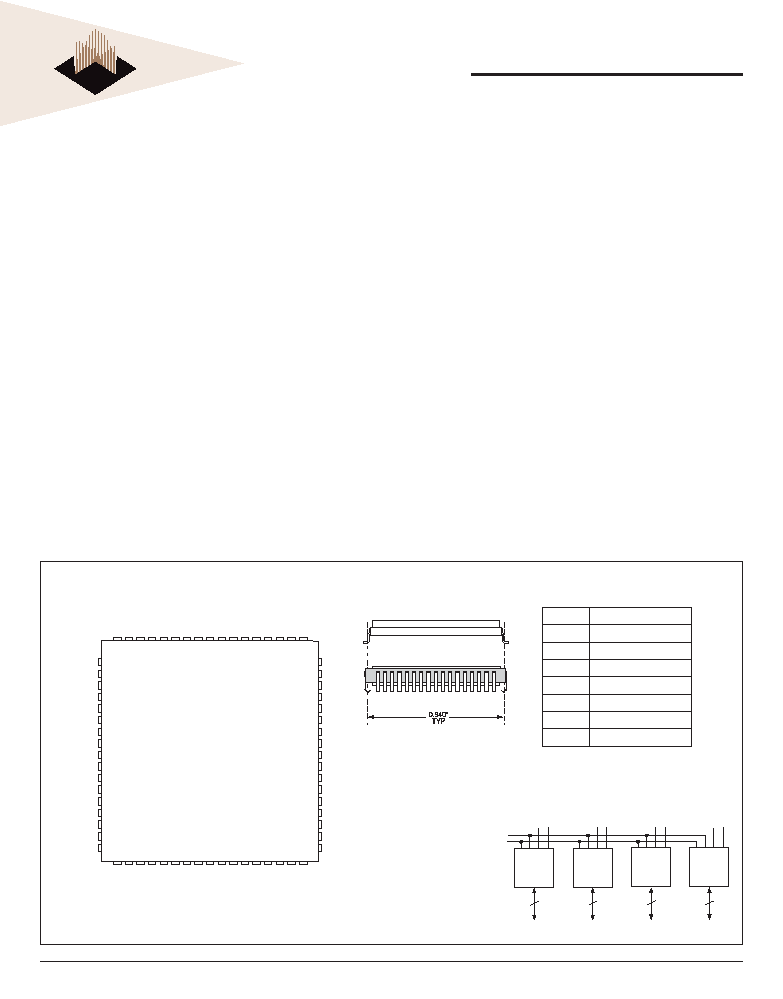

Pin Description

I/O

0-31

Data Inputs/Outputs

A

0-16

Address Inputs

WE

1-4

#

Write Enables

CS

1-4

#

Chip Selects

OE#

Output Enable

V

CC

Power Supply

GND Ground

NC

Not Connected

Block Diagram

Top View

FIGURE 1 ≠ PIN CONFIGURATION FOR WS128K32N-XG2TXE

WE

1

# CS

1

#

CS

2

#

CS

3

#

CS

4

#

WE

4

#

WE

3

#

WE

2

#

128K x 8

128K x 8

128K x 8

128K x 8

OE#

A

0-16

I/O

0-7

I/O

24-31

I/O

16-23

I/O

8-15

8

8

8

8

I/O

0

I/O

1

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

GND

I/O

8

I/O

9

I/O

10

I/O

11

I/O

12

I/O

13

I/O

14

I/O

15

I/O

16

I/O

17

I/O

18

I/O

19

I/O

20

I/O

21

I/O

22

I/O

23

GND

I/O

24

I/O

25

I/O

26

I/O

27

I/O

28

I/O

29

I/O

30

I/O

31

V

CC

A

11

A

12

A

13

A

14

A

15

A

16

CS

1

#

OE#

CS

2

#

NC

WE

2

#

WE

3

#

WE

4

#

NC

NC

NC

NC

A

0

A

1

A

2

A

3

A

4

A

5

CS

3

#

GND

CS

4

#

WE

1

#

A

6

A

7

A

8

A

9

A

10

V

CC

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

9 8 7 6 5 4 3 2 1 68 67

66 65

64

63

62 61

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

The White 68 lead G2T CQFP fi lls

the same fi t and function as the

JEDEC 68 lead CQFJ or 68 PLCC.

But the G2T has the TCE and lead

inspection advantage of the CQFP

form.

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WS128K32-XG2TXE

December 2000

Rev. 0

ADVANCED

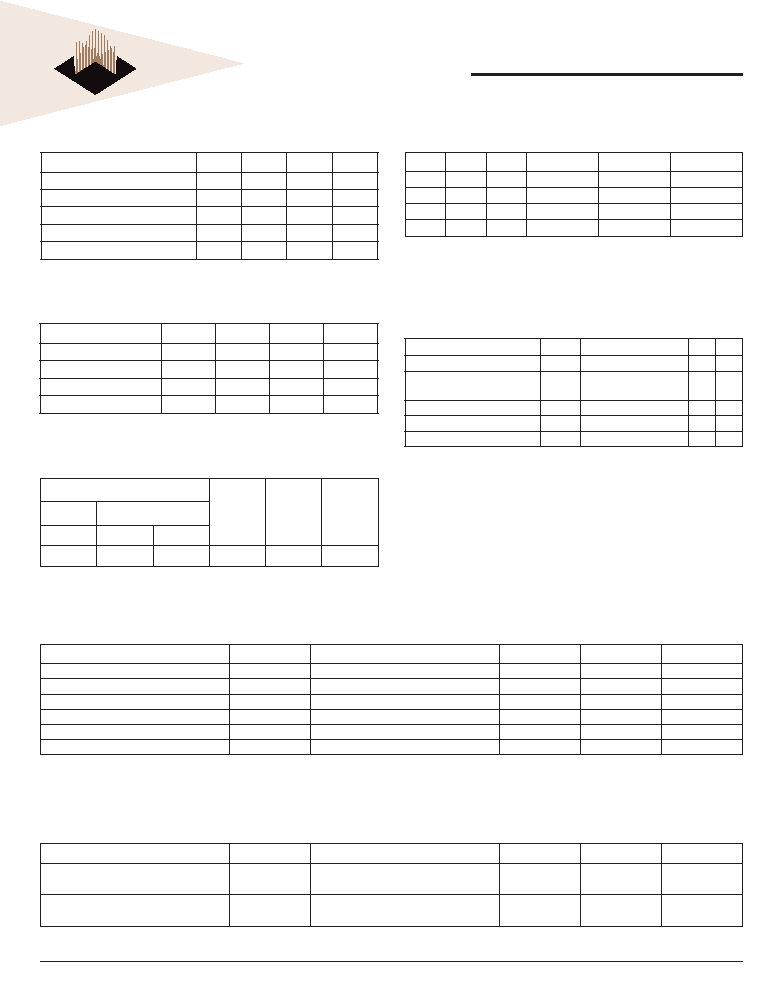

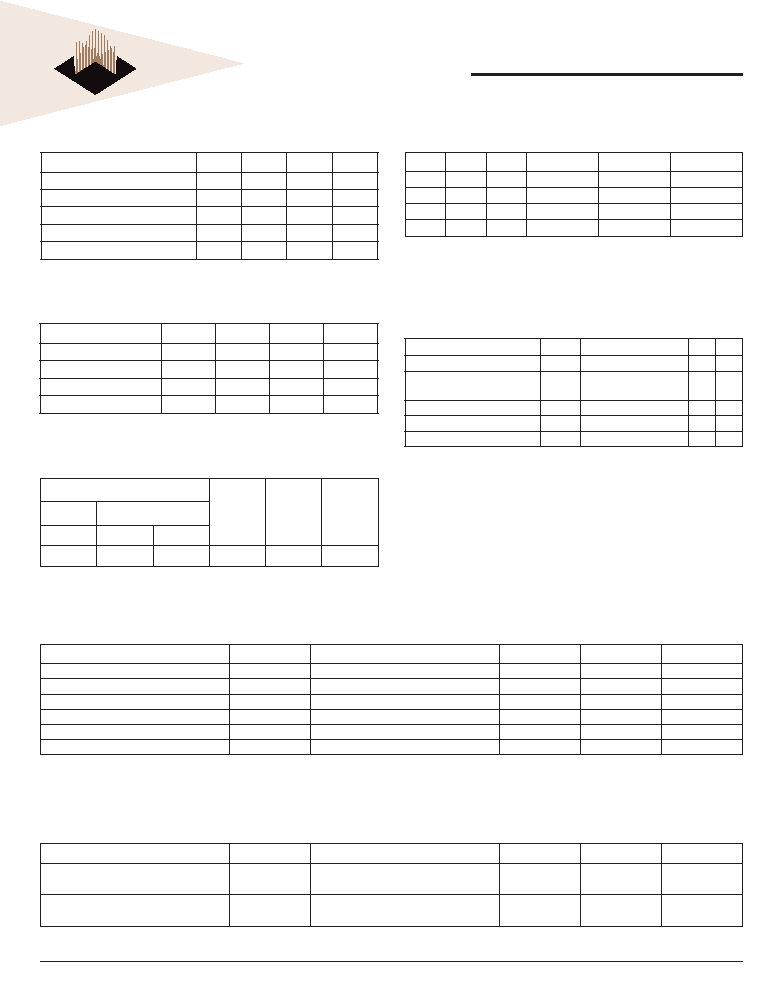

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Min

Max

Unit

Operating Temperature

T

A

-55 +125

∞C

Storage Temperature

T

STG

-65

+150

∞C

Signal Voltage Relative to GND

V

G

-0.5

V

CC

+0.5

V

Junction Temperature

T

J

150

∞C

Supply Voltage

V

CC

-0.5

7.0

V

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Min

Max

Unit

Supply Voltage

V

CC

4.5

5.5

V

Input High Voltage

V

IH

2.2

V

CC

+ 0.3

V

Input Low Voltage

V

IL

-0.3

+0.8

V

Opertating Temp. (MIL)

T

A

-55

+125

∞C

TRUTH TABLE

CS#

OE#

WE#

Mode

Data I/O

Power

H

X

X

Standby

High Z

Standby

L

L

H

Read

Data Out

Active

L

X

L

Write

Data In

Active

L

H

H

Out Disable

High Z

Active

CAPACITANCE

T

A

= +25∞C

Parameter

Symbol

Conditions Max Unit

OE# capacitance

C

OE

V

IN

= 0V, f = 1.0 MHz

50

pF

WE

1-4

# capacitance

CQFP G2T

C

WE

V

IN

= 0V, f = 1.0 MHz

20

pF

CS

1-4

# capacitance

C

CS

V

IN

= 0V, f = 1.0 MHz

20

pF

Data# I/O capacitance

C

I/O

V

I/O

= 0V, f = 1.0 MHz

20

pF

Address input capacitance

C

AD

V

IN

= 0V, f = 1.0 MHz

50

pF

This parameter is guaranteed by design but not tested.

DC CHARACTERISTICS

V

CC

= 5.0V, V

SS

= 0V, -55∞C T

A

+125∞C

Parameter

Sym

Conditions

Min

Max

Units

Input Leakage Current

I

LI

V

CC

= 5.5, V

IN

= GND to V

CC

10

µA

Output Leakage Current

I

LO

CS# = V

IH

, OE# = V

IH

, V

OUT

= GND to V

CC

10

µA

Operating Supply Current

I

CC

CS# = V

IL

, OE# = V

IH

, f = 5MHz, V

CC

= 5.5

520

mA

Standby Current

I

SB

CS# = V

IH

, OE# = V

IH

, f = 5MHz, V

CC

= 5.5

8

mA

Output Low Voltage

V

OL

I

OL

= 8mA, V

CC

= 4.5

0.4

V

Output High Voltage

V

OH

I

OH

= -40mA, V

CC

= 4.5

2.4

V

NOTE: DC test conditions: V

IH

= V

CC

-0.3V, V

IL

= 0.3V

DATA RETENTION CHARACTERISTICS

-55∞C T

A

+125∞C

Characteristic

Sym

Conditions

Min

Max

Units

Data Retention Voltage

Data Retention Quiescent Current

V

CC

I

CCDR

V

CC

= 2.0V

CS V

CC

-0.2V

2

--

--

1

V

mA

Chip Disable to Data Retention Time (1)

Operation Recovery Time (1)

T

CDR

T

R

V

IN

V

CC

-0.2V

or V

IN

0.2V

0

T

RC

--

--

ns

ns

NOTE: Parameter guaranteed, but not tested.

RADIATION CHARACTERISTICS

Total Dose (TM1019.5)

Latch-up

25∞C

V

CC

Max

(MeV/mg/cm2)

SEU LET

Threshold

(V

CC

MIN)

(MeV/mg/cm2)

Cross

Section

/BIT

(E-6 cm2)

Functional

Parametric

(Krads)

(Krads)

Typical Iccsb (mA

)

30

30

1.2

>100

2

0.2

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WS128K32-XG2TXE

December 2000

Rev. 0

ADVANCED

I

Current Source

D.U.T.

C = 50 pf

eff

I

OL

V

1.5V

(Bipolar Supply)

Z

Current Source

OH

AC CHARACTERISTICS

V

CC

= 5.0V, GND = 0V, -55∞C T

A

+125∞C

Parameter

Write Cycle

Symbol

-35

-45

-55

Units

Min

Max

Min

Max

Min

Max

Write Cycle Time

t

WC

35

45

55

ns

Chip Select to End of Write

t

CW

25

35

45

ns

Address Valid to End of Write

t

AW

25

35

45

ns

Data Valid to End of Write

t

DW

20

25

25

ns

Write Pulse Width

t

WP

25

35

45

ns

Address Setup Time

t

AS

0

0

0

ns

Address Hold Time

t

AH

0

0

0

ns

Output Active from End of Write

t

OW

1

0

0

0

ns

Write Enable to Output in High Z

t

WHZ

1

10

15

20

ns

Data Hold Time

t

DH

0

0

0

ns

1. This parameter is guaranteed by design but not tested.

AC CHARACTERISTICS

V

CC

= 5.0V, GND = 0V, -55∞C T

A

+125∞C

Parameter

Read Cycle

Symbol

-35

-45

-55

Units

Min

Max

Min

Max

Min

Max

Read Cycle Time

t

RC

35

45

55

ns

Address Access Time

t

AA

35

45

55

ns

Output Hold from Address Change

t

OH

3

3

3

ns

Chip Select Access Time

t

ACS

35

45

55

ns

Output Enable to Output Valid

t

OE

15

20

30

ns

Chip Select to Output in Low Z

t

CLZ

1

3

3

3

ns

Output Enable to Output in Low Z

t

OLZ

1

0

0

0

ns

Chip Disable to Output in High Z

t

CHZ

1

20

20

20

ns

Output Disable to Output in High Z

t

OHZ

1

12

15

20

ns

1. This parameter is guaranteed by design but not tested.

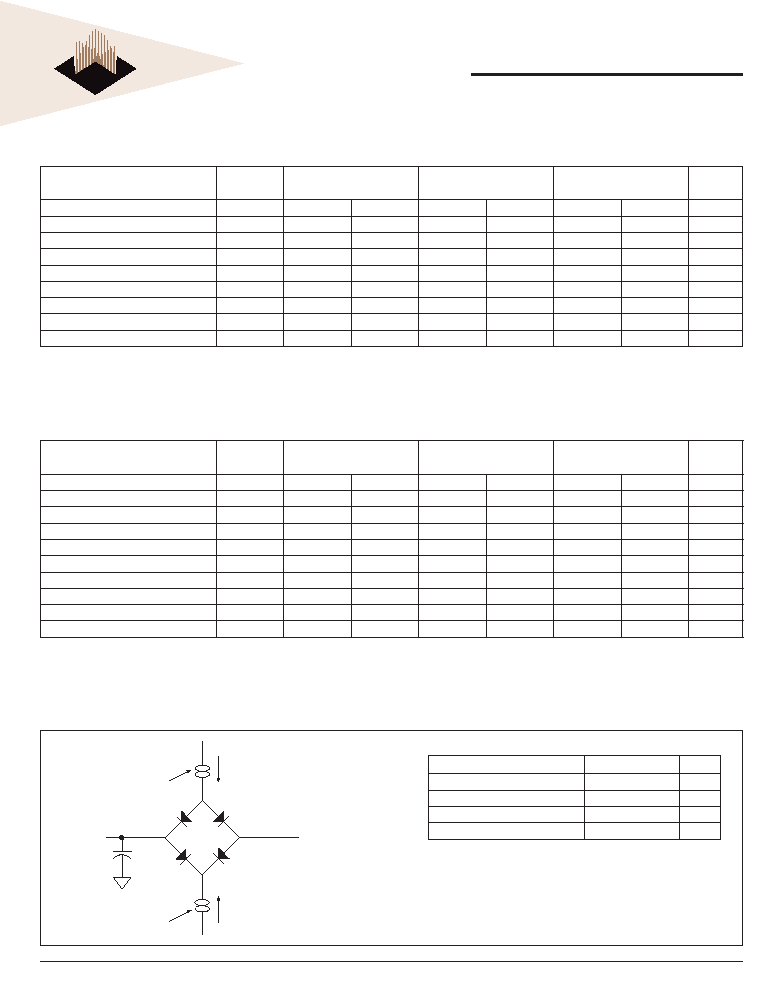

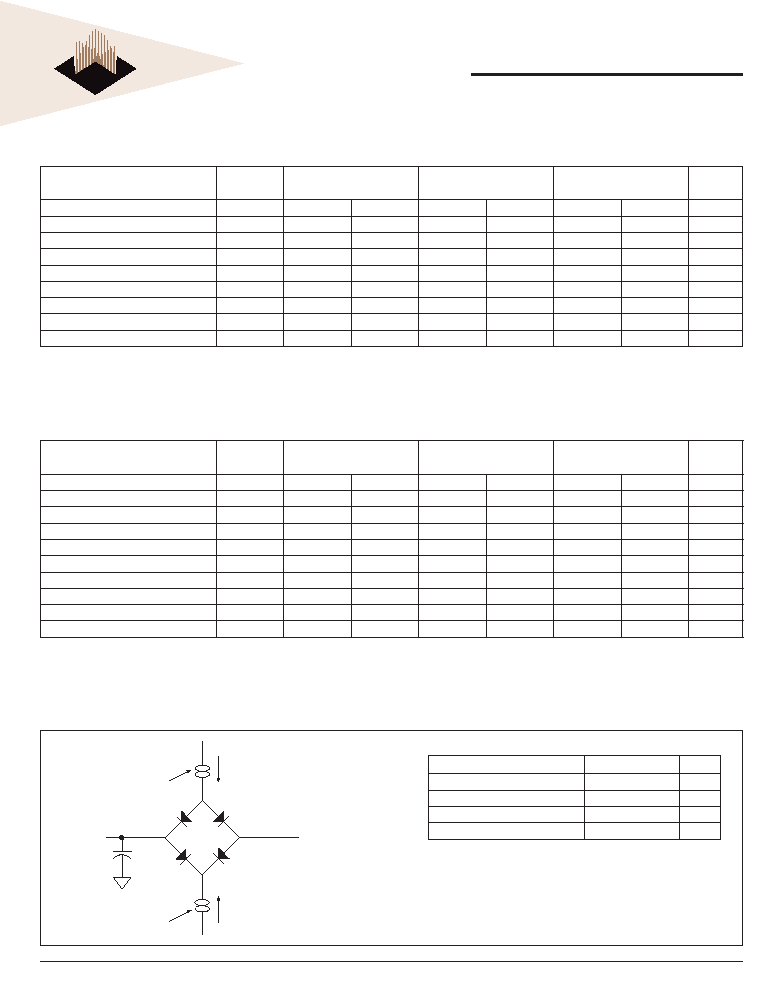

FIGURE 2 ≠ AC TEST CIRCUIT

Notes:

V

Z

is programmable from -2V to +7V.

I

OL

& I

OH

programmable from 0 to 16mA.

Tester Impedance Z0 = 75.

V

Z

is typically the midpoint of V

OH

and V

OL

.

I

OL

& I

OH

are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

AC Test Conditions

Parameter

Typ

Unit

Input Pulse Levels

V

IL

= 0, V

IH

= 3.0

V

Input Rise and Fall

5

ns

Input and Output Reference Level

1.5

V

Output Timing Reference Level

1.5

V

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WS128K32-XG2TXE

December 2000

Rev. 0

ADVANCED

WS32K32-XHX

READ CYCLE 1, (CS# = OE# = V

IL

, WE# = V

IH

)

READ CYCLE 2 (WE# = V

IH

)

CS#

OE#

WRITE CYCLE 1, WE# CONTROLLED

CS#

WE#

WRITE CYCLE 2, CS# CONTROLLED

CS#

WE#

FIGURE 3 ≠ TIMING WAVEFORM - READ CYCLE

FIGURE 5 ≠ WRITE CYCLE - CS# CONTROLLED

FIGURE 4 ≠ WRITE CYCLE - WE# CONTROLLED

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WS128K32-XG2TXE

December 2000

Rev. 0

ADVANCED

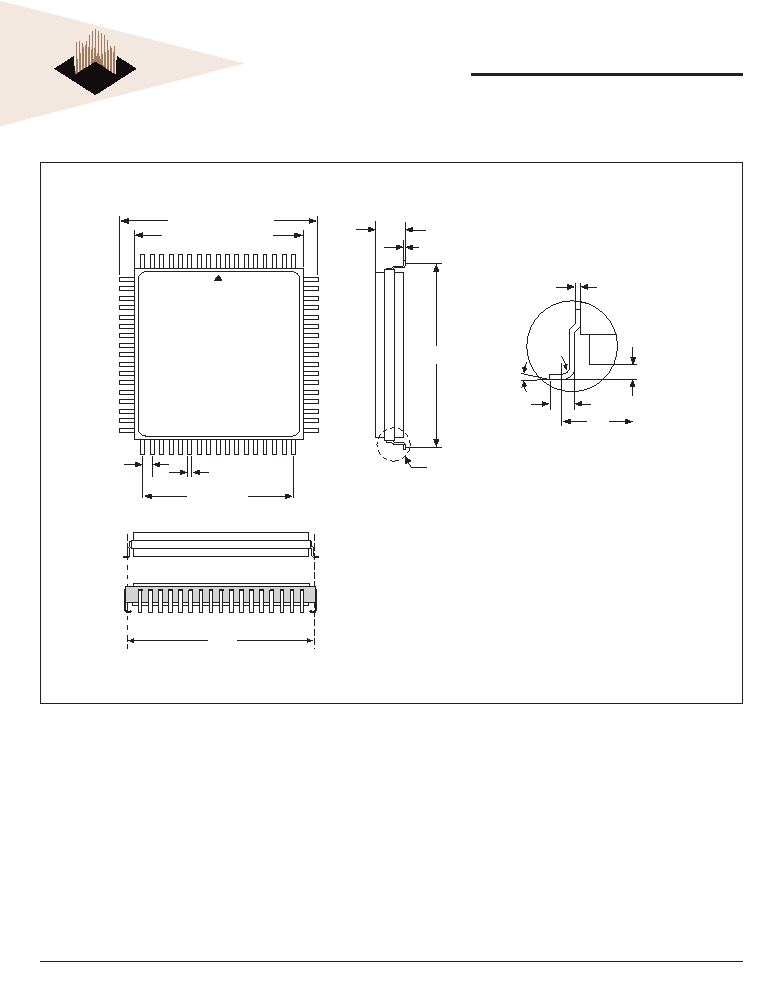

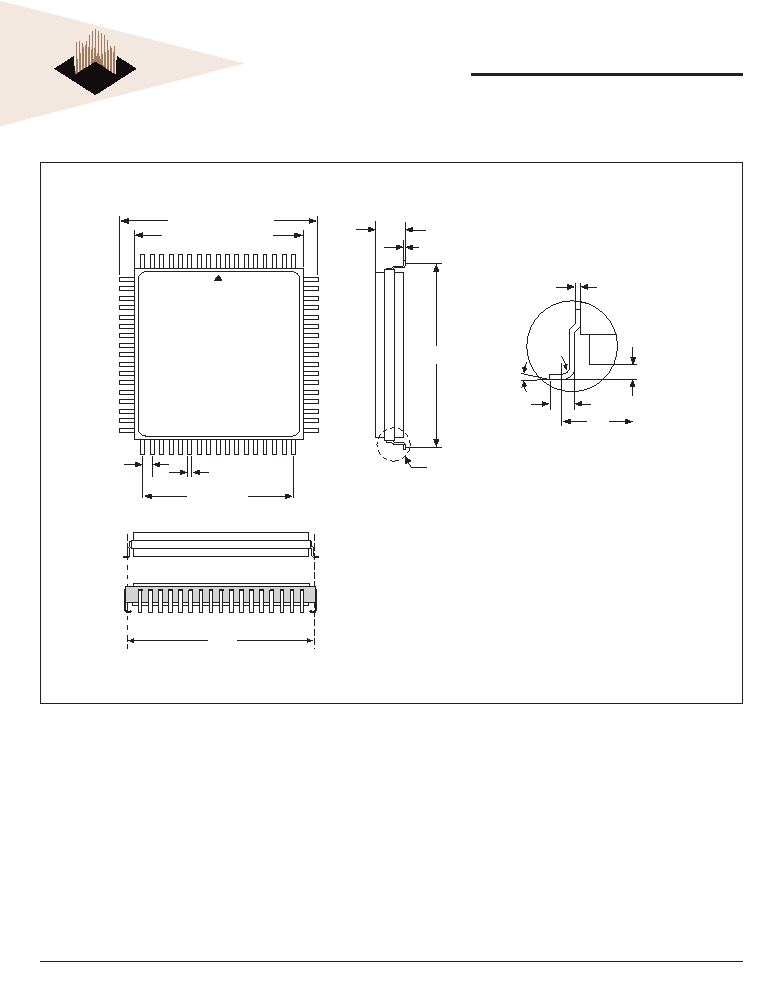

PACKAGE 510: 68 LEAD, CERAMIC QUAD FLAT PACK, CQFP (G2T)

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

The White 68 lead G2T CQFP

fi lls the same fi t and function

as the JEDEC 68 lead CQFJ

or 68 PLCC. But the G2T has

the TCE and lead inspection

advantage of the CQFP form.

0.38 (0.015) ± 0.05 (0.002)

0.27 (0.011) ± 0.04 (0.002)

25.15 (0.990) ± 0.26 (0.010) SQ

1.27

(0.050)

TYP

24.03 (0.946)

± 0.26 (0.010)

22.36 (0.880) ± 0.26 (0.010) SQ

20.3 (0.800) REF

4.57 (0.180) MAX

0.19 (0.007)

± 0.06 (0.002)

23.87

(0.940) REF

1.0 (0.040)

± 0.127 (0.005)

0.25 (0.010) REF

1∞ / 7∞

R 0.25

(0.010)

DETAIL A

SEE DETAIL "A"

Pin 1

0.940"

TYP