White Electronic Designs

1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY*

FEATURES

PC2700

@

CL2.5

Double-data-rate

architecture

Bi-directional data strobes (DQS)

Differential clock inputs (CK & CK#)

Programmable Read Latency 2,2.5 (clock)

Programmable Burst Length (2,4,8)

Programmable Burst type (sequential & interleave)

Auto and self refresh, (8K/64ms refresh)

Serial presence detect with EEPROM

Power

supply:

V

CC

/V

CCQ

: 2.5V ± 0.20V

Dual

Rank

Standard 200 pin SO-DIMM package

∑ Package height options

D4: 31.75mm (1.25")

NOTE: Consult factory for availability of:

∑ RoHS compliant products

∑ Vendor source control options

∑

Industrial

Temperature

option

DESCRIPTION

The WV3EG232M64STSU is a 2x32Mx64 Double Data

Rate SDRAM memory module based on 512Mb DDR

SDRAM component. The module consists of eight 32Mx16

DDR SDRAMs in 66 pin TSOP packages mounted on a

200 pin FR4 substrate.

Synchronous design allows precise cycle control with the

use of system clock. Data 1/0 transactions are possible on

both edges and Burst Lengths allow the same device to be

useful for a variety of high bandwidth, high performance

memory system applications.

* This product is under development, is not qualifi ed or characterized and is subject to

change without notice.

512MB ≠ 2x32Mx64 DDR SDRAM UNBUFFERED

OPERATING FREQUENCIES

DDR333@CL=2.5

Clock Speed

166MHz

CL-t

RCD

-t

RP

2.5-3-3

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

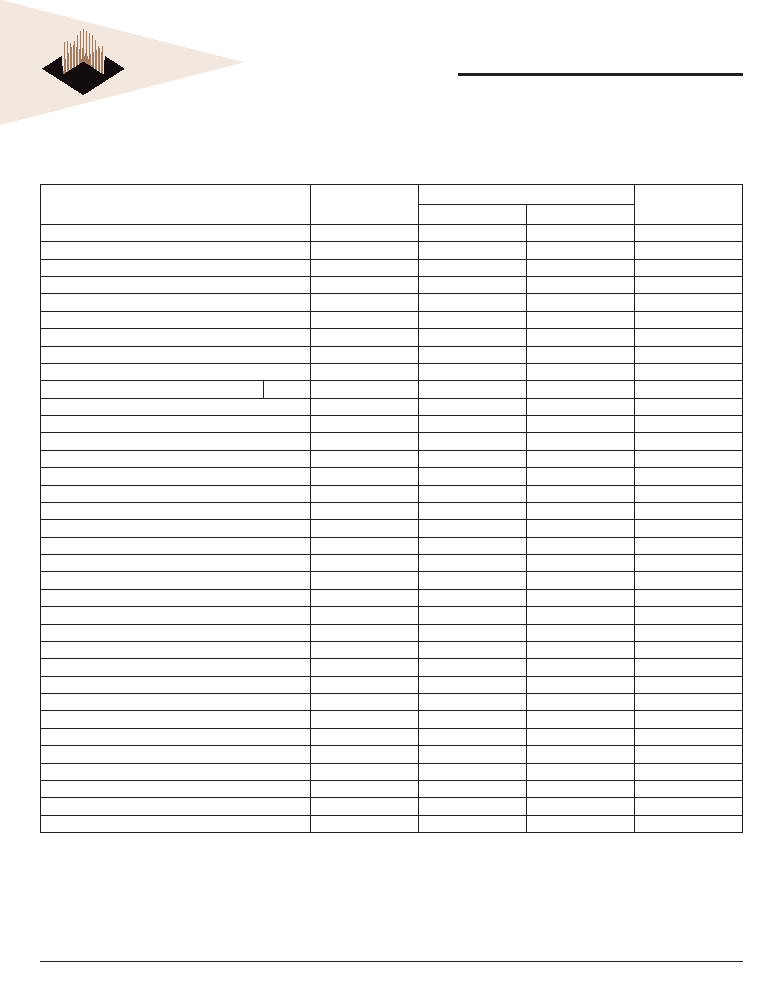

PIN CONFIGURATION

PIN NAMES

AO -A12

Address input (Multiplexed)

BA0-BA1

Bank SelectAddress

DQO-DQ63

Data I nput/Output

DQSO-DQS7

Data Strobe Input/Output

CK0, CK1

Clock Input

CK0#, CK1#

Clock input

CKE0, CKE1

Clock Enable input

CS0#, CS1#

Chip select Input

RAS#

Row Address Strobe

CAS#

Column Address Strobe

WE#

Write Enable

DM0-DM7

Data-In Mask

V

CC

Power Supply

V

CCQ

Power Supply for DQS

V

SS

Ground

V

REF

Power Supply for Reference

V

CCSPD

Serial EEPROM Power Supply

SDA

Serial data I/O

SCL

Serial clock

SA0-SA2

Address in EEPROM

NC

No Connect

PIN

SYMBOL

PIN

SYMBOL

PIN

SYMBOL

PIN

SYMBOL

1

V

REF

51

V

SS

101

A9

151

DQ42

2

V

REF

52

V

SS

102

A8

152

DQ46

3

V

SS

53

DQ19

103

V

SS

153

DQ43

4

V

SS

54

DQ23

104

V

SS

154

DQ47

5

DQ0

55

DQ24

105

A7

155

V

CC

6

DQ4

56

DQ28

106

A6

156

V

CC

7

DQ1

57

V

CC

107

A5

157

V

CC

8

DQ5

58

V

CC

108

A4

158

CK1#

9

V

CC

59

DQ25

109

A3

159

V

SS

10

V

CC

60

DQ29

110

A2

160

CK1

11

DQS0

61

DQS3

111

A1

161

V

SS

12

DM0

62

DM3

112

A0

162

V

SS

13

DQ2

63

V

SS

113

V

CC

163

DQ48

14

DQ6

64

V

SS

114

V

CC

164

DQ52

15

V

SS

65

DQ26

115

A10/AP

165

DQ49

16

V

SS

66

DQ30

116

BA1

166

DQ53

17

DQ3

67

DQ27

117

BA0

167

V

CC

18

DQ7

68

DQ31

118

RAS#

168

V

CC

19

DQ8

69

V

CC

119

WE#

169

DQS6

20

DQ12

70

V

CC

120

CAS#

170

DM6

21

V

CC

71

NC

121

CS0#

171

DQ50

22

V

CC

72

NC

122

CS1#

172

DQ54

23

DQ9

73

NC

123

NC

173

V

SS

24

DQ13

74

NC

124

NC

174

V

SS

25

DQS1

75

V

SS

125

V

SS

175

DQ51

26

DM1

76

V

SS

126

V

SS

176

DQ55

27

V

SS

77

NC

127

DQ32

177

DQ56

28

V

SS

78

NC

128

DQ36

178

DQ60

29

DQ10

79

NC

129

DQ33

179

V

CC

30

DQ14

80

NC

130

DQ37

180

V

CC

31

DQ11

81

V

CC

131

V

CC

181

DQ57

32

DQ15

82

V

CC

132

V

CC

182

DQ61

33

V

CC

83

NC

133

DQS4

183

DQS7

34

V

CC

84

NC

134

DM4

184

DM7

35

CK0

85

NC

135

DQ34

185

V

SS

36

V

CC

86

NC

136

DQ38

186

V

SS

37

CK0#

87

V

SS

137

V

SS

187

DQ58

38

V

SS

88

V

SS

138

V

SS

188

DQ62

39

V

SS

89

NC

139

DQ35

189

DQ59

40

V

SS

90

V

SS

140

DQ39

190

DQ63

41

DQ16

91

NC

141

DQ40

191

V

CC

42

DQ20

92

V

CC

142

DQ44

192

V

CC

43

DQ17

93

V

CC

143

V

CC

193

SDA

44

DQ21

94

V

CC

144

V

CC

194

SA0

45

V

CC

95

CKE1

145

DQ41

195

SCL

46

V

CC

96

CKE0

146

DQ45

196

SA1

47

DQS2

97

NC

147

DQS5

197

V

CC

SPD

48

DM2

98

NC

148

DM5

198

SA2

49

DQ18

99

A12

149

V

SS

199

NC

50

DQ22

100

A11

150

V

SS

200

NC

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

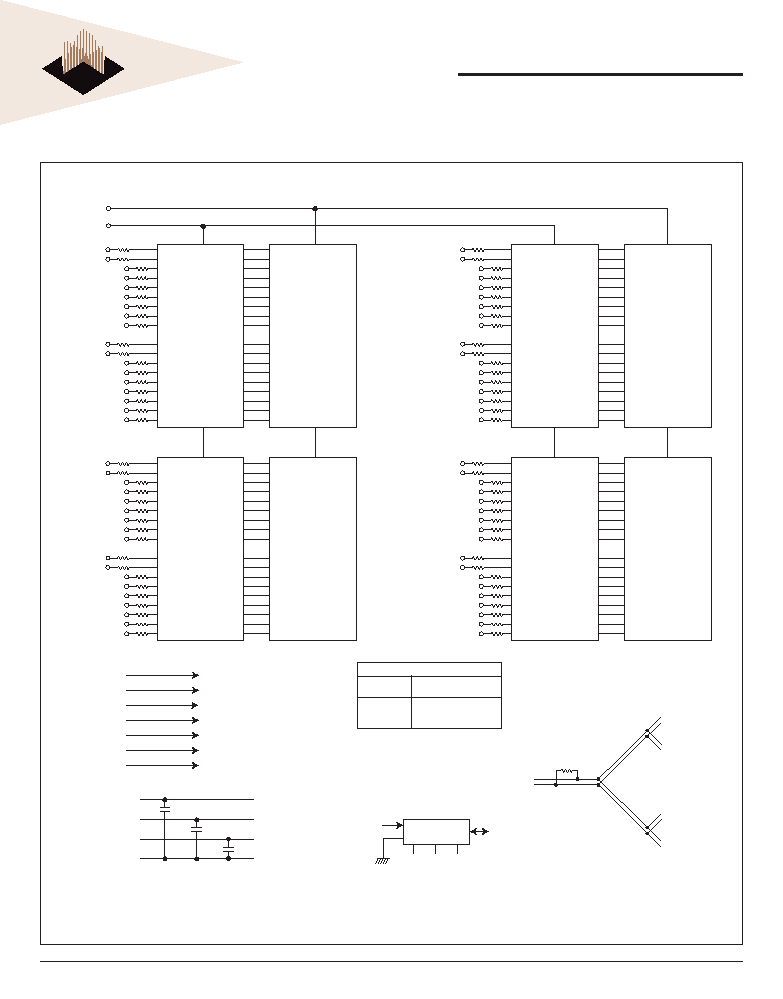

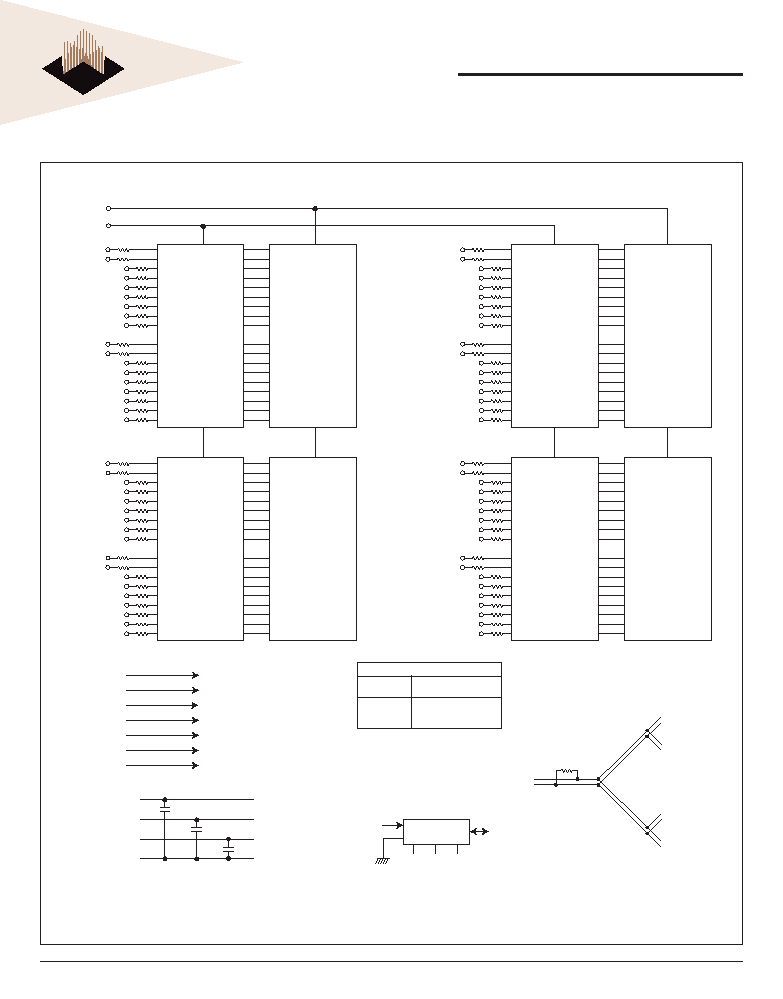

FUNCTIONAL BLOCK DIAGRAM

CS1#

CS0#

DQS0

DM0

DQS1

DM1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

CS#

CS#

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

DQS4

DM4

DQS5

DM5

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

CS#

CS#

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

DQS2

DM2

DQS3

DM3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

CS#

CS#

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

DQS6

DM6

DQS7

DM7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

CS#

CS#

LDQS

LDM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

UDQS

UDM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

BA0, BA1

A0-A12

RAS#

BA0, BA1: DDR SDRAMs

A0-A12: DDR SDRAMs

RAS#: DDR SDRAMs

CAS#: DDR SDRAMs

CKE0: DDR SDRAMs

WE#: DDR SDRAMs

CAS#

CKE0

WE#

CKE1: DDR SDRAMs

CKE1

DDR SDRAM

DDR SDRAM

V

CCSPD

V

CC

/V

CCQ

V

REF

V

SS

DDR SDRAM

SPD

A0

SA0

SERIAL PD

SDA

A1

SA1

A2

SA2

WP

SCL

*Clock Net Wiring

Card

Edge

DDR SDRAMs

DDR SDRAMs

DDR SDRAMs

DDR SDRAMs

R = 120 Ohm

CK0/1/2

CK0/1/2#

Clock Wiring

Clock

Input

SDRAMs

4 SDRAMs

4 SDRAMs

NC

CK0/CK0#

CK1/CK1#

CK2/CK2#

NOTE: All resistor values are 22 ohmes unless otherwise specifi ed.

Notes:

1.

DQ-to-I/O wiring is shown as recommended but may be changed.

2.

DQ/DQS/DM/CKE/CS relationships must be maintained as shown.

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

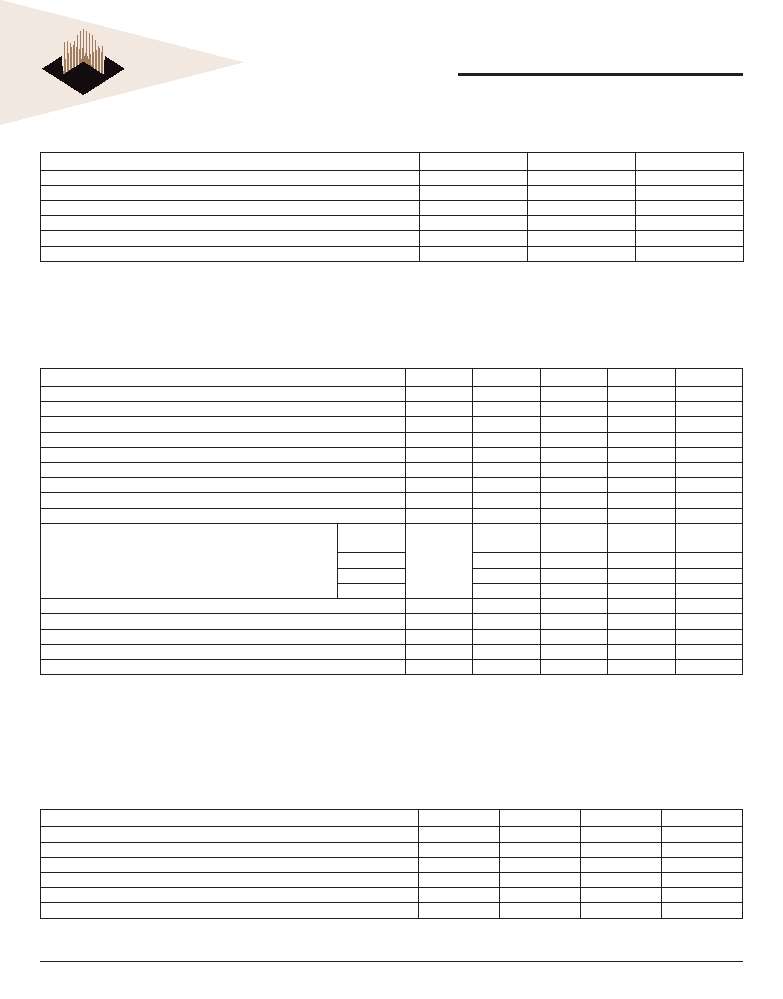

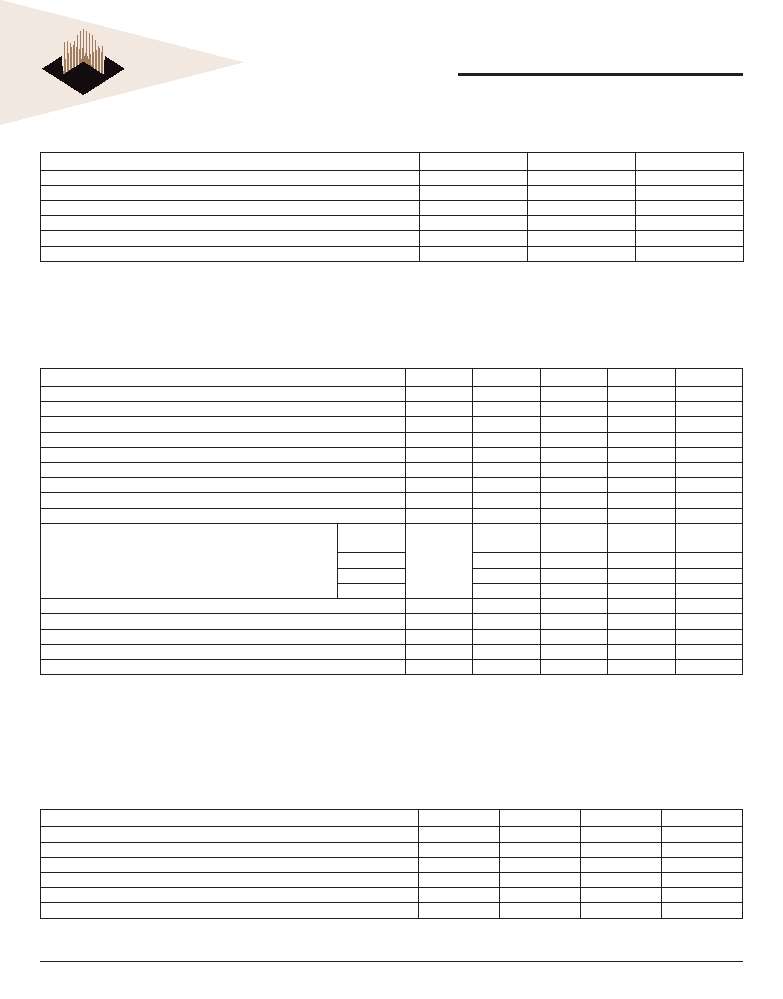

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Value

Units

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-0.5 ~ 3.6

V

Voltage on V

CC

and V

CCQ

supply relative to V

SS

V

CC,

V

CCQ

-0.5 ~ 3.6

V

Storage temperature

T

STG

-55 ~ +150

∞C

Operating temperature

T

A

0 ~ 70

∞C

Power Dissipation

P

D

8

W

Short circuit output current

I

OS

50

mA

NOTES:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC CHARACTERISTICS

0∞C

T

A

70∞C, V

CC

= 2.5V ± 0.2V

Parameter

Symbol

Min

Max

Unit

Note

Supply voltage DDR266/DDR333 (nominal V

CC

of 2.5V)

V

CC

2.3

2.7

I/O Supply voltage DDR266/DDR333 (nominal V

CC

of 2.5V)

V

CCQ

2.3

2.7

V

I/O Reference voltage

V

REF

0.49*V

CCQ

0.51*V

CCQ

V

1

I/O Termination voltage

V

TT

V

REF

-0.04

V

REF

+0.04

V

2

Input logic high voltage

V

IH

(DC)

V

REF

+0.15

V

CCQ

+0.30

V

Input logic low voltage

V

IL

(DC)

-0.3

V

REF

-0.15

V

Input voltage level, CK and CK#

V

IN

(DC)

-0.3

V

CCQ

+0.30

V

Input differential voltage, CK and CK#

V

ID

(DC)

0.3

V

CCQ

+0.60

V

3

Input crossing point voltage, CK and CK#

V

IX

(DC)

0.3

V

CCQ

+0.60

V

Input leakage current

Addr, CAS#,

RAS#, WE#

I

I

-40

40

uA

CS#, CKE

-20

20

uA

CK, CK#

-20

20

uA

DM

-10

10

uA

Output leakage current

I

OZ

-10

10

uA

Output high current (normal strengh); V

OUT

= V +0.84V

I

OH

-16.8

--

mA

Output high current (normal strengh); V

OUT

= V

TT

-0.84V

I

OL

16.8

--

mA

Output high current (half strengh); V

OUT

= V

TT

+0.45V

I

OH

-9

--

mA

Output high current (half strengh); V

OUT

= V

TT

-0.45V

I

OL

9

--

mA

Based on NANYA components.

NOTES:

1. V

REF

is expected to be equal to 0.5*V

CCQ

of the transmitting device, and to track variations in the DC level of the same. Peak to peak noise on V

REF

may not exceed ±2% of the DC

value

2. V

TT

is not applied directly to the device. V

TT

is a system supply for signal termination resistors,is expected to be set equal to V

REF

, and must track variations in the DC level of V

REF

3. V

ID

is the magnitude of the difference between the input level on CK and the input level on CK#.

CAPACITANCE

V

CC

= 2.5V, V

CCQ

=2.5V, T

A

= 25∞C, f = 1MHz

Parameter

Symbol

Min

Max

Unit

Input Capacitance (A0-A12, BA0-BA1, RAS#, CAS#, WE#)

C

IN1

21

29

pF

Input Capacitance (CKE0, CKE1)

C

IN2

13

17

pF

Input Capacitance (CS0#, CS1#)

C

IN3

13

17

pF

Input Capacitance (CK0,CK0#, CK1, CK1#)

C

IN4

13

17

pF

Input Capacitance (DM0-DM7)

C

IN5

13

15

pF

Data and DQS input/output capacitance (DQ0-DQ63), CB0-7

C

OUT

13

15

pF

Based on NANYA components.

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

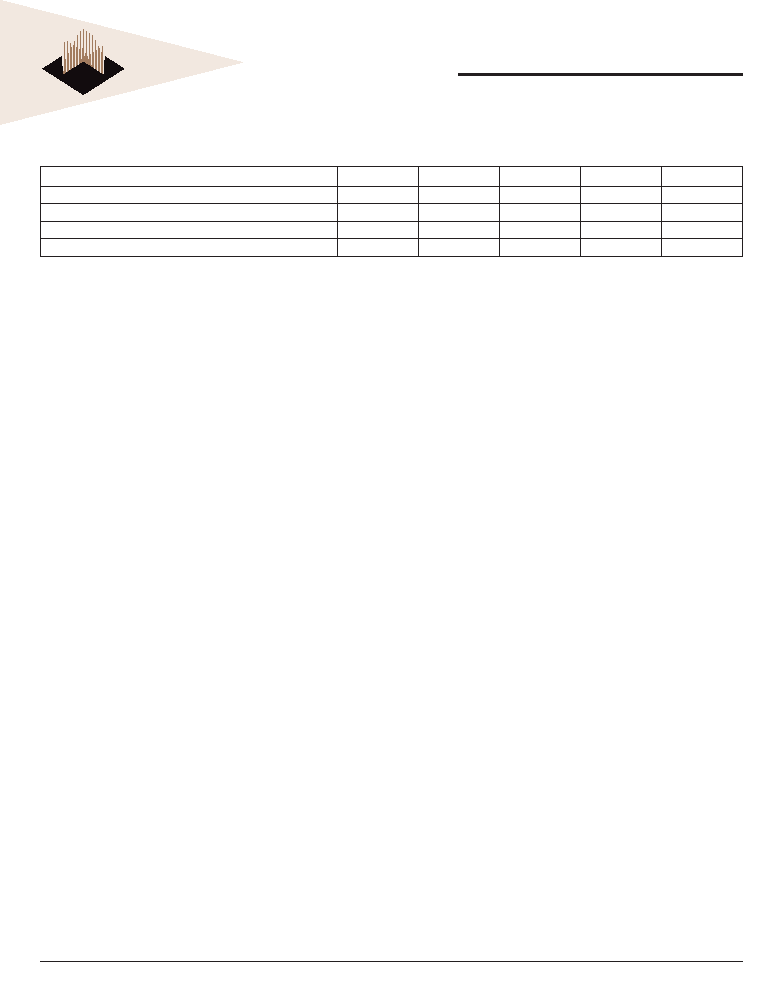

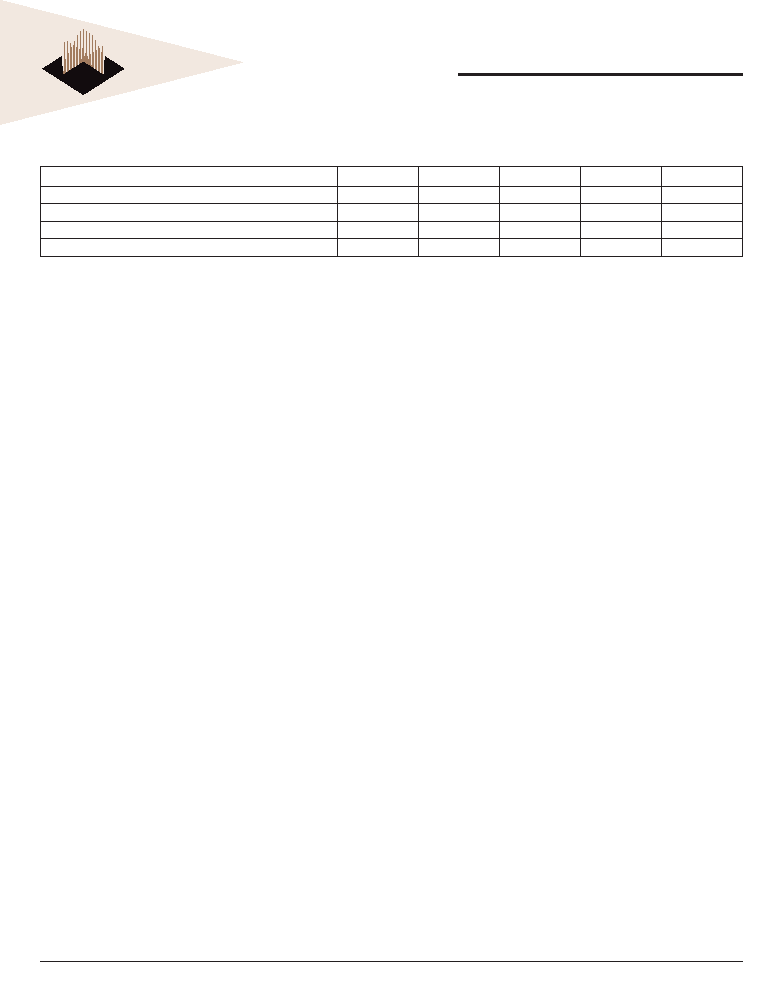

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Value

Units

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-0.5 ~ 3.6

V

Voltage on V

CC

and V

CCQ

supply relative to V

SS

V

CC,

V

CCQ

-0.5 ~ 3.6

V

Storage temperature

T

STG

-55 ~ +150

∞C

Operating temperature

T

A

0 ~ 70

∞C

Power Dissipation

P

D

8

W

Short circuit output current

I

OS

50

mA

NOTES:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC CHARACTERISTICS

-40∞C

T

A

85∞C

Parameter

Symbol

Min

Max

Unit

Note

Supply voltage DDR266/DDR333 (nominal V

CC

of 2.5V)

V

CC

2.3

2.7

I/O Supply voltage DDR266/DDR333 (nominal V

CC

of 2.5V)

V

CCQ

2.3

2.7

V

I/O Reference voltage

V

REF

0.49*V

CCQ

0.51*V

CCQ

V

1

I/O Termination voltage

V

TT

V

REF

-0.04

V

REF

+0.04

V

2

Input logic high voltage

V

IH

(DC)

V

REF

+0.15

V

CCQ

+0.30

V

Input logic low voltage

V

IL

(DC)

-0.3

V

REF

-0.15

V

Input voltage level, CK and CK#

V

IN

(DC)

-0.3

V

CCQ

+0.30

V

Input differential voltage, CK and CK#

V

ID

(DC)

0.3

V

CCQ

+0.60

V

3

Input crossing point voltage, CK and CK#

V

IX

(DC)

0.3

V

CCQ

+0.60

V

Input leakage current

Addr, CAS#,

RAS#, WE#

I

I

-16

16

uA

CS#, CKE

-8

8

uA

CK, CK#

-8

8

uA

DM

-4

4

uA

Output leakage current

I

OZ

-10

10

uA

Output high current (normal strengh); V

OUT

= V +0.84V

I

OH

-16.8

--

mA

Output high current (normal strengh); V

OUT

= V

TT

-0.84V

I

OL

16.8

--

mA

Output high current (half strengh); V

OUT

= V

TT

+0.45V

I

OH

-9

--

mA

Output high current (half strengh); V

OUT

= V

TT

-0.45V

I

OL

9

--

mA

Based on SAMSUNG components.

NOTES:

1. V

REF

is expected to be equal to 0.5*V

CCQ

of the transmitting device, and to track variations in the DC level of the same. Peak to peak noise on V

REF

may not exceed ±2% of the DC

value

2. V

TT

is not applied directly to the device. V

TT

is a system supply for signal termination resistors,is expected to be set equal to V

REF

, and must track variations in the DC level of V

REF

3. V

ID

is the magnitude of the difference between the input level on CK and the input level on CK#.

CAPACITANCE

T

A

= 25∞C, f = 100MHz

Parameter

Symbol

Min

Max

Unit

Input Capacitance (A0-A12, BA0-BA1, RAS#, CAS#, WE#)

C

IN1

20

28

pF

Input Capacitance (CKE0, CKE1)

C

IN2

12

16

pF

Input Capacitance (CS0#, CS1#)

C

IN3

12

16

pF

Input Capacitance (CK0, CK0#, CK1, CK1#)

C

IN4

12

16

pF

Input Capacitance (DM0-DM7), (DQS0-DQS7)

C

IN5

12

14

pF

Input Capacitance (DQ0-DQ63)

C

OUT1

12

14

pF

Based on SAMSUNG components.

6

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

AC OPERATING TEST CONDITIONS

-40∞C

T

A

85∞C

Parameter/Condition

Symbol

Min

Max

Unit

Note

Input High (Logic 1) Voltage

V

IH(AC)

V

REF

+0.31

V

1

Input Low (Logic 0) Voltage

V

IL(AC)

V

REF

-0.31

V

1

Input Differential Voltage, CK and CK# inputs

V

ID(AC)

0.7

V

CCQ

+0.6

V

Input Crossing Point Voltage, CK and CK# inputs

V

IX(AC)

0.5*V

CCQ

-0.2

0.5*V

CCQ

+0.2

V

Based on SAMSUNG components.

NOTES:

1.

V

IH

overshoot: V

IH

= V

CCQ

+1.5V for a pulse width < 3ns and the pulse can not be greater than 1/3 of the cycle rate.

V

IL

undershoot: V

IL

= -1.5V for a pulse width < 3ns and the pulse can not be greater than 1/3 of the cycle rate.

7

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

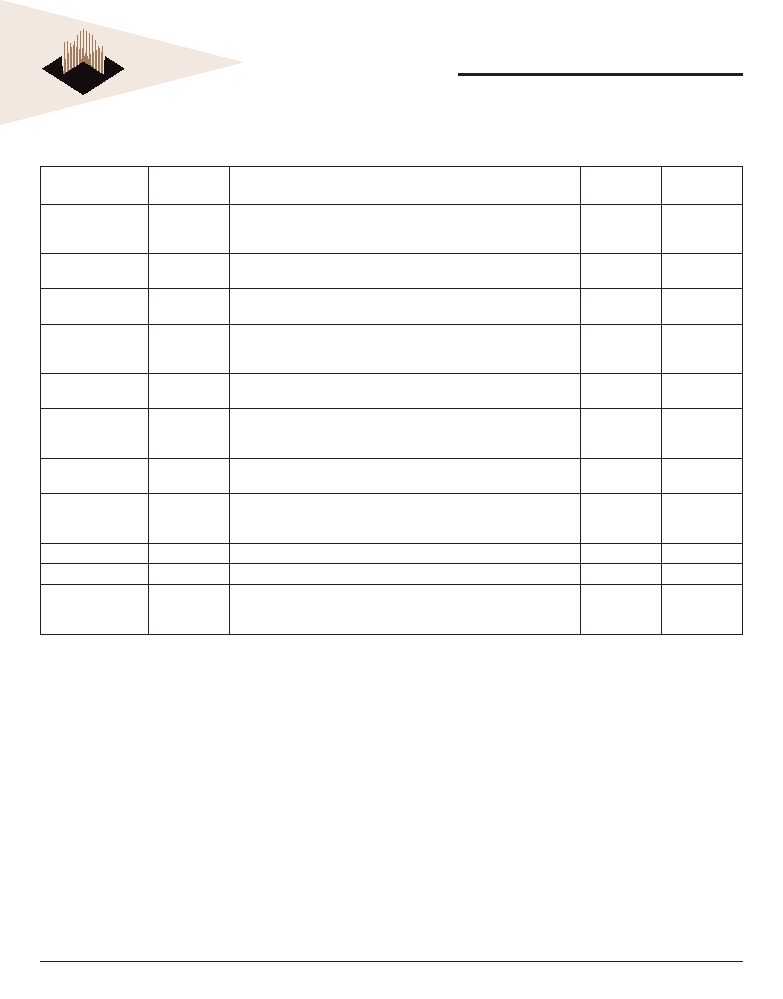

I

DD

SPECIFICATIONS AND TEST CONDITIONS

-40∞C T

A

85∞C, V

CC

= V

CCQ

= 2.5V ±0.2V

Parameter

Symbol

Conditions

DDR333 @

CL = 2.5 Max

Unit

Operating current:

I

DD0*

One device bank active; Active-Precharge; t

RC

= t

RC(MIN)

; t

CK

= t

CK(MIN)

; DQ,DM

and DQS inputs change once per clock cycle; Address and control inputs

change once every two clock cycles

840

mA

Operating current

I

DD1*

One device bank; Active-Read-Precharge; BL=4; t

RC

= t

RC(MIN)

; t

CK

= t

CK(MIN)

;

I

OUT

= 0mA; Address and control inputs change once per clock cycle

1120

mA

Percharge power-

down standby current

I

DD2P**

All device banks are idle; Power-down mode; t

CK

= t

CK(MIN)

; CKE=LOW

40

mA

Idle standby current

I

DD2F**

CS# = HIGH; All device banks are idle; t

CK

= t

CK(MIN)

; CKE=HIGH; Address

and other control inputs changing once per clock cycle. V

IN

= V

REF

for DQ,

DQS and DM

240

mA

Active power-down

standby current

I

DD3P**

One device bank active; Power-down mode; t

CK

= t

CK(MIN)

; CKE=LOW

240

mA

Active standby

current

I

DD3N**

CS# = HIGH; CKE=HIGH; One device bank active; t

RC

= t

RAS(MAX)

; t

CK

=

t

CK(MIN)

; DQ, DM and DQS inputs change twice per clock cycle; Address and

other control inputs changing once per clock cycle

360

mA

Operating current

I

DD4R*

Burst = 2; Reads; Continuos burst; One device bank active; Address and

other control inputs changing once per clock cycle; t

CK

= t

CK(MIN)

; I

OUT

= 0mA

1360

mA

Operating current

I

DD4W*

Burst = 2; Writes; Continuos burst; One device bank active; Address and

other control inputs changing once per clock cycle; t

CK

= t

CK(MIN)

; DQ, DM and

DQS inputs change twice per clock cycle

1480

mA

Auto refresh current

I

DD5**

t

RC

=t

RFC(MIN)

1640

mA

Self refresh current

I

DD6**

CKE < 0.2V

40

mA

Orerating current

I

DD7A*

Four device bank interleaving Reads Burst=4 with auto precharge; t

CK

=

t

CK(MIN)

; Address and control inputs change only during Active READ, or

WRITE commands

3040

mA

NOTE:

I

DD

specifi cation is based on SAMSUNG components. Other DRAM Manufacturers specifi cation may be different.

* Value calculated as one module rank in this operation condition and other module rank in I

DD2P

(CKE low) mode.

** Value calculated as all module ranks in this operation condition.

8

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

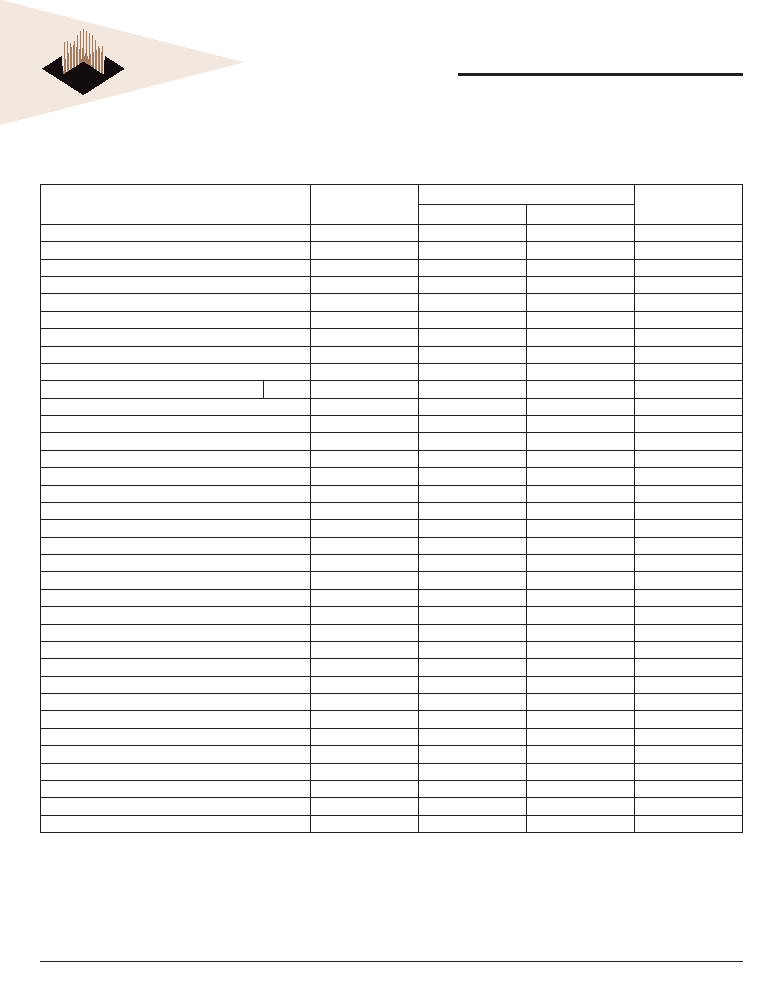

I

DD

SPECIFICATIONS AND TEST CONDITIONS

0∞C T

A

70∞C, V

CCQ

= 2.5V ±0.2V, V

CC

= 2.5V ±0.2V

Parameter

Symbol

Conditions

DDR333 @

CL = 2.5 Max

Unit

Operating current

- One bank Active-

Precharge

I

DD0*

t

RC

= t

RC

(min); t

CK

= 100Mhz for DDR200, 133Mhz for DDR266A & DDR266B;

DQ,DM and DQS inputs changing twice per clock cycle; address and control

inputs changing once per clock cycle

404

mA

Operating current

- One bank operation

I

DD1*

One bank open, BL=4, Reads - Refer to the following page for detailed test

condition

416

mA

Percharge power-

down standby current

I

DD2P**

All banks idle; power - down mode; CKE = <V

IL

(max); t

CK

= 100Mhz for

DDR200, 133Mhz for DDR266A & DDR266B; Vin = Vref for DQ,DQS and DM

40

mA

Precharge Floating

standby current

I

DD2F**

CS# > = V

IH

(min);All banks idle; CKE > = V

IH

(min); t

CK

= 100Mhz for DDR200,

133Mhz for DDR266A & DDR266B; Address and other control inputs

changing once per clock cycle; V

IN

= V

REF

for DQ,DQS and DM

200

mA

Active power - down

standby current

I

DD3P**

one bank active; power-down mode; CKE=< V

IL

(max); t

CK

= 100Mhz for

DDR200, 133Mhz for DDR266A & DDR266B; V

IN

= V

REF

for DQ, DQS and

DM

88

mA

Active standby

current

I

DD3N**

CS# > = V

IH

(min); CKE> = V

IH

(min); one bank active; active - precharge; t

RC

= t

RAS

max; t

CK

= 100Mhz for DDR200, 133Mhz for DDR266A & DDR266B;

DQ, DQS and DM inputs changing twice per clock cycle; address and other

control inputs changing once per clock cycle

360

mA

Operating current

- burst read

I

DD4R*

Burst length = 2; reads; continguous burst; One bank active; address and

control inputs changing once per clock cycle; CL = 2 at t

CK

= 100Mhz for

DDR200, CL = 2 at t

CK

= 133Mhz for DDR266A, CL = 2.5 at t

CK

= 133Mhz for

DDR266B ; 50% of data changing at every burst; lout = 0mA

436

mA

Operating current

- burst write

I

DD4W*

Burst length = 2; writes; continuous burst; One bank active address and

control inputs changing once per clock cycle; CL = 2 at t

CK

= 100Mhz for

DDR200, CL = 2 at t

CK

= 133Mhz for DDR266A, CL = 2.5 at t

CK

= 133Mhz for

DDR266B ; DQ, DM and DQS inputs changing twice per clock cycle, 50% of

input data changing at every burst

488

mA

Auto refresh current

I

DD5**

t

RC

= t

RFC

(min) - 8*t

CK

for DDR200 at 100Mhz, 10*t

CK

for DDR266A &

DDR266B at 133Mhz; distributed refresh

1544

mA

Self refresh current;

CKE =< 0.2V

I

DD6**

External clock should be on; t

CK

= 100Mhz for DDR200, 133Mhz for

DDR266A & DDR266B

40

mA

Orerating current

- Four bank operation

I

DD7A*

Four bank interleaving with BL=4 -Refer to the following page for detailed test

condition

1248

mA

NOTE:

I

DD

specifi cation is based on NANYA components. Other DRAM Manufacturers specifi cation may be different.

* Value calculated as one module rank in this operation condition and other module rank in I

DD2P

(CKE low) mode.

** Value calculated as all module ranks in this operation condition.

9

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

DDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND

RECOMMENDED AC OPERATING CONDITIONS

0∞C T

A

70∞C, V

CCQ

= 2.5V ±0.2V, V

CC

= 2.5V ±0.2V

Parameter

Symbol

335

Unit

Min

Max

Row Cycle Time

t

RC

60

ns

Refresh row cycle time

t

RFC

72

ns

Row active

t

RAS

42

120K

ns

RAS# to CAS# delay

t

RCD

18

ns

Row precharge time

t

RP

18

ns

Row active to row active delay

t

RRD

12

ns

Write recovery time

t

WR

15

ns

Last data into Read command

t

WTR

1

t

CK

Clock cycle time

CL=2.5

t

CK

6

12

ns

Clock high level width

t

CH

0.45

0.55

t

CK

Clock low level width

t

CL

0.55

0.55

t

CK

DQS-out access time from CK/CK#

t

DQSCK

-0.6

+0.6

ns

Output data access time from CK/CK#

t

AC

-0.7

+0.7

ns

Data strobe edge to output data edge

t

DQSQ

-

0.45

ns

Read Preamble

t

RPRE

0.9

1.1

t

CK

Read Postamble

t

RPST

0.4

0.6

t

CK

CK to valid DQS-in

t

DQSS

0.75

1.25

t

CK

DQS-in setup time

t

WPRES

0

ns

DQS-in hold time

t

WPRE

0.25

t

CK

DQS falling edge to CK rising-setup time

t

DSS

0.2

t

CK

DQS falling edge to CK rising-hold time

t

DSH

0.2

t

CK

DQS-in high level width

t

DQSH

0.35

t

CK

DQS-in low level width

t

DQSL

0.35

t

CK

Address and control input setup time (fast)

t

IS

0.75

ns

Address and control input hold time (fast)

t

IH

0.75

ns

Address and control input setup (slow)

t

IS

0.7

ns

Address and control input hold time (slow)

t

IH

0.7

ns

Data-out high impedence time from CK/CK#

t

HZ

-0.7

+0.7

ns

Data-out low impedence time from CK/CK#

t

LZ

-0.7

+0.7

ns

Mode register set cycle time

t

MRD

10

ns

DQ & DM setup time to DQS

t

DS

0.4

ns

DQ & DM hold time to DQS

t

DH

0.4

ns

Control & address input pulse width

t

IPW

2.2

ns

DQ & DM input pulse width

t

DIPW

1.75

ns

Exit self refresh to non-Read command

t

XSNR

75

ns

Exit self refresh to Read command

t

XSRD

200

t

CK

Refresh interval time

t

REFI

7.8

us

Output DQS valid window

t

QH

t

HP

- t

QHS

--

ns

Clock half period

t

HP

t

CL

min or t

CH

min

--

ns

Data hold skew factor

t

QHS

0.55

ns

DQS write postamble

t

WPST

0.4

0.6

ns

Active Read with auto precharge command

t

RAP

18

ns

Auto precharge write recovery + Precharge time

t

RAL

(t

WR

/t

CK

) + (t

RP

/t

CK

)

t

CK

NOTE:

AC Timing Parameters are based on SAMSUNG components. Other DRAM Manufacturers parameters may be different.

10

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

DDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND

RECOMMENDED AC OPERATING CONDITIONS

0∞C T

A

70∞C, V

CCQ

= 2.5V ±0.2V, V

CC

= 2.5V ±0.2V

Parameter

Symbol

335

Unit

Min

Max

Row cycle time

t

RC

60

ns

Refresh row cycle time

t

RFC

72

ns

Row active time

t

RAS

42

70K

ns

RAS# to CAS# delay

t

RCD

18

ns

Row precharge time

t

RP

18

ns

Row active to Row active delay

t

RRD

12

ns

Write recovery time

t

WR

15

ns

Last data into Read command

t

WTR

1

t

CK

Col. address to Col. address delay

t

CCD

1

t

CK

Clock cycle time

CL=2.5

t

CK

6

12

ns

Clock high level width

t

CH

0.45

0.55

t

CK

Clock low level width

t

CL

0.45

0.55

t

CK

DQS-out access time from CK/CK#

t

DQSCK

-0.6

+0.6

ns

Output data access time from CK/CK#

t

AC

-0.7

+0.7

ns

Data strobe edge to output data edge

t

DQSQ

-

0.4

ns

Read Preamble

t

RPRE

0.9

1.1

t

CK

Read Postamble

t

RPST

0.4

0.6

t

CK

CK to valid DQS-in

t

DQSS

0.75

1.25

t

CK

DQS-in setup time

t

WPRES

0

ns

DQS-in hold time

t

WPRE

0.25

t

CK

DQS falling edge to CK rising-setup time

t

DSS

0.2

t

CK

DQS falling edge from CK rising-hold time

t

DSH

0.2

t

CK

DQS-in high level width

t

DQSH

0.35

t

CK

DQS-in low level width

t

DQSL

0.35

t

CK

DQS-in cycle time

t

DSC

0.9

1.1

t

CK

Address and Control Input setup time (fast)

t

IS

0.75

ns

Address and Control Input hold time (fast)

t

IH

0.75

ns

Address and Control Input setup time (slow)

t

IS

0.8

ns

Address and Control Input hold time (slow)

t

IH

0.8

ns

Data-out high impedence time from CK/CK#

t

HZ

-0.7

+0.7

ns

Data-out low impedence time from CK/CK#

t

LZ

-0.7

+0.7

ns

Input Slew Rate (for input only pins)

t

SL(I)

0.5

V/ns

Input Slew Rate (for I/O pins)

t

SL(IO)

0.5

V/ns

Output Slew Rate (x4, x8)

t

SL(O)

1.0

4.5

V/ns

Output Slew Rate Matching Ratio (rise to fall)

t

SLMR

0.67

1.5

Note:

AC Timing Parameters are based on NANYA components. Other DRAM Manufacturers parameters may be different.

11

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

DDR SDRAM COMPONENT ELECTRICAL CHARACTERISTICS AND

RECOMMENDED AC OPERATING CONDITIONS (Continued)

0∞C T

A

70∞C, V

CCQ

= 2.5V ±0.2V, V

CC

= 2.5V ±0.2V

Parameter

Symbol

335

Unit

Min

Max

Mode register set cycle time

tMRD

12

ns

DQ & DM setup time to DQS

tDS

0.45

ns

DQ & DM hold time to DQS

tDH

0.45

ns

Control & Address input pulse width

tIPW

2.2

ns

DQ & DM input pulse width

tDIPW

1.75

ns

Power down exit time

tPDEX

6

ns

Exit self refresh o non-Read command

tXSNR

75

ns

Exit self refresh to read command

tXSRD

200

t

CK

Refresh interval time

tREFI

7.8

us

Output DQS valid window

tQH

t

HP

- t

QHS

--

ns

Clock half period

tHP

t

CL

min or t

CH

min

--

ns

Data hold skew factor

tQHS

0.5

ns

DQS write postamble time

tWPST

0.4

0.6

t

CK

Active to Read with Auto precharge command

tRAP

18

Auto precharge write recovery + Precharge time

tDAL

(t

WR

/t

CK

) + (t

RP

/t

CK

)

t

CK

12

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

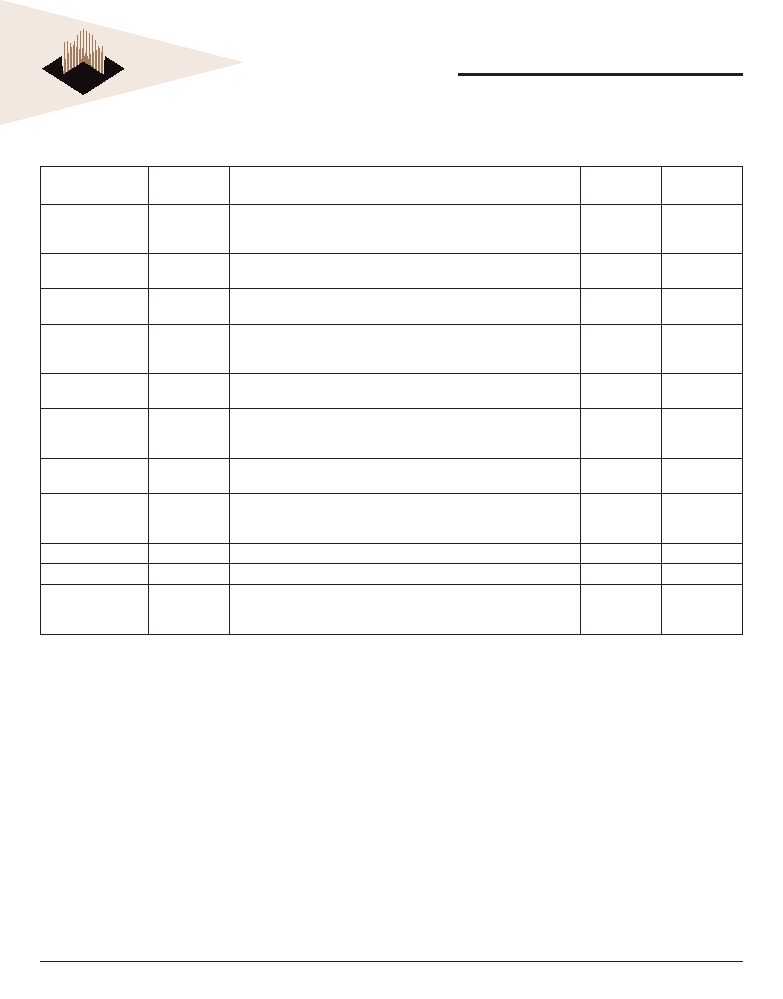

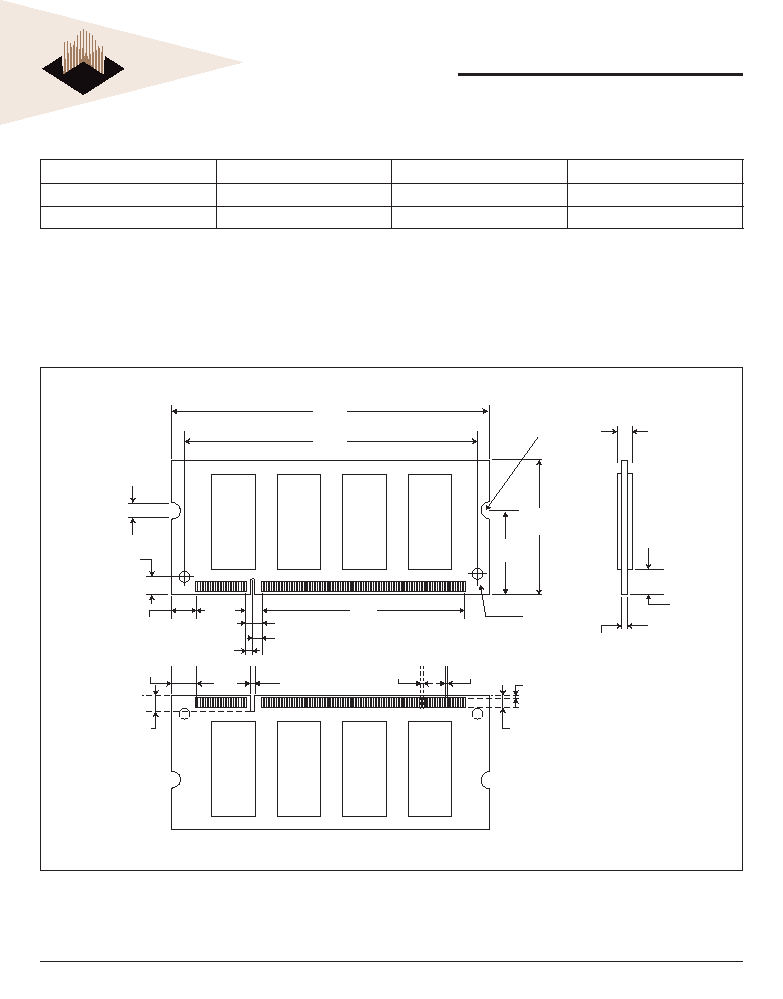

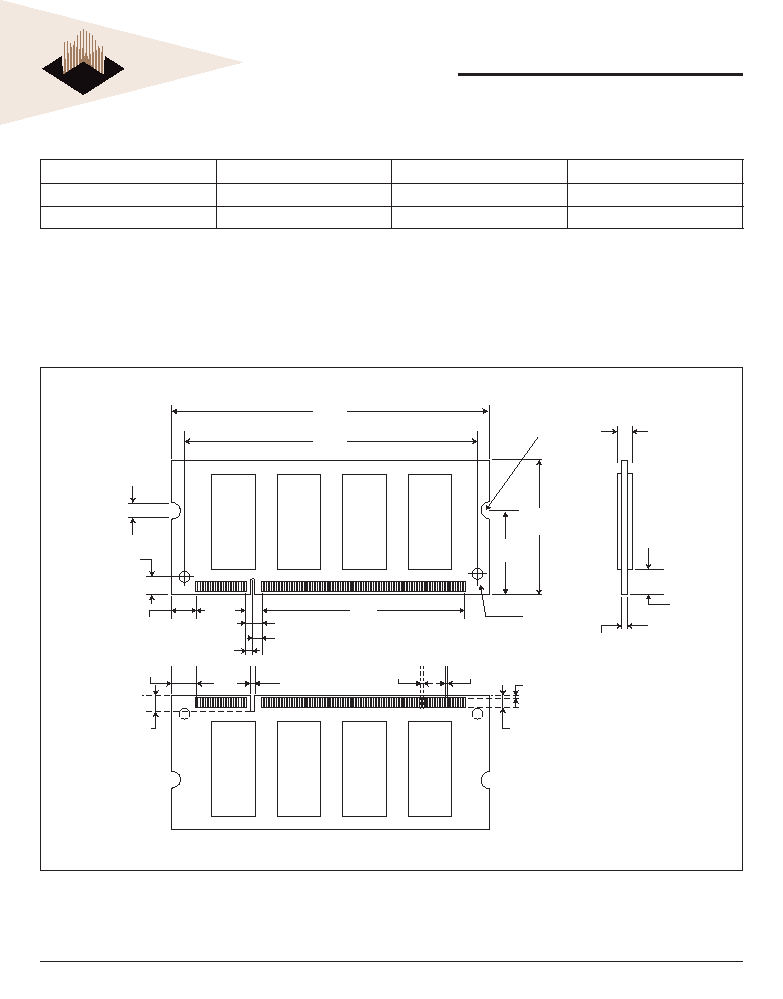

67.60

(2.661)

63.60

(2.504)

1.0 ± 0.1

(0.04 ± 0.0039)

3.80

(0.150) MAX.

2.15

(0.085)

6.0

0.236

4.20 (0.165)

1.8

(0.071)

4.00

(0.158) MIN.

47.40

(1.866)

2- 1.80

(0.071)

11.40

(0.449)

1

39

41

199

31.75

(1.25)

Full R 2x

2.40 (0.094)

4.00 ±0.10

(0.158 ±0.039)

20

(0.787)

2.45

(0.098)

4.00 ±0.10

(0.158 ±0.039)

1.00 ±0.1

(0.04 ±0.0039)

0.45 ±0.03

(0.018 ±0.001)

0.60

(0.024)

2.55 Min

(0.102 Min)

0.25

(0.01)

ORDERING INFORMATION FOR D4

Part Number

Speed

Height*

Commercial Operating Range

WV3EG232M64STSU335D4xG

166MHz/333Mbps, CL=2.5

31.75mm (1.25") MAX

0∞C to 70∞C

WV3EG232M64STSU335D4IxG

166MHz/333Mbps, CL=2.5

31.75mm (1.25") MAX

-40∞C to 85∞C

NOTES:

∑ Consult Factory for availability of RoHS compliant products. (G = RoHS Compliant)

∑ Vendor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case "x" in the part numbers above and is to

be replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron, S = Samsung, N = Nanya and consult factory for others)

∑ Consult factory for availability of industrial temperature (-40∞C to 85∞C) option (add "I" for industrial temperature option).

* ALL DIMENSIONS ARE IN MILLIMETERS AND (INCHES)

PACKAGE DIMENSIONS FOR D4

Tolerances: ±0.15 (0.006) unless otherwise specifi ed

13

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

PART NUMBERING GUIDE

WV 3 E G 232M 64 S T S U xxx D4 I x G

WEDC

MEMORY (SDRAM)

DDR

GOLD

DEPTH (Dual Rank)

BUS WIDTH

COMPONENT WIDTH (x16)

TSOP

2.5V

UNBUFFERED

SPEED (MHz)

PACKAGE 200 PIN

INDUSTRIAL TEMPERATURE

(-40∞C to +85∞C)

(Blank = Commerical Temperature)

COMPONENT VENDOR

NAME

(M = Micron)

(S = Samsung)

(N = Nanya)

G = RoHS COMPLIANT

14

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

WV3EG232M64STSU-D4

September 2005

Rev. 1

PRELIMINARY

White Electronic Designs Corp. reserves the right to change products or specifi cations without notice.

Document Title

512MB ≠ 2x32Mx64, DDR SDRAM UNBUFFERED

Revision History

Rev #

History

Release Date

Status

Rev 0

Created

8-05

Preliminary

Rev 1

1.0 Added Samsung's I

DD

, CAP and AC Specifi cations

9-05

Preliminary