WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED*

1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

1GB ≠ 128Mx72 DDR2 SDRAM REGISTERED, w/PLL, Mini-DIMM

DESCRIPTION

The WV3HG128M72EER is a 128Mx72 Double Data

Rate DDR2 SDRAM high density module. This memory

module consists of nine 128Mx8 bit with 4 banks DDR2

Synchronous DRAMs in FBGA packages, mounted on a

244-pin DIMM FR4 substrate.

* This product is under development, is not qualifi ed or characterized and is subject to

change without notice.

NOTE: Consult factory for availability of:

∑ Vendor source control options

∑ Industrial temperature option

FEATURES

244-pin, dual in-line memory module (Mini-DIMM)

Fast data transfer rates: PC2-6400*, PCS-5300*,

PC2-4200 and PC2-3200

Utilizes 800*, 667*, 533 and 400 Mb/s DDR2

SDRAM components

V

CC

= V

CCQ

= 1.8V ±0.1V

V

CCSPD

= 1.7V to 3.6V

Differential data strobe (DQS, DQS#) option

Four-bit

prefetch

architecture

Programmable CAS# latency (CL): 3, 4, 5* and 6*

On-die

termination

(ODT)

Serial Presence Detect (SPD) with EEPROM

JEDEC Standard 1.8V I/O (SSTL_18 Compatible)

Gold (Au) edge contacts

Sinlge

Rank

RoHS

compliant

Package

option

∑ 244 Pin Mini-DIMM

∑ PCB ≠ 30.00mm (1.181") TYP

OPERATING FREQUENCIES

PC2-3200

PC2-4200

PC2-5300*

PC2-6400*

Clock Speed

200MHz

266MHz

333MHz

400MHz

CL-t

RCD

-t

RP

3-3-3

4-4-4

5-5-5

6-6-6

*Consult factory for availability.

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

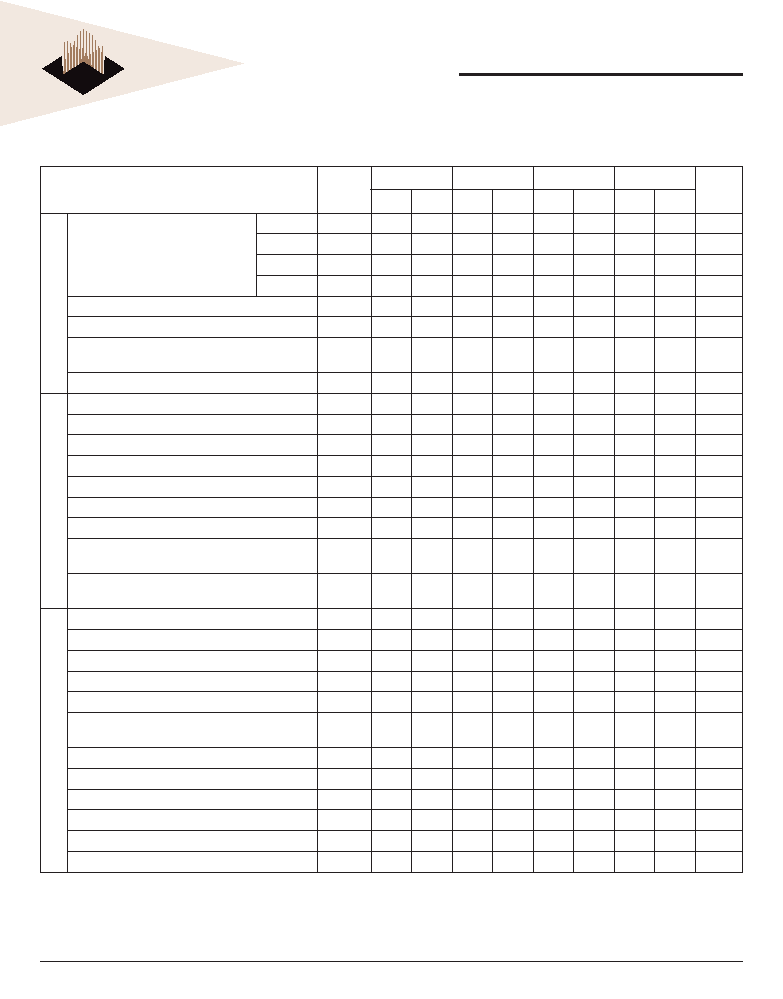

PIN NAMES

Pin Name

Function

A0-A13

Address Inputs

BA0-BA2

SDRAM Bank Address

DQ0-DQ63

Data Input/Output

CB0-CB7

Check Bits

DQS0-DQS8

Data strobes

DQS0#-DQS8#

Data strobes complement

ODT0

On-die termination control

CK0,CK0#

Clock Inputs, positive line

CKE0

Clock Enables

CS0#

Chip Selects

RAS#

Row Address Strobe

CAS#

Column Address Strobe

WE#

Write Enable

RESET#

Register Reset Input

DM (0-8)

Data Masks

V

CCSPD

SPD Power

V

CC

Voltage Supply (1.8V±0.1V)

V

SS

Ground

SA0-SA2

SPD address

SDA

SPD Data Input/Output

SCL

Serial Presence Detect(SPD) Clock Input

V

REF

Input/Output Reference

NC

Spare pins, No connect

PIN CONFIGURATION

Pin No.

Symbol

Pin No.

Symbol

Pin No.

Symbol

Pin No.

Symbol

1

V

REF

62

A4

123

V

SS

184

V

CC

2

V

SS

63

V

CC

124

DQ4

185

A3

3

DQ0

64

A2

125

DQ5

186

A1

4

DQ1

65

V

CC

126

V

SS

187

V

CC

5

V

SS

66

V

SS

127

DM0

188

CK0

6

DQS0#

67

V

SS

128

NC

189

CK0#

7

DQS0

68

NC

129

V

SS

190

V

CC

8

V

SS

69

V

CC

130

DQ6

191

A0

9

DQ2

70

A10/AP

131

DQ7

192

BA1

10

DQ3

71

BA0

132

V

SS

193

V

CC

11

V

SS

72

V

CC

133

DQ12

194

RAS#

12

DQ8

73

WE#

134

DQ13

195

V

CC

13

DQ9

74

V

CC

135

V

SS

196

CS0#

14

V

SS

75

CAS#

136

DM1

197

V

CC

15

DQS1#

76

V

CC

137

NC

198

ODT0

16

DQS1

77

NC

138

V

SS

199

A13

17

V

SS

78

NC

139

NC

200

V

CC

18

RESET#

79

V

CC

140

NC

201

NC

19

NC

80

NC

141

V

SS

202

V

SS

20

V

SS

81

V

SS

142

DQ14

203

DQ36

21

DQ10

82

DQ32

143

DQ15

204

DQ37

22

DQ11

83

DQ33

144

V

SS

205

V

SS

23

V

SS

84

V

SS

145

DQ20

206

DM4

24

DQ16

85

DQS4#

146

DQ21

207

NC

25

DQ17

86

DQS4

147

V

SS

208

V

SS

26

V

SS

87

V

SS

148

DM2

209

DQ38

27

DQS2#

88

DQ34

149

NC

210

DQ39

28

DQS2

89

DQ35

150

V

SS

211

V

SS

29

V

SS

90

V

SS

151

DQ22

212

DQ44

30

DQ18

91

DQ40

152

DQ23

213

DQ45

31

DQ19

92

DQ41

153

V

SS

214

V

SS

32

V

SS

93

V

SS

154

DQ28

215

DM5

33

DQ24

94

DQS5#

155

DQ29

216

NC

34

DQ25

95

DQS5

156

V

SS

217

V

SS

35

V

SS

96

V

SS

157

DM3

218

DQ46

36

DQS3#

97

DQ42

158

NC

219

DQ47

37

DQS3

98

DQ43

159

V

SS

220

V

SS

38

V

SS

99

V

SS

160

DQ30

221

DQ52

39

DQ26

100

DQ48

161

DQ31

222

DQ53

40

DQ27

101

DQ49

162

V

SS

223

V

SS

41

V

SS

102

V

SS

163

CB4

224

NC

42

CB0

103

SA2

164

CB5

225

NC

43

CB1

104

NC

165

V

SS

226

V

SS

44

V

SS

105

V

SS

166

DM8

227

DM6

45

DQS8#

106

DQS6#

167

NC

228

NC

46

DQS8

107

DQS6

168

V

SS

229

V

SS

47

V

SS

108

V

SS

169

CB6

230

DQ54

48

CB2

109

DQ50

170

CB7

231

DQ55

49

CB3

110

DQ51

171

V

SS

232

V

SS

50

V

SS

111

V

SS

172

NC

233

DQ60

51

NC

112

DQ56

173

V

CC

234

DQ61

52

V

CC

113

DQ57

174

NC

235

V

SS

53

CKE0

114

V

SS

175

V

CC

236

DM7

54

V

CC

115

DQS7#

176

NC

237

NC

55

BA2

116

DQS7

177

NC

238

V

SS

56

NC

117

V

SS

178

V

CC

239

DQ62

57

V

CC

118

DQ58

179

A12

240

DQ63

58

A11

119

DQ59

180

A9

241

V

SS

59

A7

120

V

SS

181

V

CC

242

SDA

60

V

CC

121

SA0

182

A8

243

SCL

61

A5

122

SA1

183

A6

244

V

CCSPD

RESET (pin 18) is connected to both OE of the PLL and Reset# of the register .

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

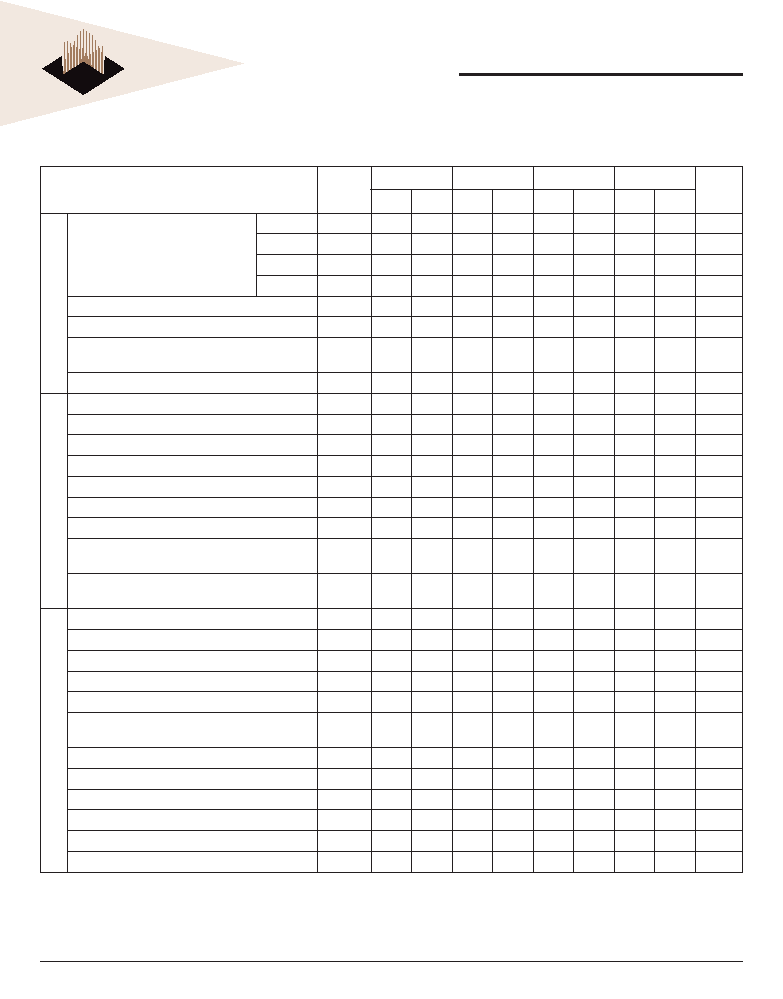

FUNCTIONAL BLOCK DIAGRAM

A0

Serial PD

A1

A2

SA0 SA1 SA2

SDA

SCL

WP

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/ CS# DQS DQS#

RDQS

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

RCS0#

DQS0

DQS0#

DM0

DQS4

DQS4#

DM4

DQS1

DQS1#

DM1

DQS5

DQS5#

DM5

DQS2

DQS2#

DM2

DQS6

DQS6#

DM6

DQS3

DQS3#

DM3

DQS7

DQS7#

DM7

DQS8

DQS8#

DM8

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

P

L

L

V

REF

V

SS

DDR2 SDRAMs

DDR2 SDRAMs

V

CC\

V

CCSPD

Serial PD

V

CCQ

DDR2 SDRAMs

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

DM/ CS# DQS DQS#

RDQS

R

E

G

I

S

T

E

R

CS0#

BA0-BA2

A0-A13

RAS#

CAS#

WE#

CKE0

ODT0

RESET#

RST#

PCK7**

PCK7#**

RCS0# CS#: SDRAMs

CK0

CK0#

RESET#**

PCK7# CK#: Register

PCK0# , PCK4#-PCK6#, PCK9# CK#: SDRAMs

PCK0, PCK4-PCK6, PCK9 CK: SDRAMs

RBA0-RBA2 BA0-BA2: SDRAMs

RA0-RA13 A0-A13: SDRAMs

RRAS# RAS# SDRAMs

RCAS# CAS# SDRAMs

RWE# WE# SDRAMs

RCKE0 CKE SDRAMs

RODT0 ODT SDRAMs

PCK7 CK#: Register

** RESET#, CK AND CK# connects to both Registers. Other signals connct to one of two Registers.

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NOTE: All resistor values are 22 ohms ±5% unless otherwise specifi ed.

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Min

Max

Units

V

CC

Voltage on V

CC

pin relative to V

SS

-0.5

2.3

V

V

IN

, V

OUT

Voltage on any pin relative to V

SS

-0.5

2.3

V

T

STG

Storage Temperature

-55

100

∞C

I

L

Input leakage current; Any input 0V<V

IN

<V

CC

; V

REF

input

0V,V

IN

,0.95V; Other pins not under test = 0V

Command/Address,

RAS#, CAS#, WE#,

-5

5

µA

CK, CK#

-10

10

µA

DM

-5

5

µA

I

OZ

Output leakage current; 0V<V

IN

<V

CC

; DQs and ODT are disable

DQ, DQS, DQS#

-5

5

µA

I

VREF

V

REF

leakage current; V

REF

= Valid V

REF

level

-18

18

µA

DC OPERATING CONDITIONS

All voltages referenced to V

SS

Parameter

Symbol

Min

Typical

Max

Unit

Notes

Supply Voltage

V

CC

1.7

1.8

1.9

V

3

I/O Reference Voltage

V

REF

0.49 x V

CC

0.50 x V

CC

0.51 x V

CC

V

1

I/O Termination Voltage

V

TT

V

REF

-0.04

V

REF

V

REF

+0.04

V

2

SPD Supply Voltage

V

CCSPD

1.7

-

3.6

V

Notes:

1

V

REF

is expected to equal V

CC/2

of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise on

V

REF

may not exceed +/-1 percent of the

DC value. Peak-to-peak AC noise on V

REF

may not exceed +/-2 percent of V

REF

. This measurement is to be taken at the nearest V

REF

bypass capacitor.

2. V

TT

is not applied directly to the device. V

TT

is a system supply for signal termination resistors, is expected to be set equal to V

REF

and must track variations in the DC level of V

REF

.

3. V

CCQ

of all IC's are tied to V

CC

.

INPUT/OUTPUT CAPACITANCE

TA=25 0 C, f=1 00MHz

Parameter

Symbol

Min

Max

Unit

Input capacitance (A0 - A13, BA0 - BA1 ,RAS#,CAS#,WE#)

C

IN1

11

12

pF

Input capacitance ( CKE0), (ODT0)

C

IN2

11

12

pF

Input capacitance (CS0#)

C

IN3

11

12

pF

Input capacitance (CK0, CK0#)

C

IN4

10

11

pF

Input capacitance (DM0 - DM8), (DQS0 - DQS8)

C

IN5 (665)

6.5

8

pF

C

IN5 (534,403)

6.5

7.5

pF

Input capacitance (DQ0 - DQ63), (CB0 - CB7)

C

OUT1 (665)

6.5

8

pF

C

OUT1 (534,403)

6.5

7.5

pF

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

OPERATING TEMPERATURE CONDITION

Parameter

Symbol

Rating

Units

Notes

Operating temperature (Commercial)

T

OPER

0∞C to 85∞C

∞C

1, 2

Notes:

1. Operating temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JEDEC JESD51 .2

2. At 0 - 85∞C, operation temperature range, all DRAM specifi cation will be supported.

INPUT DC LOGIC LEVEL

All voltages referenced to V

SS

Parameter

Symbol

Min

Max

Unit

Input High (Logic 1 ) Voltage

V

IH

(DC)

V

REF

+ 0.125

V

REF

+ 0.300

V

Input Low (Logic 0) Voltage

V

IL

(DC)

-0.300

V

REF

- 0.125

V

INPUT AC LOGIC LEVEL

All voltages referenced to V

SS

Parameter

Symbol

Min

Max

Unit

AC Input High (Logic 1 ) Voltage DDR2-400 & DDR2-533

V

IH

(AC)

V

REF

+ 0.250

--

V

AC Input High (Logic 1 ) Voltage DDR2-667

V

IH

(AC)

V

REF

+ 0.200

--

V

AC Input Low (Logic 0) Voltage DDR2-400 & DDR2-533

V

IL

(AC)

--

V

REF

- 0.250

V

AC Input Low (Logic 1 ) Voltage DDR2-667, DDR2-800(TBD)

V

IL

(AC)

--

V

REF

- 0.200

V

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

6

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

DDR2 I

CC

SPECIFICATIONS AND CONDITIONS

V

CC

= +1.8V ± 0.1V

Symbol

Parameter

Condition

806

665

534

403

Unit

I

CC0*

Operating

one bank

active-

precharge;

t

CK

= t

CK(ICC)

; t

RC

= t

RC(ICC)

; t

RAS

= t

RAS MIN(ICC)

; CKE is HIGH, CS# is HIGH between valid

commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

1,210

1,165

1,120

mA

I

CC1*

Operating

one bank

active-

read-

precharge;

I

OUT

= 0mA; BL = 4; CL = CL(I

CC

); t

CK

= t

CK(ICC)

; t

RC

= t

RC(ICC)

; t

RAS

= t

RAS MIN(ICC)

; CKE is

HIGH, CS# is HIGH between valid commands; Address bus inputs are SWITCHING;

Data bus inputs are SWITCHING; Data pattern is same as I

CC4W

.

TBD

1,300

1,255

1,210

mA

I

CC2P**

Precharge

power-

down

current;

All banks idle; t

CK

= t

CK(ICC)

; CKE is LOW; Other control and address bus inputs are

STABLE; Data bus inputs are FLOATING

TBD

508

508

508

mA

I

CC2Q**

Precharge

quite

standby

current;

All banks idle; t

CK

= t

CK(ICC)

; CKE is HIGH; CS# is HIGH; Other control and address bus

inputs are STABLE; Data bus inputs are FLOATING

TBD

760

715

715

mA

I

CC2N**

Precharge

standby

current;

All banks idle; t

CK

= t

CK(ICC)

; CKE is HIGH; CS# is HIGH; Other control and address bus

inputs are STABLE; Data bus inputs are SWITCHING

TBD

805

760

760

mA

I

CC3P**

Active

power-

down

current;

All banks open; t

CK

= t

CK(ICC)

, CKE is LOW; Other control

and address bus inputs are STABLE; Data bus inputs are

FLOATING

Fast PDN Exit

MRS(12) = 0

TBD

670

625

625

mA

Slow PDN Exit

MRS(12) = 1

TBD

508

508

508

mA

I

CC3N**

Active

standby

current;

All banks open; t

CK

= t

CK(ICC)

; t

RC

= t

RC(ICC)

; t

RAS

= t

RAS MIN(ICC)

; CKE is HIGH, CS#

is HIGH between valid commands; Other control and address bus inputs are

SWITCHING; Data bus inputs are SWITCHING

TBD

850

805

805

mA

I

CC4W*

Operating

burst write

current;

All banks open; Continuous burst writes; BL = 4; CL = CL(I

CC

); AL = 0; t

CK

= t

CK(ICC)

;

t

RC

= t

RC(ICC)

; t

RAS

= t

RAS MIN(ICC)

; CKE is HIGH, CS# is HIGH between valid commands;

Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

1,795

1,570

1,435

mA

I

CC4R*

Operating

burst read

current;

All banks open; Continuous burst reads; TOUT = 0mA; BL = 4; CL = CL(I

CC

); AL = 0;

t

CK

= t

CK(ICC)

; t

RC

= t

RC(ICC)

; t

RAS

= t

RAS MIN(ICC)

; CKE is HIGH, CS# is HIGH between

valid commands; Address bus inputs are SWITCHING; Data pattern is same as I

CC4W

.

TBD

1,795

1,570

1,435

mA

I

CC5**

Burst auto

refresh

current;

t

CK

= t

CK(ICC)

; Refresh command at every t

RC(ICC)

interval; CKE is HIGH; CS# is HIGH

between valid commands; Other control and address bus inputs are SWITCHING;

Data bus inputs are SWITCHING

TBD

2,380

2,335

2,290

mA

I

CC6**

Self

refresh

current;

CK and CK# at 0V; CKE < 0.2V; Other control and address bus

inputs are FLOATING; Data bus inputs are FLOATING

Normal

TBD

90

90

90

mA

I

CC7*

Operating

bank

interleave

read

current;

All bank interleaving reads; I

OUT

= 0mA; BL = 4; CL = CL(I

CC

); AL = t

RCD(ICC)

- 1*t

CK(ICC)

;

t

CK

= t

CK(ICC)

; t

RC

= t

RC(ICC)

; t

RRD

= t

RRD MIN(ICC)

= 1*t

CK(ICC)

; CKE is HIGH; CS# is HIGH

between valid commands; Address bus inputs are STABLE during DESELECTs; Data

bus inputs are SWITCHING

TBD

3,100

2,920

2,740

mA

Notes:

I

CC

specifi cation is based on SAMSUNG components. Other DRAM manufacturers specifi cation may be different.

* Value calculated as one module rank in this operating condition, and all other module ranks in I

CC2P

( CKE LOW) mode.

** Value calculated refl ects all module ranks in this operating condition.

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

7

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

AC TIMING PARAMETERS

V

CC

= +1.8V ± 0.1V

Parameter

Symbol

806

665

534

403

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Clock

Clock cycle time

CL=6

t

CK

(6)

TBD

TBD

CL=5

t

CK

(5)

TBD

TBD

3000

8000

-

-

-

-

ps

CL=4

t

CK

(4)

TBD

TBD

3750

8000

3,750

8,000

5,000

8,000

ps

CL=3

t

CK

(3)

TBD

TBD

5000

8000

5,000

8,000

5,000

8,000

ps

CK high-level width

t

CH

TBD

TBD

0.45 0.55

0.45

0.55

0.45

0.55

t

CK

CK low-level width

t

CL

TBD

TBD

0.45

0.55

0.45

0.55

0.45

0.55

t

CK

Half clock period

t

HP

TBD

TBD

MIN(t

CH

,

t

CL)

MIN (t

CH

,

t

CL

)

MIN (t

CH

,

t

CL

)

ps

Clock jitter

t

JIT

TBD

TBD

-125

125

-125

125

-125

125

ps

Data

DQ output access time from CK/CK#

t

AC

TBD

TBD

-450

+450

-500

+500

-600

+600

ps

Data-out high impedance window from CK/CK#

t

HZ

TBD

TBD

t

AC(MAX)

t

AC(MAX)

t

AC(MAX)

ps

Data-out low-impedance window from CK/CK#

t

LZ

TBD

TBD

t

AC(MIN)

t

AC(MAX)

t

AC(MIN)

t

AC(MAX)

t

AC(MIN)

t

AC(MAX)

ps

DQ and DM input setup time relative to DQS

t

DS

TBD

TBD

100

100

150

DQ and DM input hold time relative to DQS

t

DH

TBD

TBD

175

225

275

DQ and DM input pulse width (for each input)

t

DIPW

TBD

TBD

0.35

0.35

0.35

t

CK

Data hold skew factor

t

QHS

TBD

TBD

340

400

450

ps

DQ-DQS hold, DQS to fi rst DQ to go nonvalid, per

access

t

QH

TBD

TBD

t

HP

- t

QHS

t

HP

- t

QHS

t

HP

- t

QHS

ps

Data valid output window (DVW)

t

DVW

TBD

TBD

t

QH

- t

DQSQ

t

QH

- t

DQSQ

t

QH

- t

DQSQ

ns

Data Strobe

DQS input high pulse width

t

DQSH

TBD

TBD

0.35

0.35

0.35

t

CK

DQS input low pulse width

t

DQSL

TBD

TBD

0.35

0.35

0.35

t

CK

DQS output access time from CK/CK#

t

DQSCK

TBD

TBD

-400

+400

-450

+450

-500

+500

ps

DQS falling edge to CK rising - setup time

t

DSS

TBD

TBD

0.2

0.2

0.2

t

CK

DQS falling edge from CK rising - hold time

t

DSH

TBD

TBD

0.2

0.2

0.2

t

CK

DQS-DQ skew, DOS to last DQ valid, per group, per

access

t

DQSQ

TBD

TBD

240

300

350

ps

DQS read preamble

t

RPRE

TBD

TBD

0.9

1.1

0.9

1.1

0.9

1.1

t

CK

DQS read postamble

t

RPST

TBD

TBD

0.4

0.6

0.4

0.6

0.4

0.6

t

CK

DQS write preamble setup time

t

WPRES

TBD

TBD

0

0

0

ps

DQS write preamble

t

WPRE

TBD

TBD

0.35

0.35

0.35

t

CK

DQS write postamble

t

WPST

TBD

TBD

0.4

0.6

0.4

0.6

0.4

0.6

t

CK

Write command to fi rst DQS latching transition

t

DQSS

TBD

TBD

WL-0.25 WL+0.25 WL-0.25 WL+0.25 WL-0.25 WL+0.25

t

CK

AC specifi cation is based on SAMSUNG components. Other DRAM manufacturers specifi cation may be different.

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

8

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

AC TIMING PARAMETERS (continued)

V

CC

= +1.8V ± 0.1V

Parameter

Symbol

806

665

534

403

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Command and

Address

Address and control input pulse width for each input

t

IPW

TBD

TBD

0.6

0.6

0.6

t

CK

Address and control input setup time

t

IS

TBD

TBD

200

250

250

ps

Address and control input hold time

t

IH

TBD

TBD

275

375

475

ps

CAS# to CAS# command delay

t

CCD

TBD

TBD

2

2

2

ps

ACTIVE to ACTIVE (same bank) command

t

RC

TBD

TBD

55

55

55

ns

ACTIVE bank a to ACTIVE bank b command

t

RRD

TBD

TBD

7.5

7.5

7.5

ns

ACTIVE to READ or WRITE delay

t

RCD

TBD

TBD

15

15

15

ns

Four Bank Activate period

t

FAW

TBD

TBD

37.5

37.5

37.5

ns

ACTIVE to PRECHARGE command

t

RAS

TBD

TBD

40

70,000

40

70,000

40

70,000

ns

Internal READ to precharge command delay

t

RTP

TBD

TBD

7.5

7.5

7.5

ns

Write recovery time

t

WR

TBD

TBD

15

15

15

ns

Auto precharge write recovery + precharge time

t

DAL

TBD

TBD

t

WR

+ t

RP

t

WR

+ t

RP

t

WR

+ t

RP

ns

Internal WRITE to READ command delay

t

WTR

TBD

TBD

7.5

7.5

10

ns

PRECHARGE command period

t

RP

TBD

TBD

15

15

15

ns

PRECHARGE ALL command period

t

RPA

TBD

TBD

t

RP

+ t

CK

t

RP

+ t

CK

t

RP

+ t

CK

ns

LOAD MODE command cycle time

t

MRD

TBD

TBD

2

2

2

t

CK

CKE low to CK, CK# uncertainty

t

DELAY

TBD

TBD

t

IS+

t

CK+

t

IH

t

IS+

t

CK+

t

IH

t

IS+

t

CK+

t

IH

ns

Self Refresh

REFRESH to Active or Refresh to Refresh command interval

t

RFC

TBD

TBD

127.5

70,000

127.5

70,000

127.5

70,000

ns

Average periodic refresh interval

t

REFI

TBD

TBD

7.8

7.8

7.8

µs

Exit self refresh to non-READ command

t

XSNR

TBD

TBD

t

RFC(MIN)

+ 10

t

RFC(MIN)

+ 10

t

RFC(MIN)

+ 10

ns

Exit self refresh to READ

t

XSRD

TBD

TBD

200

200

200

t

CK

Exit self refresh timing reference

t

lSXR

TBD

TBD

t

IS

t

IS

t

IS

ps

ODT

ODT turn-on delay

t

AOND

TBD

TBD

2

2

2

2

2

2

t

CK

ODT turn-on

t

ACN

TBD

TBD

t

AC(MIN)

t

AC(MAX)

+ 1000

t

AC(MIN)

t

AC(MAX)

+ 1000

t

AC(MIN)

t

AC(MAX)

+ 1000

ps

ODT turn-off delay

t

AOFD

TBD

TBD

2.5

2.5

2.5

2.5

2.5

2.5

t

CK

ODT turn-off

t

AOF

TBD

TBD

t

AC(MIN)

t

AC(MAX)

+

600

t

AC(MIN)

t

AC(MAX)

+

600

t

AC(MIN)

t

AC(MAX)

+

600

ps

ODT turn-on (power-down mode)

t

AONPD

TBD

TBD

t

AC(MIN)

+

2000

2 x t

CK

+

t

AC(MAX)

+ 1000

t

AC(MIN)

+

2000

2 x t

CK

+

t

AC(MAX)

+ 1000

t

AC(MIN)

+

2000

2 x t

CK

+

t

AC(MAX)

+ 1000

ps

ODT turn-off (power-down mode)

t

AOFPD

TBD

TBD

t

AC(MIN)

+

2000

2.5 x

t

CK

+

t

AC(MAX)

+

1000

t

AC(MIN)

+

2000

2.5 x

t

CK

+

t

AC(MAX)

+

1000

t

AC(MIN)

+

2000

2.5 x

t

CK

+

t

AC(MAX)

+ 1000

ps

ODT to power-down entry latency

t

ANPD

TBD

TBD

3

3

3

t

CK

ODT power-down exit latency

t

AXPD

TBD

TBD

8

8

8

t

CK

Power-Down

Exit active power-down to READ command, MR[bit12=0]

t

XARD

TBD

TBD

2

2

2

t

CK

Exit active power-down to READ command, MR[bit12=1]

t

XARDS

TBD

TBD

7-AL

6-AL

6-AL

t

CK

Exit precharge power-down to any non-READ command

t

XP

TBD

TBD

2

2

2

t

CK

CKE minimum high/low time

t

CKE

TBD

TBD

3

3

3

t

CK

AC specifi cation is based on SAMSUNG components. Other DRAM manufacturers specifi cation may be different.

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

9

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

3.3 (0.130)

TYP

82.15 (3.234)

81.15 (3.222)

FRONT VIEW

30.15 (1.187)

29.85 (1.175)

20.0 (0.787)

TYP

10.0 (0.394)

TYP

1.0 (0.039)

TYP

4.10 (0.161)

3.90 (0.154)

2.10 (0.083)

1.90 (0.075)

0.50 (0.02) R

1.80 (0.071) D

X2

6.0 (0.236)

TYP

2.0 (0.079)

TYP

78.0 (3.071)

TYP

PIN 1

PIN 122

42.90 (1.689)

TYP

BACK VIEW

3.6 (0.142) TYP

Detail A

Detail B

33.6 (1.323)

TYP

38.4 (1.512)

TYP

3.2 (0.126)

TYP

PIN 244

PIN 123

Tolerances: + /- 0.13 (0.005) unless otherwise specified.

Detail A

3.60 (0.142)

FULL R

3.80 ±0.10

(0.150 ±0.004)

1.30

(0.051)

1.00 ±0.05

(0.039 ±0.002)

2.55 (0.100)

Detail B

0.45±0.03

(0.018 ±0.001)

0.60 TYP

(0.024)TYP

0.25

(0.010) MAX

3.80 (0.150)

MAX

1.10 (0.043) MAX

PACKAGE DIMENSIONS FOR D7

* ALL DIMENSIONS ARE IN MILLIMETERS AND (INCHES)

ORDERING INFORMATION FOR D7

Part Number

Clock Speed/

Data Rate

CAS

Latency

t

RCD

t

RP

Height*

WV3HG128M72EER806D7xxG**

400MHz/800Mb/s

6

6

6

30.00mm (1.181") TYP

WV3HG128M72EER665D7xxG**

333MHz/667Mb/s

5

5

5

30.00mm (1.181") TYP

WV3HG128M72EER534D7xxG

266MHz/533Mb/s

4

4

4

30.00mm (1.181") TYP

WV3HG128M72EER403D7xxG

200MHz/400Mb/s

3

3

3

30.00mm (1.181") TYP

** Contact factory for availability.

NOTES:

∑ RoHS product. ("G" = RoHS Compliant)

∑ Vendor specifi c part numbers are used to provide memory components source control. The place holder for this is shown as lower case"x" in

the part numbers above and is to be replaced with the respective vendors code. Consult factory for qualifi ed sourcing options. (M = Micron,

S = Samsung & consult factory for others)

∑ Consult factory for availability of industrial temperature (-40∞C to 85∞C) option

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

10

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

PART NUMBERING GUIDE

WV 3 H G 128M 72 E E R xxx D7 x x G

WEDC

MEMORY (SDRAM)

DDR 2

GOLD

DEPTH

BUS WIDTH

COMPONENT WIDTH (x8)

1.8V

REGISTERED

SPEED (Mb/s)

PACKAGE 244 PIN

INDUSTRIAL TEMP OPTION

(For commercial leave "blank"

for industrial add "I")

COMPONENT VENDOR NAME

(M = Micron)

(S = Samsung)

G = RoHS COMPLIANT

WV3HG128M72EER-D7

May 2006

Rev. 0

ADVANCED

11

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

Document Title

1GB ≠ 128Mx72 DDR2 SDRAM REGISTERED, w/PLL, Mini-DIMM

DRAM DIE OPTIONS:

∑

SAMSUNG: B-Die

∑

MICRON: U28A:A: will move to U38z:D Q4'06 and U488:E Q2'07

Revision History

Rev #

History

Release Date

Status

Rev 0

Created

May 2006

Advanced