WV3HG64M72EER-D6

August 2006

Rev. 1

ADVANCED*

1

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

512MB ≠ 64Mx72 DDR2 SDRAM REGISTERED DIMM, w/PLL

DESCRIPTION

The WV3HG64M72EER is a 64Mx72 Double Data

Rate DDR2 SDRAM high density module. This memory

module consists of nine 64Mx8 bit with 4 banks DDR2

Synchronous DRAMs in FBGA packages, mounted on a

240-pin DIMM FR4 substrate.

* This product is under development, is not qualifi ed or characterized and is subject to

change or cancellation without notice.

NOTE: Consult factory for availability of:

∑ Vendor source control options

∑ Industrial temperature option

FEATURES

Registered 240-pin, dual in-line memory module

Fast data transfer rates: PC2-6400*, PC2-5300*,

PC2-4200 and PC2-3200

Utilizes 800*, 667*, 533 and 400 MT/s DDR2

SDRAM components

V

CC

= V

CCQ

= 1.8V ± 0.1V

V

CCSPD

= 1.7V to 3.6V

JEDEC standard 1.8V I/O (SSTL_18-compatible)

Differential data strobe (DQS, DQS#) option

Four-bit prefetch architecture

Multiple internal device banks for concurrent

operation

Supports duplicate output strobe (RDQS/RDQS#)

Write Latency = Read Latency 1

tck

Programmable CAS# latency (CL): 3, 4, 5* and 6*

Adjustable data-output drive strength

On-die termination (ODT)

7.8µs average periodic refresh interval

Posted CAS# latency: 0, 1, 2, 3 and 4

Serial Presence Detect (SPD) with EEPROM

Auto & Self Refresh (8k/64ms refresh)

Gold edge contacts

RoHS

compliant

Package

option

∑ 240 Pin DIMM

∑ PCB ≠ 30.00mm (1.181") TYP

OPERATING FREQUENCIES

PC2-3200

PC2-4200

PC2-5300*

PC2-6400*

Clock Speed

200MHz

266MHz

333MHz

400MHz

CL-t

RCD

-t

RP

3-3-3

4-4-4

5-5-5

6-6-6

* Consult factory for availability

WV3HG64M72EER-D6

ADVANCED

2

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

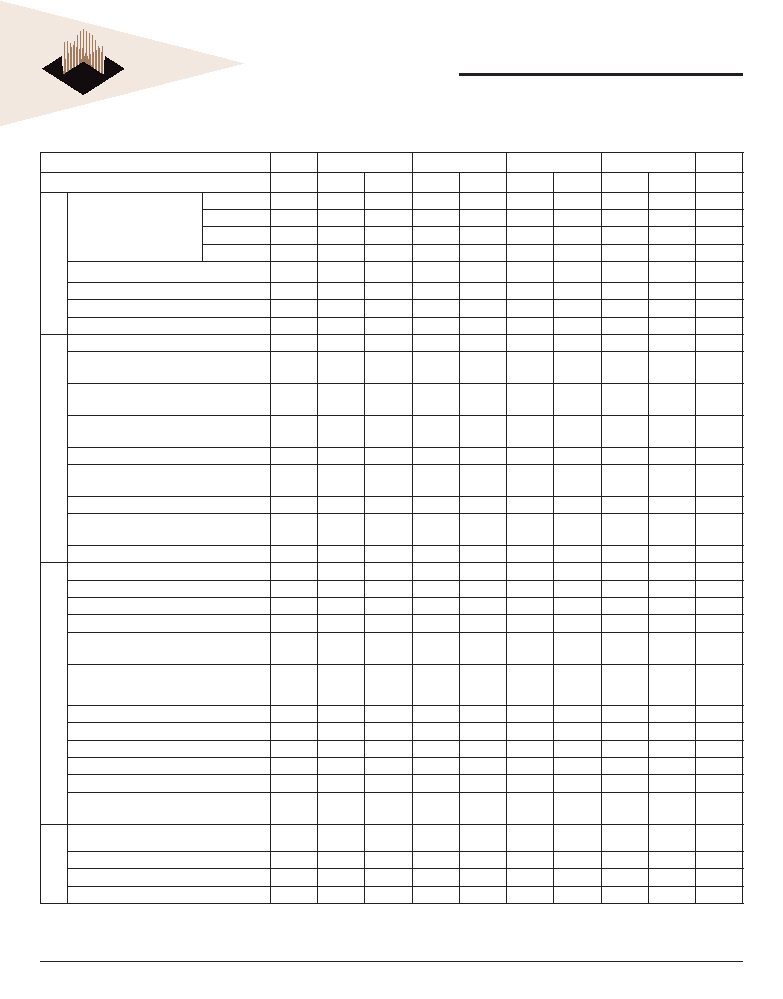

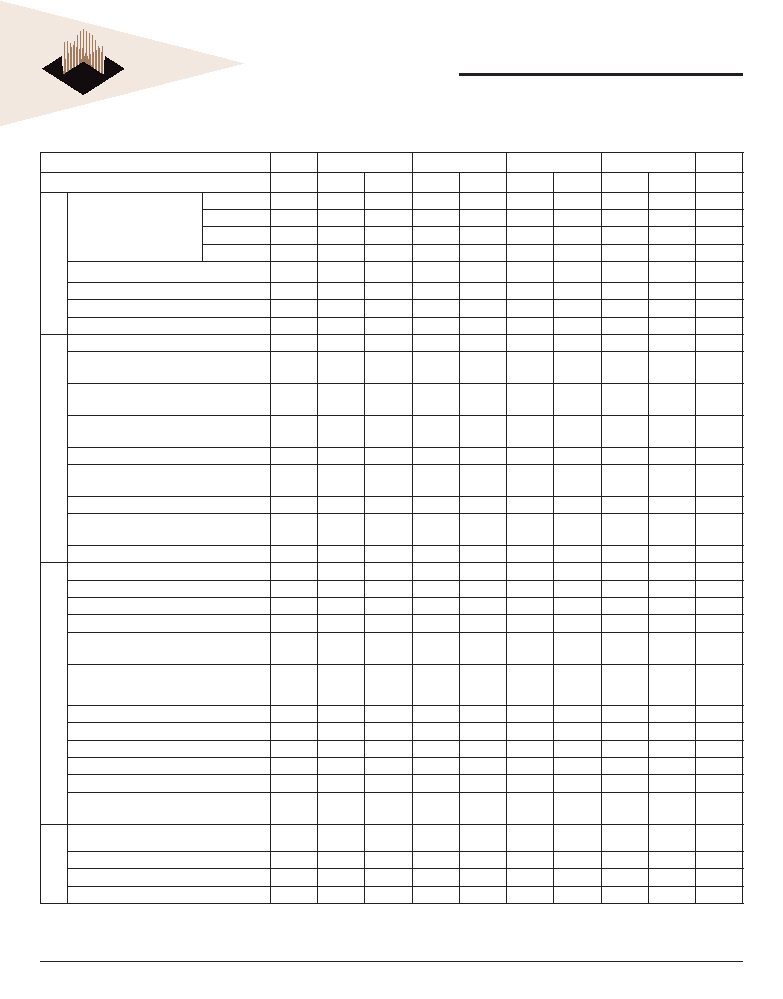

PIN CONFIGURATION

Pin No.

Symbol

Pin No.

Symbol

Pin No.

Symbol

Pin No.

Symbol

1

V

REF

61

A4

121

V

SS

181

V

CC

2

V

SS

62

V

CC

122

DQ4

182

A3

3

DQ0

63

A2

123

DQ5

183

A1

4

DQ1

64

V

CC

124

V

SS

184

V

CC

5

V

SS

65

V

SS

125

DM0/DQS9

185

CK0

6

DQS0#

66

V

SS

126

NC/DQS9#

186

CK0#

7

DQS0

67

V

CC

127

V

SS

187

V

CC

8

V

SS

68

NC

128

DQ6

188

A0

9

DQ2

69

V

CC

129

DQ7

189

V

CC

10

DQ3

70

A10/AP

130

V

SS

190

BA1

11

V

SS

71

BA0

131

DQ12

191

V

CC

12

DQ8

72

V

CC

132

DQ13

192

RAS#

13

DQ9

73

WE#

133

V

SS

193

CS0#

14

V

SS

74

CAS#

134

DM1/DQS10

194

V

CC

15

DQS1#

75

V

CC

135

NC/DQS10#

195

ODT0

16

DQS1

76

NC

136

V

SS

196

A13

17

V

SS

77

NC

137

NC

197

V

CC

18

RESET#

78

V

CC

138

NC

198

V

SS

19

NC

79

V

SS

139

V

SS

199

DQ36

20

V

SS

80

DQ32

140

DQ14

200

DQ37

21

DQ10

81

DQ33

141

DQ15

201

V

SS

22

DQ11

82

V

SS

142

V

SS

202

DM4/DQS13

23

V

SS

83

DQS4#

143

DQ20

203

NC/DQS13#

24

DQ16

84

DQS4

144

DQ21

204

V

SS

25

DQ17

85

V

SS

145

V

SS

205

DQ38

26

V

SS

86

DQ34

146

DM2/DQS11

206

DQ39

27

DQS2#

87

DQ35

147

NC/DQS11#

207

V

SS

28

DQS2

88

V

SS

148

V

SS

208

DQ44

29

V

SS

89

DQ40

149

DQ22

209

DQ45

30

DQ18

90

DQ41

150

DQ23

210

V

SS

31

DQ19

91

V

SS

151

V

SS

211

DM5/DQS14

32

V

SS

92

DQS5#

152

DQ28

212

NC/DQS14#

33

DQ24

93

DQS5

153

DQ29

213

V

SS

34

DQ25

94

V

SS

154

V

SS

214

DQ46

35

V

SS

95

DQ42

155

DM3/DQS12

215

DQ47

36

DQS3#

96

DQ43

156

NC/DQS12#

216

V

SS

37

DQS3

97

V

SS

157

V

SS

217

DQ52

38

V

SS

98

DQ48

158

DQ30

218

DQ53

39

DQ26

99

DQ49

159

DQ31

219

V

SS

40

DQ27

100

V

SS

160

V

SS

220

NC

41

V

SS

101

SA2

161

CB4

221

NC

42

CB0

102

NC

162

CB5

222

V

SS

43

CB1

103

V

SS

163

V

SS

223

DM6/DQS15

44

V

SS

104

DQS6#

164

DM8/DQS17

224

NC/DQS15#

45

DQS8#

105

DQS6

165

NC/DQS17#

225

V

SS

46

DQS8

106

V

SS

166

V

SS

226

DQ54

47

V

SS

107

DQ50

167

CB6

227

DQ55

48

CB2

108

DQ51

168

CB7

228

V

SS

49

CB3

109

V

SS

169

V

SS

229

DQ60

50

V

SS

110

DQ56

170

V

CC

230

DQ61

51

V

CC

111

DQ57

171

NC

231

V

SS

52

CKE0

112

V

SS

172

V

CC

232

DM7/DQS16

53

V

CC

113

DQS7#

173

NC

233

NC/DQS16#

54

NC

114

DQS7

174

NC

234

V

SS

55

NC

115

V

SS

175

V

CC

235

DQ62

56

V

CC

116

DQ58

176

A12

236

DQ63

57

A11

117

DQ59

177

A9

237

V

SS

58

A7

118

V

SS

178

V

CC

238

V

CC

SPD

59

V

CC

119

SDA

179

A8

239

SA0

60

A5

120

SCL

180

A6

240

SA1

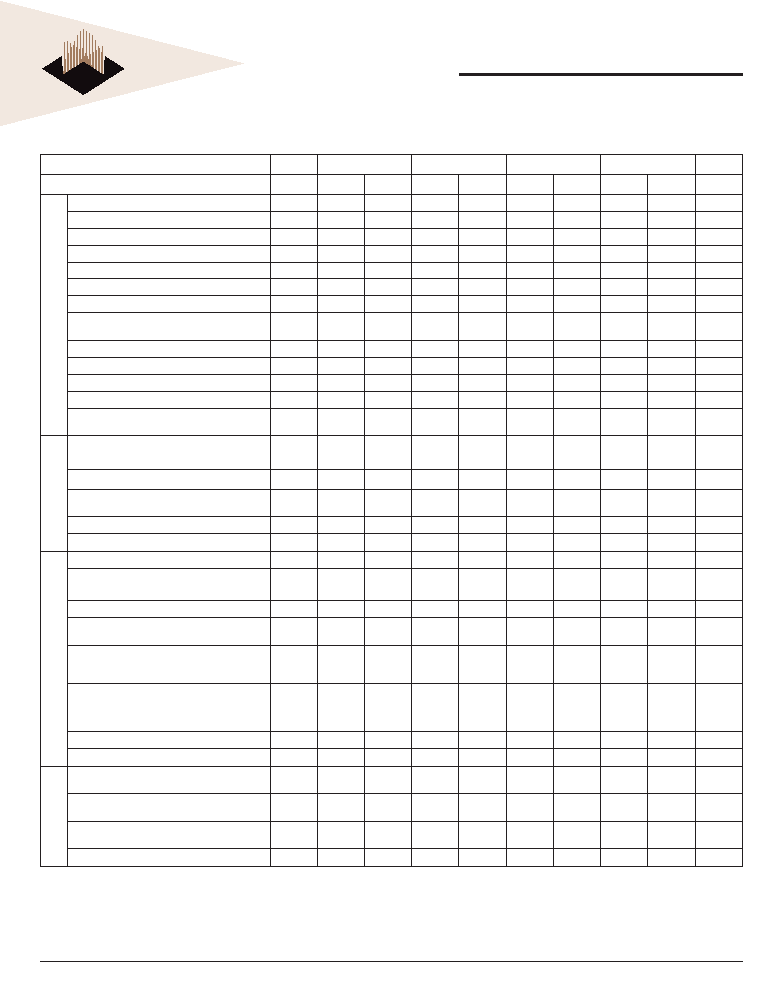

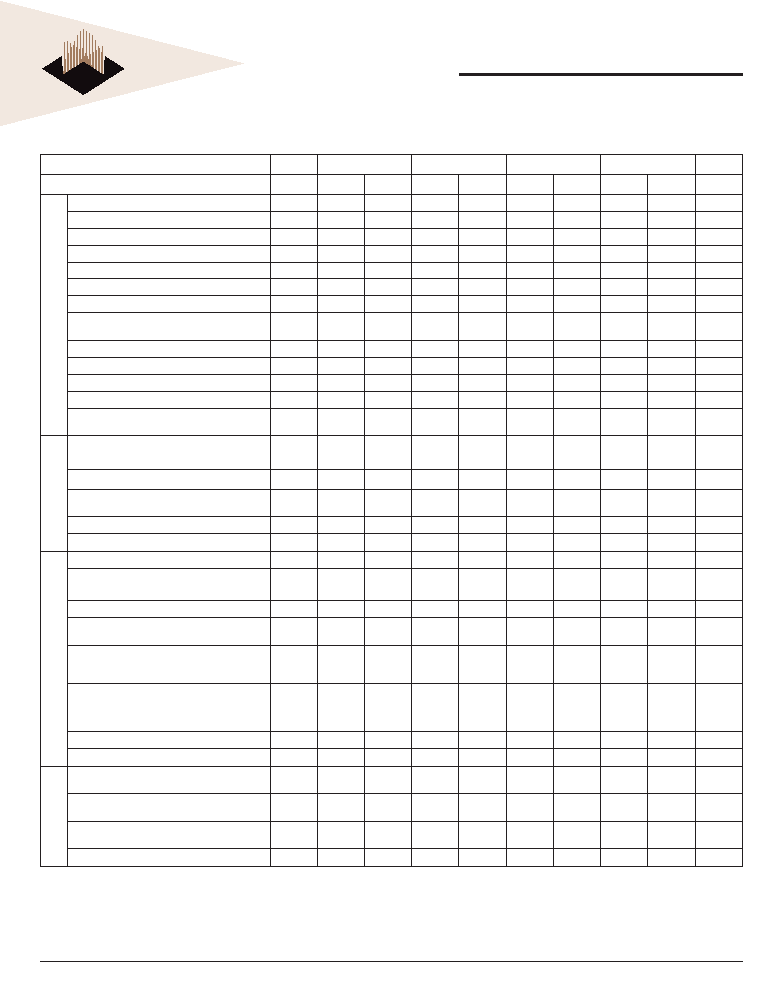

PIN NAMES

Pin Name

Function

A0-A13

Address Inputs

BA0,BA1

SDRAM Bank Addresses

DQ0-DQ63

Data Input/Output

CB0-CB7

Check Bits

DQS0-DQS17

Data strobes

DQS0#-DQS17#

Data strobes complement

DM0 - DM8

Data Masks

ODT0

On-die termination control

CK0,CK0#

Clock Inputs

CKE0

Clock Enable

CS0#

Chip Select

RAS#

Row Address Strobe

CAS#

Column Address Strobe

WE#

Write Enable

RESET#

Register Reset Input/PLL OE

V

CC

Core and I/O Power (1.8V)

V

SS

Ground

SA0-SA2

SPD address

SDA

SPD Data Input/Output

SCL

Serial Presence Detect(SPD) Clock Input

V

REF

Input/Output Reference Voltage

V

CC

SPD

SPD Power

NC

Spare pins, No connect

WV3HG64M72EER-D6

ADVANCED

3

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

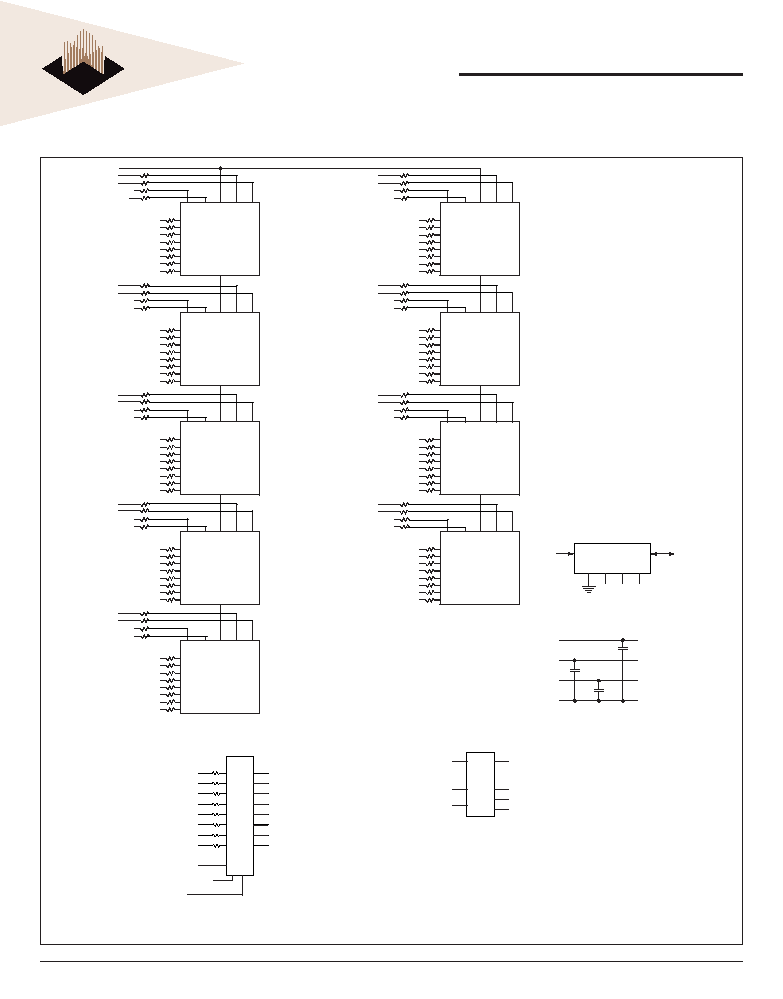

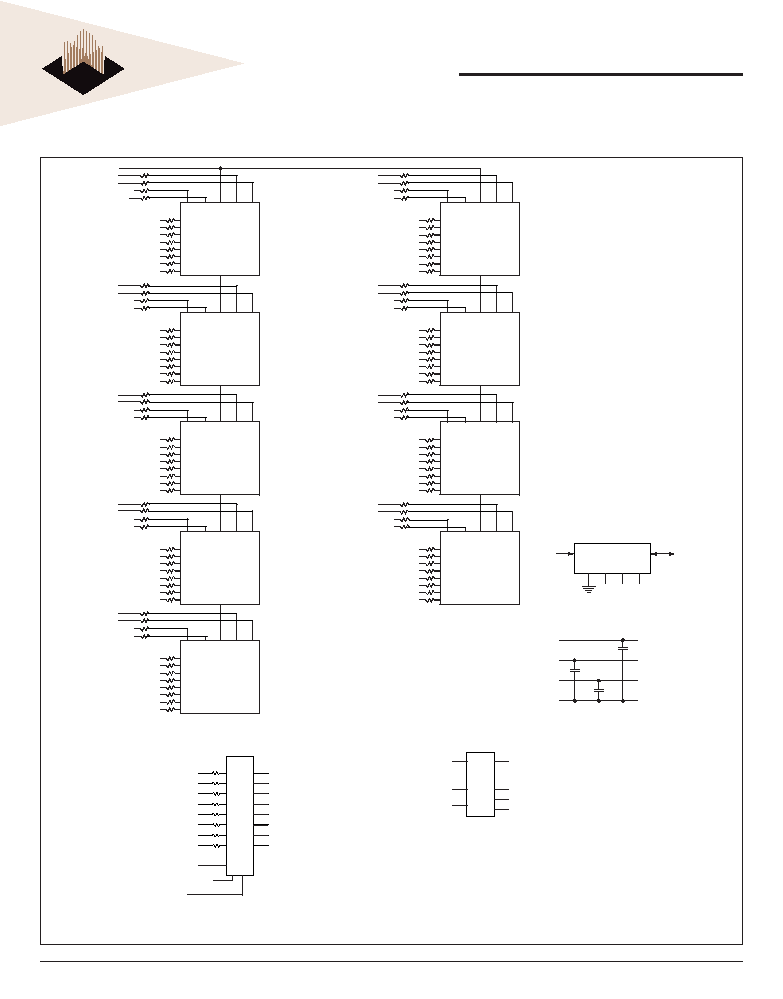

FUNCTIONAL BLOCK DIAGRAM

A0

Serial PD

A1 A2

SA0 SA1 SA2

SCL

SDA

V

CCSPD

V

CC

/V

CCQ

V

REF

V

SS

Serial PD

DDR2 SDRAMs

DDR2 SDRAMs

DDR2 SDRAMs

WP

1:2

R

E

G

I

S

T

E

R

RST#

CS0#

BA0 - BA1

A0 - A13

RAS#

CAS#

WE#

CKE0

ODT0

RESET#**

PCK7**

PCK7#**

P

L

L

OE

CK0

CK0#

RESET#

PCK0-PCK6, PCK8, PCK9 CK : DDR2 SDRAMs

PCK0#-PCK6#, PCK8#, PCK9# CK# : DDR2 SDRAMs

PCK7 CK : Register

PCK7# CK# : Register

RCS0# : DDR2 SDRAMs

RBA0 - RBA1 : DDR2 SDRAMs

RA0 - RA13 : DDR2 SDRAMs

RRAS# : DDR2 SDRAMs

RCAS# : DDR2 SDRAMs

RWE# : DDR2 SDRAMs

RCKE0 : DDR2 SDRAMs

RODT0 : DDR2 SDRAMs

RCS0#

DQS0

DQS0#

DM0/DQS9

NC/DQS9#

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

DQ1

DQ0

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS1

DQS1#

NC/DQS10#

DM1/DQS10

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS2

DQS2#

DM2/DQS11

NC/DSS11#

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS3

DQS3#

DM3/DQS12

NC/DSS12#

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS8

DQS8#

DM8/DQS17

NC/DSS17#

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQS4

DQS4#

DM4/DQS13

NC/DQS13#

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQS5

DQS5#

DM5/DQS14

NC/DQS14#

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQS6

DQS6#

DM6/DQS15

NC/DQS15#

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQS7

DQS7#

DM7/DQS16

NC/DQS16#

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DM/

RDQS

NU/

RDQS#

CS# DQS DQS#

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

NOTE: All resistor values are 22 ohms unless otherwise specifi ed.

**RESET#, PCK7 and RCK7# connects both registers. Other signals connect to one of two registers.

WV3HG64M72EER-D6

ADVANCED

4

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

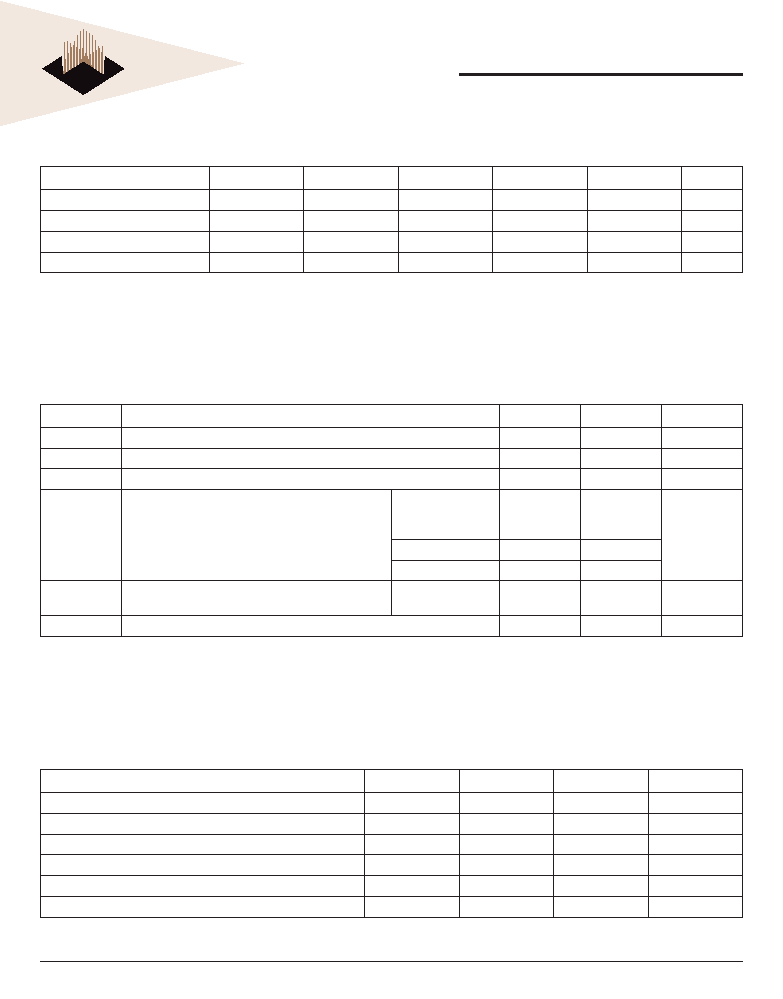

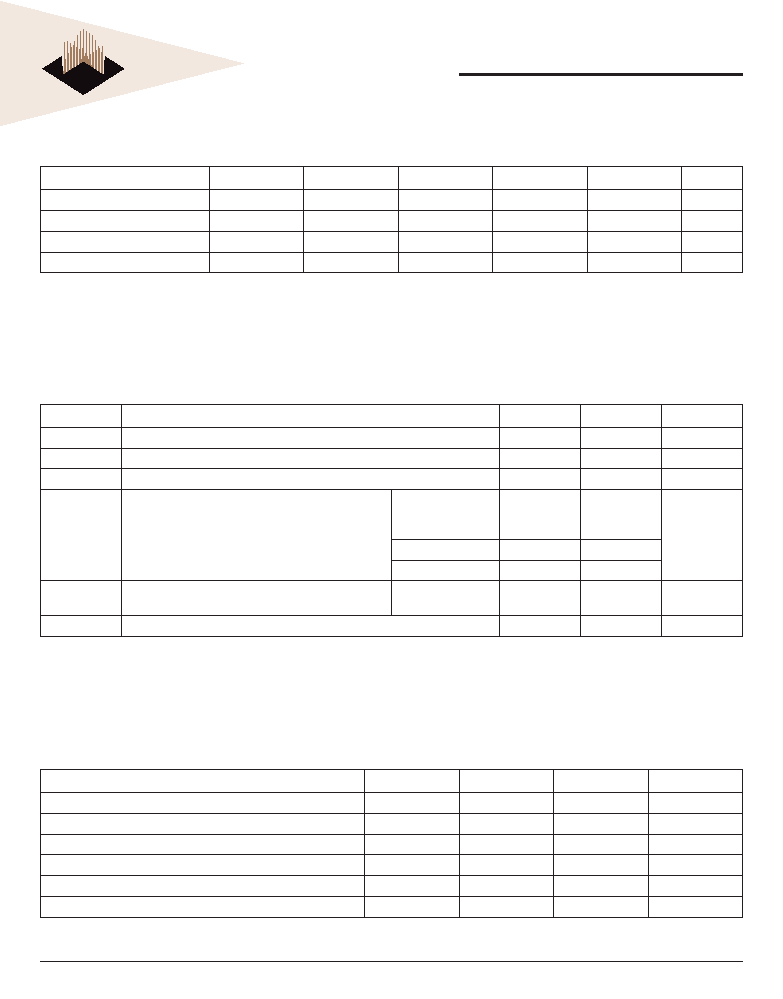

DC OPERATING CONDITIONS

All voltages referenced to V

SS

Parameter

Symbol

Min

Typical

Max

Unit

Notes

Supply Voltage

V

CC

1.7

1.8

1.9

V

3

I/O Reference Voltage

V

REF

0.49 x V

CC

0.50 x V

CC

0.51 x V

CC

V

1

I/O Termination Voltage

V

TT

V

REF

-0.04

V

REF

V

REF

+0.04

V

2

SPD Supply Voltage

V

CCSPD

1.7

-

3.6

V

Notes:

1

V

REF

is expected to equal V

CC/2

of the transmitting device and to track variations in the DC level of the same. Peak-to-peak noise on

V

REF

may not exceed +/-1 percent of the

DC value. Peak-to-peak AC noise on V

REF

may not exceed +/-2 percent of V

REF

. This measurement is to be taken at the nearest V

REF

bypass capacitor.

2. V

TT

is not applied directly to the device. V

TT

is a system supply for signal termination resistors, is expected to be set equal to V

REF

and must track variations in the DC level of V

REF

.

3. V

CCQ

of all IC's are tied to V

CC

.

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Min

Max

Units

V

CC

Voltage on V

CC

pin relative to V

SS

-0.5

2.3

V

V

IN

, V

OUT

Voltage on any pin relative to V

SS

- 0.5

2.3

V

T

STG

Storage Temperature

-55

100

∞C

I

L

Input leakage current: Any input

0V<VIN<V

CC

; V

REF

input

0V<VIN<0.95V; Other pins not under test = 0V

Command/Address,

RAS#, CAS#, WE#,

CS#, CKE

-5

5

µA

CK, CK#

-10

10

DM

-5

5

I

OZ

Output leakage current;

0V<VOUT<V

CC

; DQs and ODT are disable

DQ, DQS, DQS#

-5

5

µA

I

VREF

V

REF

leakage current; V

REF

= Valid V

REF

level

-18

18

µA

CAPACITANCE

T

A

= 25∞C, f = 100MHz

Parameter

Symbol

Min

Max

Units

Input Capacitance: (A0~A13, BA0~BA1, RAS#, CAS#, WE#)

CIN

1

11

12

pF

Input Capacitance: (CKE0), (ODT0)

CIN

2

11

12

pF

Input Capacitance: (CS0#)

CIN

3

11

12

pF

Input Capacitance: (CK0, CK0#)

CIN

4

10

11

pF

Input Capacitance: (DM0~DM8), DQS0~DQS17)

CIN

5

6.5

8

pF

Input/Output Capacitance: (DQ0 ~ DQ63), (CB0 ~CB7)

COUT

1

6.5

8

pF

WV3HG64M72EER-D6

ADVANCED

5

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

OPERATING TEMPERATURE CONDITION

Parameter

Symbol

Rating

Units

Notes

Operating Case Temperature (Commercial)

TOPER

0 to +85∞C

∞C

1, 2

NOTE:

1. Operation temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JEDEC JESD51.2

2. At 0 to +85

∞C, operation temperature range, all DRAM specifi cation will be supported.

INPUT DC LOGIC LEVEL

All voltages referenced to V

SS

Parameter

Symbol

Min

Max

Unit

Input High (Logic 1) Voltage

V

IH

(DC)

V

REF

+ 0.125

V

CC

+ 0.300

V

Input Low (Logic 0) Voltage

V

IL

(DC)

- 0.300

VREF - 0.125

V

INPUT AC LOGIC LEVEL

All voltages referenced to V

SS

Parameter

Symbol

Min

Max

Unit

AC Input High (Logic 1) Voltage

DDR2-400 & DDR2-533

V

IH

(AC)

V

REF

+ 0.250

-

V

AC Input High (Logic 1) Voltage

DDR2-667

V

IH

(AC)

V

REF

+ 0.200

-

V

AC Input High (Logic 0) Voltage

DDR2-400 & DDR2-533

V

IL

(AC)

-

V

REF

- 0.250

V

AC Input High (Logic 0) Voltage

DDR2-667

V

IL

(AC)

-

V

REF

- 0.200

V

WV3HG64M72EER-D6

ADVANCED

6

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

DDR2 I

CC

SPECIFICATIONS AND CONDITIONS

Includes DDR2 SDRAM components only

Symbol Proposed Conditions

806

665

534

403

Units

I

CC0*

Operating one bank active-precharge current;

t

CK

= t

CK

(I

CC

), t

RC

= t

RC

(I

CC

), t

RAS

= t

RAS

min(I

CC

); CKE is HIGH, CS# is HIGH between valid

commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

TBD

1,120

1,120

mA

I

CC1*

Operating one bank active-read-precharge current;

I

OUT

= 0mA; BL = 4, CL = CL(I

CC

), AL = 0; t

CK

= t

CK

(I

CC

), t

RC

= t

RC

(I

CC

), t

RAS

= t

RAS

min(I

CC

), t

RCD

= t

RCD

(I

CC

); CKE is HIGH, CS# is HIGH between valid commands; Address bus inputs are

SWITCHING; Data pattern is same as I

CC

4W

TBD

TBD

1,255

1,255

mA

I

CC2P*

Precharge power-down current;

All banks idle; t

CK

= t

CK

(I

CC

); CKE is LOW; Other control and address bus inputs are STABLE; Data

bus inputs are FLOATING

TBD

TBD

472

472

mA

I

CC2Q**

Precharge quiet standby current;

All banks idle; t

CK

= t

CK

(I

CC

); CKE is HIGH, CS# is HIGH; Other control and address bus inputs are

STABLE; Data bus inputs are FLOATING

TBD

TBD

670

670

mA

I

CC2N**

Precharge standby current;

All banks idle; t

CK

= t

CK

(I

CC

); CKE is HIGH, CS# is HIGH; Other control and address bus inputs are

SWITCHING; Data bus inputs are SWITCHING

TBD

TBD

715

715

mA

I

CC3P**

Active power-down current;

All banks open; t

CK

= t

CK

(I

CC

); CKE is LOW; Other control and

address bus inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0

TBD

TBD

670

670

mA

Slow PDN Exit MRS(12) = 1

TBD

TBD

508

508

mA

I

CC3N**

Active standby current;

All banks open; t

CK

= t

CK

(I

CC

), t

RAS

= t

RAS

max(I

CC

), t

RP

= t

RP

(I

CC

); CKE is HIGH, CS# is HIGH between

valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are

SWITCHING

TBD

TBD

850

850

mA

I

CC4W*

Operating burst write current;

All banks open, Continuous burst writes; BL = 4, CL = CL(I

CC

), AL = 0; t

CK

= t

CK

(I

CC

), t

RAS

=

t

RAS

max(I

CC

), t

RP

= t

RP

(I

CC

); CKE is HIGH, CS# is HIGH between valid commands; Address bus

inputs are SWITCHING; Data bus inputs are SWITCHING

TBD

TBD

1,480

1,390

mA

I

CC4R*

Operating burst read current;

All banks open, Continuous burst reads, I

OUT

= 0mA; BL = 4, CL = CL(I

CC

), AL = 0; t

CK

= t

CK

(I

CC

), t

RAS

= t

RAS

max(I

CC

), t

RP

= t

RP

(I

CC

); CKE is HIGH, CS# is HIGH between valid commands; Address bus

inputs are SWITCHING; Data pattern is same as I

CC

4W

TBD

TBD

1,525

1,390

mA

I

CC5B**

Burst auto refresh current;

t

CK

= t

CK

(I

CC

); Refresh command at every t

RFC

(I

CC

) interval; CKE is HIGH, CS# is HIGH between

valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are

SWITCHING

TBD

TBD

1,160

1,660

mA

I

CC6**

Self refresh current;

CK and CK\ at 0V; CKE 0.2V; Other control and address bus

inputs

are FLOATING; Data bus inputs are FLOATING

Normal

TBD

TBD

72

72

mA

I

CC7*

Operating bank interleave read current;

All bank interleaving reads, I

OUT

= 0mA; BL = 4, CL = CL(I

CC

), AL = t

RC

D(I

CC

)-1*t

CK

(I

CC

); t

CK

=

t

CK

(I

CC

), t

RC

= t

RC

(I

CC

), t

RRD

= t

RRD

(I

CC

), t

RCD

= 1*t

CK

(I

CC

); CKE is HIGH, CS# is HIGH between valid

commands; Address bus inputs are STABLE during DESELECTs; Data bus inputs are SWITCHING.

TBD

TBD

2,380

2,380

mA

Note: I

CC

specifi cation is based on

SAMSUNG components. Other DRAM Manufacturers specifi cation may be different.

*: Value calculated as one module rank in this operating condition, and all other module ranks in I

CC2P

(CKE LOW) mode.

**: Value calculated refl ects all module ranks in this operating condition.

WV3HG64M72EER-D6

ADVANCED

7

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

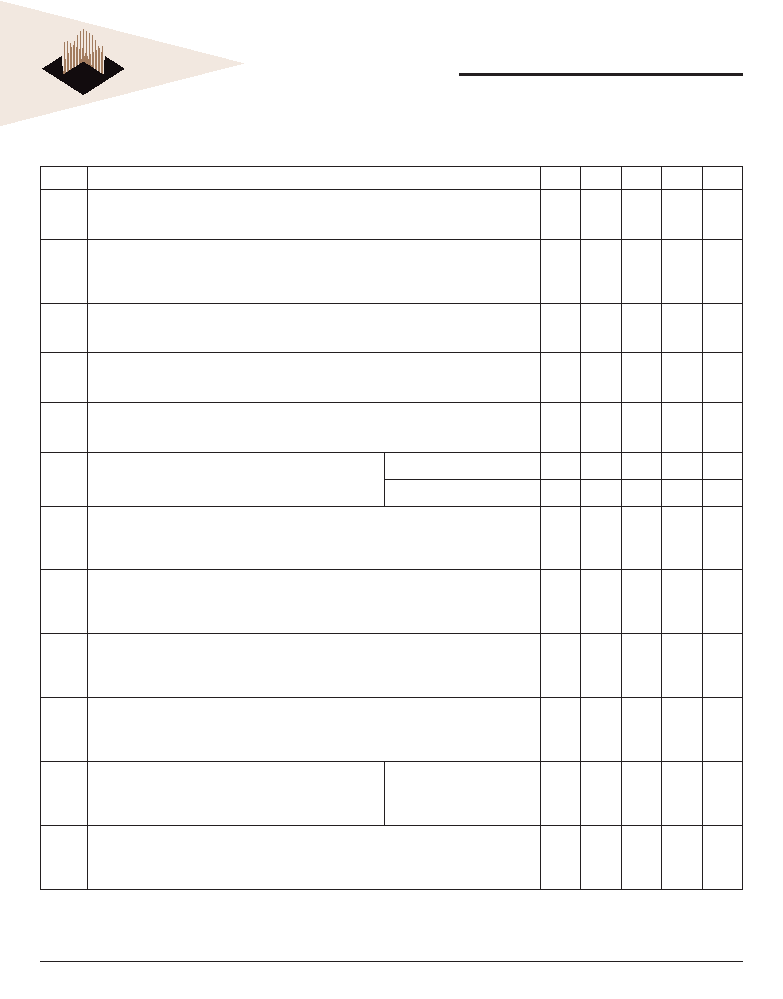

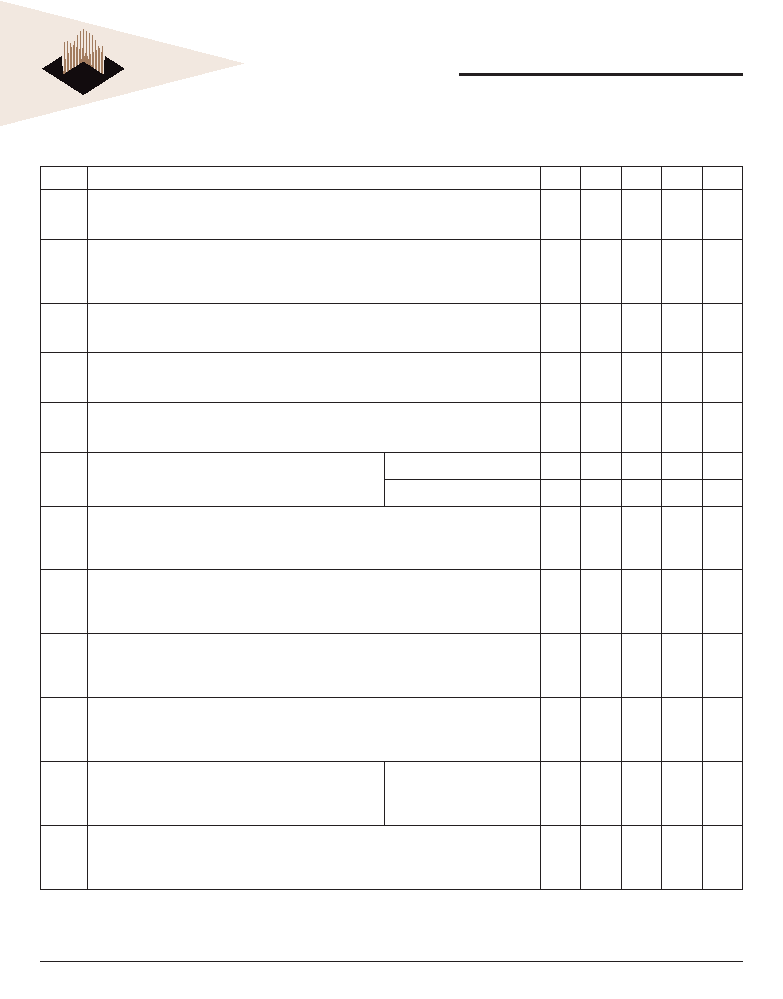

AC TIMING PARAMETERS & SPECIFICATIONS

AC CHARACTERISTICS

806

665

534

403

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Clock

Clock cycle time

CL = 6

t

CK (6)

TBD

TBD

ps

CL = 5

t

CK (5)

TBD

TBD

3,000

8,000

ps

CL = 4

t

CK (4)

TBD

TBD

3,750

8,000

3,750

8,000

5,000

8,000

ps

CL = 3

t

CK (3)

TBD

TBD

5,000

8,000

5,000

8,000

5,000

8,000

ps

CK high-level width

t

CH

TBD

TBD

0.45

0.55

0.45

0.55

0.45

0.55

t

CK

CK low-level width

t

CL

TBD

TBD

0.45

0.55

0.45

0.55

0.45

0.55

t

CK

Half clock period

t

HP

TBD

TBD

MIN

(t

CH,

t

CL

)

MIN

(t

CH,

t

CL

)

MIN

(t

CH,

t

CL

)

ps

Clock jitter

t

J

I

T

TBD

TBD

-125

125

-125

125

-125

125

ps

Data

DQ output access time from CK/CK#

t

AC

TBD

TBD

-450

+450

-500

+500

-600

+600

ps

Data-out high-impedance window from

CK/CK#

t

HZ

TBD

TBD

t

AC(MAX)

t

AC(MAX)

t

AC(MAX)

ps

Data-out low-impedance window from

CK/CK#

t

LZ

TBD

TBD

t

AC(MIN)

t

AC(MAX)

t

AC(MIN)

t

AC(MAX)

t

AC(MIN)

t

AC(MAX)

ps

DQ and DM input setup time relative to

DQS

t

DS

TBD

TBD

100

100

150

DQ and DM input hold time relative to DQS

t

DH

TBD

TBD

225

225

275

DQ and DM input pulse width (for each

input)

t

D

I

PW

TBD

TBD

0.35

0.35

0.35

t

CK

Data hold skew factor

t

QHS

TBD

TBD

340

400

450

ps

DQ...DQS hold, DQS to fi rst DQ to go

nonvalid, per access

t

QH

TBD

TBD

t

HP -

t

QHS

t

HP -

t

QHS

t

HP -

t

QHS

ps

Data valid output window (DVW)

t

DVW

TBD

TBD

t

QH -

t

DQSQ

t

QH -

t

DQSQ

t

QH -

t

DQSQ

ns

Data Strobe

DQS input high pulse width

t

DQSH

TBD

TBD

0.35

0.35

0.35

t

CK

DQS input low pulse width

t

DQSL

TBD

TBD

0.35

0.35

0.35

t

CK

DQS output access time from CK/CK#

t

DQSCK

TBD

TBD

-400

+400

-450

+450

-500

+500

ps

DQS falling edge to CK rising ... setup time

t

DSS

TBD

TBD

0.2

0.2

0.2

t

CK

DQS falling edge from CK rising ... hold

time

t

DSH

TBD

TBD

0.2

0.2

0.2

t

CK

DQS...DQ skew, DQS to last DQ valid, per

group,

per access

t

DQSQ

TBD

TBD

240

300

350

ps

DQS read preamble

t

RPRE

TBD

TBD

0.9

1.1

0.9

1.1

0.9

1.1

t

CK

DQS read postamble

t

RPST

TBD

TBD

0.4

0.6

0.4

0.6

0.4

0.6

t

CK

DQS write preamble setup time

t

WPRES

TBD

TBD

0

0

0

ps

DQS write preamble

t

WPRE

TBD

TBD

0.35

0.35

0.35

t

CK

DQS write postamble

t

WPST

TBD

TBD

0.4

0.6

0.4

0.6

0.4

0.6

t

CK

Write command to fi rst DQS latching

transition

t

DQSS

TBD

TBD

WL-

0.25

WL+

0.25

WL-

0.25

WL+

0.25

WL-

0.25

WL+

0.25

t

CK

Address and control input pulse width for

each input

t

IPW

TBD

TBD

0.6

0.6

0.6

t

CK

Address and control input setup time

t

IS

TBD

TBD

200

250

250

ps

Address and control input hold time

t

IH

TBD

TBD

275

375

475

ps

Address and control input hold time

t

CCD

TBD

TBD

2

2

2

t

CK

* AC specifi cation is based on

SAMSUNG components. Other DRAM manufactures specifi cation may be different.

Continued on next page

WV3HG64M72EER-D6

ADVANCED

8

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

AC TIMING PARAMETERS (cont'd)

AC CHARACTERISTICS

806

665

534

403

PARAMETER

SYMBOL

MIN

MAX

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

Command and

Address

ACTIVE to ACTIVE (same bank) command

t

RC

TBD

TBD

55

55

55

ns

ACTIVE bank a to ACTIVE bank b command

t

RRD

TBD

TBD

7.5

7.5

7.5

ns

ACTIVE to READ or WRITE delay

t

RCD

TBD

TBD

15

15

15

ns

Four Bank Activate period

t

FAW

TBD

TBD

37.5

37.5

37.5

37.5

37.5

37.5

ns

ACTIVE to PRECHARGE command

t

RAS

TBD

TBD

40

70,000

40

70,000

40

70,000

ns

Internal READ to precharge command delay

t

RTP

TBD

TBD

7.5

7.5

7.5

ns

Write recovery time

t

WR

TBD

TBD

15

15

15

ns

Auto precharge write recovery + precharge

time

t

DAL

TBD

TBD

t

WR

+t

RP

t

WR

+t

RP

t

WR

+t

RP

ns

Internal WRITE to READ command delay

t

WTR

TBD

TBD

7.5

7.5

7.5

ns

PRECHARGE command period

t

RP

TBD

TBD

15

15

15

ns

PRECHARGE ALL command period

t

RPA

TBD

TBD

t

RP

+t

CK

t

RP

+t

CK

t

RP

+t

CK

ns

LOAD MODE command cycle time

t

MRD

TBD

TBD

2

2

2

t

CK

CKE low to CK,CK# uncertainty

t

DELAY

TBD

TBD

t

IS

+t

CK

t

IH

t

IS

+t

CK

t

IH

t

IS

+t

CK

t

IH

ns

Self Refresh

REFRESH to Active of Refresh to Refresh

command interfal

t

RFC

TBD

TBD

127.5

70,000

127.5

70,000

127.5

70,000

ns

Average periodic refresh interval

t

REF

I

TBD

TBD

7.8

7.8

7.8

µs

Exit self refresh to non-READ command

t

XSNR

TBD

TBD

t

RFC(MIN)

+10

t

RFC(MIN)

+10

t

RFC(MIN)

+10

ns

Exit self refresh to READ command

t

XSRD

TBD

TBD

200

200

200

t

CK

Exit self refresh timing reference

tI

SXR

TBD

TBD

t

IS

t

IS

t

IS

ps

ODT

ODT turn-on delay

t

AOND

TBD

TBD

2

2

2

2

2

2

t

CK

ODT turn-on

t

AON

TBD

TBD

t

AC(MIN)

t

AC(MAX)

+1000

t

AC(MIN)

t

AC(MAX)

+1000

t

AC(MIN)

t

AC(MAX)

+1000

ps

ODT turn-off delay

t

AOFD

TBD

TBD

2.5

2.5

2.5

2.5

2.5

2.5

t

CK

ODT turn-off

t

AOF

TBD

TBD

t

AC(MIN)

t

AC(MAX)

+600

t

AC(MIN)

t

AC(MAX)

+600

t

AC(MIN)

t

AC(MAX)

+600

ps

ODT turn-on (power-down mode)

t

AONPD

TBD

TBD

t

AC(MIN)

+2000

2 x t

CK

+

t

AC(MAX)

+1000

t

AC(MIN)

+2000

2 x t

CK

+

t

AC(MAX)

+1000

t

AC(MIN)

+2000

2 x t

CK

+

t

AC(MAX)

+1000

ps

ODT turn-off (power-down mode)

t

AOFPD

TBD

TBD

t

AC(MIN)

+2000

2.5 x

t

CK

+

t

AC(MAX)

+1000

t

AC(MIN)

+2000

2.5 x

t

CK

+

t

AC(MAX)

+1000

t

AC(MIN)

+2000

2.5 x

t

CK

+

t

AC(MAX)

+1000

ps

ODT to power-down entry latency

t

ANPD

TBD

TBD

3

3

3

t

CK

ODT power-down exit latency

t

AXPD

TBD

TBD

8

8

8

t

CK

Power-Down

Exit active power-down to READ command,

MR[bit12=0]

t

XARD

TBD

TBD

2

2

2

t

CK

Exit active power-down to READ command,

MR[bit12=1]

t

XARDS

TBD

TBD

7-AL

6-AL

6-AL

t

CK

A Exit precharge power-down to any non-

READ command.

t

XP

TBD

TBD

2

2

2

t

CK

CKE minimum high/low time

t

CKE

TBD

TBD

3

3

3

t

CK

* AC specifi cation is based on

SAMSUNG components. Other DRAM manufactures specifi cation may be different.

WV3HG64M72EER-D6

ADVANCED

9

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

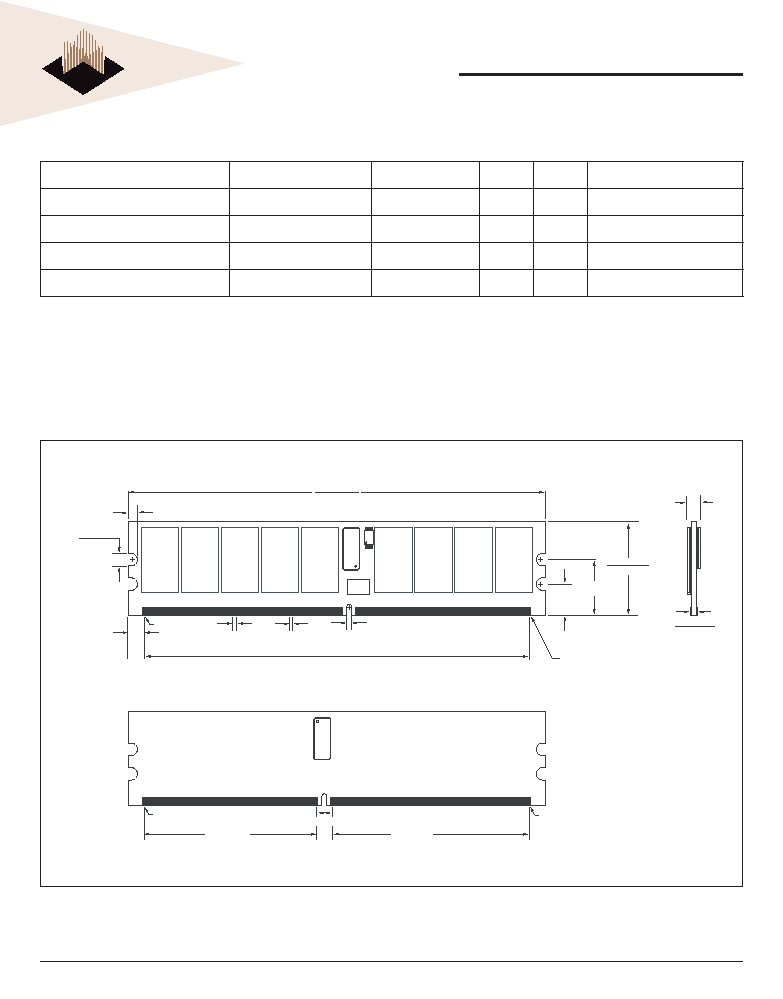

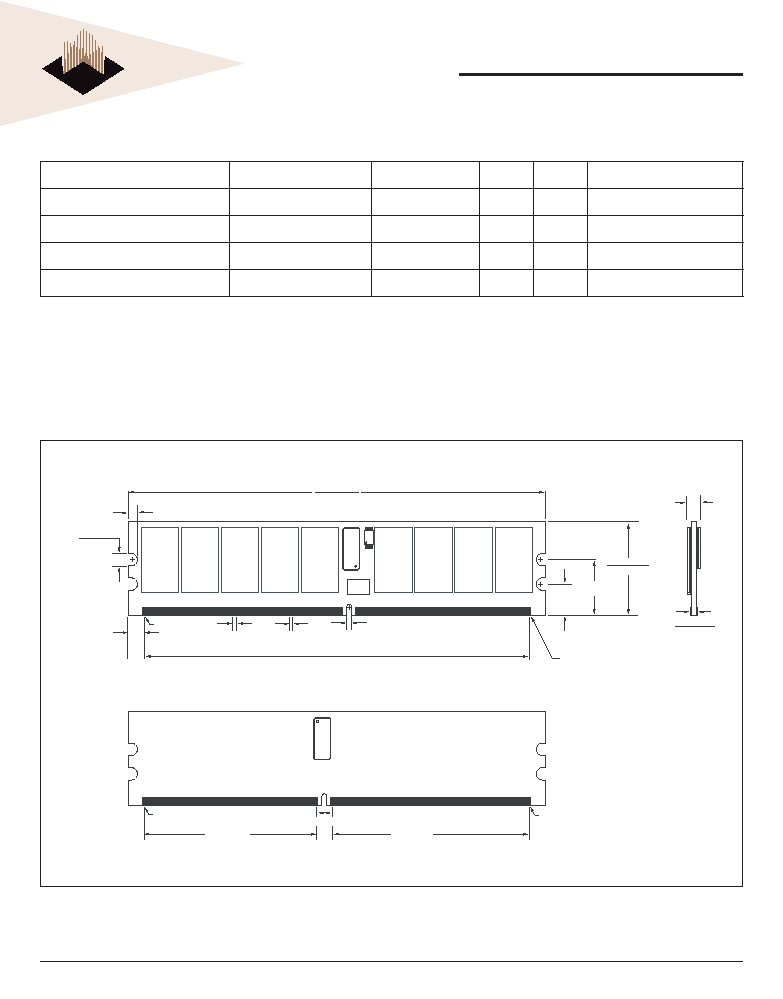

30.50 (1.201)

29.85 (1.175)

PIN 1

17.80 (0.700)

TYP.

5.0 (0.197) TYP.

123.0 (4.843)

TYP.

1.0 (0.039)

TYP.

0.80 (0.032)

TYP.

4.00 (0.158)

(4X)

PIN 120

FRONT VIEW

133.50 (5.256)

133.20 (5.244)

63.0 (2.480)

TYP.

55.0 (2.165)

TYP.

10.00(0.394 )

TYP.

BACK VIEW

PIN 240

PIN 121

1.37 (0.054)

1.17 (0.046)

4.0 (0.158)

MAX

1.50 (0.059)

3.00 (0.118)

(4X)

5.175 (0.204)

(2X)

PACKAGE DIMENSIONS FOR D6

* ALL DIMENSIONS ARE IN MILLIMETERS AND (INCHES)

ORDERING INFORMATION FOR D6

Part Number

Speed

CAS Latency

t

RCD

t

RP

Height*

WV3HG64M72EER806D6

400MHz/800Mb/s

6

6

6

30.00mm (1.181") TYP

WV3HG64M72EER665D6

333MHz/667Mb/s

5

5

5

30.00mm (1.181") TYP

WV3HG64M72EER534D6

266MHz/533Mb/s

4

4

4

30.00mm (1.181") TYP

WV3HG64M72EER403D6

200MHz/400Mb/s

3

3

3

30.00mm (1.181") TYP

NOTES:

∑ RoHS products. ("G" = RoHS Compliant)

∑

Vendor

specifi c part numbers are used to provide memory component source control. The place holder for this is shown as a lower case "x"

in the part numbers above and is to be replaced with respective vendors code. Consult factory for qualifi ed sourcing options.

(M = Micron, S = Samsung & consult factory for others)

∑ Consult factory for availability of industrial temperature (-40∞C to 85∞C) option

WV3HG64M72EER-D6

ADVANCED

10

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

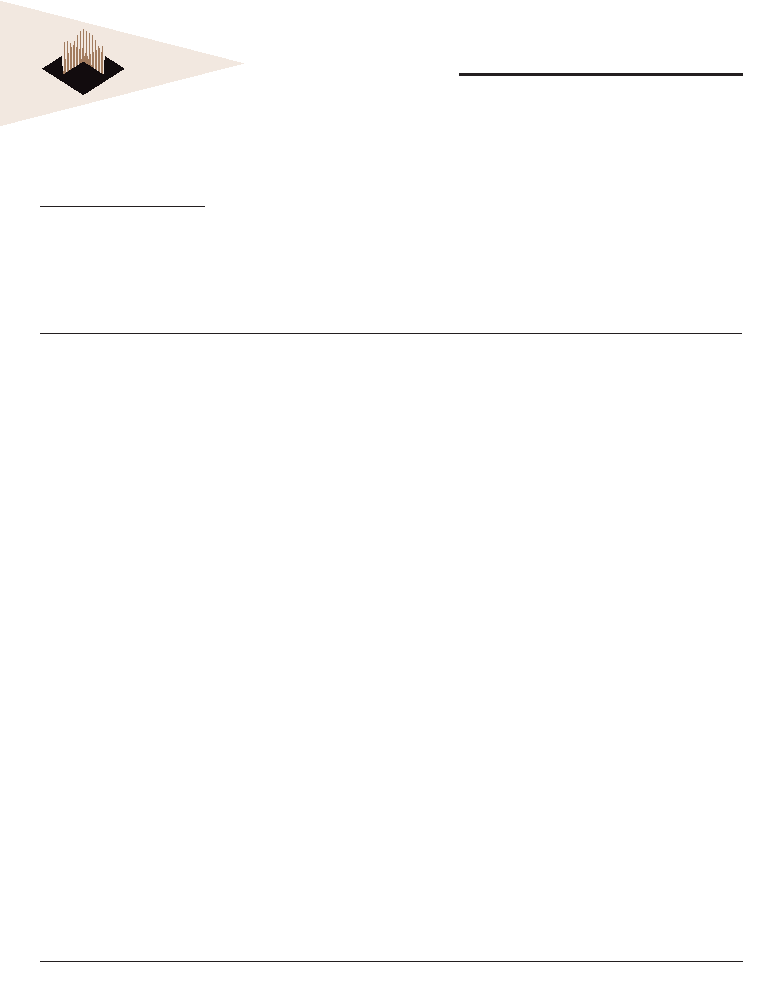

PART NUMBERING GUIDE

WV 3 H G 64M 72 E E R xxx D6 x x G

WEDC

MEMORY

DDR 2

GOLD

DEPTH

BUS WIDTH

x8

1.8V

REGISTERED

SPEED (Mb/s)

PACKAGE 240 PIN

INDUSTRIAL TEMP OPTION

(For commercial leave "blank"

for industrial add "I")

COMPONENT VENDOR NAME

(M = Micron)

(S = Samsung)

G = RoHS COMPLIANT

WV3HG64M72EER-D6

ADVANCED

11

White Electronic Designs Corporation ∑ (602) 437-1520 ∑ www.wedc.com

White Electronic Designs

August 2006

Rev. 1

Document Title

512MB ≠ 64Mx72 DDR2 SDRAM REGISTERED, w/PLL

DRAM DIE OPTIONS:

∑

SAMSUNG: C-Die, will move to E-Die Q2'06

∑

MICRON: U37: B-Die

Revision History

Rev #

History

Release Date Status

Rev 0

Created

August 2006

Concept

Rev 1

1.0 Moved to Advanced

August 14 2006

Advanced