128K x 8 Static RAM

WCFS1008V1C

Revised April 19, 2002

S1008V1C

Features

∑ High speed

-- t

AA

= 12ns

∑ CMOS for optimum speed/power

∑ Center power/ground pinout

∑ Automatic power-down when deselected

∑ Easy memory expansion with CE

and OE options

Functional Description

The WCFS1008V1C is a high-performance CMOS static RAM

organized as 131,072 words by 8 bits. Easy memory expan-

sion is provided by an active LOW Chip Enable (CE), an active

LOW Output Enable (OE), and three-state drivers. This device

has an automatic power-down feature that significantly reduc-

es power consumption when deselected.

Writing to the device is accomplished by taking Chip Enable

(CE) and Write Enable (WE) inputs LOW. Data on the eight I/O

pins (I/O

0

through I/O

7

) is then written into the location speci-

fied on the address pins (A

0

through A

16

).

Reading from the device is accomplished by taking Chip

Enable (CE) and Output Enable (OE) LOW while forcing Write

Enable (WE) HIGH. Under these conditions, the contents of

the memory location specified by the address pins will appear

on the I/O pins.

The eight input/output pins (I/O

0

through I/O

7

) are placed in a

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), or during a write

operation (CE LOW, and WE LOW).

The WCFS1008V1C is available in standard 400-mil-wide

package.

Selection Guide

WCFS1008V1C 12ns

Maximum Access Time (ns)

12

Maximum Operating Current (mA)

160

Maximum Standby Current (mA)

5

14

15

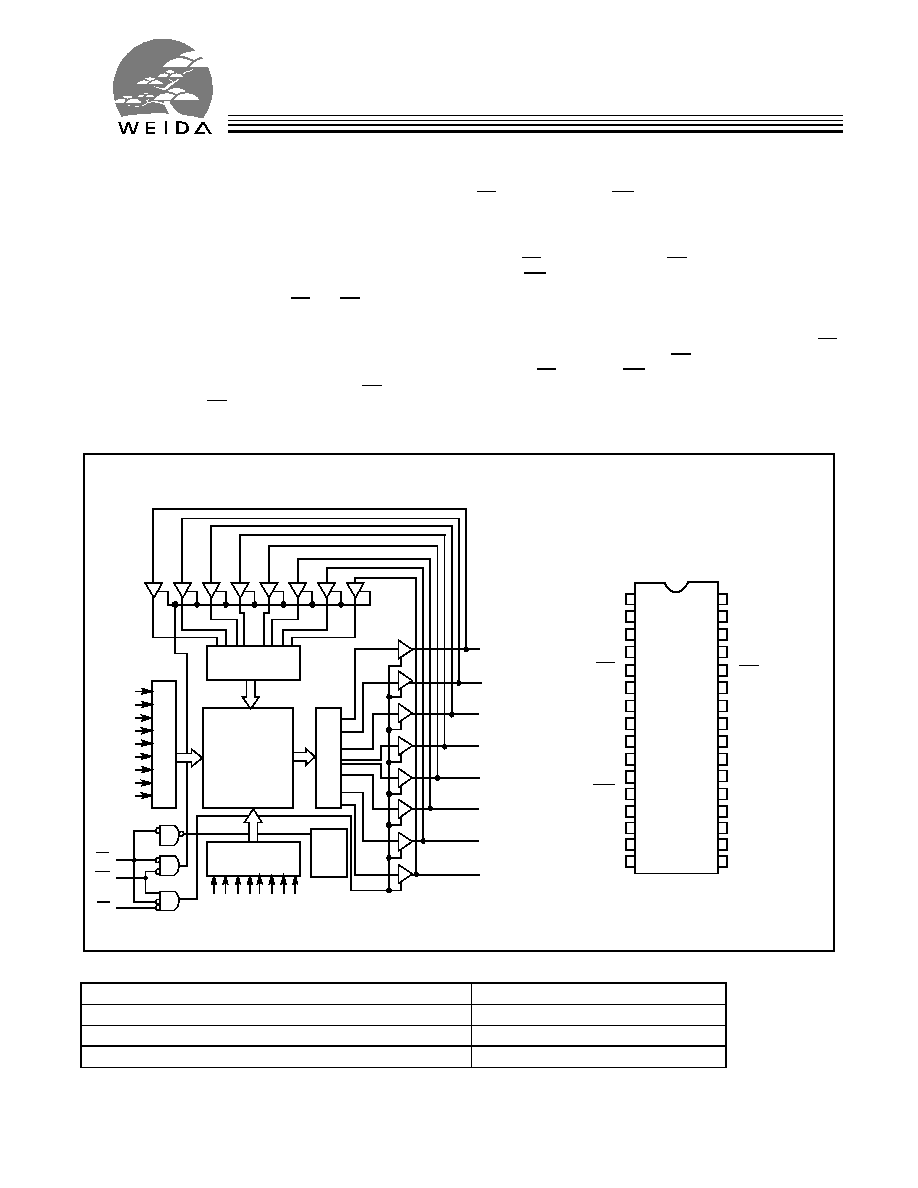

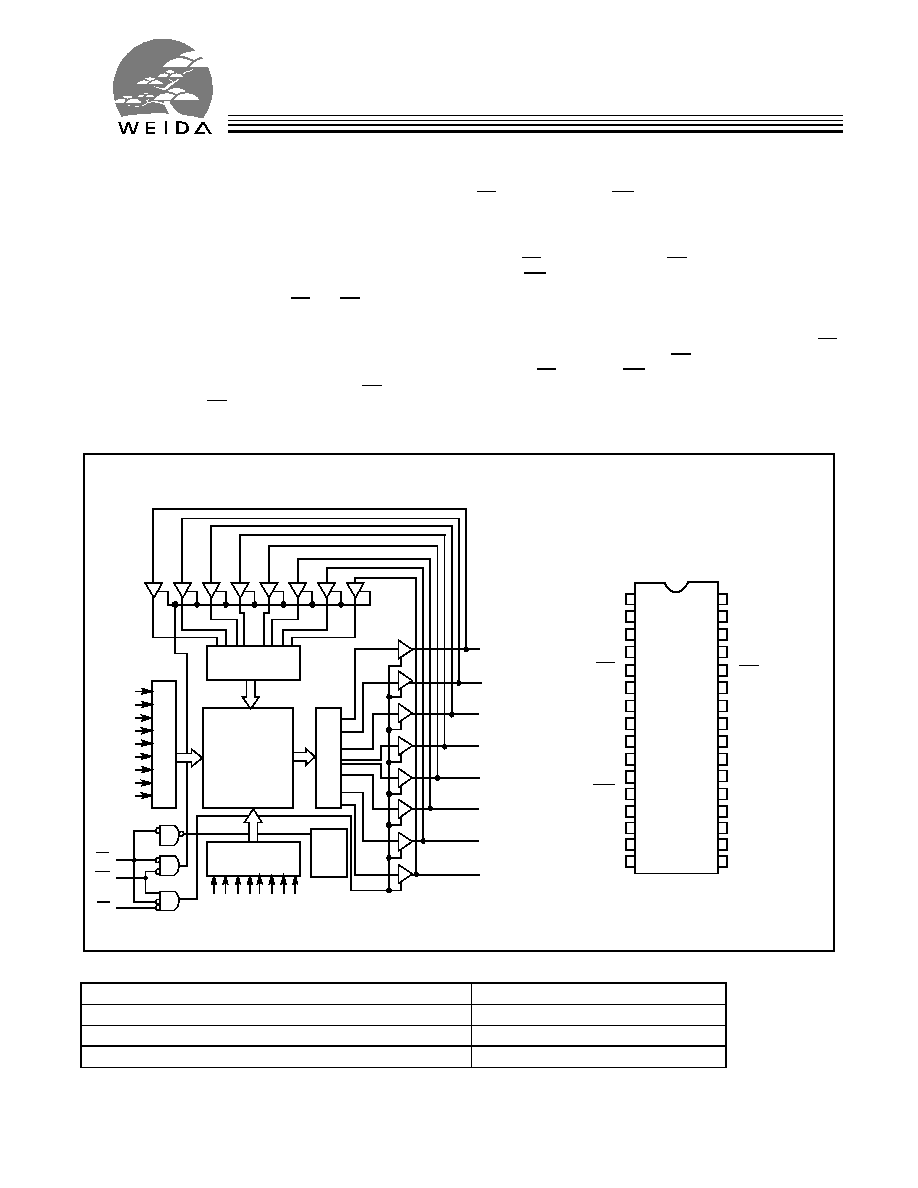

Logic Block Diagram

Pin Configurations

A

1

A

2

A

3

A

4

A

5

A

6

A

7

A

8

COLUMN

DECODER

RO

W

DECODER

SE

N

S

E A

M

P

S

INPUT BUFFER

POWER

DOWN

WE

OE

I/O0

I/O1

I/O2

I/O3

512 x 256 x 8

ARRAY

I/O7

I/O6

I/O5

I/O4

A

0

A

11

A

13

A

12

A

A

10

CE

A

A

16

A

9

1

2

3

4

5

6

7

8

9

10

11

14

19

20

24

23

22

21

25

28

27

26

Top View

SOJ

12

13

29

32

31

30

16

15

17

18

A

7

A

1

A

2

A

3

CE

I/O

0

I/O

1

V

CC

A

13

A

16

A

15

OE

I/O

7

I/O

6

A

12

A

11

A

10

A

9

I/O

2

A

0

A

4

A

5

A

6

I/O

4

V

CC

I/O

5

A

8

I/O

3

WE

V

SS

A

14

V

SS

WCFS1008V1C

2

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature ................................. ≠65∞C to +150∞C

Ambient Temperature with

Power Applied............................................. ≠55∞C to +125∞C

Supply Voltage on V

CC

to Relative GND

[1]

.... ≠0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State

[1]

....................................≠0.5V to V

CC

+ 0.5V

DC Input Voltage

[1]

.................................≠0.5V to V

CC

+ 0.5V

Current into Outputs (LOW) ........................................ 20 mA

Static Discharge Voltage............................................ >2001V

(per MIL-STD-883, Method 3015)

Latch-Up Current ..................................................... >200 mA

Operating Range

Range

Ambient

Temperature

[2]

V

CC

Commercial

0∞C to +70∞C

3.3V

±

10%

Electrical Characteristics

Over the Operating Range

Test Conditions

WCFS1008V1C 12ns

Parameter

Description

Min.

Max.

Unit

V

OH

Output HIGH Voltage

V

CC

= Min.,

I

OH

= ≠ 4.0 mA

2.4

V

V

OL

Output LOW Voltage

V

CC

= Min.,

I

OL

= 8.0 mA

0.4

V

V

IH

Input HIGH Voltage

2.2

V

CC

+ 0.3

V

V

IL

Input LOW Voltage

[1]

≠0.3

0.8

V

I

IX

Input Load Current

GND < V

I

< V

CC

≠1

+1

µ

A

I

OZ

Output Leakage

Current

GND < V

I

< V

CC

,

Output Disabled

≠5

+5

µ

A

I

CC

V

CC

Operating

Supply Current

V

CC

= Max.,

I

OUT

= 0 mA,

f = f

MAX

= 1/t

RC

160

mA

I

SB1

Automatic CE

Power-Down Current

--TTL Inputs

Max. V

CC

, CE > V

IH

V

IN

> V

IH

or

V

IN

< V

IL

, f = f

MAX

20

mA

I

SB2

Automatic CE

Power-Down Current

--CMOS Inputs

Max. V

CC

,

CE > V

CC

≠ 0.3V,

V

IN

> V

CC

≠ 0.3V,

or V

IN

< 0.3V, f = 0

5

mA

Capacitance

[3]

Parameter

Description

Test Conditions

Max.

Unit

C

IN

Input Capacitance

T

A

= 25∞C, f = 1 MHz,

V

CC

= 5.0V

6

pF

C

OUT

Output Capacitance

8

pF

Notes:

1.

V

IL

(min.) = ≠2.0V for pulse durations of less than 20 ns.

2.

T

A

is the "Instant On" case temperature.

3.

Tested initially and after any design or process changes that may affect these parameters.

WCFS1008V1C

3

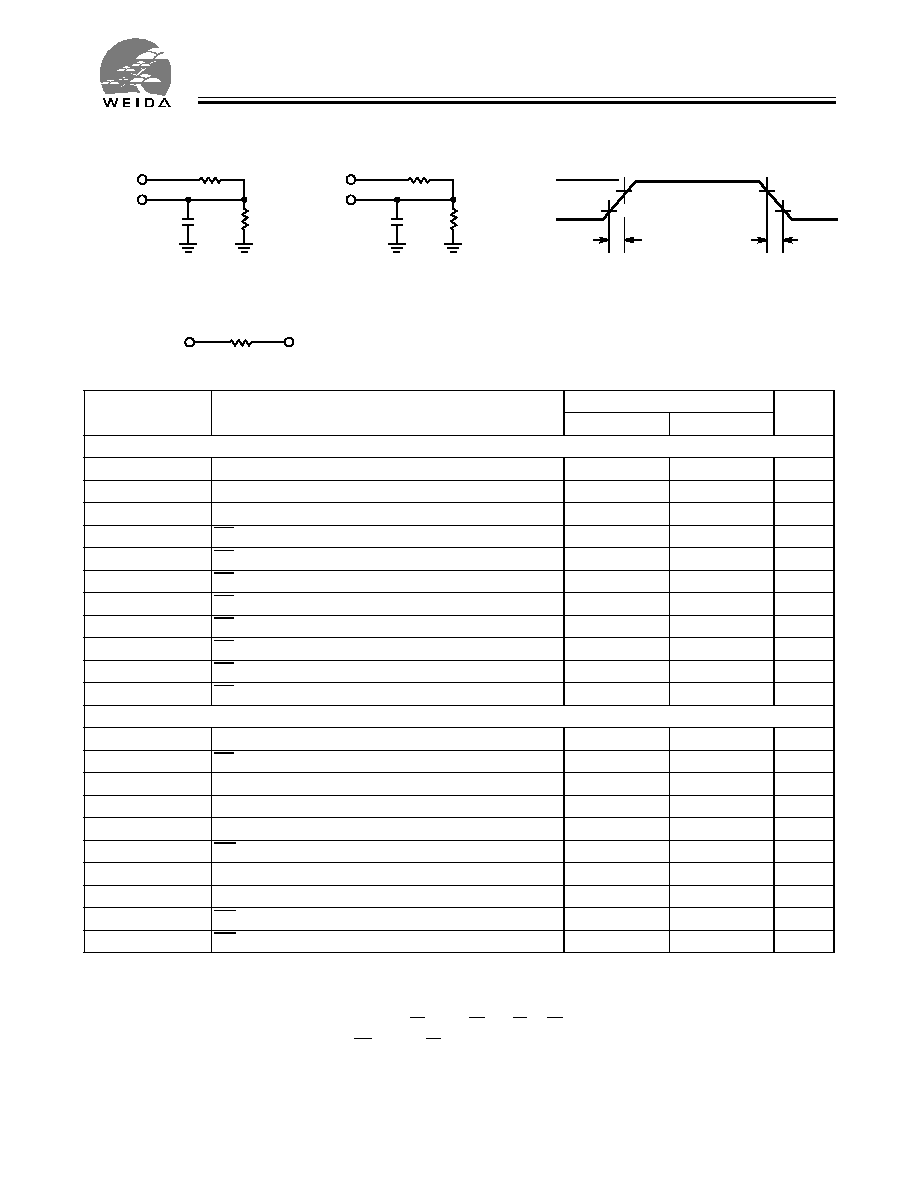

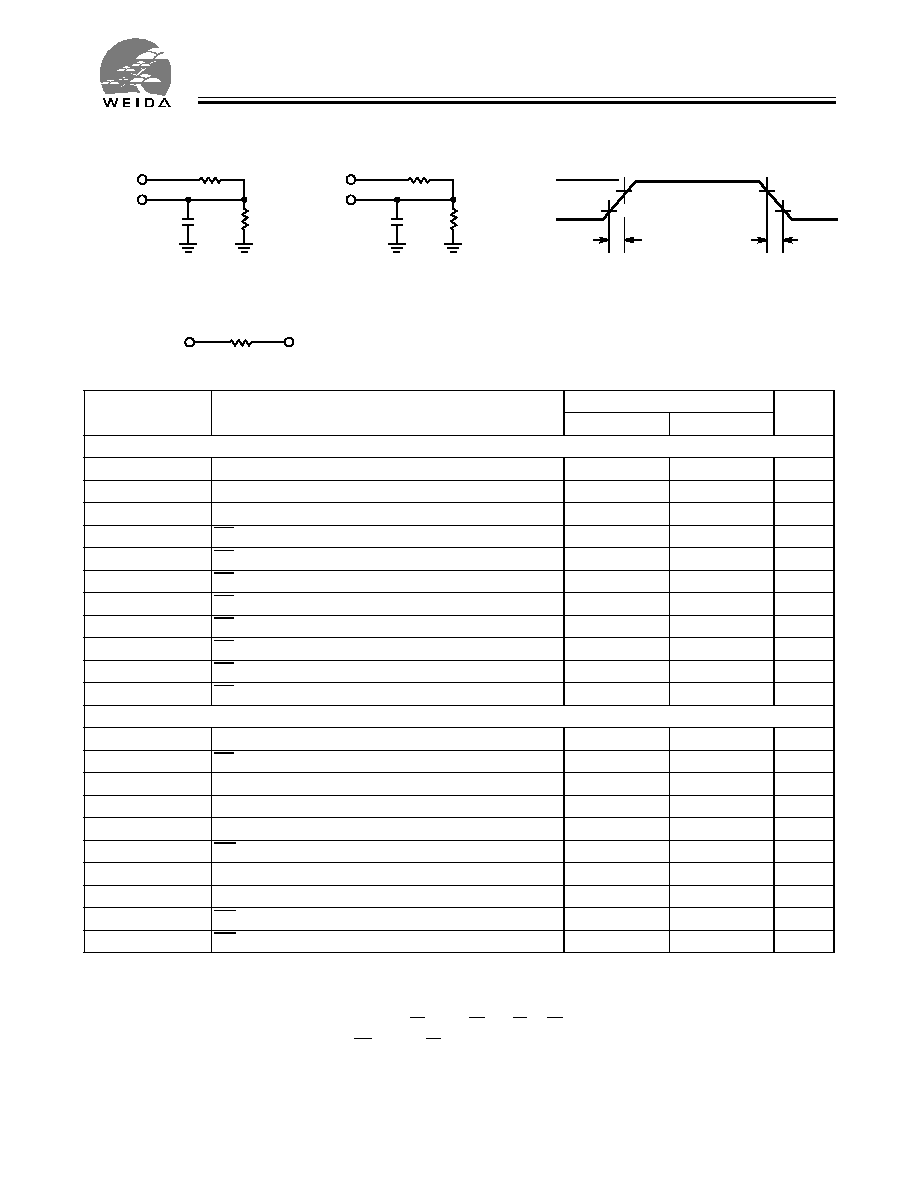

AC Test Loads and Waveforms

90%

10%

3.0V

GND

90%

10%

ALL INPUT PULSES

3.3V

OUTPUT

30 pF

INCLUDING

JIG AND

SCOPE

3.3V

OUTPUT

5 pF

INCLUDING

JIG AND

SCOPE

(a)

(b)

3 ns

3 ns

OUTPUT

R1 480

R1 480

R2

255

R2

255

167

Equivalent to:

VENIN EQUIVALENT

1.73V

TH…

Switching Characteristics

[4]

Over the Operating Range

WCFS1008V1C 12ns

Parameter

Description

Min.

Max.

Unit

READ CYCLE

t

RC

Read Cycle Time

12

ns

t

AA

Address to Data Valid

12

ns

t

OHA

Data Hold from Address Change

3

ns

t

ACE

CE LOW to Data Valid

12

ns

t

DOE

OE LOW to Data Valid

6

ns

t

LZOE

OE LOW to Low Z

0

ns

t

HZOE

OE HIGH to High Z

[5, 6]

6

ns

t

LZCE

CE LOW to Low Z

[6]

3

ns

t

HZCE

CE HIGH to High Z

[5, 6]

6

ns

t

PU

CE LOW to Power-Up

0

ns

t

PD

CE HIGH to Power-Down

12

ns

WRITE CYCLE

[7, 8]

t

WC

Write Cycle Time

12

ns

t

SCE

CE LOW to Write End

9

ns

t

AW

Address Set-Up to Write End

8

ns

t

HA

Address Hold from Write End

0

ns

t

SA

Address Set-Up to Write Start

0

ns

t

PWE

WE Pulse Width

8

ns

t

SD

Data Set-Up to Write End

6

ns

t

HD

Data Hold from Write End

0

ns

t

LZWE

WE HIGH to Low Z

[6]

3

ns

t

HZWE

WE LOW to High Z

[5, 6]

6

ns

Notes:

4.

Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified

I

OL

/I

OH

and 30-pF load capacitance.

5.

t

HZOE

, t

HZCE

, and t

HZWE

are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured

±

500 mV from steady-state voltage.

6.

At any given temperature and voltage condition, t

HZCE

is less than t

LZCE

, t

HZOE

is less than t

LZOE

, and t

HZWE

is less than t

LZWE

for any given device.

7.

The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. CE and WE must be LOW to initiate a write, and the transition of any of these

signals can terminate the write. The input data set-up and hold timing should be referenced to the leading edge of the signal that terminates the write.

8.

The minimum write cycle time for Write Cycle no. 3 (WE controlled, OE LOW) is the sum of t

HZWE

and t

SD

.

WCFS1008V1C

4

Data Retention Characteristics

Over the Operating Range

Parameter

Description

Conditions

Min.

Max.

Unit

V

DR

V

CC

for Data Retention

No input may exceed V

CC

+ 0.5V

V

CC

= V

DR

= 2.0V,

CE > V

CC

≠ 0.3V,

V

IN

> V

CC

≠ 0.3V or V

IN

< 0.3V

2.0

V

t

CDR

[3]

Chip Deselect to Data Retention Time

0

ns

t

R

Operation Recovery Time

200

µ

s

Data Retention Waveform

3.0V

3.0V

t

CDR

V

DR

> 2V

DATA RETENTION MODE

t

R

CE

V

CC

Switching Waveforms

Read Cycle No. 1

[9, 10]

Read Cycle No. 2 (OE Controlled)

[10, 11]

Notes:

9.

Device is continuously selected. OE, CE = V

IL

.

10. WE is HIGH for read cycle.

11. Address valid prior to or coincident with CE transition LOW.

PREVIOUS DATA VALID

DATA VALID

t

RC

t

AA

t

OHA

ADDRESS

DATA OUT

50%

50%

DATA VALID

t

RC

t

ACE

t

DOE

t

LZOE

t

LZCE

t

PU

HIGH IMPEDANCE

t

HZOE

t

HZCE

t

PD

HIGH

OE

CE

ICC

ISB

IMPEDANCE

ADDRESS

DATA OUT

V

CC

SUPPLY

CURRENT

WCFS1008V1C

5

Write Cycle No. 1 (CE Controlled)

[12, 13]

Write Cycle No. 2 (WE Controlled, OE HIGH During Write)

[12, 13]

Notes:

12. Data I/O is high impedance if OE = V

IH

.

13. If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high-impedance state.

14. During this period the I/Os are in the output state and input signals should not be applied.

Switching Waveforms

(continued)

t

WC

DATA VALID

t

AW

t

SA

t

PWE

t

HA

t

HD

t

SD

t

SCE

t

SCE

CE

ADDRESS

WE

DATA I/O

t

HD

t

SD

t

PWE

t

SA

t

HA

t

AW

t

SCE

t

WC

t

HZOE

DATA

IN

VALID

CE

ADDRESS

WE

DATA I/O

OE

NOTE

14

WCFS1008V1C

6

Write Cycle No. 3 (WE Controlled, OE LOW)

[13]

Switching Waveforms

(continued)

DATA VALID

t

HD

t

SD

t

LZWE

t

PWE

t

SA

t

HA

t

AW

t

SCE

t

WC

t

HZWE

CE

ADDRESS

WE

DATA I/O

NOTE

14

Truth Table

CE

OE

WE

I/O

0

≠I/O

7

Mode

Power

H

X

X

High Z

Power-Down

Standby (I

SB

)

X

X

X

High Z

Power-Down

Standby (I

SB

)

L

L

H

Data Out

Read

Active (I

CC

)

L

X

L

Data In

Write

Active (I

CC

)

L

H

H

High Z

Selected, Outputs Disabled

Active (I

CC

)

Ordering Information

Speed

(ns)

Ordering Code

Package

Name

Package Type

Operating

Range

12

WCFS1008V1C-JC12

J

32-Lead 300-Mil Molded SOJ

Commercial

WCFS1008V1C

7

Package Diagram

51-85041-A

32-Lead (400-Mil) Molded SOJ J

WCFS1008V1C

8

Document Title: WCFS1008V1C 128K x 8 Static RAM

REV.

Issue Date

Orig. of Change

Description of Change

**

4/15/02

XFL

New Datasheet