| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 15102EI | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PRELIMINARY

Publication Release Date: October, 2003

- 1 -

Revision 0.2

ISD5100 SERIES

SINGLE-CHIP

1 TO 16 MINUTES DURATION

VOICE RECORD/PLAYBACK DEVICES

WITH DIGITAL STORAGE CAPABILITY

ISD5100 ≠ SERIES

- 2 -

1. GENERAL DESCRIPTION

The ISD5100 ChipCorder

Series provide high quality, fully integrated, single-chip Record/Playback

solutions for 1- to 16-minute messaging applications that are ideal for use in cellular phones,

automotive communications, GPS/navigation systems and other portable products. The ISD5100

Series products are an enhancement of the ISD5000 architecture, providing: 1) the I

2

C serial port -

address, control and duration selection are accomplished through an I

2

C interface to minimize pin

count (ONLY two control lines required); 2) the capability of storing digital data, in addition to analog

data. This feature allows customers to store phone numbers, system configuration parameters and

message address locations for message management capability; 3) Various internal circuit blocks can

be individually powered-up or -down for power saving.

The ISD5100 Series include:

∑ ISD5116 from 8 to 16 minutes

∑ ISD5108 from 4 to 8 minutes

∑ ISD5104 from 2 to 4 minutes

∑ ISD5102 from 1 to 2 minutes

Analog functions and audio gating have also been integrated into the ISD5100 Series products to

allow easy interface with integrated digital cellular chip sets on the market. Audio paths have been

designed to enable full duplex conversation record, voice memo, answering machine (including

outgoing message playback) and call screening features. This product enables playback of messages

while the phone is in standby, AND both simplex and duplex playback of messages while on a phone

call.

Additional voice storage features for digital cellular phones include: 1) a personalized outgoing

message can be sent to the person by getting caller-ID information from the host chipset, 2) a private

call announce while on call can be heard from the host by giving caller-ID on call waiting information

from the host chipset.

Logic Interface Options of 2.0V and 3.0V are supported by the ISD5100 Series to accommodate

portable communication products (2.0- and 3.0-volt required).

Like other ChipCorder

Æ

products, the ISD5100 Series integrate the sampling clock, anti-aliasing and

smoothing filters, and the multi-level storage array on a single-chip. For enhanced voice features, the

ISD5100 Series eliminate external circuitry by integrating automatic gain control (AGC), a power

amplifier/speaker driver, volume control, summing amplifiers, analog switches, and a car kit interface.

Input level adjustable amplifiers are also included, providing a flexible interface for multiple

applications.

Recordings are stored into on-chip nonvolatile memory cells, providing zero-power message storage.

This unique, single-chip solution is made possible through Winbond's patented multilevel storage

technology. Voice and audio signals are stored directly into solid-state memory in their natural,

uncompressed form, providing superior quality on voice and music reproduction.

ISD5100 ≠ SERIES

Publication Release Date: October, 2003

- 3 -

Revision 0.2

2. FEATURES

Fully-Integrated Solution

∑

Single-chip voice record/playback solution

∑

Dual storage of digital and analog data

∑

Durations

8 to 16-minute (ISD5116)

4 to

8-minute (ISD5108)

2 to

4-minute (ISD5104)

1 to

2-minute (ISD5102)

Low Power Consumption

∑

+2.7 to +3.3V (V

CC

) Supply Voltage

∑

Supports 2.0V and 3.0V interface logic

∑

Operating Current:

I

CC Play

= 15 mA (typical)

I

CC Rec

= 30 mA (typical)

I

CC Feedthrough

= 12 mA (typical)

∑

Standby Current:

I

SB

= 1

µA (typical)

∑

Most stages can be individually powered down to minimize power consumption

Enhanced Voice Features

∑

One or two-way conversation record

∑

One or two-way message playback

∑

Voice memo record and playback

∑

Private call screening

∑

In-terminal answering machine

∑

Personalized outgoing message

∑

Private call announce while on call

Digital Memory Features

∑

Up to 4 Mb available (ISD5116)

∑

Up to 2 Mb available (ISD5108)

∑

Up to 1 Mb available (ISD5104)

∑

Up to 512Kb available (ISD5102)

∑

Storage of phone numbers, system configuration parameters and message address table in cellular

application

Easy-to-use and Control

∑

No compression algorithm development required

∑

User-controllable sampling rates

∑

Programmable analog interface

∑

Standard & Fast mode I

2

C serial interface (100kHz ≠ 400 kHz)

∑

Fully addressable for multiple messages

High Quality Solution

∑

High quality voice and music reproduction

∑

Winbond's standard 100-year message retention (typical)

∑

100K record cycles (typical) for analog data

∑

10K record cycles (typical) for digital data

Options

∑

Available in die form, TSOP and SOIC and PDIP (ISD5116 Only)

∑

Temperature: Commercial ≠ Packaged (0 to +70∞C) & die (0 to +50∞C); Industrial (-40 to +85∞C)

ISD5100 ≠ SERIES

- 4 -

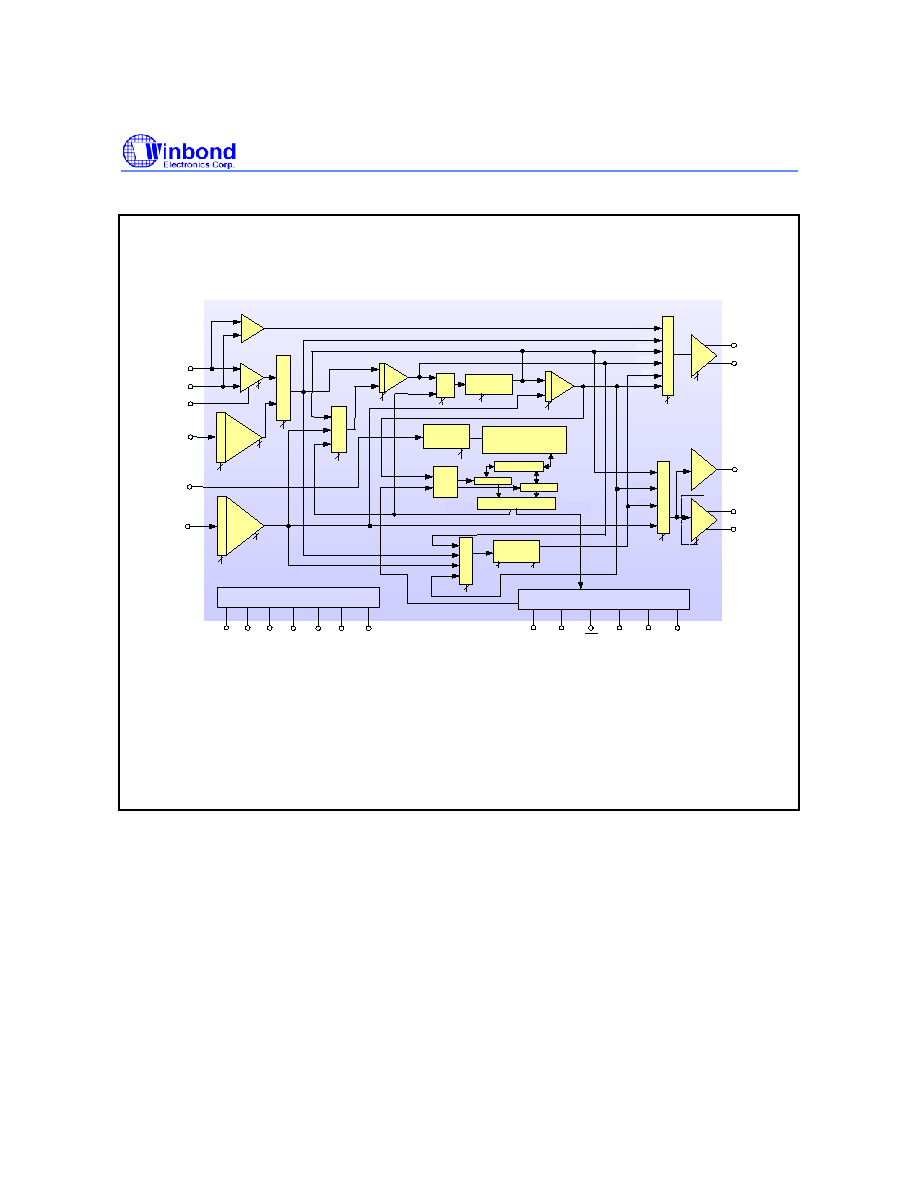

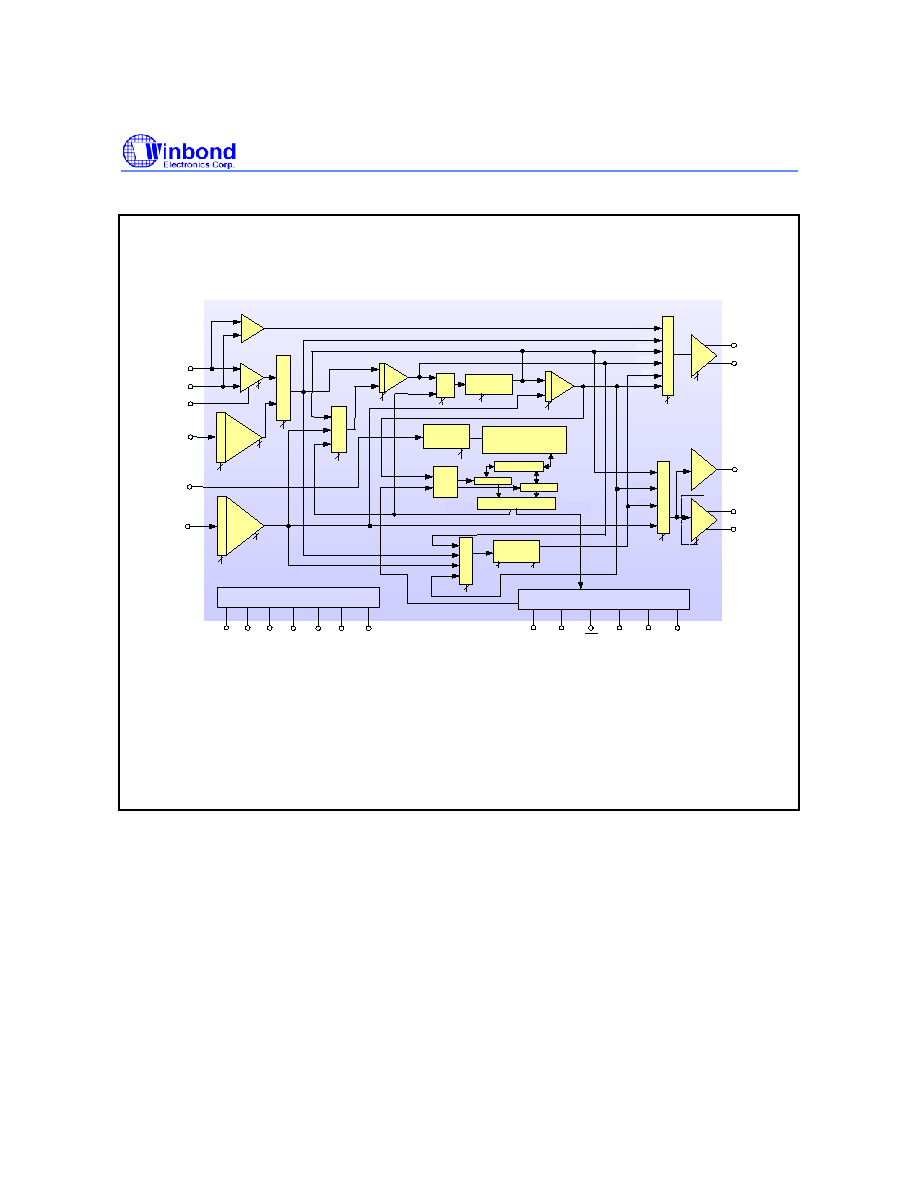

3. BLOCK DIAGRAM

ISD5100-Series Block Diagram

AUX IN

AMP

1.

0 /

1.

4 /

2.

0 /

2.

8

AGC

SU

M1

MU

X

Vo

l

MU

X

Filt

e

r

MU

X

Low Pass

Filter

SUM1

FTHRU

INP

ANA O

U

T

M

U

X

VOL

SUM2

ANA IN

VOL

SP+

SP-

SPEAKER

AUX OUT

ANA OUT-

ANA OUT+

MIC+

MIC -

AGCCAP

MICROPHONE

AUX IN

XCLK

ANA IN

V

SSA

V

CCA

V

SSA

V

SSD

V

SSD

V

CCD

V

CCD

64-bit/samp.

ARRAY OUTPUT MUX

ARRAY

IN

P

U

T

MU

X

Input

S

our

c

e

M

U

X

Array I/O Mux

FILTO

SUM1

INP

ANA IN

SUM2

FILTO

SUM2

SUM1

Summing

AMP

ANA IN

AMP

0.

625/

0.

883/

1.

25/

1.

76

6dB

SUM2

Summing

AMP

Out

put

M

U

X

Volume

Control

MIC IN

AUX IN

FILTO

ANA IN

SUM1

ANA IN

FILTO

SUM2

(ANALOG)

ARRAY

INP

SUM1 MUX

CTRL

(DIGITAL)

64-bit/samp.

ARRAY OUT

(ANALOG)

ARRAY OUT

(DIGITAL)

ARRAY

Spkr

.

AMP

AUX

OUT

AMP

Power Conditioning

RAC

INT

SDA

SCL

A1

A0

Device Control

Internal

Clock

Multilevel/Digital

Storage Array

ANA

OUT

AMP

2

( )

VLS0

VLS1

2

( )

AIG0

AIG1

2

( )

AXG0

AXG1

2

( )

S1S0

S1S1

2

( )

S1M0

S1M1

2

( )

S2M0

S2M1

( )

OPA0

OPA1

2

( )

OPS0

OPS1

2

( )

FLD0

FLD1

2

(INS0)

1

1

(AXPD)

1

(AGPD)

1

(FLPD)

1

(FLS0)

1

(AIPD)

1

(AOPD)

( )

3

AOS0

AOS1

AOS2

3

( )

VOL0

VOL1

VOL2

1

(V

LPD

)

ISD5100 ≠ SERIES

Publication Release Date: October, 2003

- 5 -

Revision 0.2

4. TABLE OF CONTENTS

1. GENERAL DESCRIPTION...................................................................................................................2

2. FEATURES ..........................................................................................................................................3

3. BLOCK DIAGRAM................................................................................................................................4

4. TABLE OF CONTENTS .......................................................................................................................5

5. PIN CONFIGURATION ........................................................................................................................7

6. PIN DESCRIPTION ..............................................................................................................................8

7. FUNCTIONAL DESCRIPTION.............................................................................................................9

7.1. Overview ........................................................................................................................................9

7.1.1 Speech/Voice Quality...............................................................................................................9

7.1.2. Duration...................................................................................................................................9

7.1.3. Flash Technology....................................................................................................................9

7.1.4. Microcontroller Interface..........................................................................................................9

7.1.5. Programming.........................................................................................................................10

7.2. Functional Details ........................................................................................................................10

7.2.1. Internal Registers ..................................................................................................................11

7.2.2. Memory Architecture .............................................................................................................11

7.3. Operational Modes Description ...................................................................................................12

7.3.1. I

2

C Interface ..........................................................................................................................12

7.3.2. I

2

C Control Registers ............................................................................................................16

7.3.3. Opcode Summary .................................................................................................................17

7.3.4. Data Bytes.............................................................................................................................19

7.3.5. Configuration Resiter Bytes ..................................................................................................20

7.3.6. Power-up Sequence..............................................................................................................21

7.3.7. Feed Through Mode..............................................................................................................22

7.3.8. Call Record............................................................................................................................24

7.3.9. Memo Record........................................................................................................................25

7.3.10. Memo and Call Playback ....................................................................................................26

7.3.11. Message Cueing .................................................................................................................27

7.4. Analog Mode................................................................................................................................28

7.4.1. Aux In and Ana In Description...............................................................................................28

7.4.2. ISD5100 Series Analog Structure (left half) Description.......................................................29

7.4.3. ISD5100 Series Aanalog Structure (right half) Description ..................................................30

7.4.4. Volume Control Description ..................................................................................................31

7.4.5. Speaker and Aux Out Description.........................................................................................32