W742E/C811

4-BIT MICROCONTROLLER

Publication Release Date: December 2000

- 1 - Revision A1

Table of Contents-

1.

GENERAL DESCRIPTION .............................................................................................................3

2.

FEATURES.....................................................................................................................................3

3.

PIN CONFIGURATION...................................................................................................................5

3.1

W742C811 PAD List .........................................................................................................6

4.

PIN DESCRIPTION ........................................................................................................................9

5.

FUNCTIONAL DESCRIPTION .....................................................................................................11

5.1

Program Counter (PC) ....................................................................................................11

5.2

Stack Register (STACK)..................................................................................................11

5.3

Program Memory (ROM) .................................................................................................12

5.3.1

ROM Page Register (ROMPR) .........................................................................................13

5.3.2

ROM Addressing Mode ....................................................................................................13

5.4

Data Memory (RAM)........................................................................................................15

5.4.1

Architecture ......................................................................................................................15

5.4.2

RAM Page Register (PAGE).............................................................................................15

5.4.3

WR Page Register (WRP)................................................................................................16

5.4.4

Data Bank Register (DBKRH, DBKRL).............................................................................17

5.4.5

RAM Addressing Mode .....................................................................................................18

5.5

Accumulator (ACC) .........................................................................................................19

5.6

Arithmetic and Logic Unit (ALU) ......................................................................................19

5.7

Main Oscillator.................................................................................................................19

5.8

Sub-oscillator...................................................................................................................20

5.9

Dividers............................................................................................................................20

5.10

Dual-clock Operation .......................................................................................................20

5.11

Watchdog Timer (WDT) ..................................................................................................21

5.12

Timer/Counter .................................................................................................................22

5.12.1

Timer 0 (TM0) .................................................................................................................22

5.12.2

Timer 1 (TM1) .................................................................................................................23

5.13

Mode Register 0 (MR0) ...................................................................................................25

5.13.1

Mode Register 1 (MR1) ..................................................................................................25

5.14

Interrupts .........................................................................................................................25

5.15

Stop Mode Operation ......................................................................................................27

5.15.1

Stop Mode Wake-up Enable Flag for RC and RD Port (SEF) ........................................27

5.16

Hold Mode Operation ......................................................................................................27

W742E/C811

- 2 -

5.16.1

Hold Mode Release Enable Flag (HEF, HEFD)..............................................................29

5.16.2

Interrupt Enable Flag (IEF) .............................................................................................29

5.16.3

Port Enable Flag (PEF, P1EF)........................................................................................30

5.16.4

Hold Mode Release Condition Flag (HCF, HCFD) .........................................................30

5.16.5

Event Flag (EVF,EVFD)..................................................................................................31

5.17

Reset Function ................................................................................................................32

5.18

Input/Output Ports RA, RB & P0......................................................................................32

5.18.1

Port Mode 0 Register (PM0) ...........................................................................................33

5.18.2

Port Mode 1 Register (PM1) ...........................................................................................34

5.18.3

Port Mode 2 Register (PM2) ...........................................................................................34

5.18.4

Port Mode 6 Register (PM6) ...........................................................................................34

5.18.5

Serial I/O Interface..........................................................................................................35

5.19

Input Ports RC .................................................................................................................37

5.19.1

Port Status Register 0 (PSR0)........................................................................................39

5.20

Input Ports RD .................................................................................................................39

5.20.1

Port Status Register 1 (PSR1)........................................................................................40

5.21

Output Port RE & RF .......................................................................................................41

5.22

Input Port P1....................................................................................................................41

5.23

DTMF Output Pin (DTMF) ...............................................................................................41

5.23.1

DTMF register.................................................................................................................42

5.23.2

Dual Tone Control Register (DTCR) ...............................................................................42

5.24

MFP Output Pin (MFP) ....................................................................................................42

5.25

LCD Controller/Driver ......................................................................................................44

5.25.1

LCD RAM addressing method ........................................................................................45

5.25.2

LCD voltage and contrast adjusting................................................................................46

5.25.3

SEG32-SEG39 using as DC output (NMOS open drain type) ........................................47

5.25.4

The output waveforms for the LCD driving mode ...........................................................47

6.

ABSOLUTE MAXIMUM RATINGS ...............................................................................................48

7.

DC CHARACTERISTICS..............................................................................................................48

8.

AC CHARACTERISTICS ..............................................................................................................49

9.

INSTRUCTION SET TABLE.........................................................................................................50

10.

PACKAGE DIMENSIONS .............................................................................................................59

W742E/C811

Publication Release Date: December 2000

- 3 - Revision A1

1. GENERAL DESCRIPTION

The W742E/C811 (W742C811 is mask type, W742E811 is electrical erasable EPROM type) is a high-

performance 4-bit microcontroller (

�

C) that built in 640-dot LCD driver. The device contains a 4-bit

ALU, two 8-bit timers, two dividers in dual-clock operation, a 40

�

16 LCD driver, ten 4-bit I/O ports

(including 2 output port for LED driving), multiple frequency output, and one channel DTMF generator.

There are also eleven interrupt sources and 16-level stack buffer. The W742E/C811 operates on very

low current and has three power reduction modes, hold mode, stop mode and slow mode, which help

to minimize power dissipation.

2. FEATURES

�

Operating Voltage

-

2.4V � 5.5V for mask type

-

2.4V � 4.8V for electrical erasable EPROM type

�

Dual-clock Operation

�

Main Oscillator

-

3.58 MHz or 400 KHz can be selected by code option

-

Crystal or RC oscillator can be selected by code option

�

Sub-oscillator

-

Connect to 32.768 KHz crystal only

�

Memory

-

16384(16K) x 16 bit program ROM (including 64K x 4 bit look-up table)

-

5120(5K) x 4 bit data RAM (including 16 nibbles x 16 pages working registers)

-

40 x 16 LCD data RAM

�

40 Input/Output Pins

-

Port for input only: 3 ports/12 pins

-

Input/output ports: 3 ports/12 pins

-

High sink current output port for LED driving: 2 port /8 pins

-

DC output port: 2 ports/ 8 pins (selected by code option)

�

Power-down Mode

-

Hold mode: no operation (main oscillator and sub-oscillator still operate)

-

Stop mode: no operation (main oscillator and sub-oscillator are stopped)

-

Slow mode: main oscillator is stopped, system is operated by the sub-oscillator (32.768 KHz)

W742E/C811

- 4 -

�

Eleven Interrupt Sources

-

Four internal interrupts (Divider0, Divider1, Timer 0, Timer 1)

-

Seven external interrupts (RC.0-3, P1.2 ( INT0 ), Serial Port, P1.3 ( INT1 ))

�

LCD Driver Output

-

40 segments x 16 commons

-

1/8 or 1/16 duty (selected by code option) 1/5 bias driving mode

-

Clock source should be the sub-oscillator clock in the dual-clock operation mode

-

8 level software LCD contrast adjusting

-

LCD operating voltage source could come from V

DD

or VLCD1 pin input

�

MFP Output Pin

-

Output is software controlled to generate modulating or nonmodulating frequency

-

Works as frequency output specified by Timer 1

-

Key tone generator

�

DTMF Output pin

-

Output is one channel Dual Tone Multi-Frequency signal for dialling

�

8-bit Serial I/O Interface

-

8-bit transmit/receive mode by internal or external clock source

�

Two Built-in 14-bit Frequency Dividers

-

Divider0: the clock source is the main oscillator (Fosc)

-

Divider1: the clock source is the sub-oscillator (Fs)

�

Two Built-in 8-bit Programmable Countdown Tmers

-

Timer 0: one of two internal clock frequencies (F

OSC

/4 or F

OSC

/1024) can be selected

-

Timer 1: with auto-reload function and one of two internal clock frequencies (F

OSC

or F

OSC

/64 or

Fs) can be selected (signal output through MFP pin)

�

Built-in 18/15-bit Watchdog Timer Selectable for System Reset, Enable/Disable by Code Option

�

Powerful Instruction Set

�

16-level Stack Buffer

�

Packaged in 100-pin QFP

W742E/C811

Publication Release Date: December 2000

- 5 - Revision A1

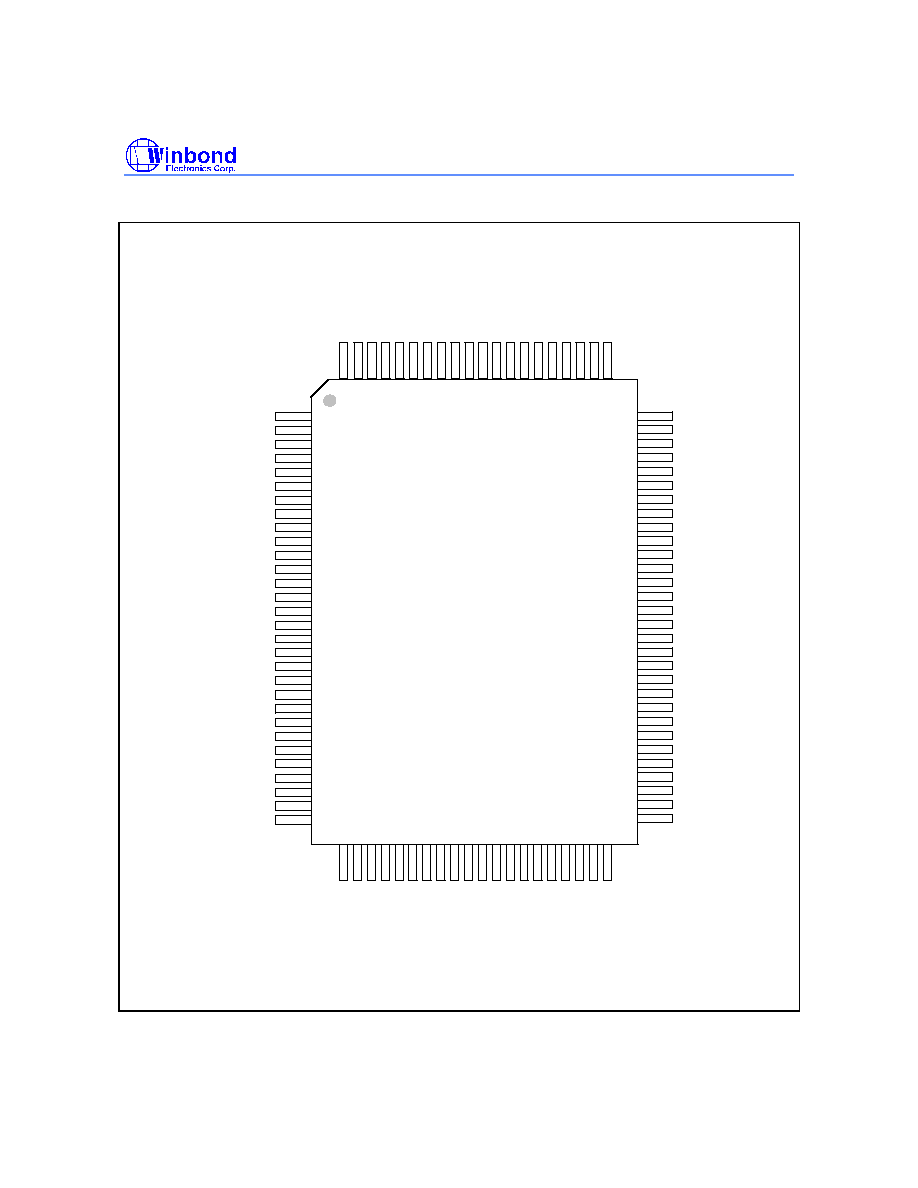

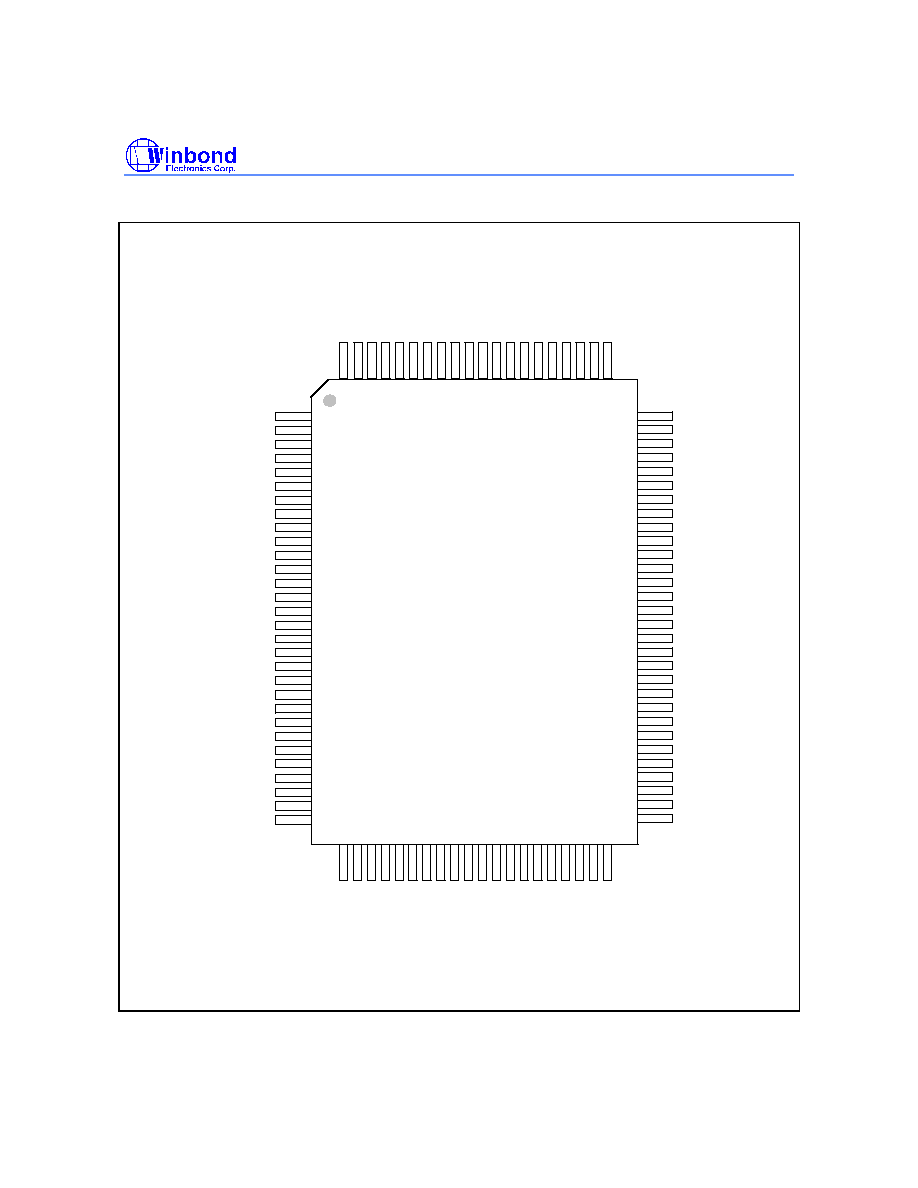

3. PIN CONFIGURATION

W742E/C811

4

5

6

7

8

9

10

11

12

13

14

15

16

17

1

2

3

18

19

9

7

8

9

0

1

2

3

4

5

6

7

8

9

20

21

22

23

24

0

1

2

3

3

3

3

4

5

3

3

3

6

3

7

8

3

3

9

0

4

51

52

53

54

55

56

57

58

59

60

61

62

63

64

0

6

5

25

26

27

28

29

30

4

1

2

3

4

5

6

7

8

9

4

4

4

4

4

4

4

4

5

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

1

2

3

4

8

8

8

8

8

8

8

8

8

9

9

9

9

9

9

9

9

9

1

0

S E G 3 5

S E G 3 6

S E G 3 7

S E G 3 8

C O M 1 5

S E G 3 9

C O M 1 4

C O M 1 2

C O M 1 1

C O M 0 8

P 0 1

P 0 0

P 1 1

P 1 2

P 1 3

C N

S E G 0 2

S E G 0 8

C P

V L C D 1

C O M 0 2

C O M 0 3

C O M 0 4

C O M 0 5

C O M 0 6

C O M 0 7

S E G 0 0

S

E

G

1

5

S

E

G

1

4

S

E

G

1

3

S

E

G

1

2

X

I

N

1

X

O

U

T

1

R

C

0

R

C

1

R

C

3

R

D

0

C O M 1 3

R

C

2

S

E

G

1

8

S

E

G

1

7

S

E

G

3

0

C O M 1 0

C O M 0 9

C O M 0 0

S

E

G

1

6

R

D

2

M F P

R

D

1

RA0

S E G 0 7

S

E

G

1

1

1 0 0 - p i n Q F P

C O M 0 1

S E G 3 2

S E G 3 1

S E G 3 3

S E G 3 4

RA2

RA3

R B 0

R B 1

R B 2

R B 3

X O U T 2

X I N 2

V S S

R

D

3

R

E

0

R

E

1

R

E

2

R

E

3

R

F

0

R

F

1

R

F

2

R

F

3

/

R

E

S

E

T

V

D

D

P 0 2

P 0 3

P 1 0

S E G 0 1

S E G 0 3

S E G 0 4

S E G 0 5

S E G 0 6

S E G 0 9

S E G 1 0

S

E

G

1

9

S

E

G

2

0

S

E

G

2

1

S

E

G

2

2

S

E

G

2

3

S

E

G

2

4

S

E

G

2

7

S

E

G

2

8

S

E

G

2

9

S

E

G

2

5

S

E

G

2

6

RA1

D T M F

(K0.0)

(K0.1)

(K0.2)

(K0.3)

(K1.0)

(K1.1)

(K1.2)

(K1.3)

[Data_IO]

[Vpp]

[ m o d e ]