W83697HF/F

WINBOND I/O

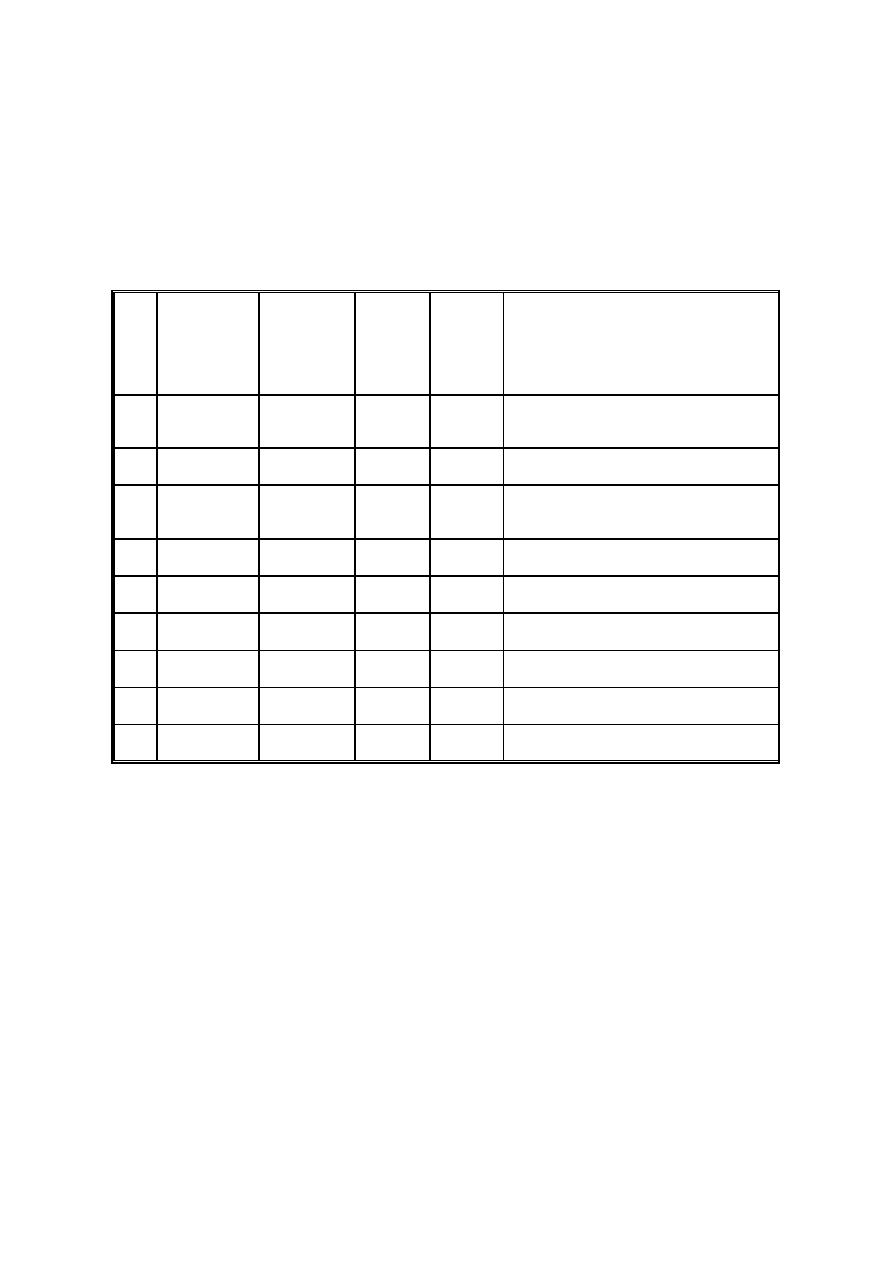

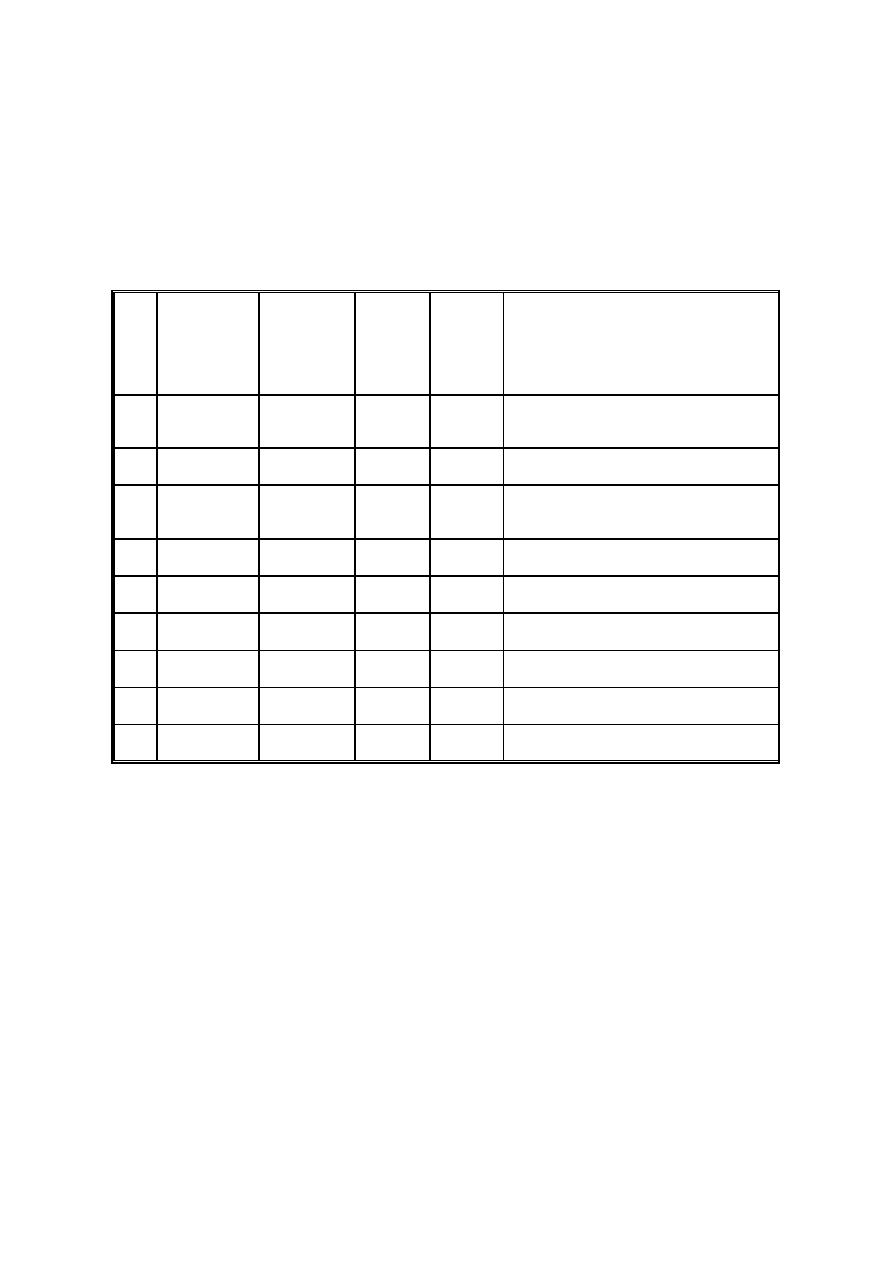

W83697HF/F Data Sheet Revision History

Pages

Dates

Version

Version

on Web

Main Contents

1

n.a.

08/23/99

0.40

First published.

For Beta Site customers only

2

98, 107, 116

11/15/99

0.41

H/W monitor register correction

3

All

11/15/2000

0.50

New composition

4

All

9/3/2001

0.6

Add W83697F pin assignment & Notice

5

2/19/2002

0.7

New Update

6

7

8

9

10

Please note that all data and specifications are subject to change without notice. All the

trade marks of products and companies mentioned in this data sheet belong to their

respective owners.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems

where malfunction of these products can reasonably be expected to result in personal

injury. Winbond customers using or selling these products for use in such applications

do so at their own risk and agree to fully indemnify Winbond for any damages resulting

from such improper use or sales.

W83697HF/F

Publication Release Date: Feb. 2002

- I - Revision 0.70

TABLE OF CONTENTS

GENERAL DESCRIPTION .....................................................................................................1

1.

PIN DESCRIPTION .....................................................................................................5

1.1 LPC INTERFACE................................................................................................................................................................ 6

1.2 FDC INTERFACE................................................................................................................................................................ 7

1.3 MULTI-MODE PARALLEL PORT...................................................................................................................................8

1.4 SERIAL PORT INTERFACE............................................................................................................................................ 13

1.5 INFRARED PORT............................................................................................................................................................. 14

1.6 FRESH ROM INTERFACE .............................................................................................................................................. 14

1.7 HARDWARE MONITOR INTERFACE........................................................................................................................ 15

1.8 GAME PORT & MIDI PORT........................................................................................................................................... 16

1.9 POWER PINS..................................................................................................................................................................... 17

2.

LPC (LOW PIN COUNT) INTERFACE.....................................................................18

3.

FDC FUNCTIONAL DESCRIPTION........................................................................19

3.1 W83697HF FDC................................................................................................................................................................. 19

3.1.1 AT interface...............................................................................................................................................................19

3.1.2 FIFO (Data)..............................................................................................................................................................19

3.1.3 Data Separator.........................................................................................................................................................20

3.1.4 Write Precompensation...........................................................................................................................................20

3.1.5 FDC Core ..................................................................................................................................................................21

3.1.6 FDC Commands .......................................................................................................................................................21

3.1.7 FDC Commands .......................................................................................................................................................21

3.2 REGISTER DESCRIPTIONS ............................................................................................................................................ 34

3.2.1 Status Register A (SA Register) (Read base address + 0)...............................................................................34

3.2.2 Status Register B (SB Register) (Read base address + 1)...............................................................................36

3.2.3 Digital Output Register (DO Register) (Write base address + 2) ..................................................................38

3.2.4 Tape Drive Register (TD Register) (Read base address + 3)..........................................................................38

3.2.5 Main Status Register (MS Register) (Read base address + 4).......................................................................39

W83697HF/F

Publication Release Date: Feb. 2002

- II - Revision 0.70

3.2.6 Data Rate Register (DR Register) (Write base address + 4)...........................................................................40

3.2.7 FIFO Register (R/W base address + 5)................................................................................................................41

3.2.8 Digital Input Register (DI Register) (Read base address + 7).......................................................................44

3.2.9 Configuration Control Register (CC Register) (Write base address + 7)....................................................45

4.

UART PORT.................................................................................................................46

4.1 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART A, UART B) ........................................... 46

4.2 REGISTER ADDRESS ...................................................................................................................................................... 46

4.2.1 UART Control Register (UCR) (Read/Write).....................................................................................................46

4.2.2 UART Status Register (USR) (Read/Write).........................................................................................................48

4.2.3 Handshake Control Register (HCR) (Read/Write)...........................................................................................50

4.2.4 Handshake Status Register (HSR) (Read/Write)...............................................................................................51

4.2.5 UART FIFO Control Register (UFR) (Write only).............................................................................................52

4.2.6 Interrupt Status Register (ISR) (Read only).......................................................................................................53

4.2.7 Interrupt Control Register (ICR) (Read/Write) .................................................................................................54

4.2.8 Programmable Baud Generator (BLL/BHL) (Read/Write) ..............................................................................54

4.2.9 User-defined Register (UDR) (Read/Write)........................................................................................................55

5.

CIR RECEIVER PORT...............................................................................................56

5.1 CIR REGISTERS................................................................................................................................................................ 56

5.1.1 Bank0.Reg0 - Receiver Buffer Registers (RBR) (Read) ....................................................................................56

5.1.2 Bank0.Reg1 - Interrupt Control Register (ICR) ................................................................................................56

5.1.3 Bank0.Reg2 - Interrupt Status Register (ISR) ....................................................................................................56

5.1.4 Bank0~3.Reg3 - CIR Control Register 0/Bank Select Register (CTR0/BSR) (BANK0~3)........................57

5.1.5 Bank0.Reg4 - CIR Control Register (CTR) .........................................................................................................58

5.1.6 Bank0.Reg5 - UART Line Status Register (USR) ..............................................................................................59

5.1.7 Bank0.Reg6 - Remote Infrared Config Register (RIR_CFG) ...........................................................................59

5.1.8 Bank0.Reg7 - User Defined Register (UDR/AUDR) ..........................................................................................60

5.1.9 Bank1.Reg0~1 - Baud Rate Divisor Latch (BLL/BHL) .....................................................................................61

5.1.10 Bank1.Reg2 - Version ID Regiister I (VID) .......................................................................................................62

5.1.11 Bank0~3.Reg3 - CIR Control Register 0/Bank Select Register (CTR0/BSR) (BANK0~3) .....................62

5.1.12 Bank1.Reg4 - Timer Low Byte Register (TMRL)..............................................................................................62

5.1.13 Bank1.Reg5 - Timer High Byte Register (TMRH) ............................................................................................ 62

6.

PARALLEL PORT......................................................................................................63

6.1 PRINTER INTERFACE LOGIC........................................................................................................................................ 63

W83697HF/F

Publication Release Date: Feb. 2002

- III - Revision 0.70

6.2 ENHANCED PARALLEL PORT (EPP).......................................................................................................................... 64

6.2.1 Data Swapper...........................................................................................................................................................65

6.2.2 Printer Status Buffer................................................................................................................................................65

6.2.3 Printer Control Latch and Printer Control Swapper .......................................................................................66

6.2.4 EPP Address Port.....................................................................................................................................................66

6.2.5 EPP Data Port 0-3...................................................................................................................................................67

6.2.6 Bit Map of Parallel Port and EPP Registers......................................................................................................67

6.2.7 EPP Pin Descriptions..............................................................................................................................................68

6.2.8 EPP Operation.........................................................................................................................................................68

6.3 EXTENDED CAPABILITIES PARALLEL (ECP) PORT.............................................................................................. 69

6.3.1 ECP Register and Mode Definitions....................................................................................................................69

6.3.2 Data and ecpAFifo Port..........................................................................................................................................70

6.3.3 Device Status Register (DSR) ................................................................................................................................70

6.3.4 Device Control Register (DCR) ............................................................................................................................ 71

6.3.5 cFifo (Parallel Port Data FIFO) Mode = 010...................................................................................................72

6.3.6 ecpDFifo (ECP Data FIFO) Mode = 011............................................................................................................72

6.3.7 tFifo (Test FIFO Mode) Mode = 110...................................................................................................................72

6.3.8 cnfgA (Configuration Register A) Mode = 111 .................................................................................................72

6.3.9 cnfgB (Configuration Register B) Mode = 111 .................................................................................................72

6.3.10 ecr (Extended Control Register) Mode = all ...................................................................................................73

6.3.11 Bit Map of ECP Port Registers............................................................................................................................ 74

6.3.12 ECP Pin Descriptions...........................................................................................................................................75

6.3.13 ECP Operation.......................................................................................................................................................76

6.3.14 FIFO Operation .....................................................................................................................................................76

6.3.15 DMA Transfers........................................................................................................................................................77

6.3.16 Programmed I/O (NON-DMA) Mode .................................................................................................................77

6.4 EXTENSION FDD MODE (EXTFDD)............................................................................................................................ 77

6.5 EXTENSION 2FDD MODE (EXT2FDD)........................................................................................................................ 77

7.

GENERAL PURPOSE I/O...........................................................................................78

8.

ACPI REGISTERS FEATURES .................................................................................81

9.

HARDWARE MONITOR ..........................................................................................82

9.1 GENERAL DESCRIPTION............................................................................................................................................... 82

9.2 ACCESS INTERFACE...................................................................................................................................................... 82