DS099 October 9, 2003

www.xilinx.com

Advance Product Specification

1-800-255-7778

� 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at

http://www.xilinx.com/legal.htm

.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

This document includes all four modules of the SpartanTM-3 FPGA data sheet.

Module 1:

Introduction and Ordering Information

DS099-1 (v1.1) April 24, 2003

6 pages

�

Introduction

�

Features

�

Architectural Overview

�

Product Availability

�

User I/O Chart

�

Ordering Information

Module 2:

Functional Description

DS099-2 (v1.2) July 11, 2003

40 pages

�

IOBs

-

IOB Overview

-

SelectIOTM Signal Standards

�

CLB Overview

�

Block RAM

�

Dedicated Multipliers

�

Digital Clock Manager (DCM)

-

Clock Network

�

Configuration

Module 3:

DC and Switching Characteristics

DS099-3 (v1.1) July 11, 2003

14 pages

�

DC Electrical Characteristics

-

Absolute Maximum Ratings

-

Recommended Operating Conditions

�

Configuration

-

Power-On Timing

-

Timing for the Configuration Modes

-

Timing for JTAG Port

�

Switching Characteristics

-

DLL Timing

Module 4:

Pinout Descriptions

DS099-4 (v1.2.2) October 9, 2003

98 pages

�

Pin Descriptions

-

Pin Behavior During Configuration

�

Package Overview

�

Pinout Tables

-

Footprints

IMPORTANT NOTE: The Spartan-3 1.2V FPGA data sheet is created and published in separate modules. This complete

version is provided for easy downloading and searching of the complete document. Page, figure, and table numbers begin

at 1 for each module, and each module has its own Revision History at the end. Use the PDF "Bookmarks" for easy

navigation in this volume.

0

Spartan-3 1.2V FPGA Family:

Complete Data Sheet

DS099 October 9, 2003

0

0

Advance Product Specification

R

DS099-1 (v1.1) April 24, 2003

www.xilinx.com

1

Advance Product Specification

1-800-255-7778

� 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at

http://www.xilinx.com/legal.htm

.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Introduction

The 1.2V SpartanTM-3 family of Field-Programmable Gate

Arrays is specifically designed to meet the needs of high

volume, cost-sensitive consumer electronic applications.

The eight-member family offers densities ranging from

50,000 to five million system gates, as shown in

Table 1

.

The Spartan-3 family builds on the success of the earlier

Spartan-IIE family by increasing the amount of logic

resources, the capacity of internal RAM, the total number of

I/Os, and the overall level of performance as well as by

improving clock management functions. Numerous

enhancements derive from state-of-the-art VirtexTM-II tech-

nology. These Spartan-3 enhancements, combined with

advanced process technology, deliver more functionality

and bandwidth per dollar than was previously possible, set-

ting new standards in the programmable logic industry.

Because of their exceptionally low cost, Spartan-3 FPGAs

are ideally suited to a wide range of consumer electronics

applications, including broadband access, home network-

ing, display/projection and digital television equipment.

The Spartan-3 family is a superior alternative to mask pro-

grammed ASICs. FPGAs avoid the high initial cost, the

lengthy development cycles, and the inherent inflexibility of

conventional ASICs. Also, FPGA programmability permits

design upgrades in the field with no hardware replacement

necessary, an impossibility with ASICs.

Features

�

Revolutionary 90-nanometer process technology

�

Very low cost, high-performance logic solution for

high-volume, consumer-oriented applications

-

Densities as high as 74,880 logic cells

-

326 MHz system clock rate

-

Three separate power supplies for the core (1.2V),

I/Os (1.2V to 3.3V), and special functions (2.5V)

�

SelectIOTM signaling

-

Up to 784 I/O pins

-

622 Mb/s data transfer rate per I/O

-

Seventeen single-ended signal standards

-

Six differential signal standards including LVDS

-

Termination by Digitally Controlled Impedance

-

Signal swing ranging from 1.14V to 3.45V

-

Double Data Rate (DDR) support

�

Logic resources

-

Abundant, flexible logic cells with registers

-

Wide multiplexers

-

Fast look-ahead carry logic

-

Dedicated 18 x 18 multipliers

-

JTAG logic compatible with IEEE 1149.1/1532

standards

�

SelectRAMTM hierarchical memory

-

Up to 1,872 Kbits of total block RAM

-

Up to 520 Kbits of total distributed RAM

�

Digital Clock Manager (up to four DCMs)

-

Clock skew elimination

-

Frequency synthesis

-

High resolution phase shifting

�

Eight global clock lines and abundant routing

�

Fully supported by Xilinx ISE development system

-

Synthesis, mapping, placement and routing

06

Spartan-3 1.2V FPGA Family:

Introduction and Ordering

Information

DS099-1 (v1.1) April 24, 2003

0

0

Advance Product Specification

R

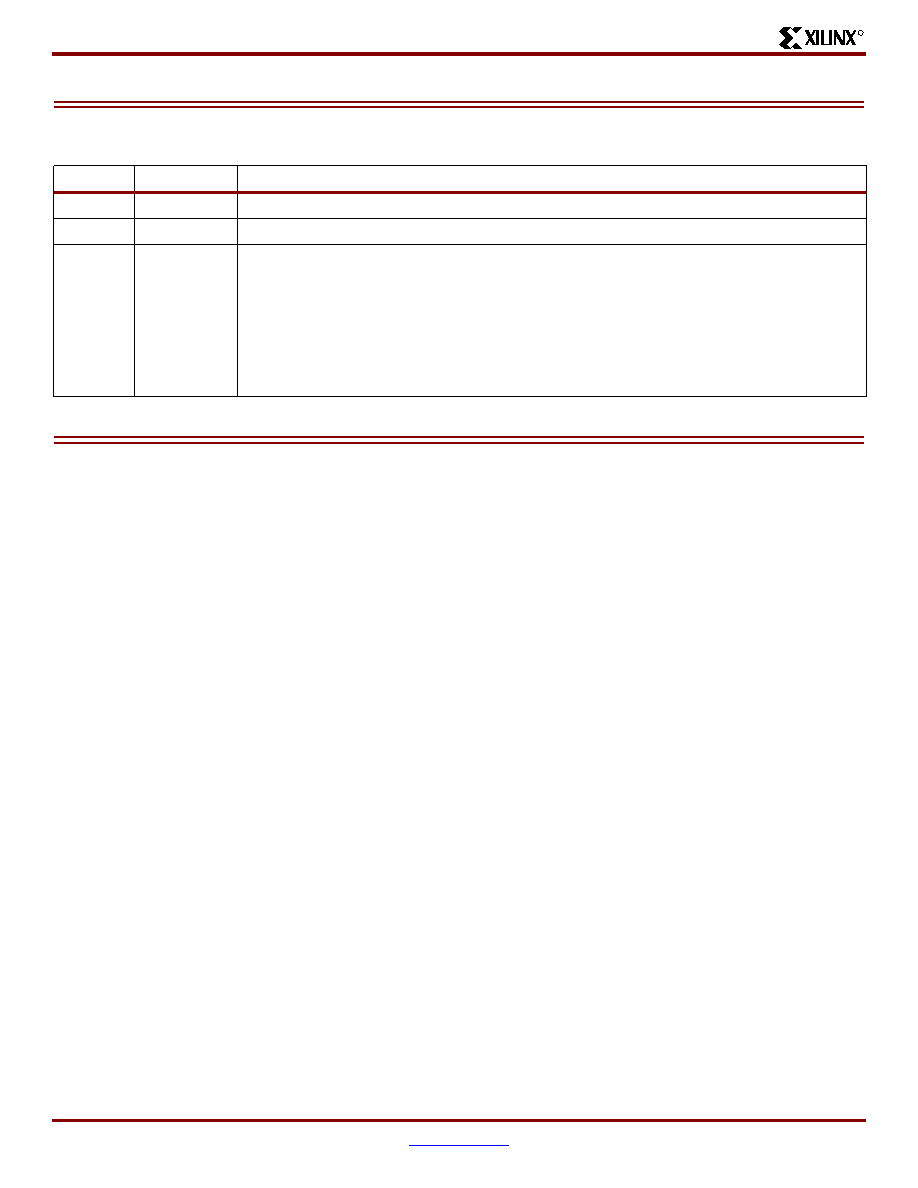

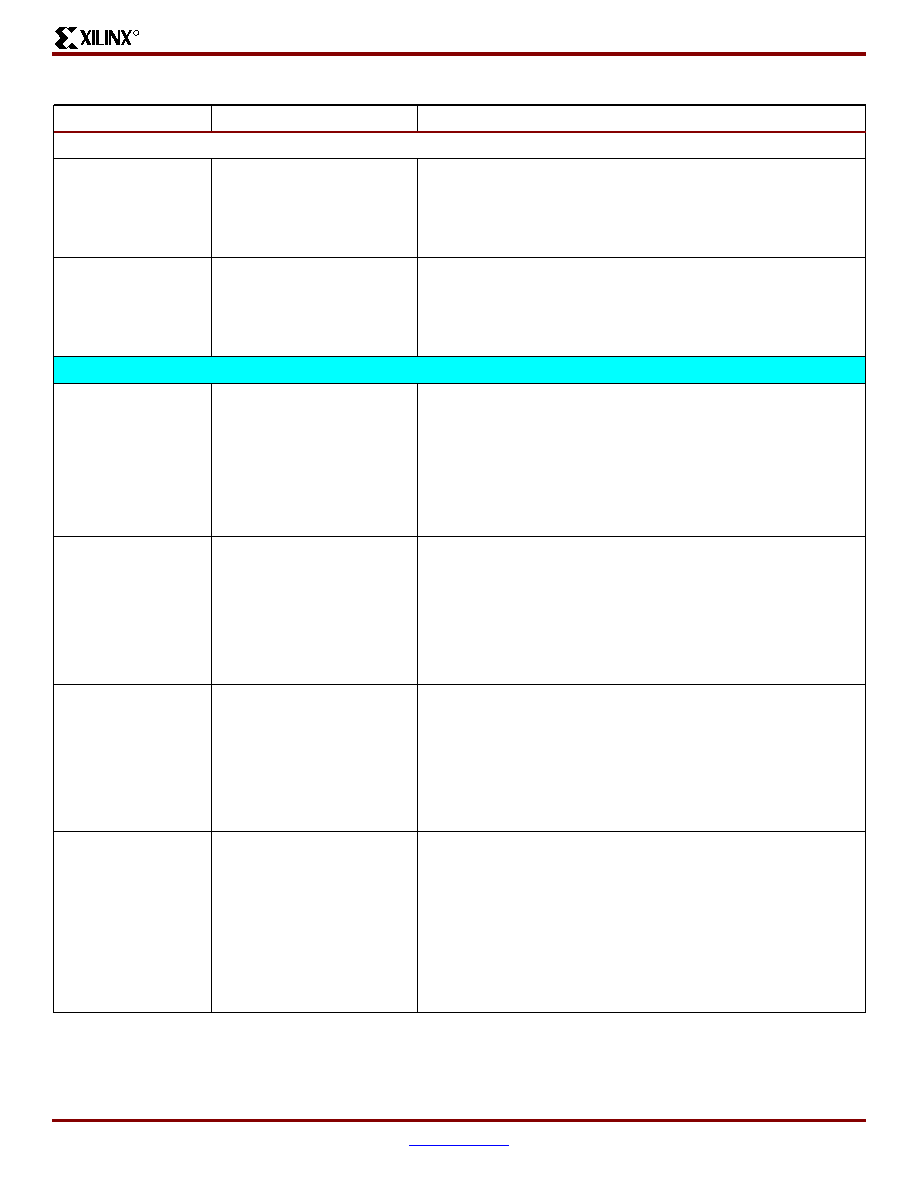

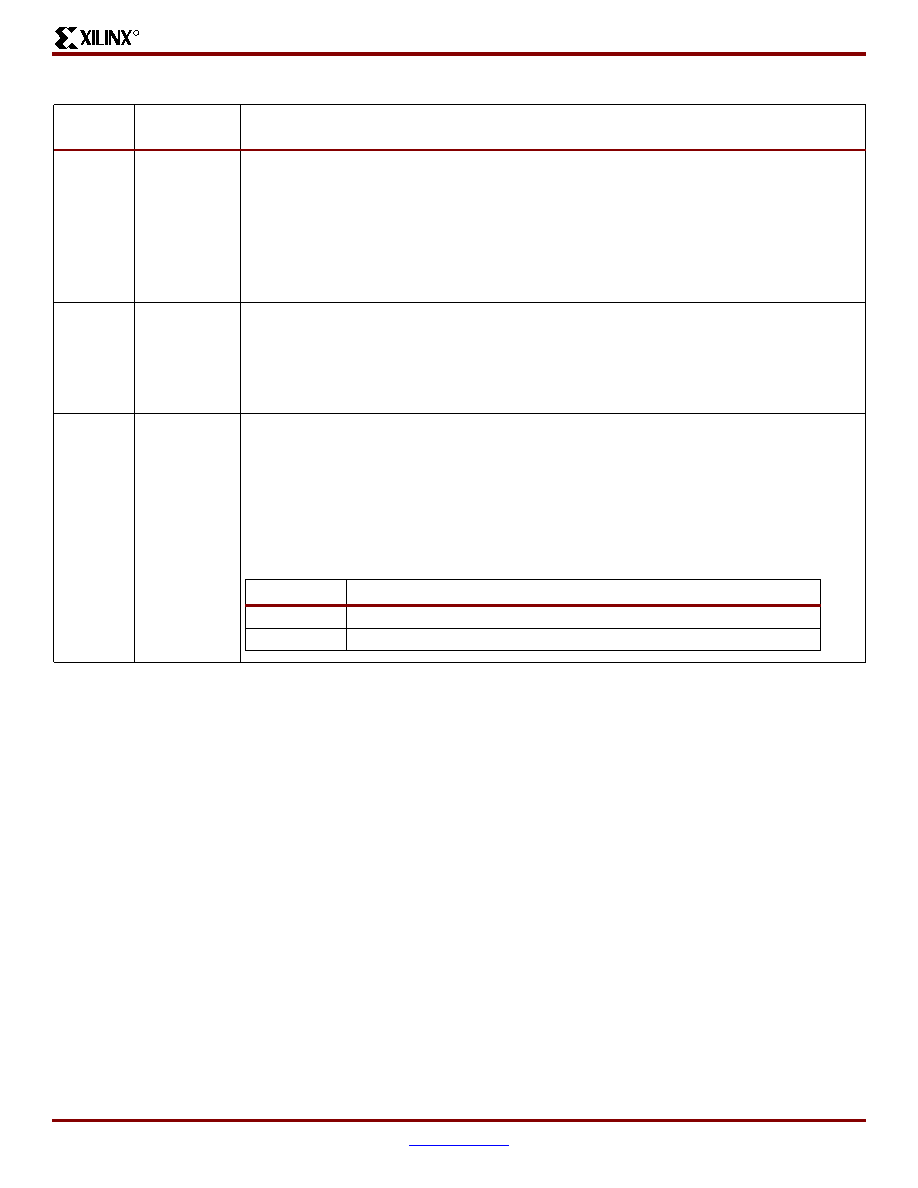

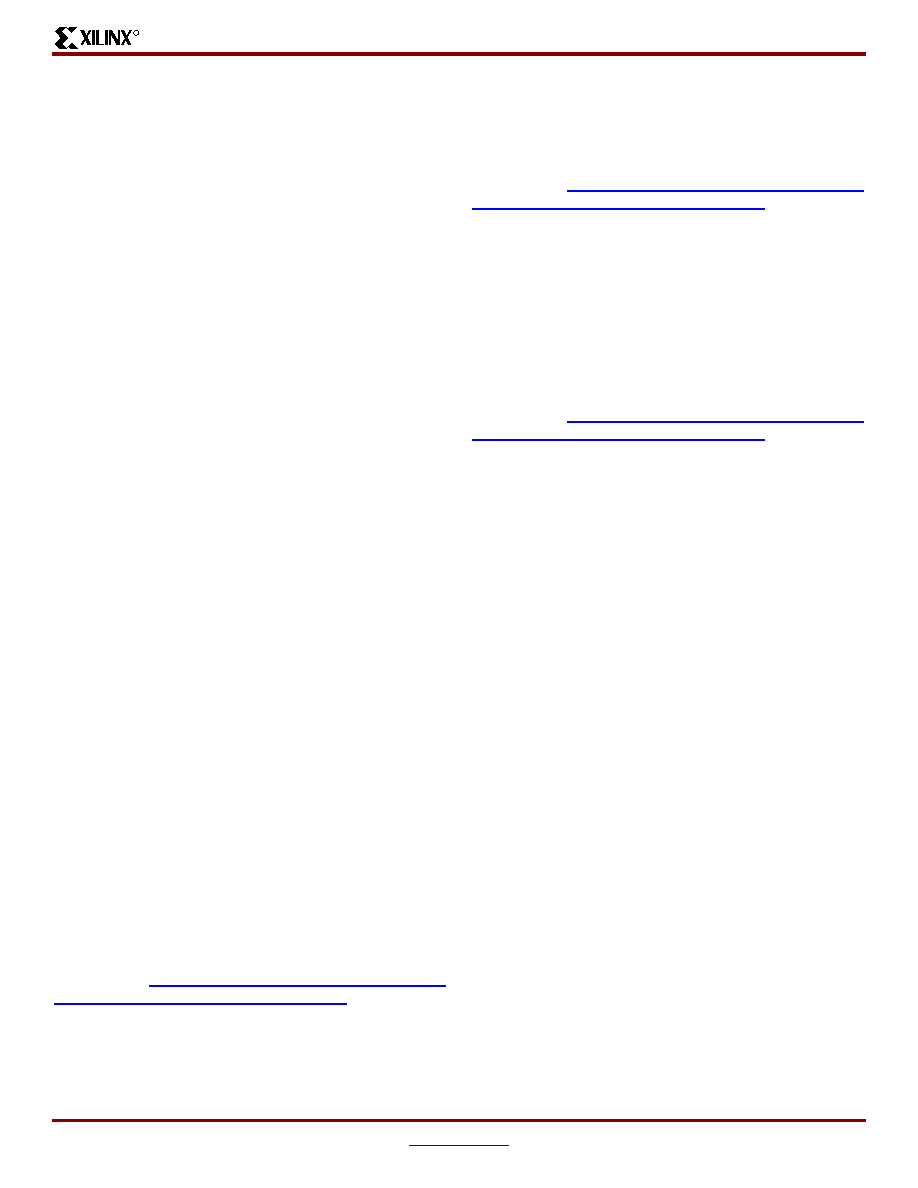

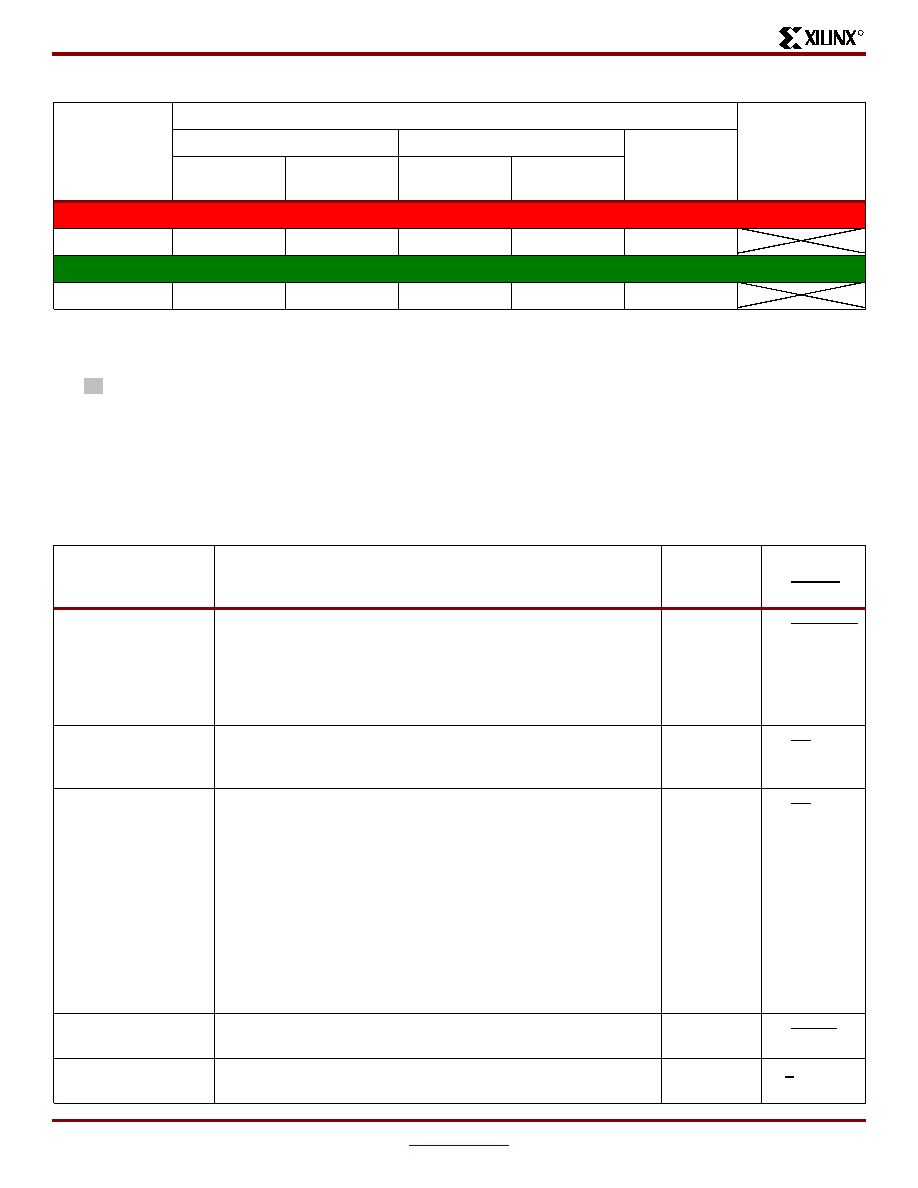

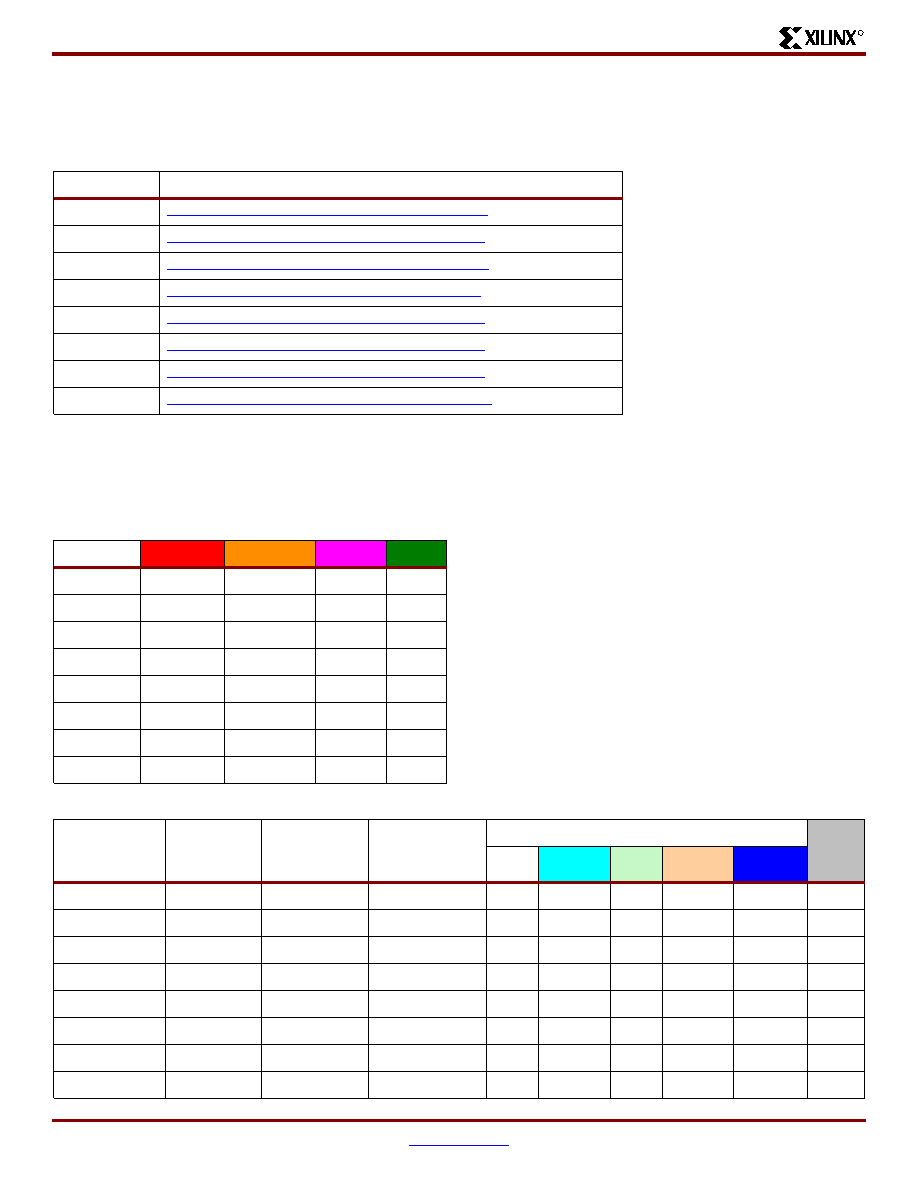

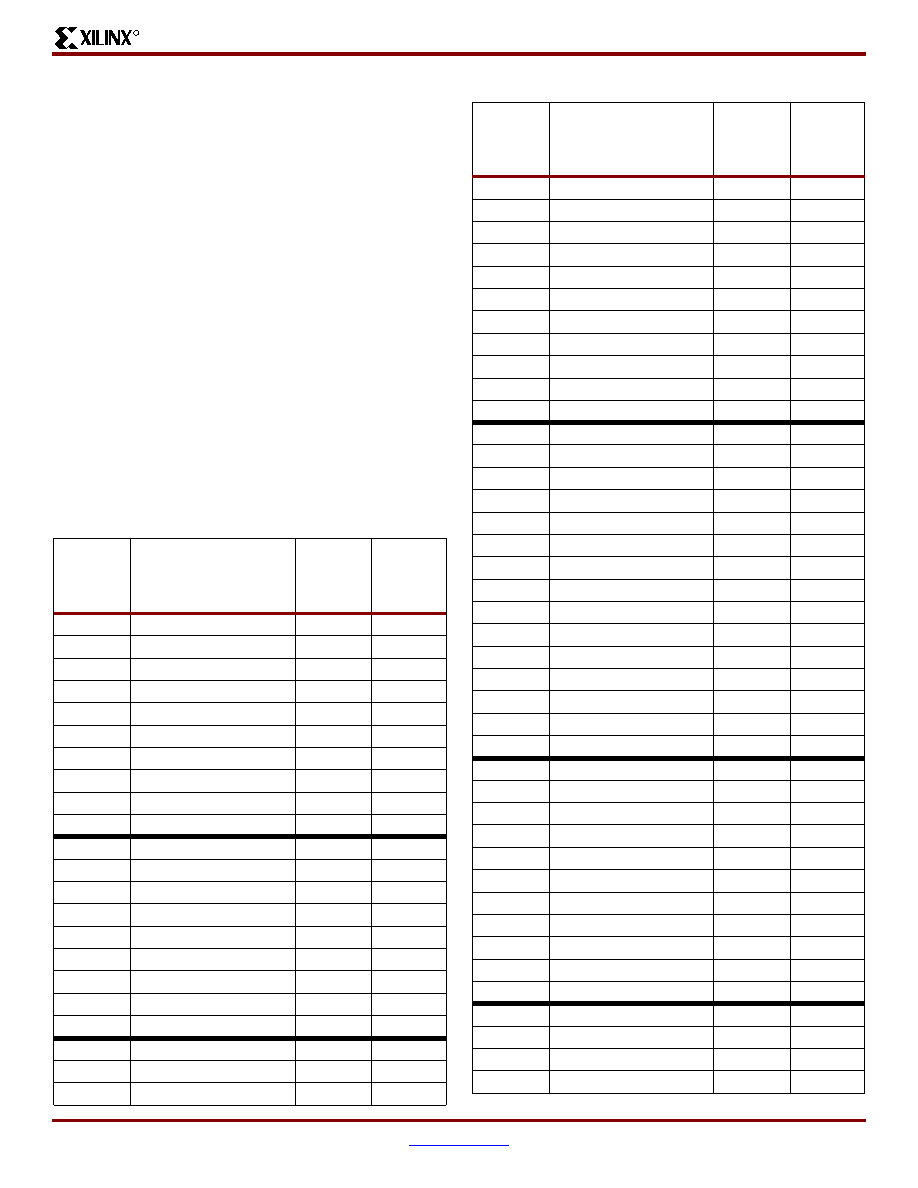

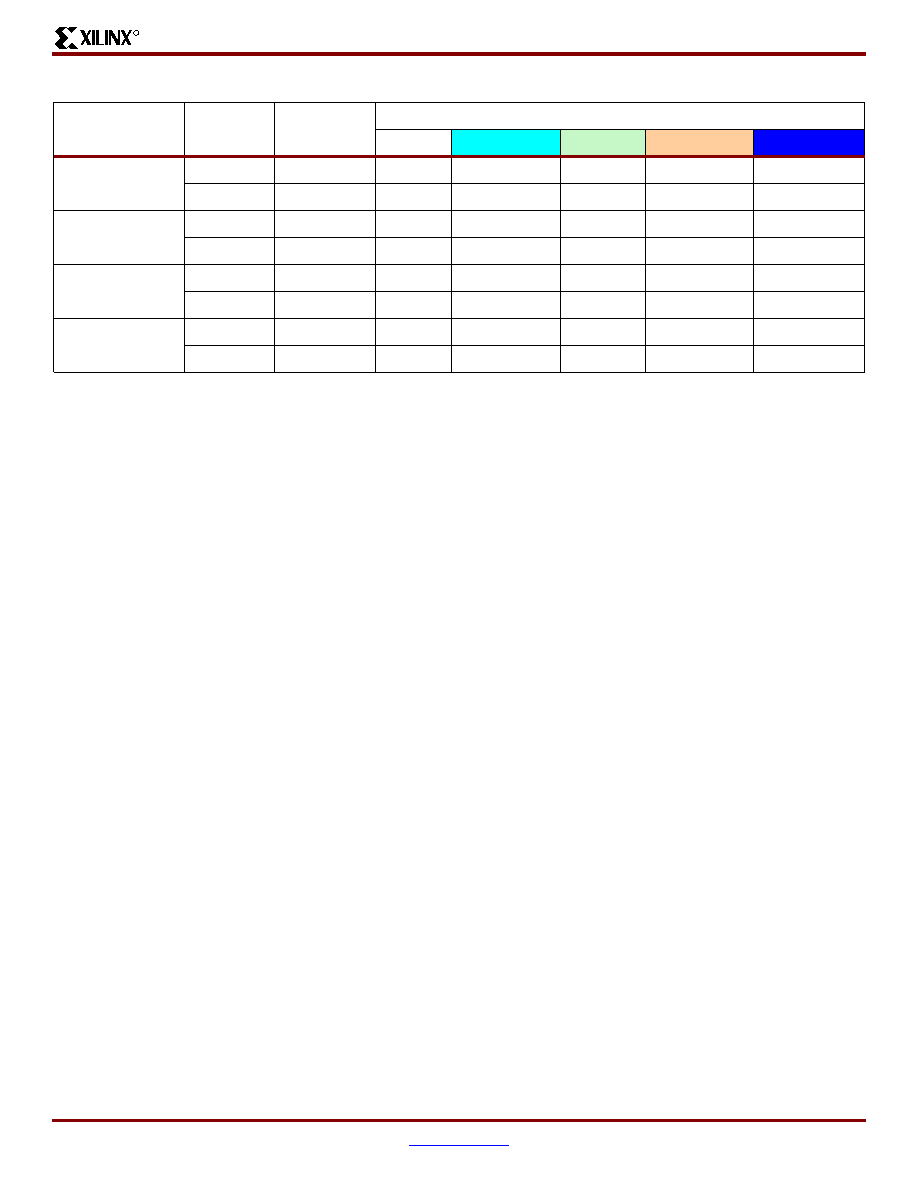

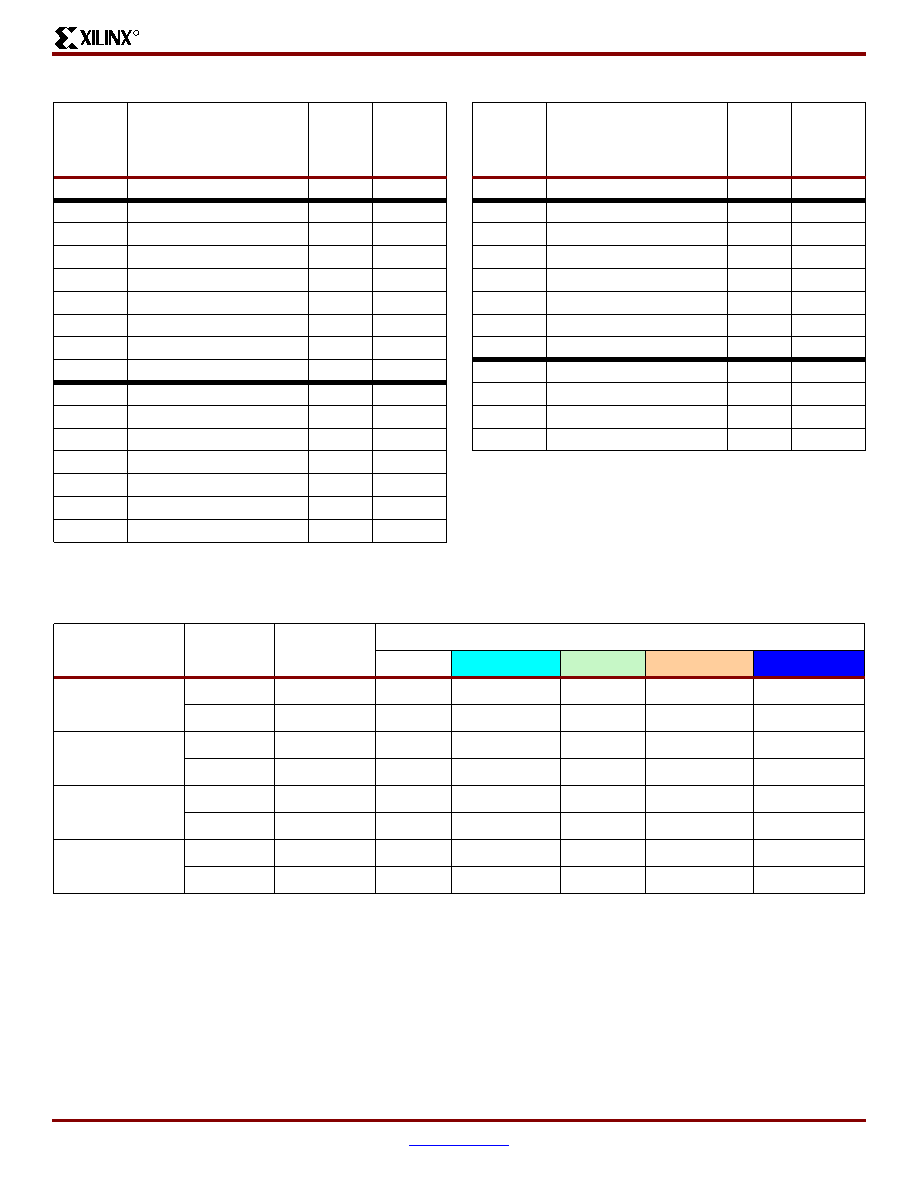

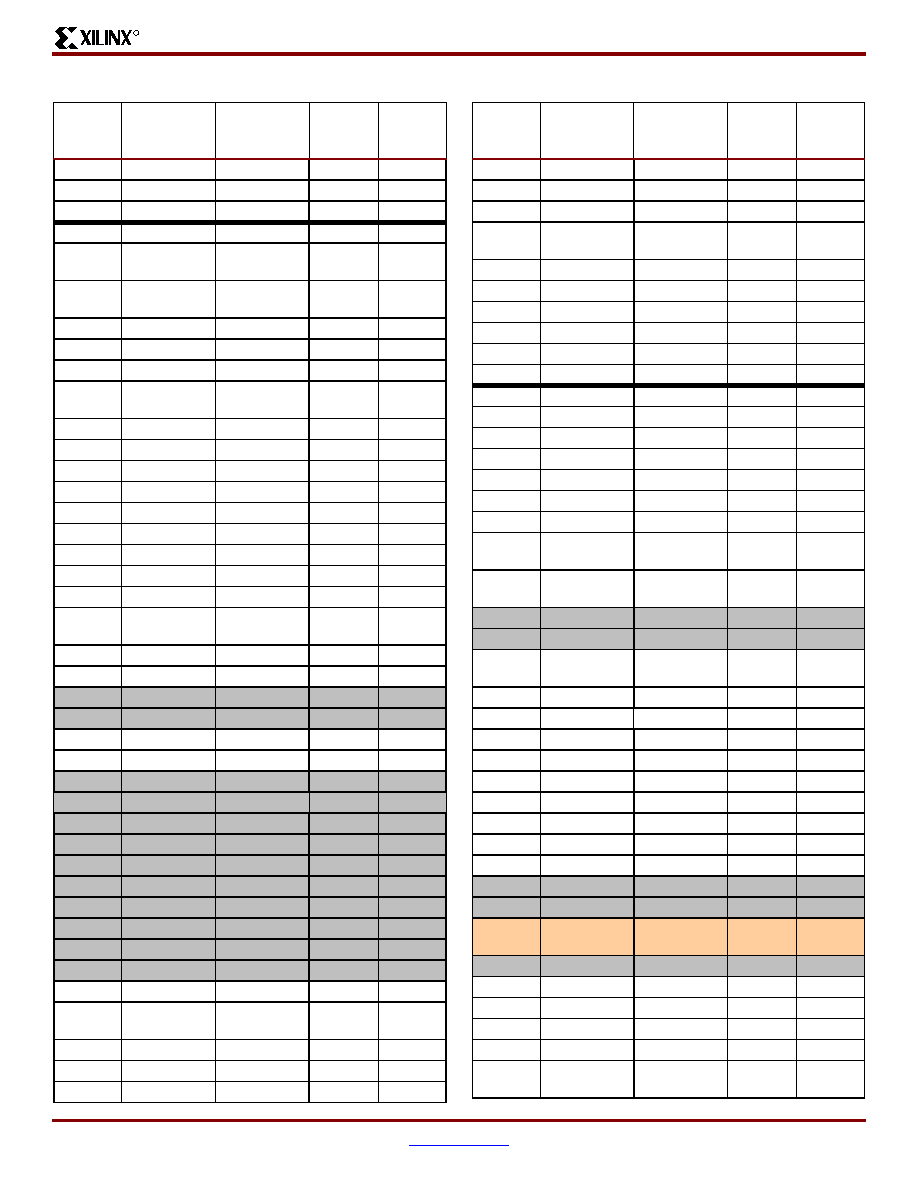

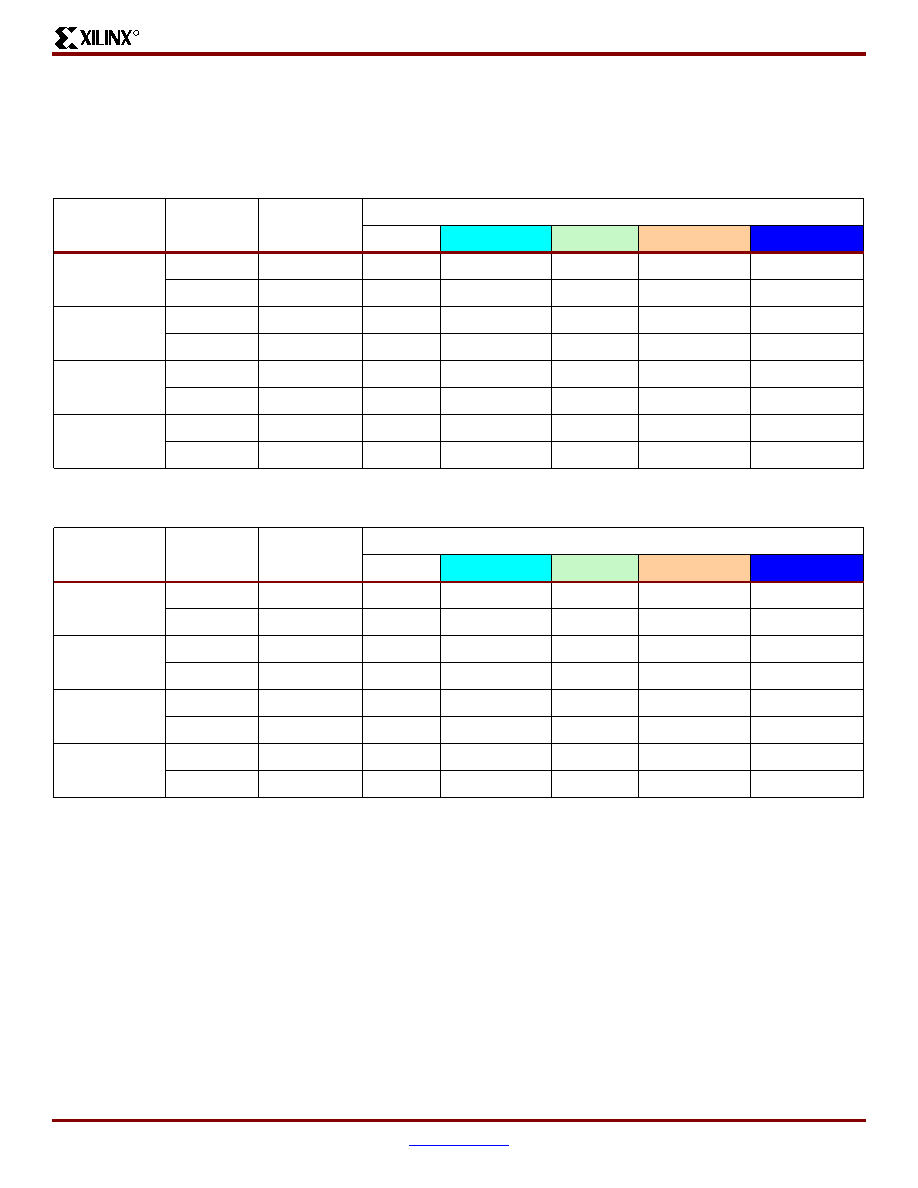

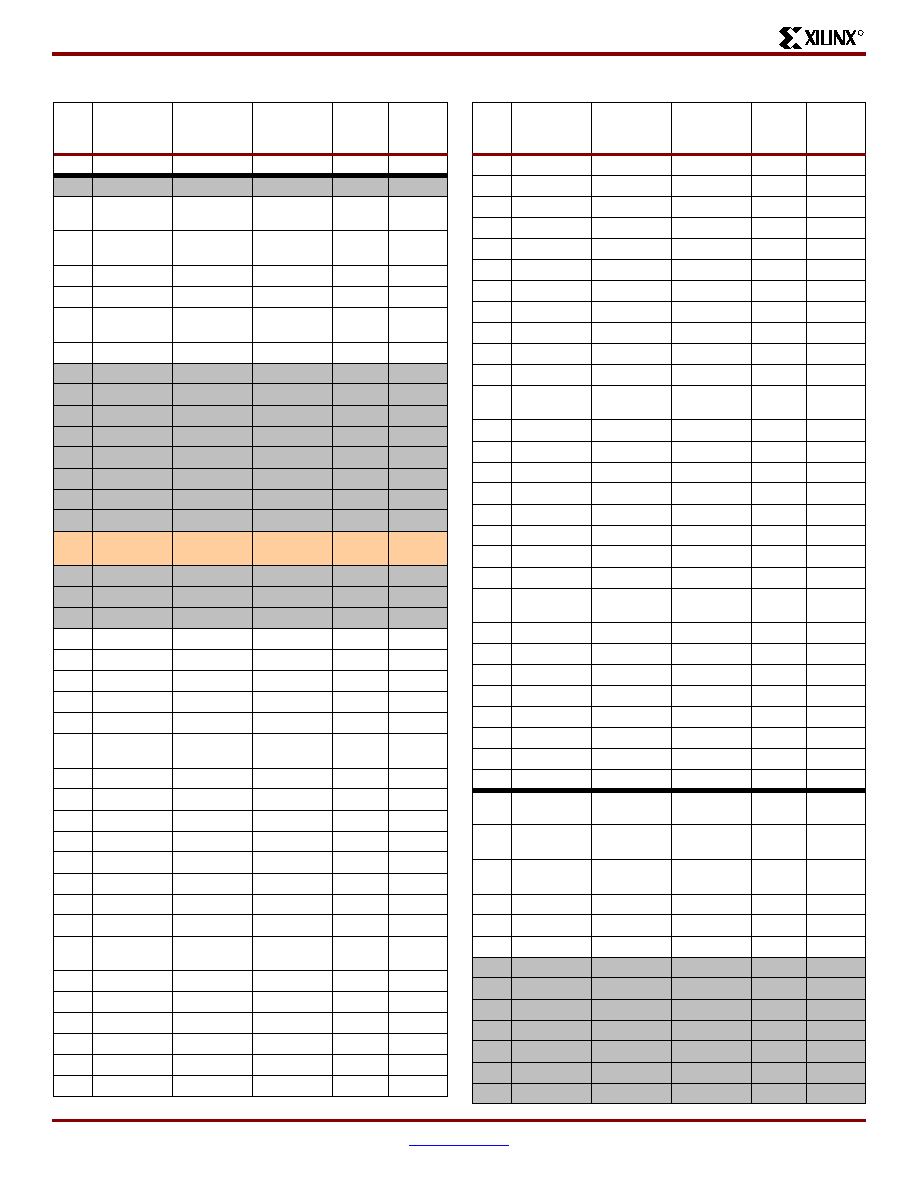

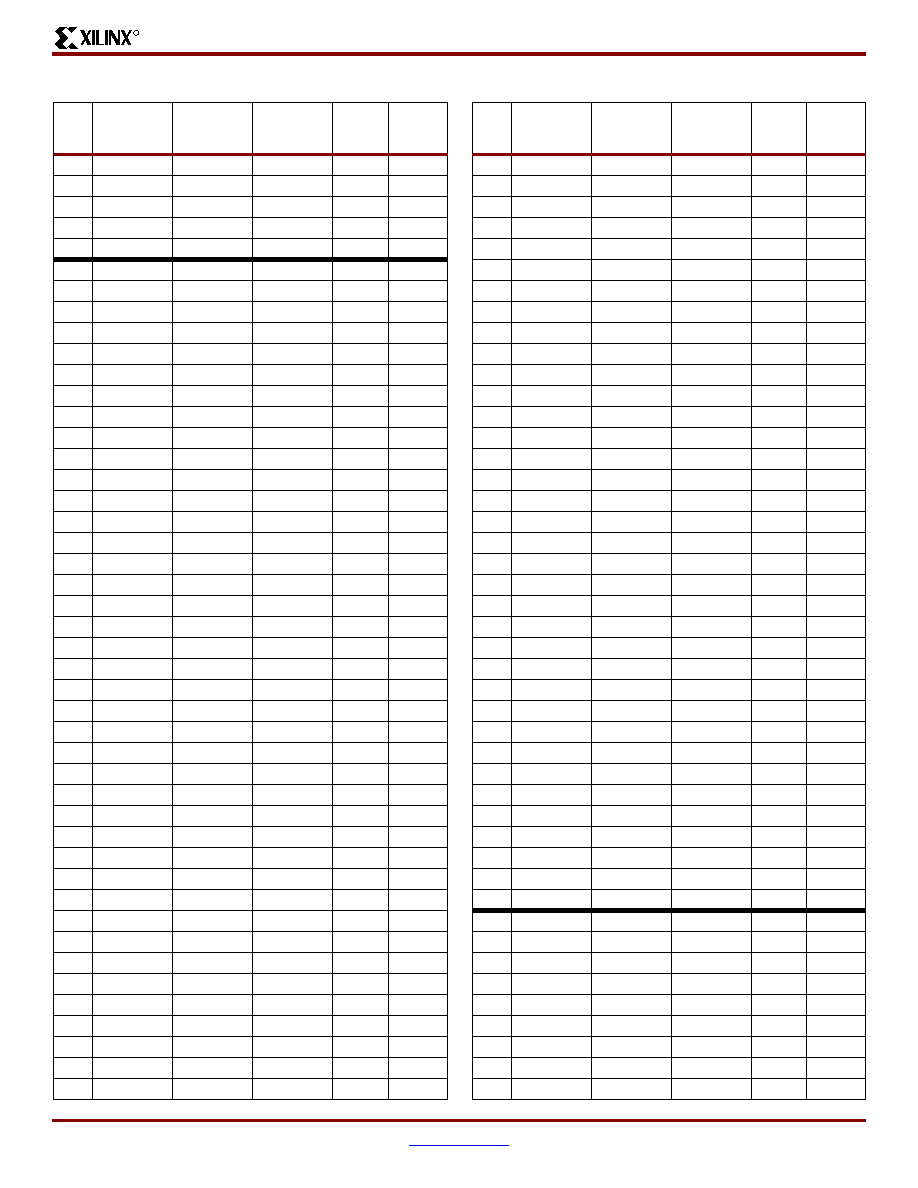

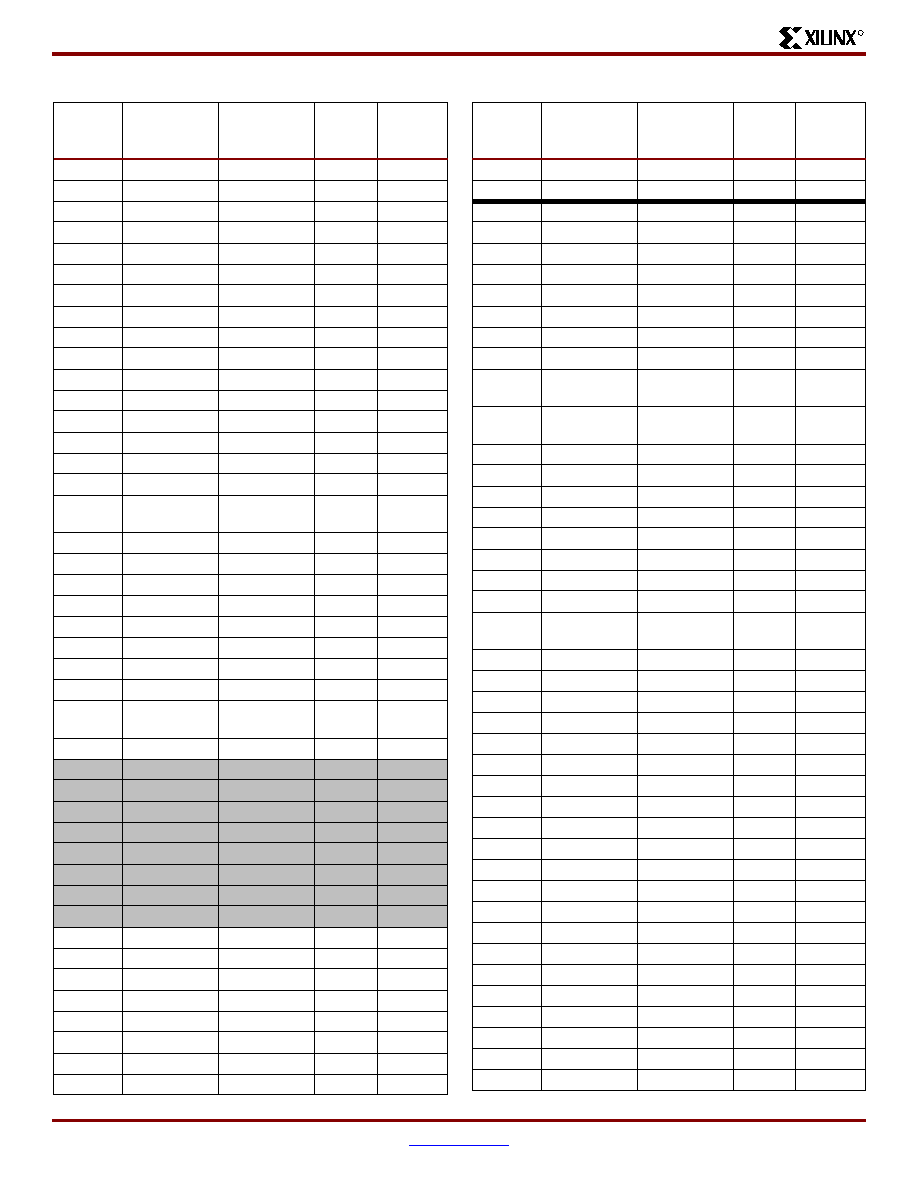

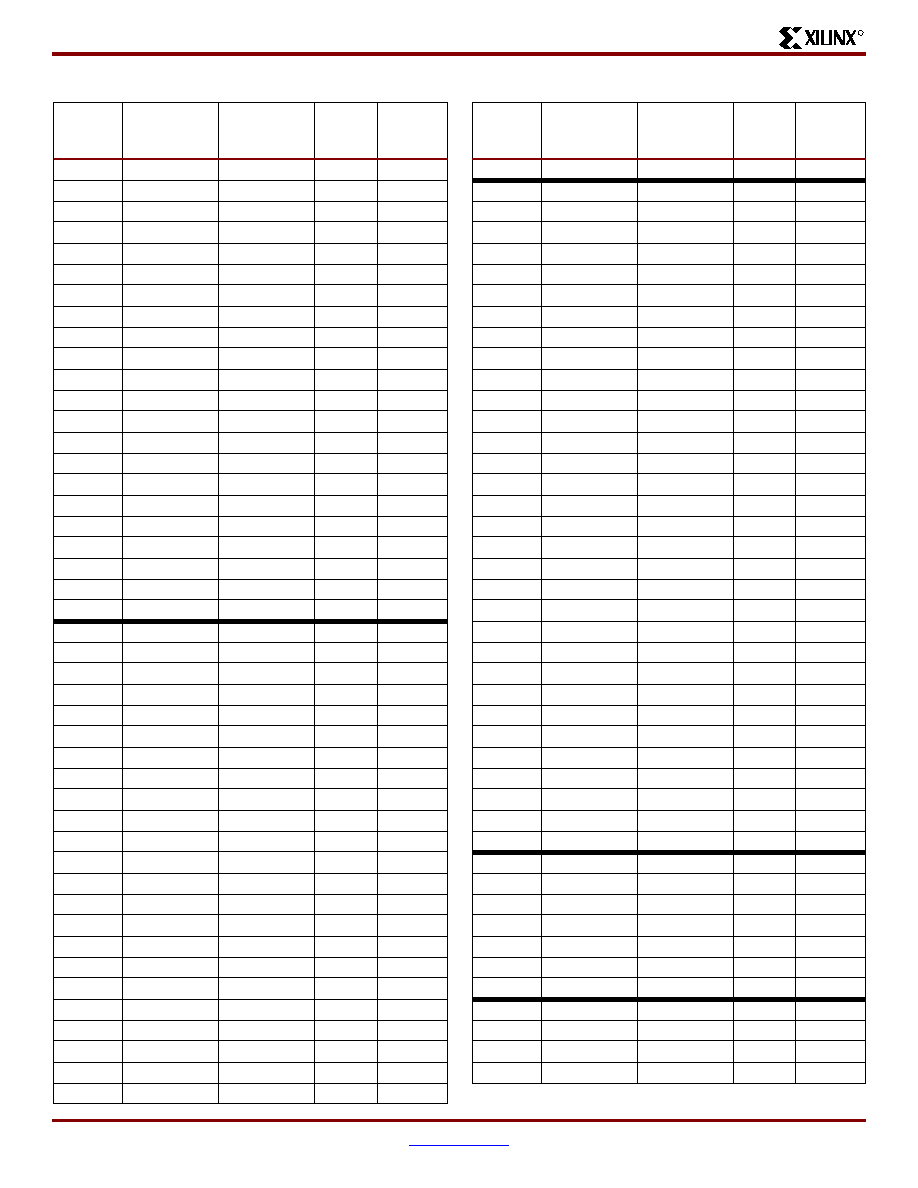

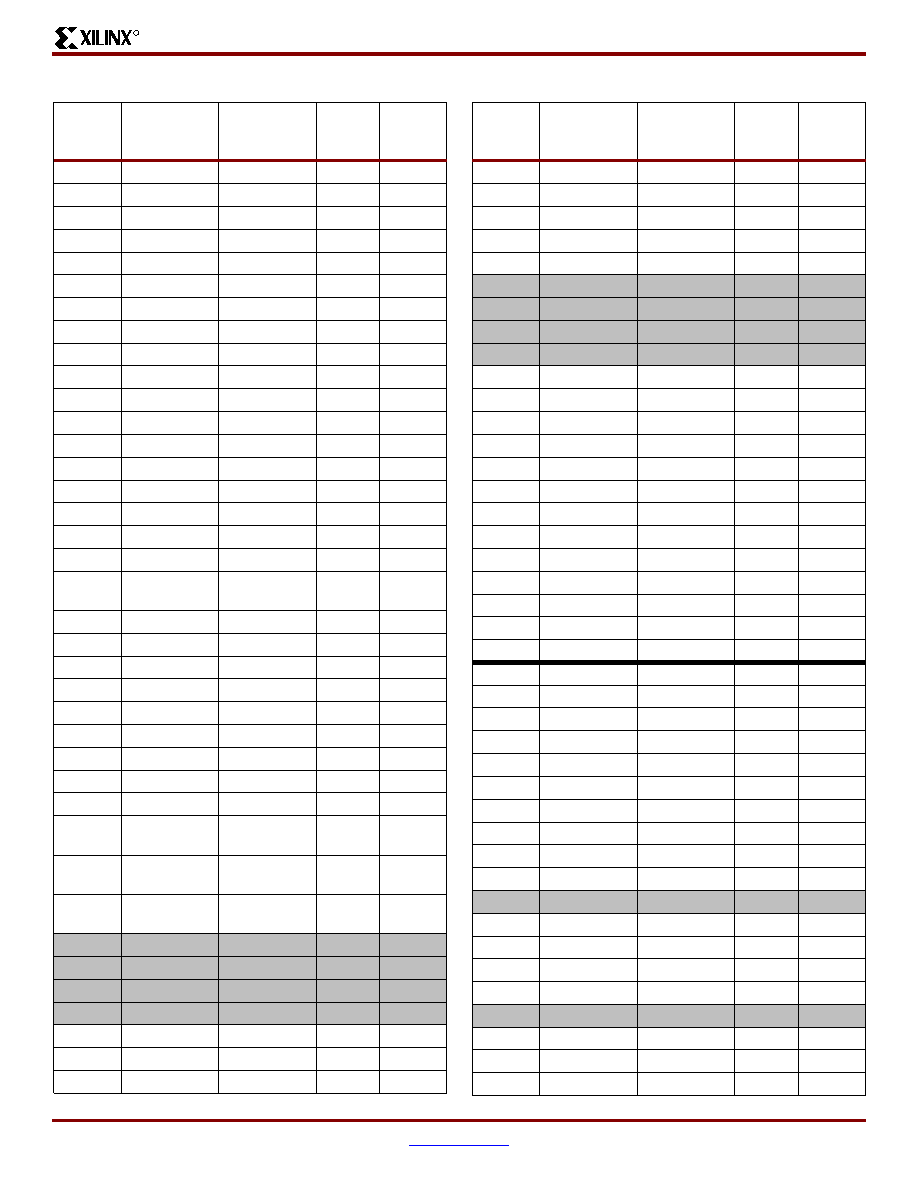

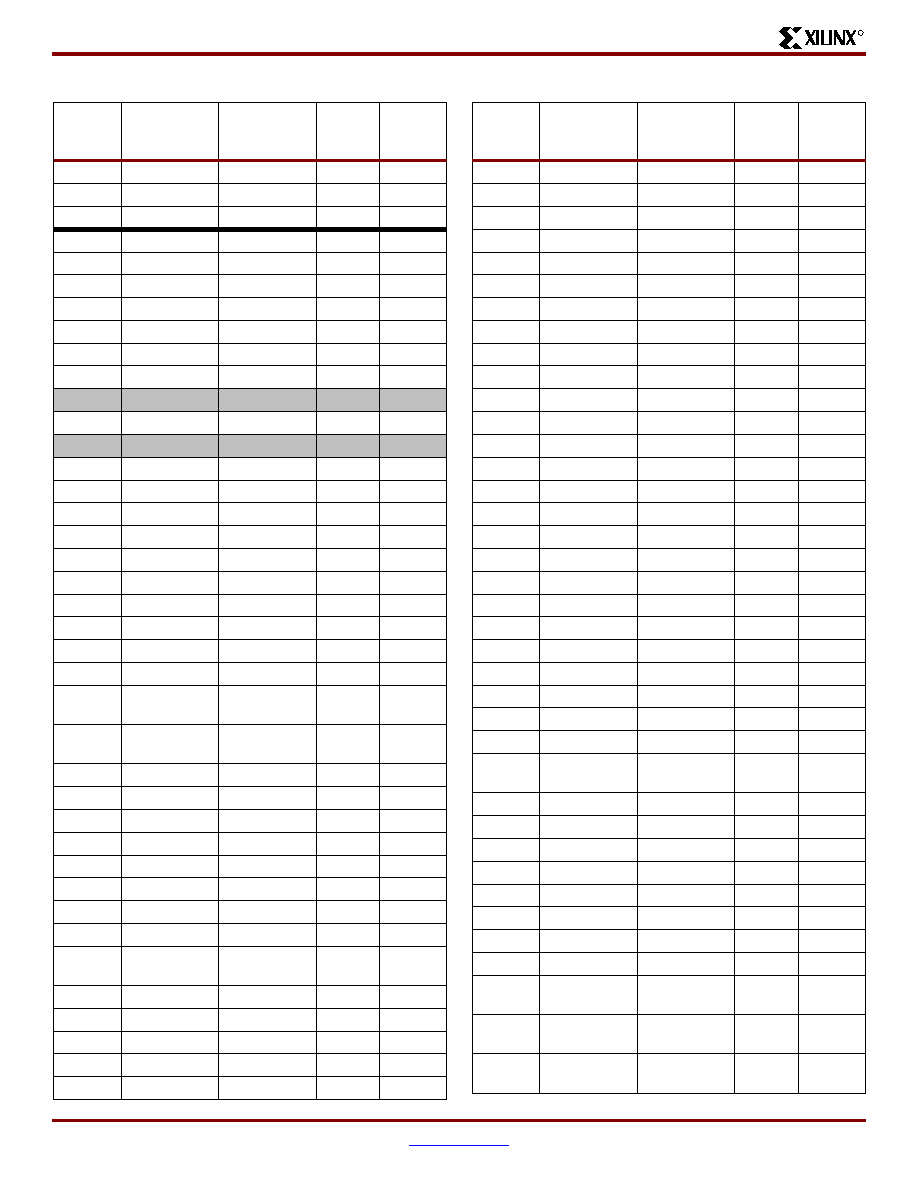

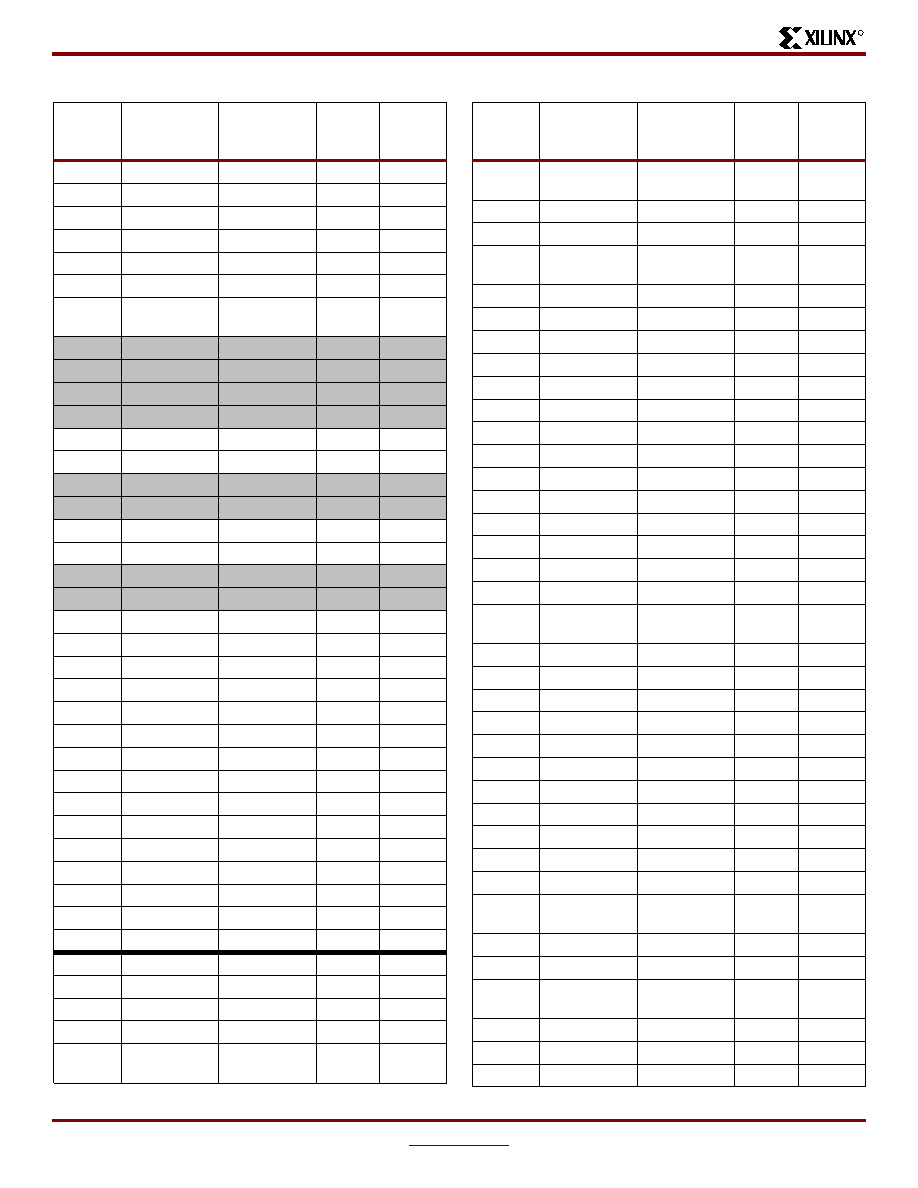

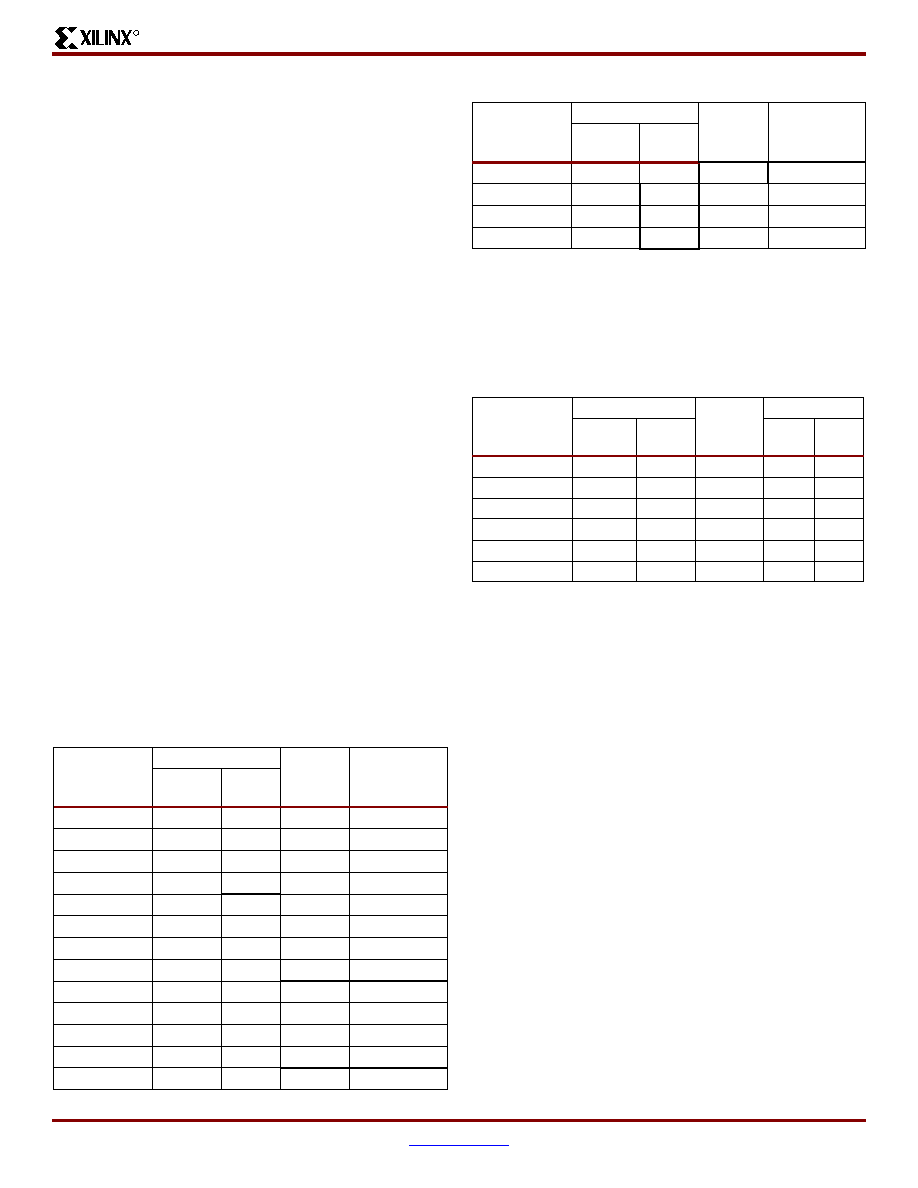

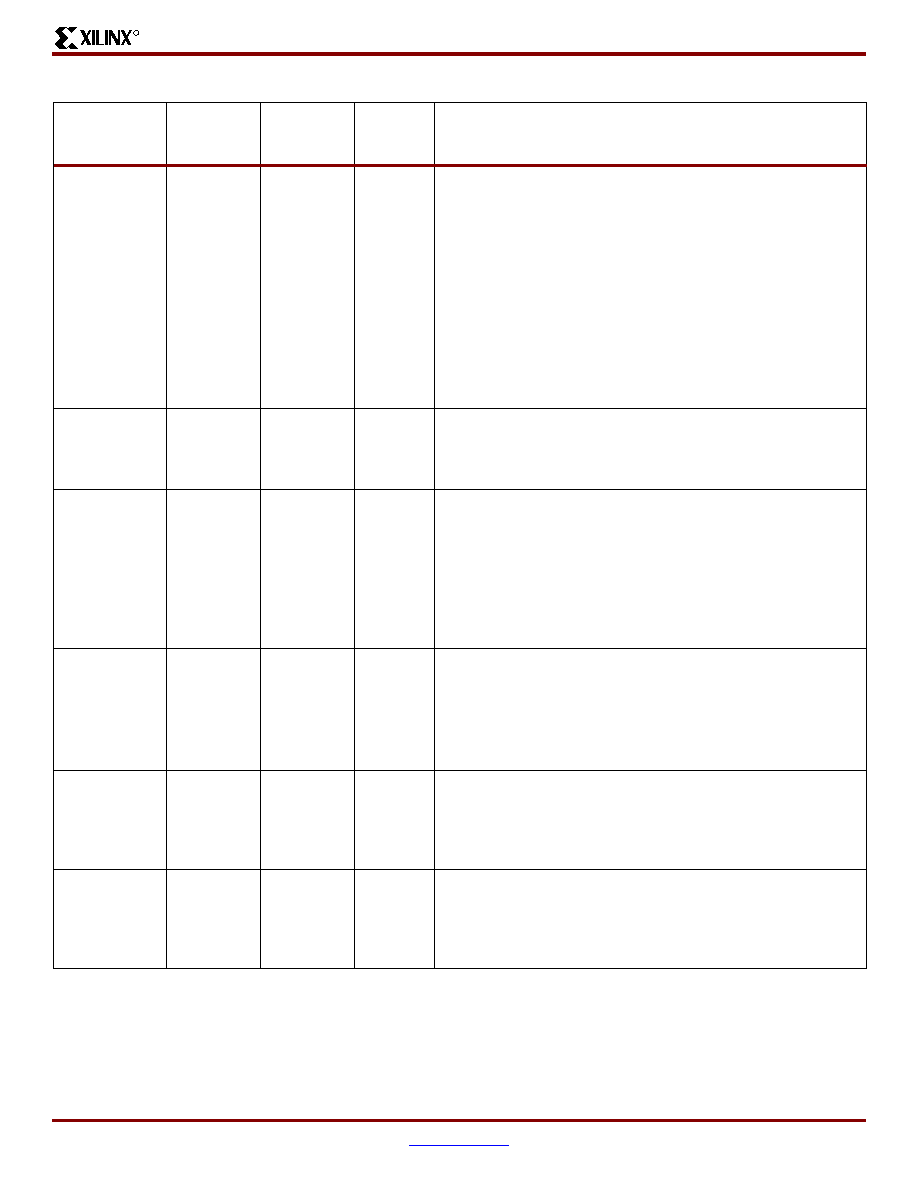

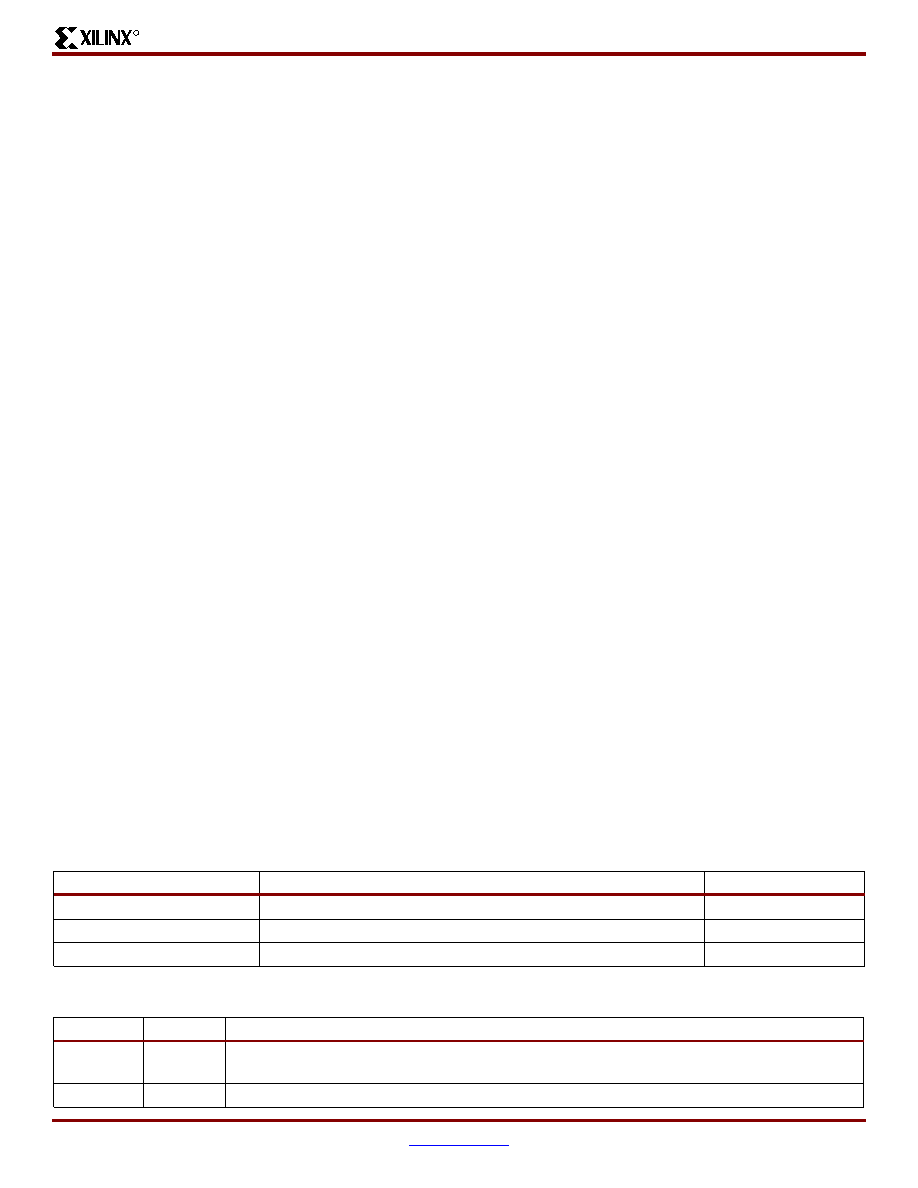

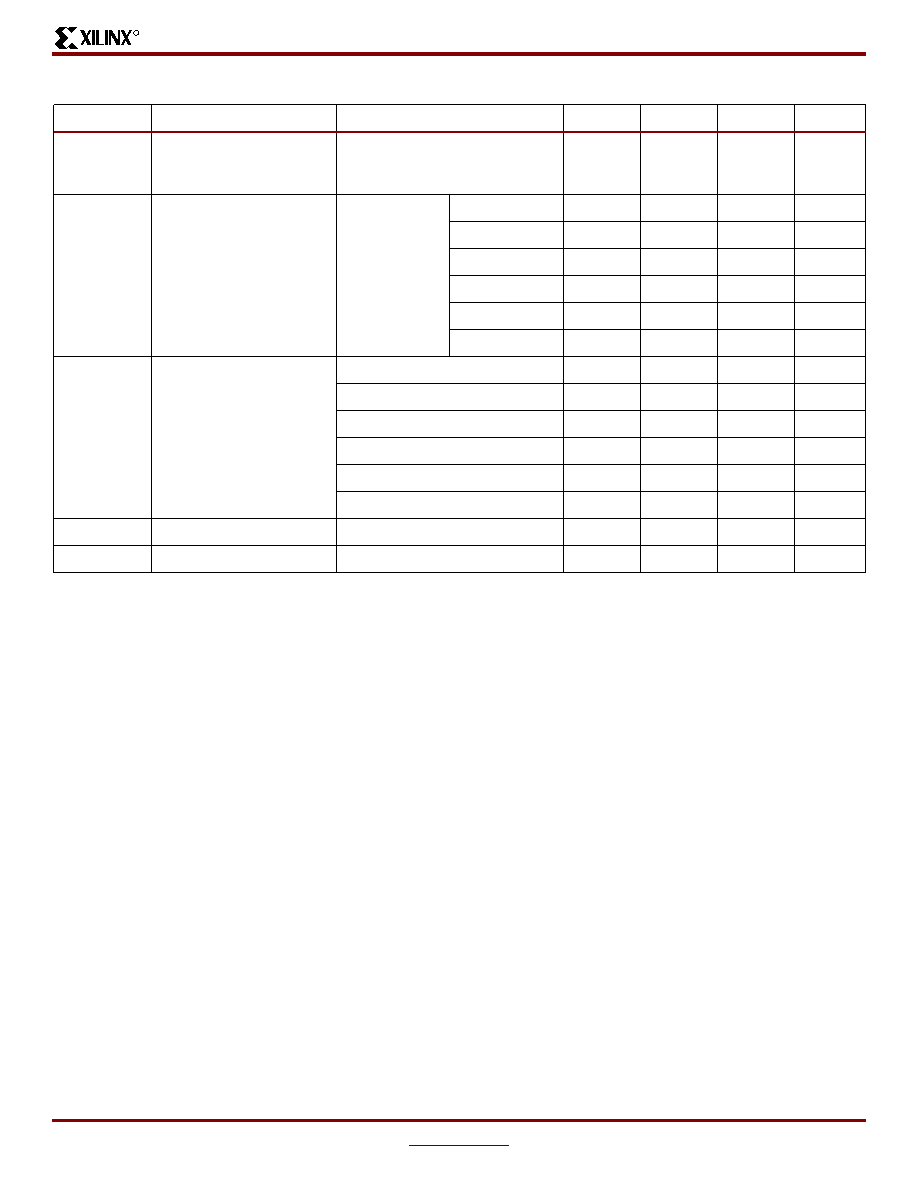

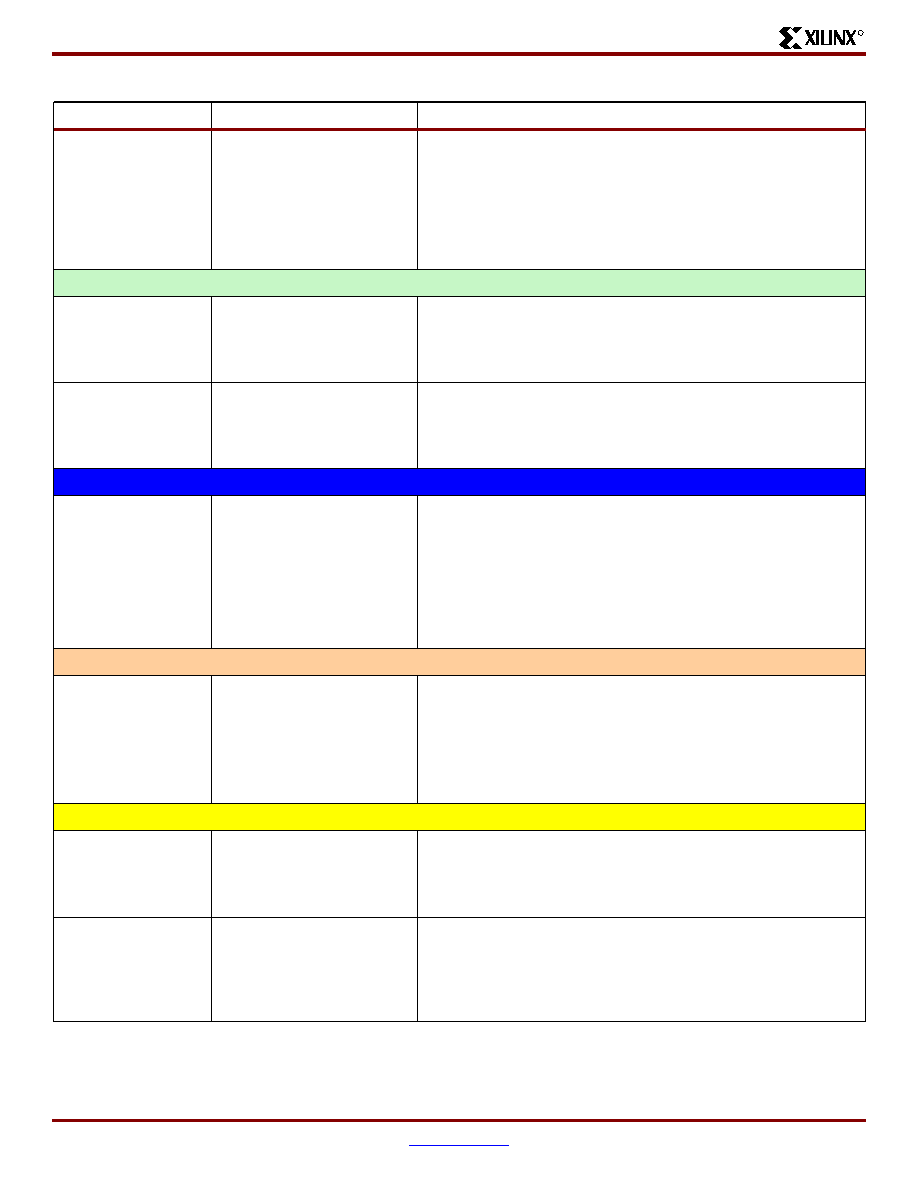

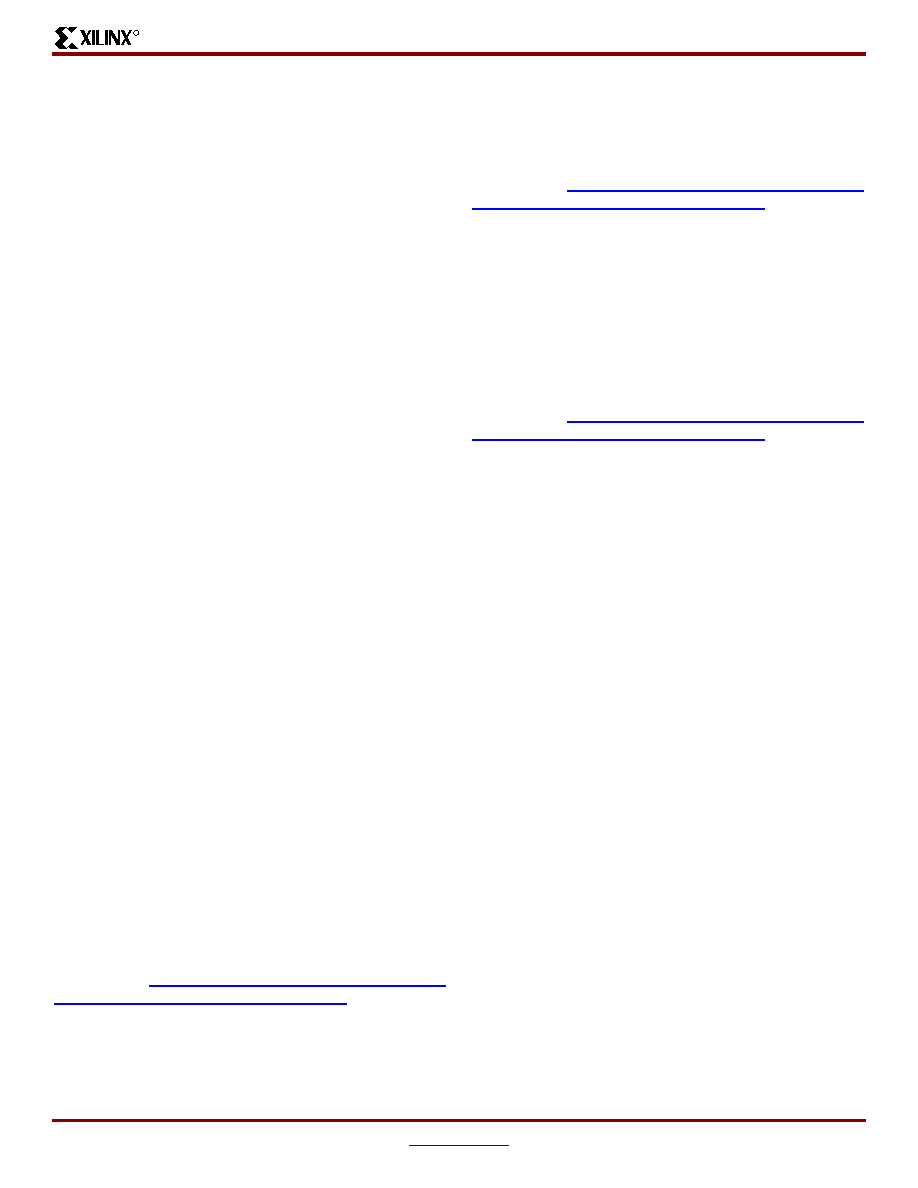

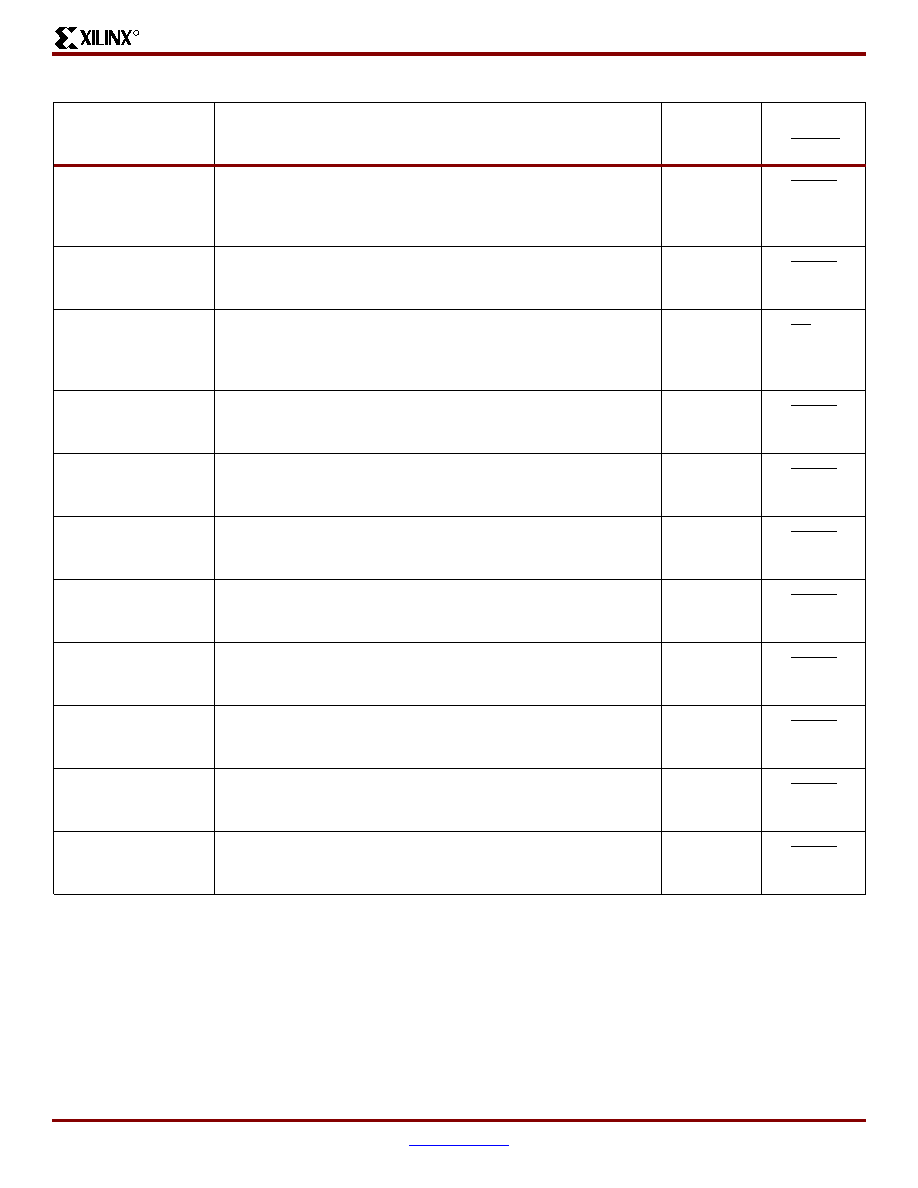

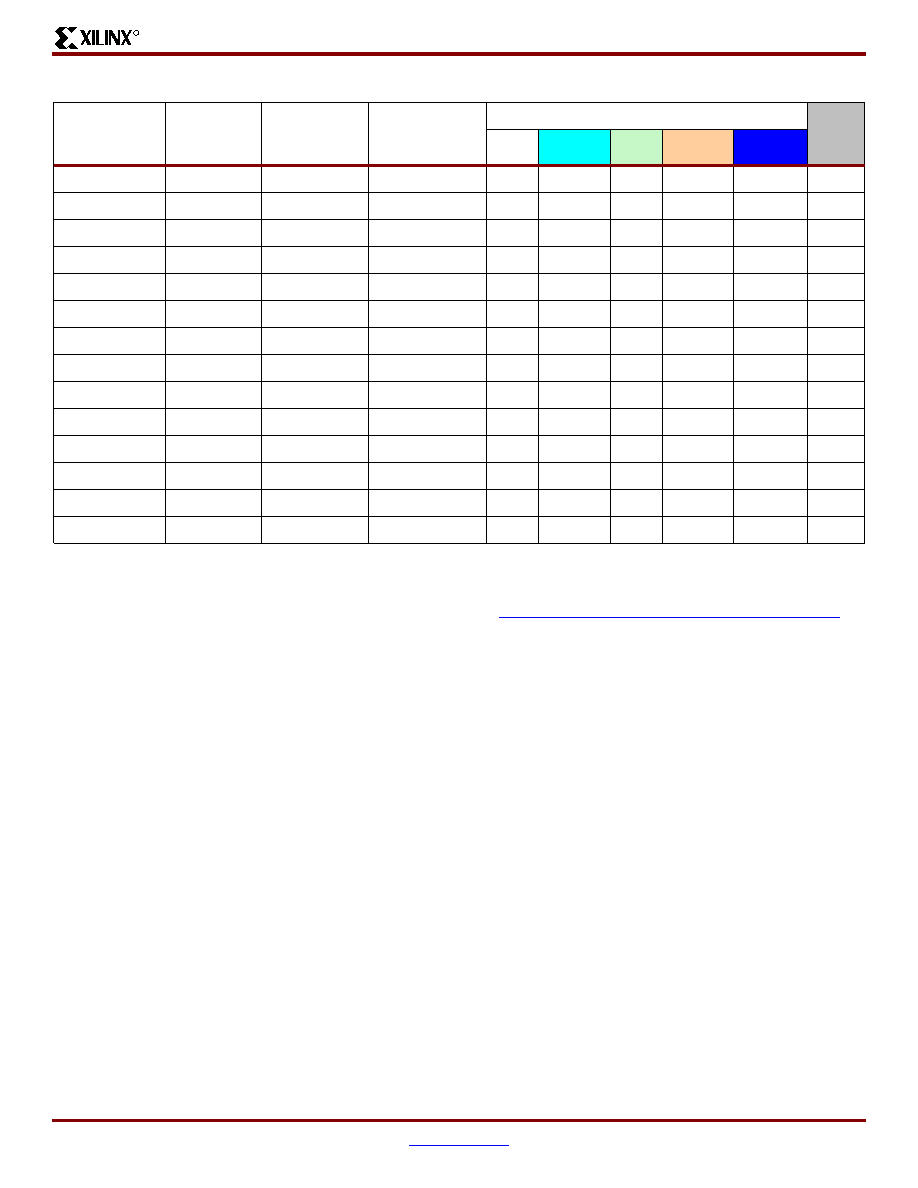

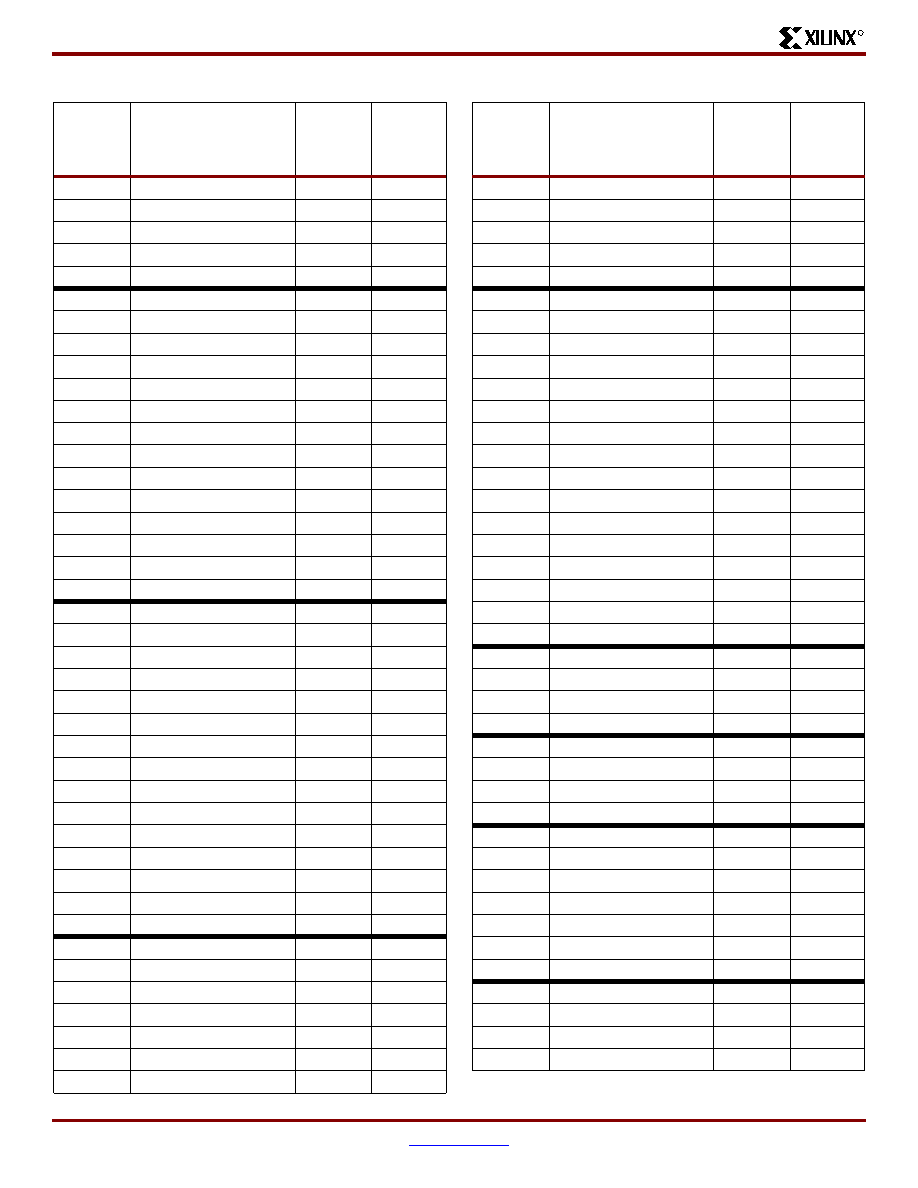

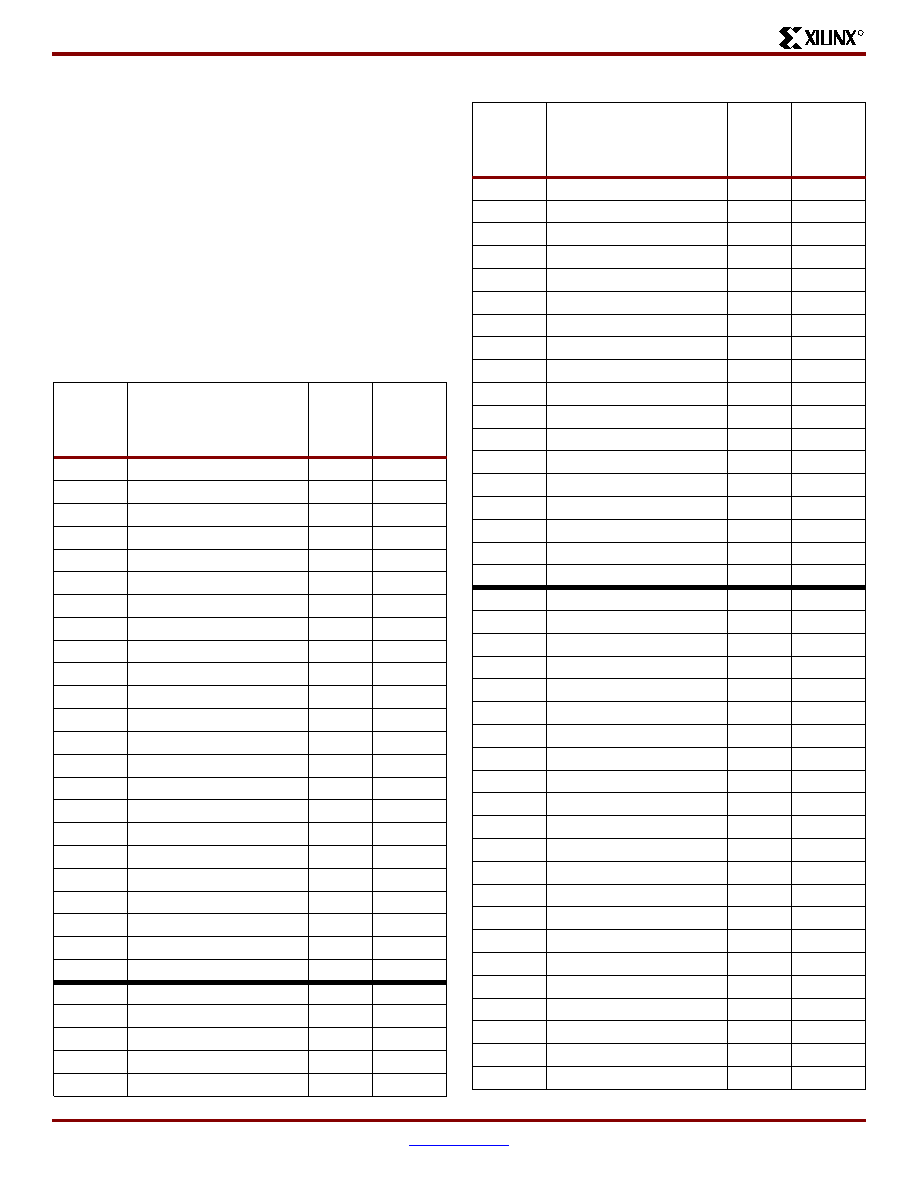

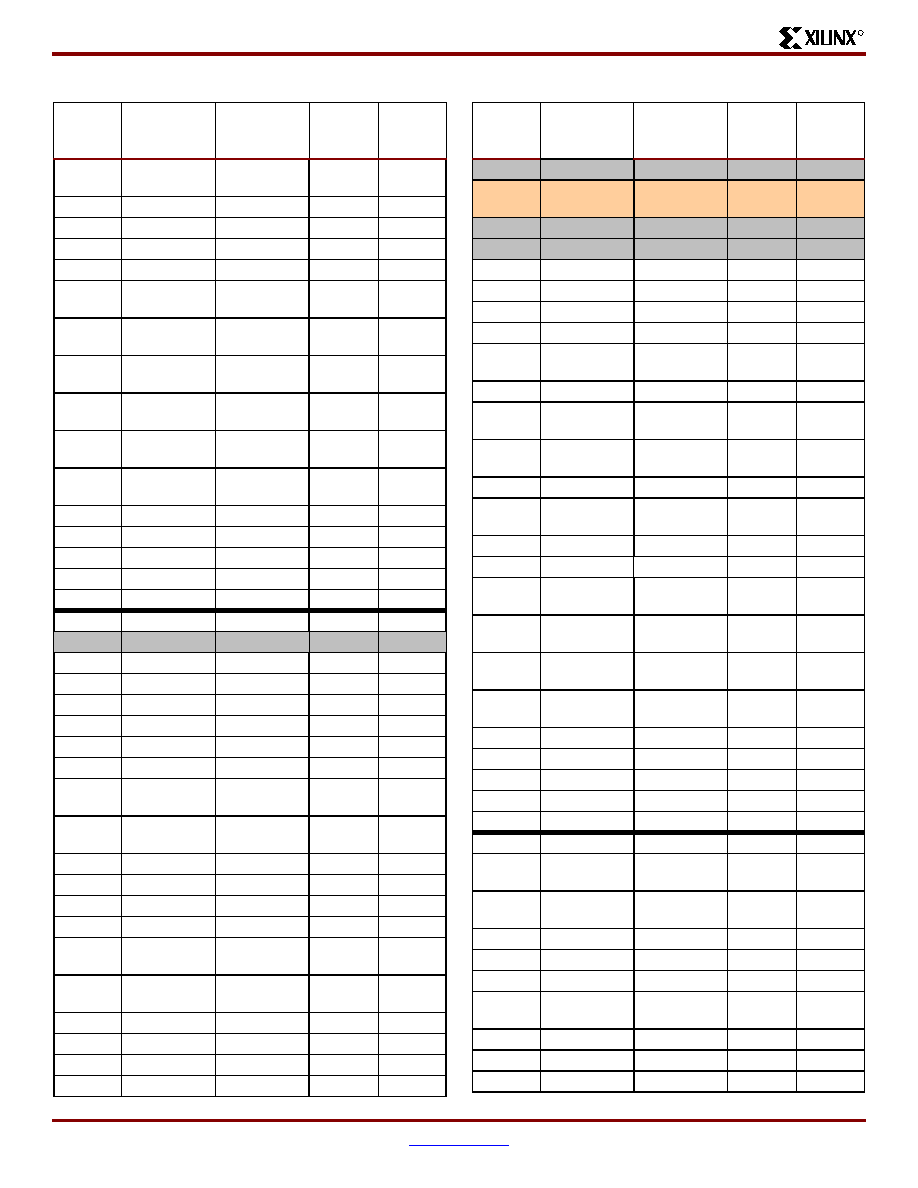

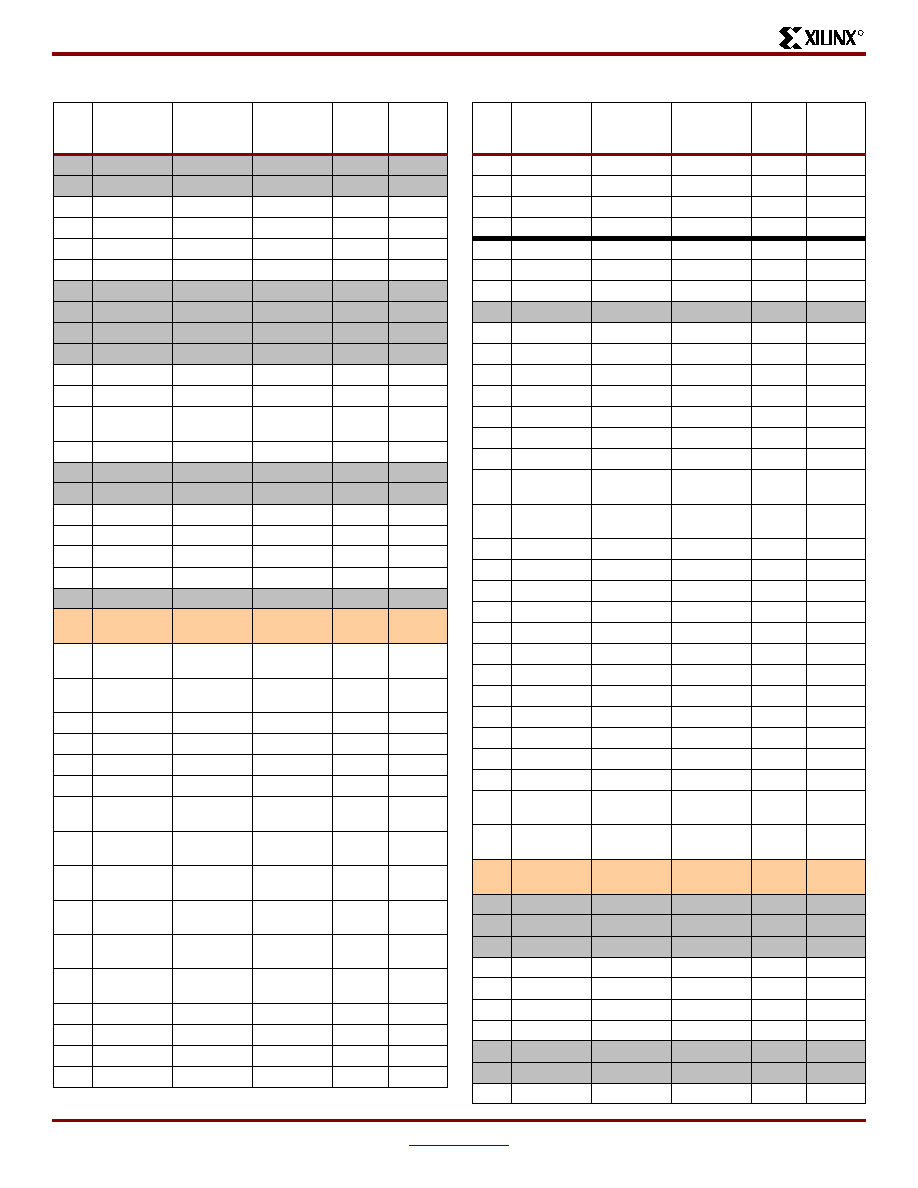

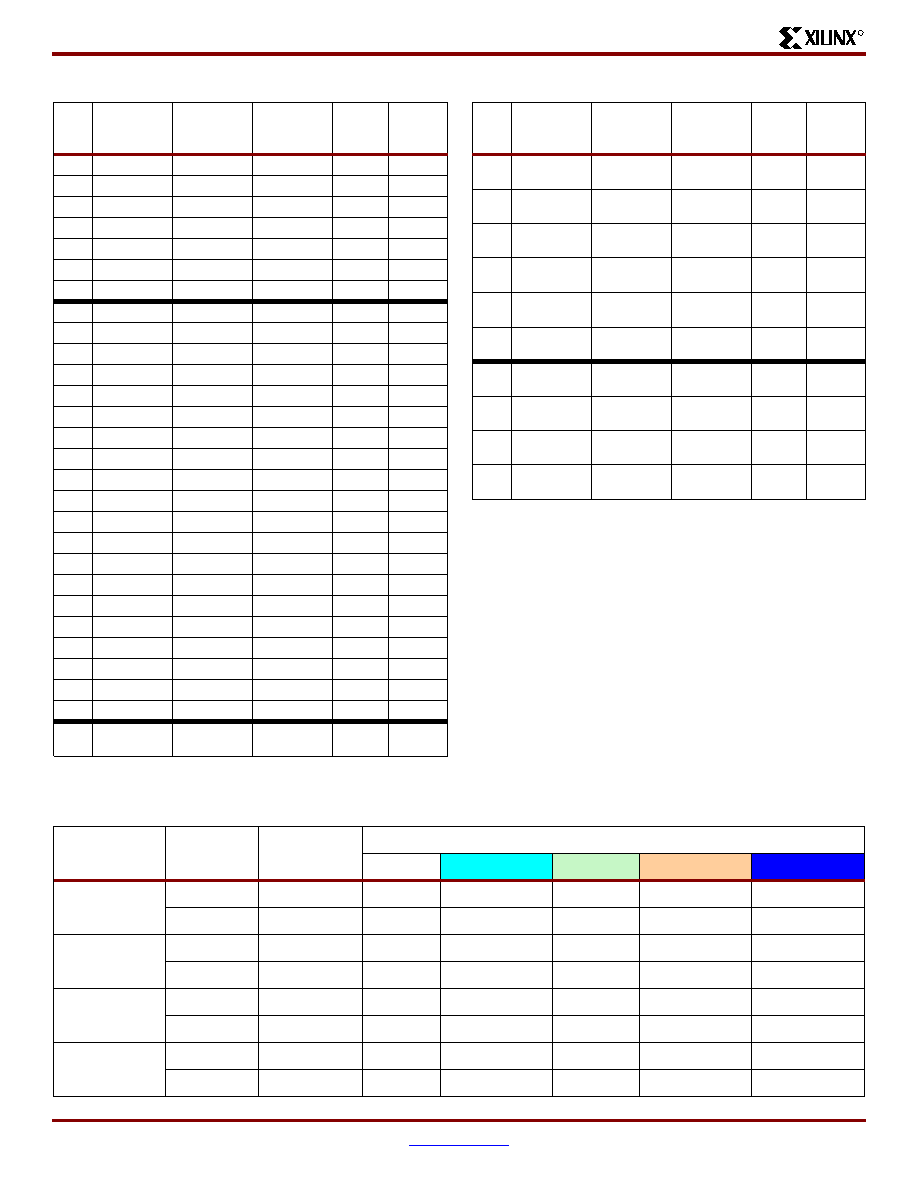

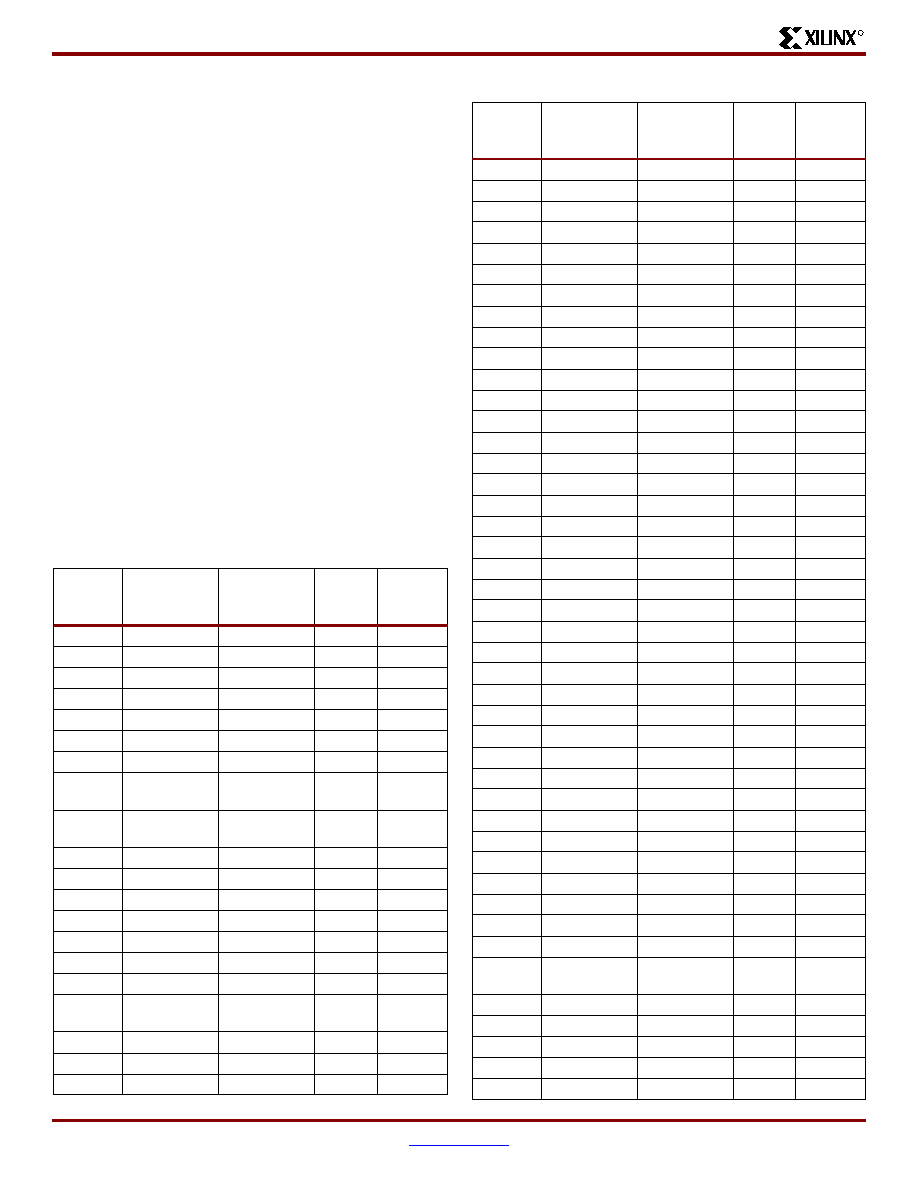

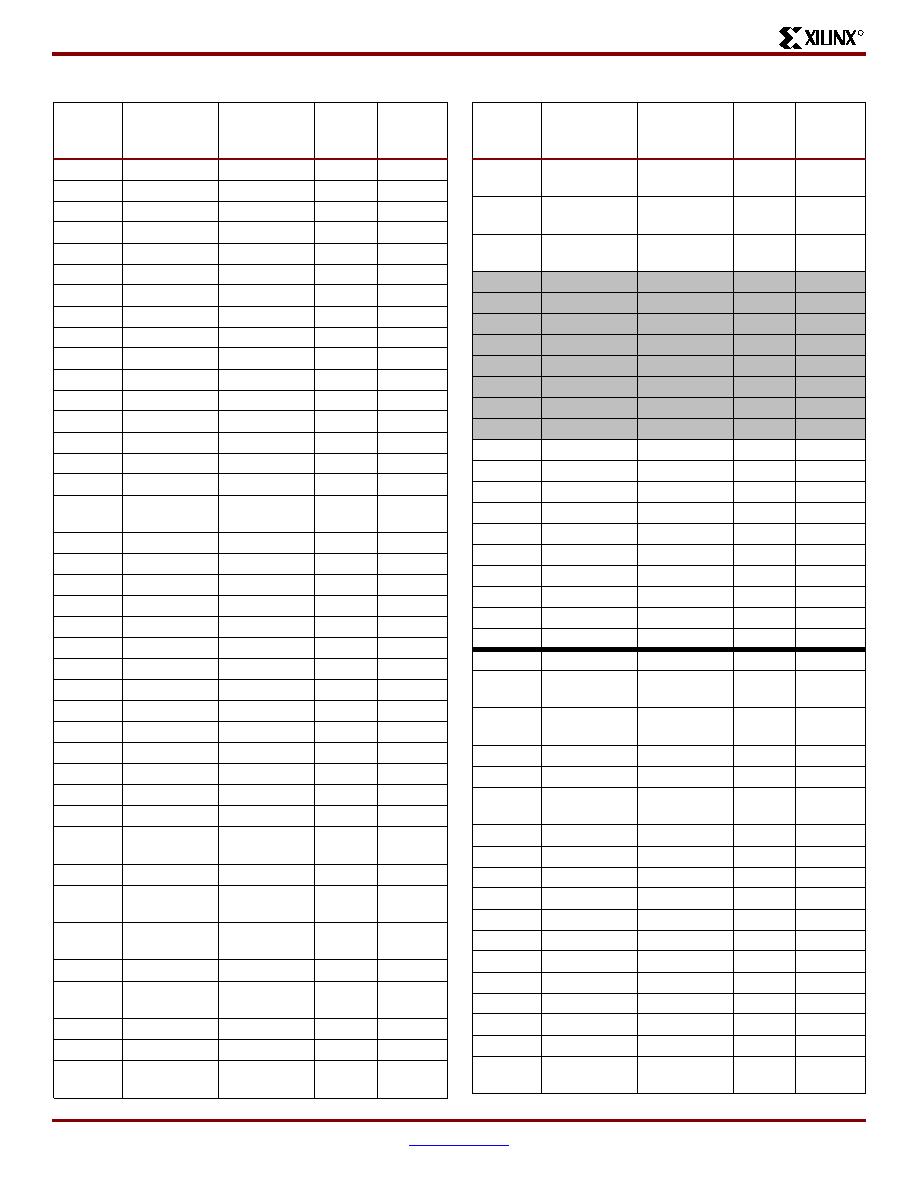

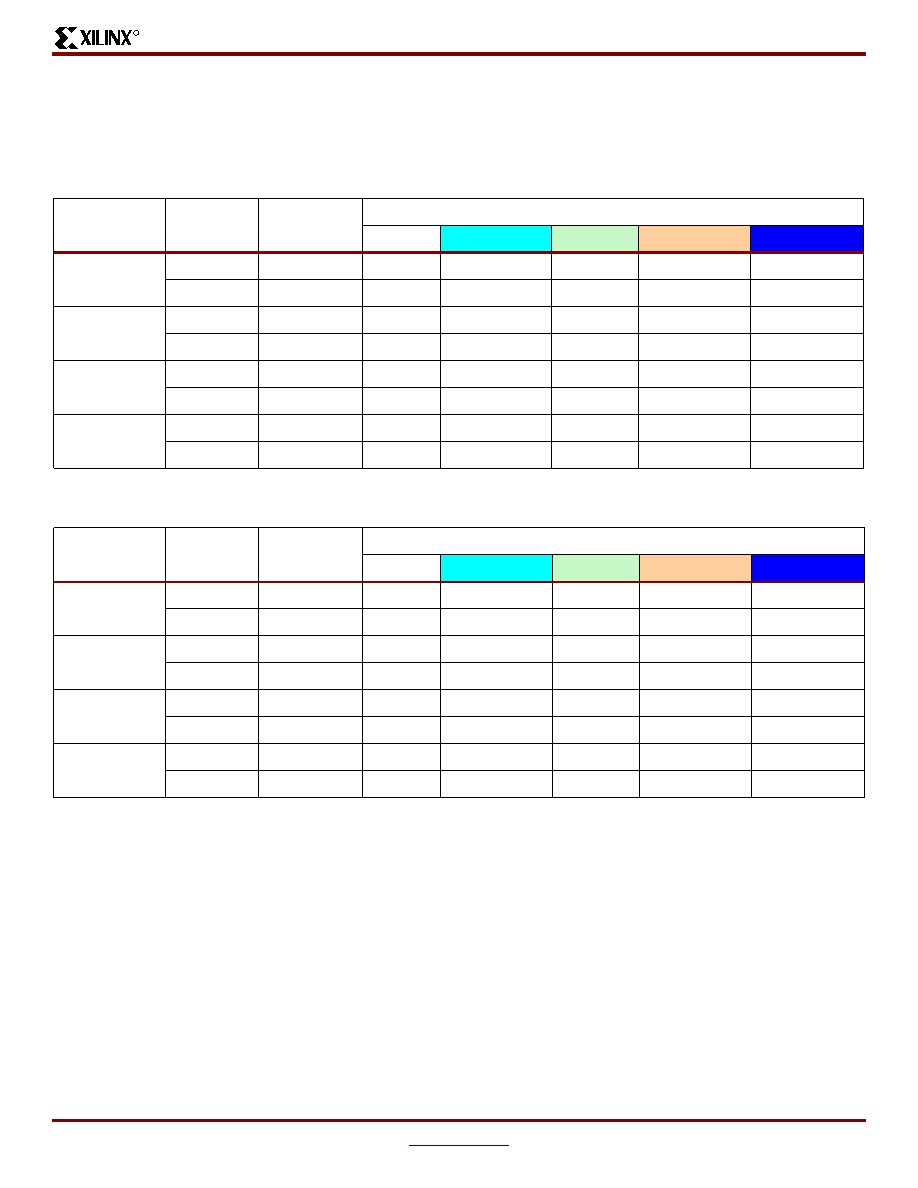

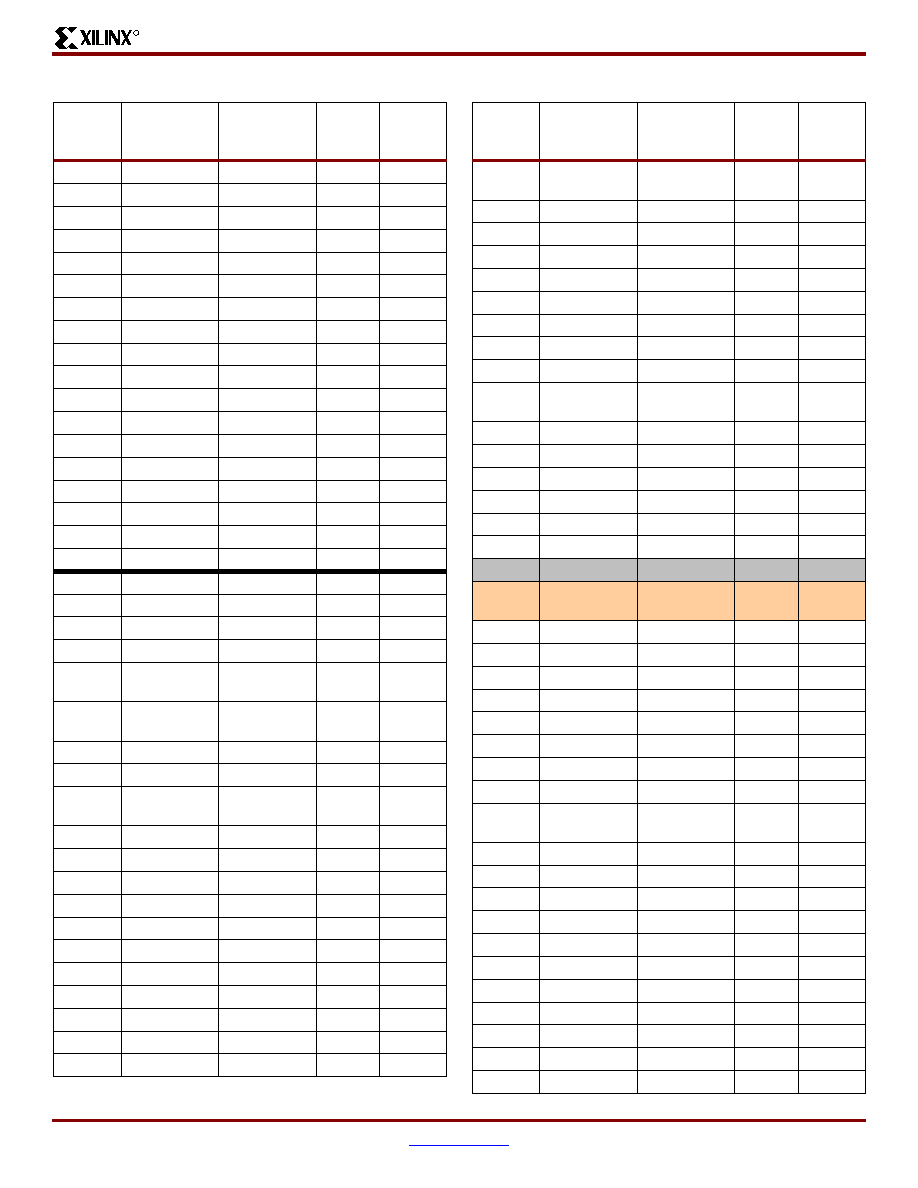

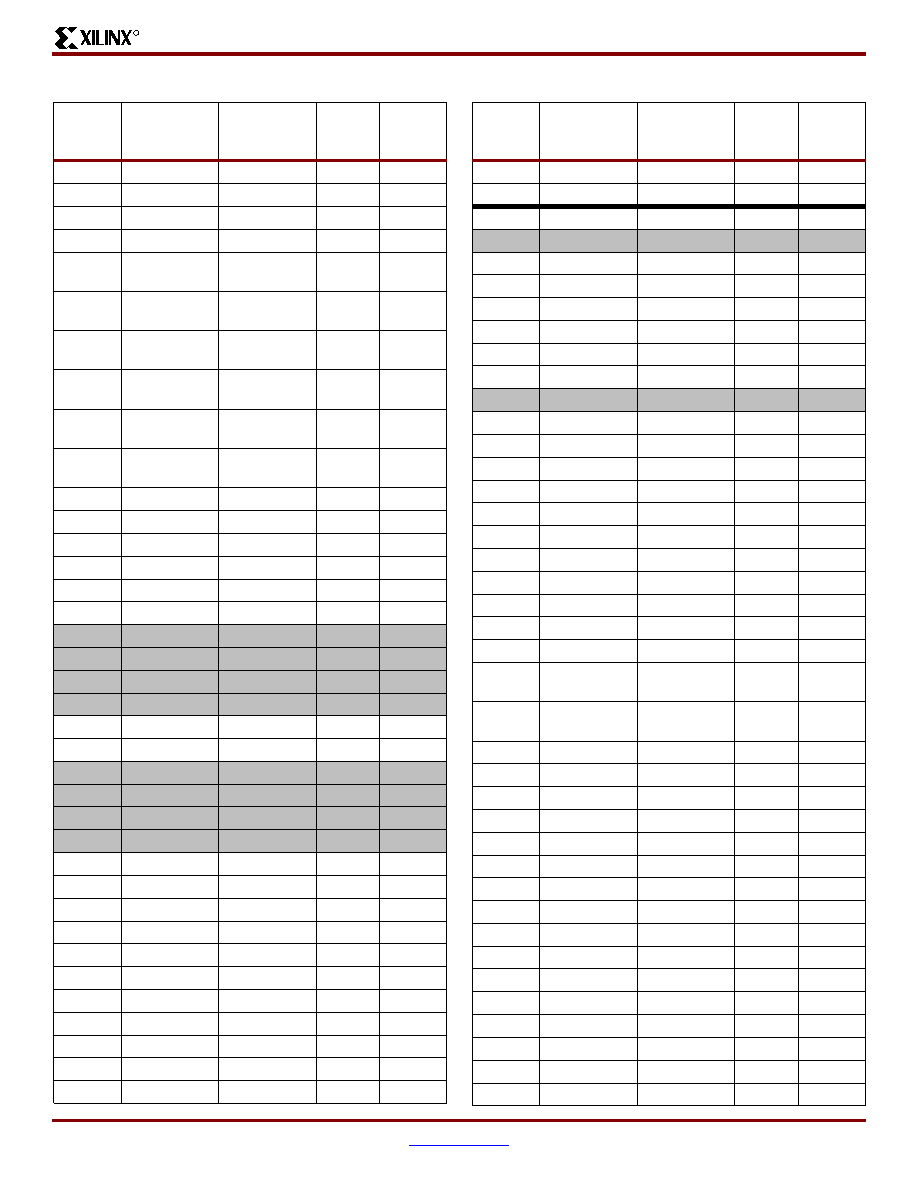

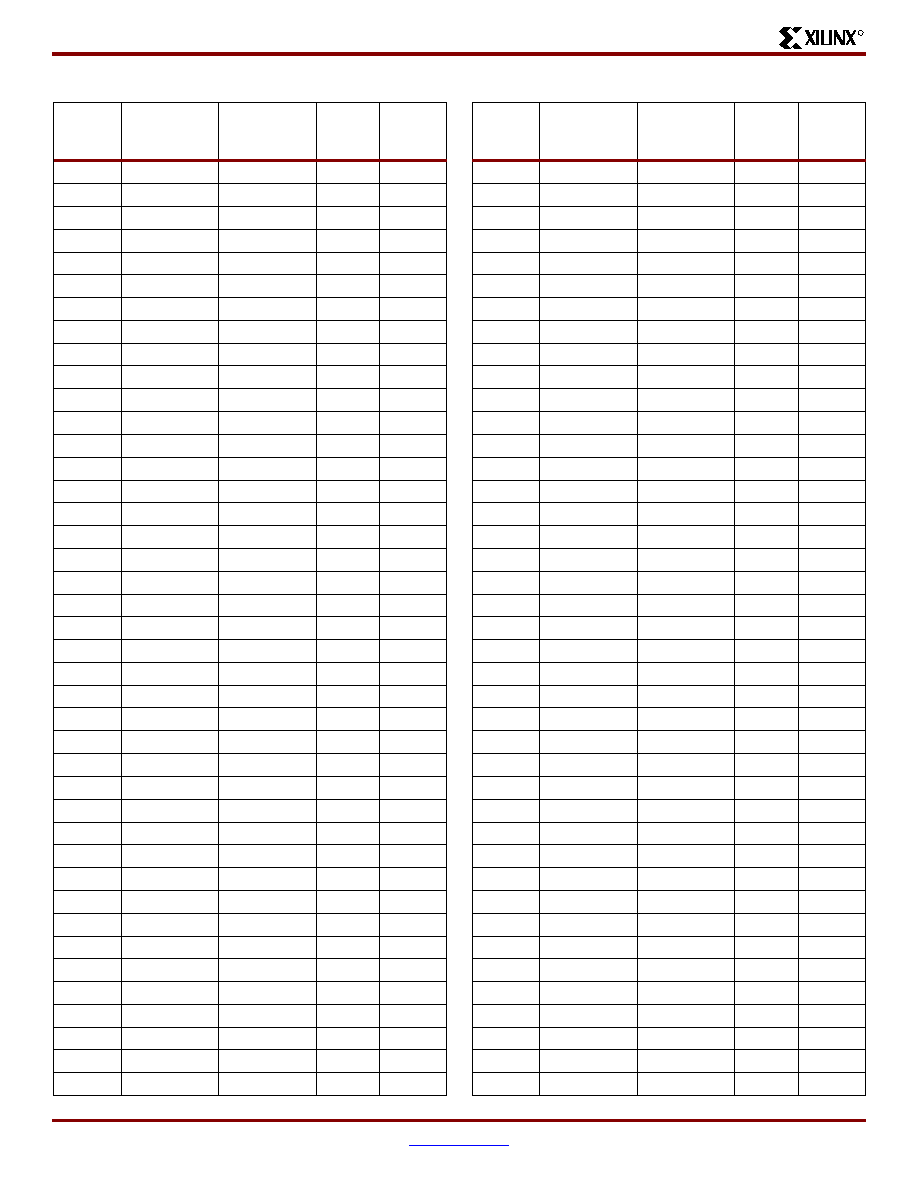

Table 1: Summary of Spartan-3 FPGA Attributes

Device

System

Gates

Logic

Cells

CLB Array

(One CLB = Four Slices)

Distributed

RAM (bits

1

)

Block RAM

(bits

1

)

Dedicated

Multipliers

DCMs

Maximum

User I/O

Maximum

Differential

I/O Pairs

Rows

Columns Total CLBs

XC3S50

50K

1,728

16

12

192

12K

72K

4

2

124

56

XC3S200

200K

4,320

24

20

480

30K

216K

12

4

173

76

XC3S400

400K

8,064

32

28

896

56K

288K

16

4

264

116

XC3S1000

1M

17,280

48

40

1,920

120K

432K

24

4

391

175

XC3S1500

1.5M

29,952

64

52

3,328

208K

576K

32

4

487

221

XC3S2000

2M

46,080

80

64

5,120

320K

720K

40

4

565

270

XC3S4000

4M

62,208

96

72

6,912

432K

1,728K

96

4

712

312

XC3S5000

5M

74,880

104

80

8,320

520K

1,872K

104

4

784

344

Notes:

1.

By convention, one Kb is equivalent to 1,024 bits.

Spartan-3 1.2V FPGA Family: Introduction and Ordering Information

2

www.xilinx.com

DS099-1 (v1.1) April 24, 2003

1-800-255-7778

Advance Product Specification

6

R

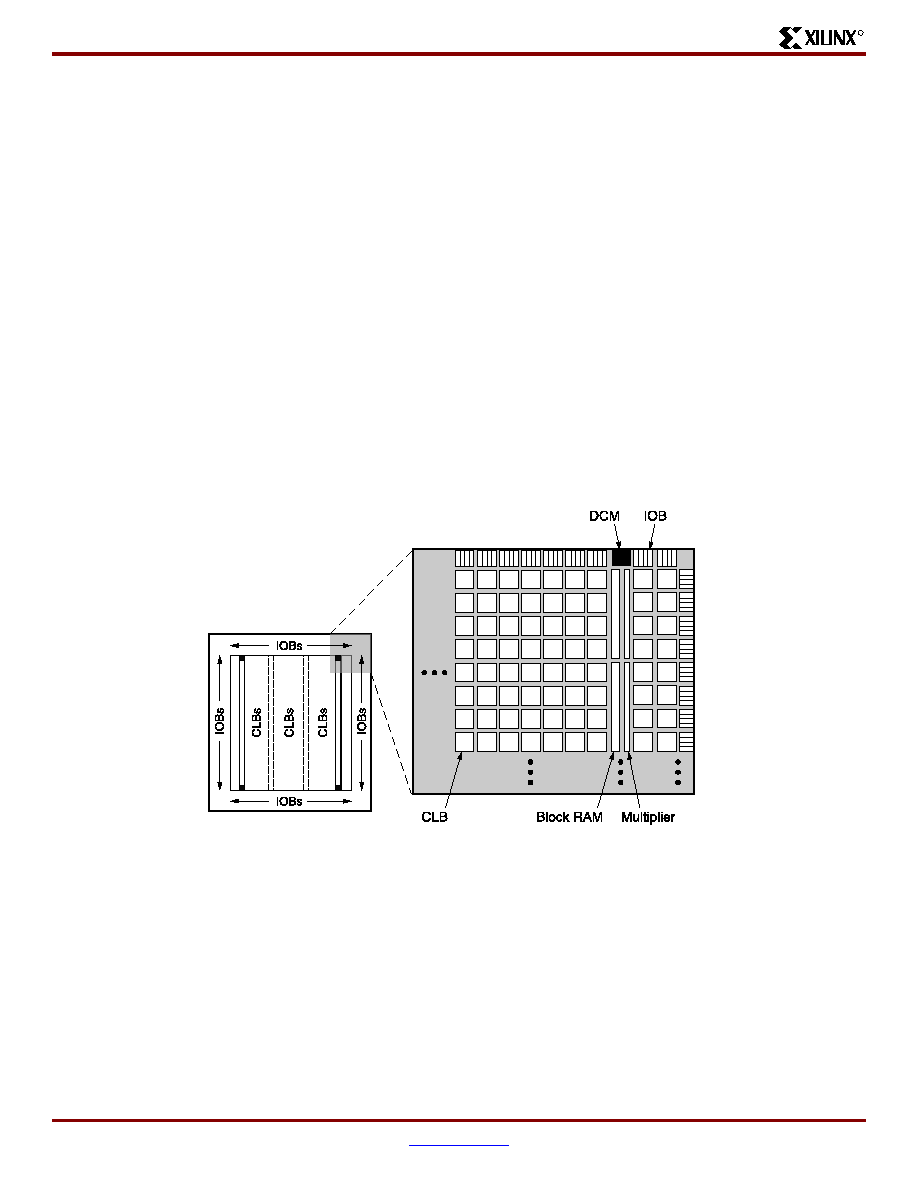

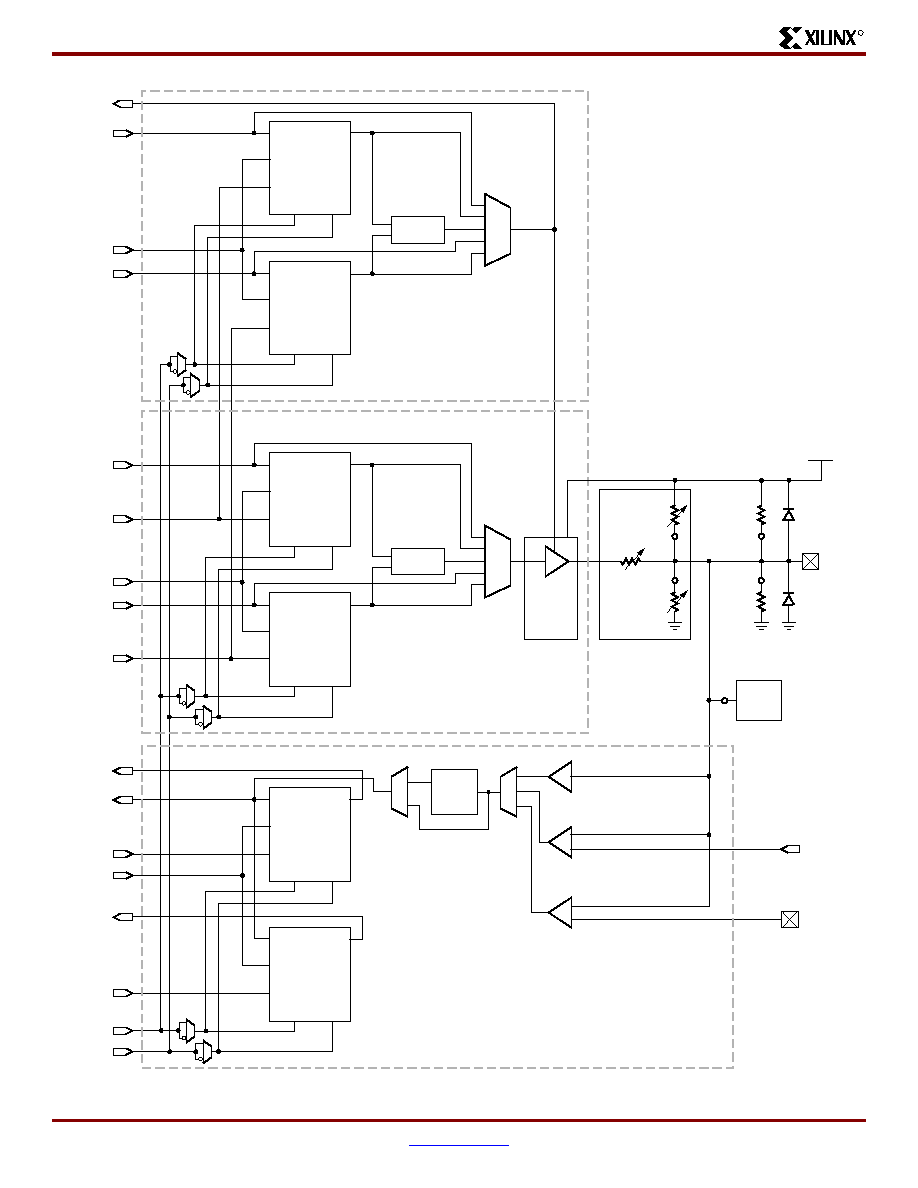

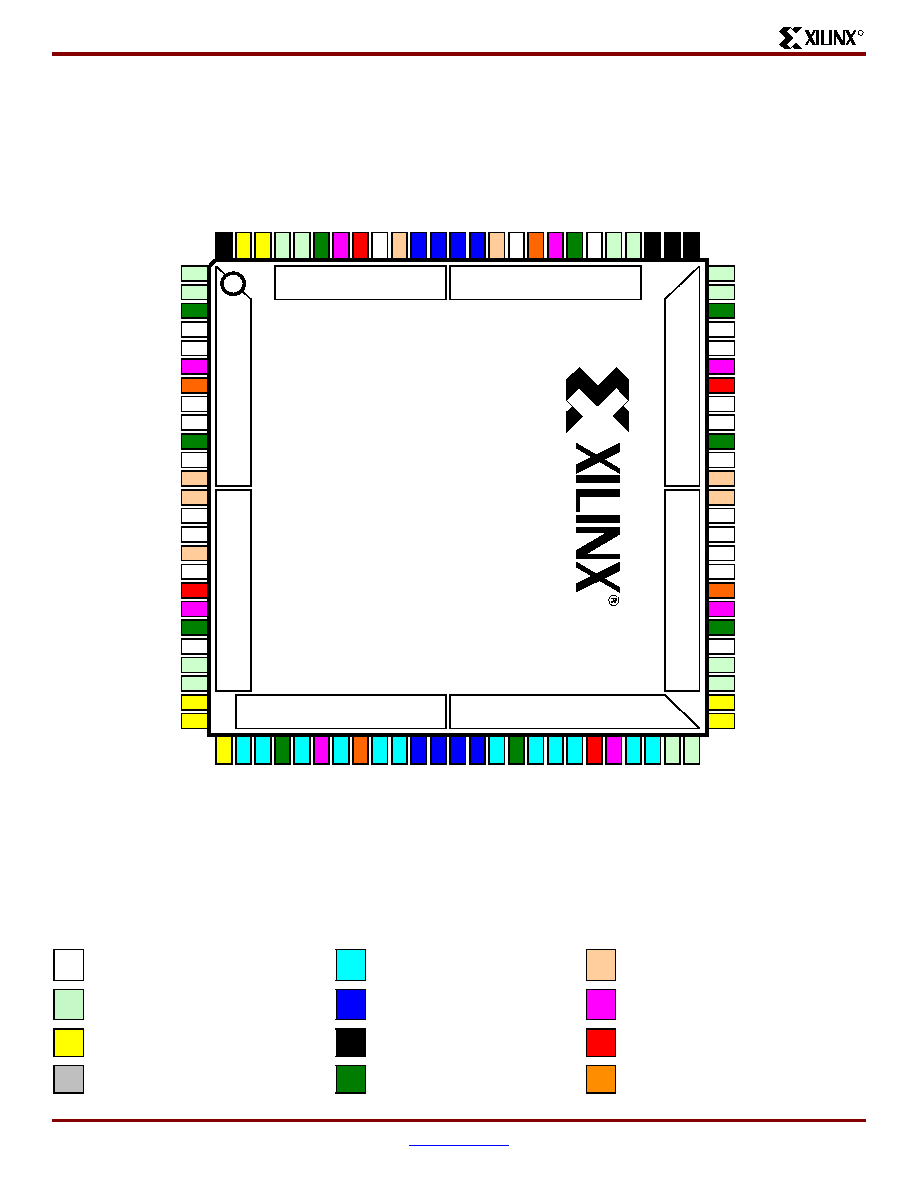

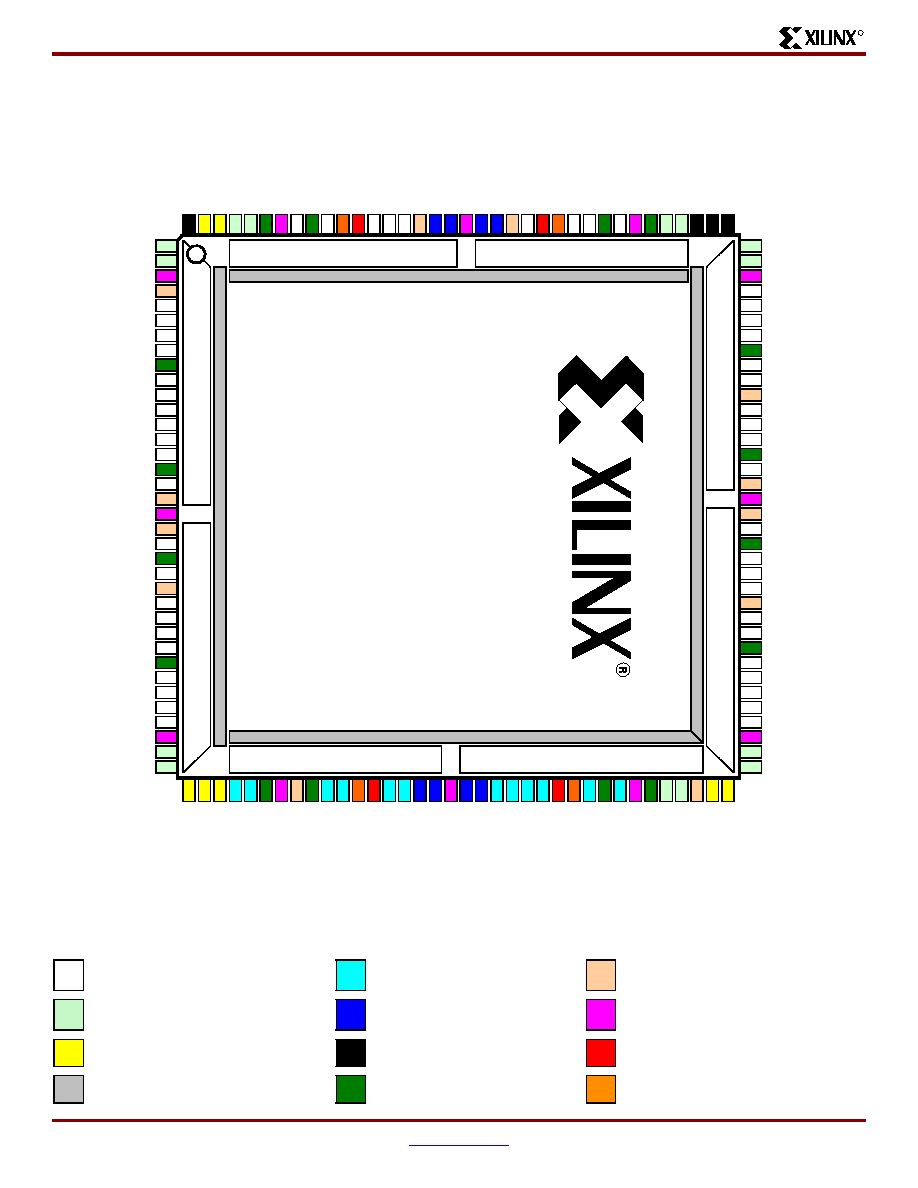

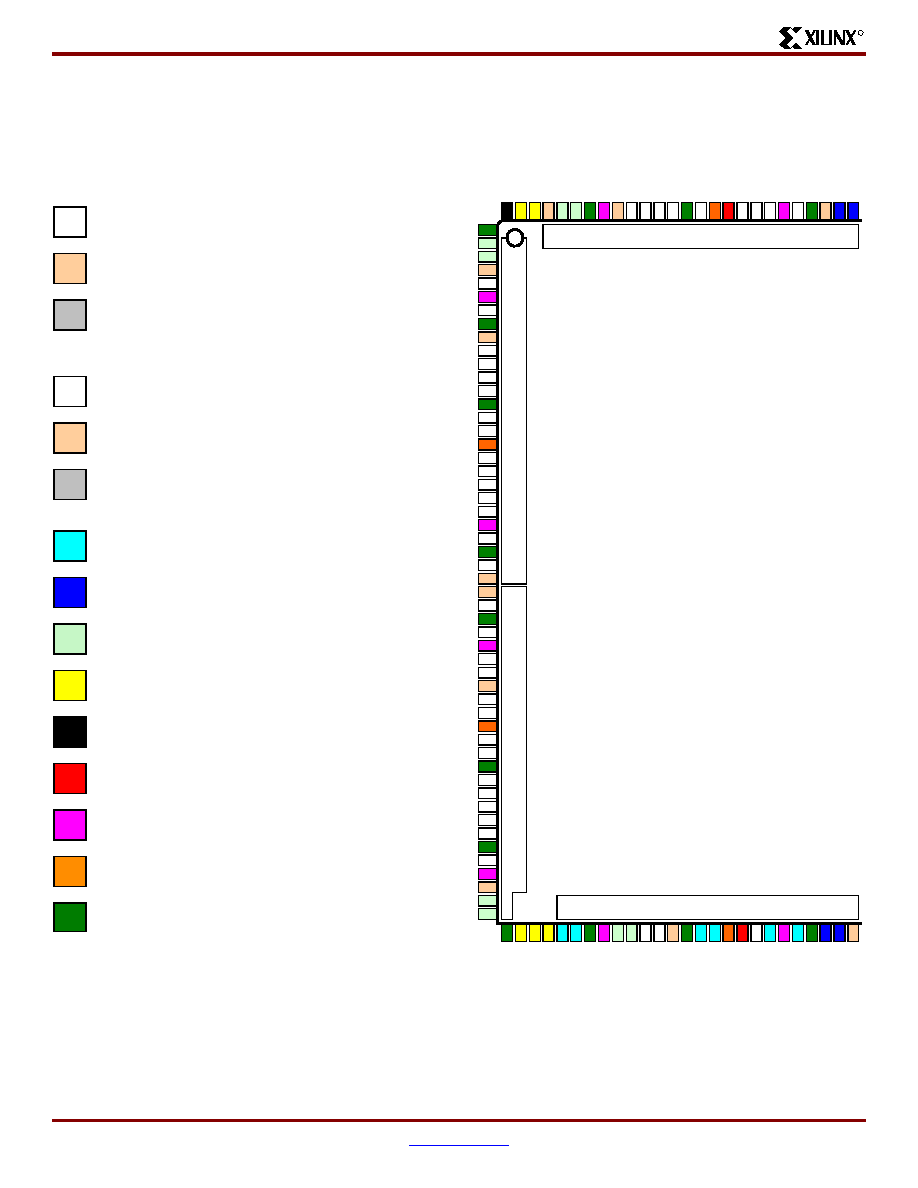

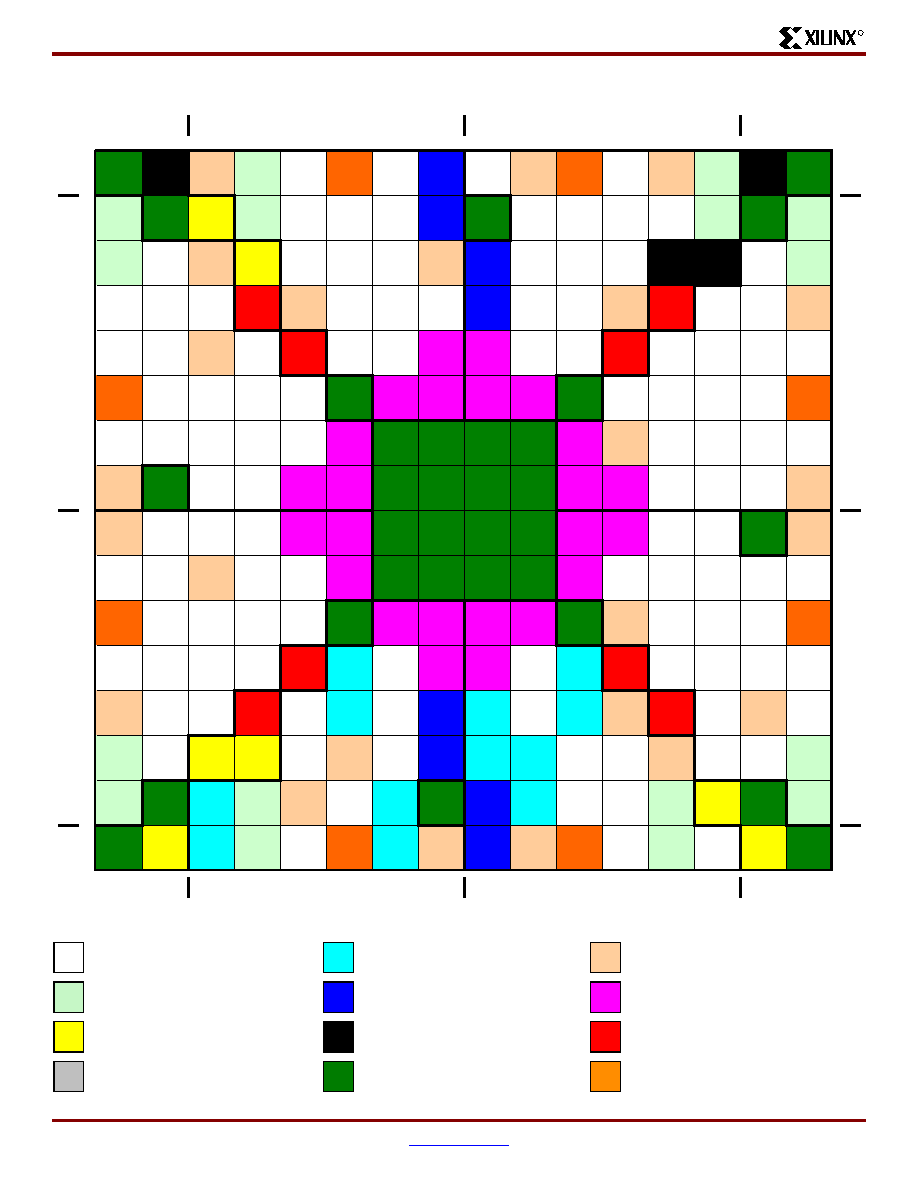

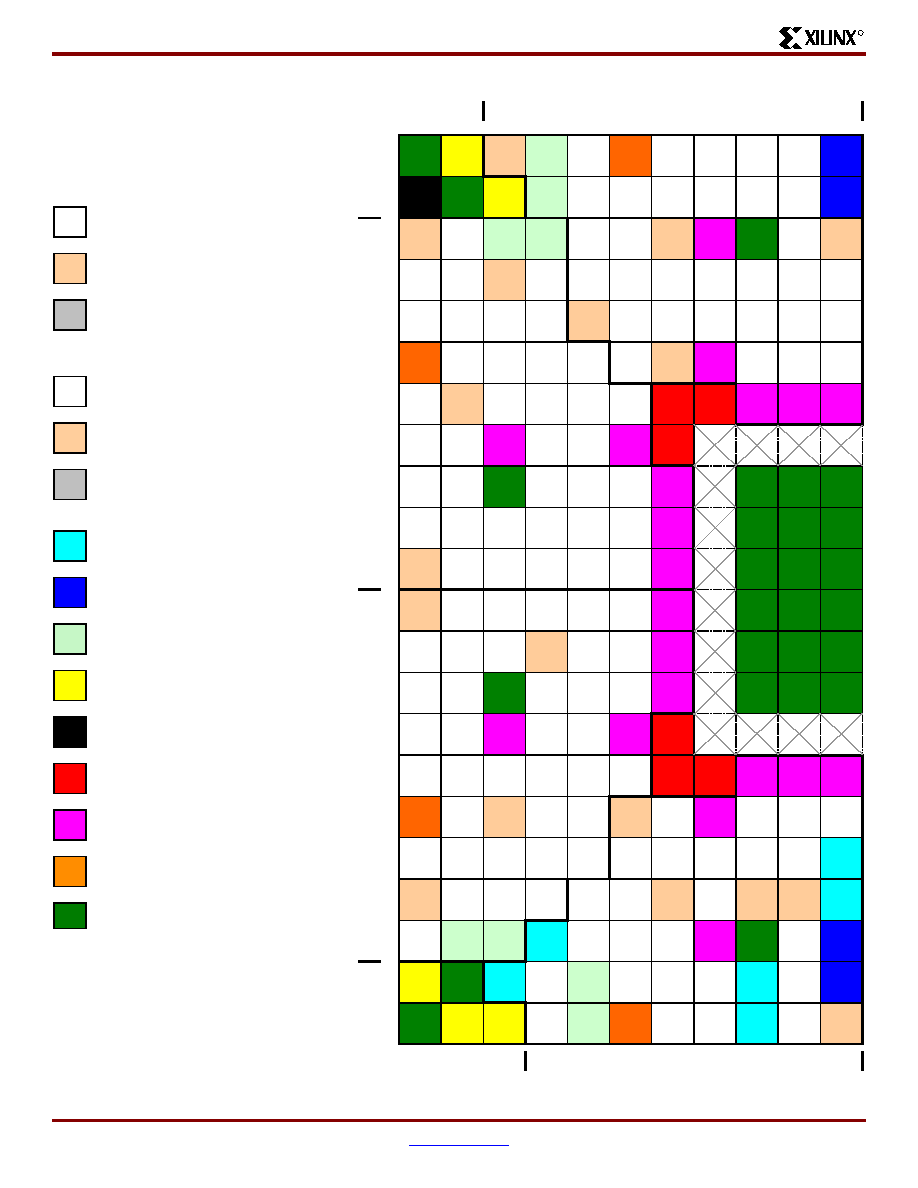

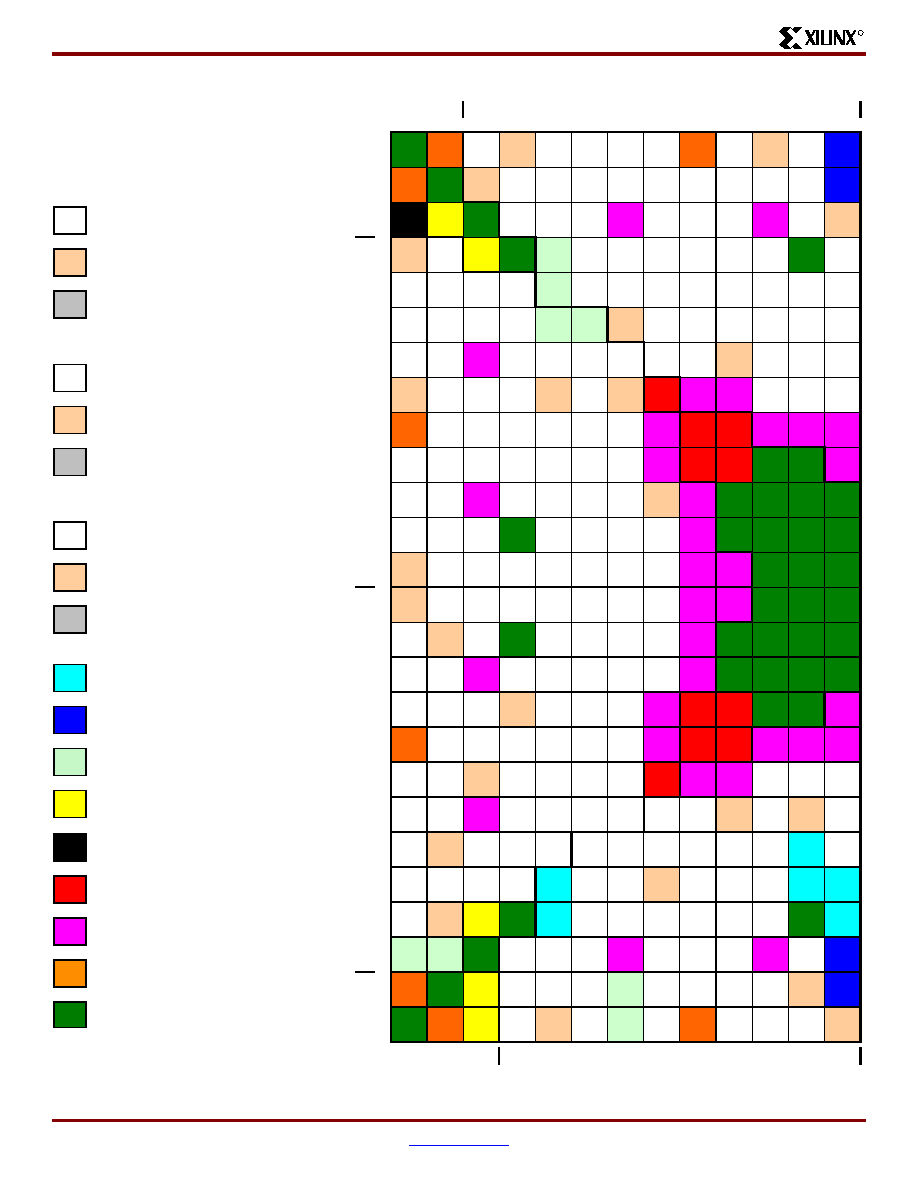

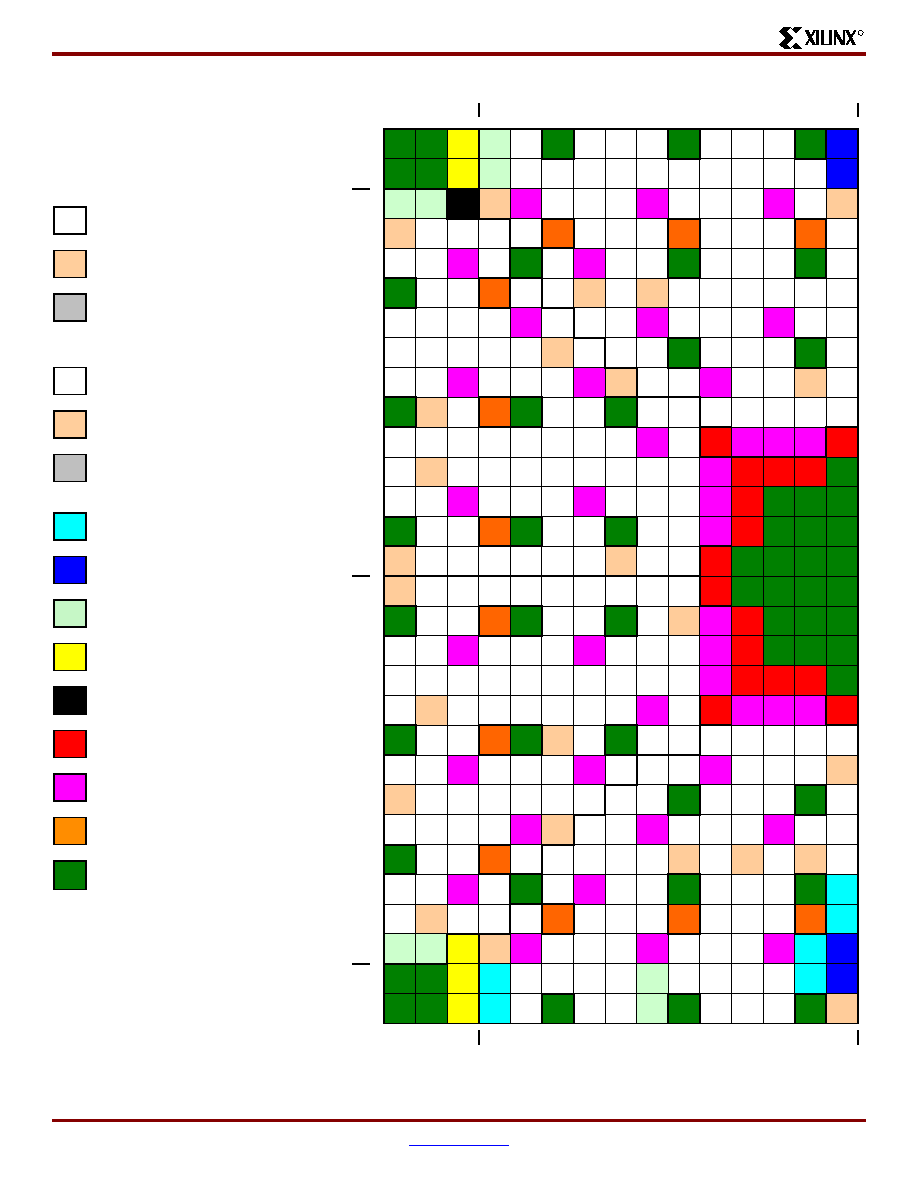

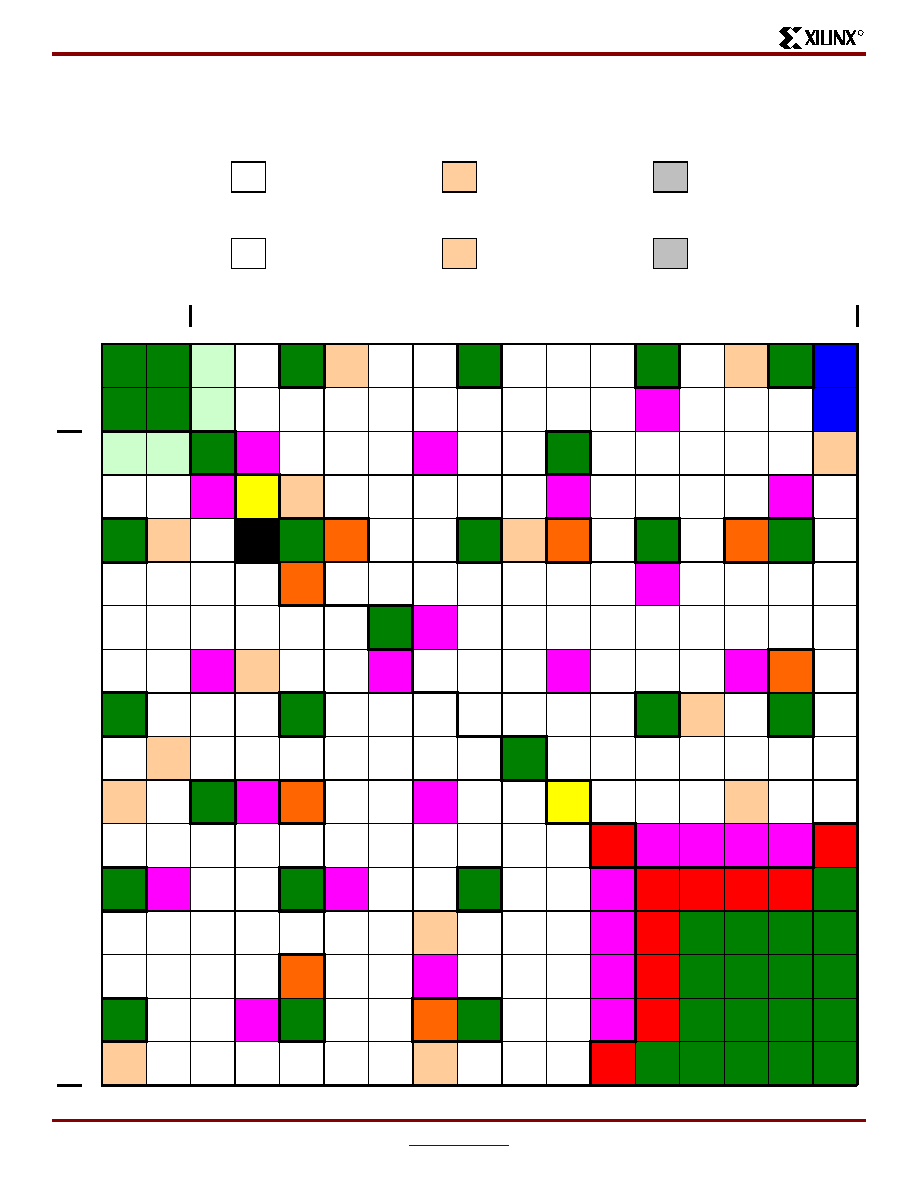

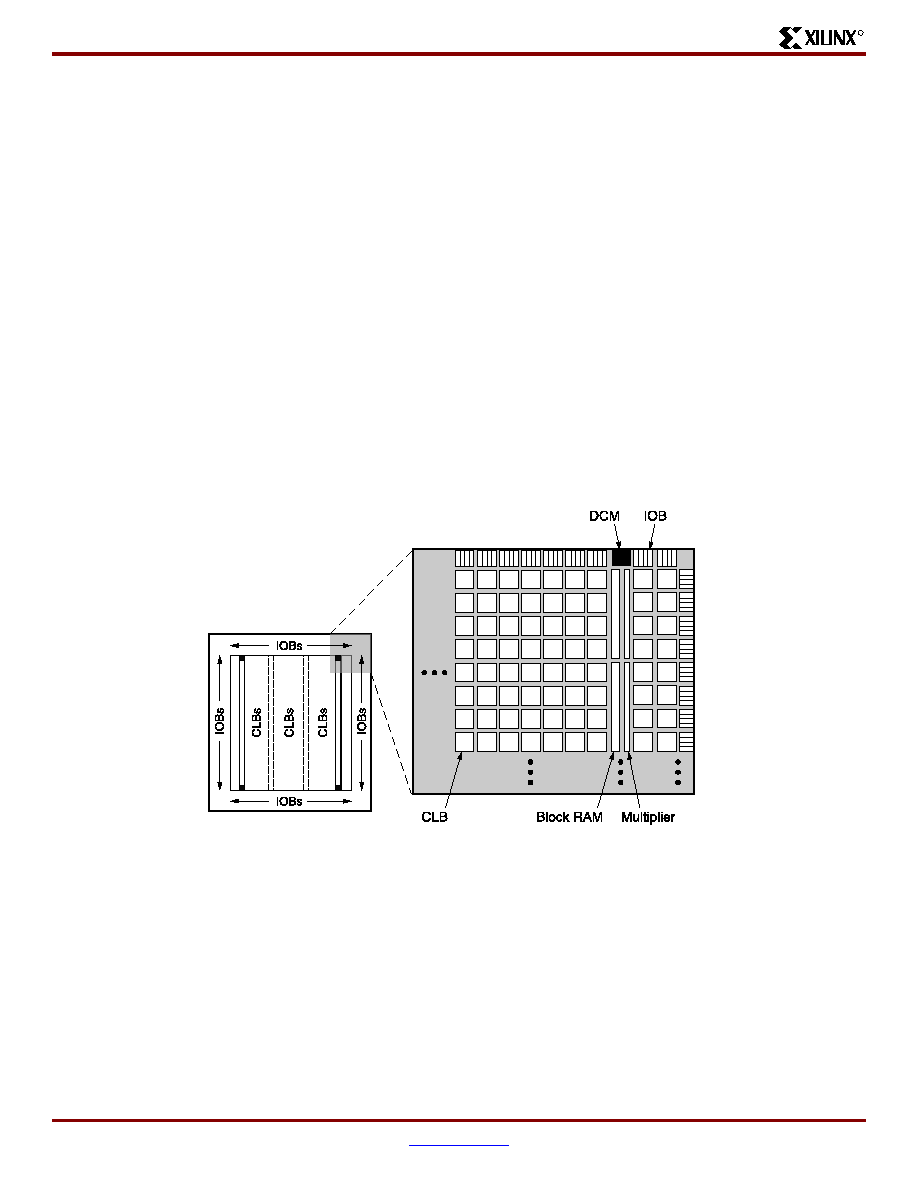

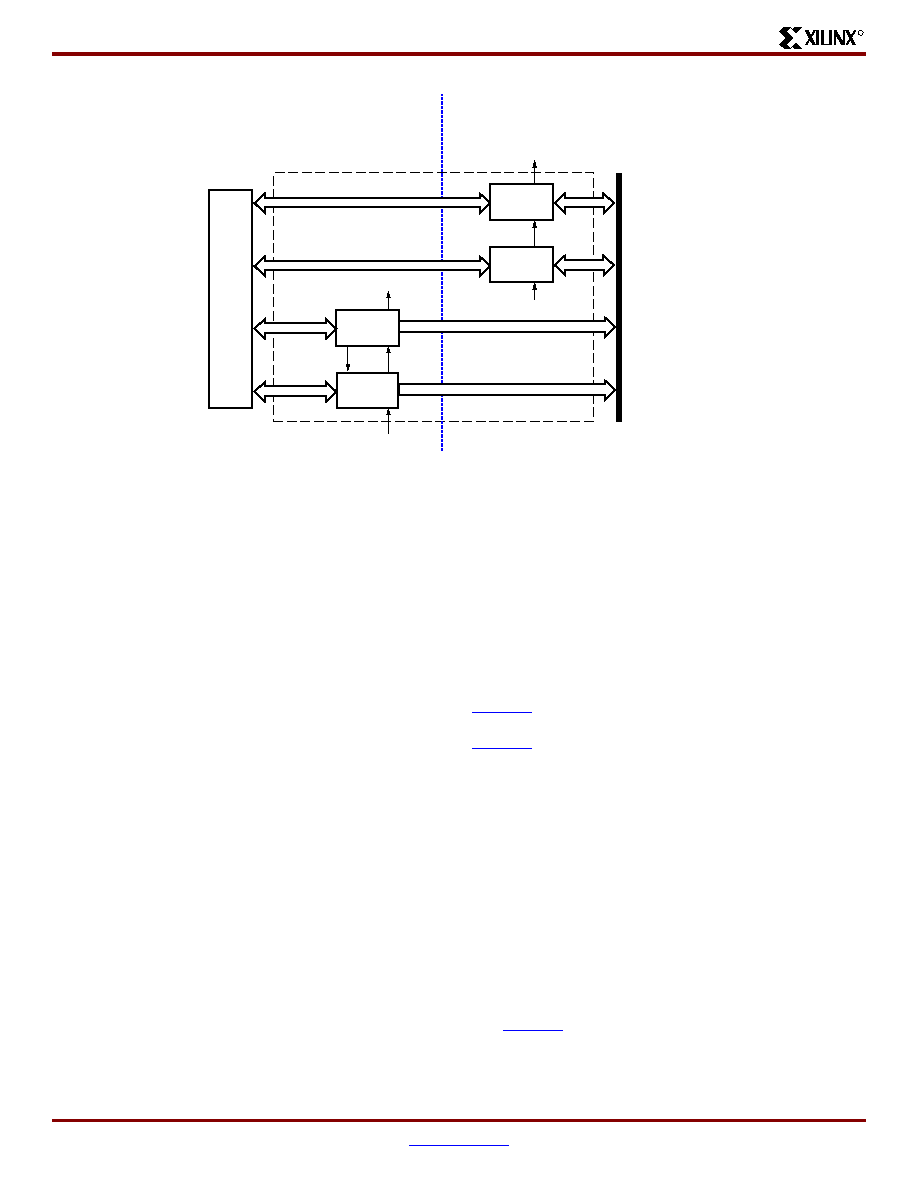

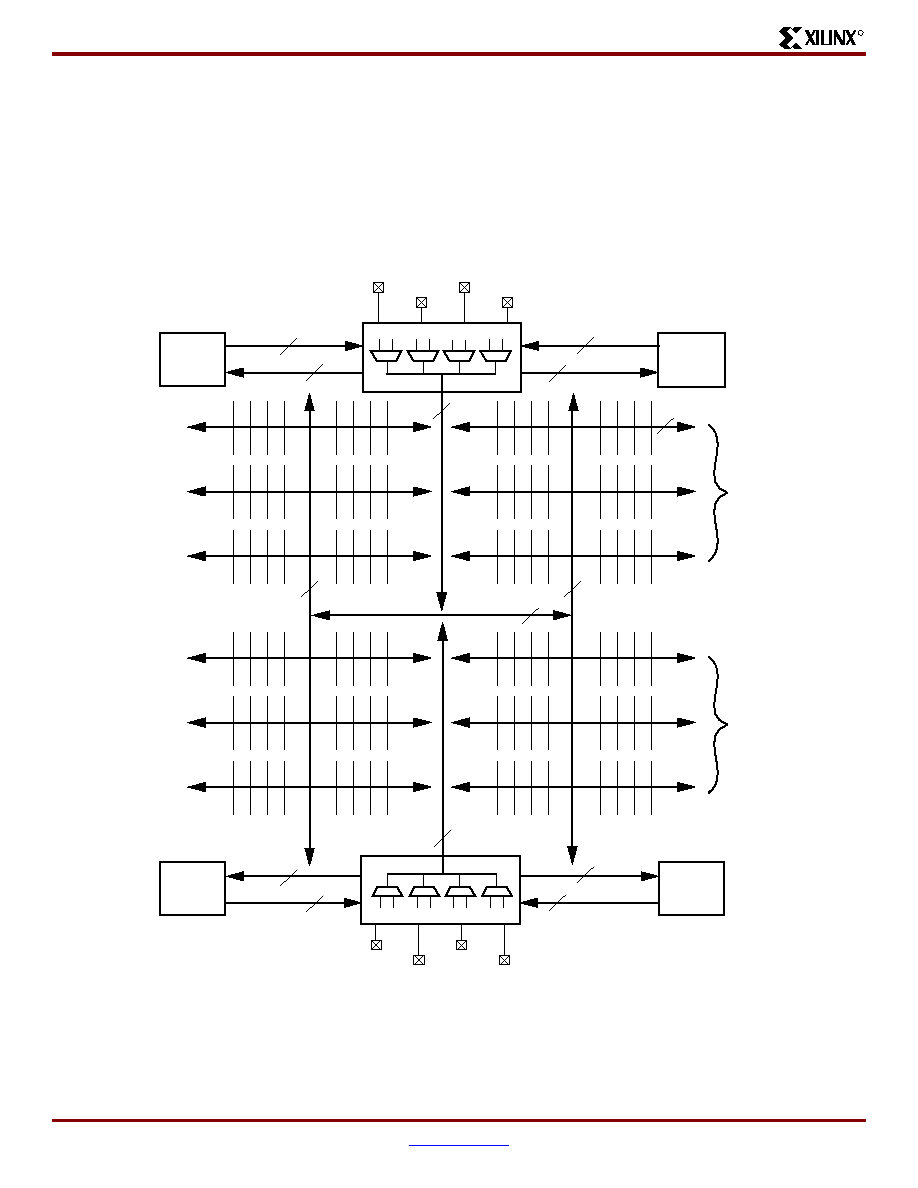

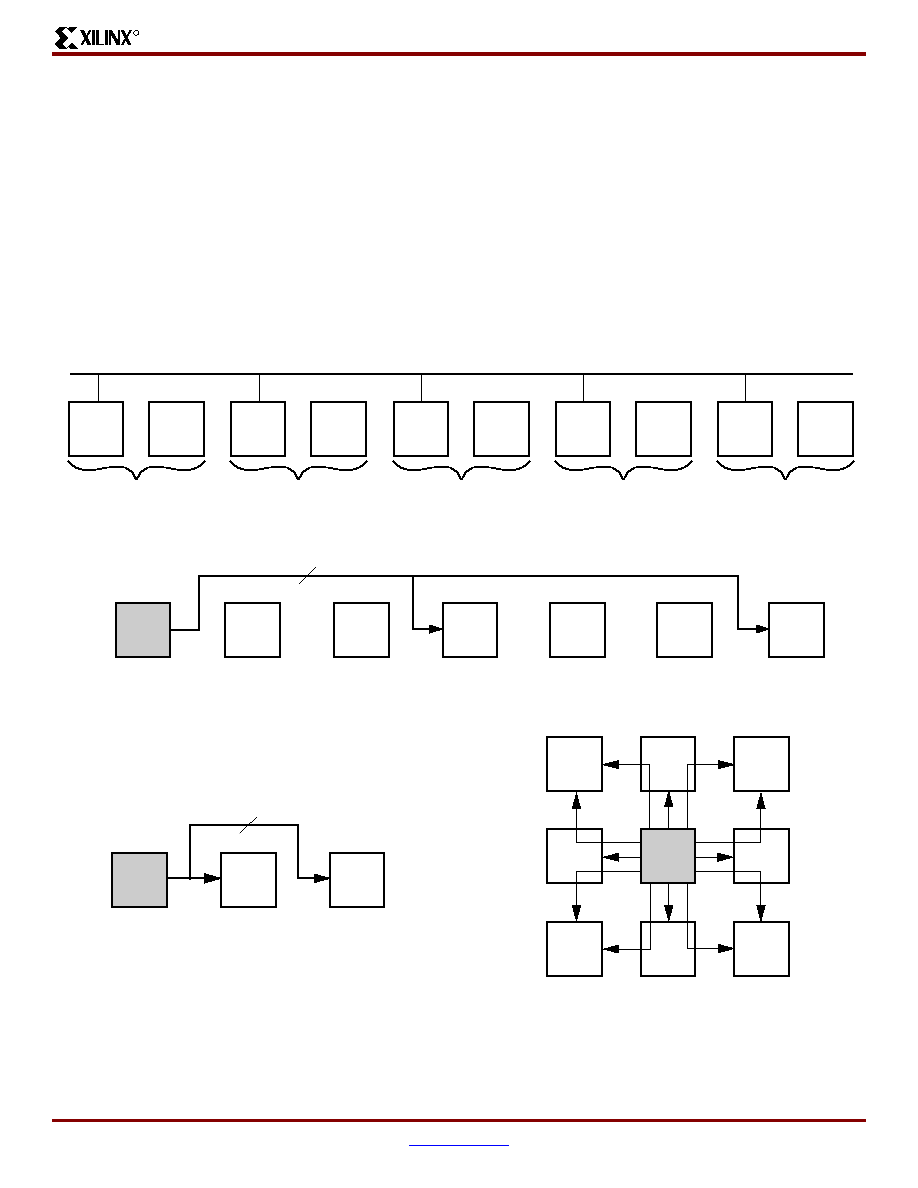

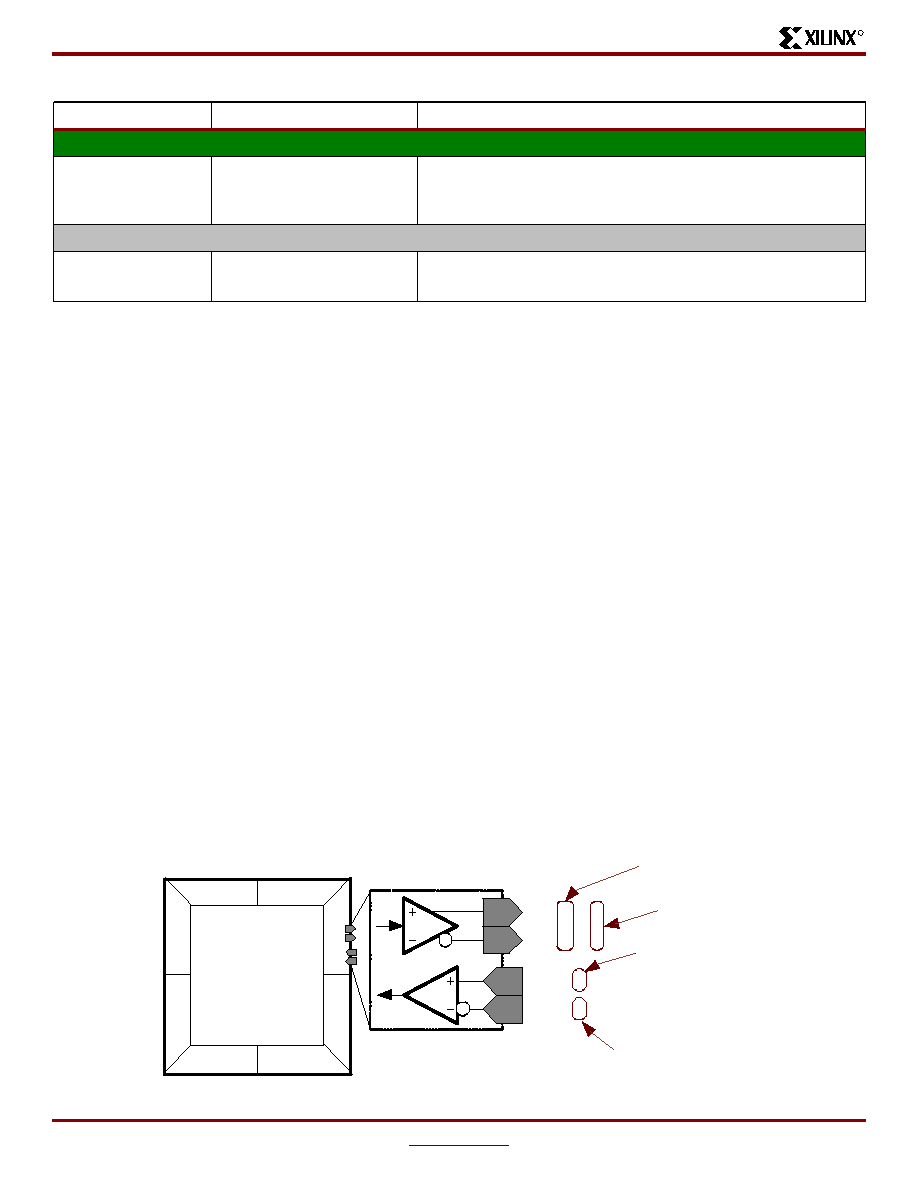

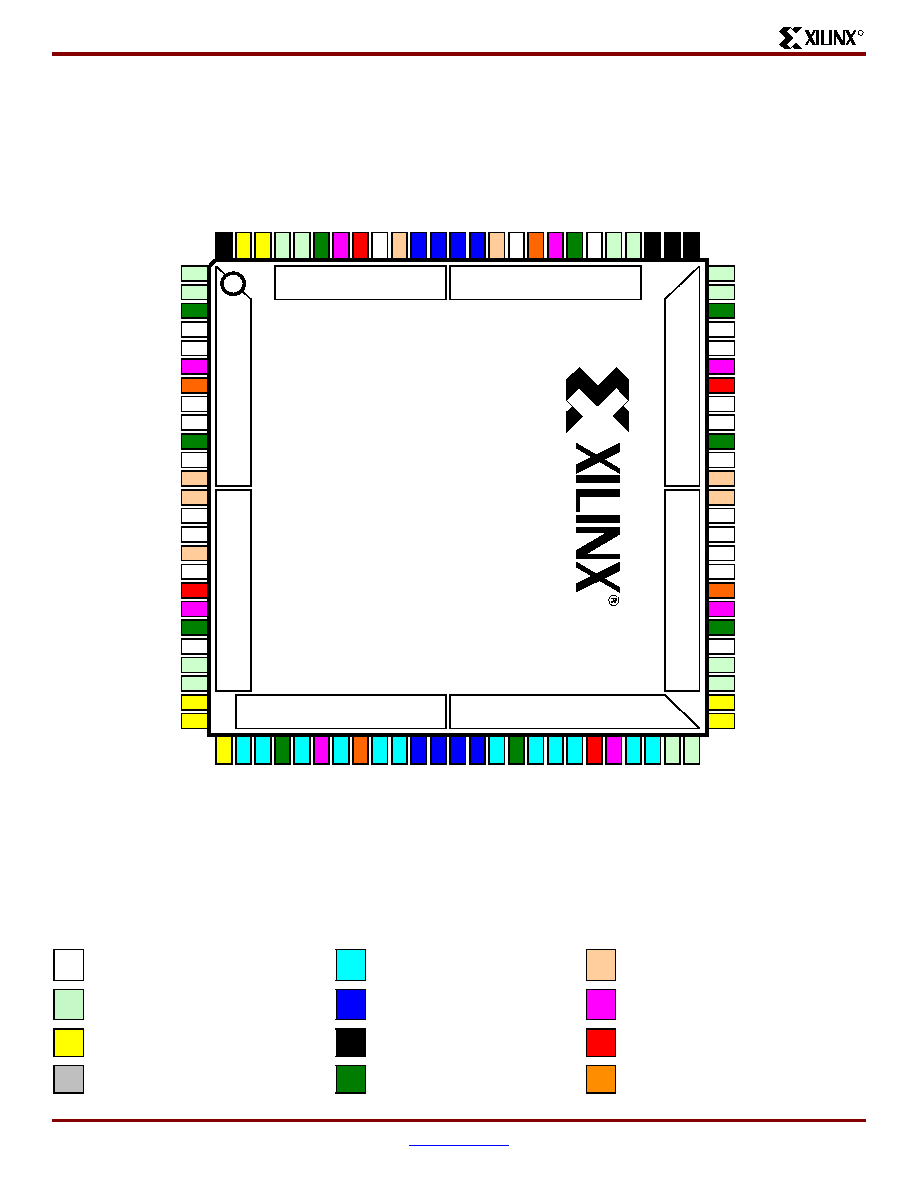

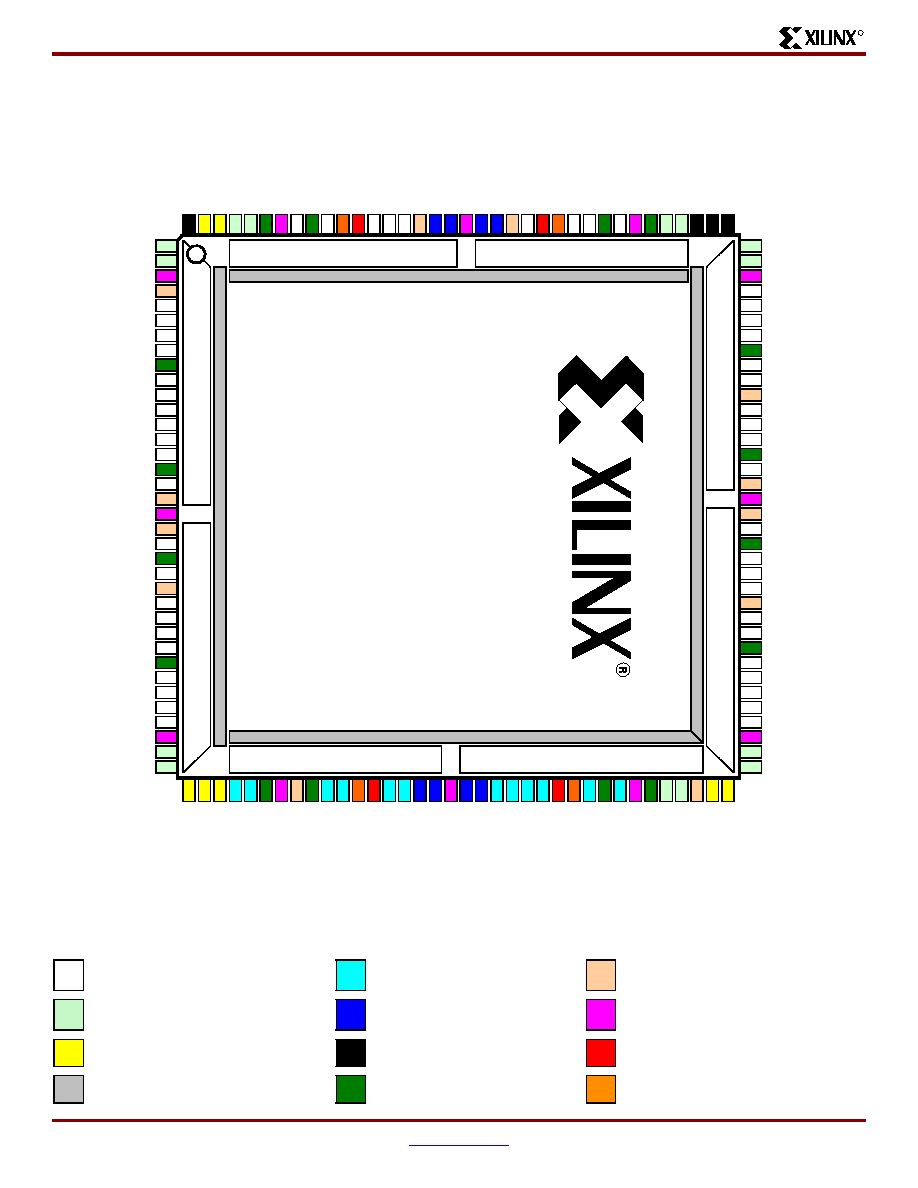

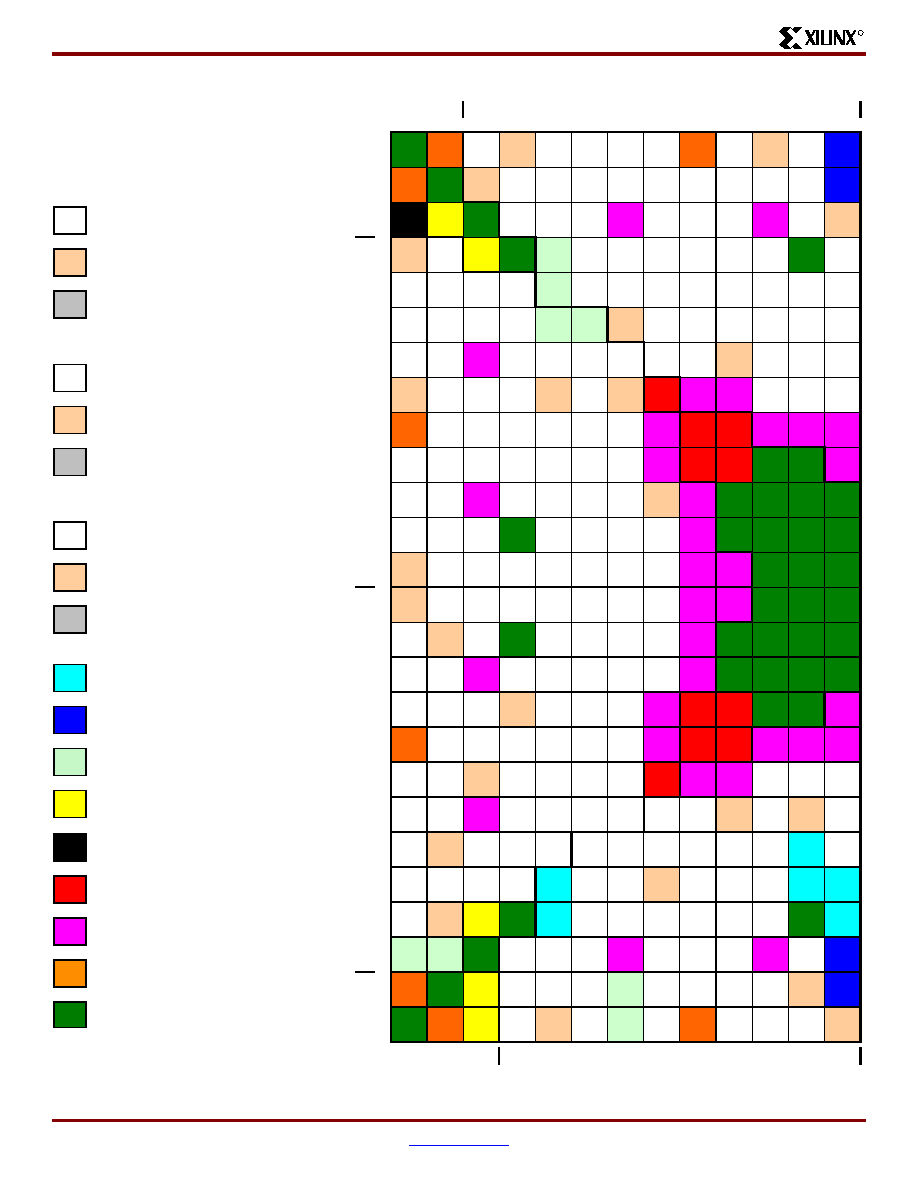

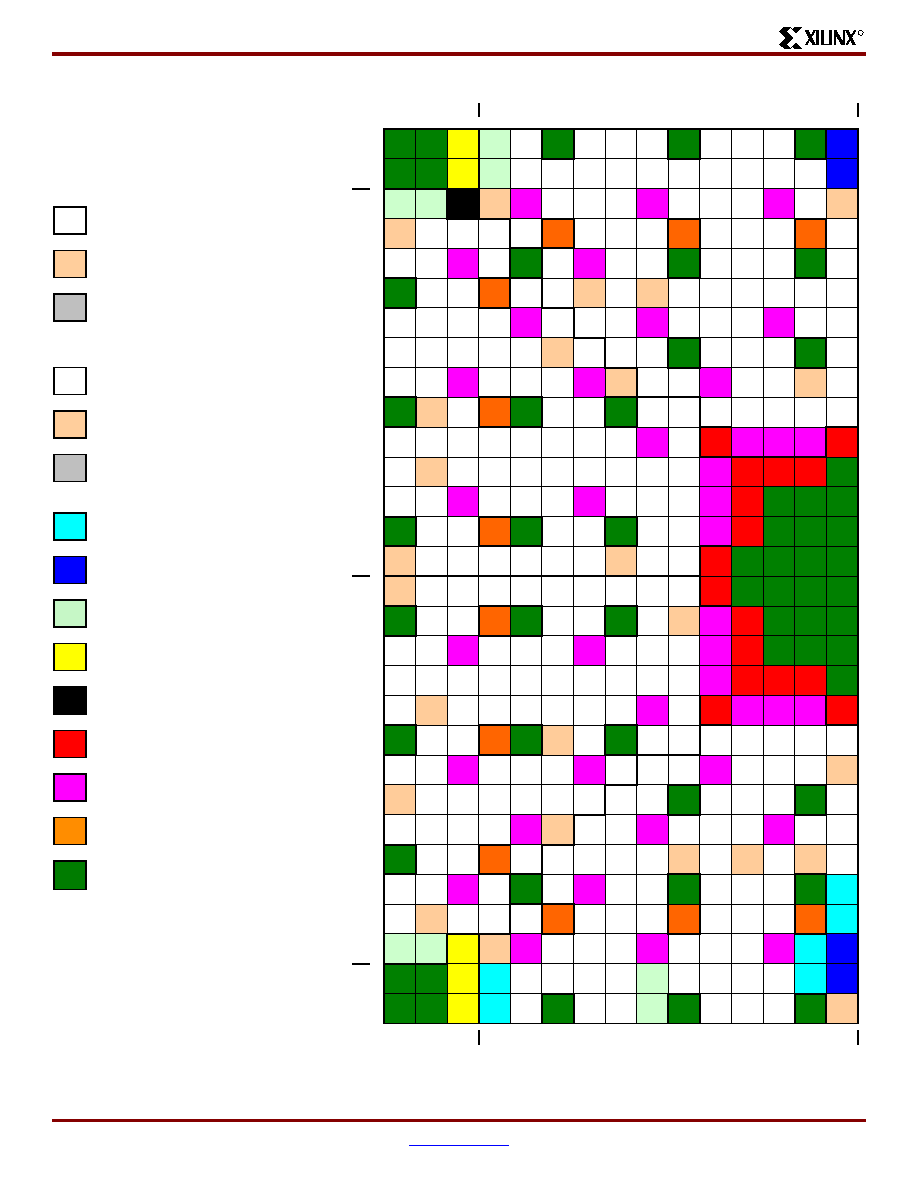

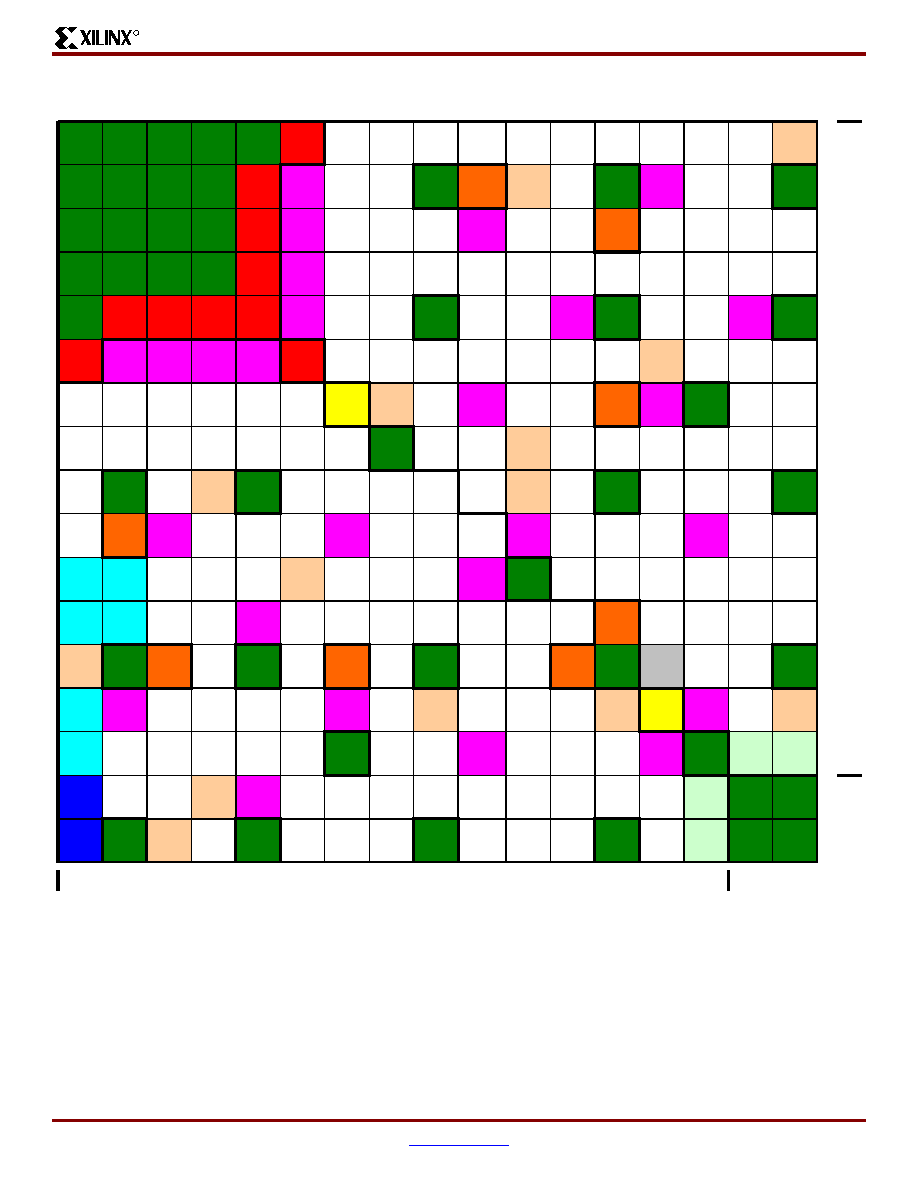

Architectural Overview

The Spartan-3 family architecture consists of five funda-

mental programmable functional elements:

�

Configurable Logic Blocks (CLBs) contain RAM-based

Look-Up Tables (LUTs) to implement logic and storage

elements that can be used as flip-flops or latches.

CLBs can be programmed to perform a wide variety of

logical functions as well as to store data.

�

Input/Output Blocks (IOBs) control the flow of data

between the I/O pins and the internal logic of the

device. Each IOB supports bidirectional data flow plus

3-state operation. Twenty-three different signal

standards, including six high-performance differential

standards, are available as shown in

Table 2

. Double

Data-Rate (DDR) registers are included. The Digitally

Controlled Impedance (DCI) feature provides

automatic on-chip terminations, simplifying board

designs.

�

Block RAM provides data storage in the form of 18-Kbit

dual-port blocks.

�

Multiplier blocks accept two 18-bit binary numbers as

inputs and calculate the product.

�

Digital Clock Manager (DCM) blocks provide

self-calibrating, fully digital solutions for distributing,

delaying, multiplying, dividing, and phase shifting clock

signals.

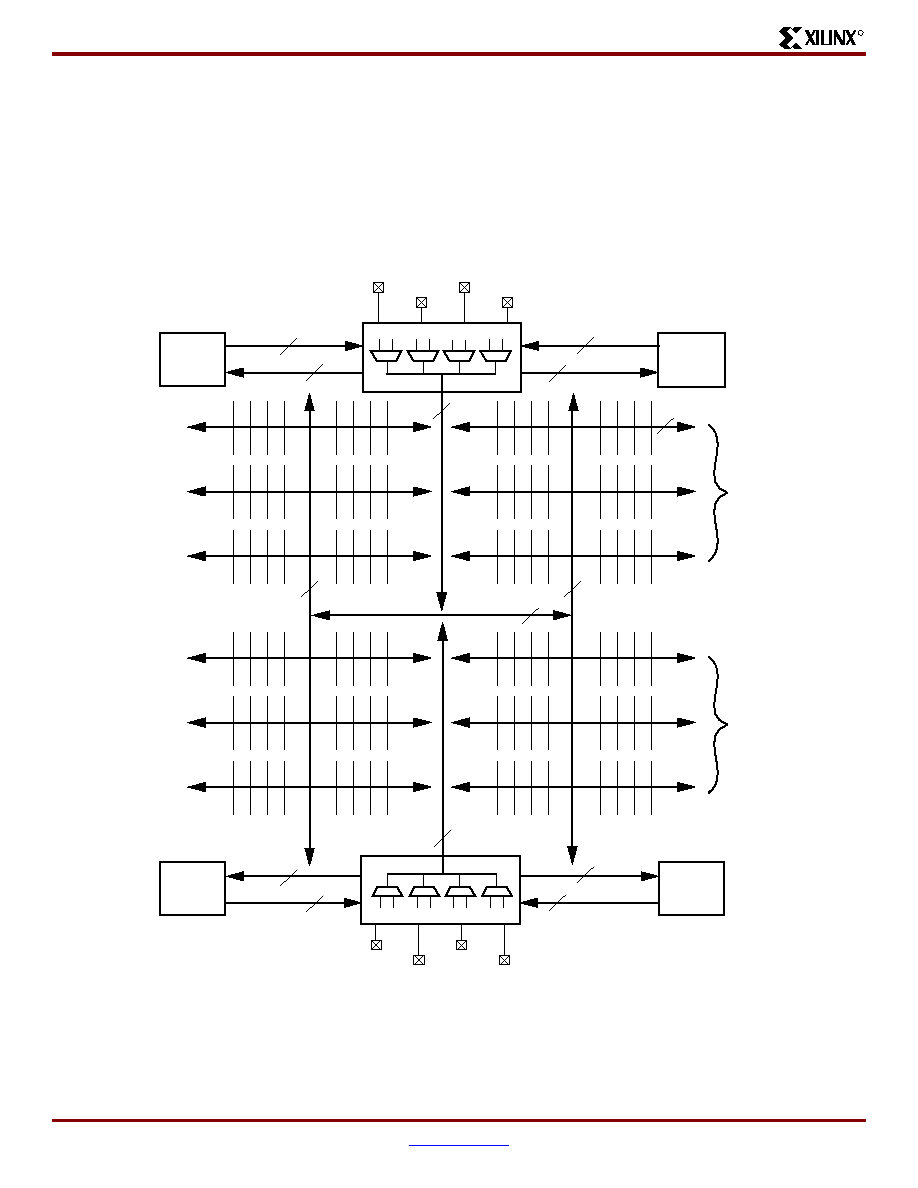

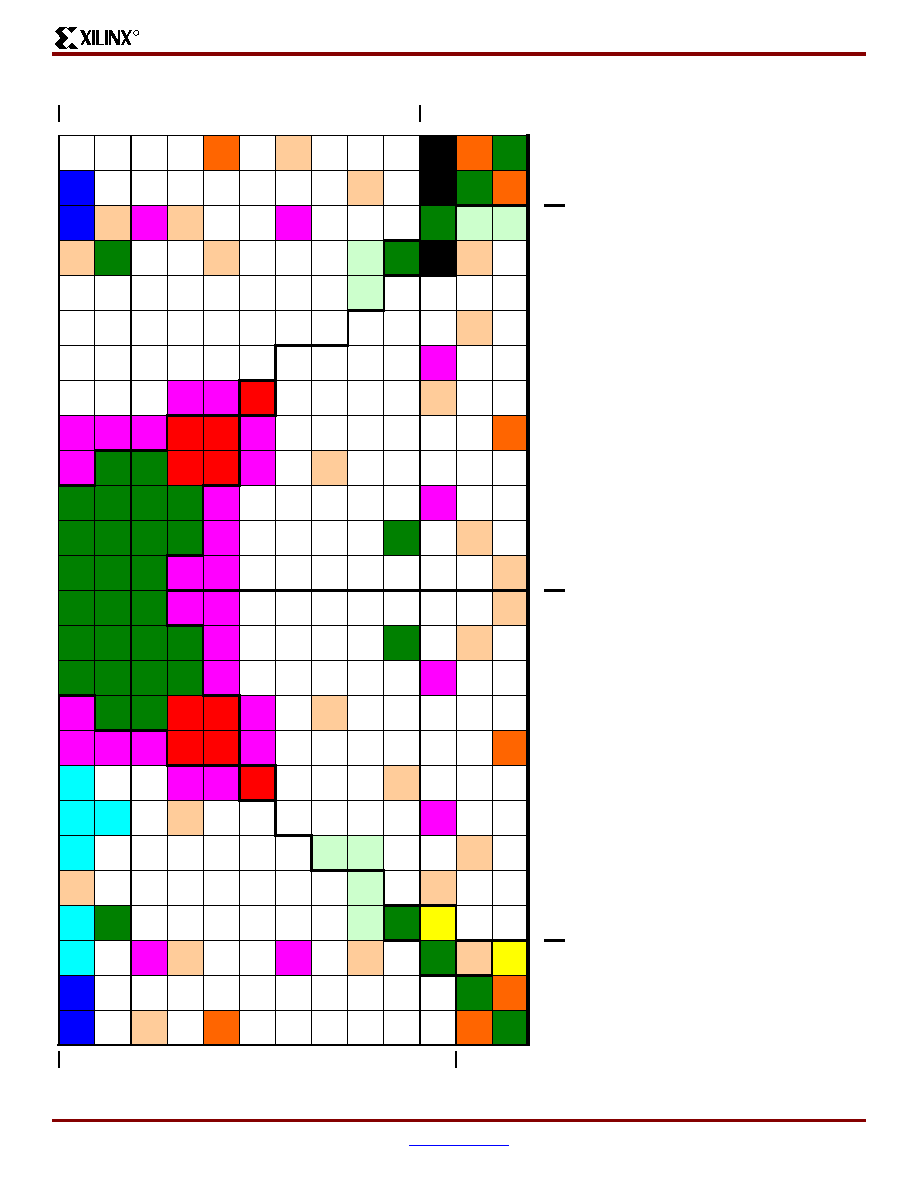

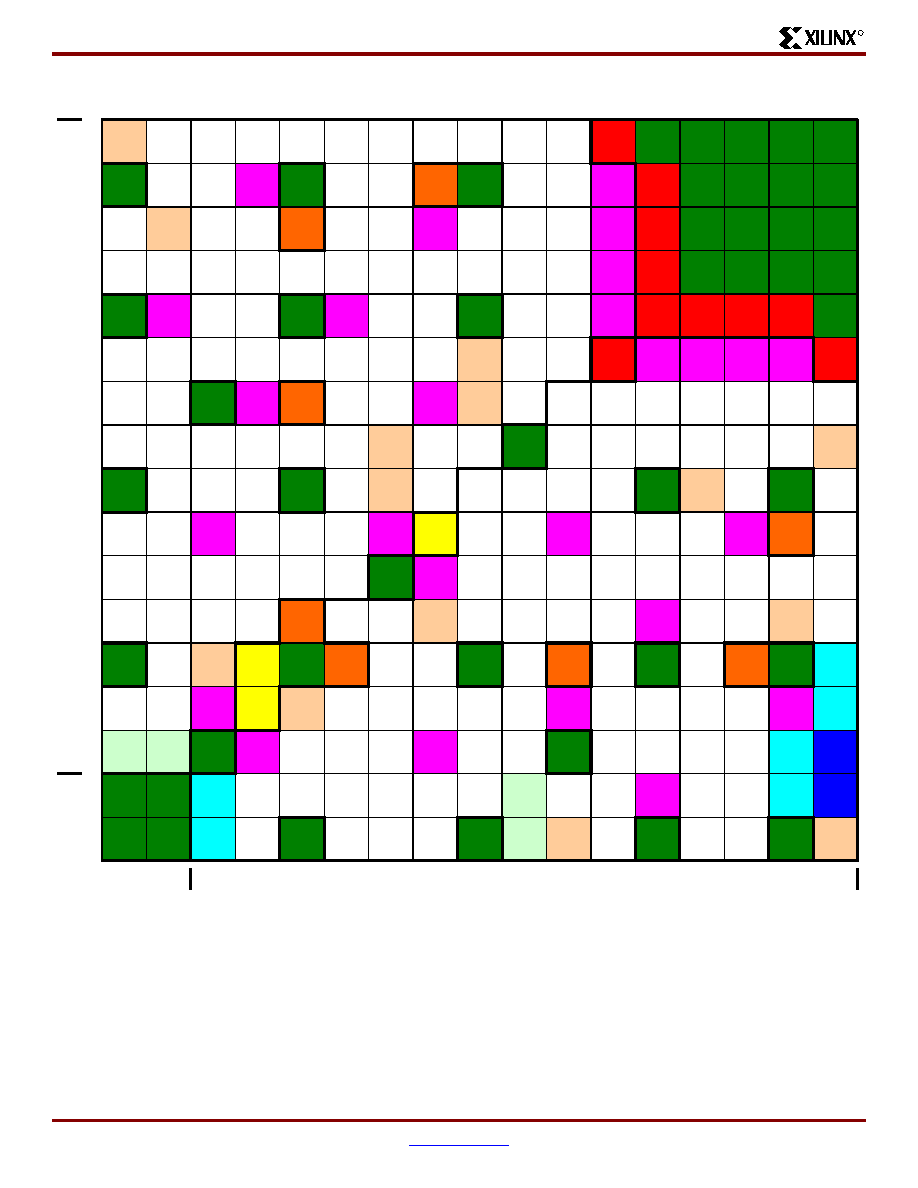

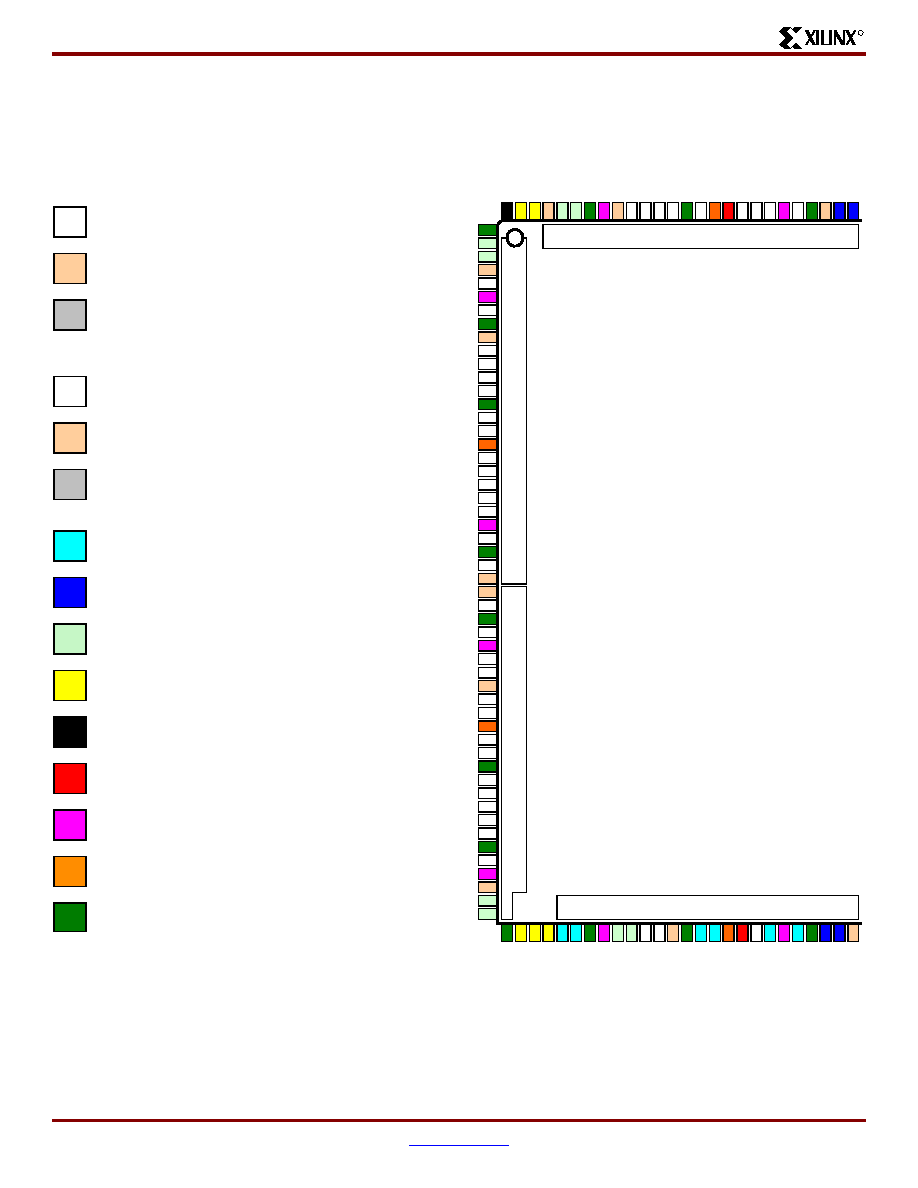

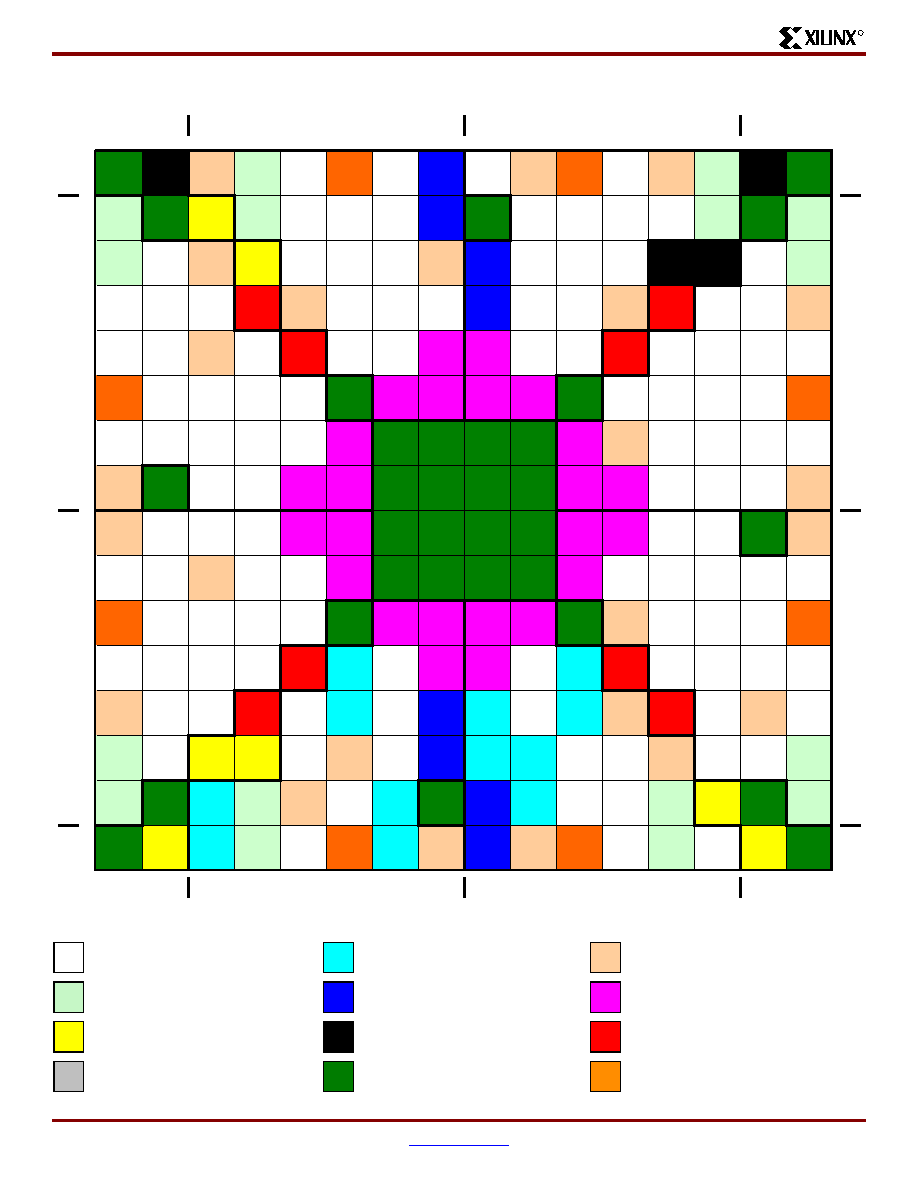

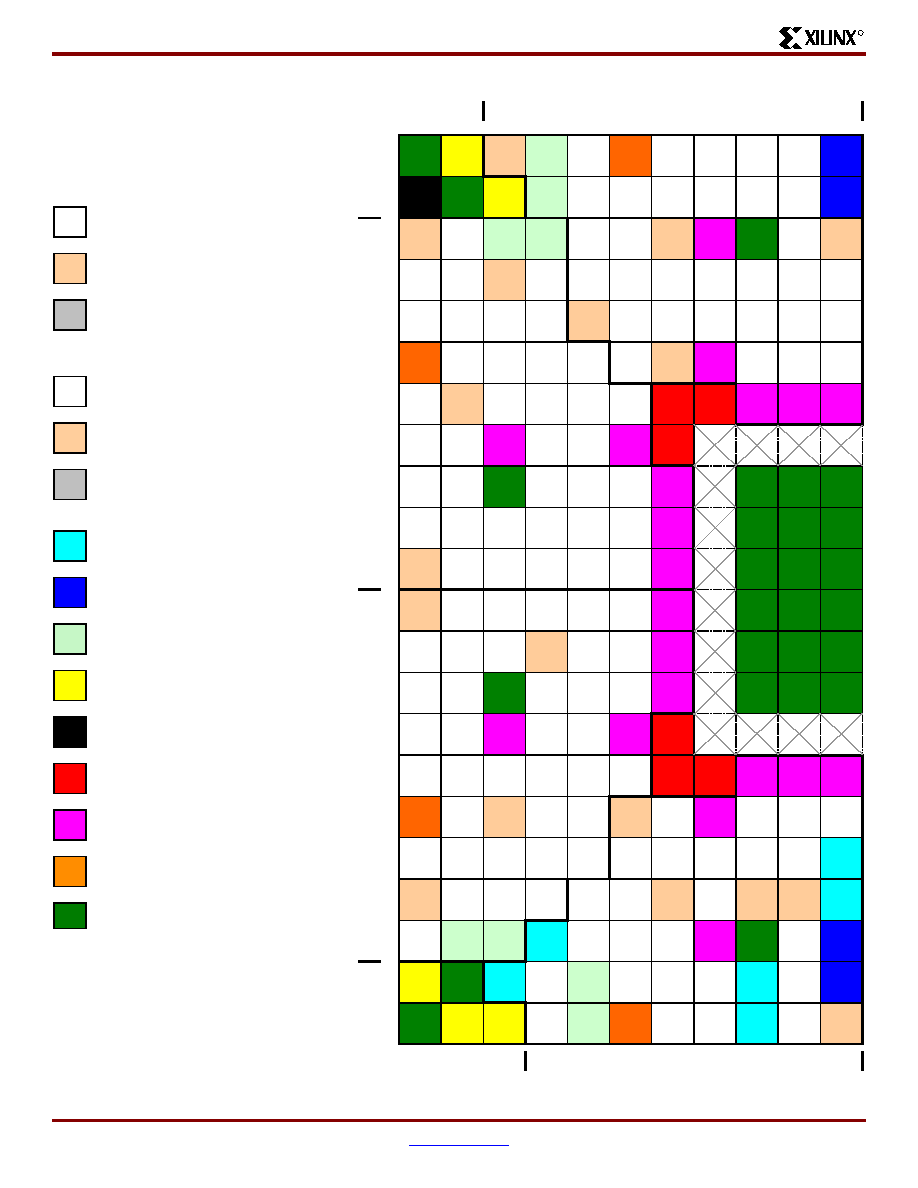

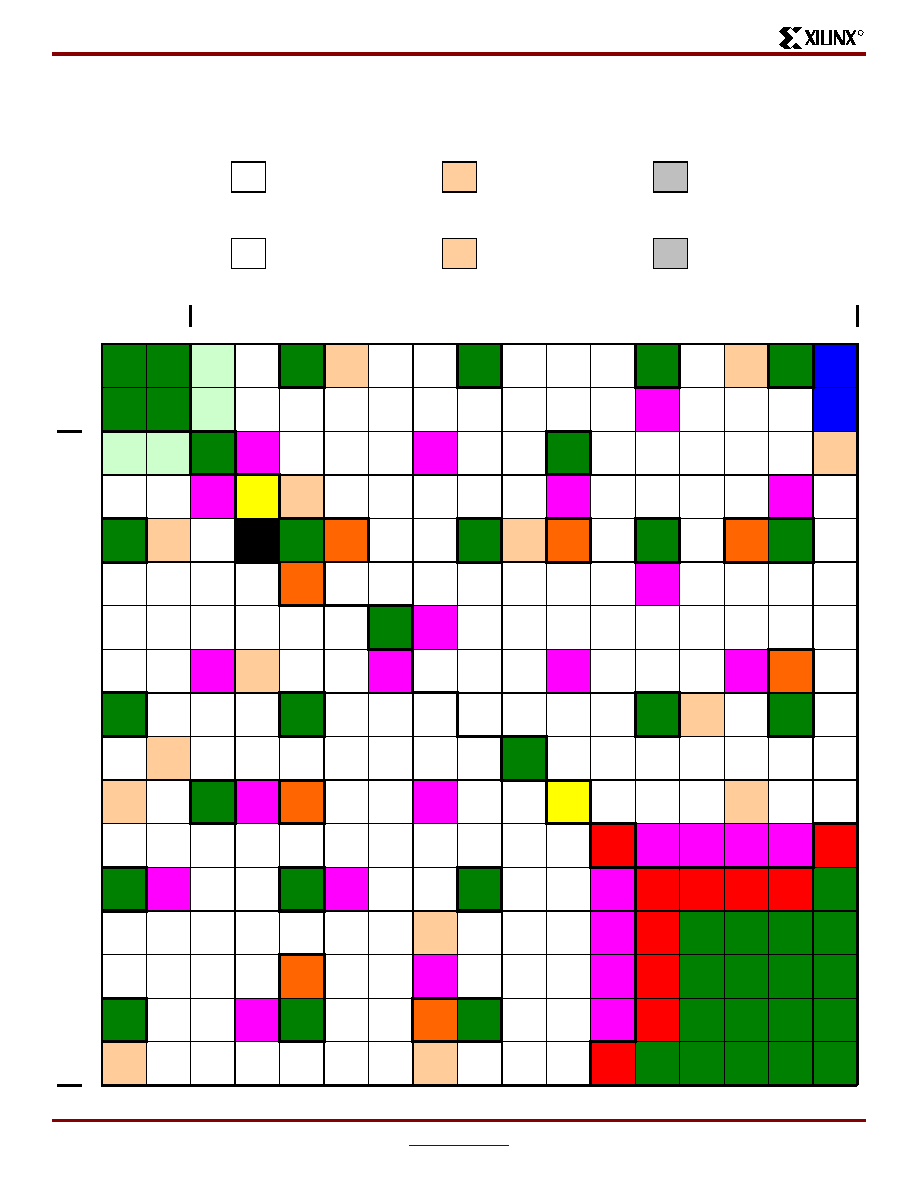

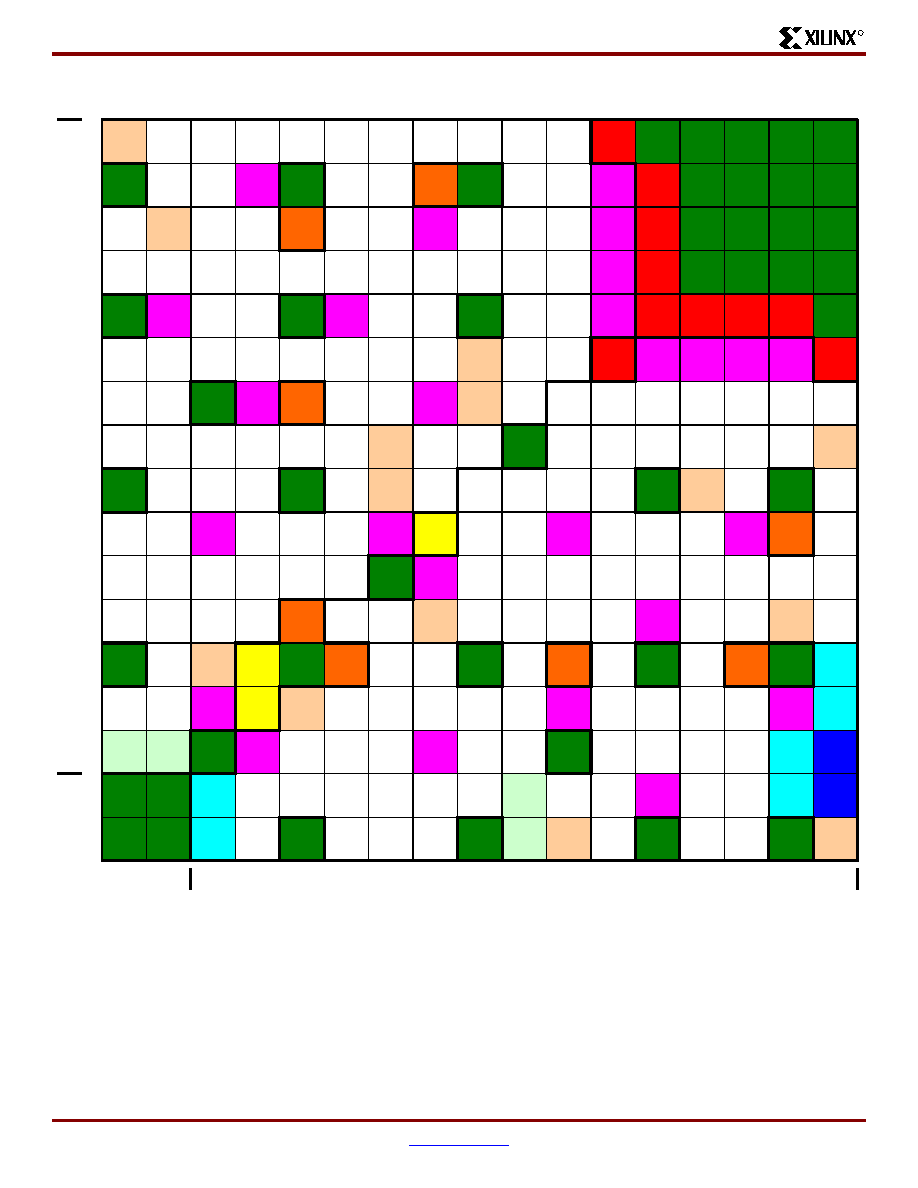

These elements are organized as shown in

Figure 1

. A ring

of IOBs surrounds a regular array of CLBs. The XC3S50

has a single column of block RAM embedded in the array.

Those devices ranging from the XC3S200 to the XC3S2000

have two columns of block RAM. The XC3S4000 and

XC3S5000 devices have four RAM columns. Each column

is made up of several 18K-bit RAM blocks; each block is

associated with a dedicated multiplier. The DCMs are posi-

tioned at the ends of each block RAM column.

The Spartan-3 family features a rich network of traces and

switches that interconnect all five functional elements,

transmitting signals among them. Each functional element

has an associated switch matrix that permits multiple con-

nections to the routing.

Figure 1: Spartan-3 Family Architecture

DS099-1_01_032703

Notes:

1.

The two additional block RAM columns of the XC3S4000 and XC3S5000

devices are shown with dashed lines. The XC3S50 has only the block RAM

column on the far left.

Spartan-3 1.2V FPGA Family: Introduction and Ordering Information

DS099-1 (v1.1) April 24, 2003

www.xilinx.com

3

Advance Product Specification

1-800-255-7778

R

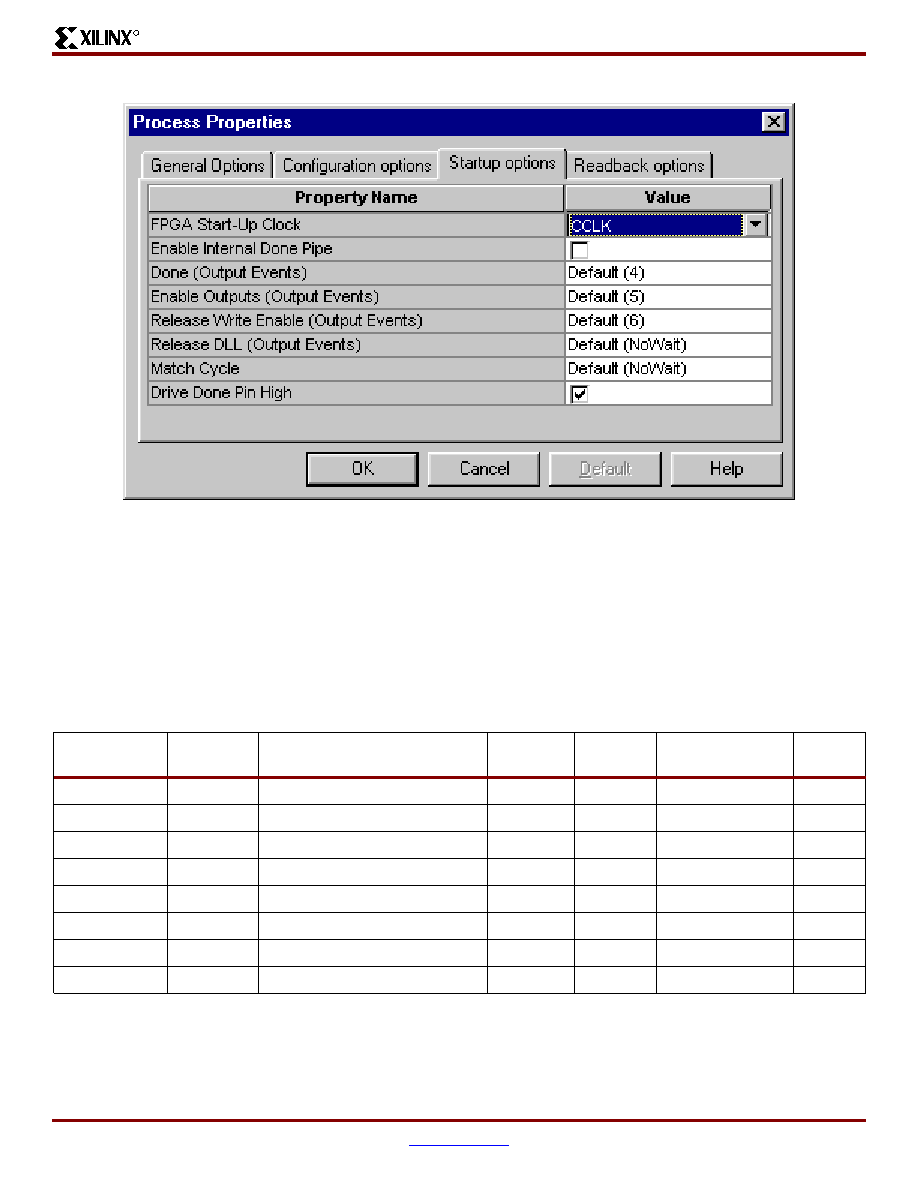

Configuration

Spartan-3 FPGAs are programmed by loading configuration

data into robust static memory cells that collectively control

all functional elements and routing resources. Before pow-

ering on the FPGA, configuration data is stored externally in

a PROM or some other nonvolatile medium either on or off

the board. After applying power, the configuration data is

written to the FPGA using any of five different modes: Mas-

ter Parallel, Slave Parallel, Master Serial, Slave Serial and

Boundary Scan (JTAG). The Master and Slave Parallel

modes use an 8-bit wide SelectMAPTM Port.

The recommended memory for storing the configuration

data is the low-cost Xilinx Platform Flash PROM family,

which includes XCF00S PROMs for serial configuration and

XCF00P PROMs for parallel configuration.

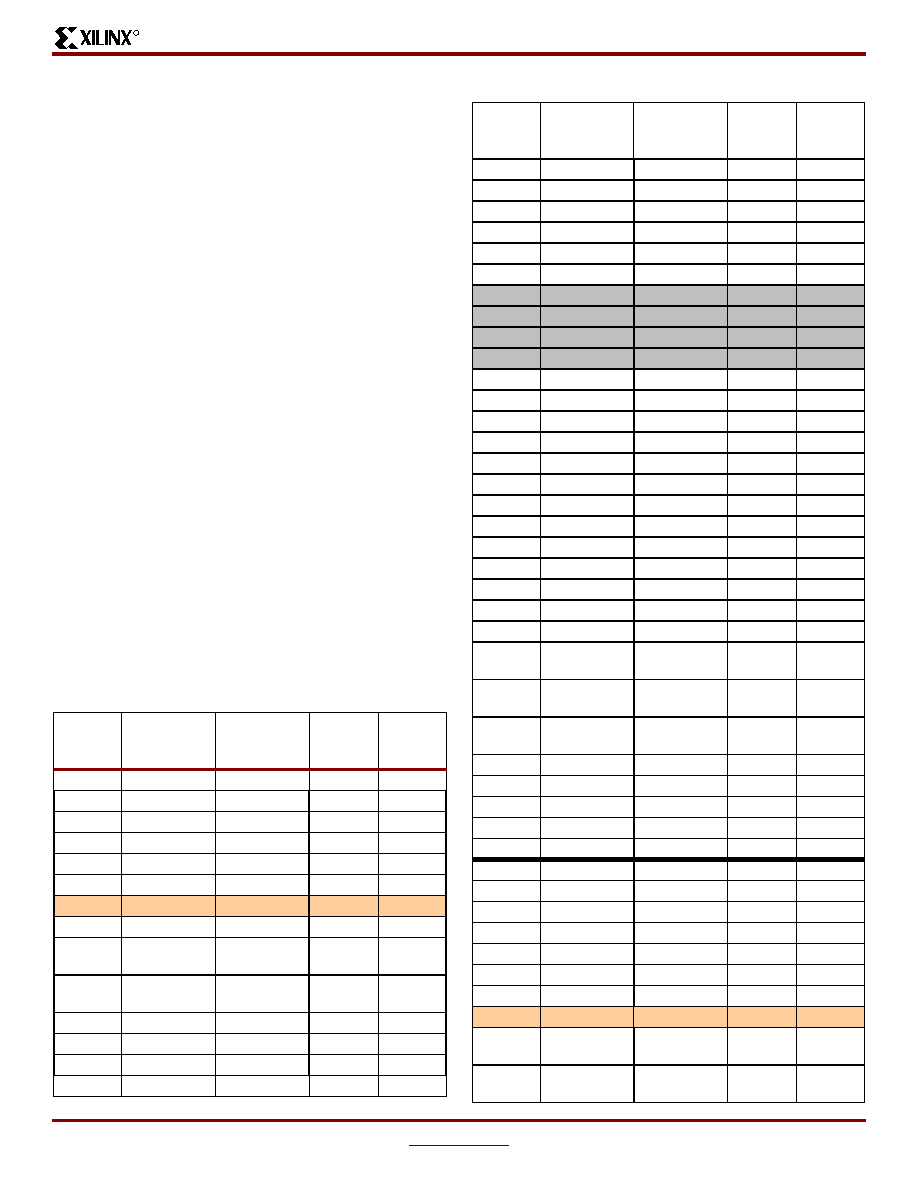

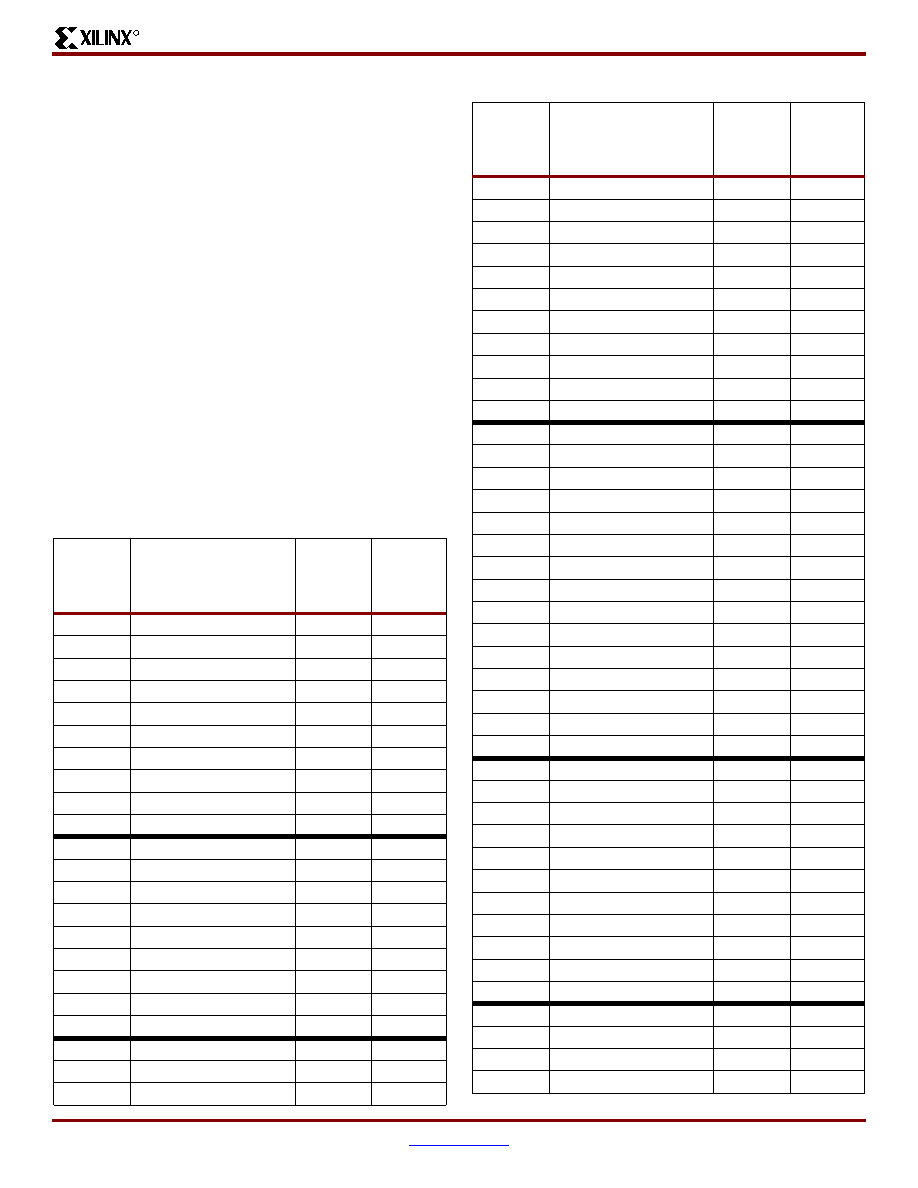

I/O Capabilities

The SelectIO feature of Spartan-3 devices supports 17 sin-

gle-ended standards and six differential standards as listed

in

Table 2

.

Table 3

shows the number of user I/Os as well as

the number of differential I/O pairs available for each

device/package combination.

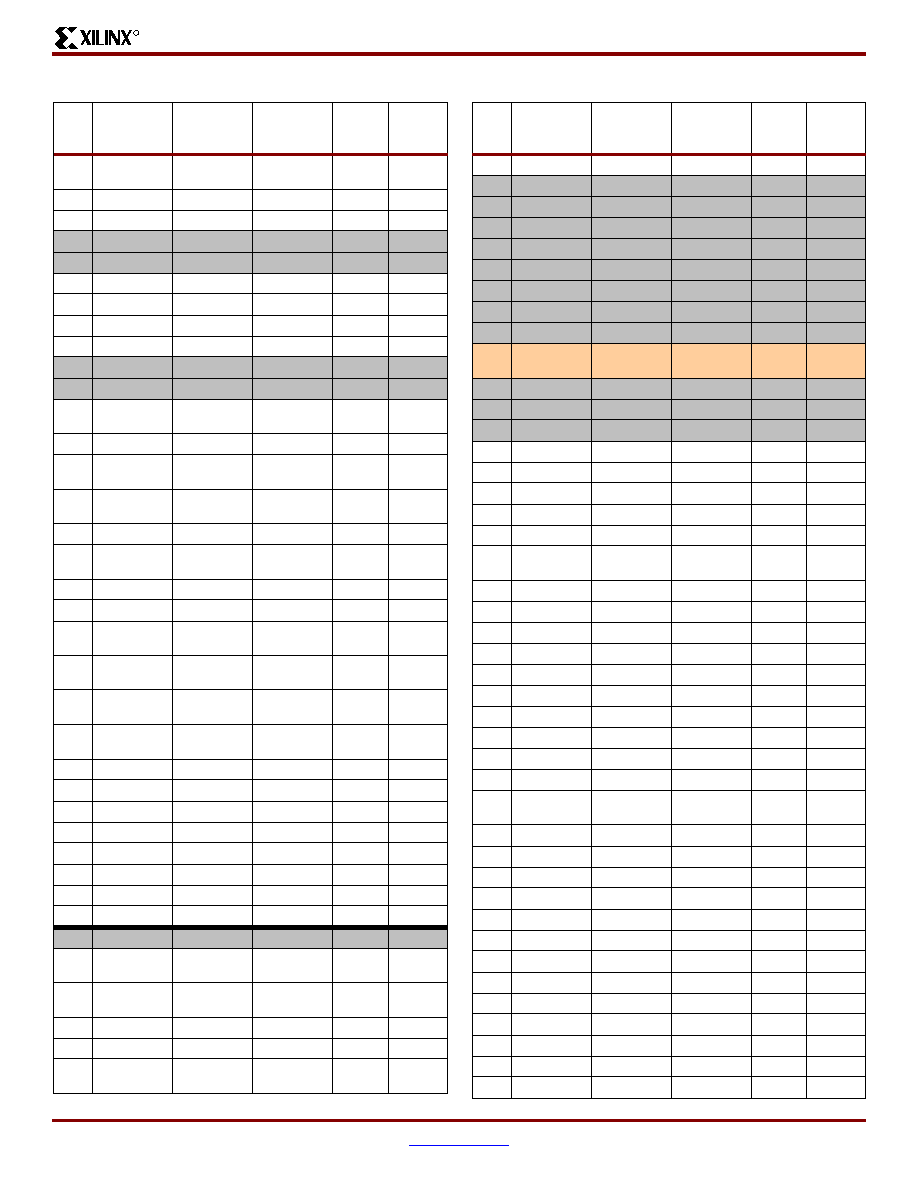

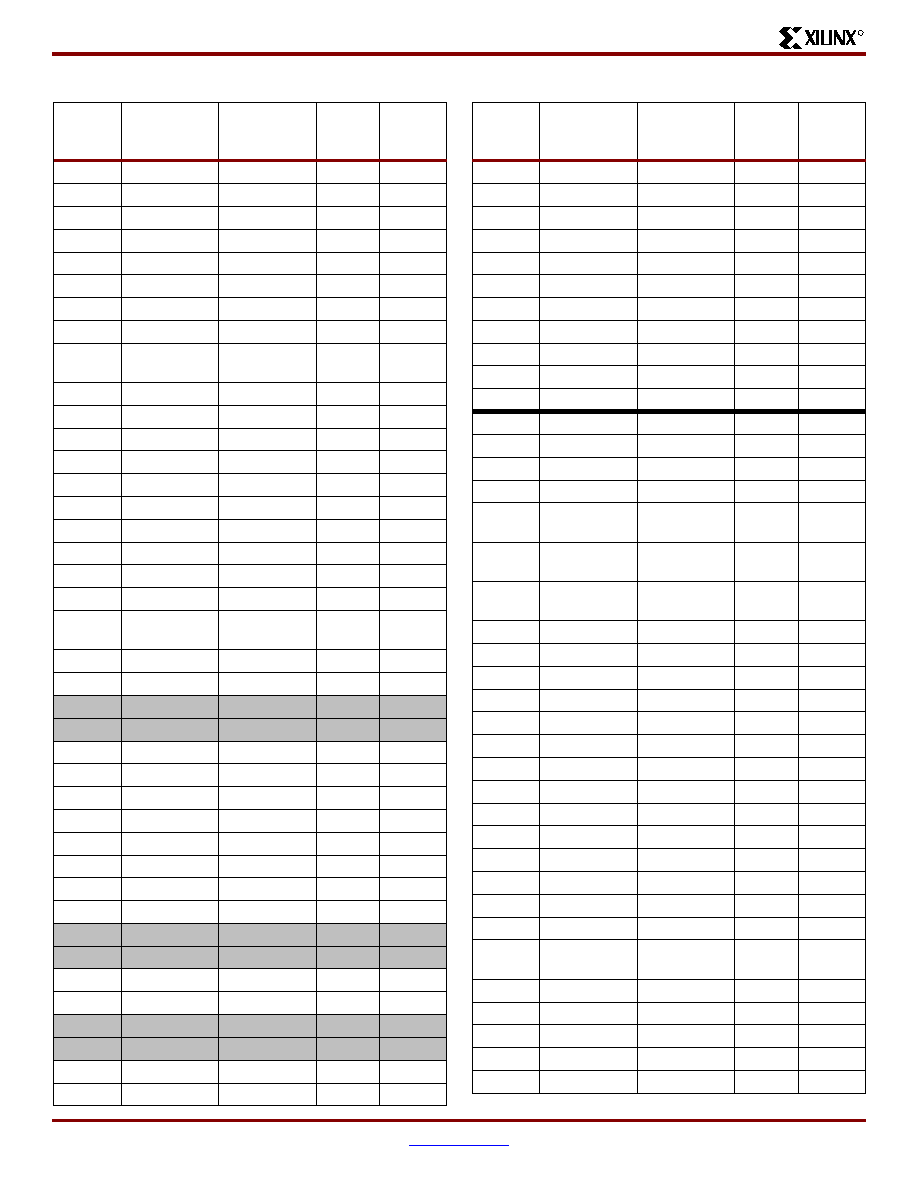

Table 2: Signal Standards Supported by the Spartan-3 Family

Standard

Category

Description

V

CCO

(V)

Class

Symbol

Single-Ended

GTL

Gunning Transceiver Logic

N/A

Terminated

GTL

Plus

GTLP

HSTL

High-Speed Transceiver Logic

1.5

I

HSTL_I

III

HSTL_III

1.8

I

HSTL_I_18

II

HSTL_II_18

III

HSTL_III_18

LVCMOS

Low-Voltage CMOS

1.2

N/A

LVCMOS12

1.5

N/A

LVCMOS15

1.8

N/A

LVCMOS18

2.5

N/A

LVCMOS25

3.3

N/A

LVCMOS33

LVTTL

Low-Voltage Transistor-Transistor Logic

3.3

N/A

LVTTL

PCI

Peripheral Component Interconnect

3.0

33 MHz

PCI33_3

SSTL

Stub Series Terminated Logic

1.8

N/A

SSTL18_I

2.5

I

SSTL2_I

II

SSTL2_II

Differential

LDT

Lightning Data Transport

(HyperTransportTM)

2.5

N/A

LDT_25

LVDS

Low Voltage Differential Signaling

Standard

LVDS_25

Bus

BLVDS_25

Extended Mode

LVDSEXT_25

Ultra

ULVDS_25

RSDS

Reduced-Swing Differential Signaling

2.5

N/A

RSDS_25

Spartan-3 1.2V FPGA Family: Introduction and Ordering Information

4

www.xilinx.com

DS099-1 (v1.1) April 24, 2003

1-800-255-7778

Advance Product Specification

6

R

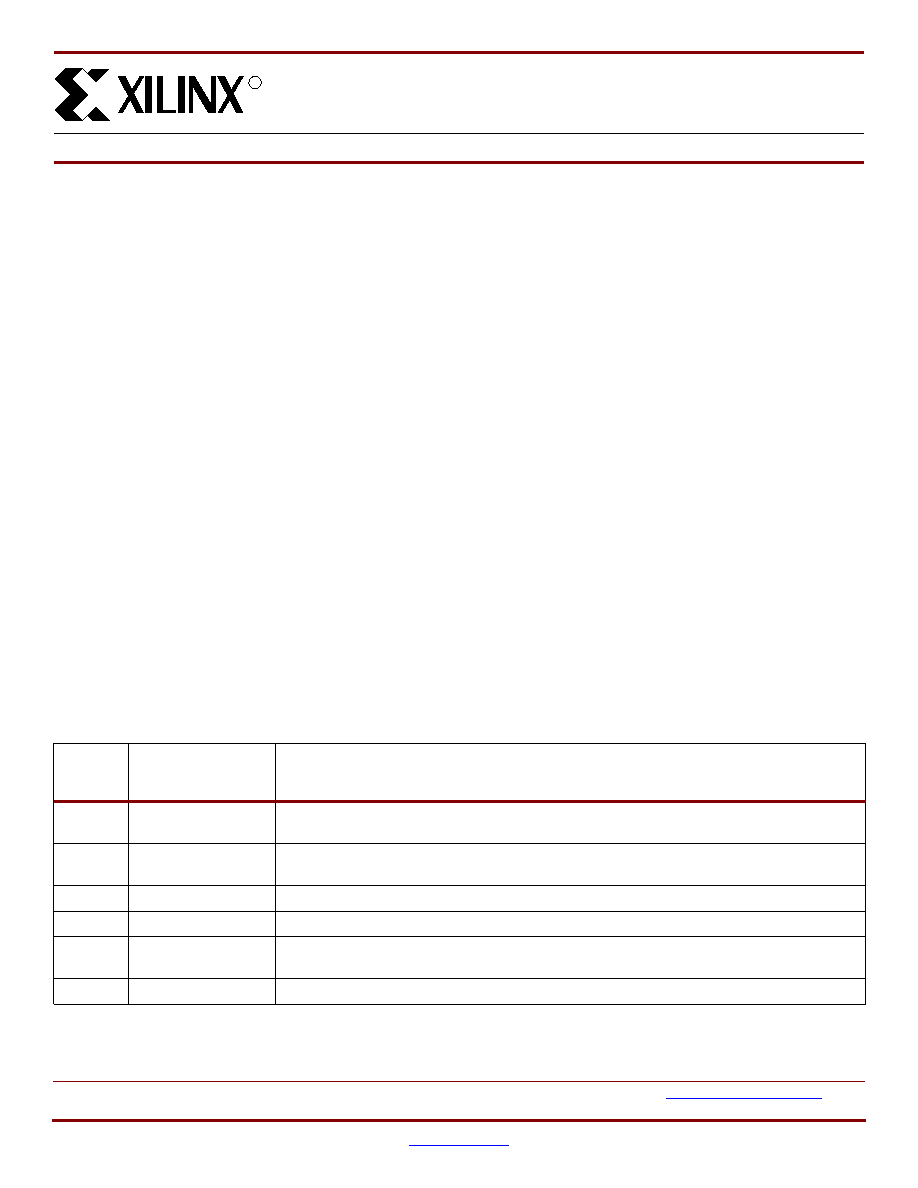

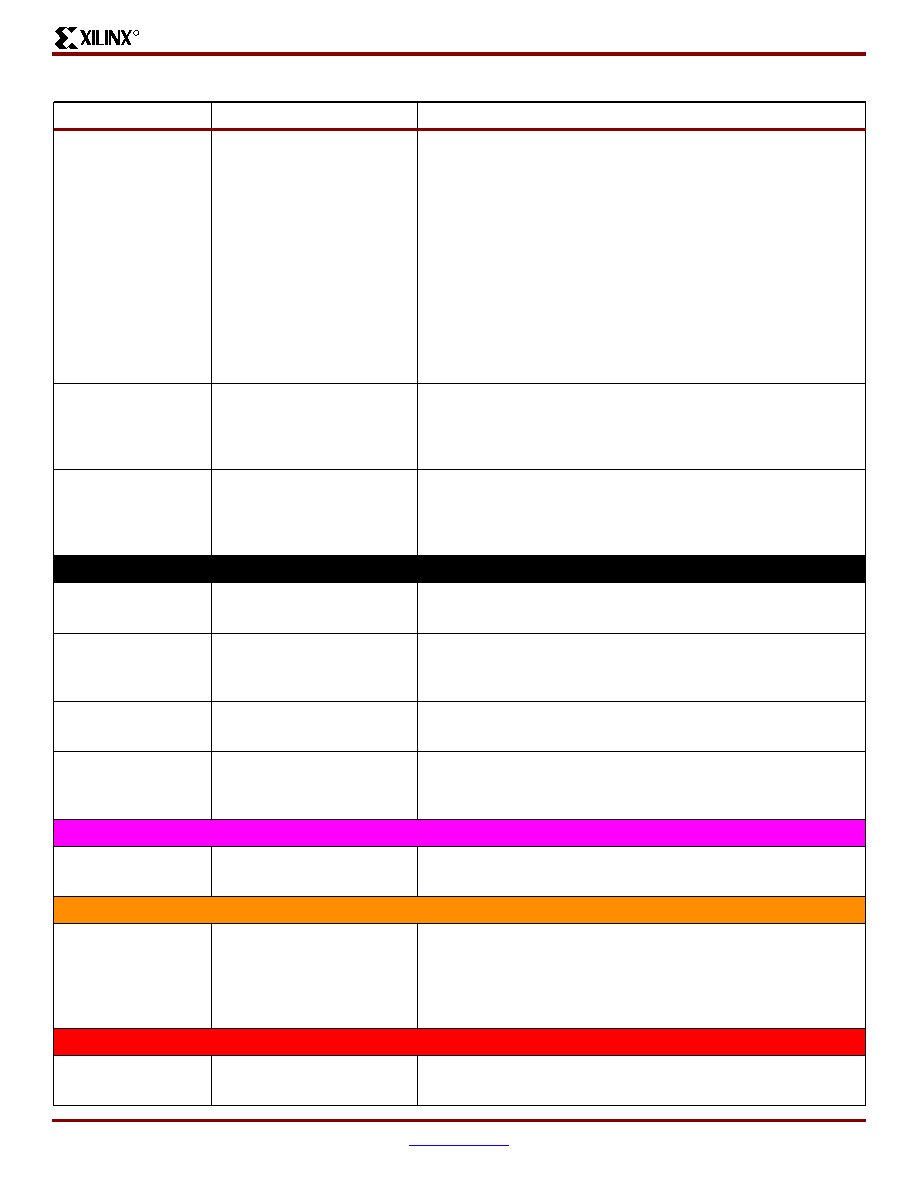

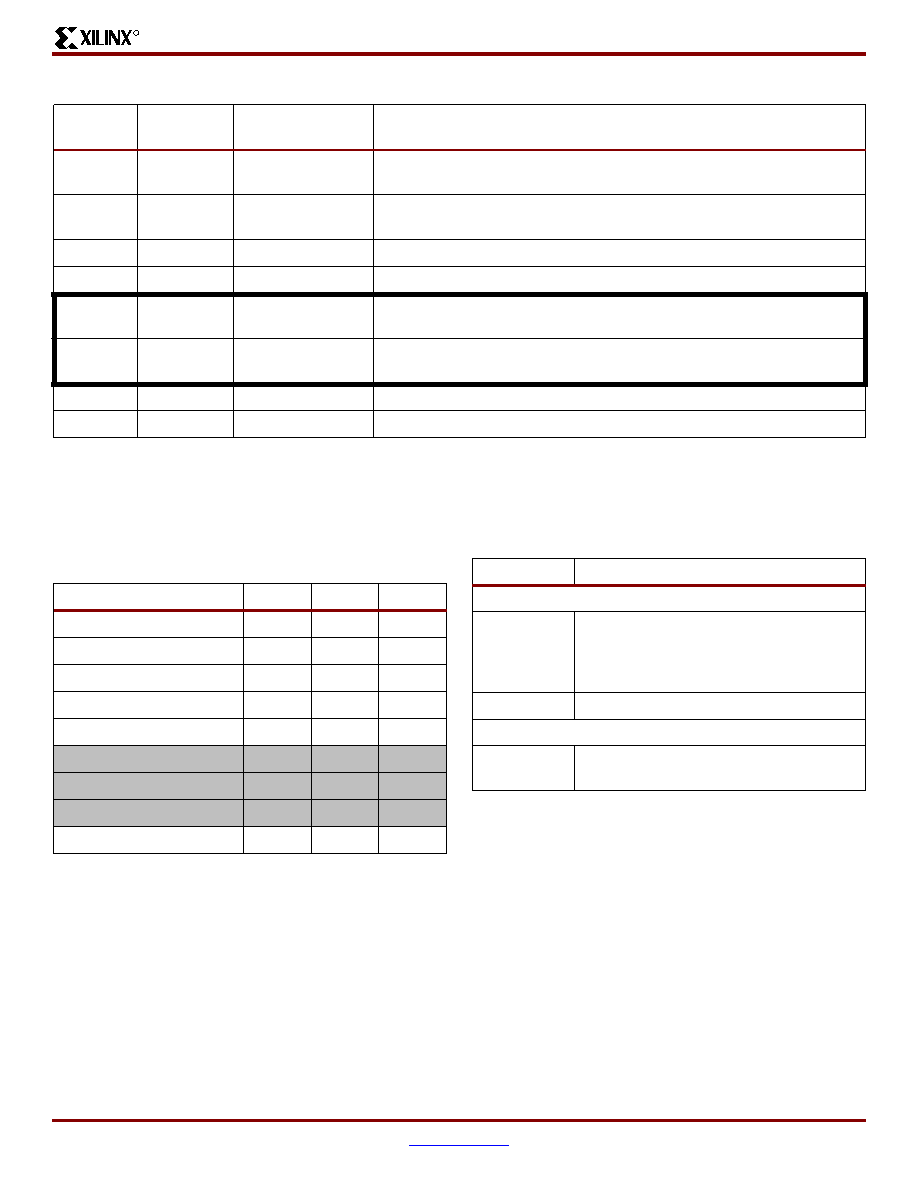

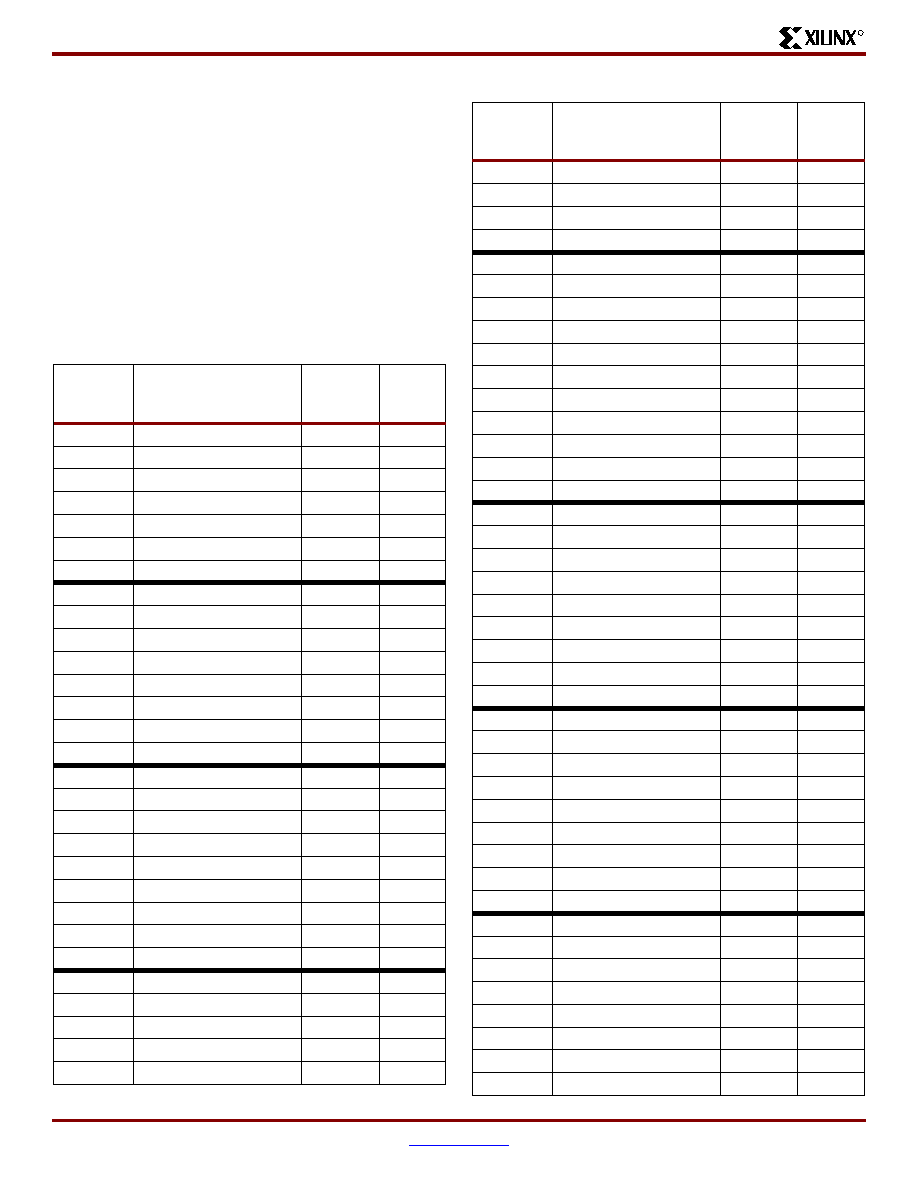

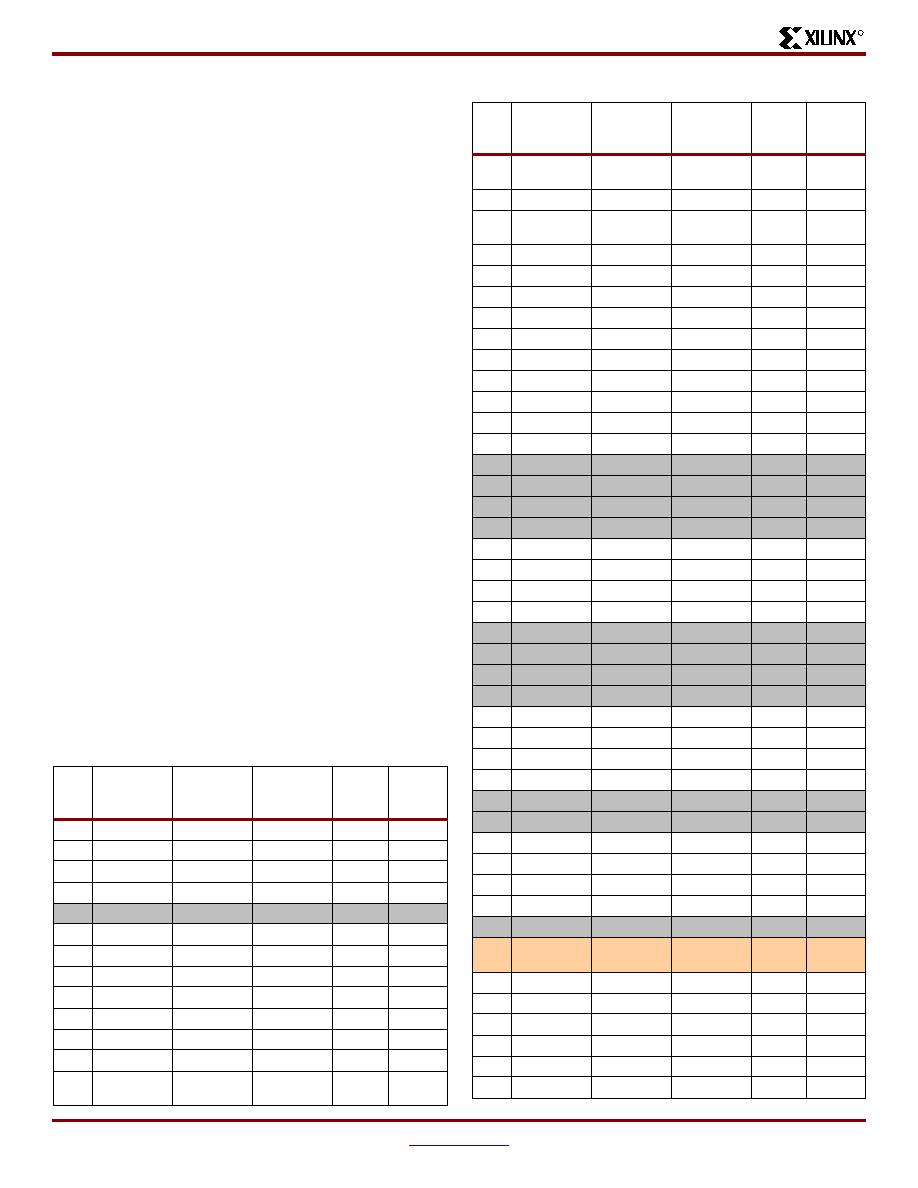

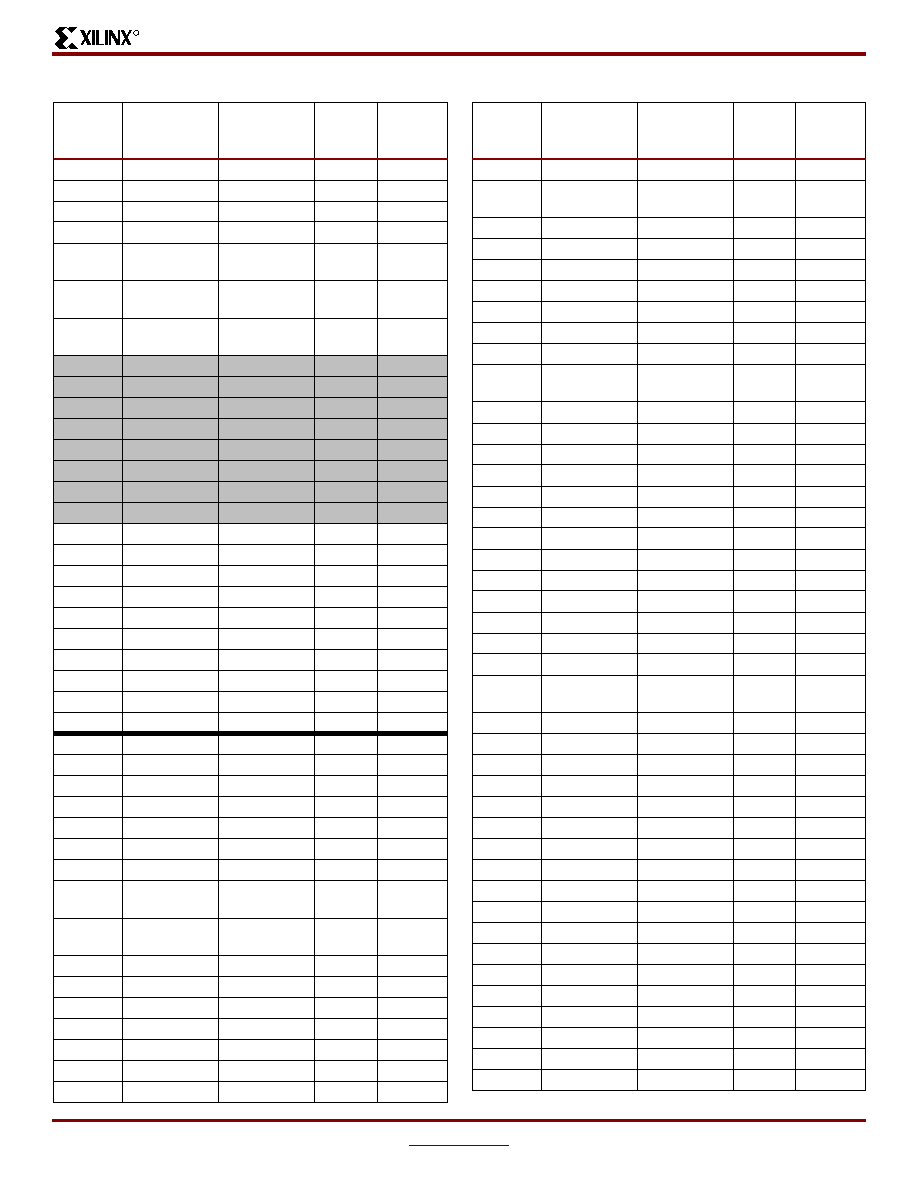

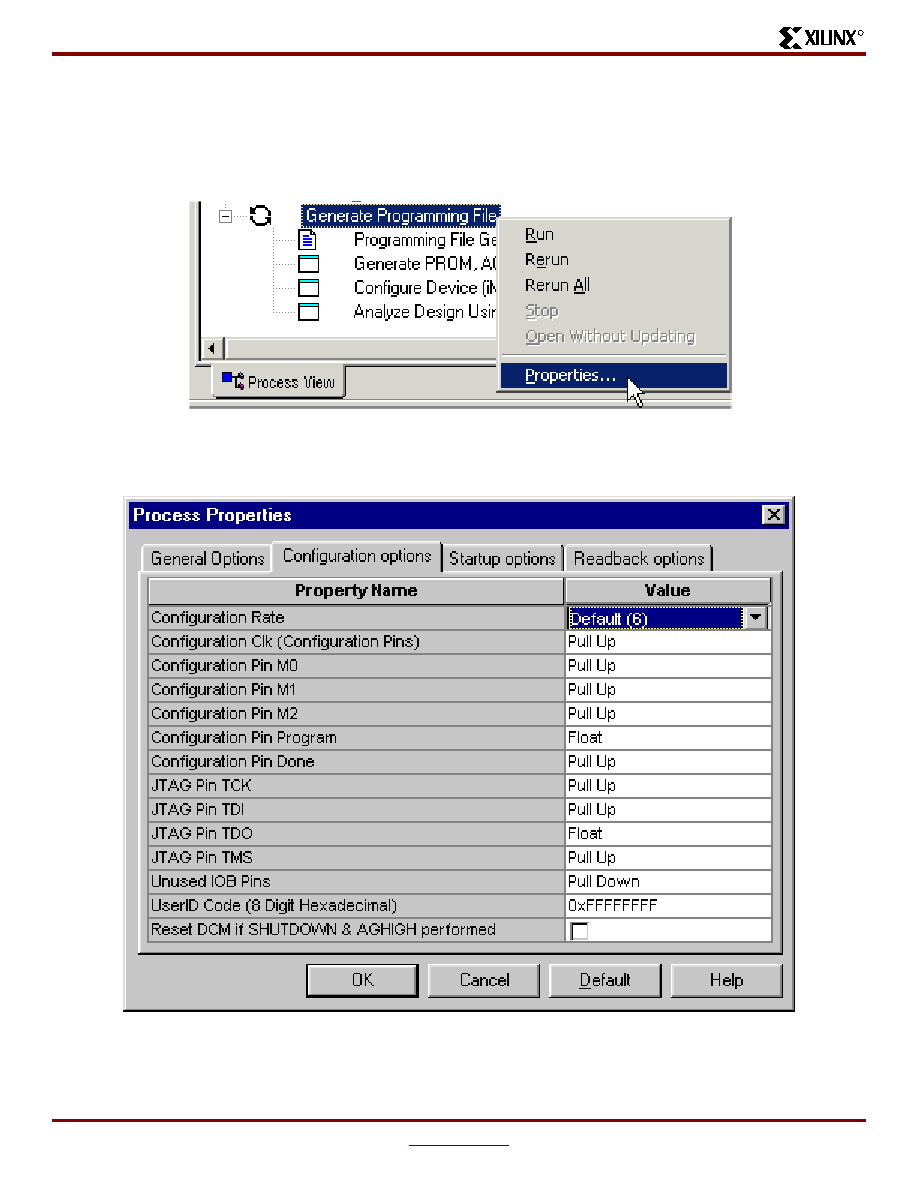

Product Ordering and Availability

Table 4

shows all valid device ordering combinations of

device density, speed grade, package, and temperature

range parameters for the Spartan-3 family as well as the

availability status of those combinations.

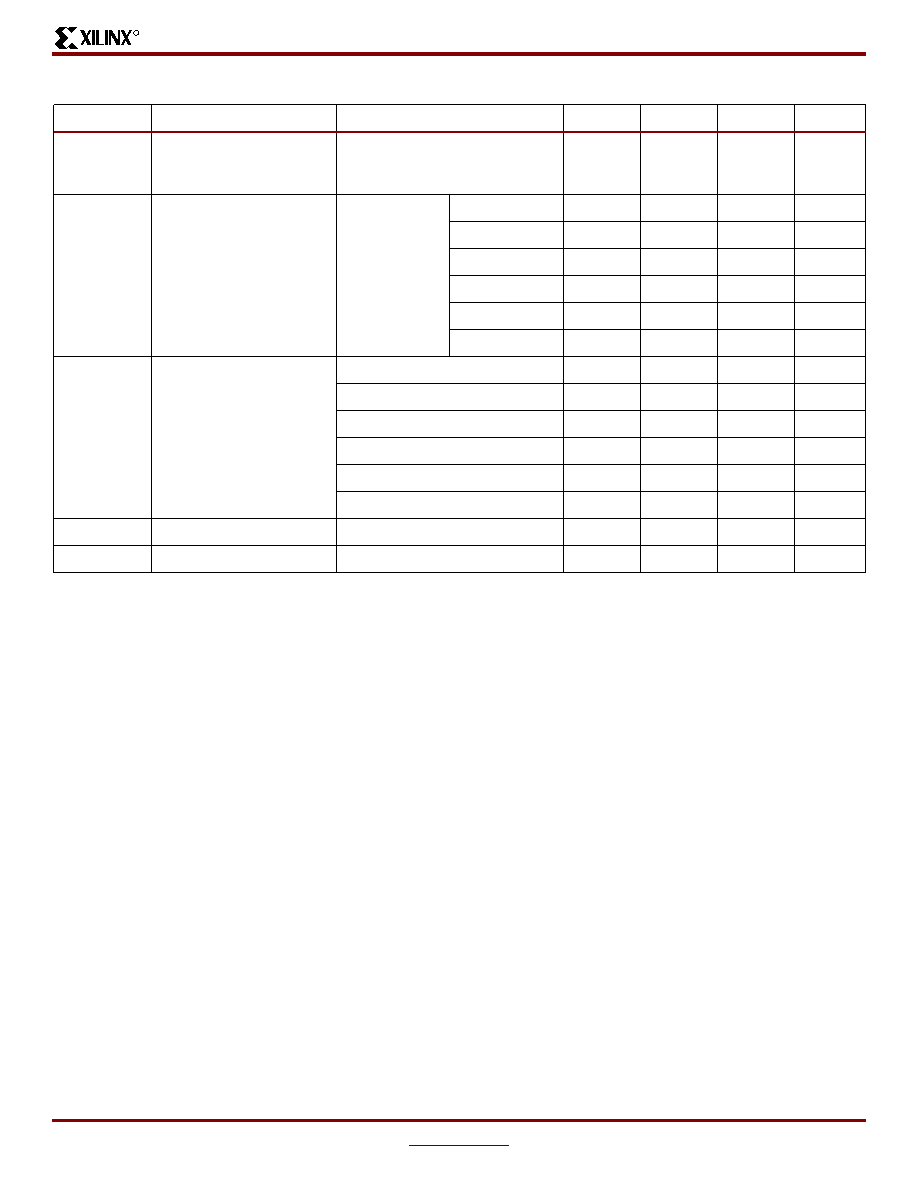

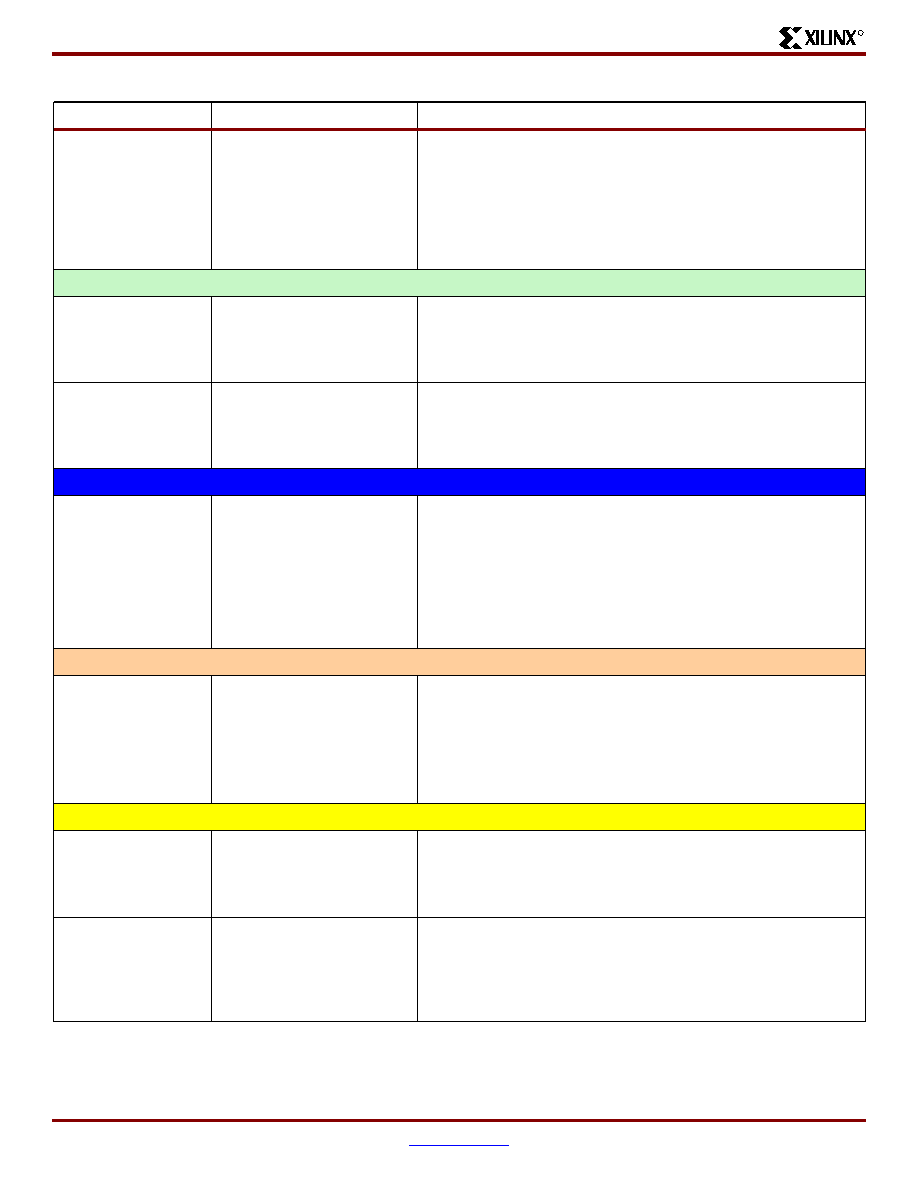

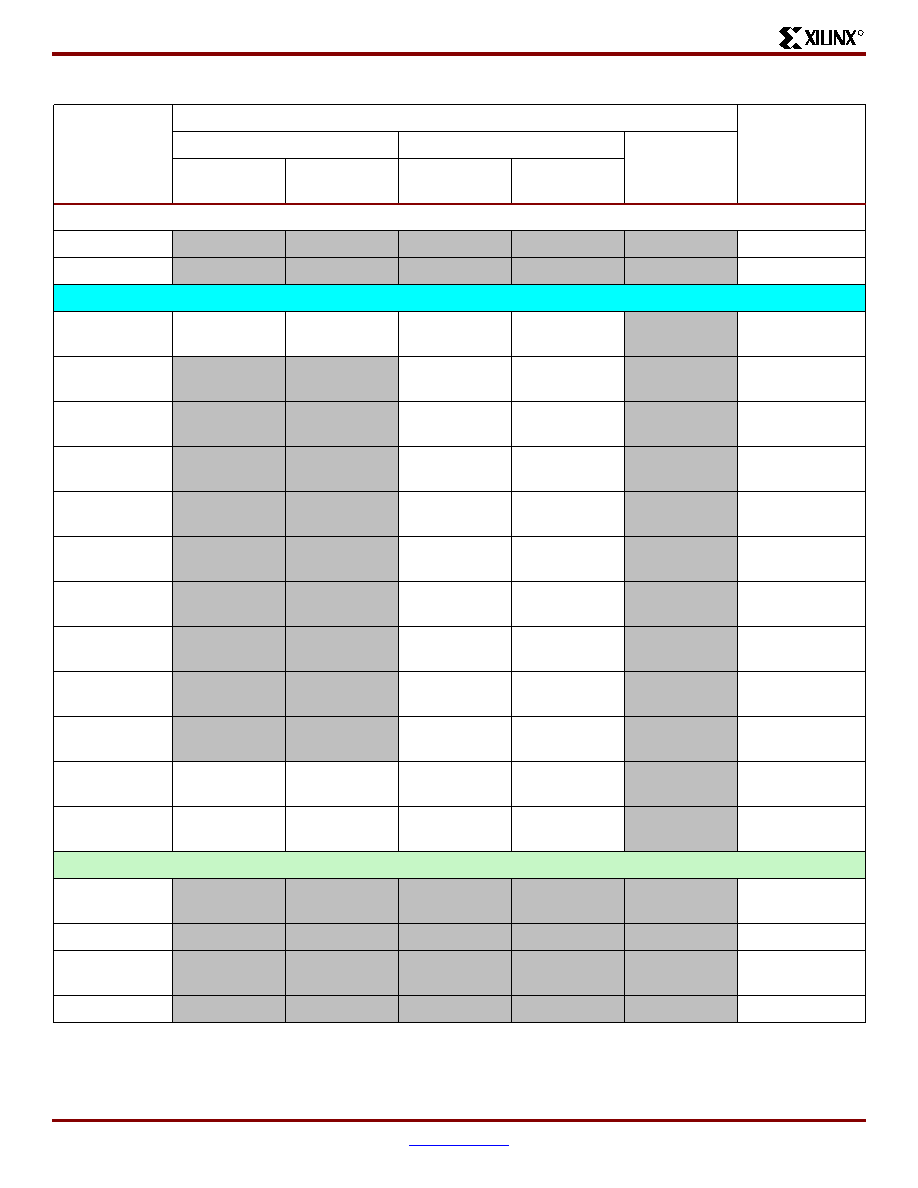

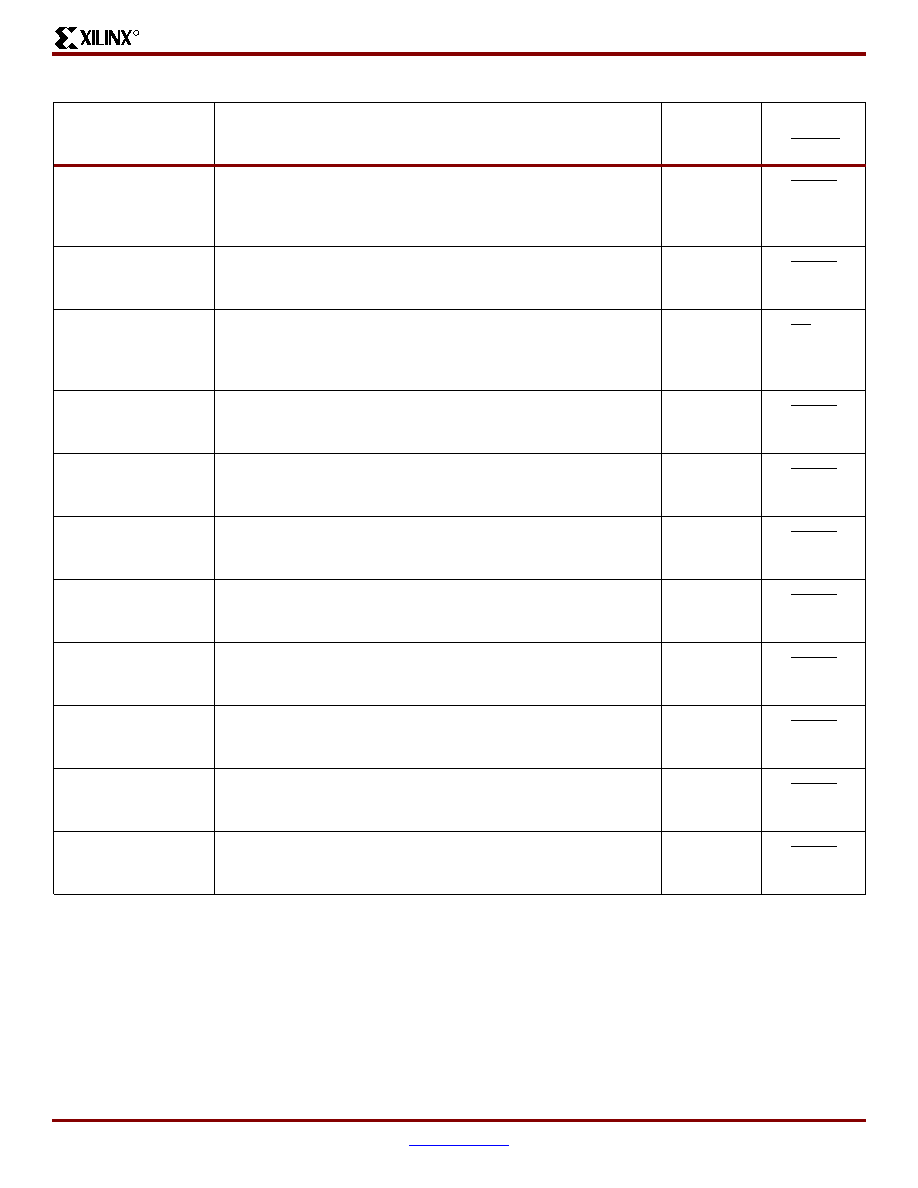

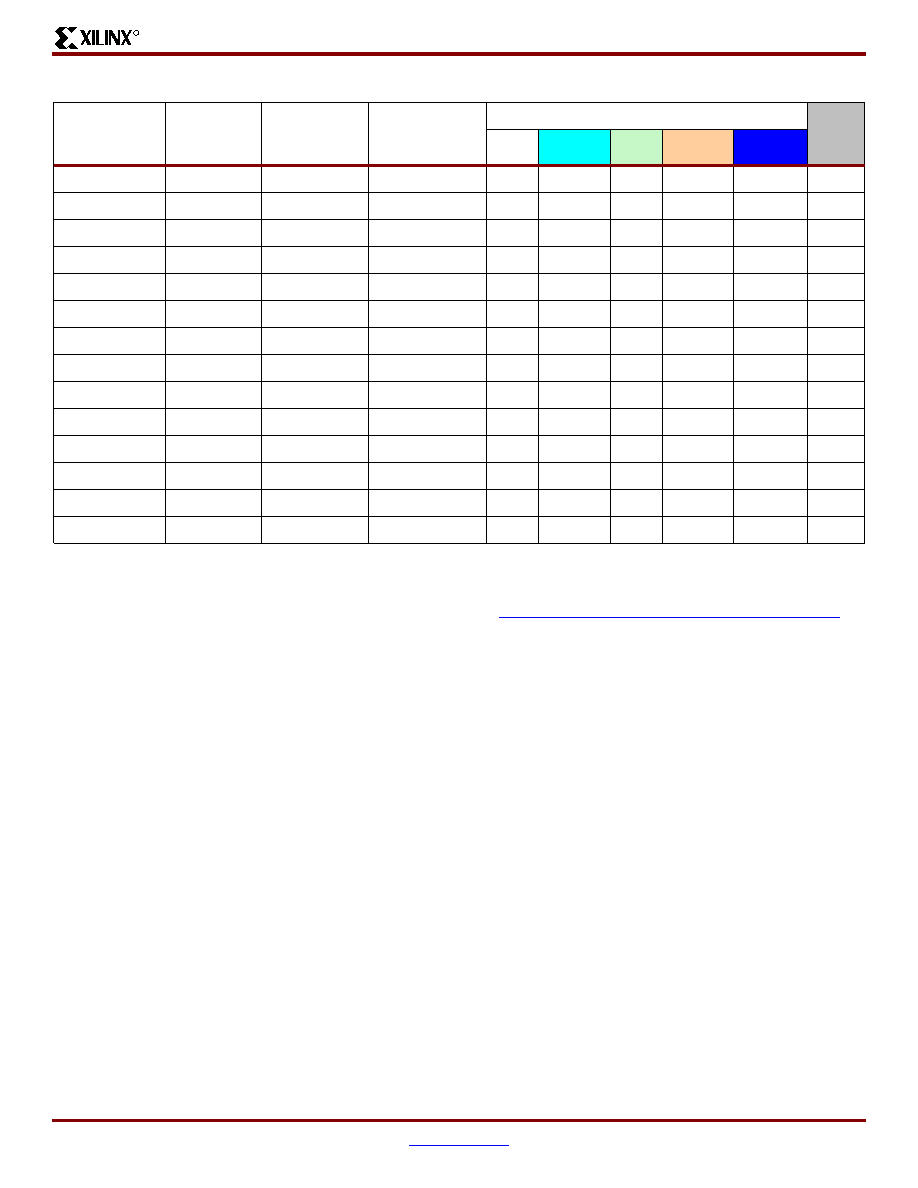

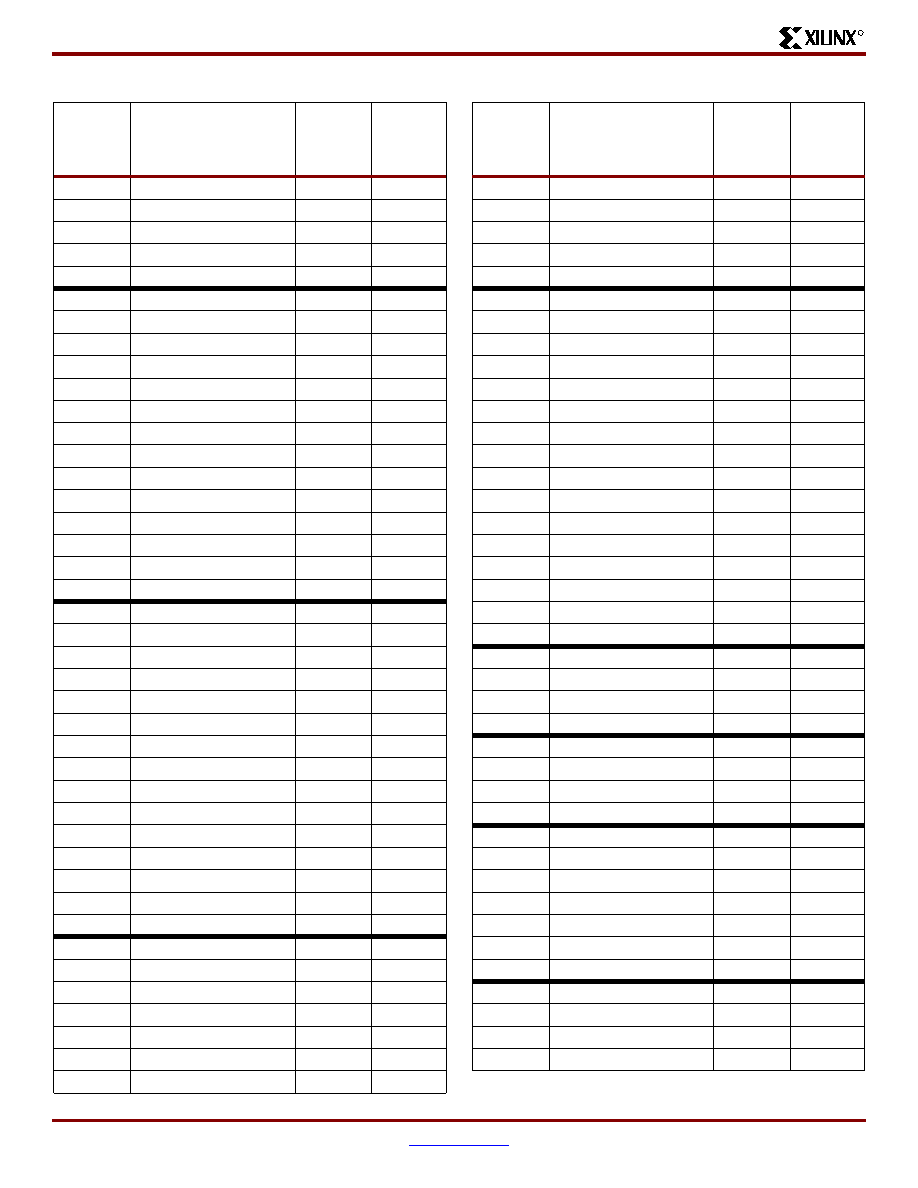

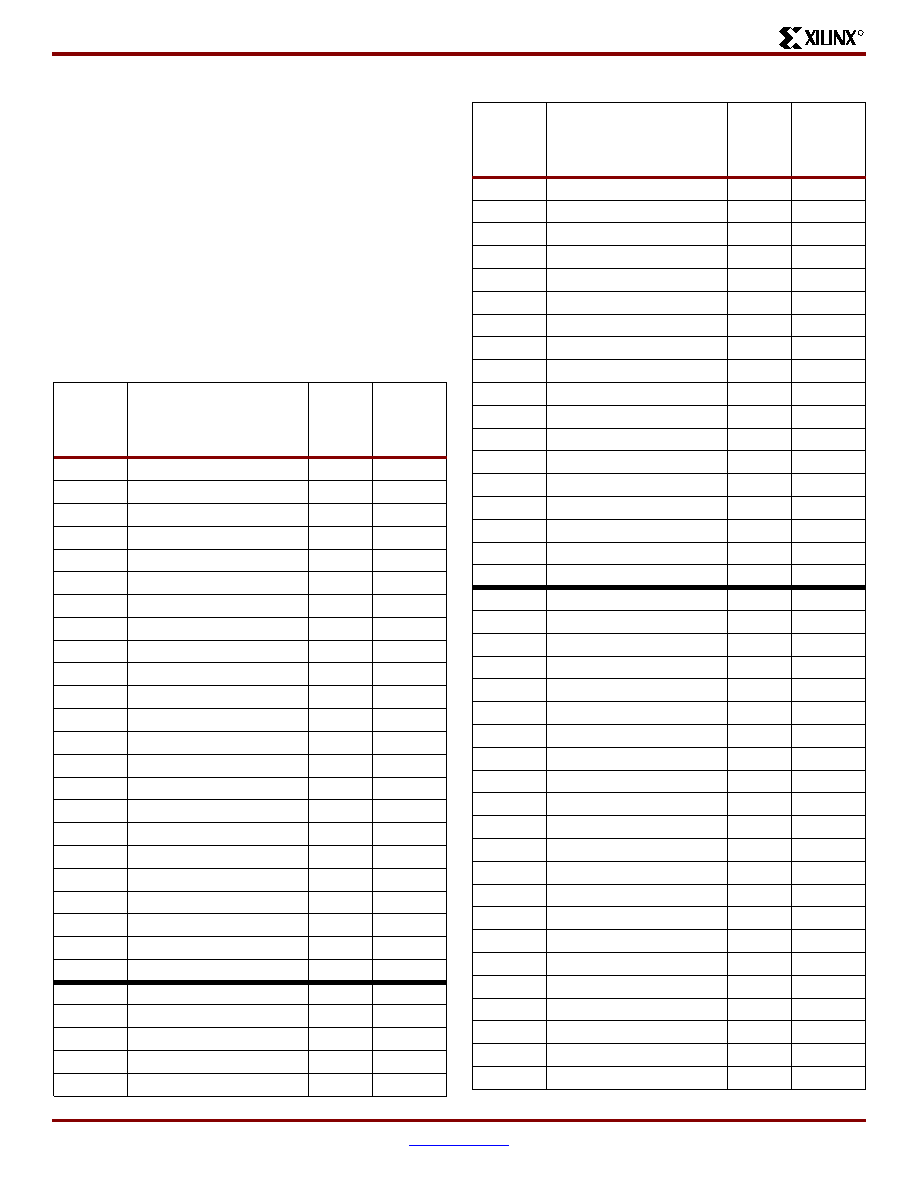

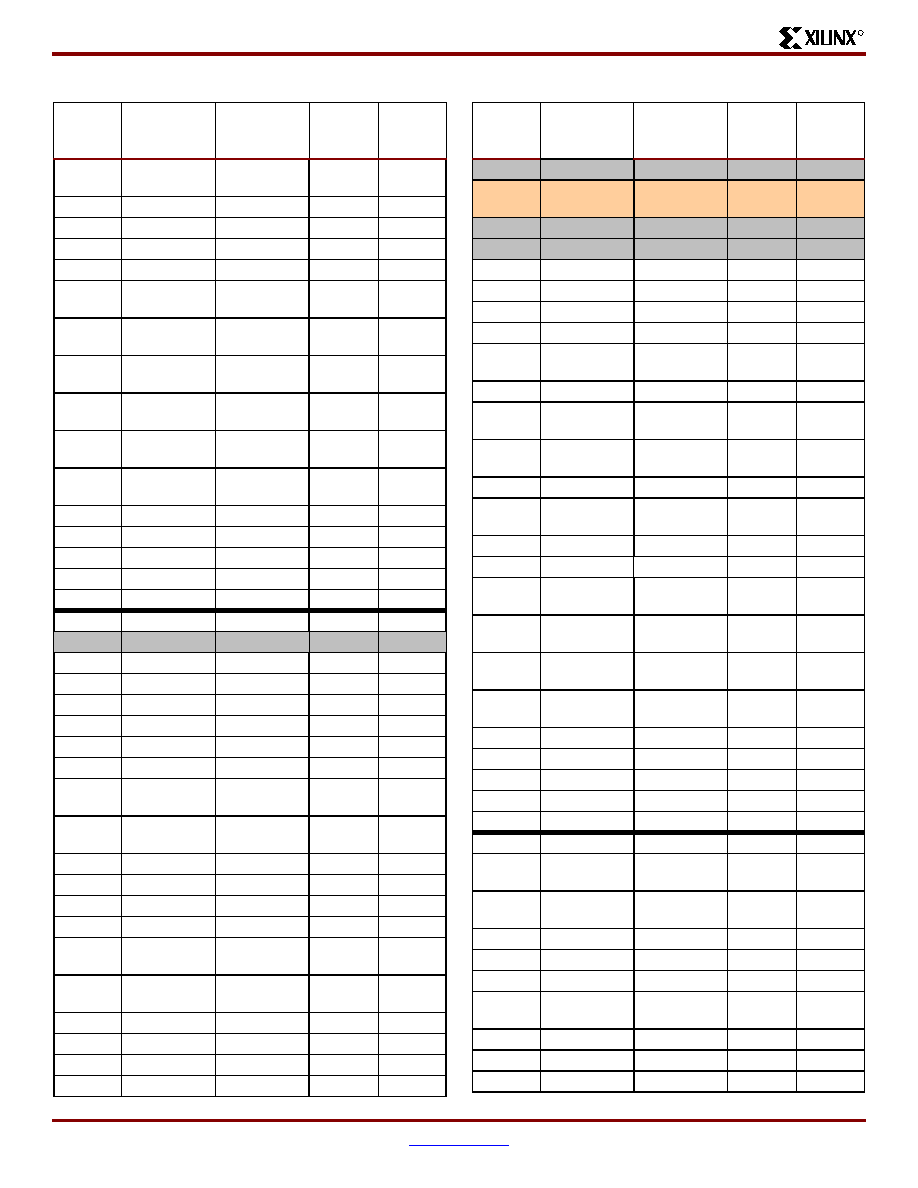

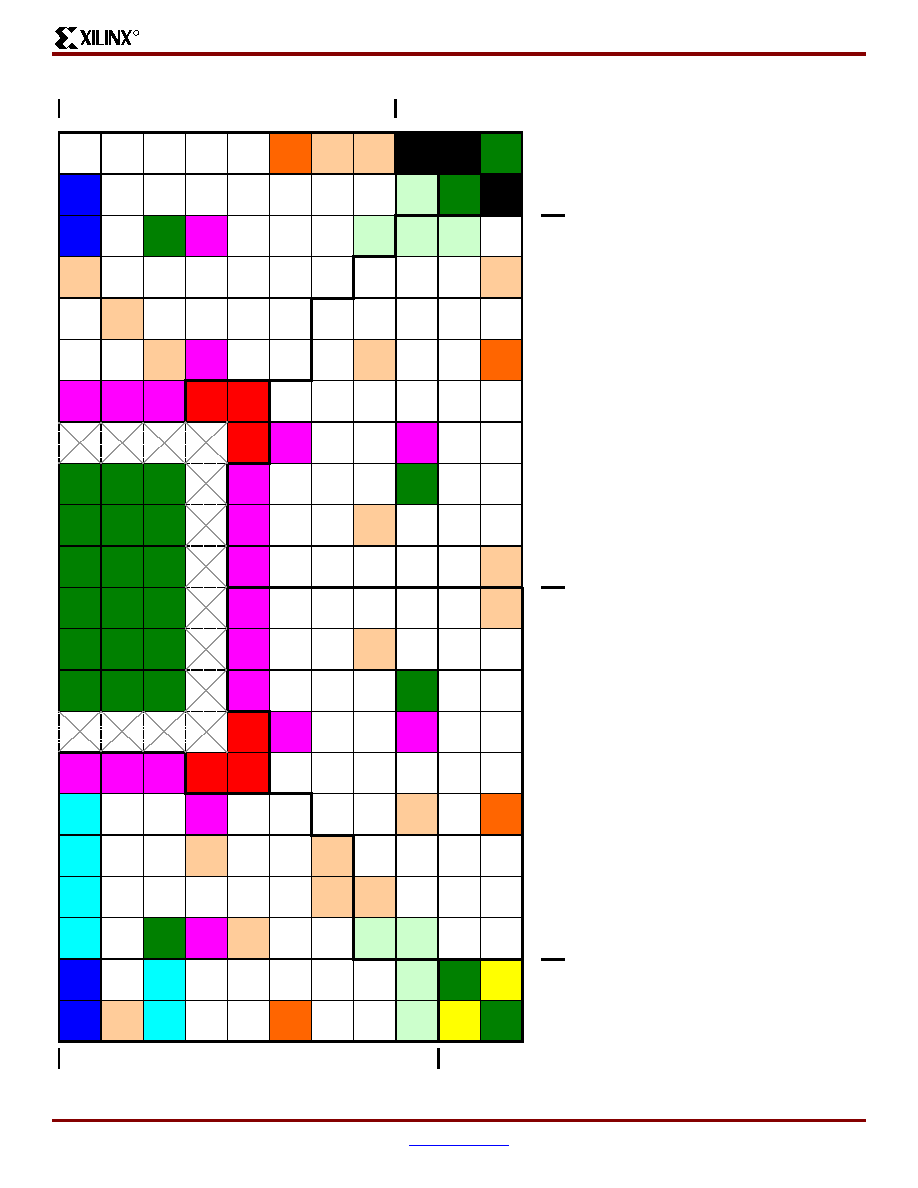

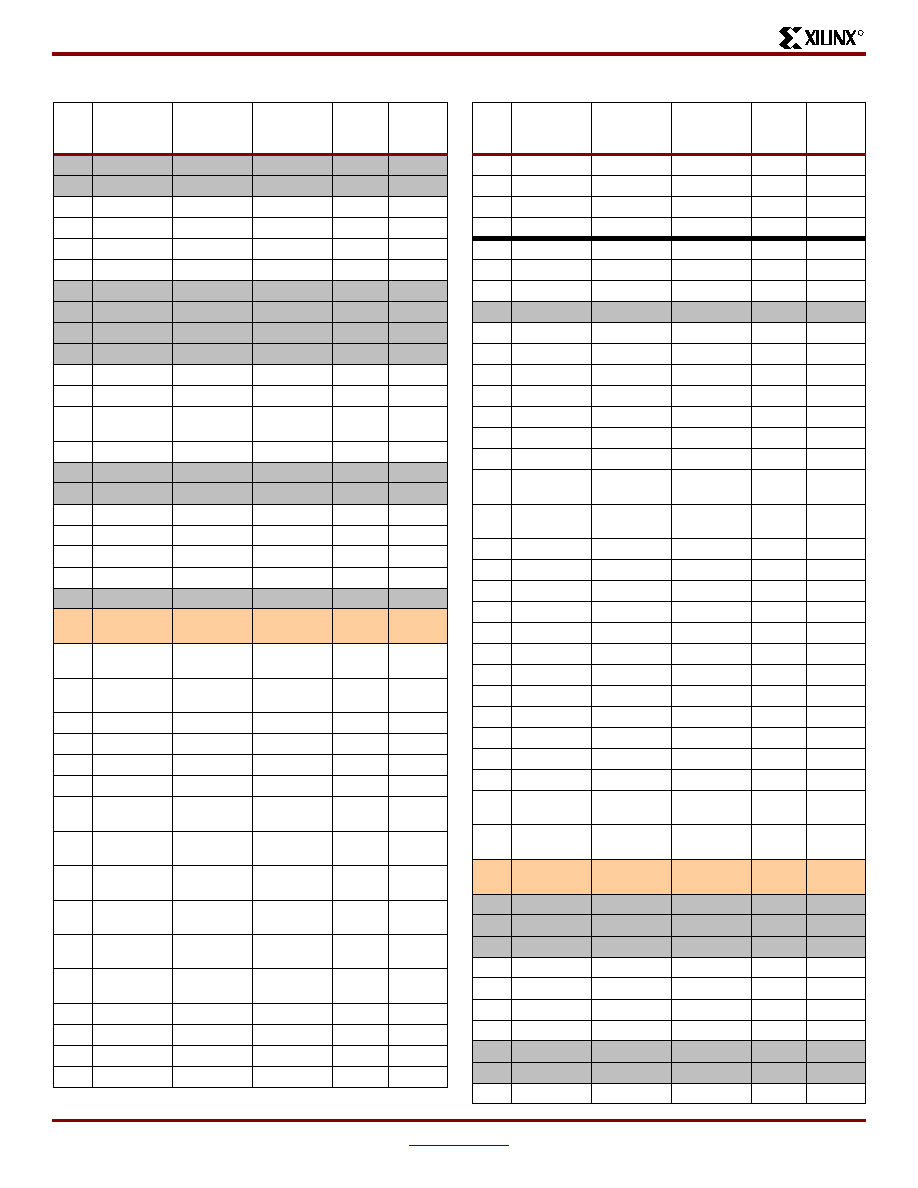

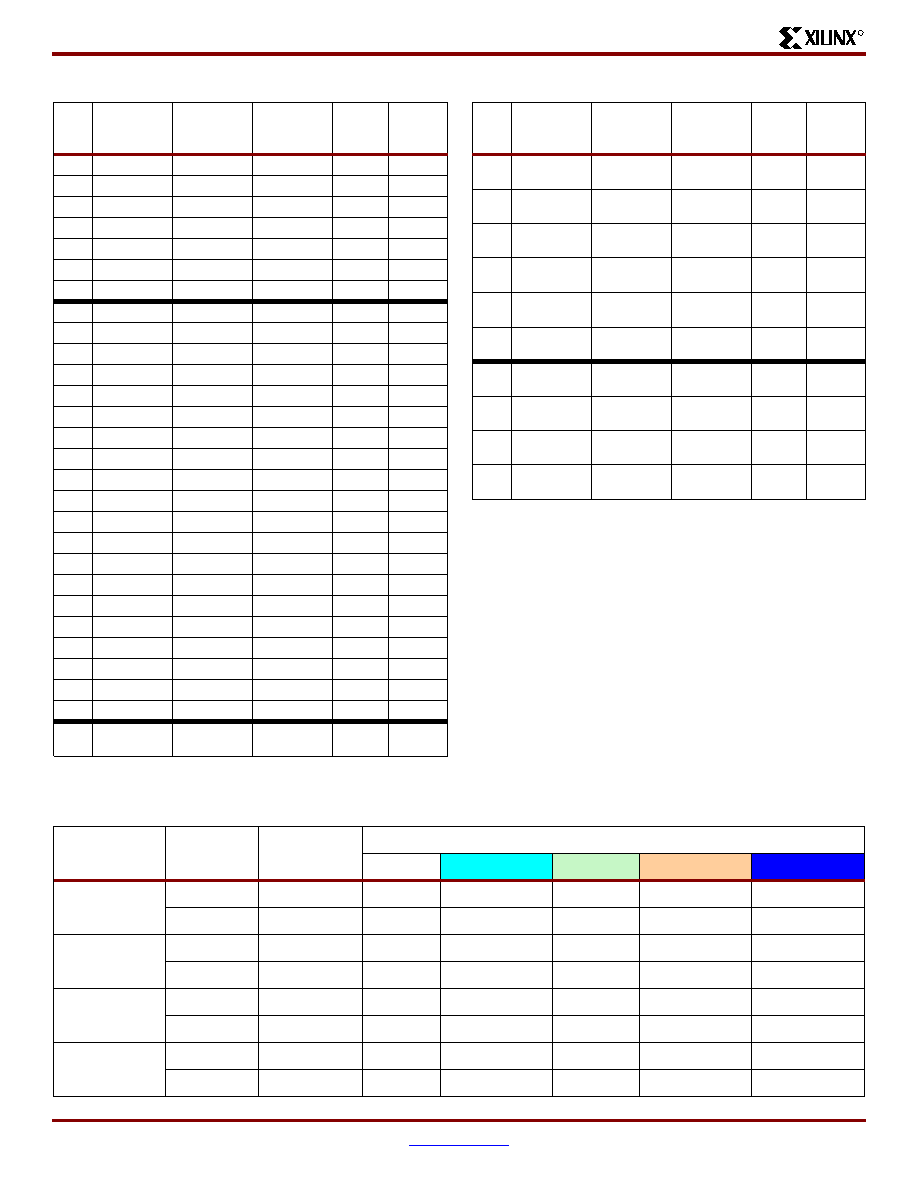

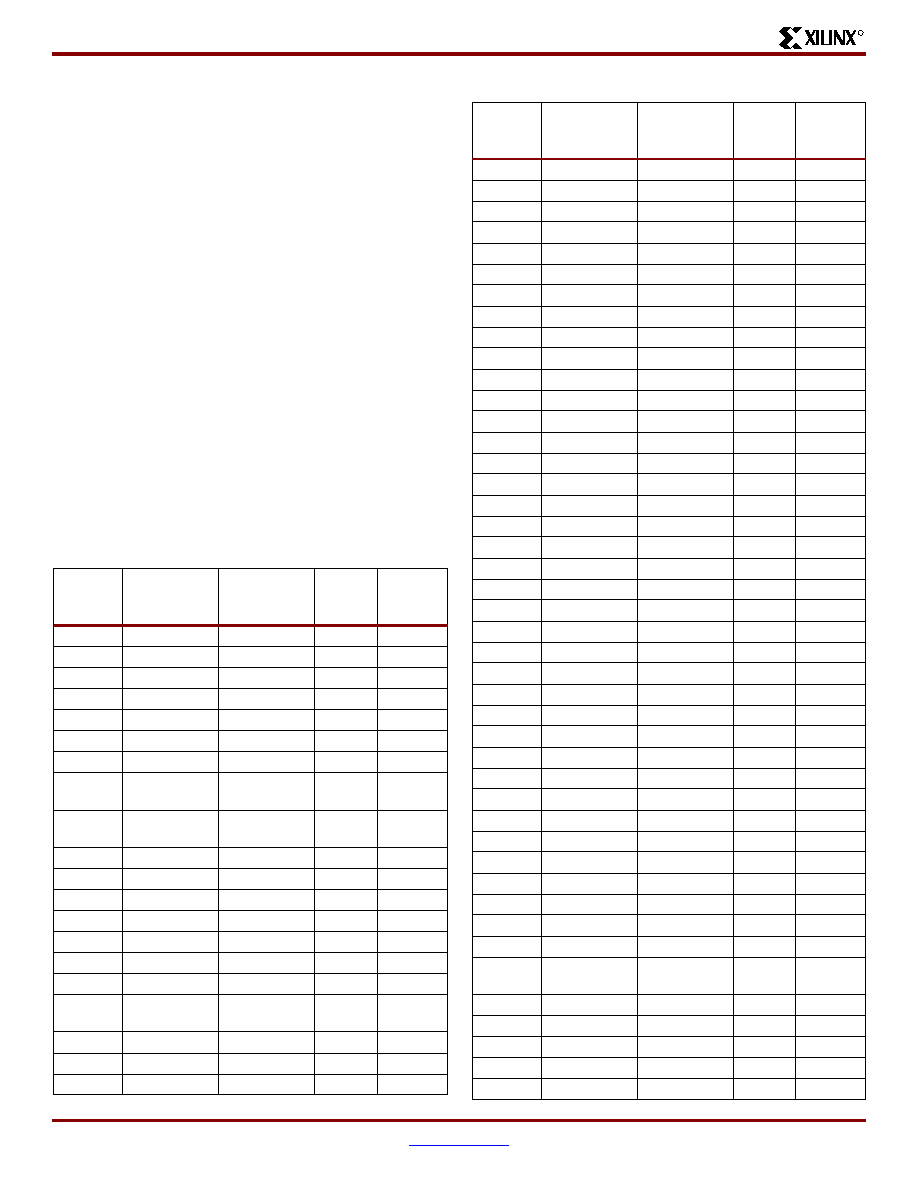

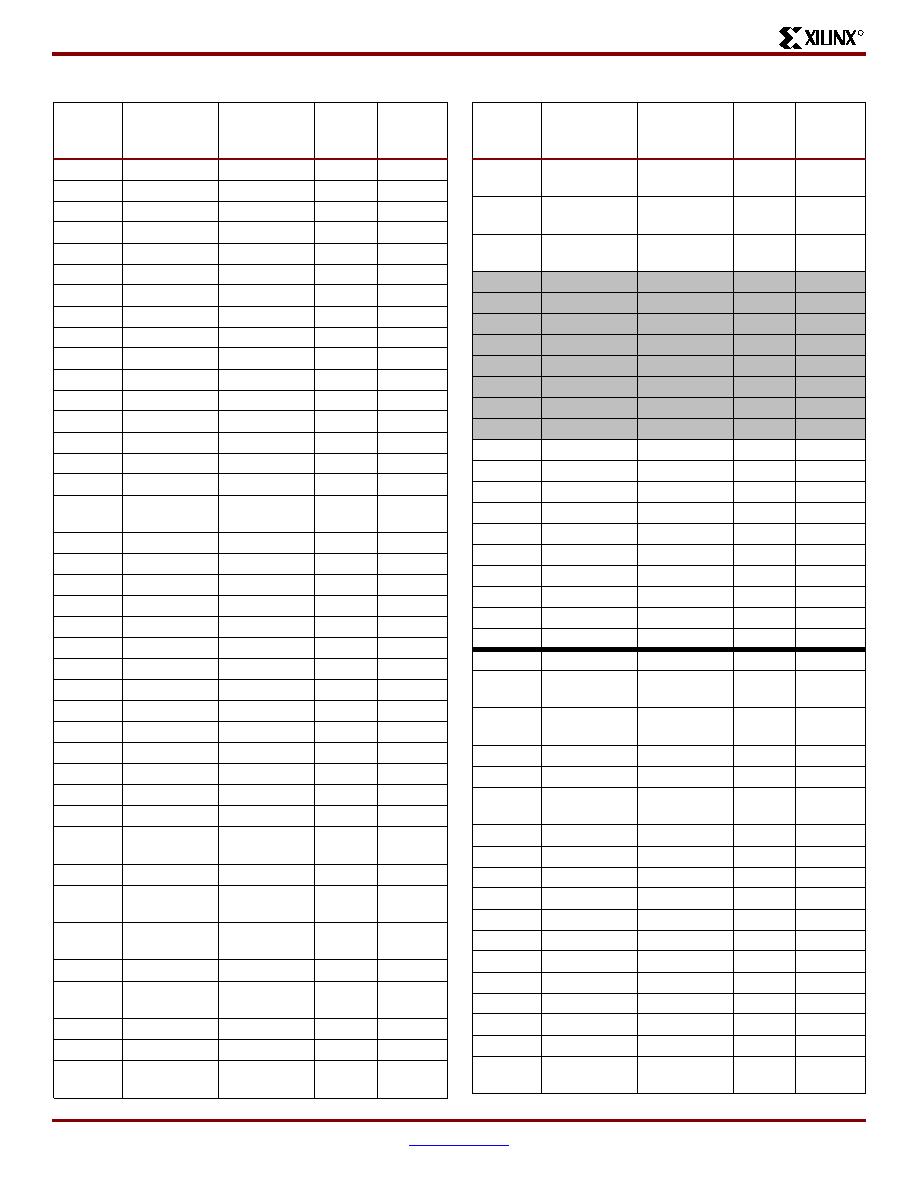

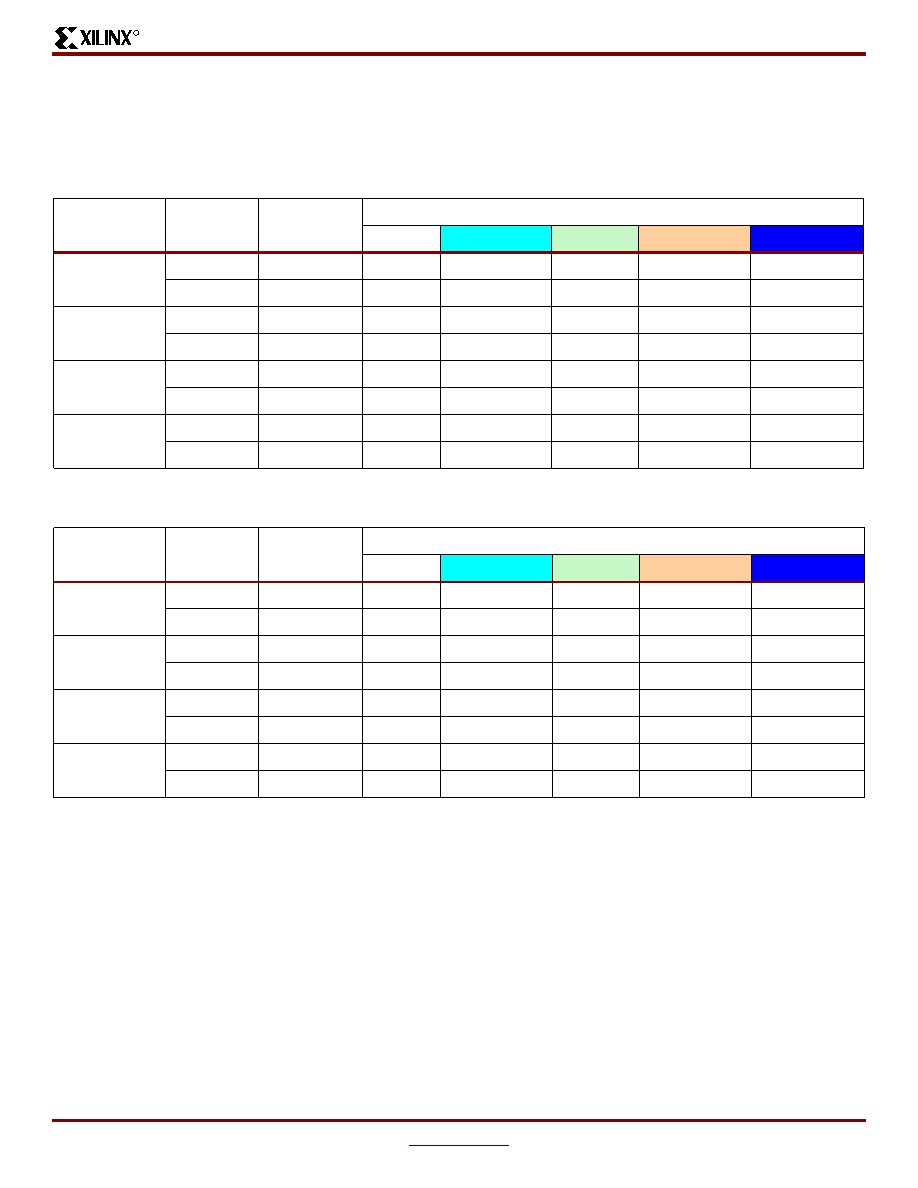

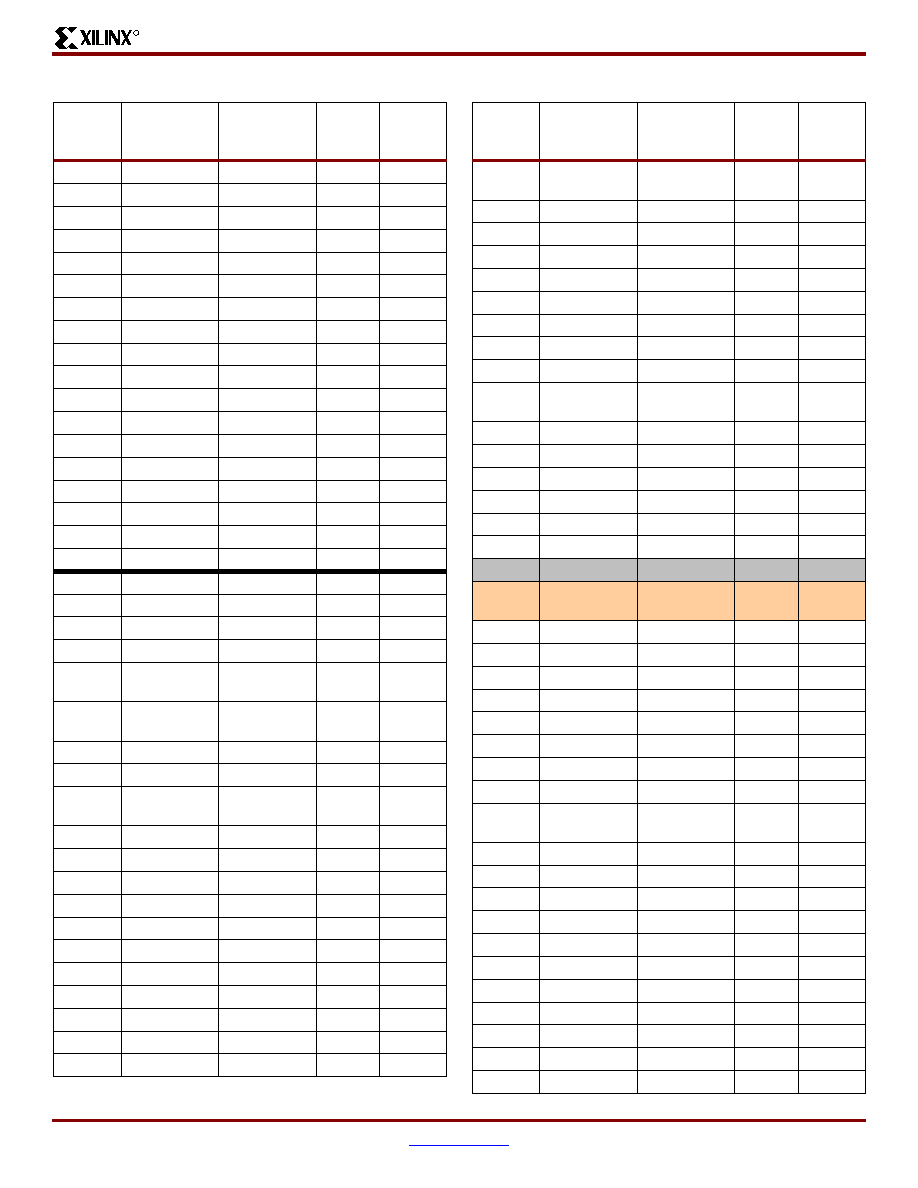

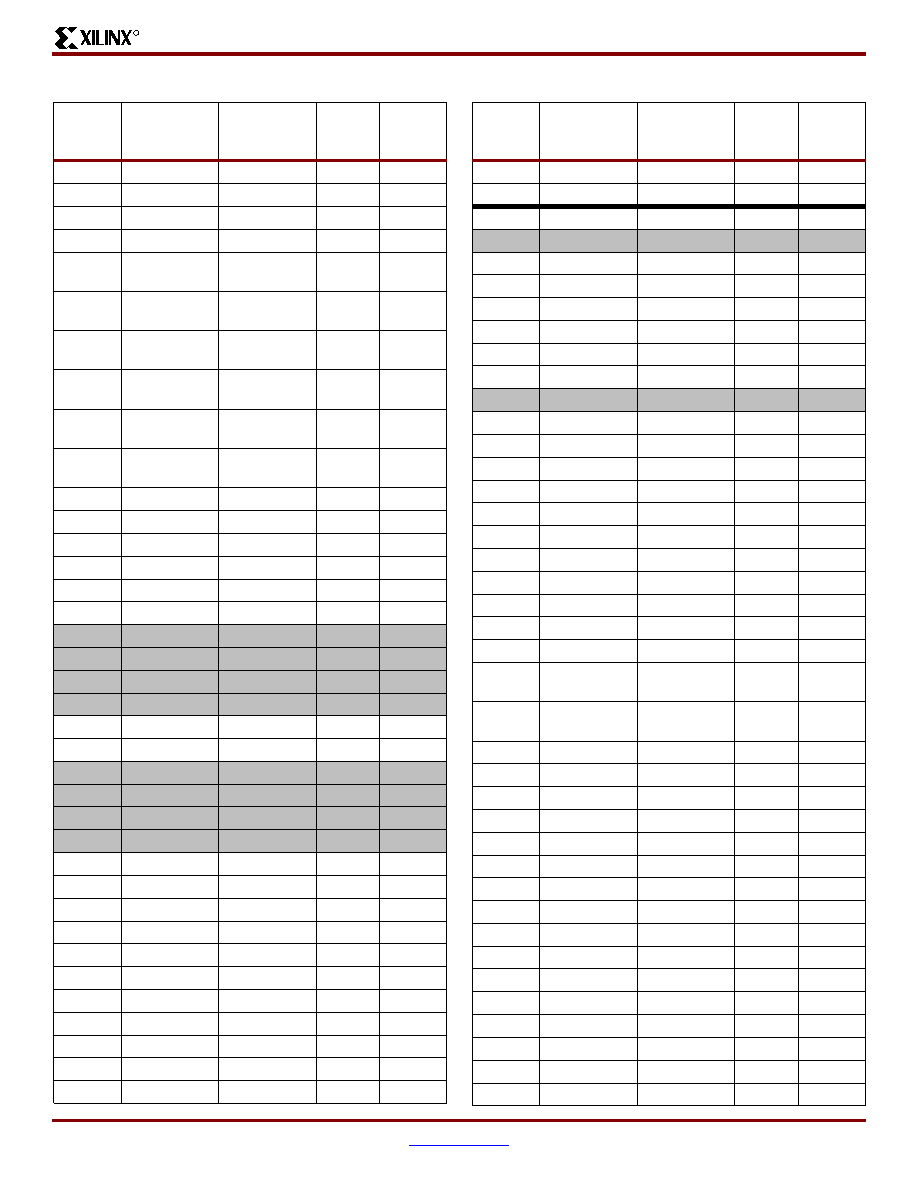

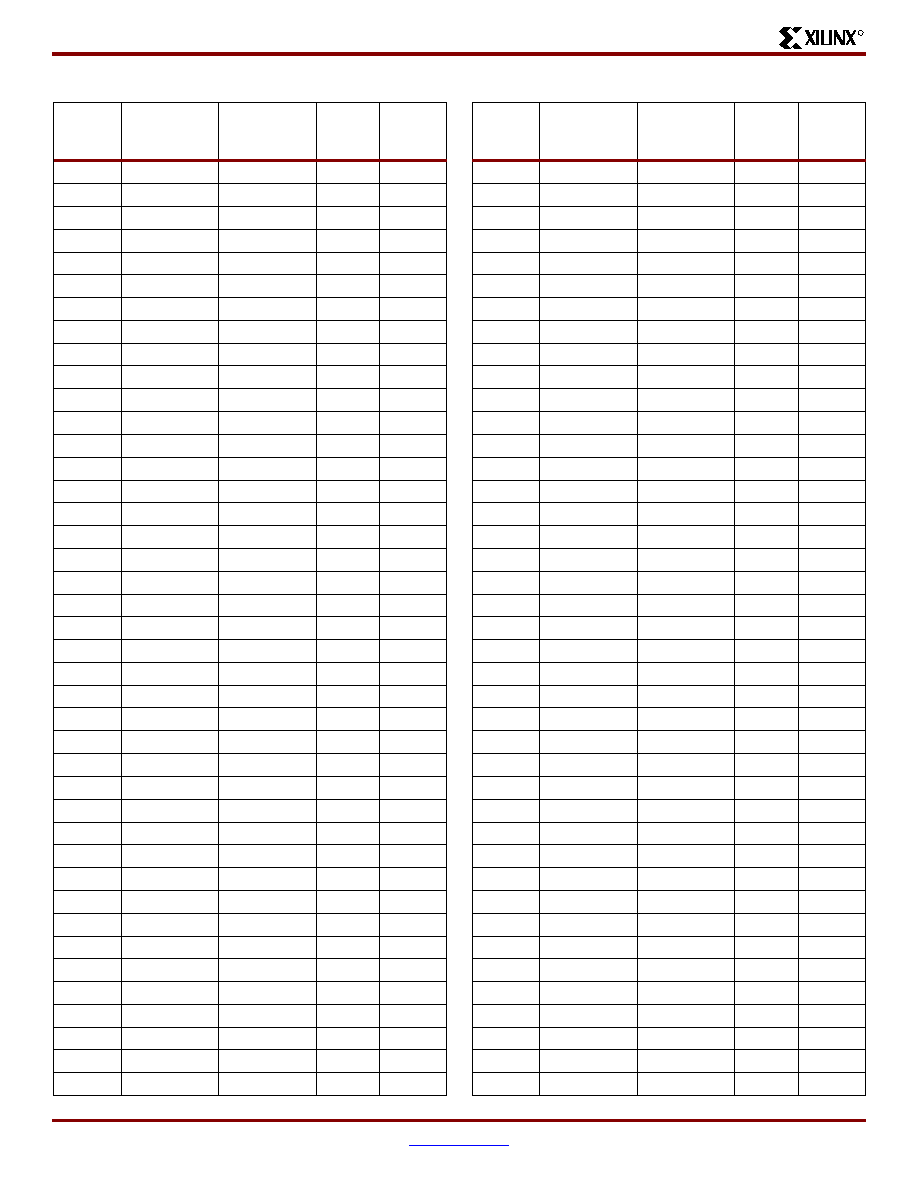

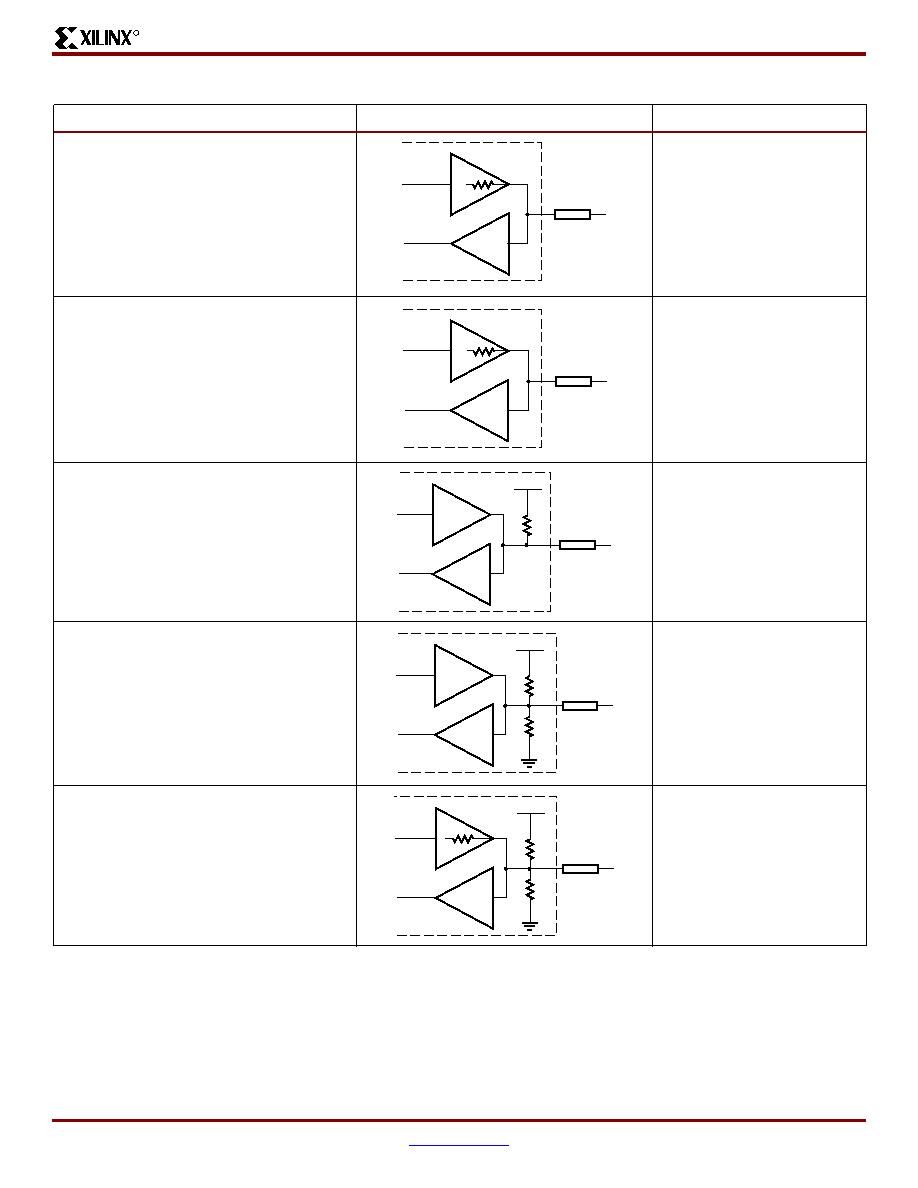

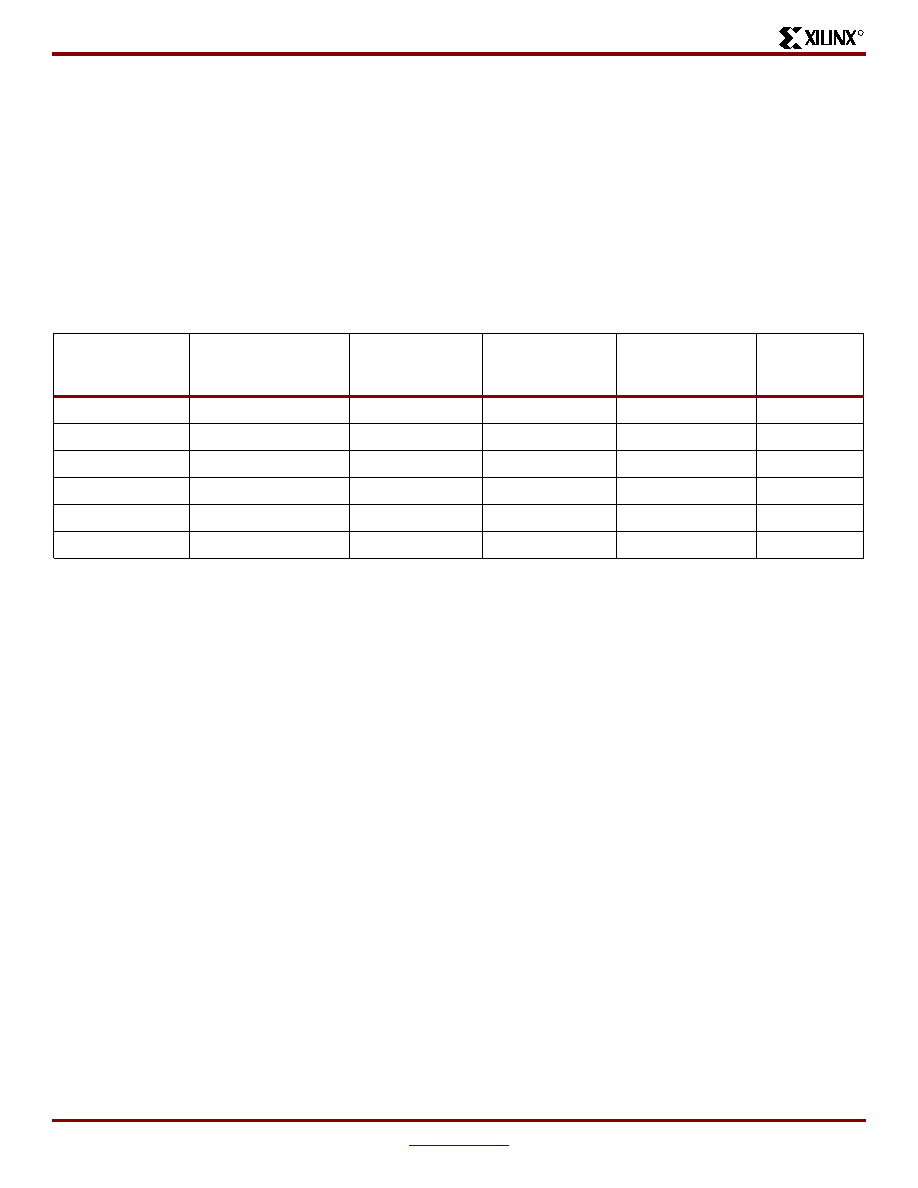

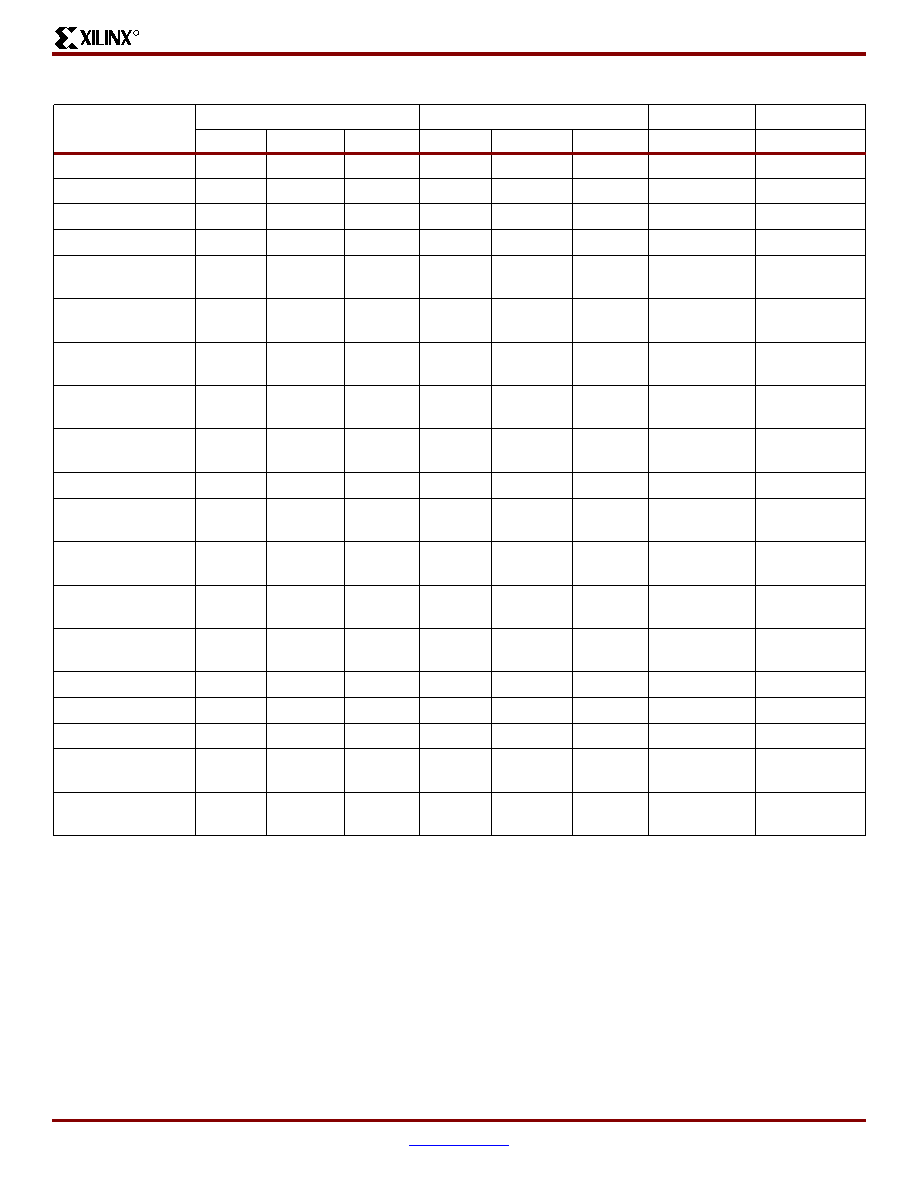

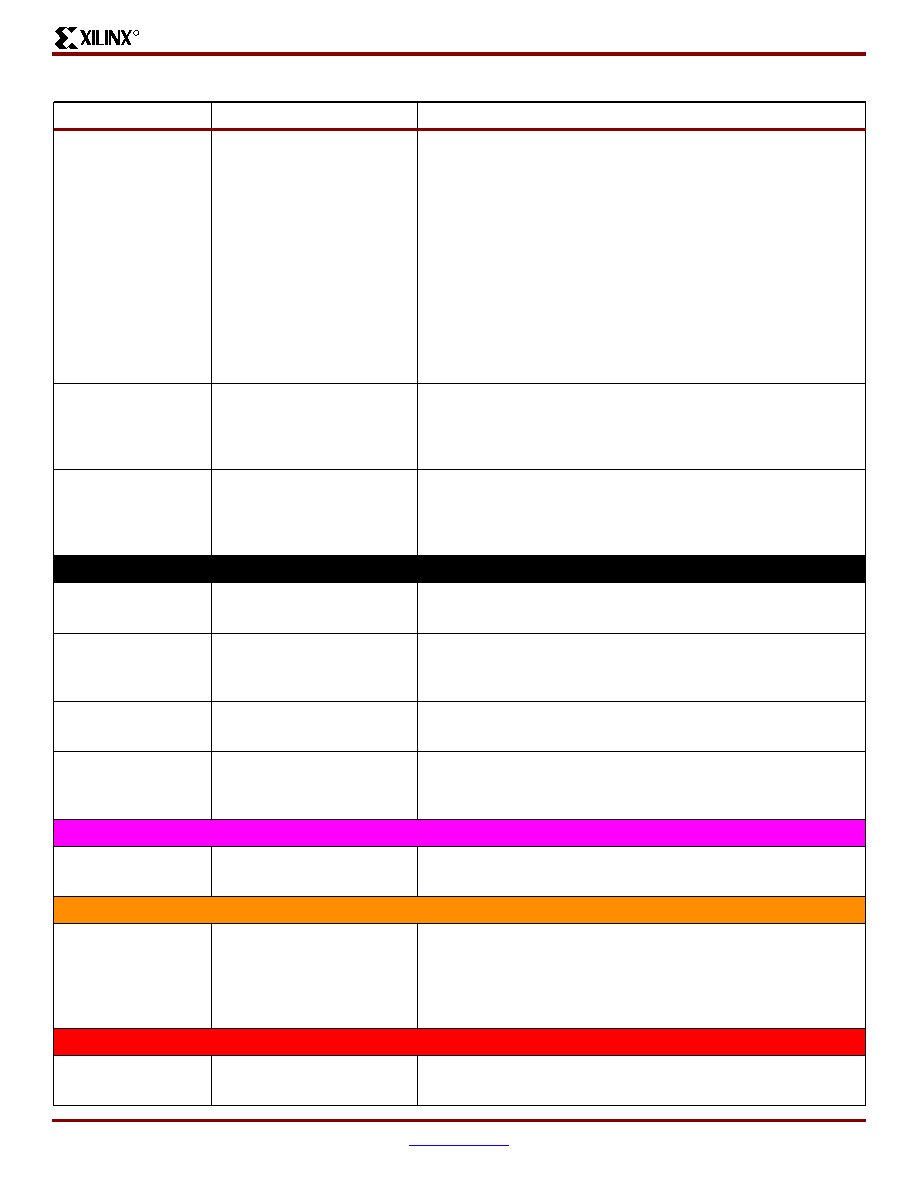

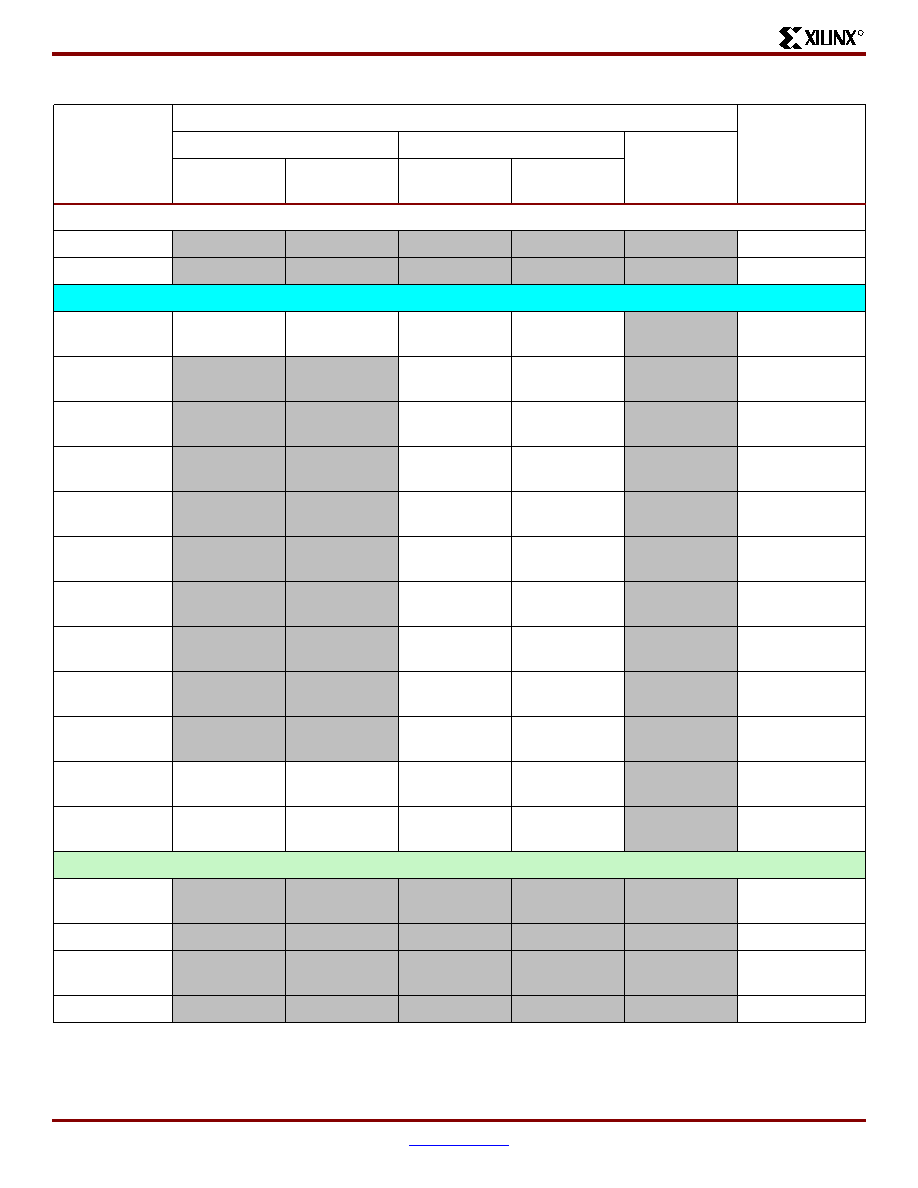

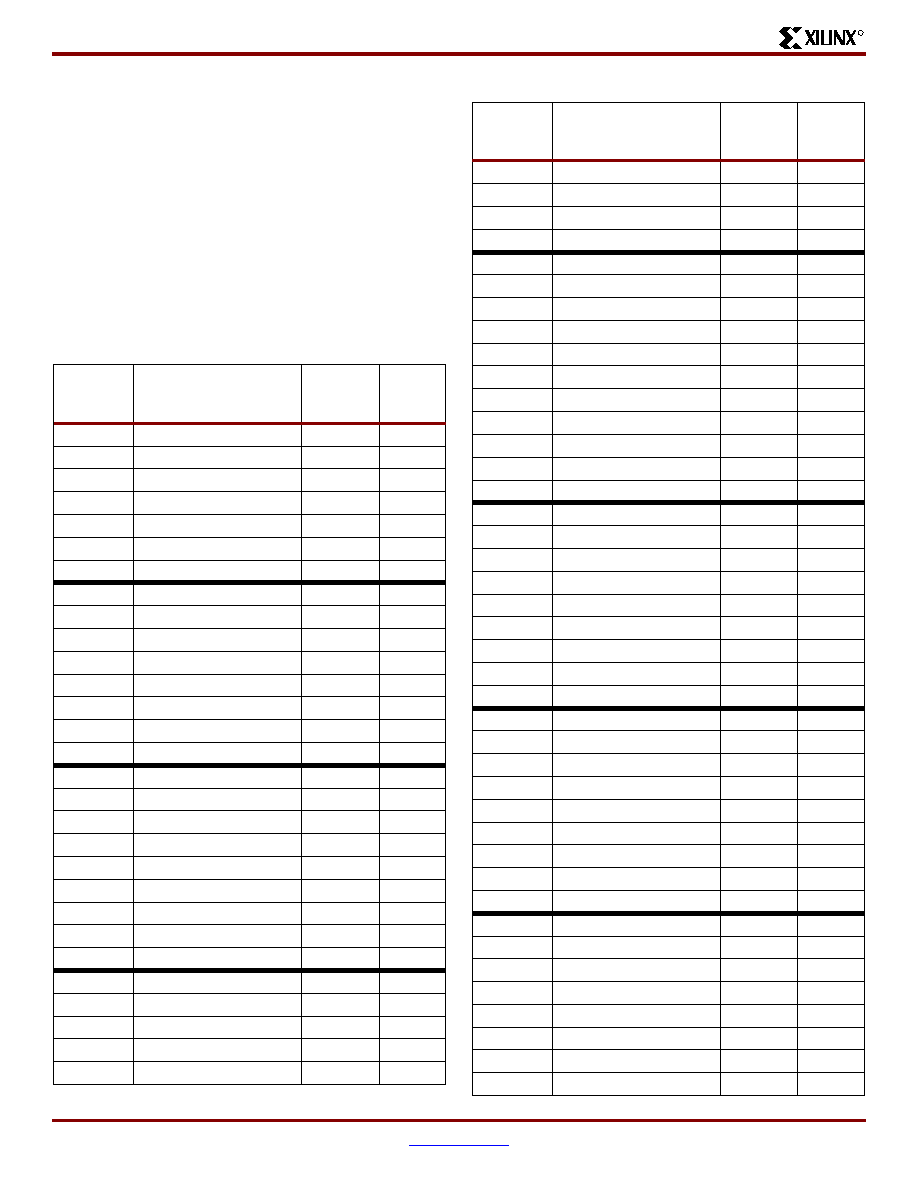

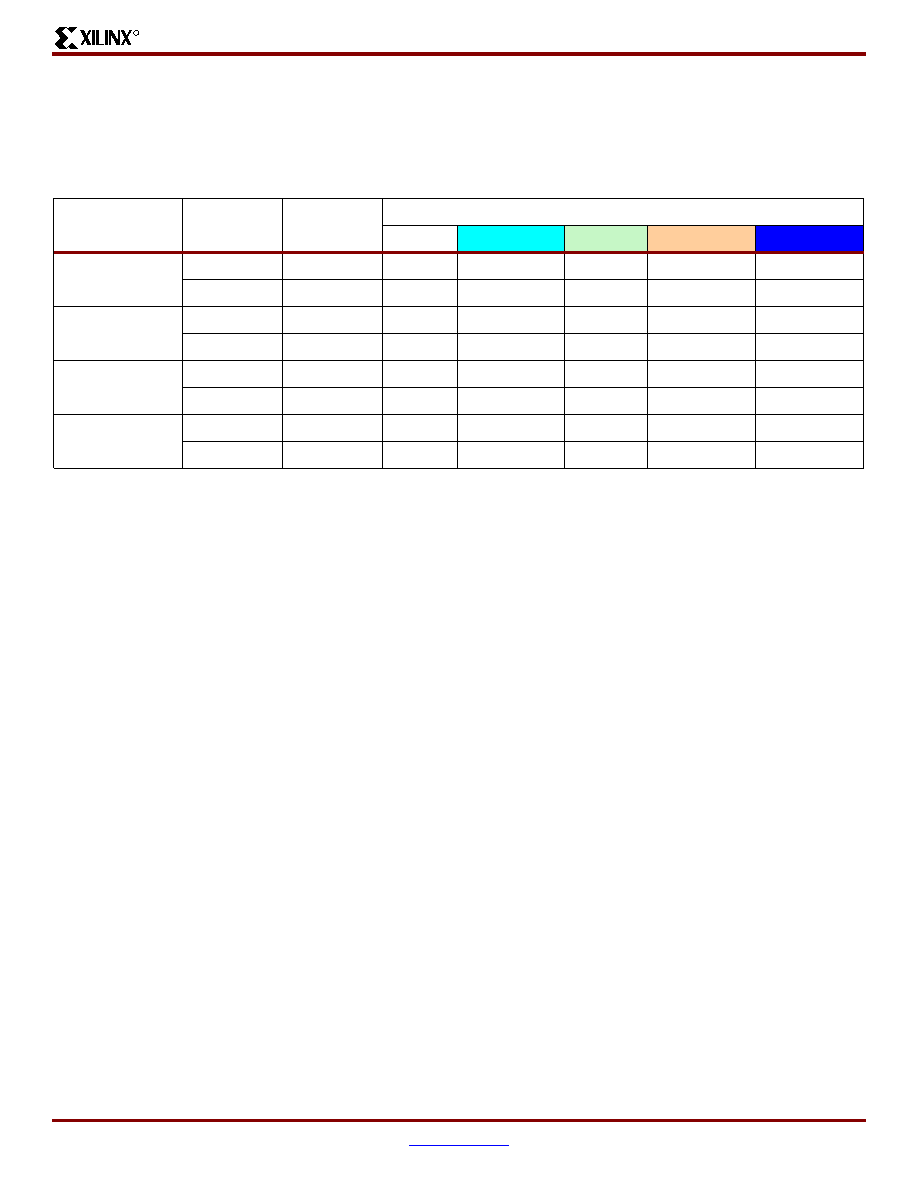

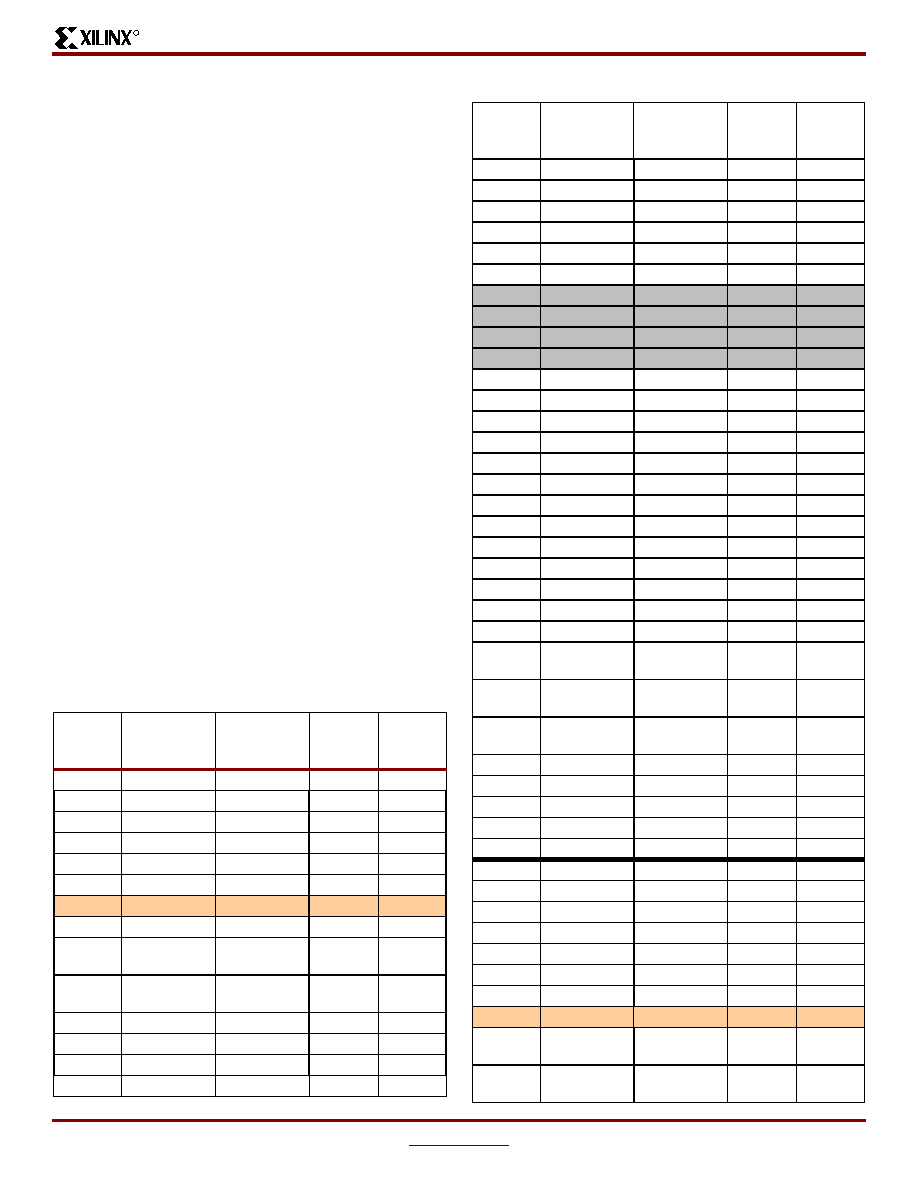

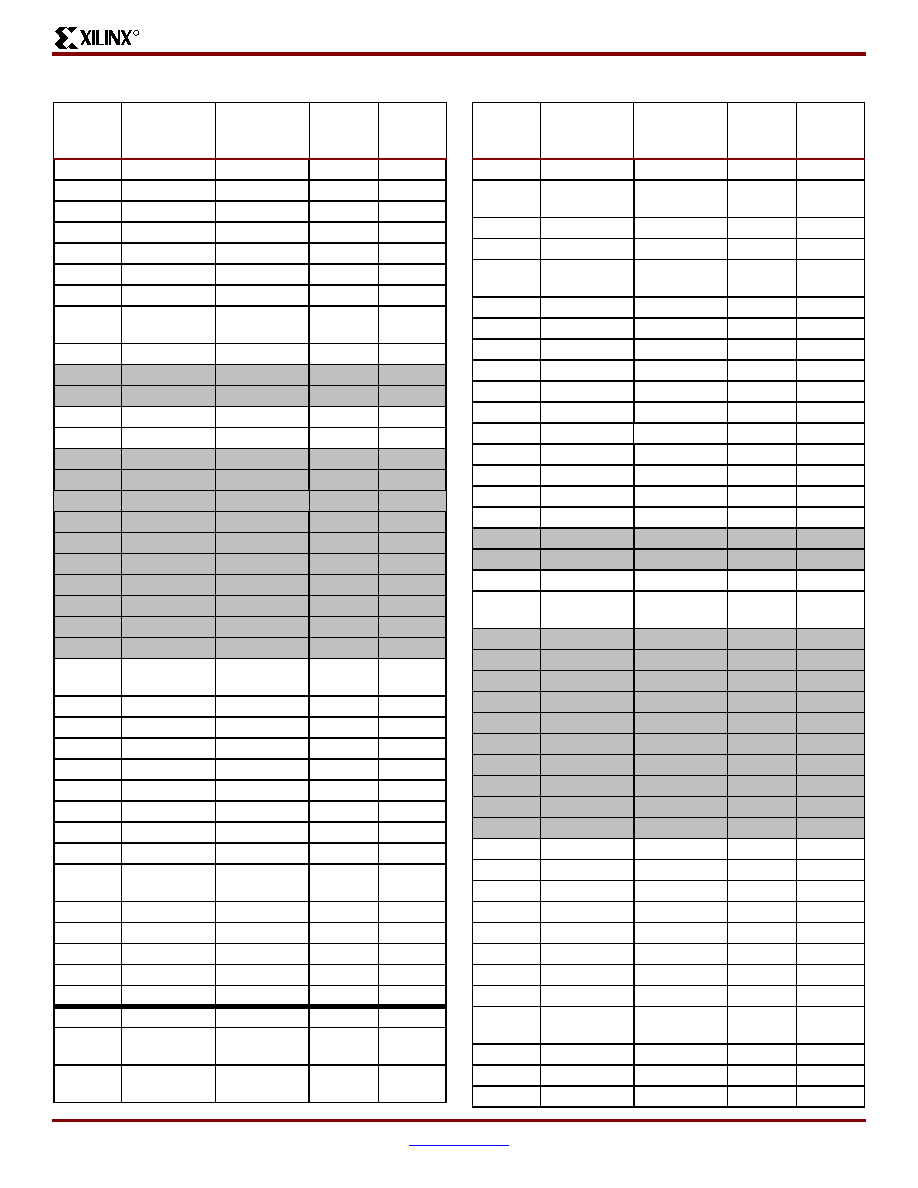

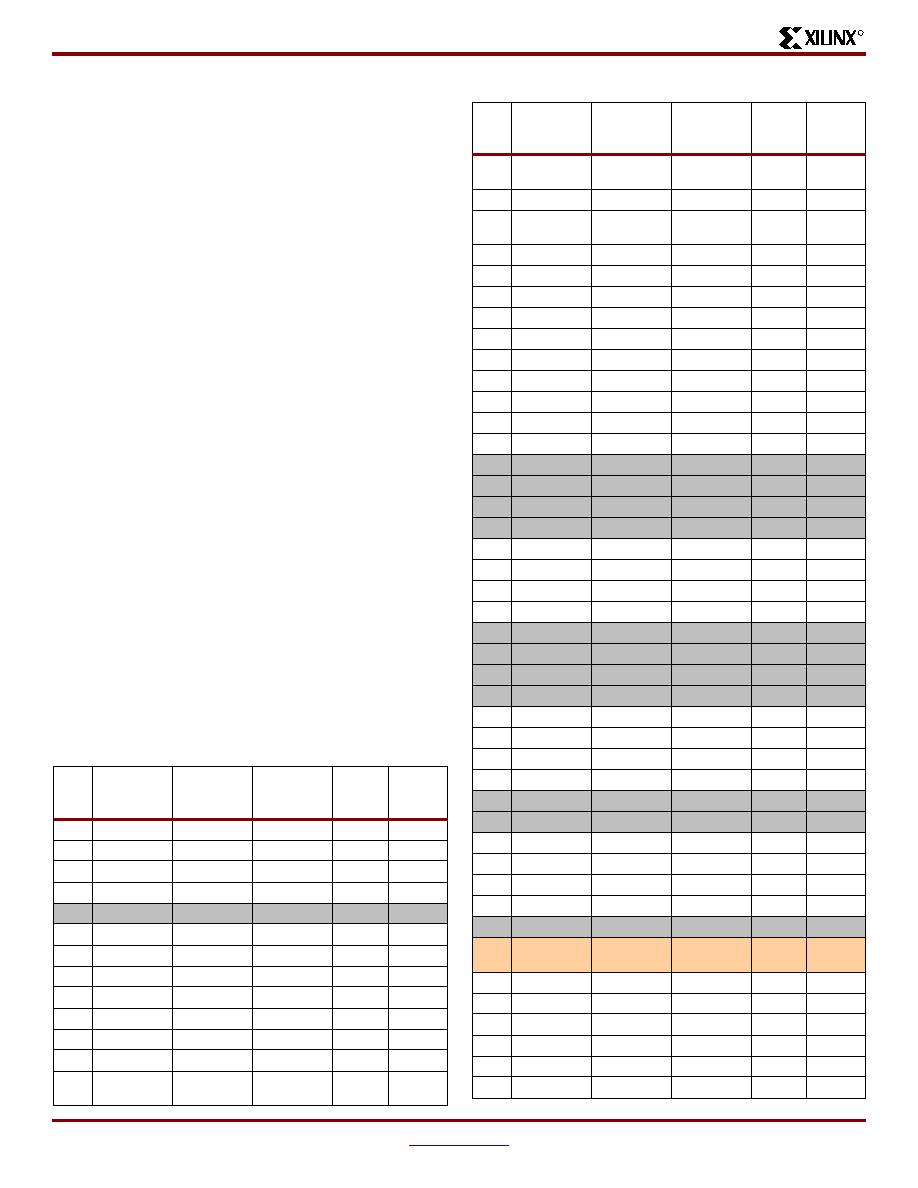

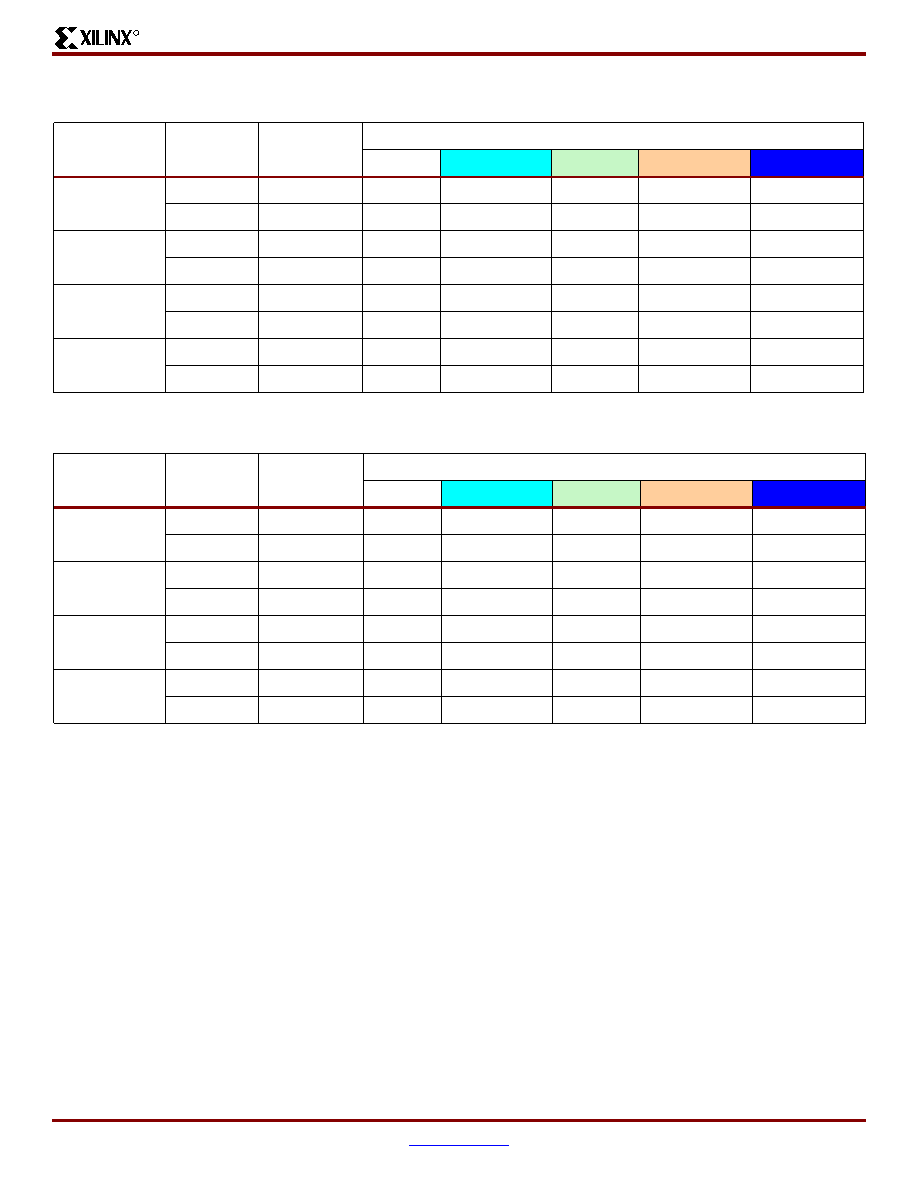

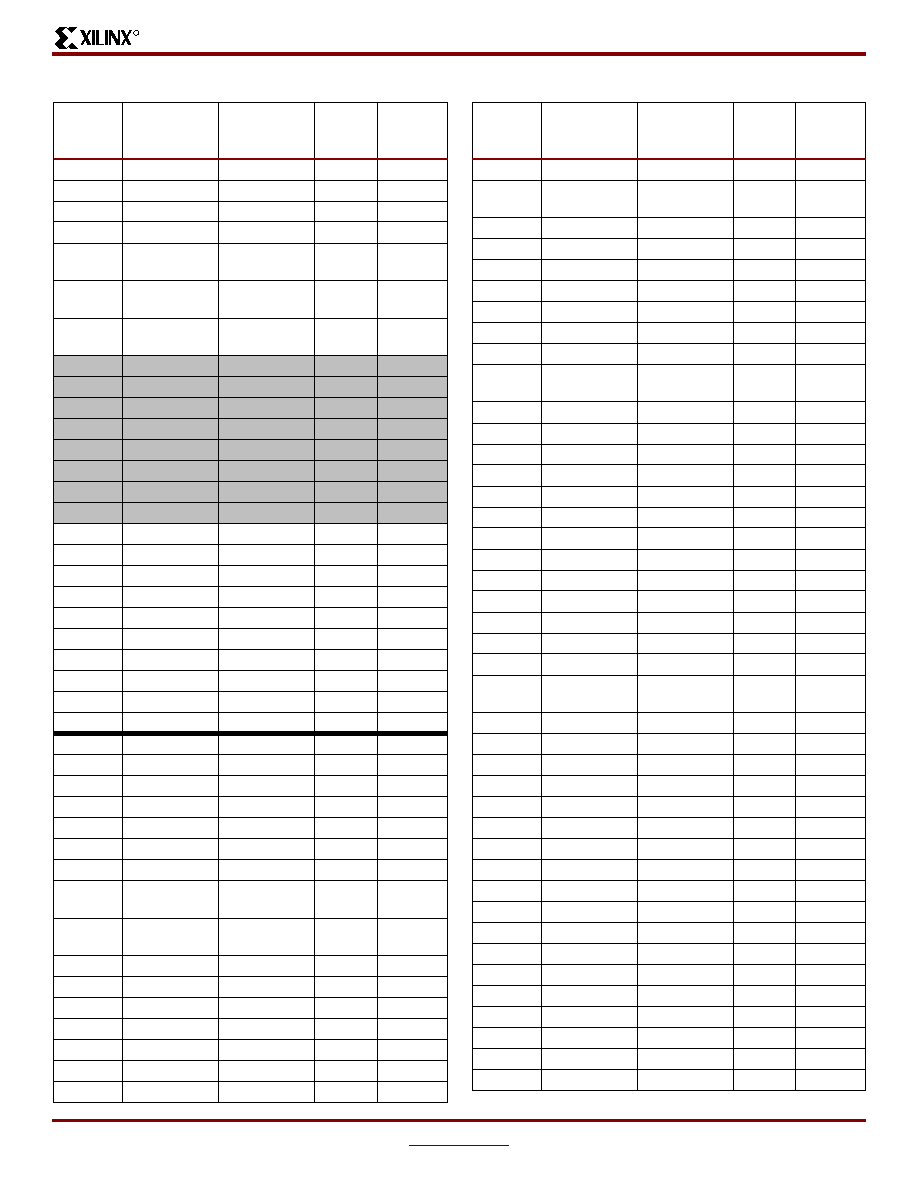

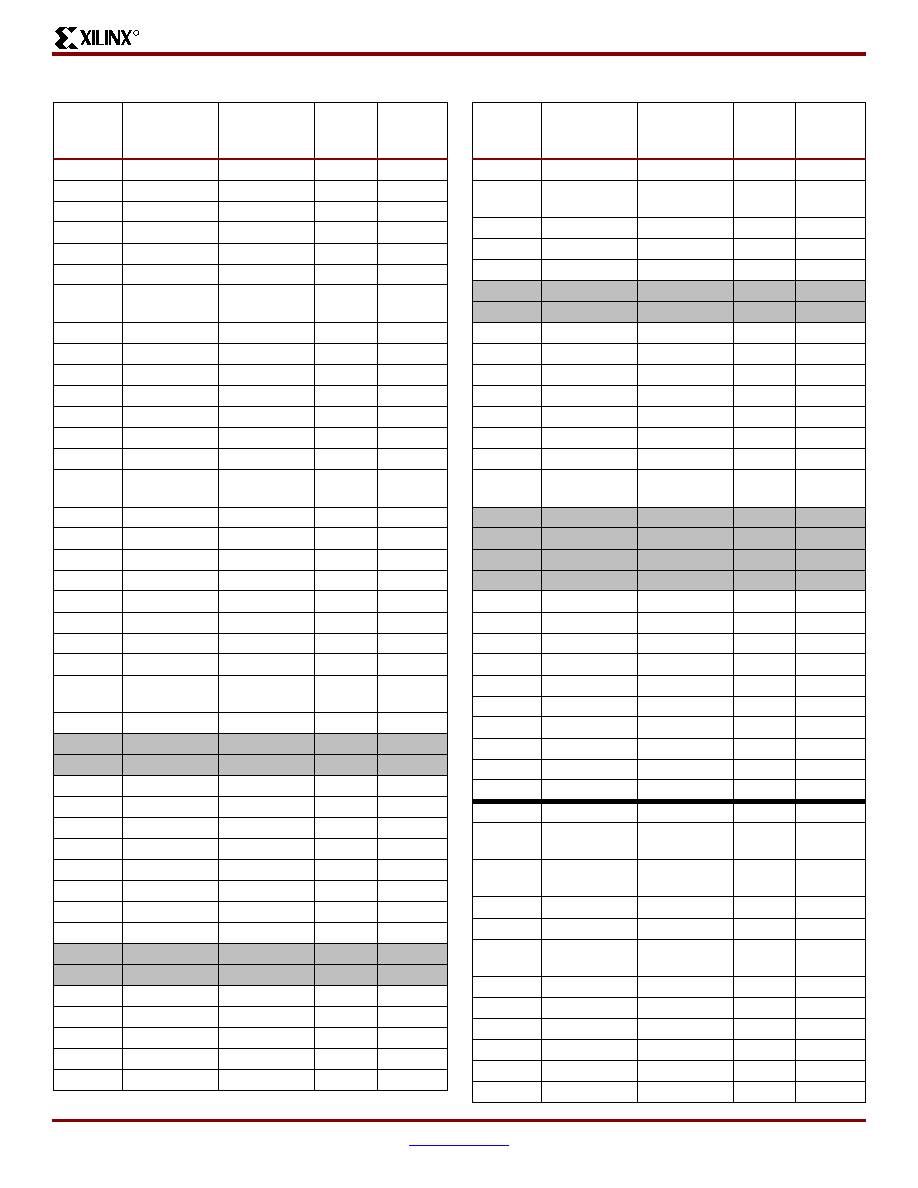

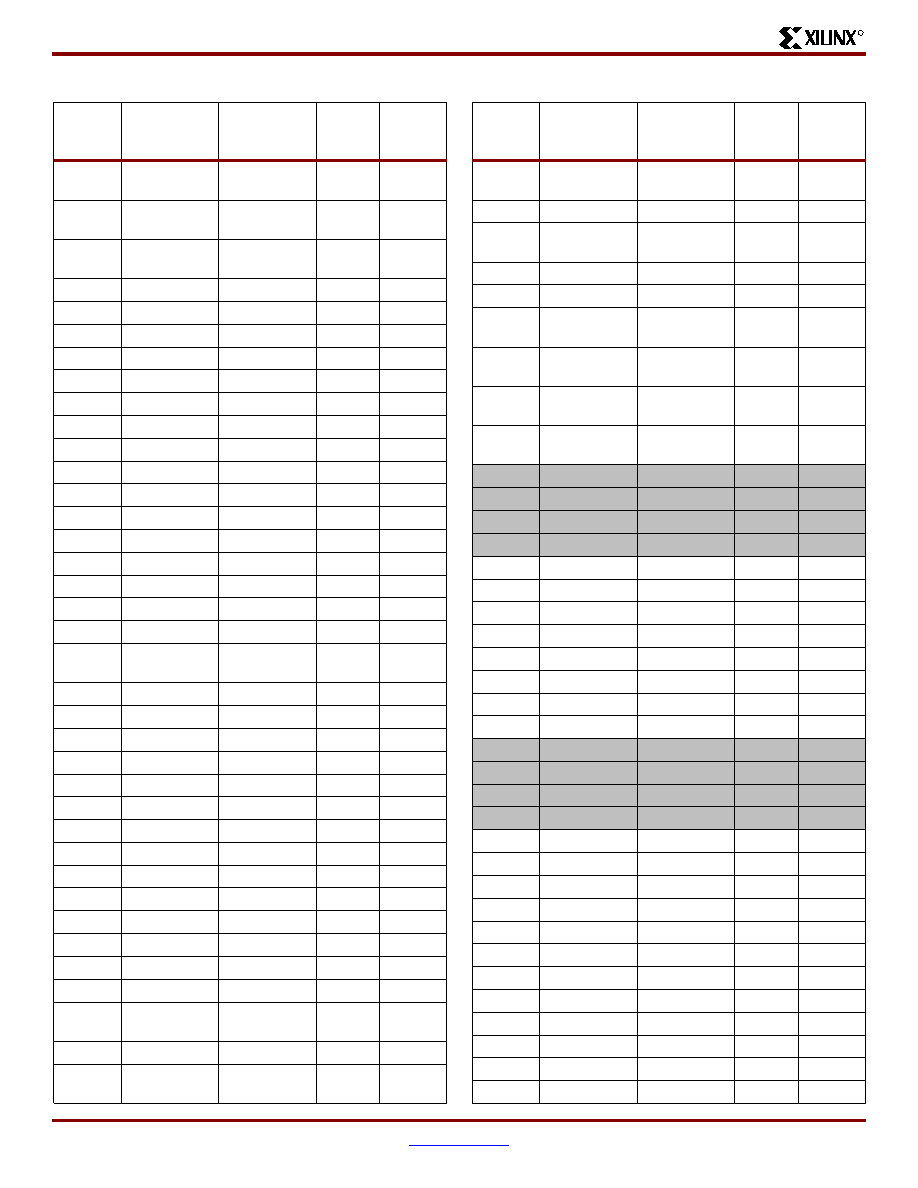

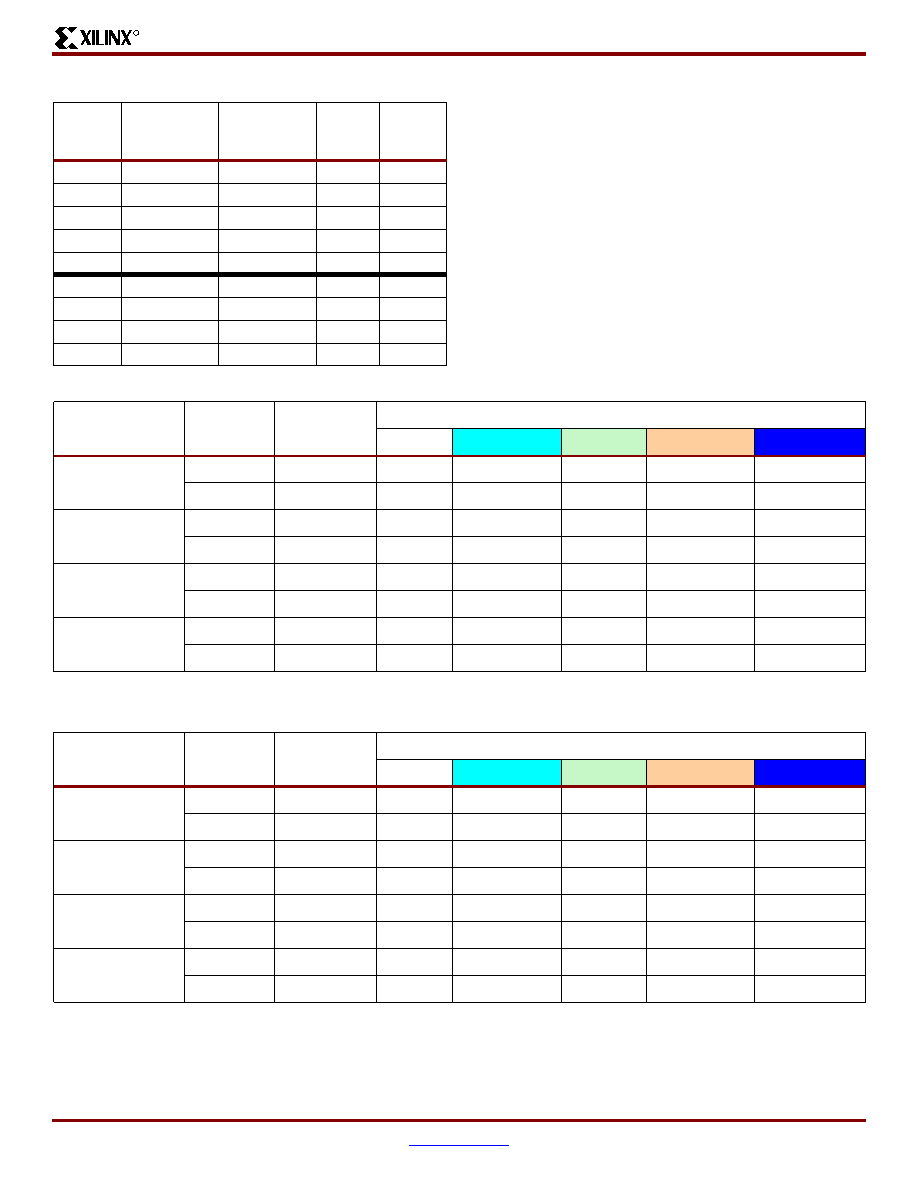

Table 3: Spartan-3 User I/O Chart

Device

Available User I/Os and Differential (Diff) I/O Pairs

VQ100

TQ144

PQ208

FT256

FG456

FG676

FG900

FG1156

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

User

Diff

XC3S50

63

29

97

46

124

56

-

-

-

-

-

-

-

-

-

-

XC3S200

63

29

97

46

141

62

173

76

-

-

-

-

-

-

-

-

XC3S400

-

-

97

46

141

62

173

76

264

116

-

-

-

-

-

-

XC3S1000

-

-

-

-

-

-

173

76

333

149

391

175

-

-

-

-

XC3S1500

-

-

-

-

-

-

-

-

333

149

487

221

-

-

-

-

XC3S2000

-

-

-

-

-

-

-

-

-

-

489

221

565

270

-

-

XC3S4000

-

-

-

-

-

-

-

-

-

-

-

-

633

300

712

312

XC3S5000

-

-

-

-

-

-

-

-

-

-

-

-

633

300

784

344

Notes:

1.

All device options listed in a given package column are pin-compatible.

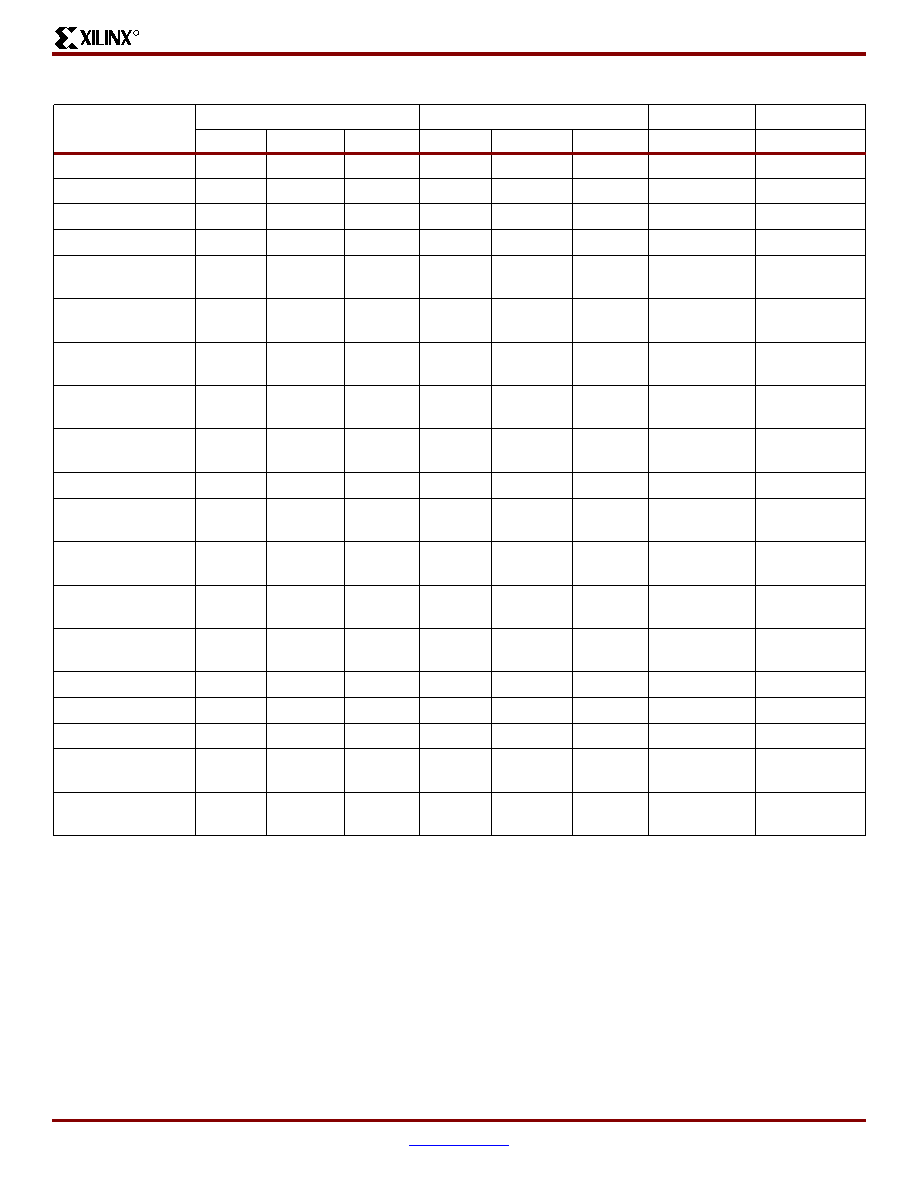

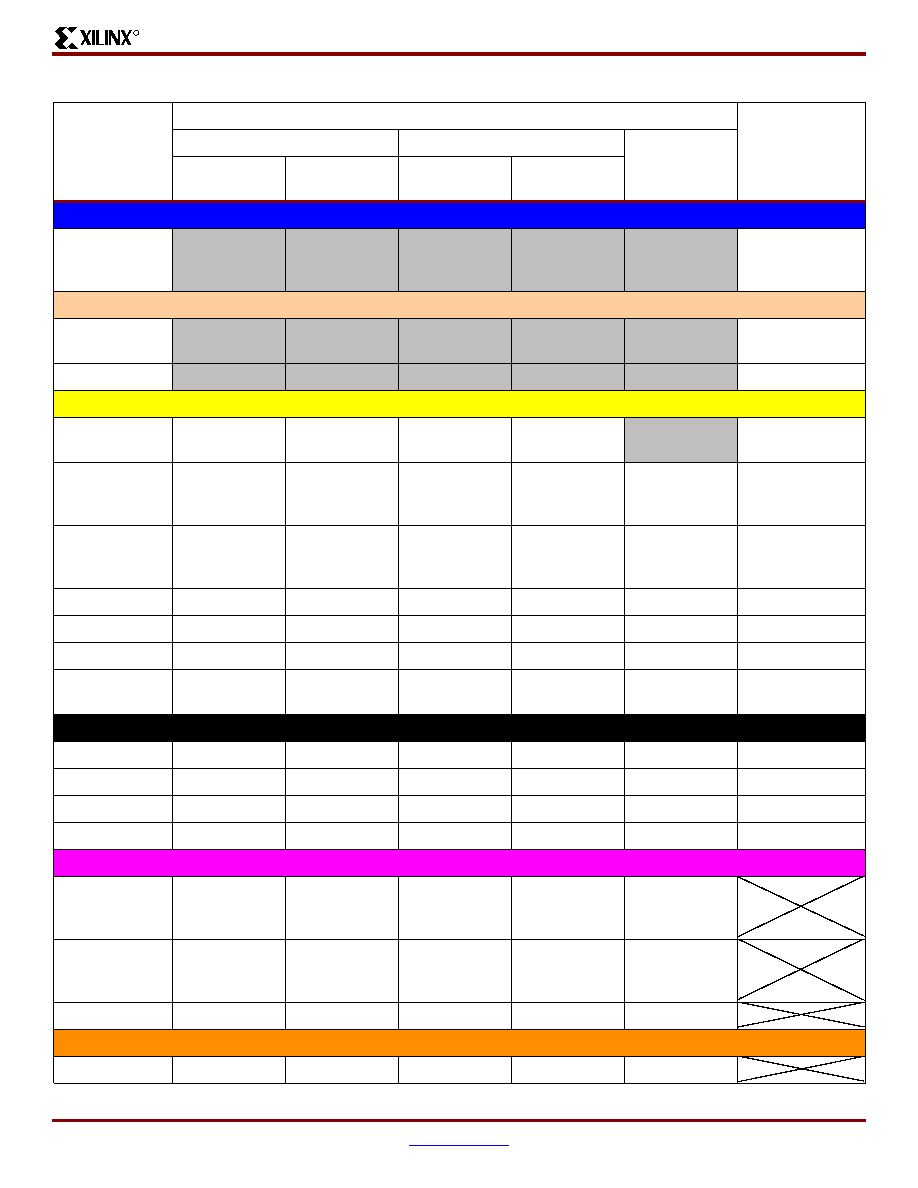

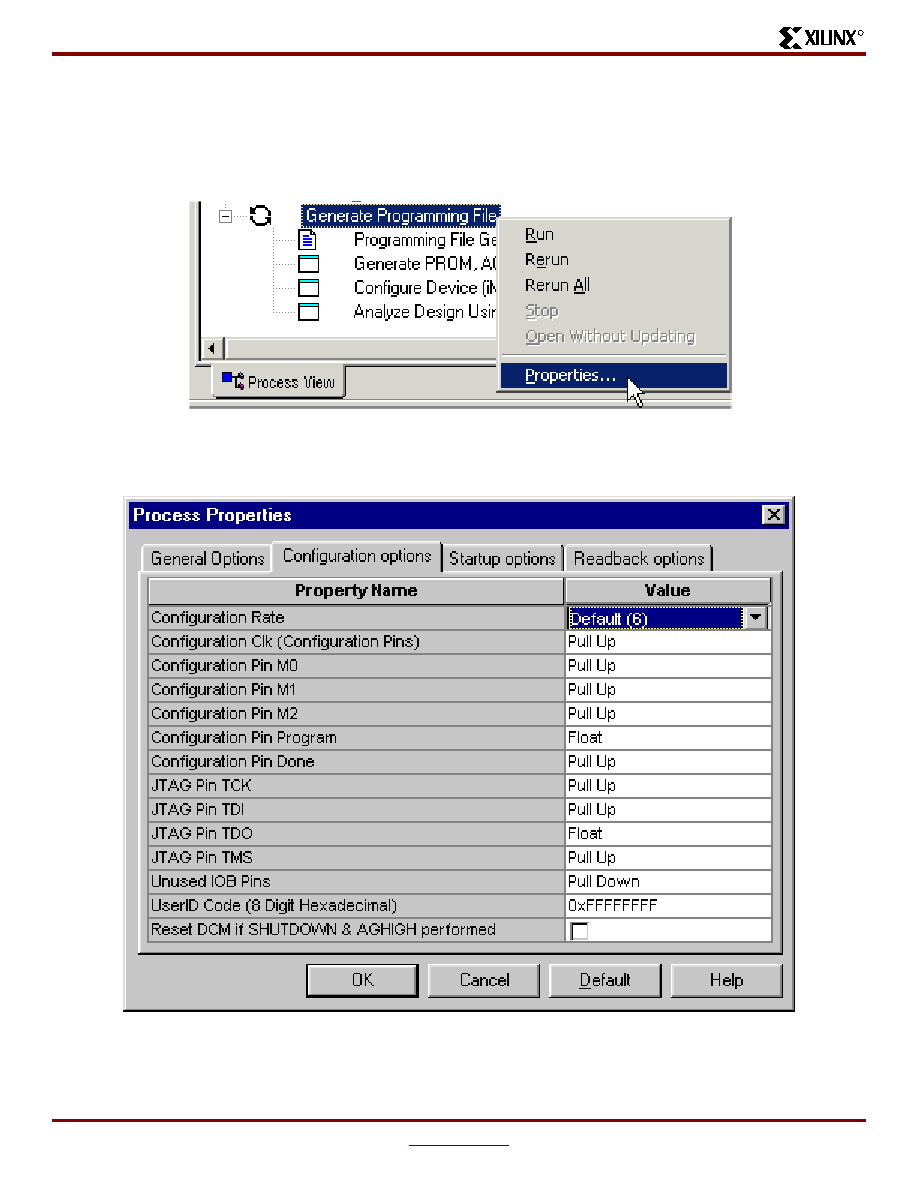

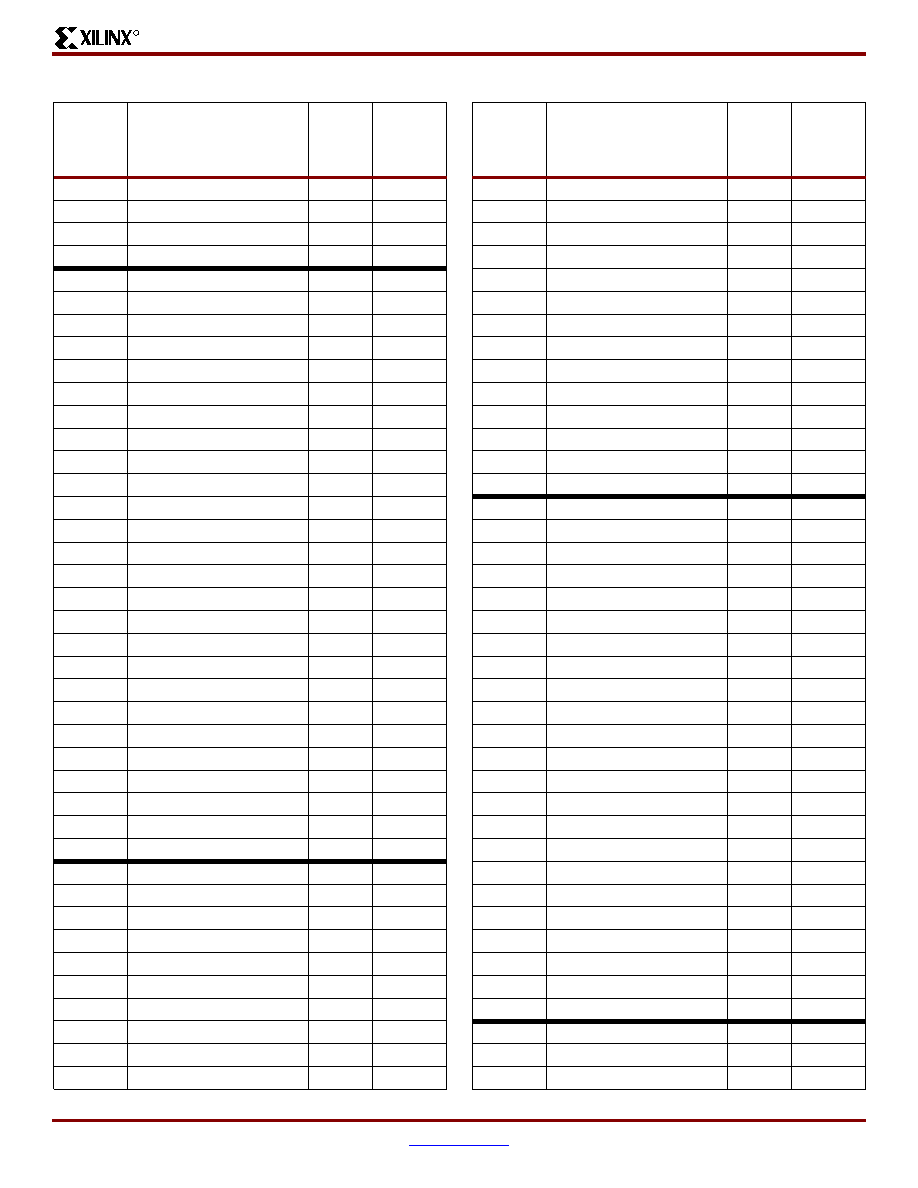

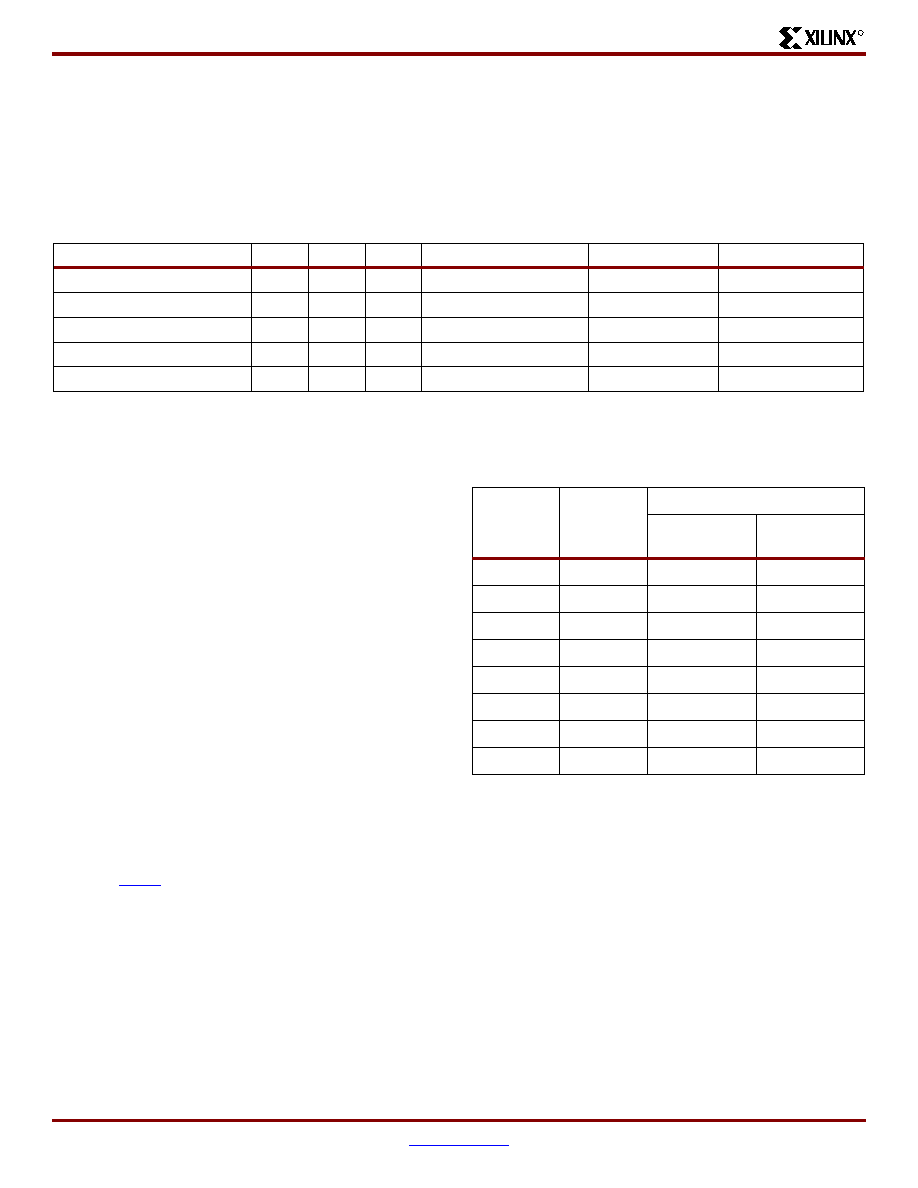

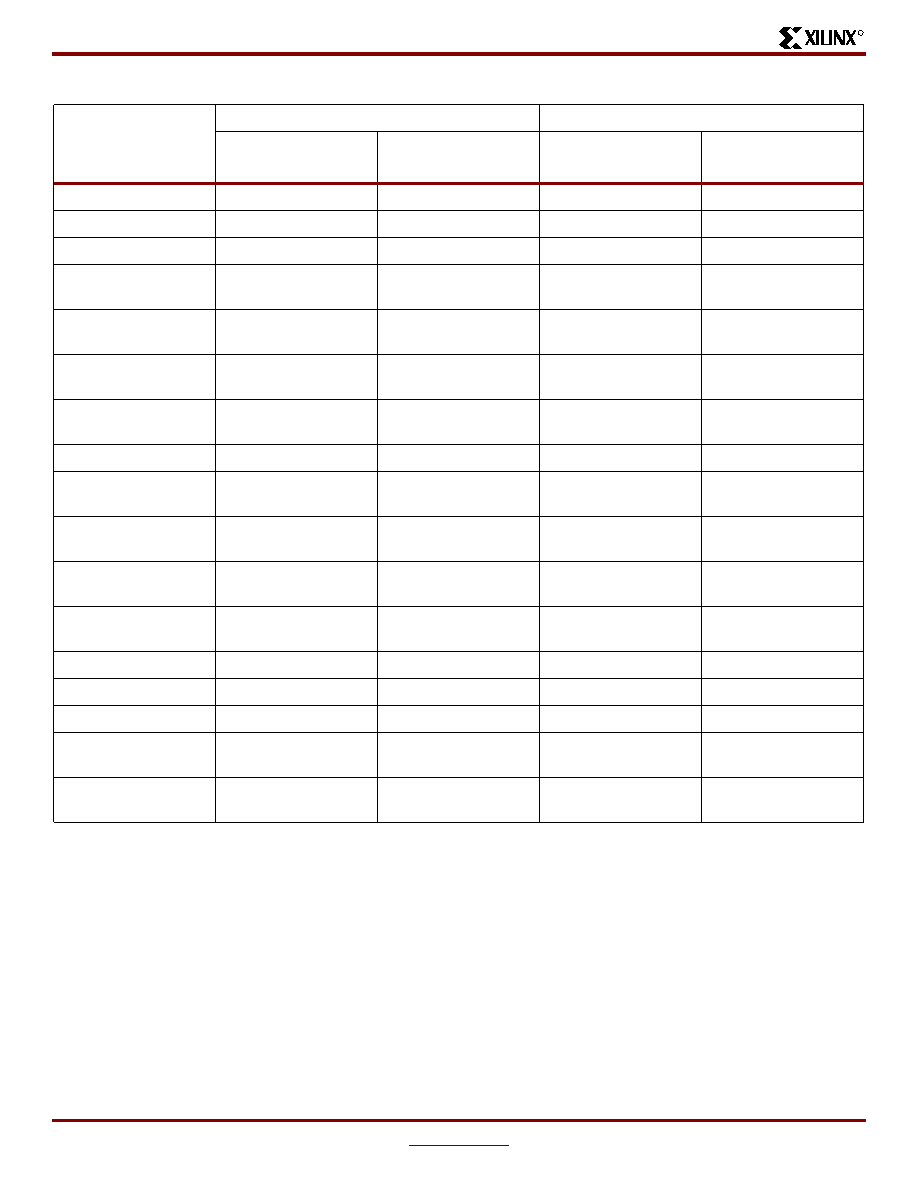

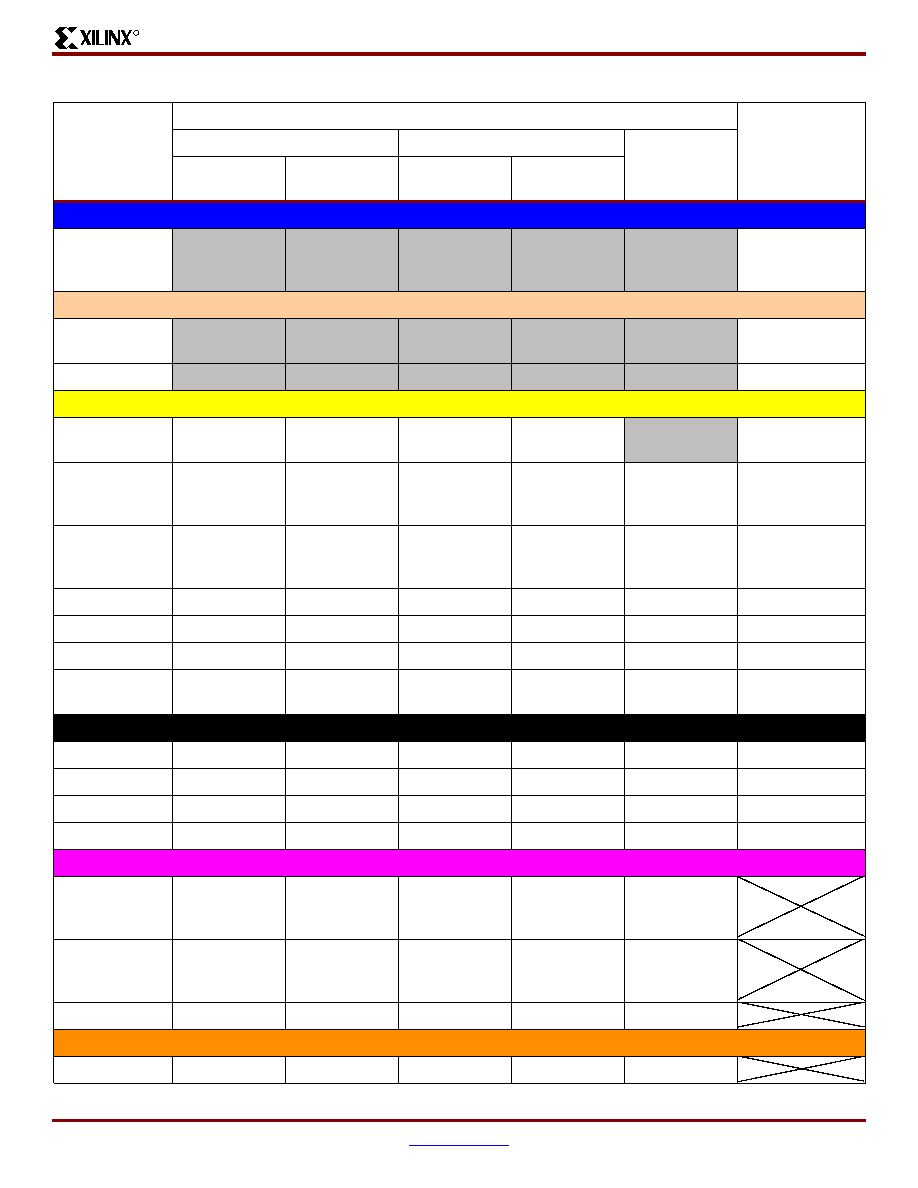

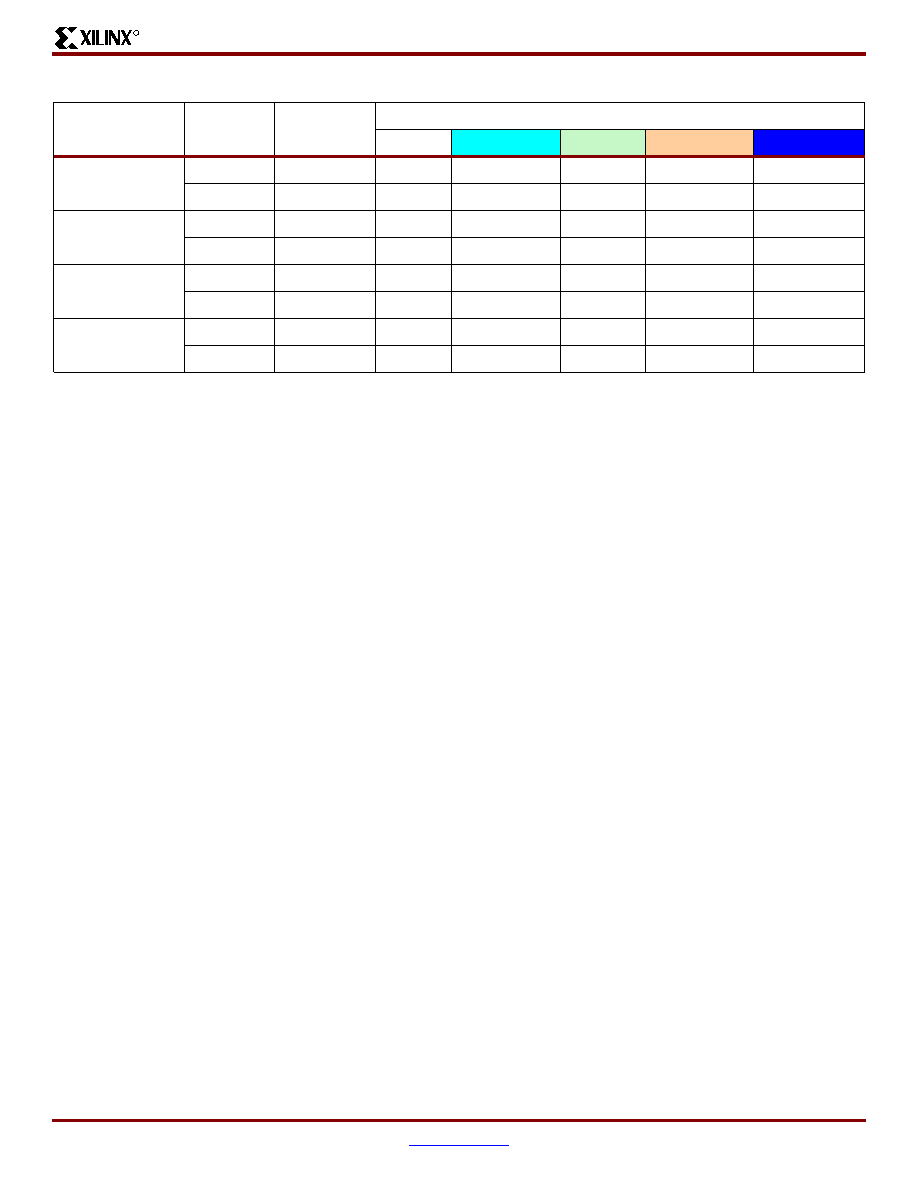

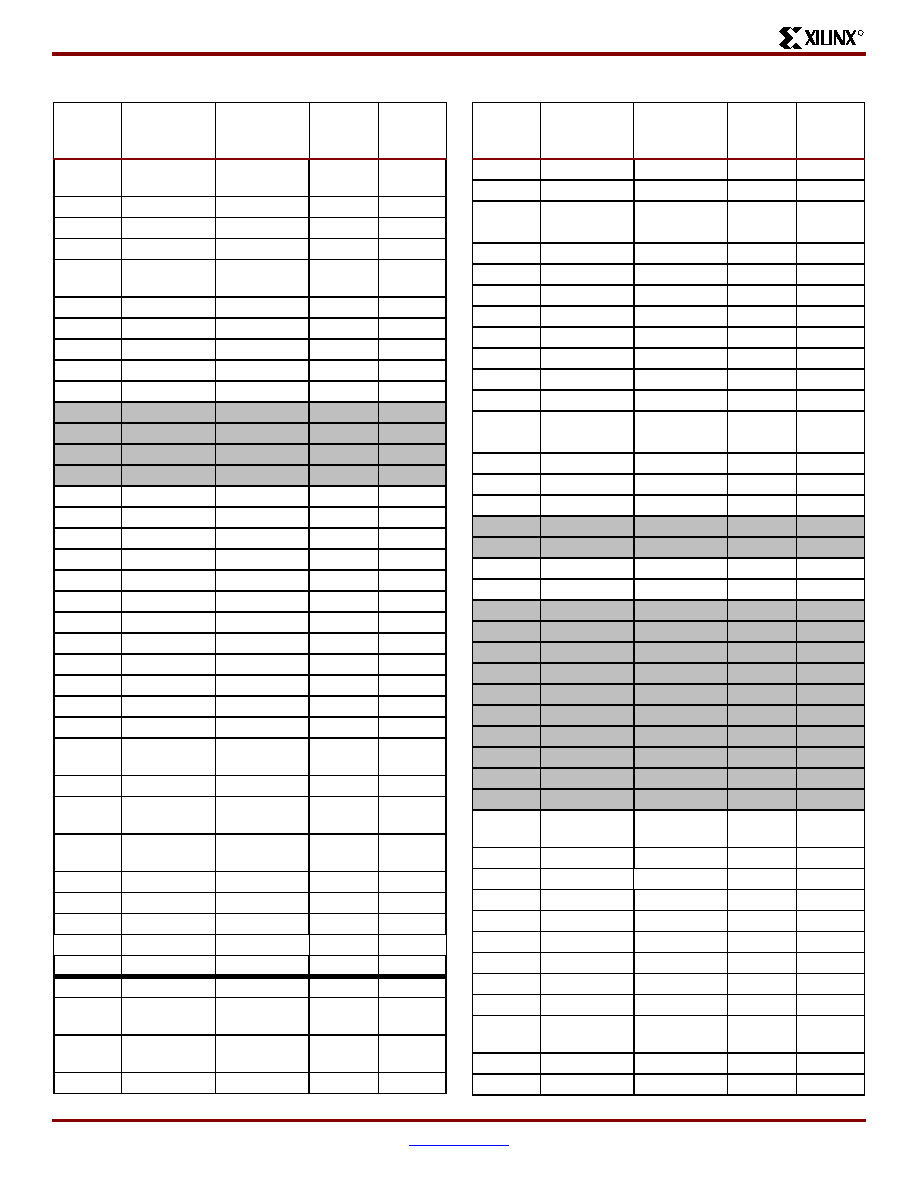

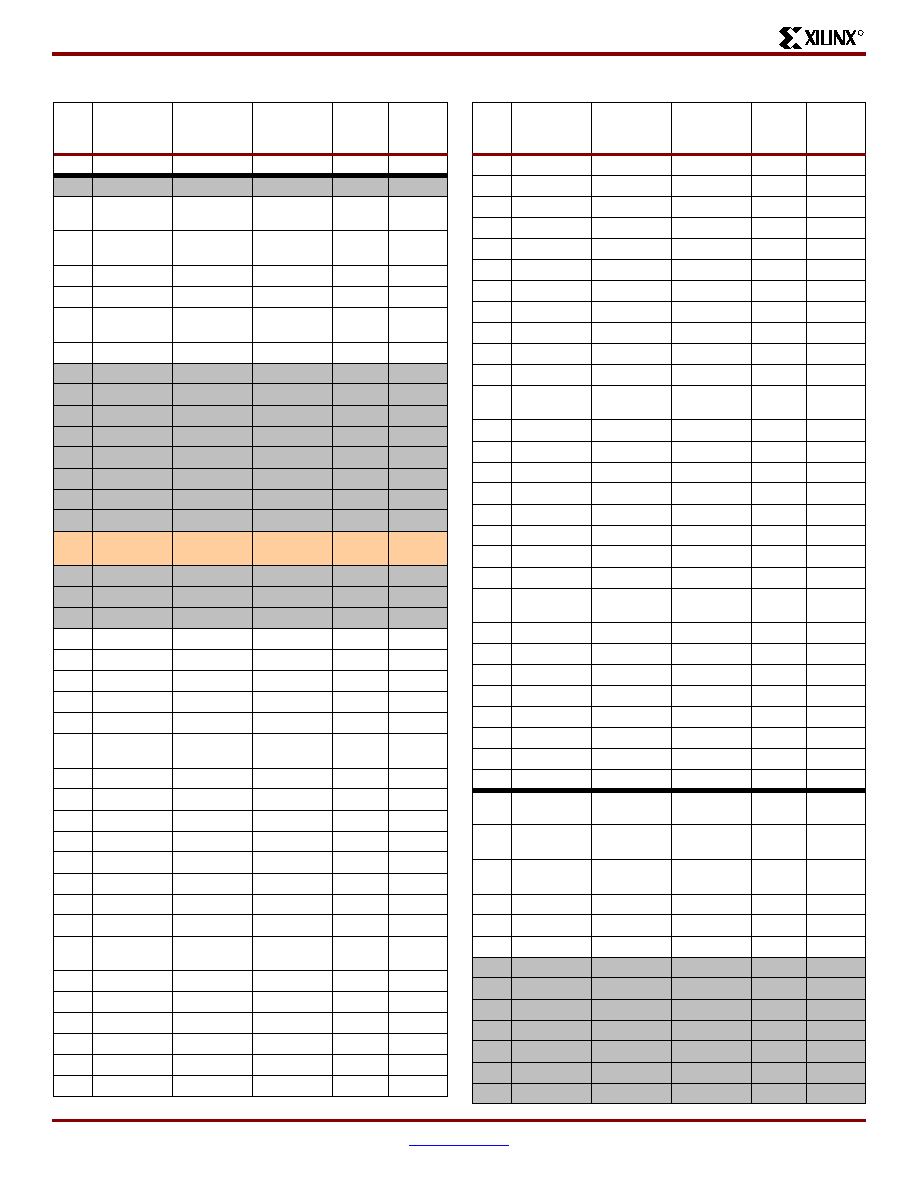

Table 4: Spartan-3 Device Availability

Package Type:

VQFP

TQFP

PQFP

FTBGA

FBGA

No. of Pins:

100

144

208

256

456

676

900

1156

Code:

VQ100

TQ144

PQ208

FT256

FG456

FG676

FG900

FG1156

Device

(1)

XC3S50

(C, I)

(C, I)

(C, I)

-

-

-

-

-

XC3S200

(C, I)

(C, I)

(C, I)

(C, I)

-

-

-

-

XC3S400

-

(C, I)

(C, I)

(C, I)

(C, I)

-

-

-

XC3S1000

-

-

-

(C, I)

(C, I)

(C, I)

-

-

XC3S1500

-

-

-

-

(C, I)

(C, I)

-

-

XC3S2000

-

-

-

-

-

(C, I)

(C, I)

-

XC3S4000

-

-

-

-

-

-

(C, I)

(C, I)

XC3S5000

-

-

-

-

-

-

(C, I)

(C, I)

Notes:

1.

Commercial devices are offered in the -4 and -5 speed grades; industrial devices are only in the -4 speed grade.

2.

C = Commercial, T

J

= 0

� to +85� C; I = Industrial, T

J

= �40

� C to +100� C.

3.

Parentheses indicate that a given device is not yet released to production. Contact your local sales office for availability information.

Spartan-3 1.2V FPGA Family: Introduction and Ordering Information

DS099-1 (v1.1) April 24, 2003

www.xilinx.com

5

Advance Product Specification

1-800-255-7778

R

Ordering Information

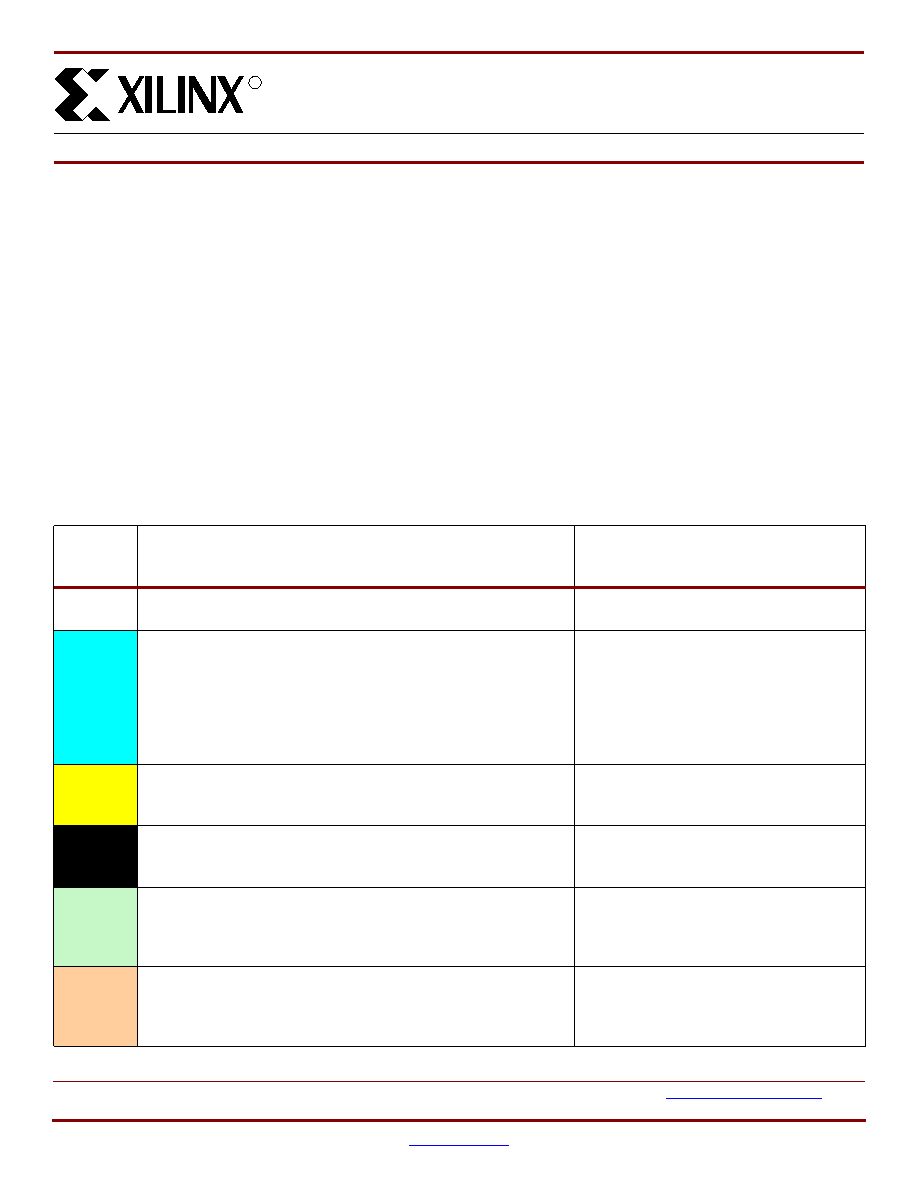

Revision History

The Spartan-3 Family Data Sheet

DS099-1, Spartan-3 1.2V FPGA Family: Introduction and Ordering Information (Module 1)

DS099-2, Spartan-3 1.2V FPGA Family:

Functional Description

(Module 2)

DS099-3, Spartan-3 1.2V FPGA Family:

DC and Switching Characteristics

(Module 3)

DS099-4, Spartan-3 1.2V FPGA Family:

Pinout Descriptions

(Module 4)

Date

Version No.

Description

04/11/03

1.0

Initial Xilinx release.

04/24/03

1.1

Updated block RAM, DCM, and multiplier counts for the XC3S50.

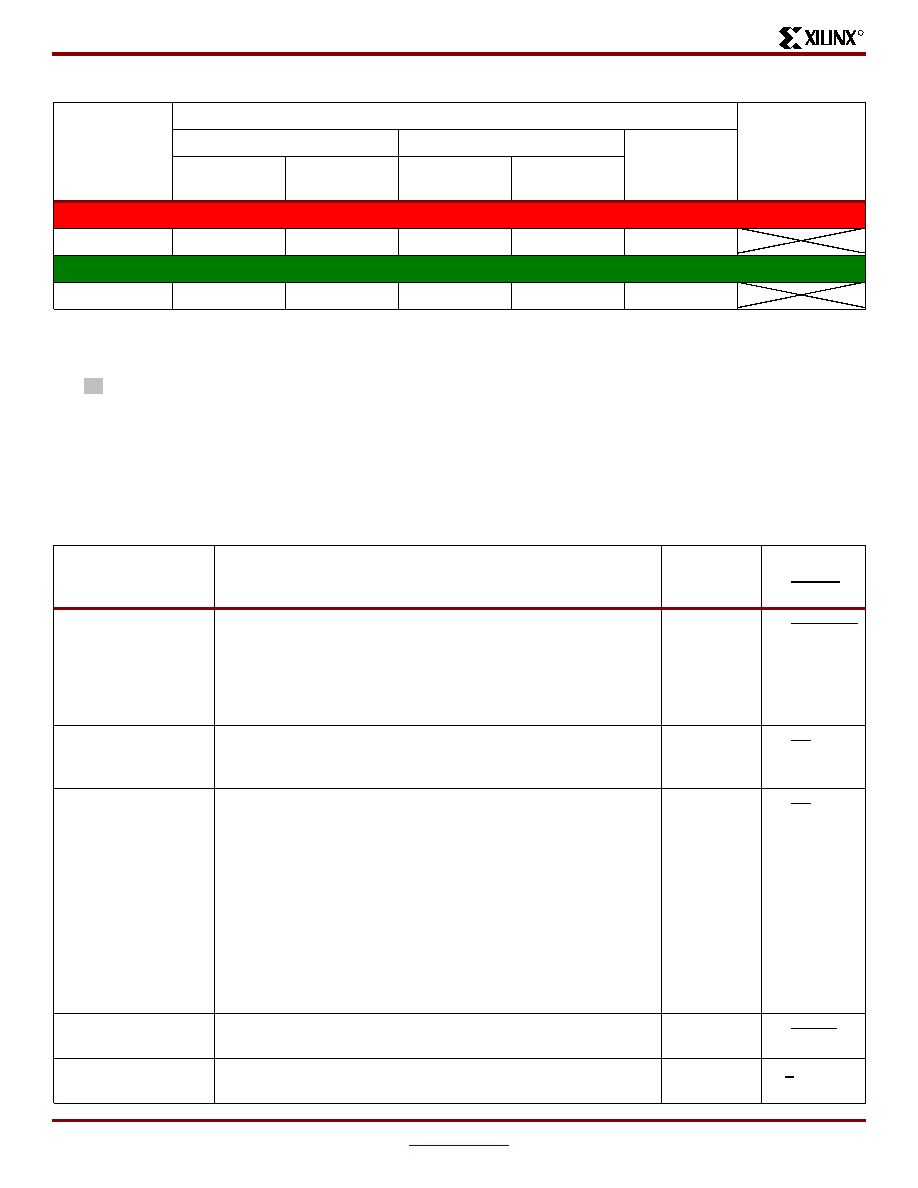

XC3S50 -4 PQ208 C

Example:

Temperature Range

Package Type / Number of Pins

Device Type

Speed Grade

Device

Speed Grade

Package Type / Number of Pins

Temperature Range (T

J

)

XC3S50

-4 Standard Performance

VQ100 100-pin Very Thin Quad Flat Pack (VQFP)

C Commercial (0�C to 85�C)

XC3S200

-5 High Performance

TQ144 144-pin Thin Quad Flat Pack (TQFP)

I

Industrial (�40�C to 100�C)

XC3S400

PQ208 208-pin Plastic Quad Flat Pack (PQFP)

XC3S1000

FT256 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA)

XC3S1500

FG456 456-ball Fine-Pitch Ball Grid Array (FBGA)

XC3S2000

FG676 676-ball Fine-Pitch Ball Grid Array (FBGA)

XC3S4000

FG900 900-ball Fine-Pitch Ball Grid Array (FBGA)

XC3S5000

FG1156 1156-ball Fine-Pitch Ball Grid Array (FBGA)

Spartan-3 1.2V FPGA Family: Introduction and Ordering Information

6

www.xilinx.com

DS099-1 (v1.1) April 24, 2003

1-800-255-7778

Advance Product Specification

6

R

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

1

Advance Product Specification

1-800-255-7778

� 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at

http://www.xilinx.com/legal.htm

.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

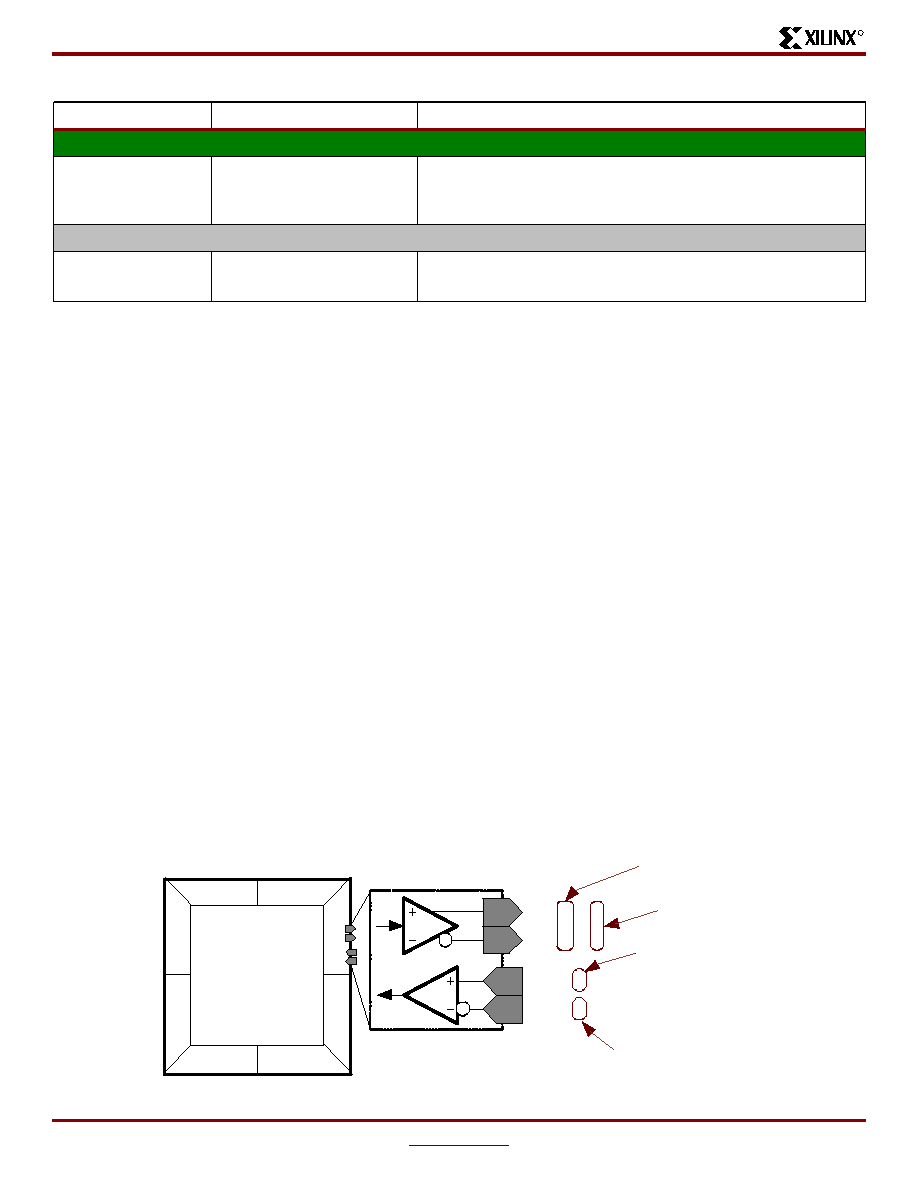

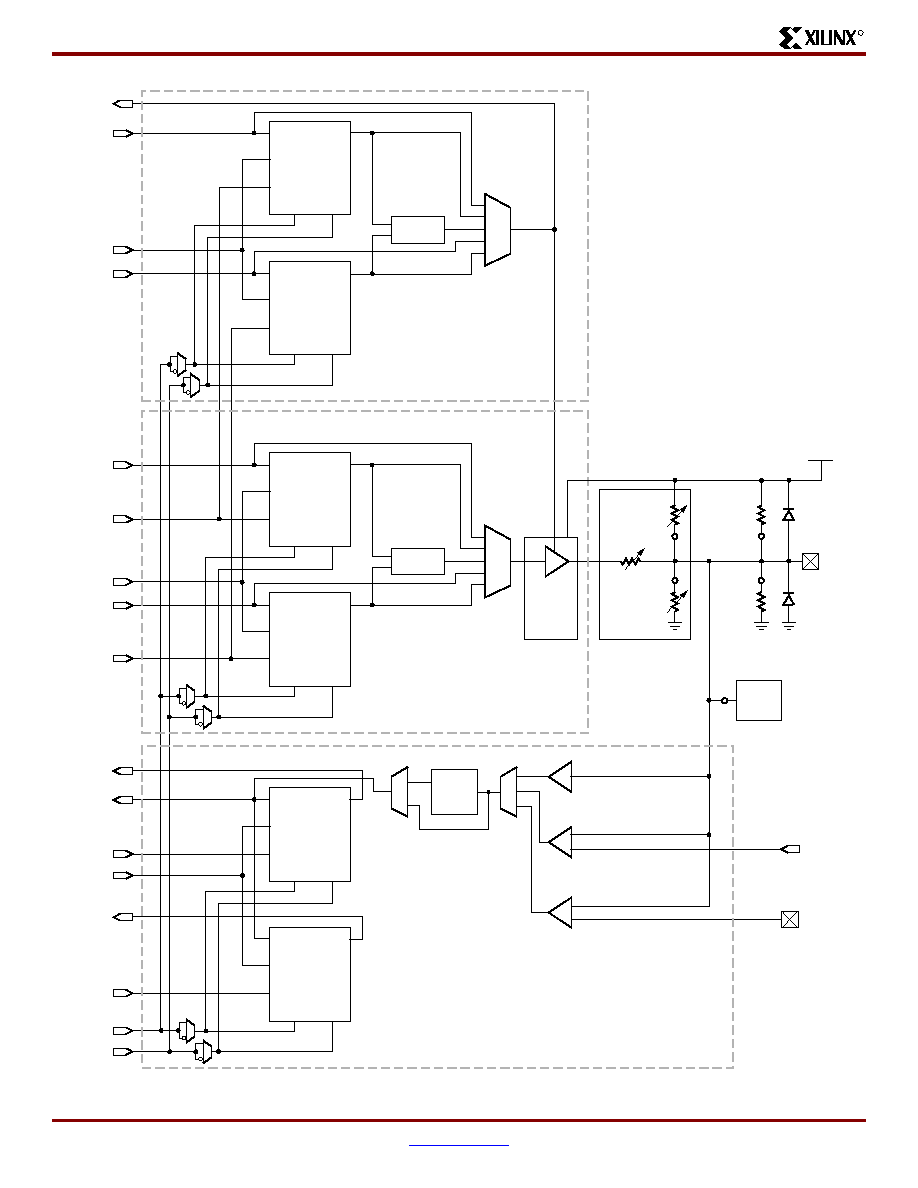

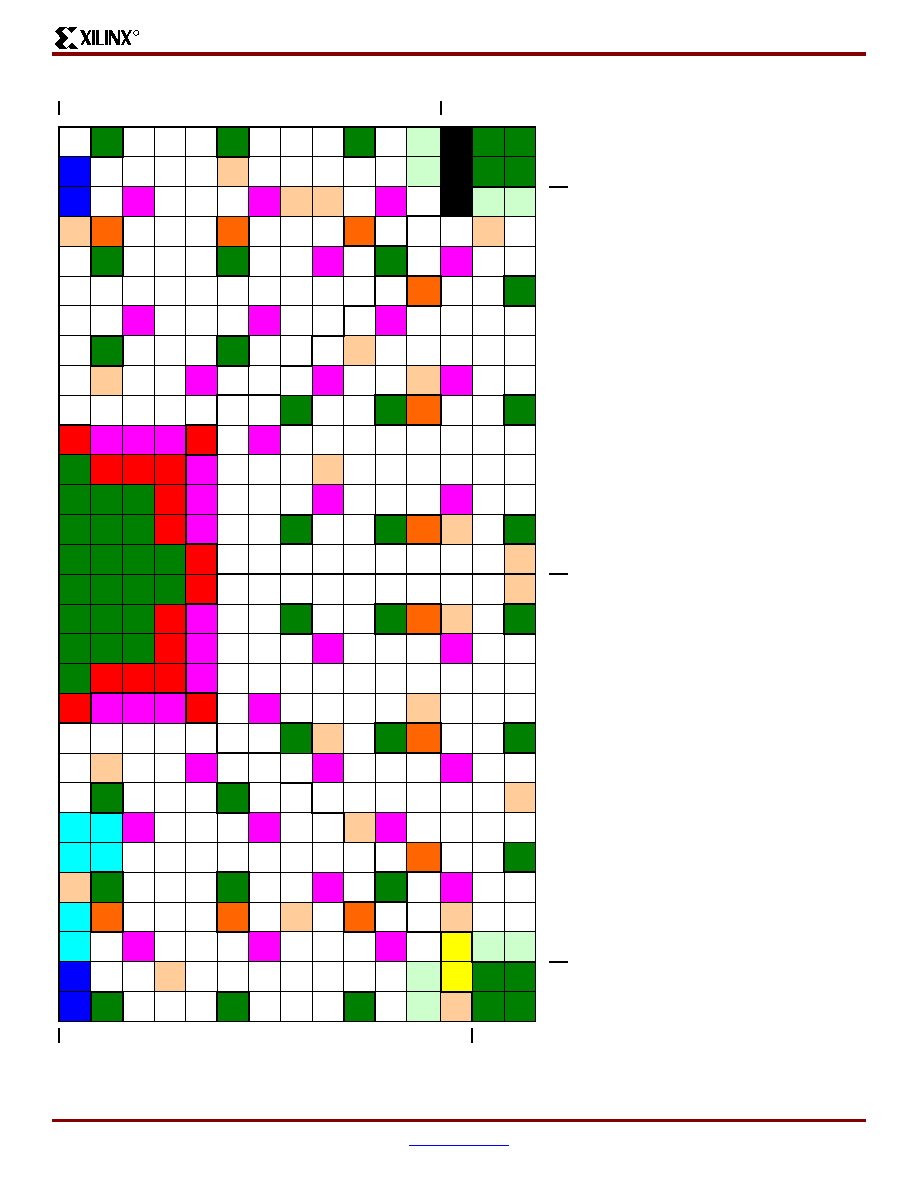

IOBs

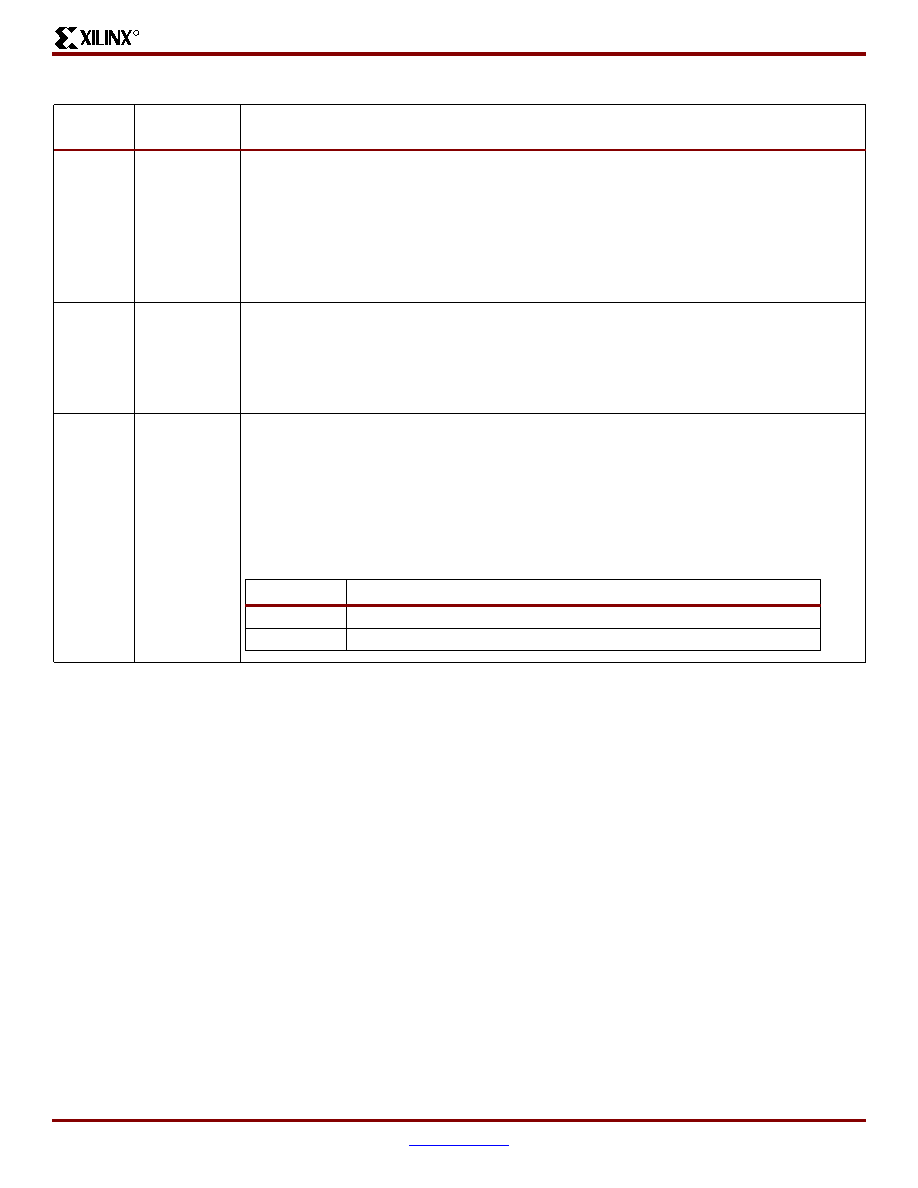

IOB Overview

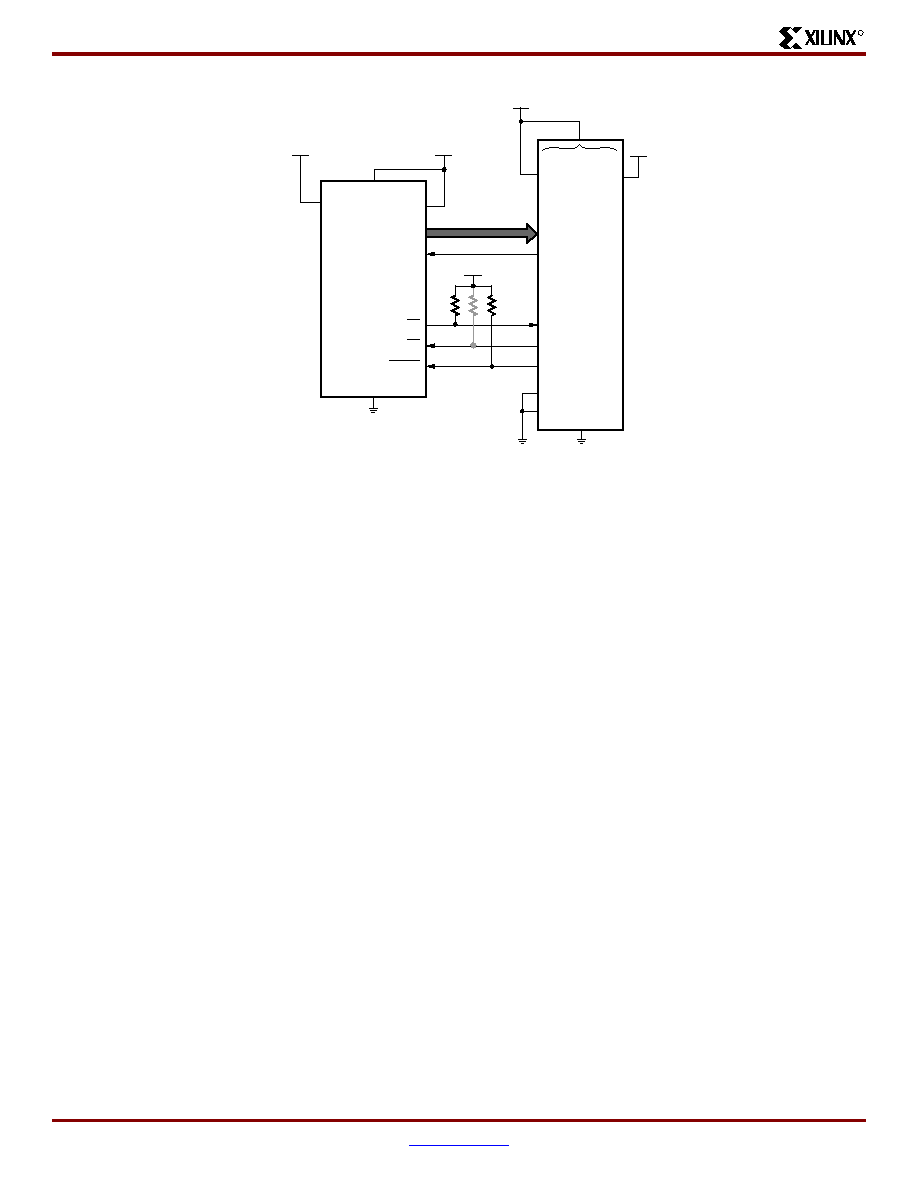

The Input/Output Block (IOB) provides a programmable,

bidirectional interface between an I/O pin and the FPGA's

internal logic.

A simplified diagram of the IOB's internal structure appears

in

Figure 1

. There are three main signal paths within the

IOB: the output path, input path, and 3-state path. Each

path has its own pair of storage elements that can act as

either registers or latches. For more information, see the

Storage Element Functions section. The three main signal

paths are as follows:

�

The input path carries data from the pad, which is

bonded to a package pin, through an optional

programmable delay element directly to the I line. After

the delay element, there are alternate routes through a

pair of storage elements to the IQ1 and IQ2 lines. The

IOB outputs I, IQ1, and IQ2 all lead to the FPGA's

internal logic. The delay element can be set to ensure a

hold time of zero.

�

The output path, starting with the O1 and O2 lines,

carries data from the FPGA's internal logic through a

multiplexer and then a three-state driver to the IOB

pad. In addition to this direct path, the multiplexer

provides the option to insert a pair of storage elements.

�

The 3-state path determines when the output driver is

high impedance. The T1 and T2 lines carry data from

the FPGA's internal logic through a multiplexer to the

output driver. In addition to this direct path, the

multiplexer provides the option to insert a pair of

storage elements.

�

All signal paths entering the IOB, including those

associated with the storage elements, have an inverter

option. Any inverter placed on these paths is

automatically absorbed into the IOB.

Storage Element Functions

There are three pairs of storage elements in each IOB, one

pair for each of the three paths. It is possible to configure

each of these storage elements as an edge-triggered

D-type flip-flop (FD) or a level-sensitive latch (LD).

The storage-element-pair on either the Output path or the

Three-State path can be used together with a special multi-

plexer to produce Double-Data-Rate (DDR) transmission.

This is accomplished by taking data synchronized to the

clock signal's rising edge and converting them to bits syn-

chronized on both the rising and the falling edge. The com-

bination of two registers and a multiplexer is referred to as a

Double-Data-Rate D-type flip-flop (FDDR).

See

Double-Data-Rate Transmission, page 3

for more

information.

The signal paths associated with the storage element are

described in

Table 1

.

040

Spartan-3 1.2V FPGA Family:

Functional Description

DS099-2 (v1.2) July 11, 2003

0

0

Advance Product Specification

R

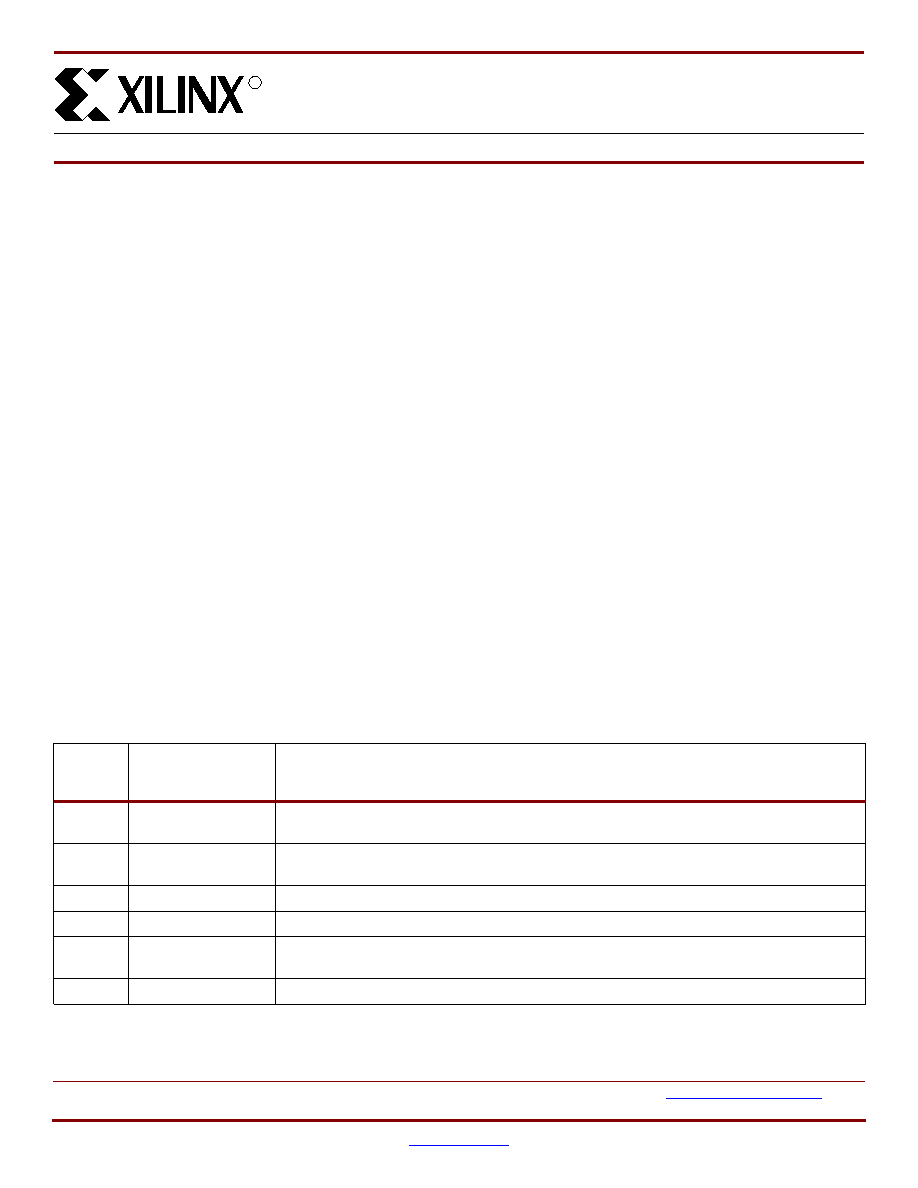

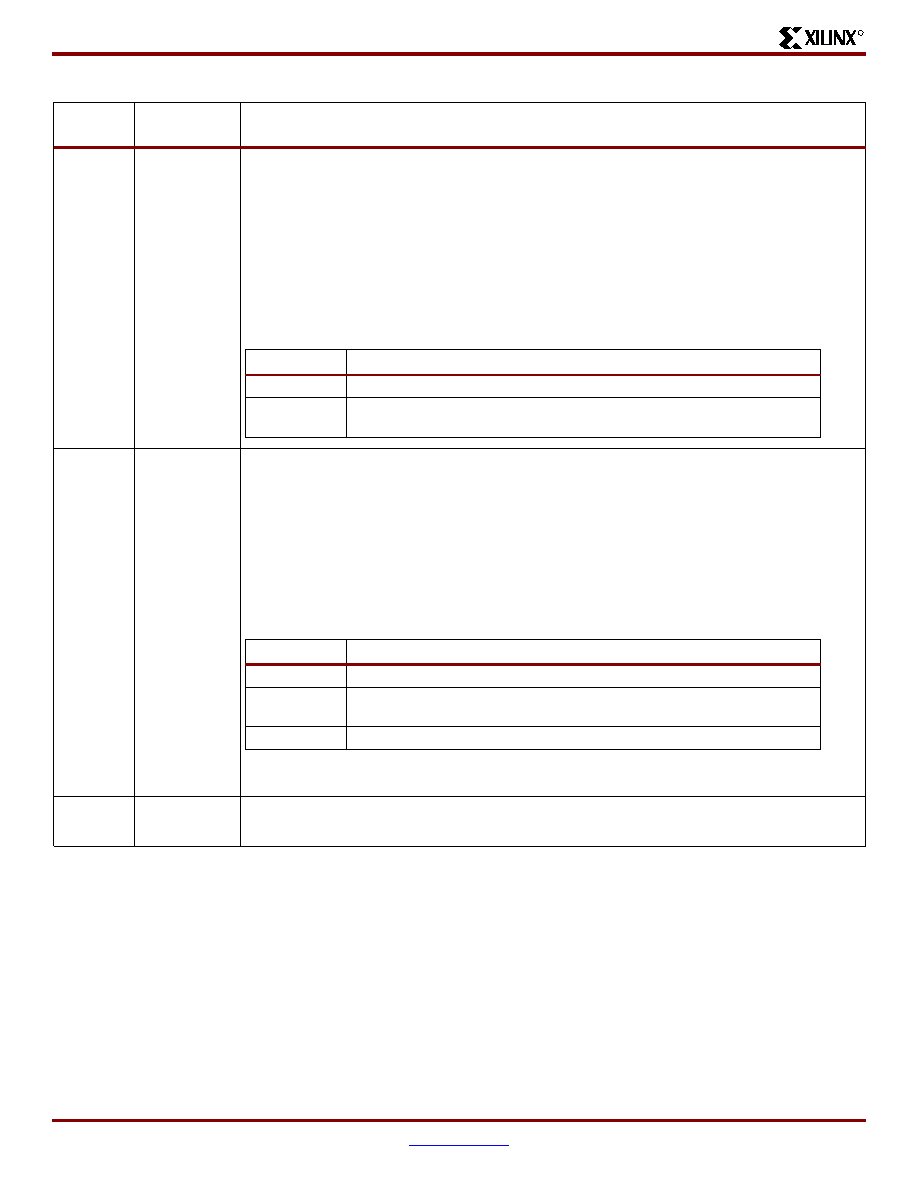

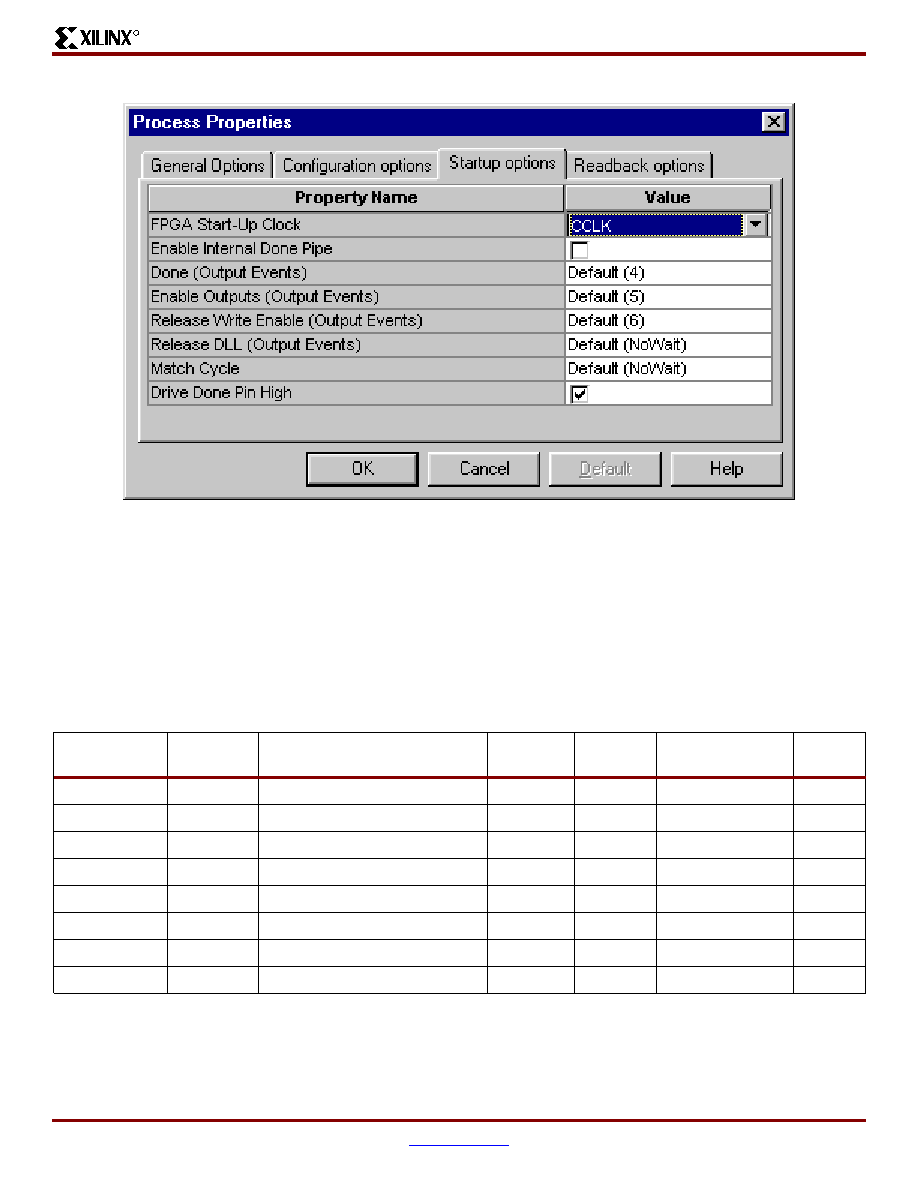

Table 1: Storage Element Signal Description

Storage

Element

Signal

Description

Function

D

Data input

Data at this input is stored on the active edge of CK enabled by CE. For latch operation when the

input is enabled, data passes directly to the output Q.

Q

Data output

The data on this output reflects the state of the storage element. For operation as a latch in

transparent mode, Q will mirror the data at D.

CK

Clock input

A signal's active edge on this input with CE asserted, loads data into the storage element.

CE

Clock Enable input

When asserted, this input enables CK. If not connected, CE defaults to the asserted state.

SR

Set/Reset

Forces storage element into the state specified by the SRHIGH/SRLOW attributes. The

SYNC/ASYNC attribute setting determines if the SR input is synchronized to the clock or not.

REV

Reverse

Used together with SR. Forces storage element into the state opposite from what SR does.

Spartan-3 1.2V FPGA Family: Functional Description

2

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

Figure 1: Simplified IOB Diagram

D

CE

CK

TFF1

Three-state Path

T

T1

TCE

T2

TFF2

Q

SR

DDR

MUX

REV

D

CE

CK

Q

SR

REV

D

CE

CK

OFF1

Output Path

O1

OCE

O2

OFF2

Q

SR

DDR

MUX

Weak

Keeper

Latch

V

CCO

V

REF

Pin

I/O Pin

from

Adjacent

IOB

DS099_01_040703

I/O

Pin

Program-

mable

Output

Driver

DCI

ESD

Weak

Pull-Up

Weak

Pull-

Down

ESD

REV

D

CE

CK

Q

SR

REV

OTCLK1

OTCLK2

D

CE

CK

IFF1

Input Path

I

ICE

IFF2

Q

SR

Fixed

Delay

LVCMOS, LVTTL, PCI

Single-ended Standards

using VREF

Differential Standards

REV

D

CE

CK

Q

SR

REV

ICLK1

ICLK2

SR

REV

Note: All IOB signals communicating with the FPGA's internal logic have the option of inverting polarity.

IQ1

IQ2

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

3

Advance Product Specification

1-800-255-7778

R

According to

Figure 1

, the clock line OTCLK1 connects the

CK inputs of the upper registers on the output and

three-state paths. Similarly, OTCLK2 connects the CK

inputs for the lower registers on the output and three-state

paths. The upper and lower registers on the input path have

independent clock lines: ICLK1 and ICLK2.

The enable line OCE connects the CE inputs of the upper

and lower registers on the output path. Similarly, TCE con-

nects the CE inputs for the register pair on the three-state

path and ICE does the same for the register pair on the

input path.

The Set/Reset (SR) line entering the IOB is common to all

six registers, as is the Reverse (REV) line.

Each storage element supports numerous options in addi-

tion to the control over signal polarity described in the IOB

Overview section. These are described in

Table 2

.

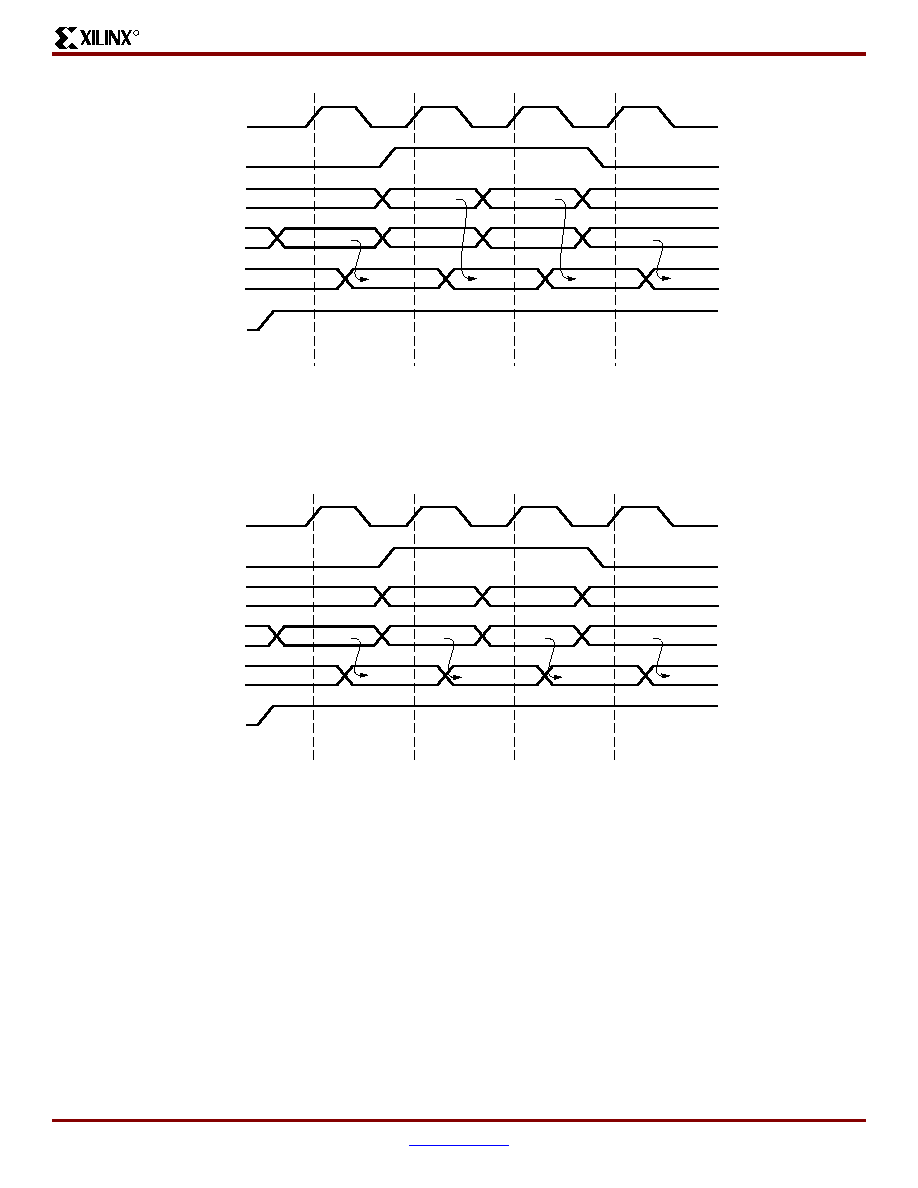

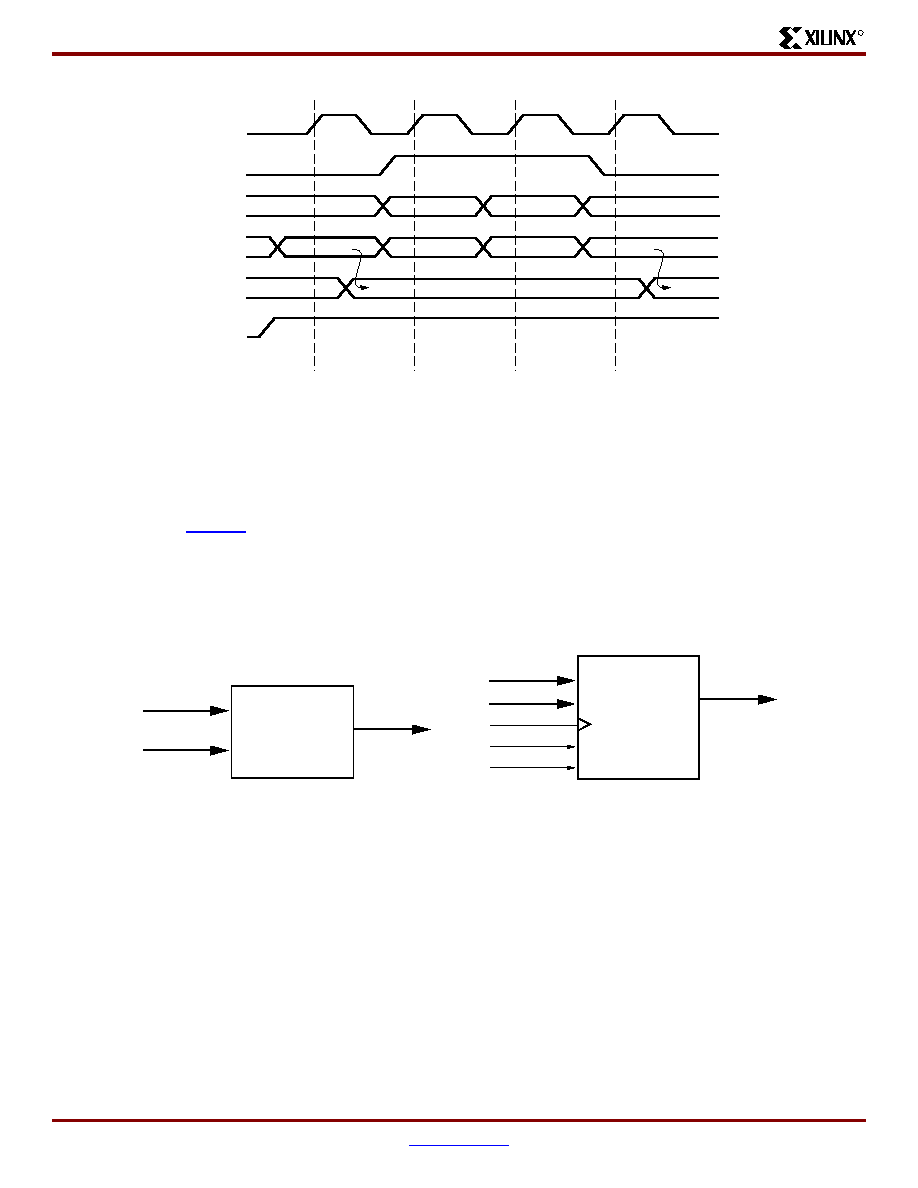

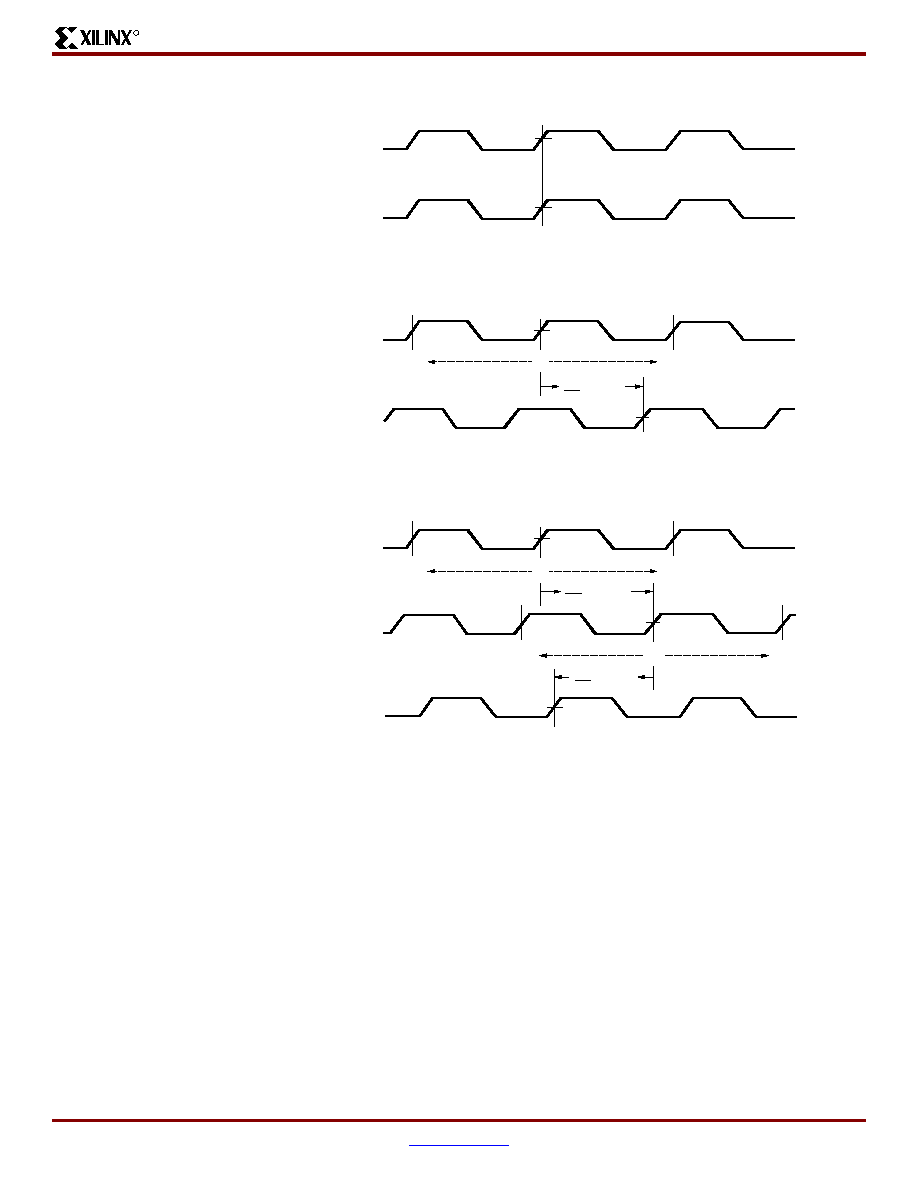

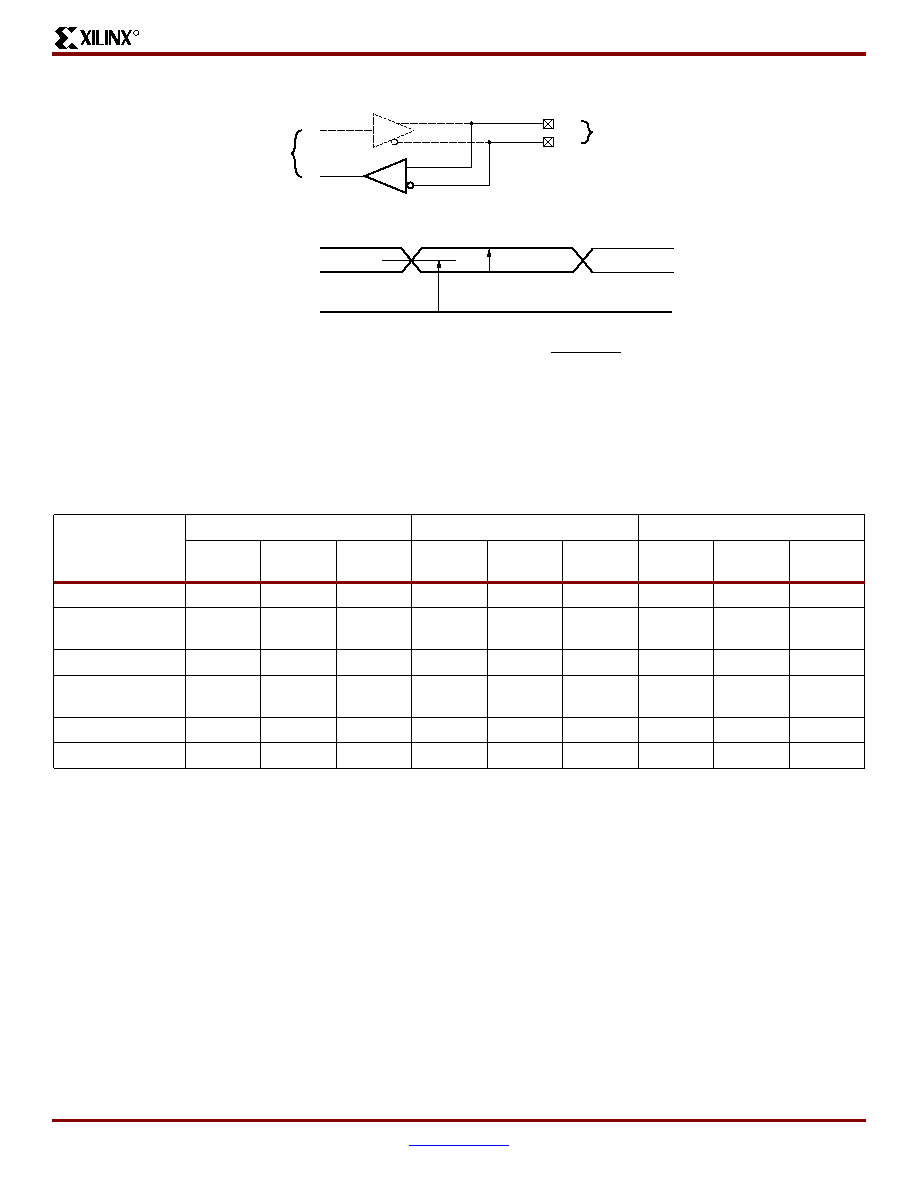

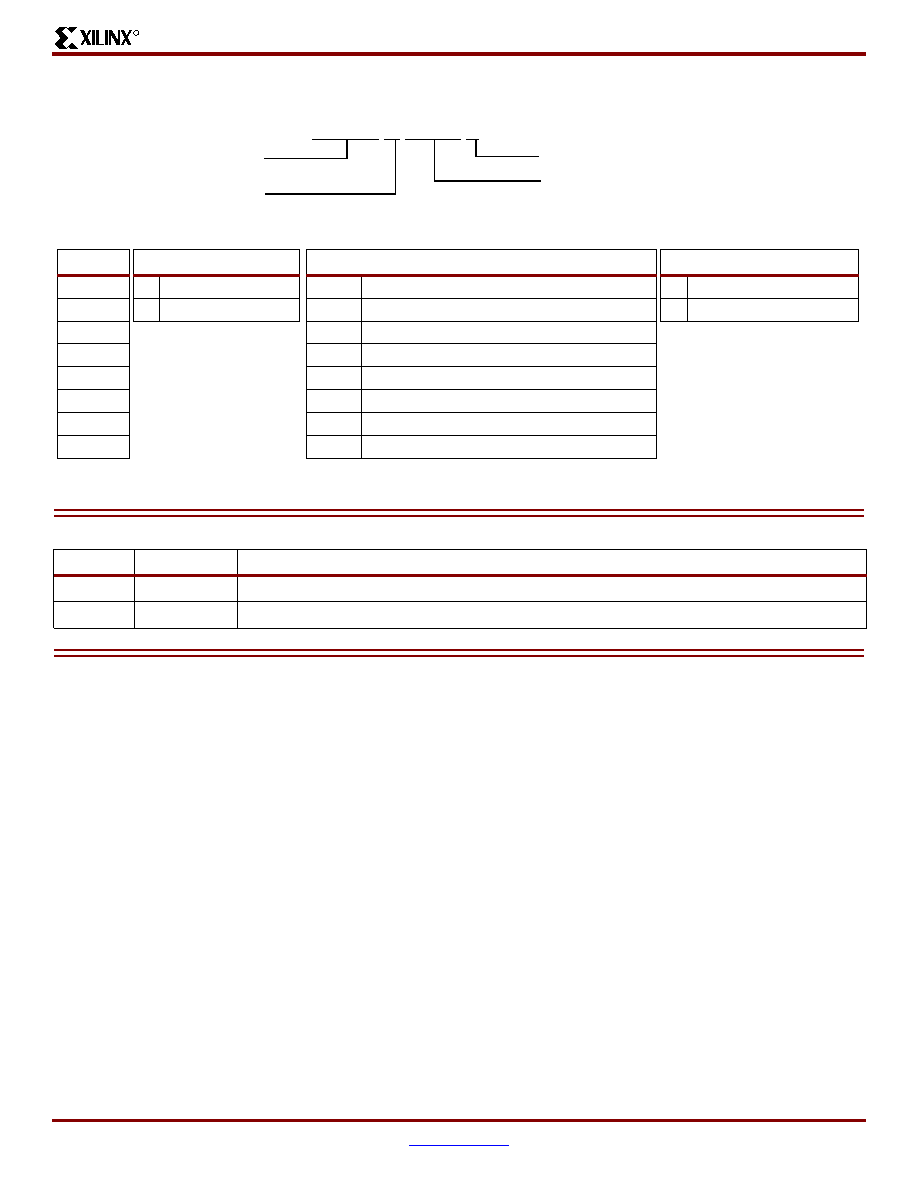

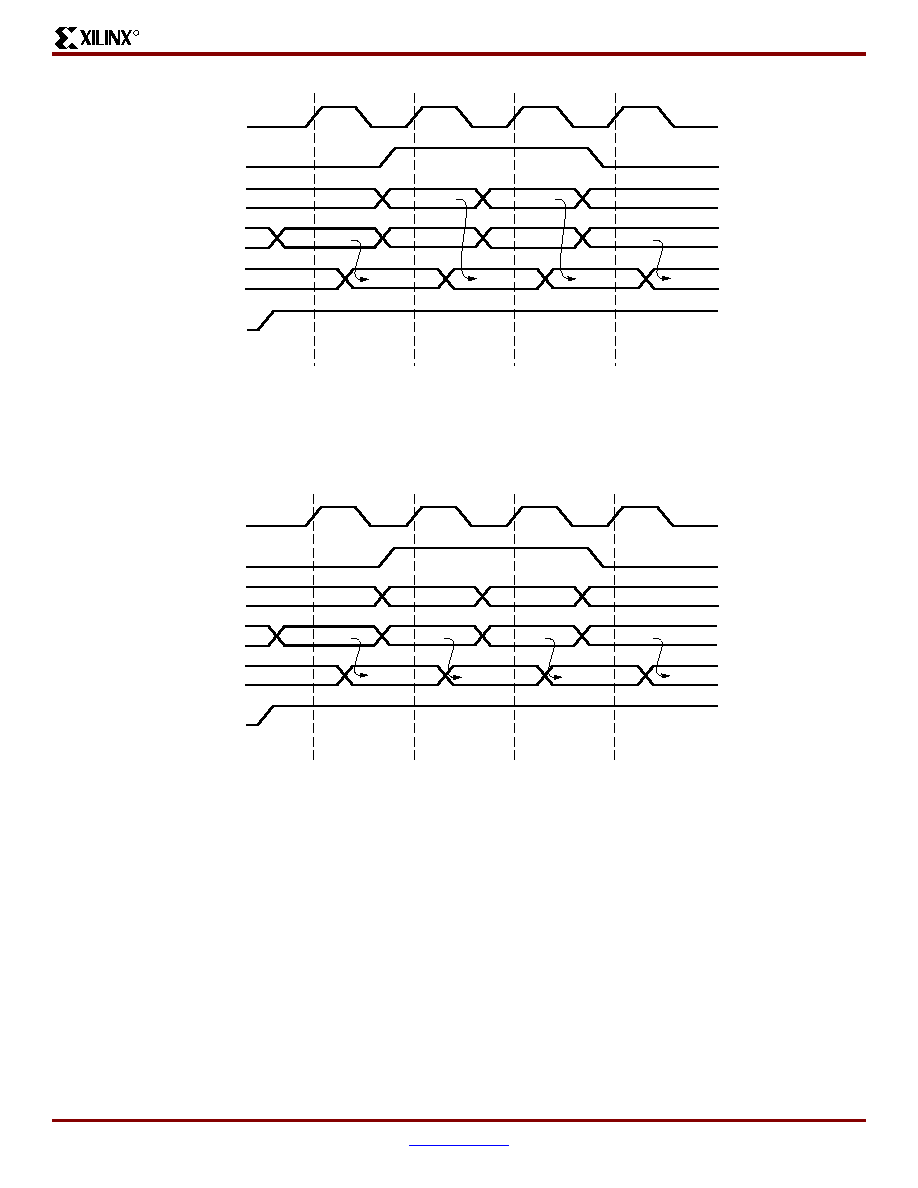

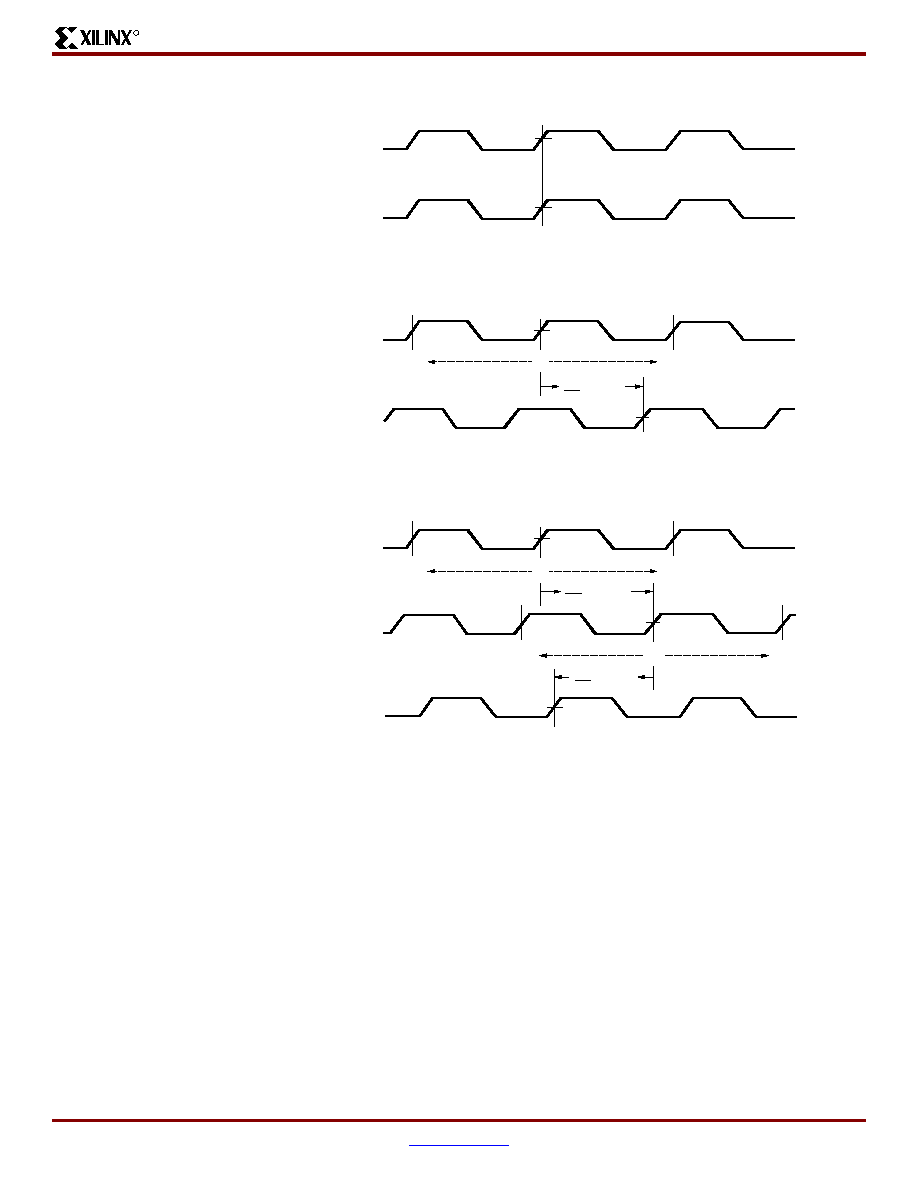

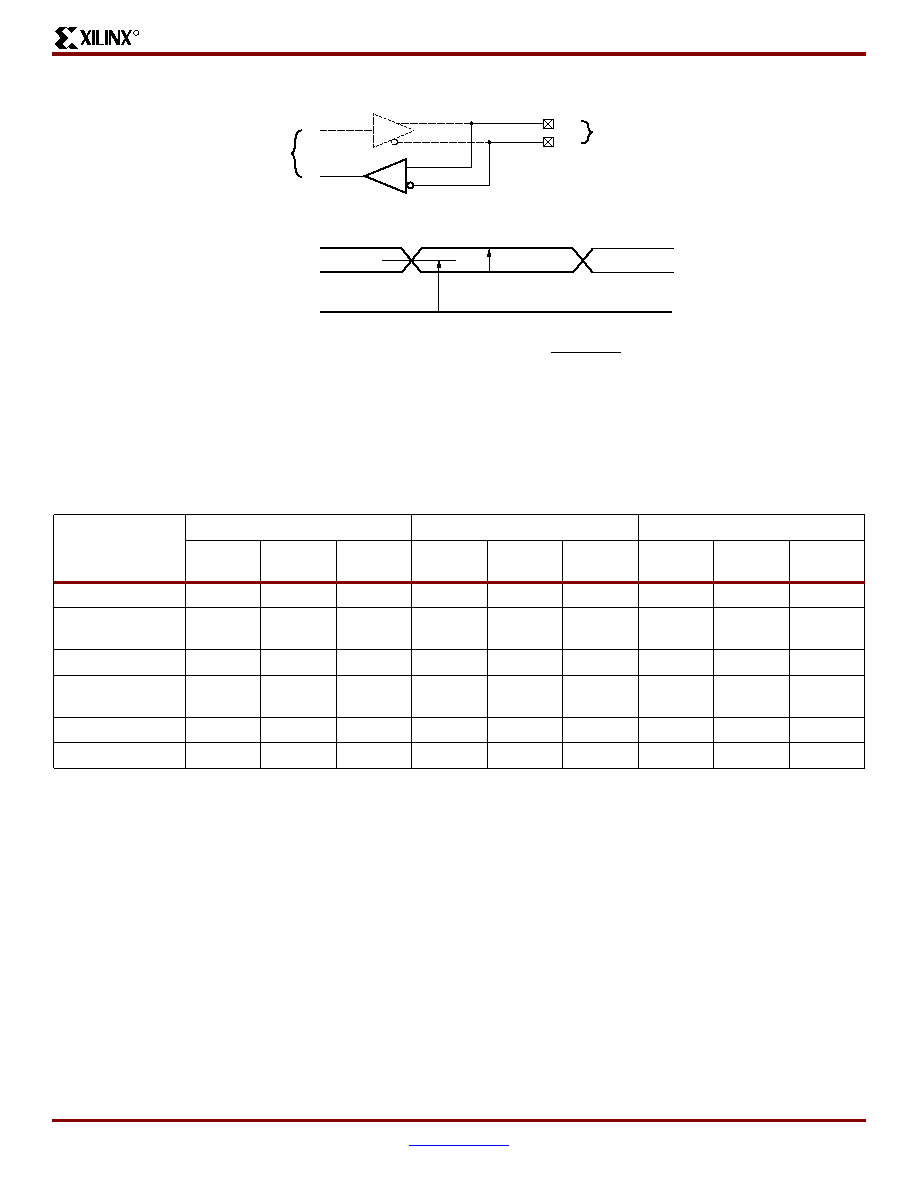

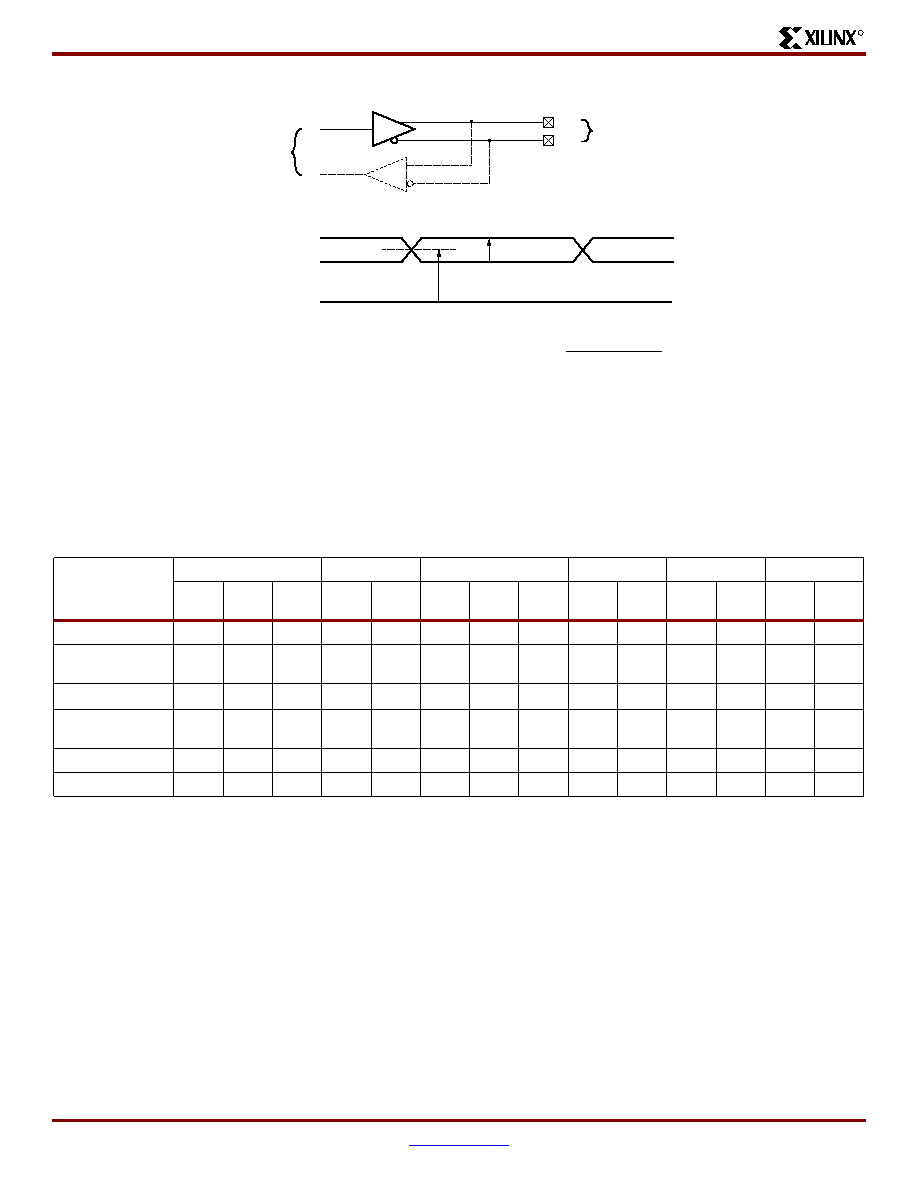

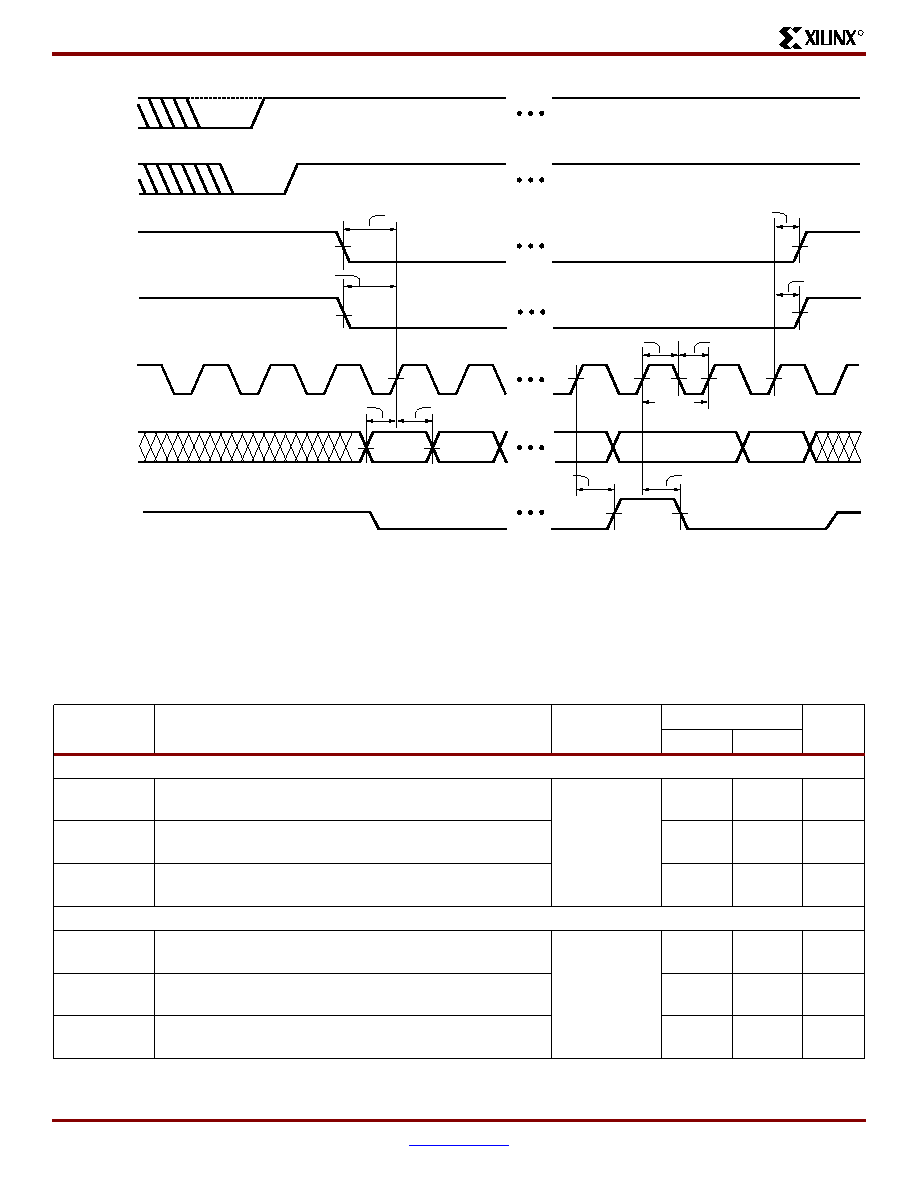

Double-Data-Rate Transmission

Double-Data-Rate (DDR) transmission describes the tech-

nique of synchronizing signals to both the rising and falling

edges of the clock signal. Spartan-3 devices use regis-

ter-pairs in all three IOB paths to perform DDR operations.

The pair of storage elements on the IOB's Output path

(OFF1 and OFF2), used as registers, combine with a spe-

cial multiplexer to form a DDR D-type flip-flop (FDDR). This

primitive permits DDR transmission where output data bits

are synchronized to both the rising and falling edges of a

clock. It is possible to access this function by placing either

an FDDRRSE or an FDDRCPE component or symbol into

the design. DDR operation requires two clock signals (50%

duty cycle), one the inverted form of the other. These sig-

nals trigger the two registers in alternating fashion, as

shown in

Figure 2

. Commonly, the Digital Clock Manager

(DCM) generates the two clock signals by mirroring an

incoming signal, then shifting it 180 degrees. This approach

ensures minimal skew between the two signals.

The storage-element-pair on the Three-State path (TFF1

and TFF2) can also be combined with a local multiplexer to

form an FDDR primitive. This permits synchronizing the out-

put enable to both the rising and falling edges of a clock.

This DDR operation is realized in the same way as for the

output path.

The storage-element-pair on the input path (IFF1 and IFF2)

allows an I/O to receive a DDR signal. An incoming DDR

clock signal triggers one register and the inverted clock sig-

nal triggers the other register. In this way, the registers take

turns capturing bits of the incoming DDR data signal.

Aside from high bandwidth data transfers, DDR can also be

used to reproduce, or "mirror", a clock signal on the output.

This approach is used to transmit clock and data signals

together. A similar approach is used to reproduce a clock

signal at multiple outputs. The advantage for both

approaches is that skew across the outputs will be minimal.

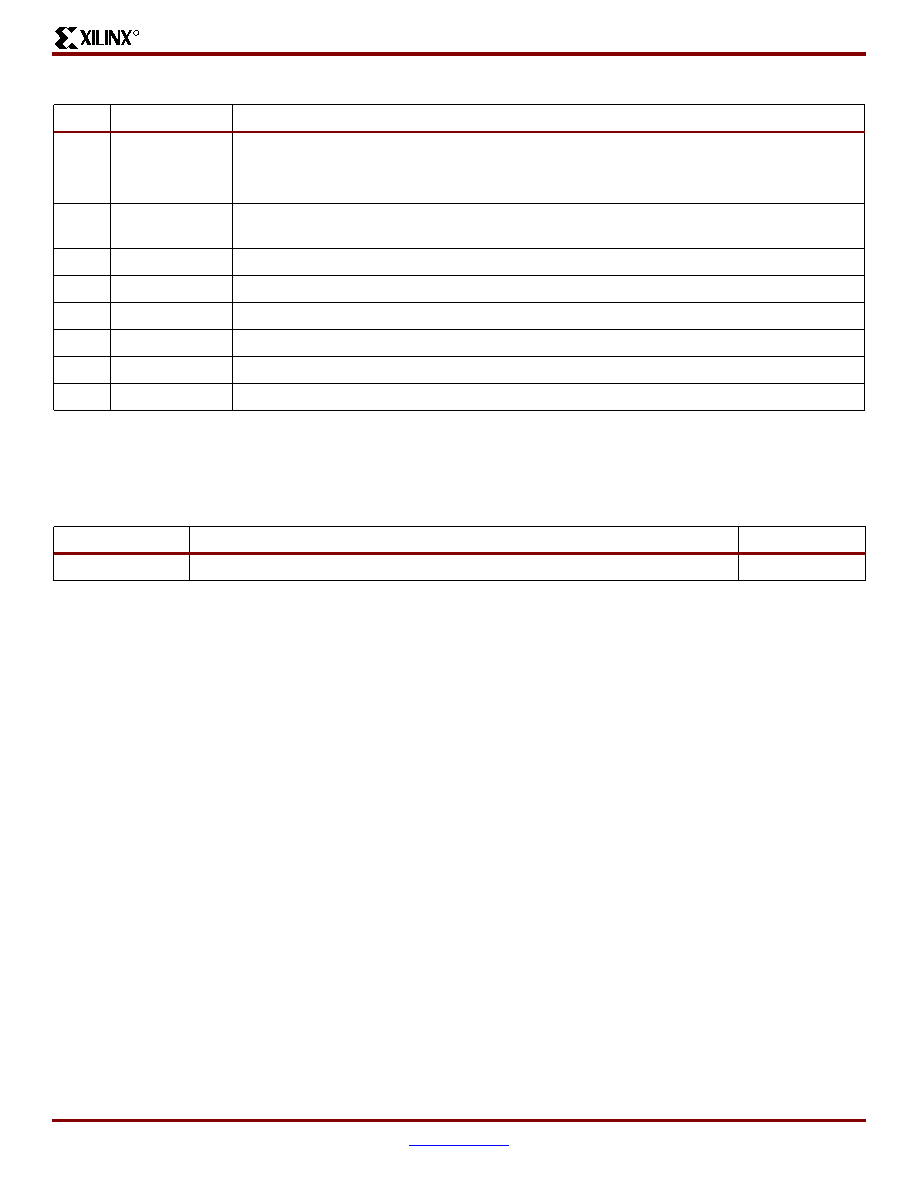

Table 2: Storage Element Options

Option Switch

Function

Specificity

FF/Latch

Chooses between an edge-sensitive flip-flop or

a level-sensitive latch

Independent for each storage element.

SYNC/ASYNC

Determines whether SR is synchronous or

asynchronous

Independent for each storage element.

SRHIGH/SRLOW

Determines whether SR acts as a Set, which

forces the storage element to a logic "1"

(SRHIGH) or a Reset, which forces a logic "0"

(SRLOW).

Independent for each storage element, except

when using FDDR. In the latter case, the selection

for the upper element (OFF1 or TFF2) will apply to

both elements.

INIT1/INIT0

In the event of a Global Set/Reset, after

configuration or upon activation of the GTS net,

this switch decides whether to set or reset a

storage element. By default, choosing SRLOW

also selects INIT0; choosing SRHIGH also

selects INIT1.

Independent for each storage element, except

when using FDDR. In the latter case, selecting

INIT0 for one element applies to both elements

(even though INIT1 is selected for the other).

Spartan-3 1.2V FPGA Family: Functional Description

4

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

Pull-Up and Pull-Down Resistors

The optional pull-up and pull-down resistors are intended to

establish High and Low levels, respectively, at unused I/Os.

The weak pull-up resistor optionally connects each IOB pad

to V

CCO

. A weak pull-down resistor optionally connects

each pad to GND. These resistors are placed in a design

using the PULLUP and PULLDOWN symbols in a sche-

matic, respectively. They can also be instantiated as com-

ponents, set as constraints or passed as attributes in HDL

code. These resistors can also be selected for all unused

I/O using the Bitstream Generator (BitGen) option Unused-

Pin. A Low logic level on HSWAP_EN activates the pull-up

resistors on all I/Os during configuration.

Weak-Keeper Circuit

Each I/O has an optional weak-keeper circuit that retains

the last logic level on a line after all drivers have been turned

off. This is useful to keep bus lines from floating when all

connected drivers are in a high-impedance state. This func-

tion is placed in a design using the KEEPER symbol.

Pull-up and pull-down resistors override the weak-keeper

circuit.

ESD Protection

Clamp diodes protect all device pads against damage from

Electro-Static Discharge (ESD) as well as excessive voltage

transients. Each I/O has two clamp diodes: One diode

extends P-to-N from the pad to V

CCO

and a second diode

extends N-to-P from the pad to GND. During operation,

these diodes are normally biased in the off state. These

clamp diodes are always connected to the pad, regardless

of the signal standard selected. The presence of diodes lim-

its the ability of Spartan-3 I/Os to tolerate high signal volt-

ages. The V

IN

absolute maximum rating in

Table 1

in

Module 3:

DC and Switching Characteristics

specifies the

voltage range that I/Os can tolerate.

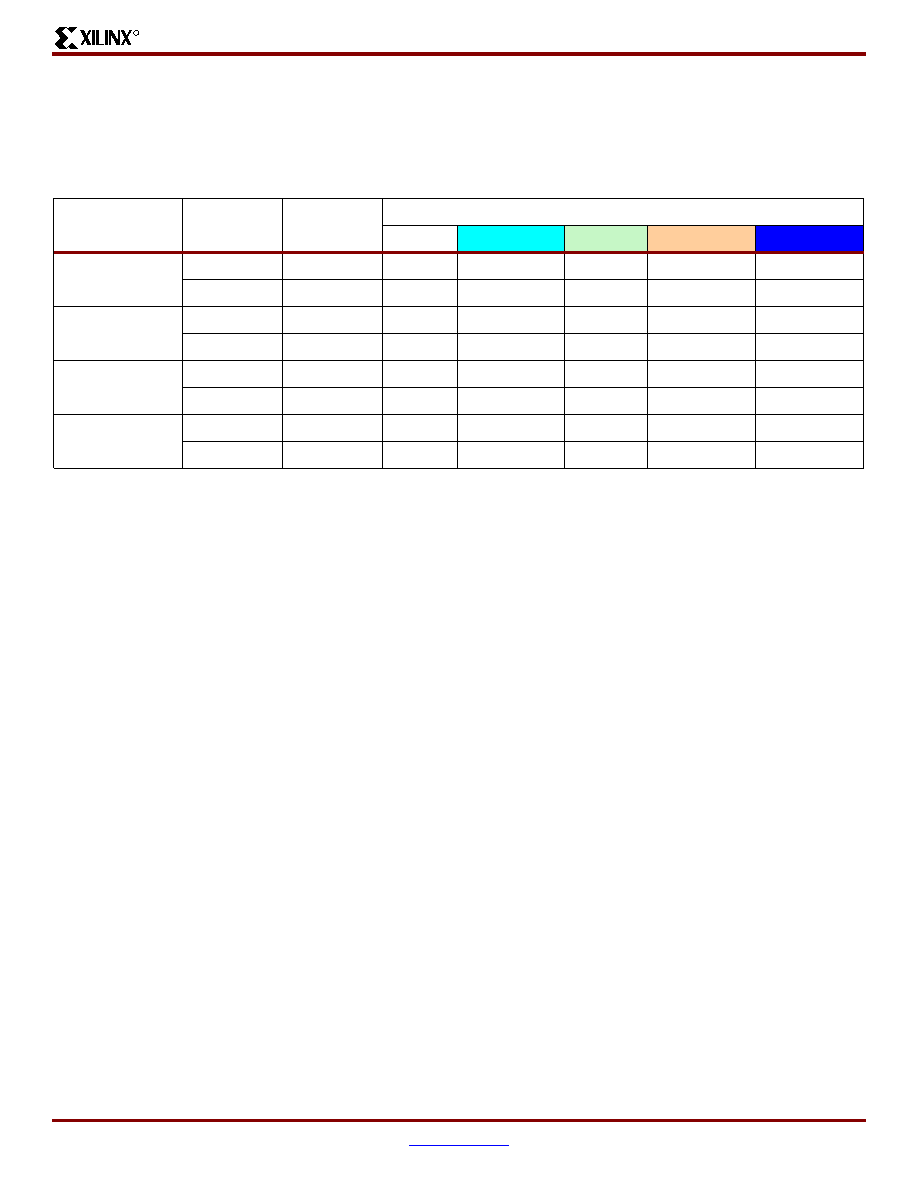

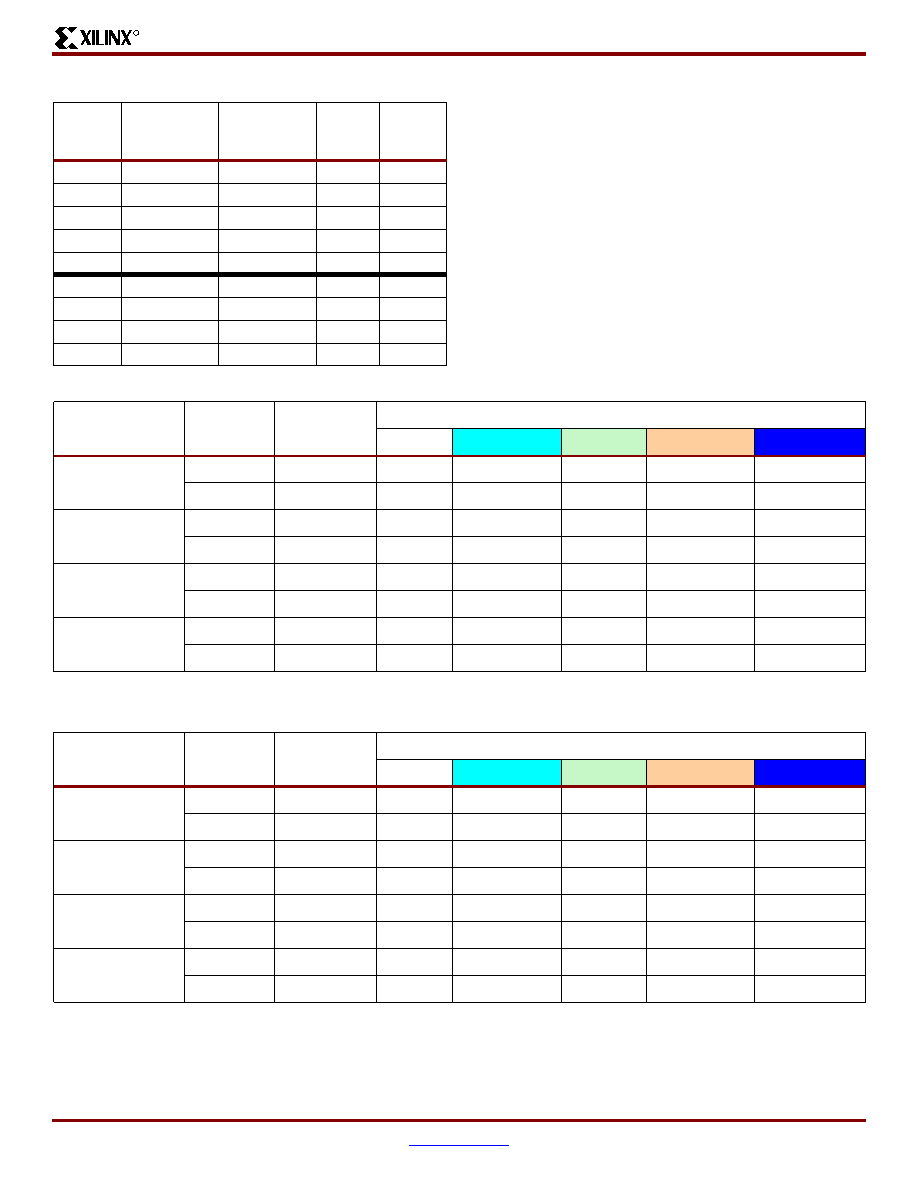

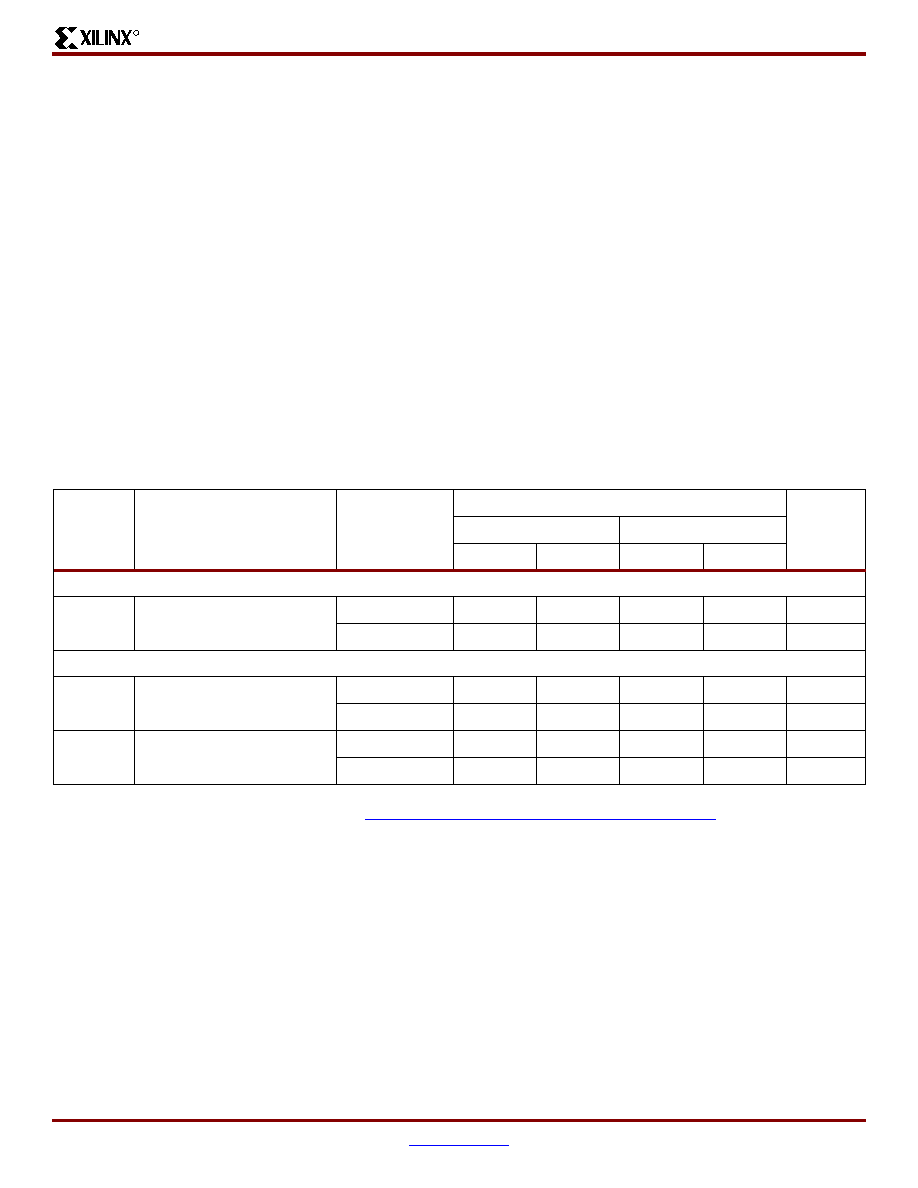

Slew Rate Control and Drive Strength

Two options, FAST and SLOW, control the output slew rate.

The FAST option supports output switching at a high rate.

The SLOW option reduces bus transients. These options are

only available when using one of the LVCMOS or LVTTL

standards, which also provide up to seven different levels of

current drive strength: 2, 4, 6, 8, 12, 16, and 24 mA. Choos-

ing the appropriate drive strength level is yet another means

to minimize bus transients.

Table 3

shows the drive strengths that the LVCMOS and

LVTTL standards support. The Fast option is indicated by

appending an "F" attribute after the output buffer symbol

OBUF or the bidirectional buffer symbol IOBUF. The Slow

option appends an "S" attribute. The drive strength in milliam-

peres follows the slew rate attribute. For example,

OBUF_LVCMOS18_S_6 or IOBUF_LVCMOS25_F_16.

Boundary-Scan Capability

All Spartan-3 IOBs support boundary-scan testing compat-

ible with IEEE 1149.1 standards. See

Boundary-Scan

(JTAG) Mode, page 36

for more information.

SelectIO

Signal Standards

The IOBs support 17 different single-ended signal stan-

dards, as listed in

Table 4

. Furthermore, the majority of

IOBs can be used in specific pairs supporting any of six dif-

ferential signal standards, as shown in

Table 5

. The desired

standard is selected by placing the appropriate I/O library

symbol or component into the FPGA design. For example,

the symbol named IOBUF_LVCMOS15_F_8 represents a

bidirectional I/O to which the 1.5V LVCMOS signal standard

has been assigned. The slew rate and current drive are set

to Fast and 8 mA, respectively.

Together with placing the appropriate I/O symbol, two exter-

nally applied voltage levels, V

CCO

and V

REF

select the

desired signal standard. The V

CCO

lines provide current to

the output driver. The voltage on these lines determines the

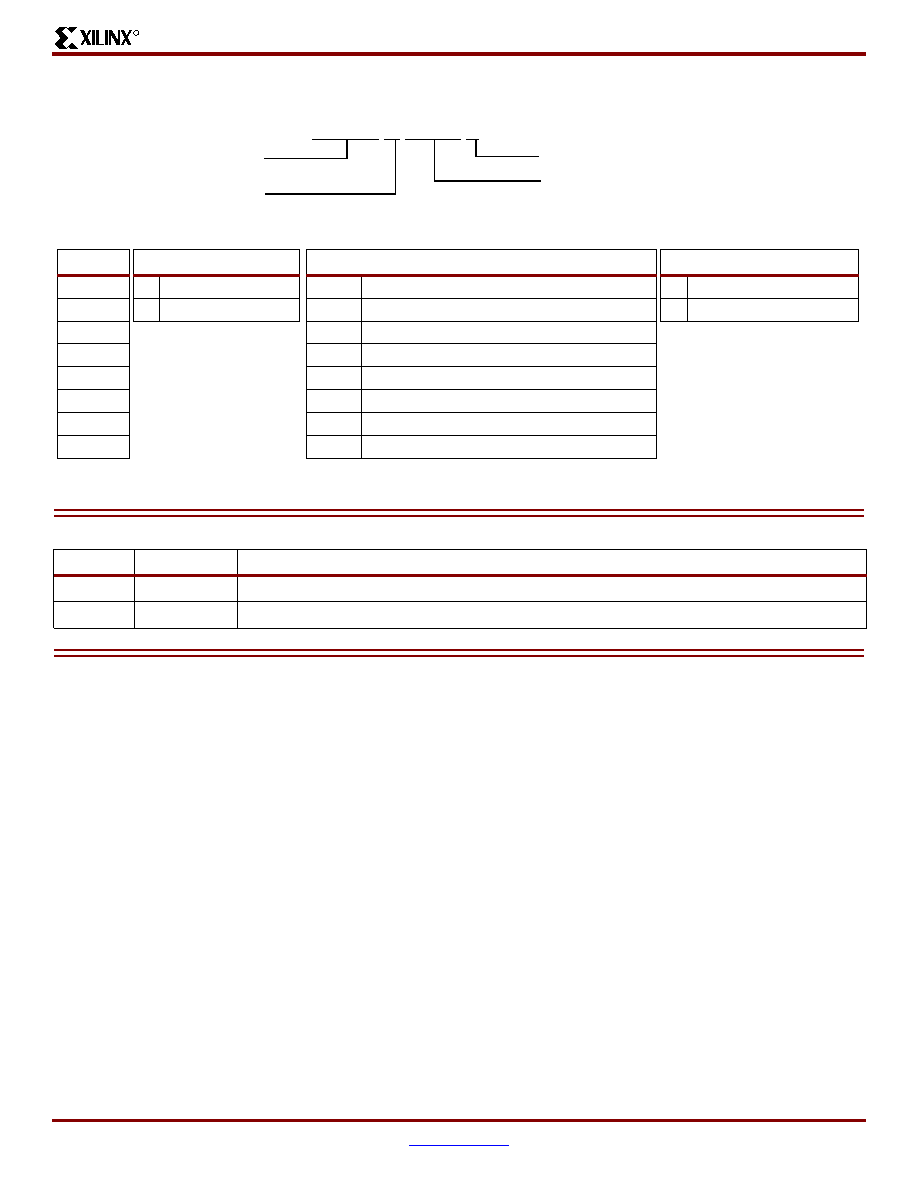

Figure 2: Clocking the DDR Register

D1

CLK1

DDR MUX

DCM

Q1

FDDR

D2

CLK2

Q2

180� 0�

DS099-2_02_070303

Q

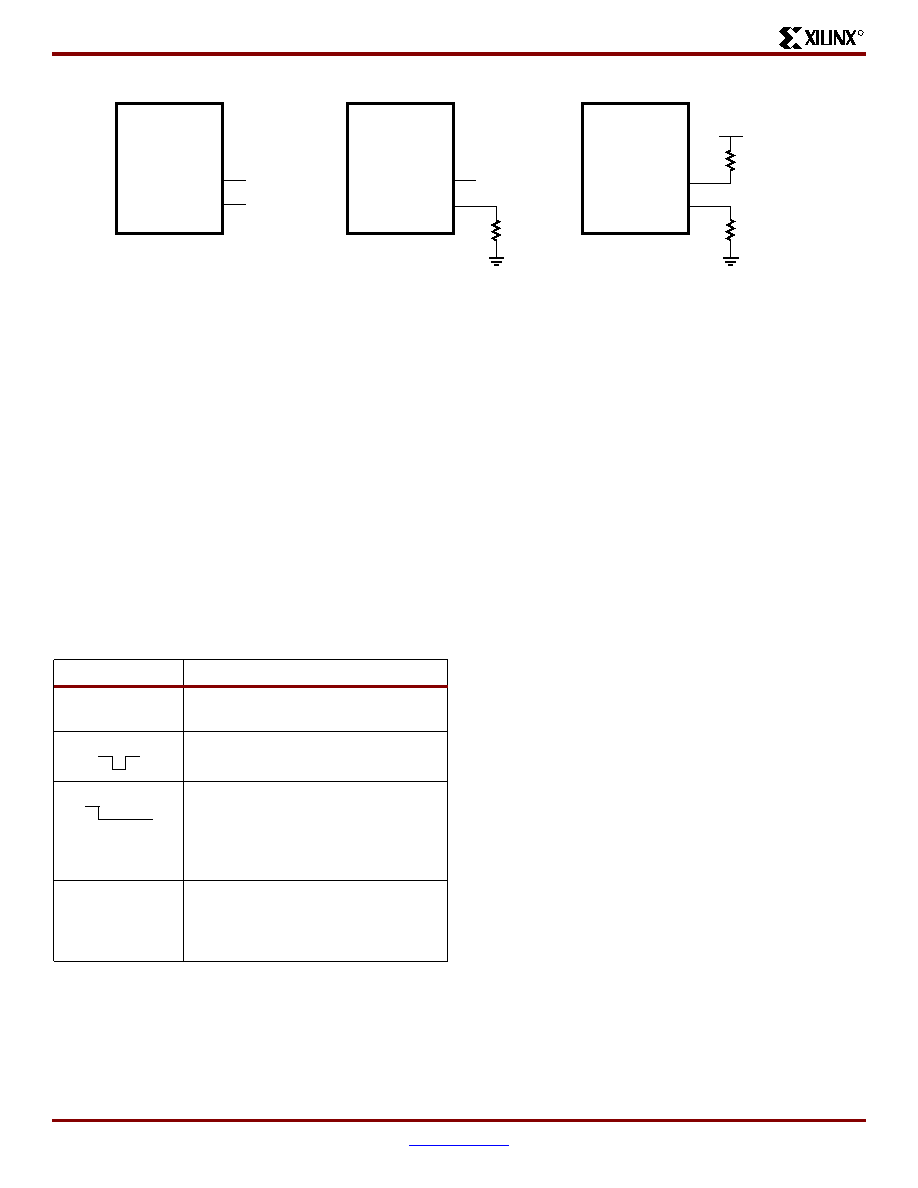

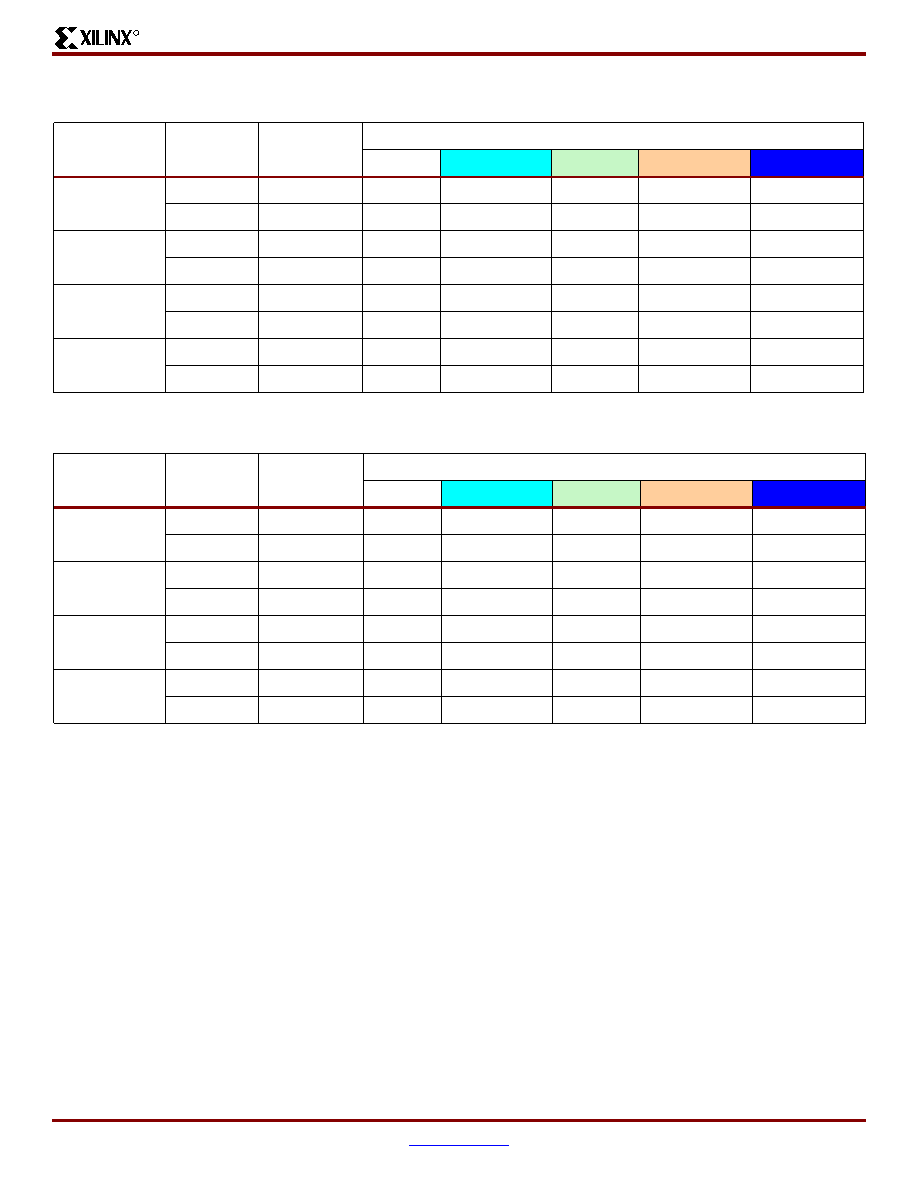

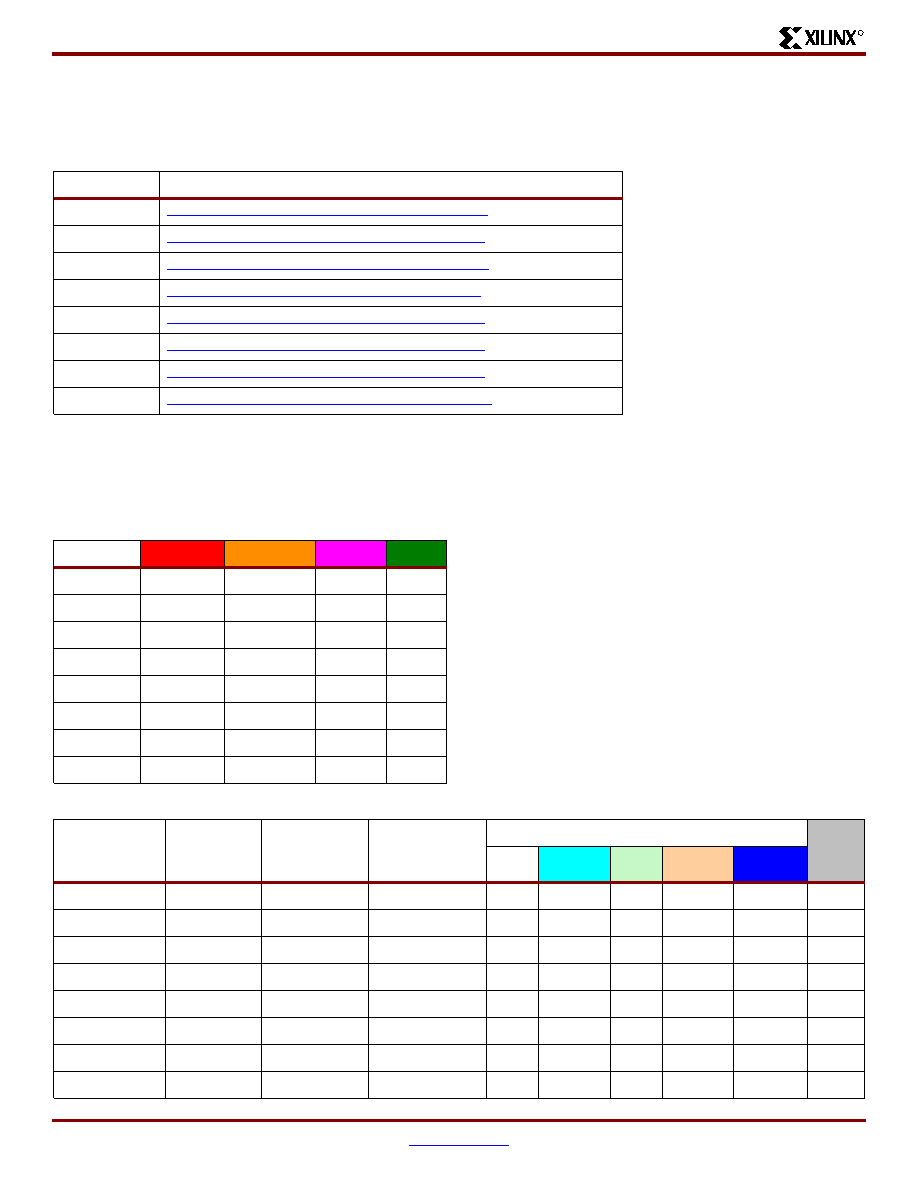

Table 3: Programmable Output Drive Current

Signal

Standard

Current Drive (mA)

2

4

6

8

12

16

24

LVCMOS12

-

-

-

-

LVCMOS15

-

-

LVCMOS18

-

LVCMOS25

LVCMOS33

LVTTL

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

5

Advance Product Specification

1-800-255-7778

R

output voltage swing for all standards except GTL and

GTLP.

All single-ended standards except the LVCMOS modes

require a Reference Voltage (V

REF

) to bias the input-switch-

ing threshold. Once a configuration data file is loaded into

the FPGA that calls for the I/Os of a given bank to use such

a signal standard, a few specifically reserved I/O pins on the

same bank automatically convert to V

REF

inputs. When

using one of the LVCMOS standards, these pins remain

I/Os because the V

CCO

voltage biases the input-switching

threshold, so there is no need for V

REF

. Select the V

CCO

and

V

REF

levels to suit the desired single-ended standard

according to

Table 4

.

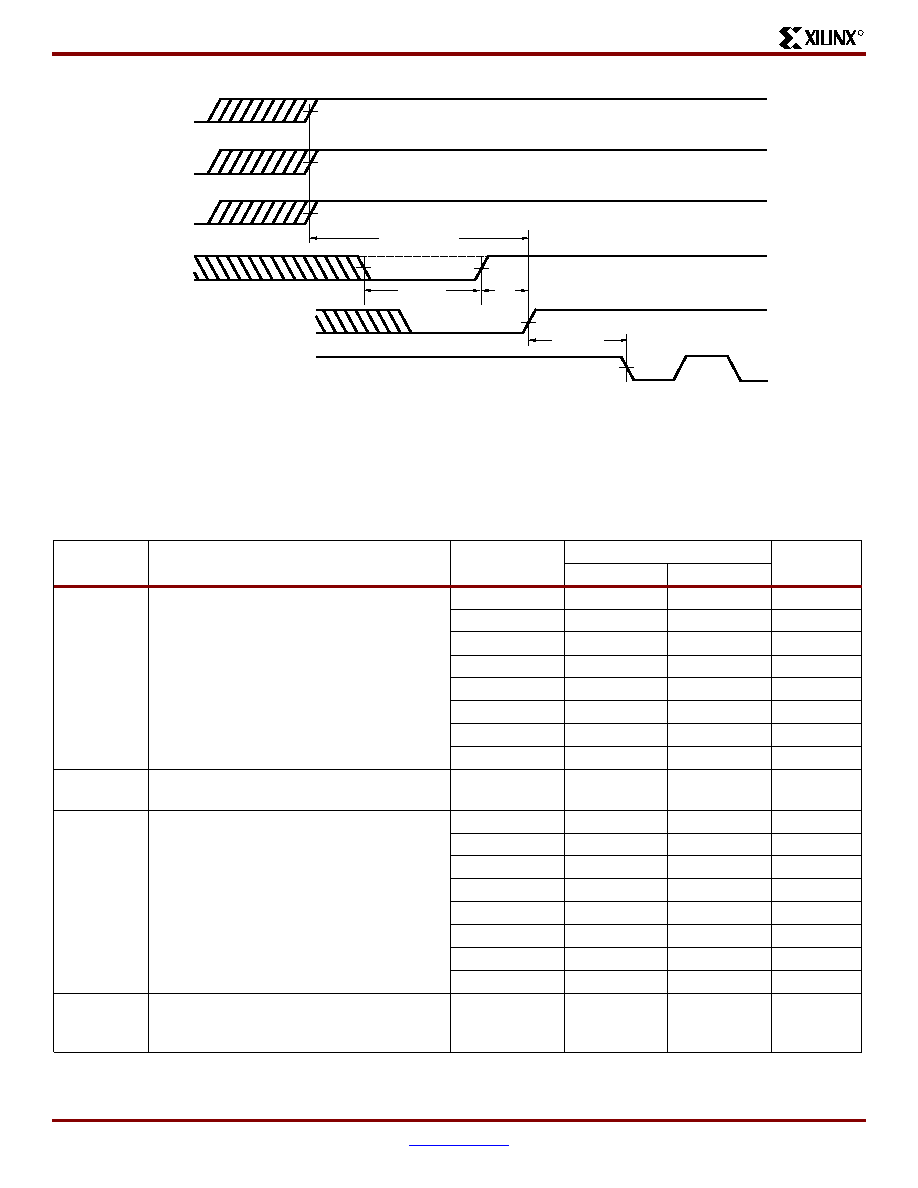

Differential standards employ a pair of signals, one the

opposite polarity of the other. The noise canceling (e.g.,

Common-Mode Rejection) properties of these standards

permit exceptionally high data transfer rates. This section

introduces the differential signaling capabilities of Spartan-3

devices.

Each device-package combination designates specific I/O

pairs that are specially optimized to support differential

standards. A unique "L-number", part of the pin name, iden-

tifies the line-pairs associated with each bank (see Module

4:

Pinout Descriptions

). For each pair, the letters "P" and

"N" designate the true and inverted lines, respectively. For

example, the pin names IO_L43P_7 and IO_L43N_7 indi-

cate the true and inverted lines comprising the line pair L43

on Bank 7. The differential Output Voltage (V

OD

) parameter

measures the voltage difference the High and Low logic lev-

els that a pair of differential outputs drive. The V

OD

range for

each of the differential standards is listed in

Table 5

. The

V

CCO

lines provide current to the outputs. The V

REF

lines

are not used. Select the V

CCO

level to suit the desired differ-

ential standard according to

Table 5

.

The need to supply V

REF

and V

CCO

imposes constraints on

which standards can be used in the same bank. See

The

Organization of IOBs into Banks

section for additional

guidelines concerning the use of the V

CCO

and V

REF

lines.

Digitally Controlled Impedance (DCI)

When the round-trip delay of an output signal -- i.e., from

output to input and back again -- exceeds rise and fall

times, it is common practice to add termination resistors to

the line carrying the signal. These resistors effectively

match the impedance of a device's I/O to the characteristic

impedance of the transmission line, thereby preventing

reflections that adversely affect signal integrity. However,

with the high I/O counts supported by modern devices, add-

ing resistors requires significantly more components and

board area. Furthermore, for some packages -- e.g., ball

grid arrays -- it may not always be possible to place resis-

tors close to pins.

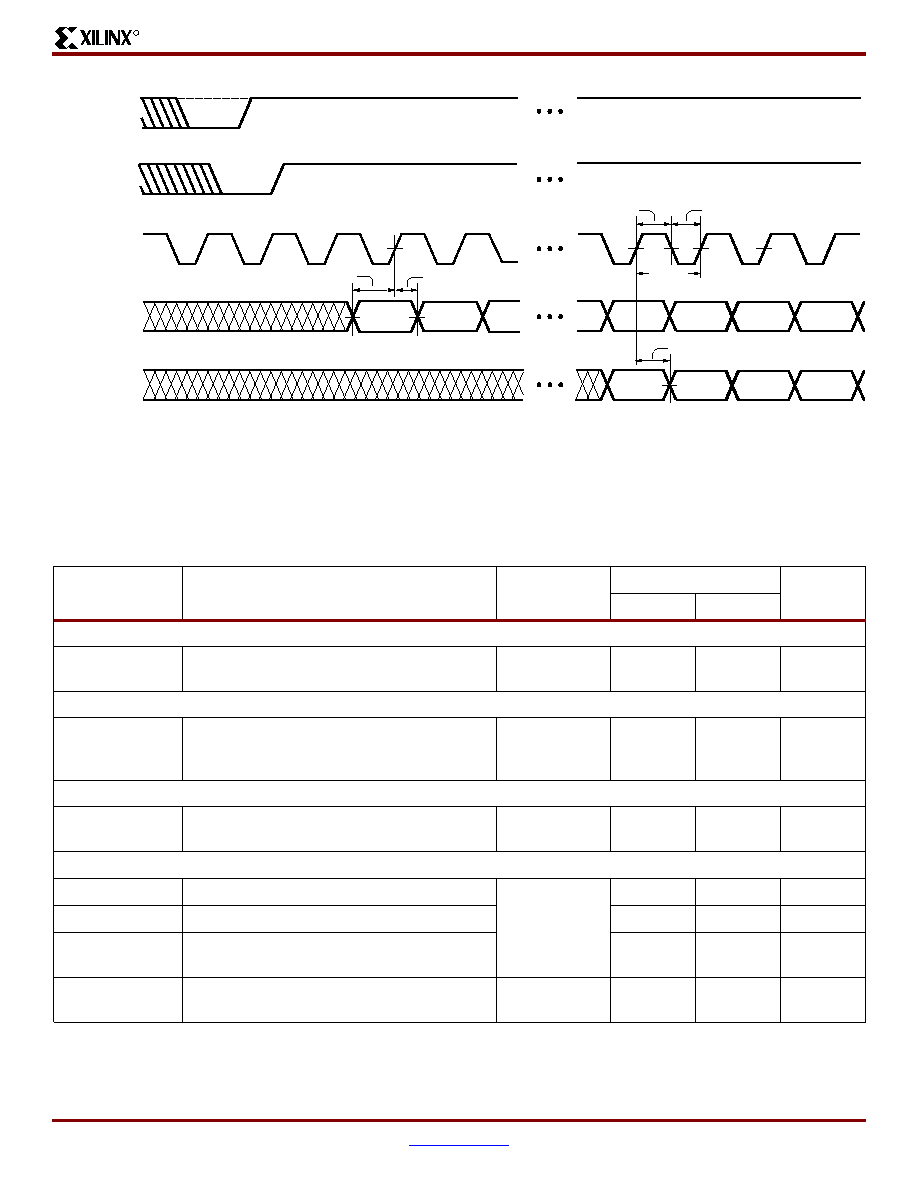

DCI answers these concerns by providing two kinds of

on-chip terminations: Parallel terminations make use of an

integrated resistor network. Series terminations result from

controlling the impedance of output drivers. DCI actively

adjusts both parallel and series terminations to accurately

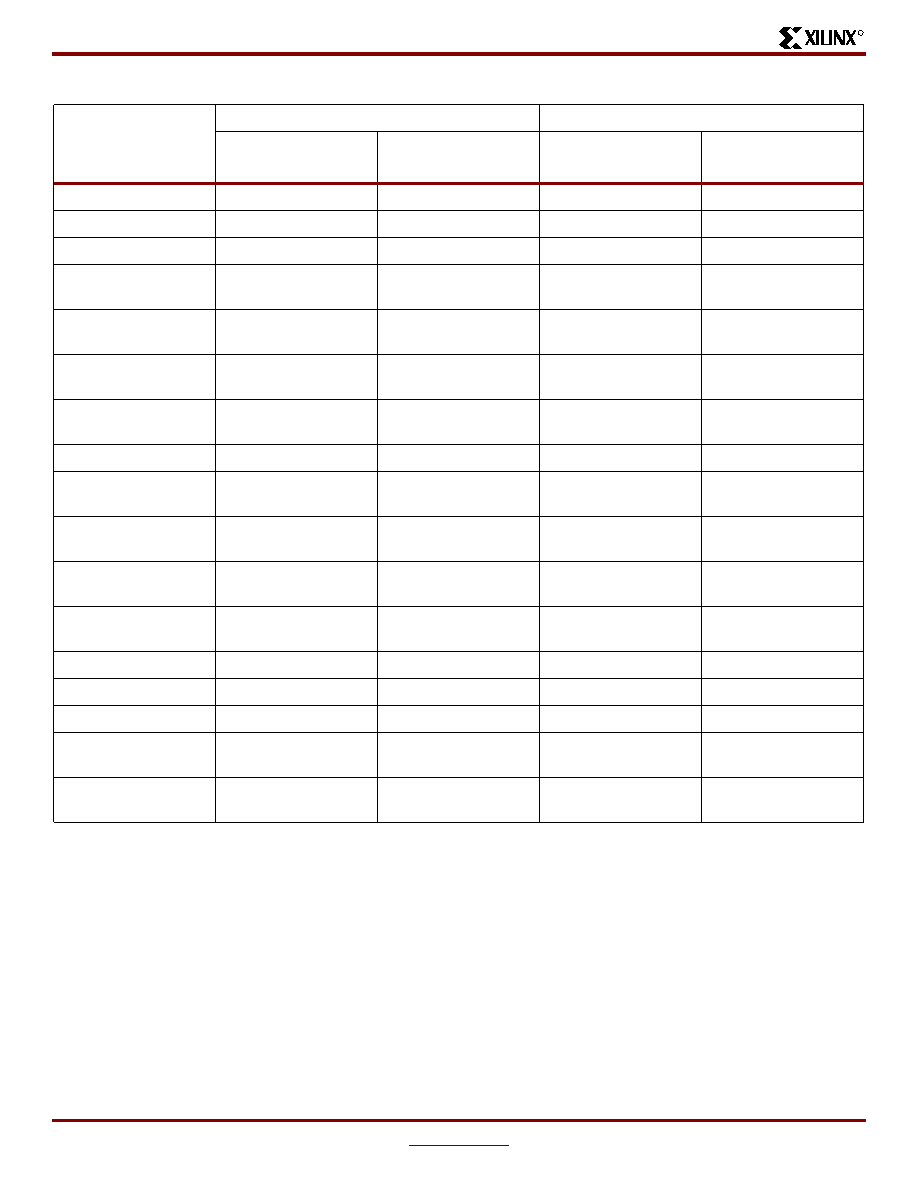

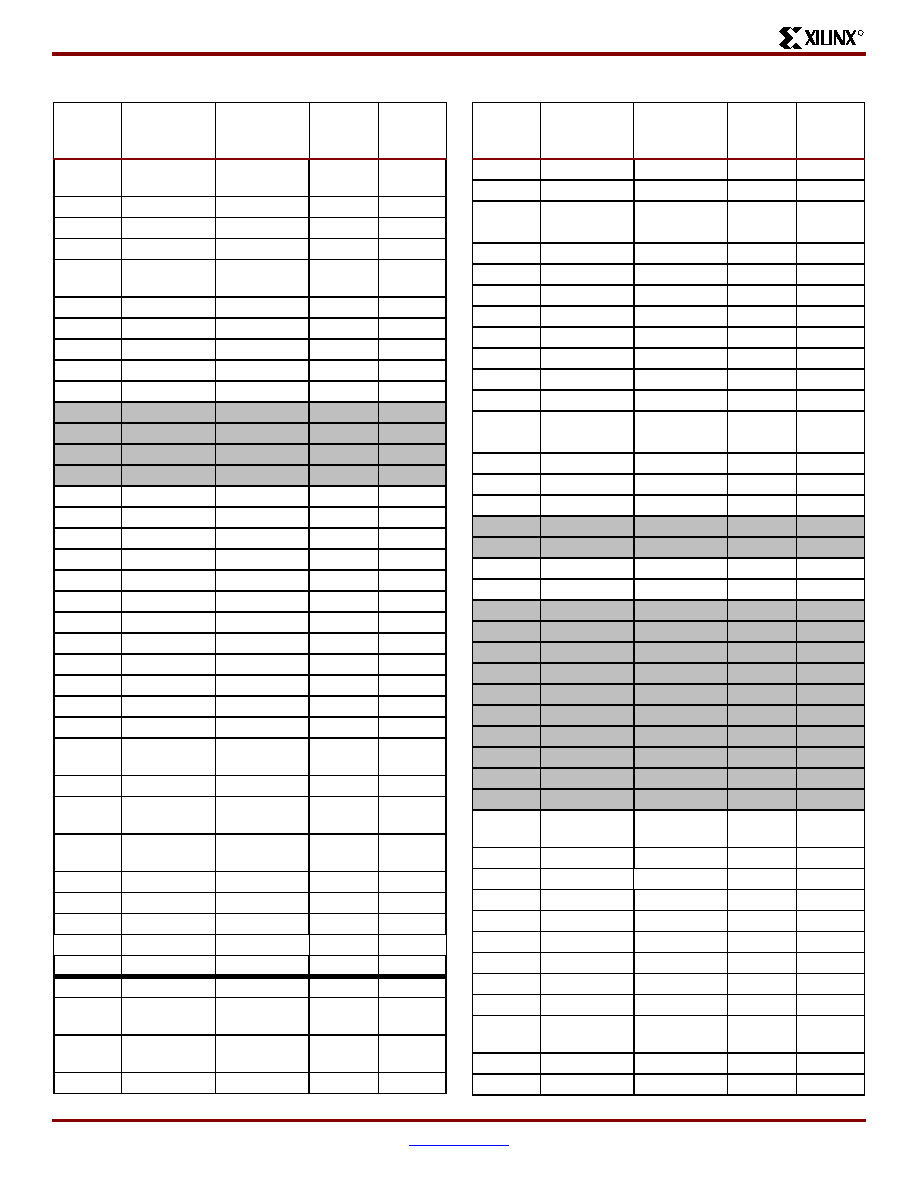

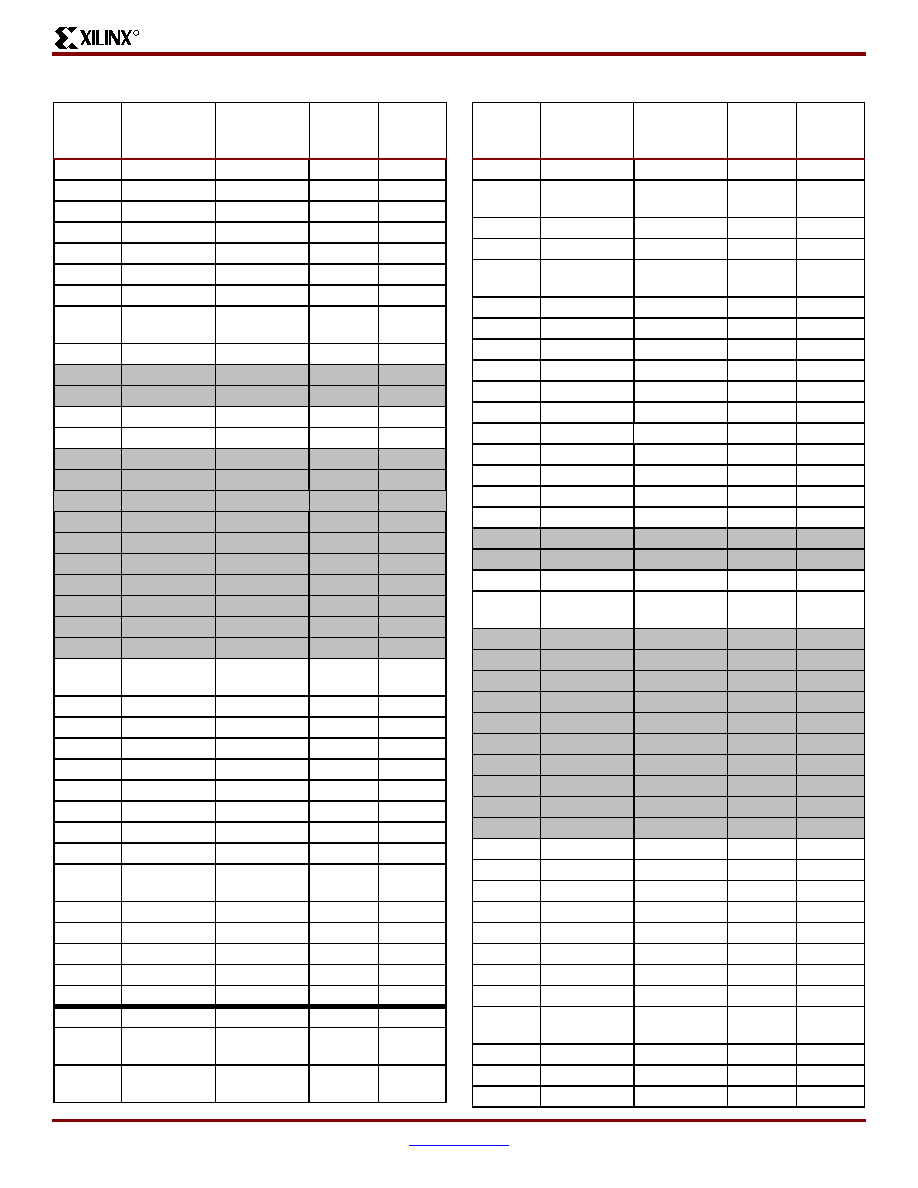

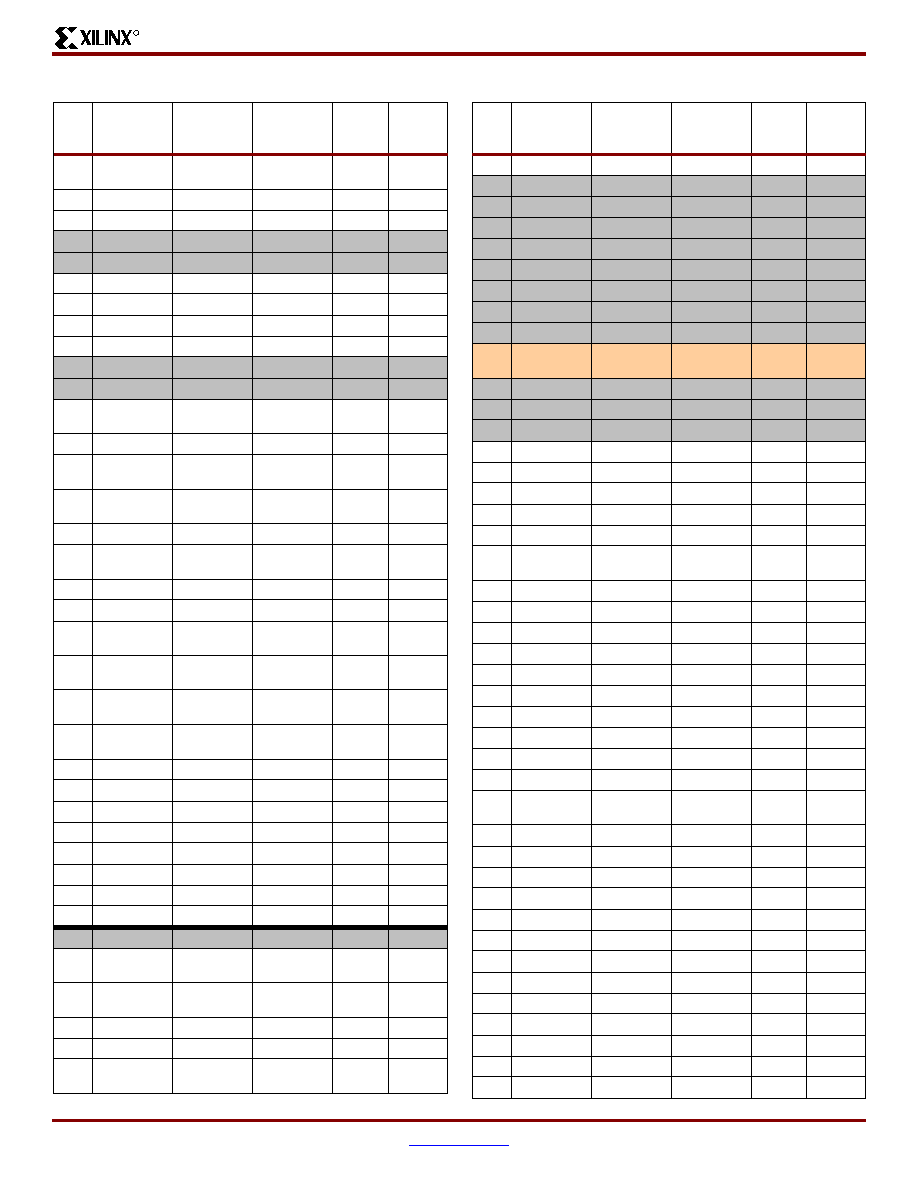

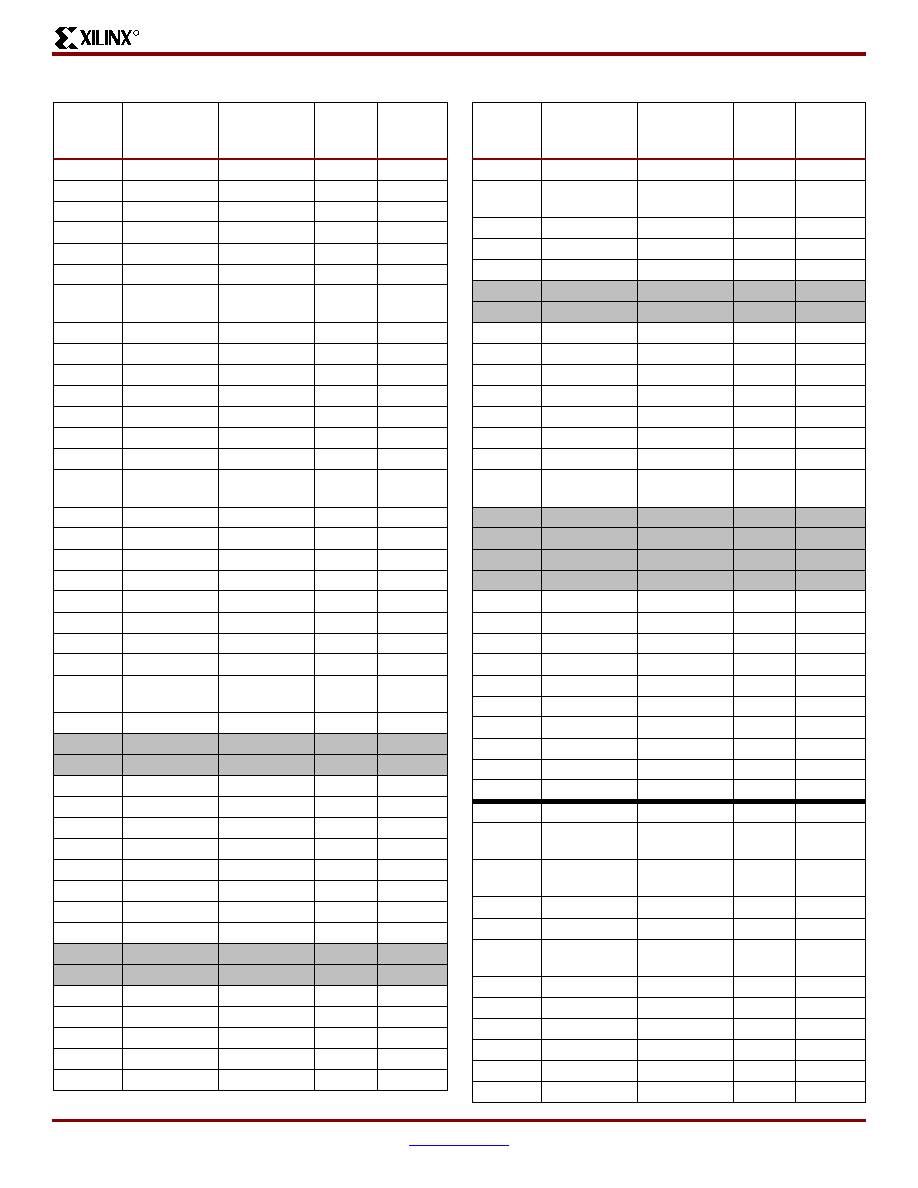

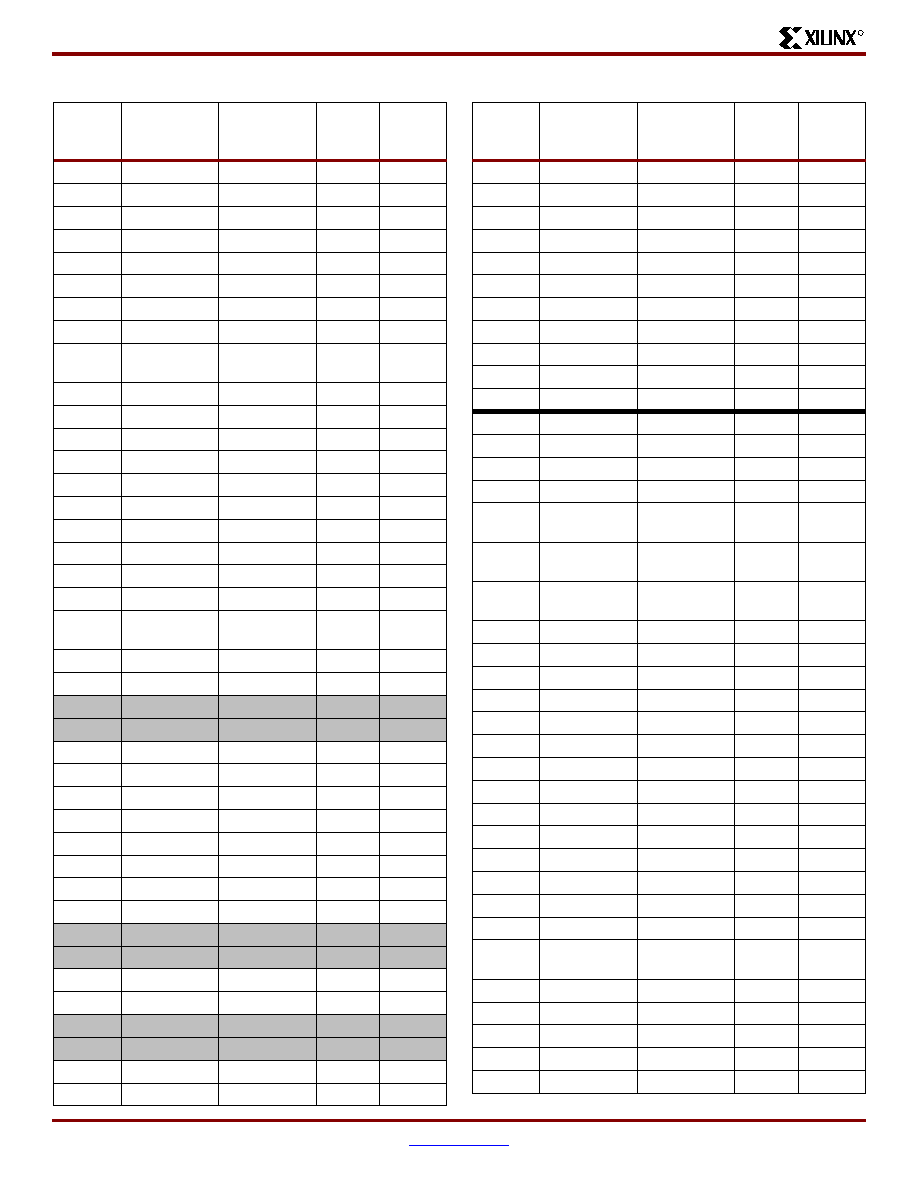

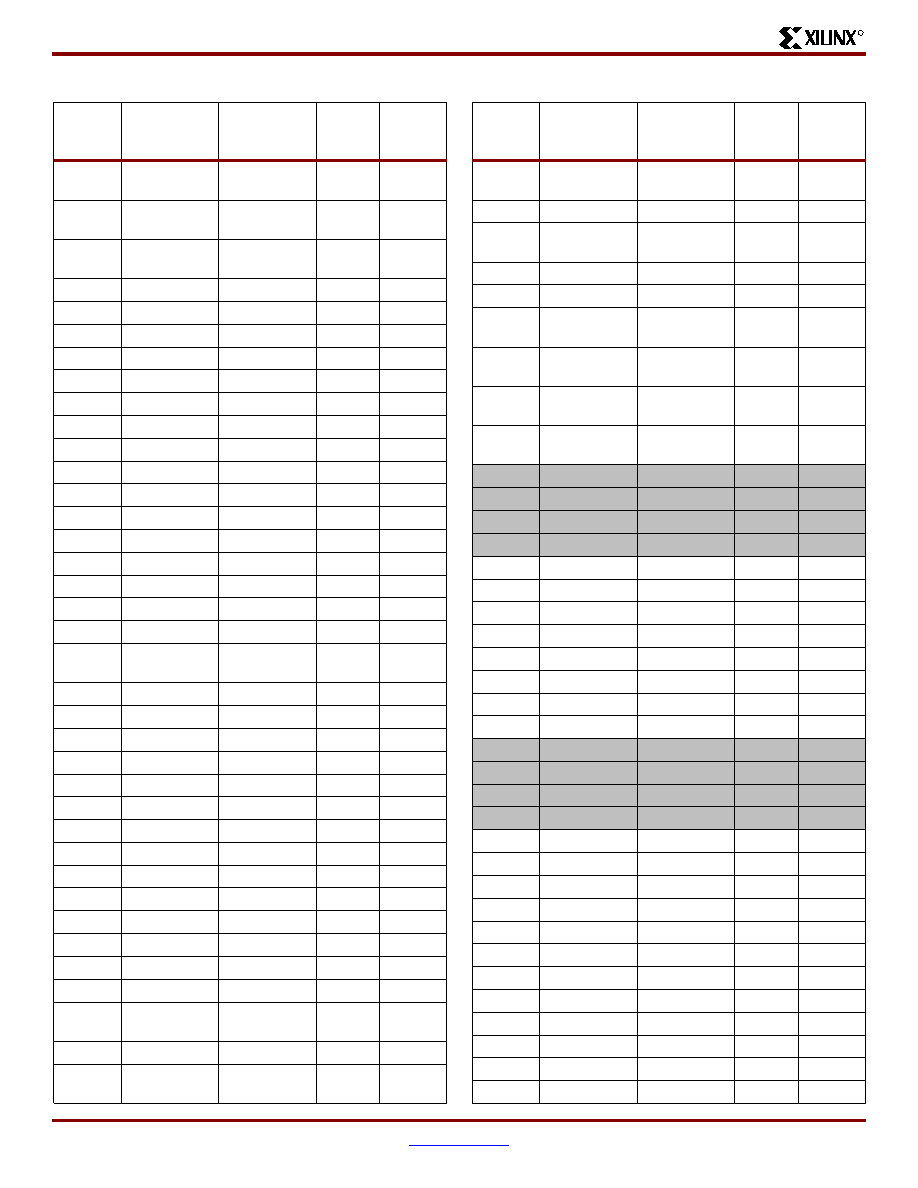

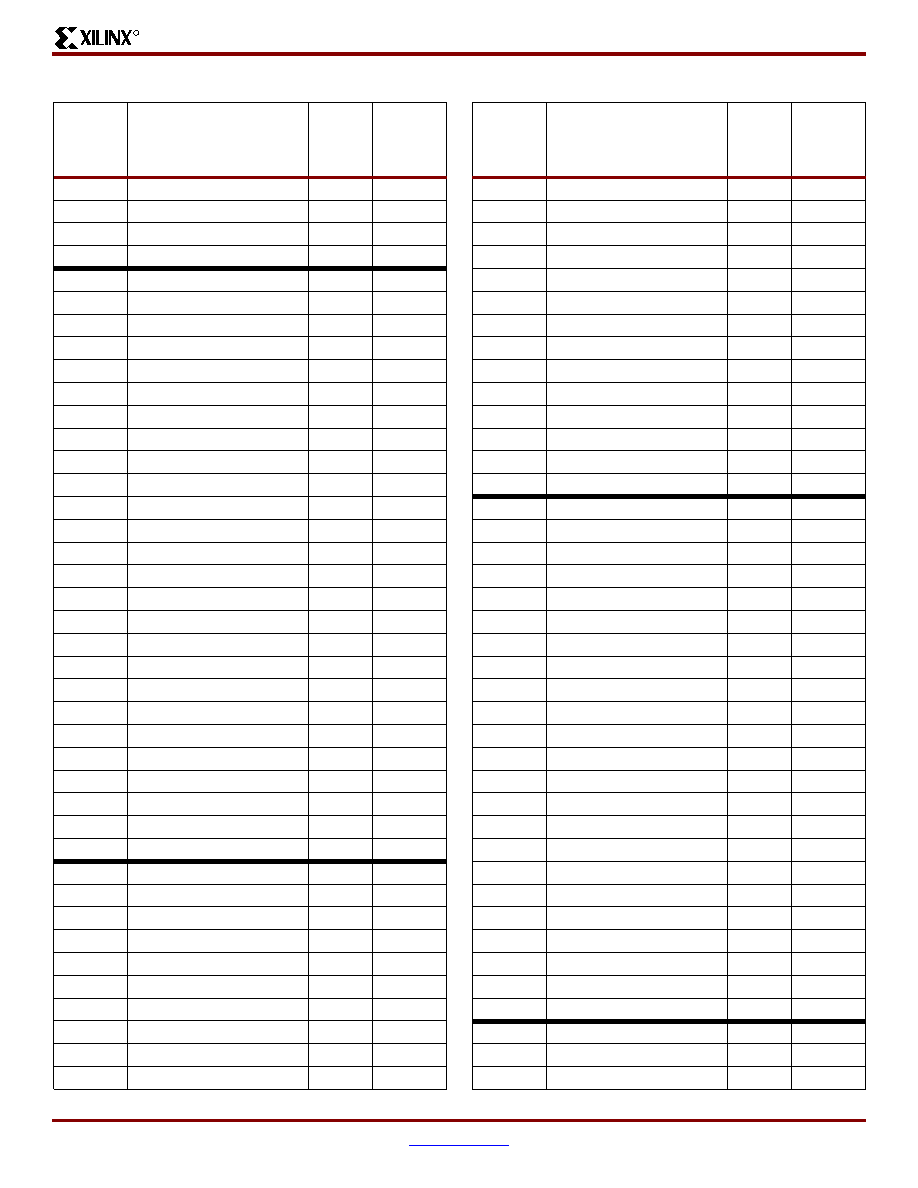

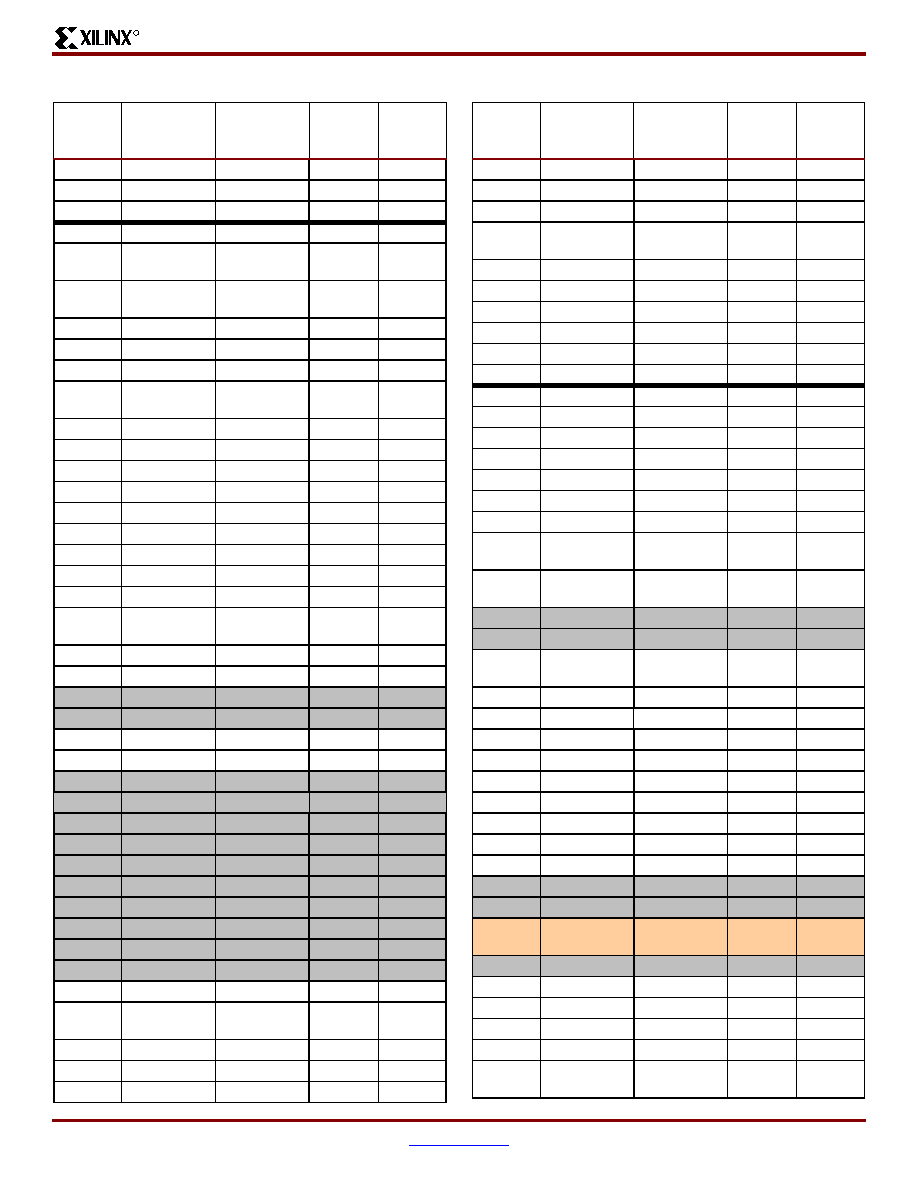

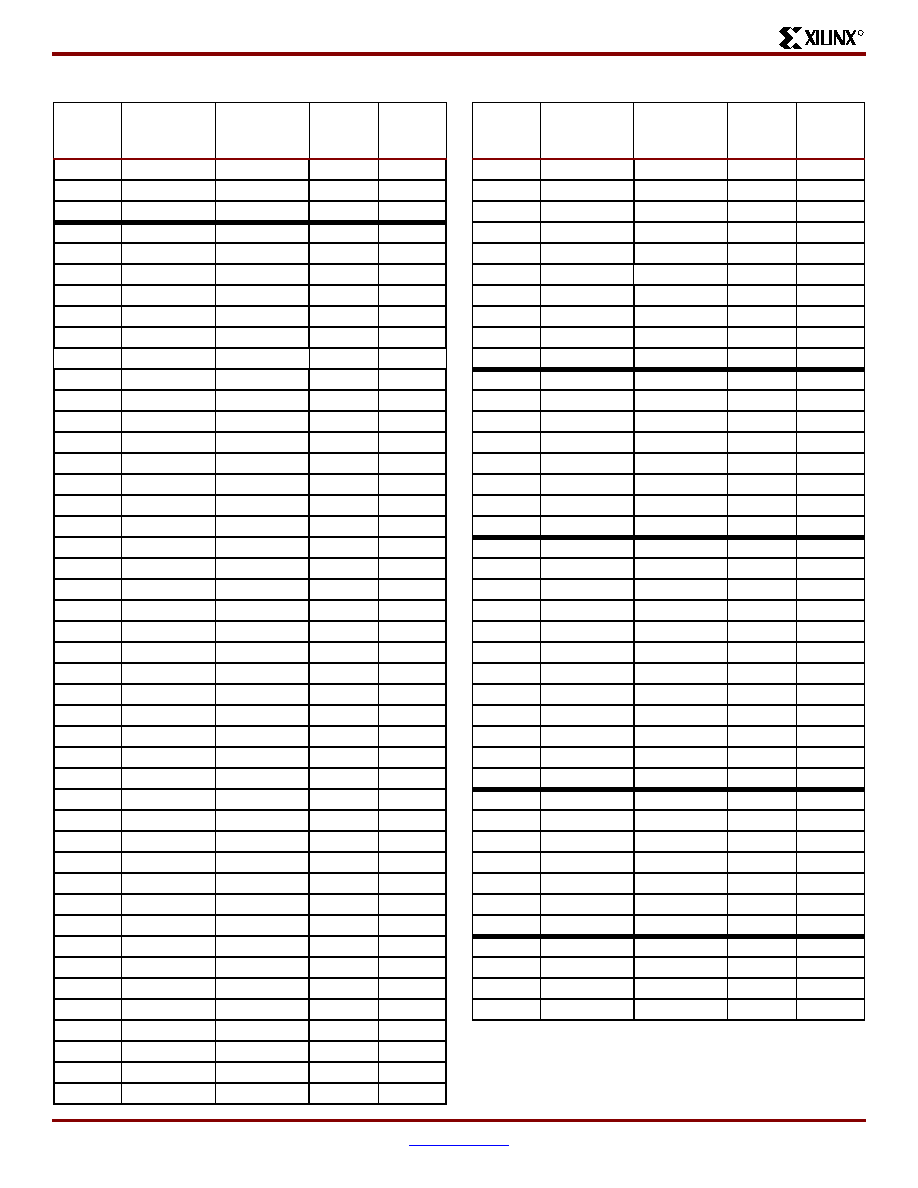

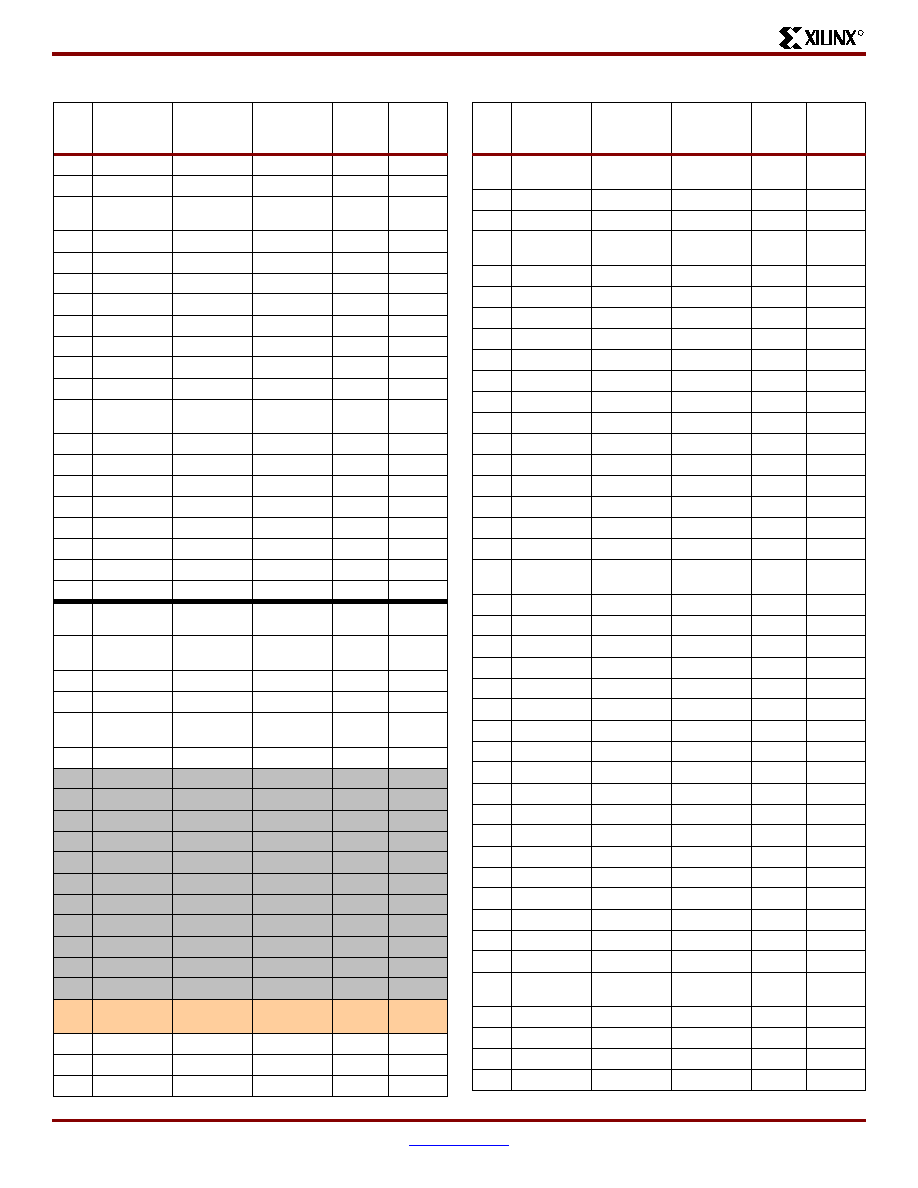

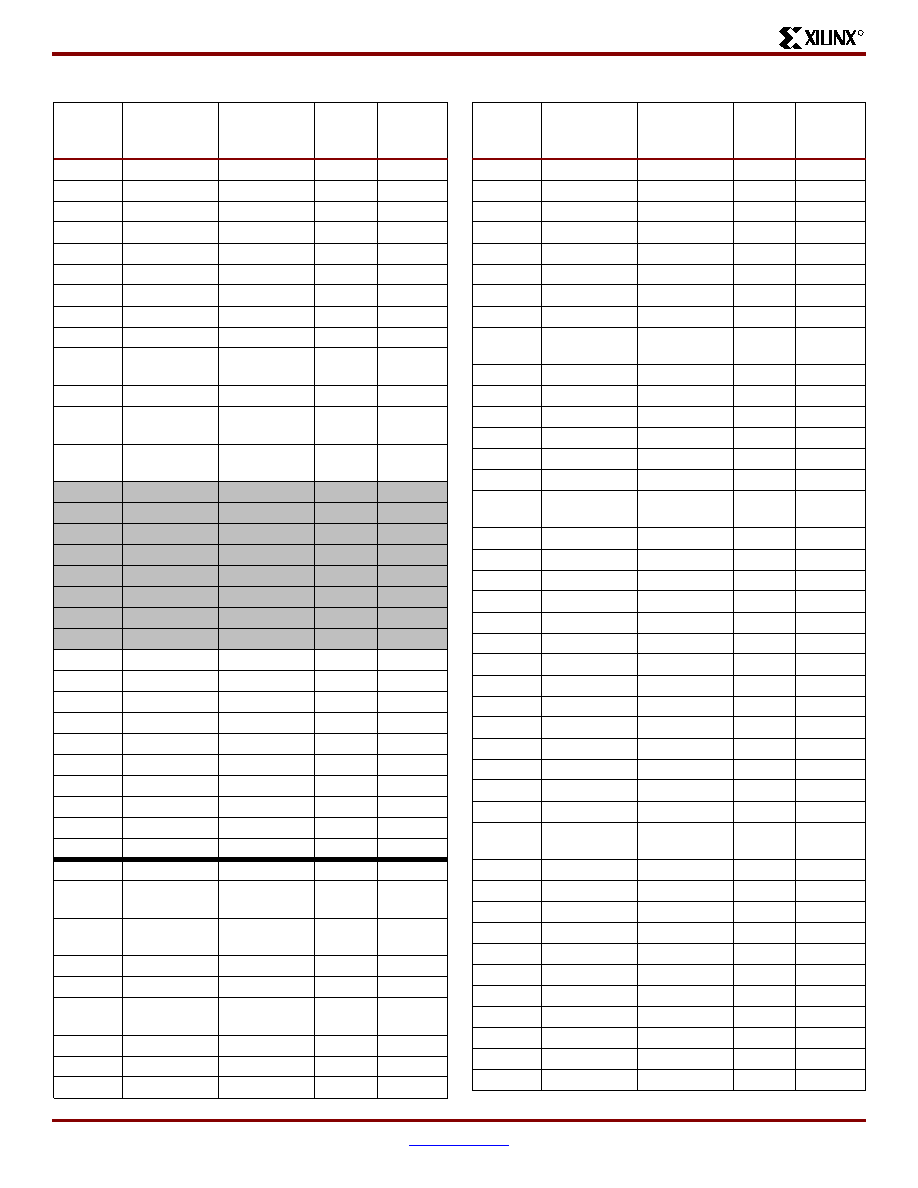

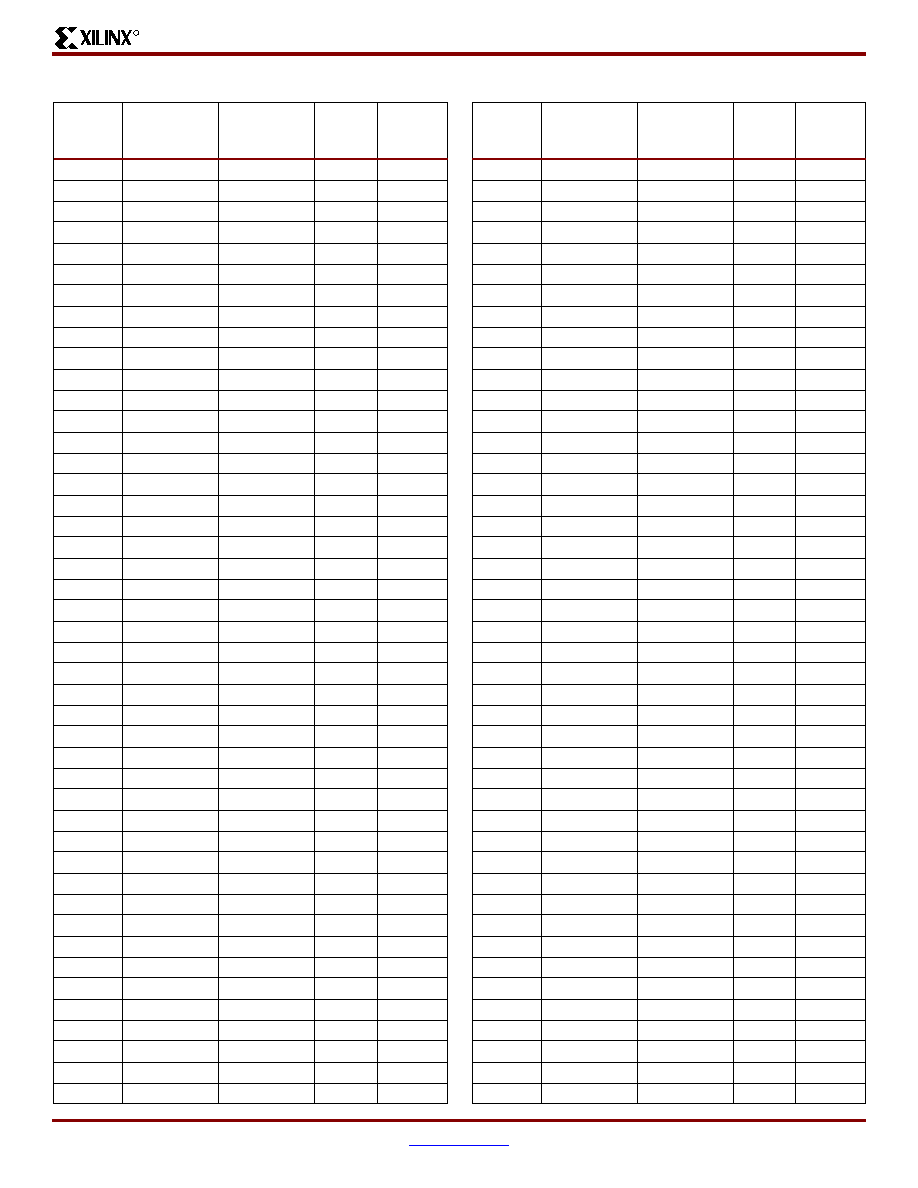

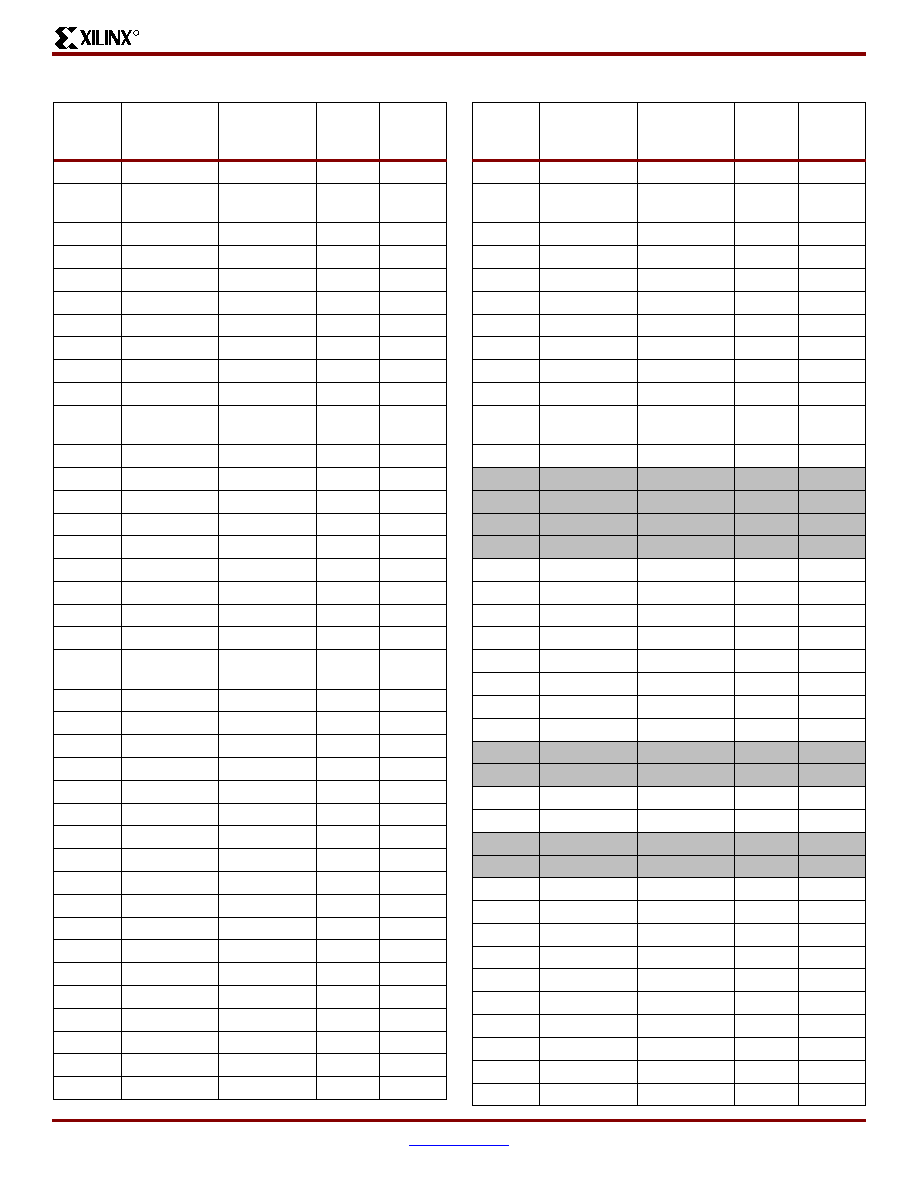

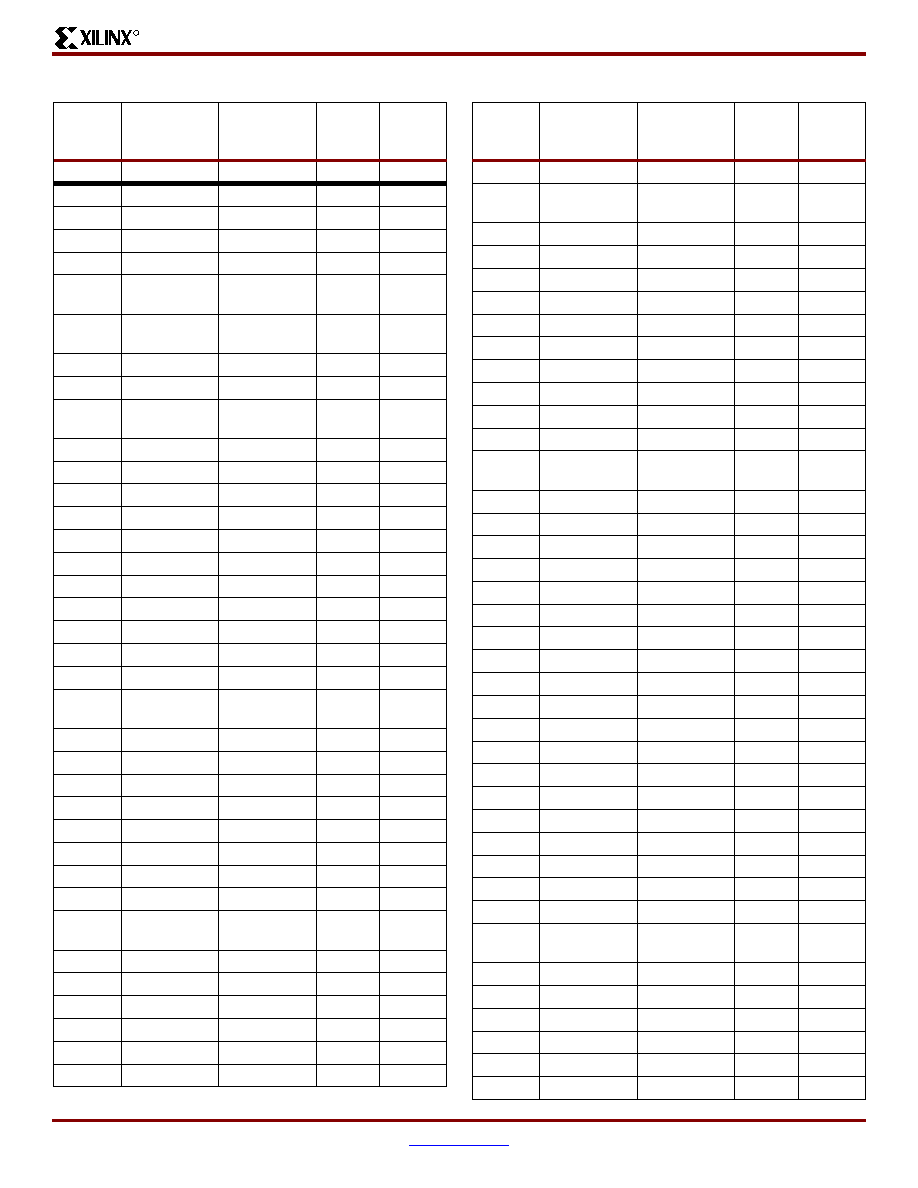

Table 4: Single-Ended I/O Standards (Values in Volts)

Signal

Standard

V

CCO

V

REF

for

Inputs

(1)

Board

Termination

Voltage (V

TT

)

For

Outputs

For

Inputs

GTL

Note 2

Note 2

0.8

1.2

GTLP

Note 2

Note 2

1

1.5

HSTL_I

1.5

-

0.75

0.75

HSTL_III

1.5

-

0.9

1.5

HSTL_I_18

1.8

-

0.9

0.9

HSTL_II_18

1.8

-

0.9

0.9

HSTL_III_18

1.8

-

1.1

1.8

LVCMOS12

1.2

1.2

-

-

LVCMOS15

1.5

1.5

-

-

LVCMOS18

1.8

1.8

-

-

LVCMOS25

2.5

2.5

-

-

LVCMOS33

3.3

3.3

-

-

LVTTL

3.3

3.3

-

-

PCI33_3

3.0

3.0

-

-

SSTL18_I

1.8

-

0.9

0.9

SSTL2_I

2.5

-

1.25

1.25

SSTL2_II

2.5

-

1.25

1.25

Notes:

1.

Banks 4 and 5 of any Spartan-3 device in a VQ100 package

do not support signal standards using V

REF

.

2.

The V

CCO

level used for the GTL and GTLP standards must

be no lower than the termination voltage (V

TT

), nor can it be

lower than the voltage at the I/O pad.

3.

See

Table 6

for a listing of the single-ended DCI standards.

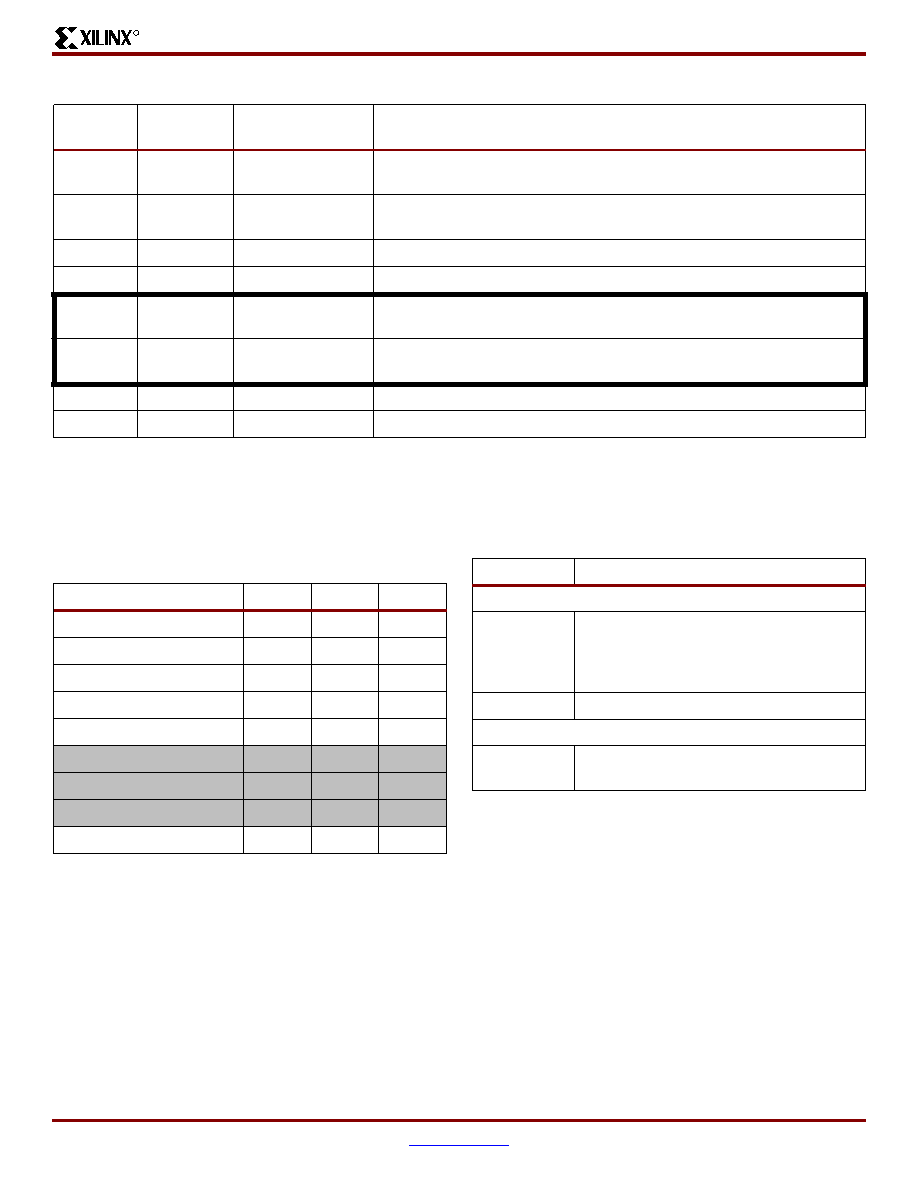

Table 5: Differential I/O Standards

Signal

Standard

V

CCO

(Volts)

V

REF

for

Inputs

(Volts)

V

OD

(1)

(mV)

For

Outputs

For

Inputs

Min.

Max.

LDT_25

2.5

-

-

430

670

LVDS_25

2.5

-

-

250

400

BLVDS_25

2.5

-

-

250

450

LVDSEXT_25

2.5

-

-

330

700

ULVDS_25

2.5

-

-

430

670

RSDS_25

2.5

-

-

100

400

Notes:

1.

Measured with a termination resistor value (RT) of 100

Ohms.

2.

See

Table 6

for a listing of the differential DCI standards.

Table 4: Single-Ended I/O Standards (Values in Volts)

Signal

Standard

V

CCO

V

REF

for

Inputs

(1)

Board

Termination

Voltage (V

TT

)

For

Outputs

For

Inputs

Spartan-3 1.2V FPGA Family: Functional Description

6

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

match the characteristic impedance of the transmission line.

This adjustment process compensates for differences in I/O

impedance that can result from normal variation in the

ambient temperature, the supply voltage and the manufac-

turing process. When the output driver turns off, the series

termination, by definition, approaches a very high imped-

ance; in contrast, parallel termination resistors remain at the

targeted values.

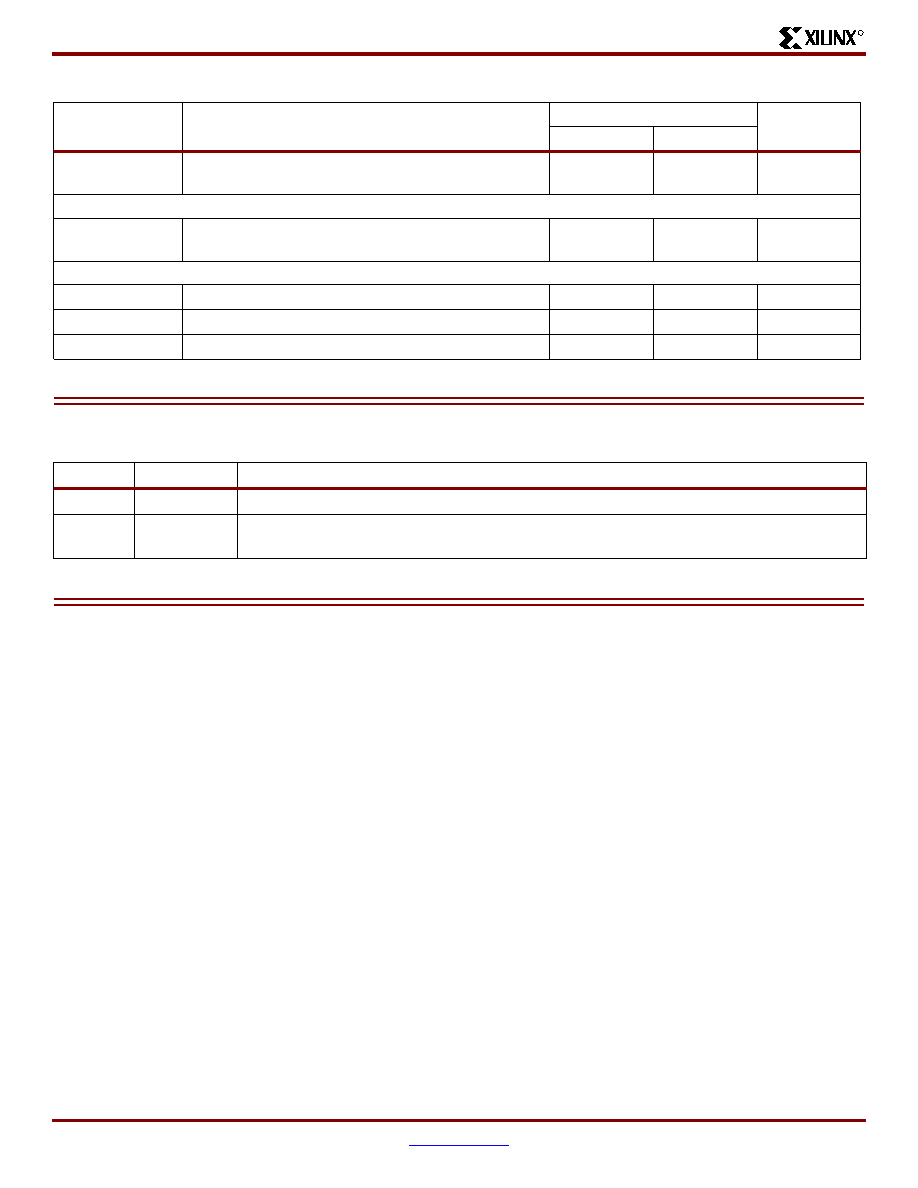

DCI is available only for certain I/O standards, as listed in

Table 6

. DCI is selected by applying the appropriate I/O

standard extensions to symbols or components. There are

five basic ways to configure terminations, as shown in

Table 7

. The DCI I/O standard determines which of these

terminations is put into effect.

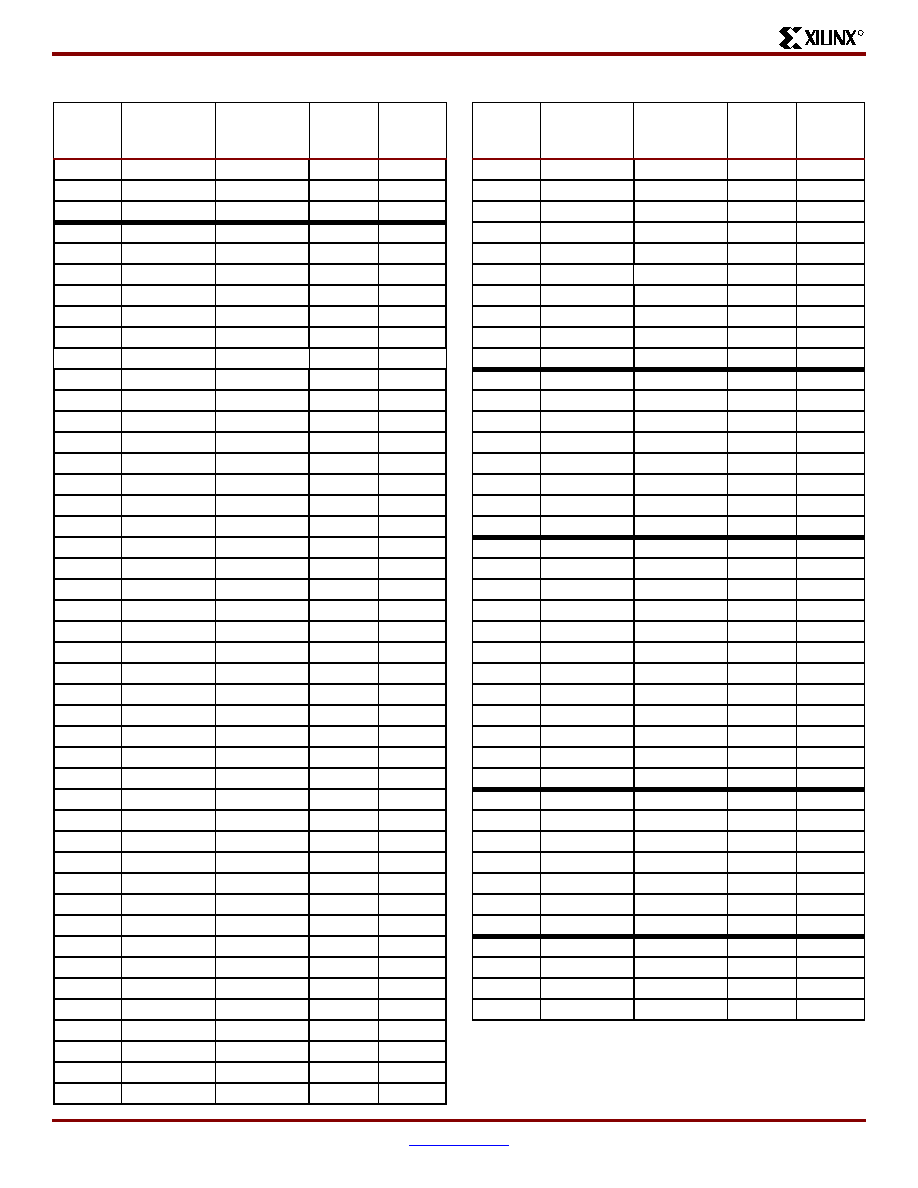

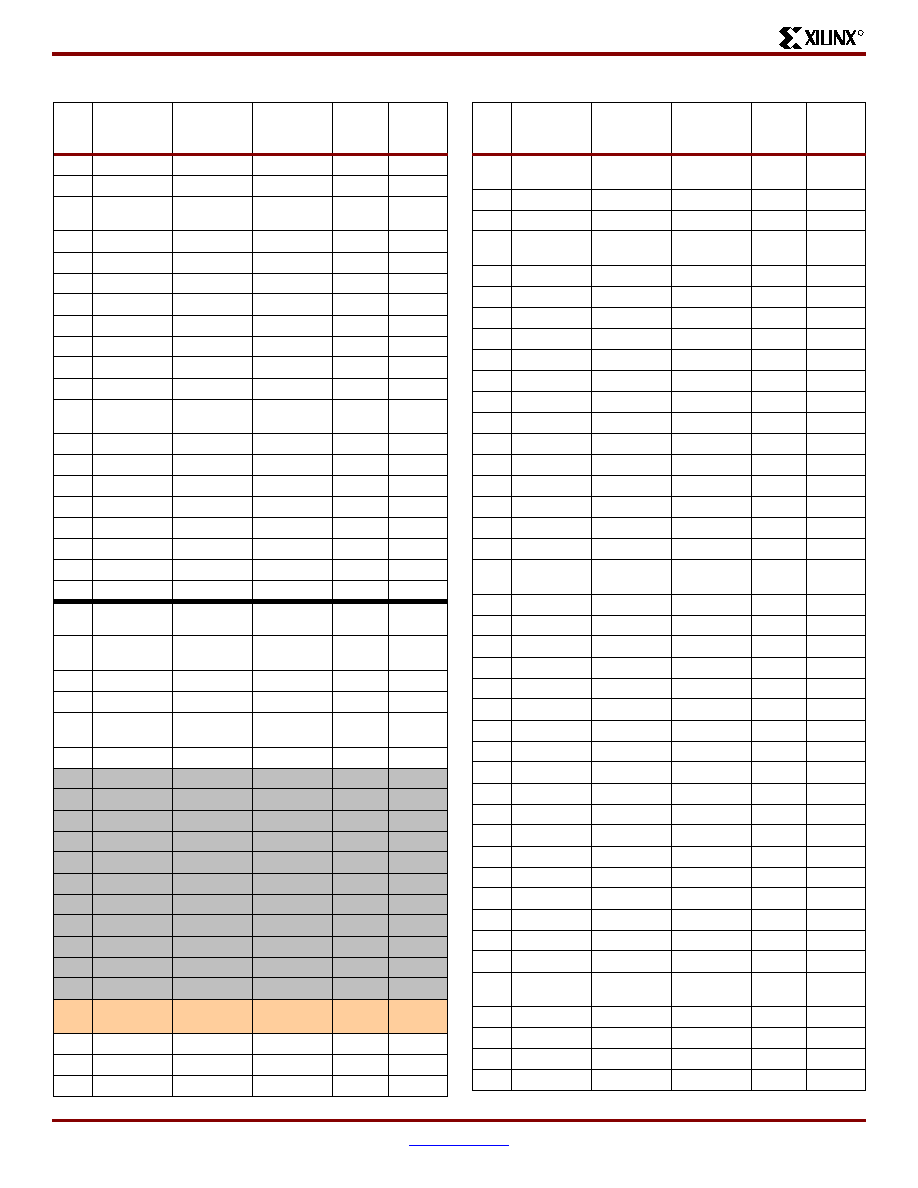

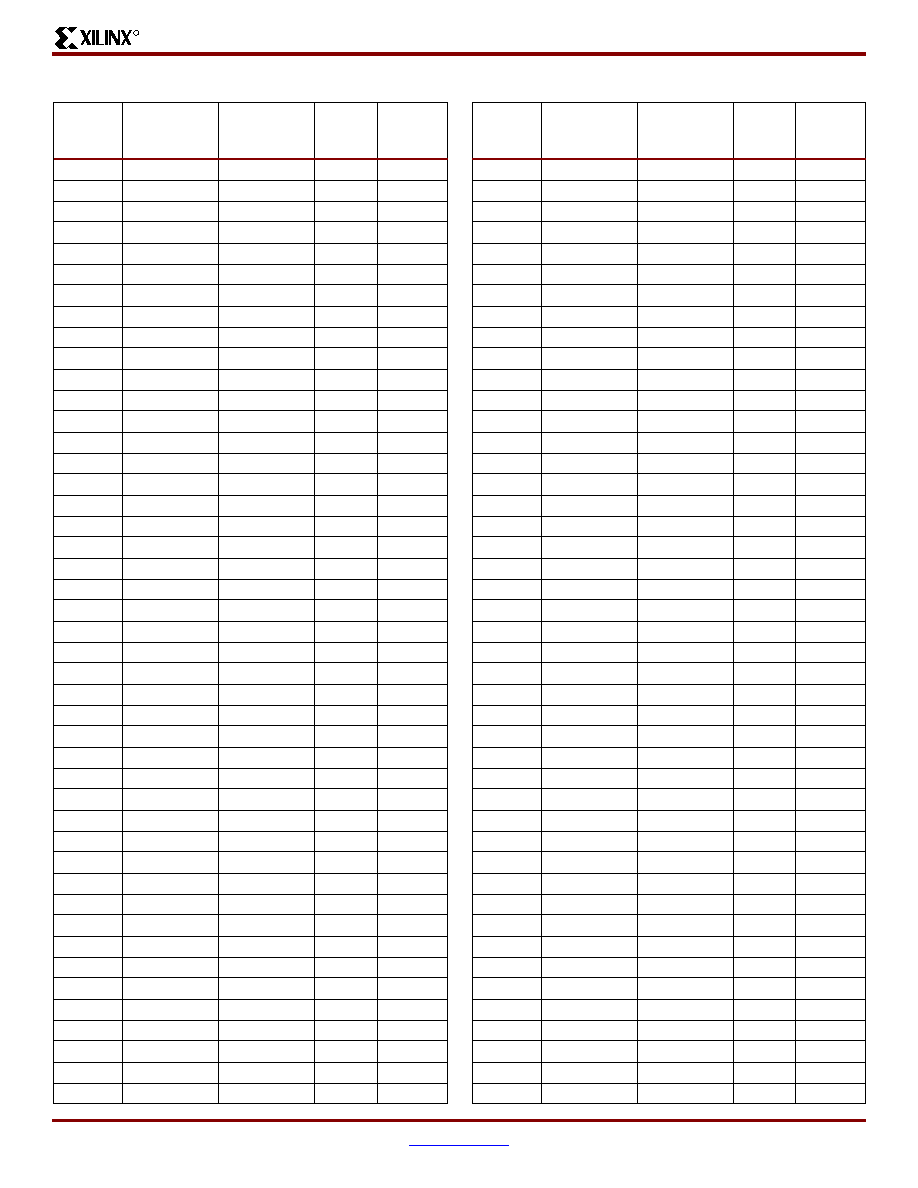

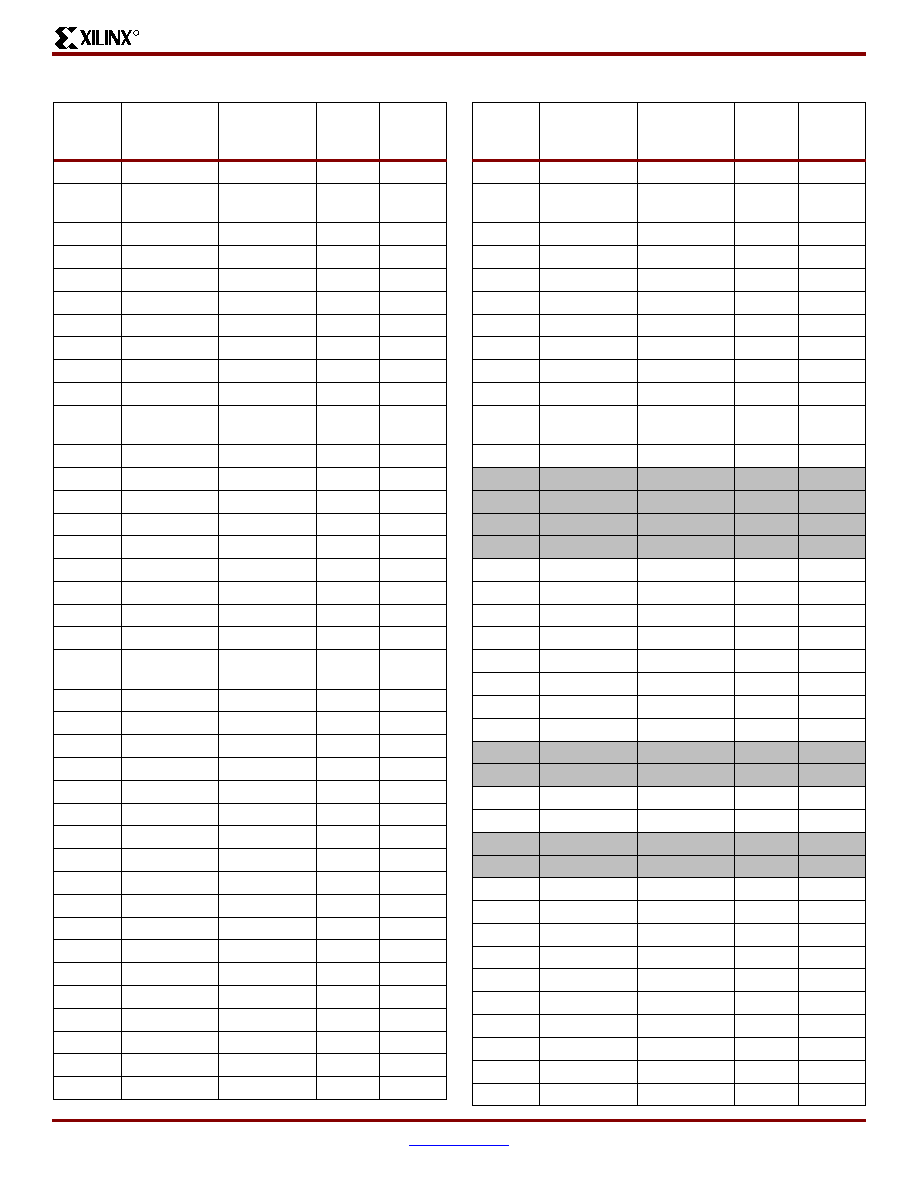

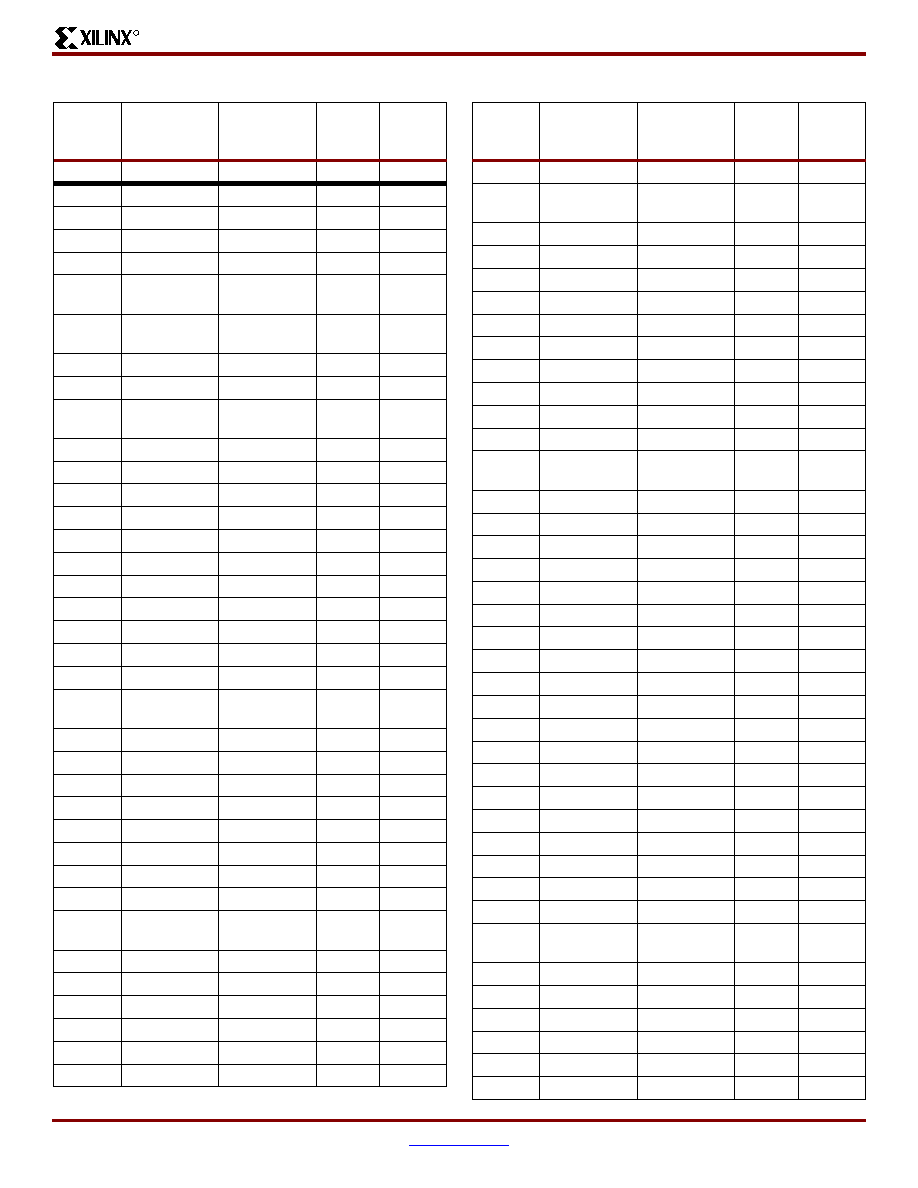

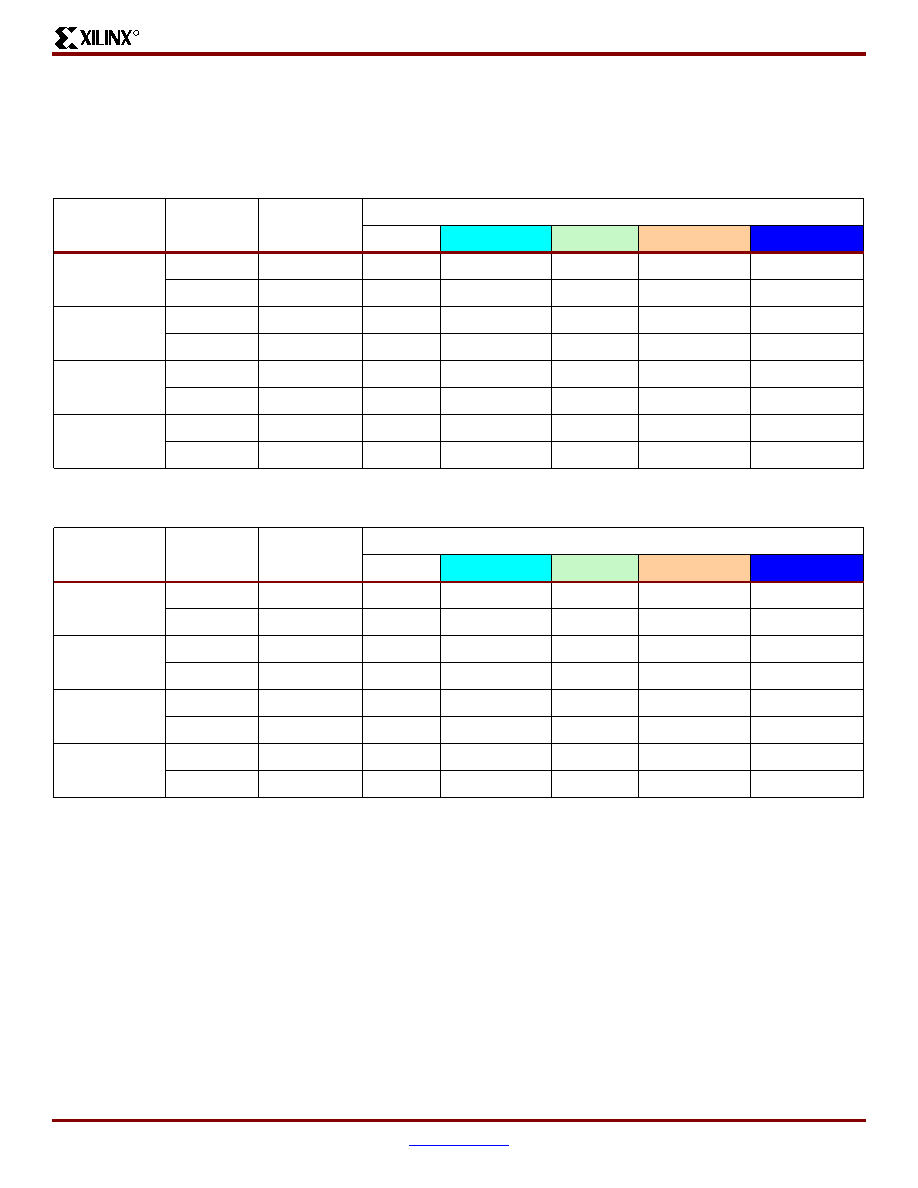

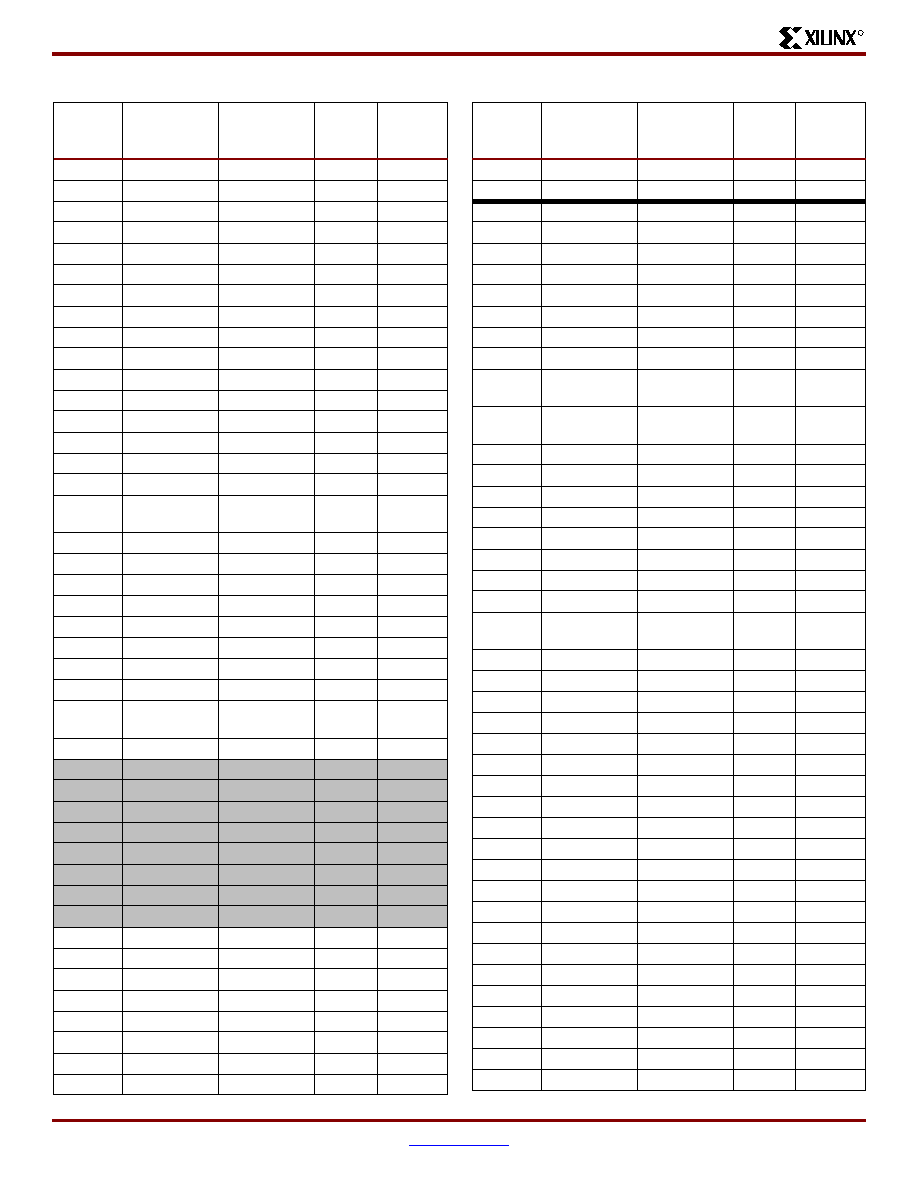

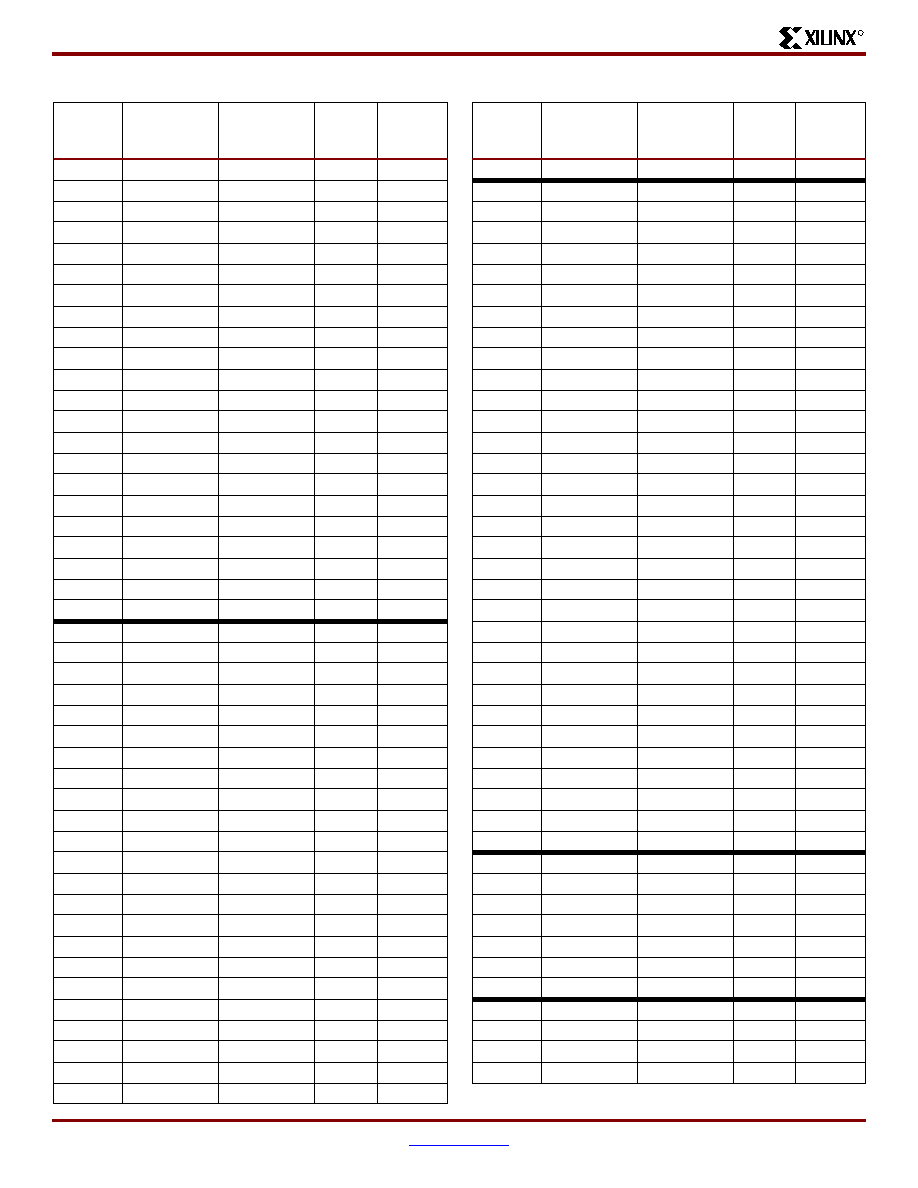

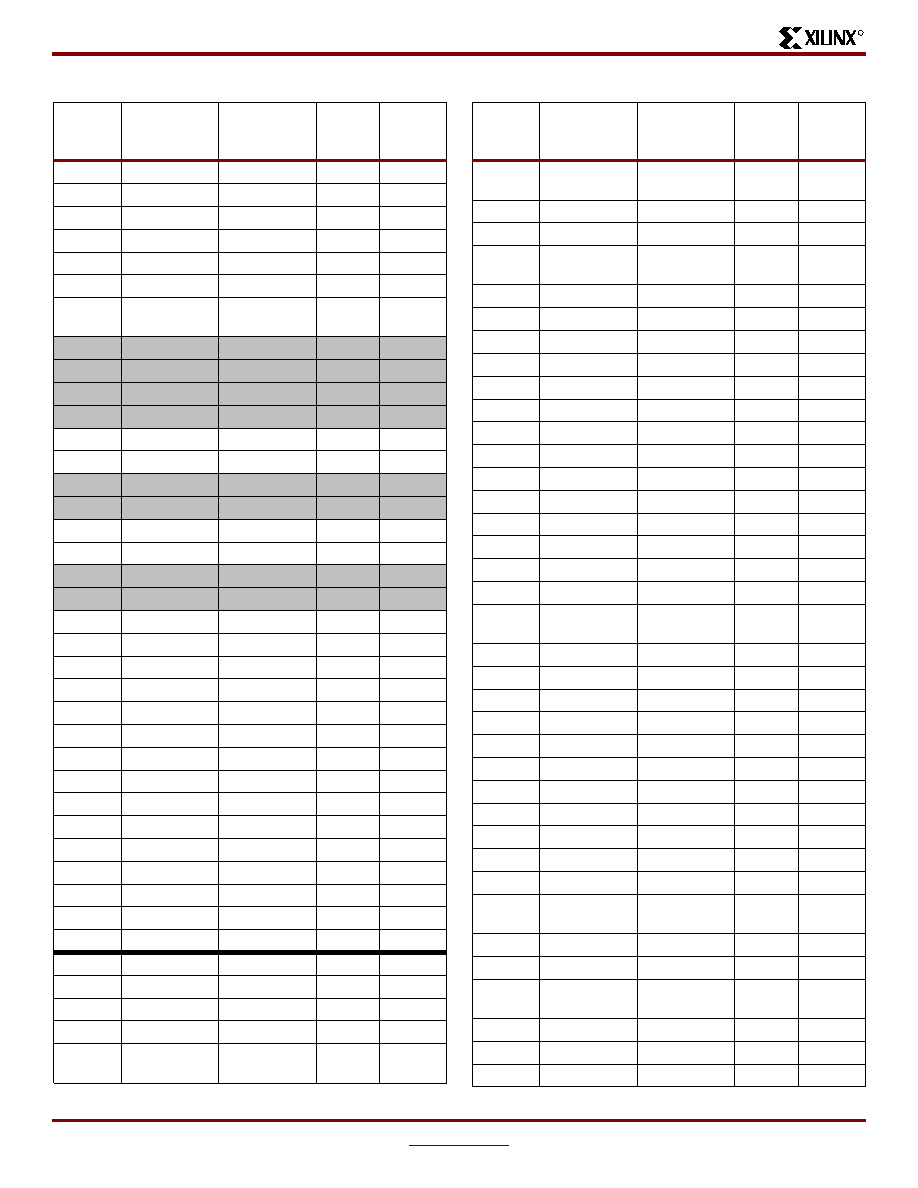

Table 6: DCI I/O Standards

Category of Signal

Standard

Signal Standard

V

CCO

(V)

V

REF

for

Inputs (V)

Termination Type

For

Outputs

For

Inputs

At Output

At Input

Single-Ended

Gunning

Transceiver Logic

GTL_DCI

1.2

1.2

0.8

Single

Single

GTLP_DCI

1.5

1.5

1.0

High-Speed

Transceiver Logic

HSTL_I_DCI

1.5

1.5

0.75

None

Split

HSTL_III_DCI

1.5

1.5

0.9

None

Single

HSTL_I_DCI_18

1.8

1.8

0.9

None

Split

HSTL_II_DCI_18

1.8

1.8

0.9

Split

HSTL_III_DCI_18

1.8

1.8

1.1

None

Single

Low-Voltage CMOS

LVDCI_15

1.5

1.5

-

Controlled impedance

driver

None

LVDCI_18

1.8

1.8

-

LVDCI_25

2.5

2.5

-

LVDCI_33

3.3

3.3

-

LVDCI_DV2_15

1.5

1.5

-

Controlled driver with

half-impedance

LVDCI_DV2_18

1.8

1.8

-

LVDCI_DV2_25

2.5

2.5

-

LVDCI_DV2_33

3.3

3.3

-

Stub Series

Terminated Logic

SSTL18_I_DCI

1.8

1.8

0.9

25-Ohm driver

Split

SSTL2_I_DCI

2.5

2.5

1.25

25-Ohm driver

SSTL2_II_DCI

2.5

2.5

1.25

Split with 25-Ohm driver

Differential

Low-Voltage

Differential

Signalling

LVDS_25_DCI

2.5

2.5

-

None

Split on

each line

of pair

LVDSEXT_25_DCI

2.5

2.5

-

Notes:

1.

Bank 5 of any Spartan-3 device in a VQ100 or TQ144 package does not support DCI signal standards.

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

7

Advance Product Specification

1-800-255-7778

R

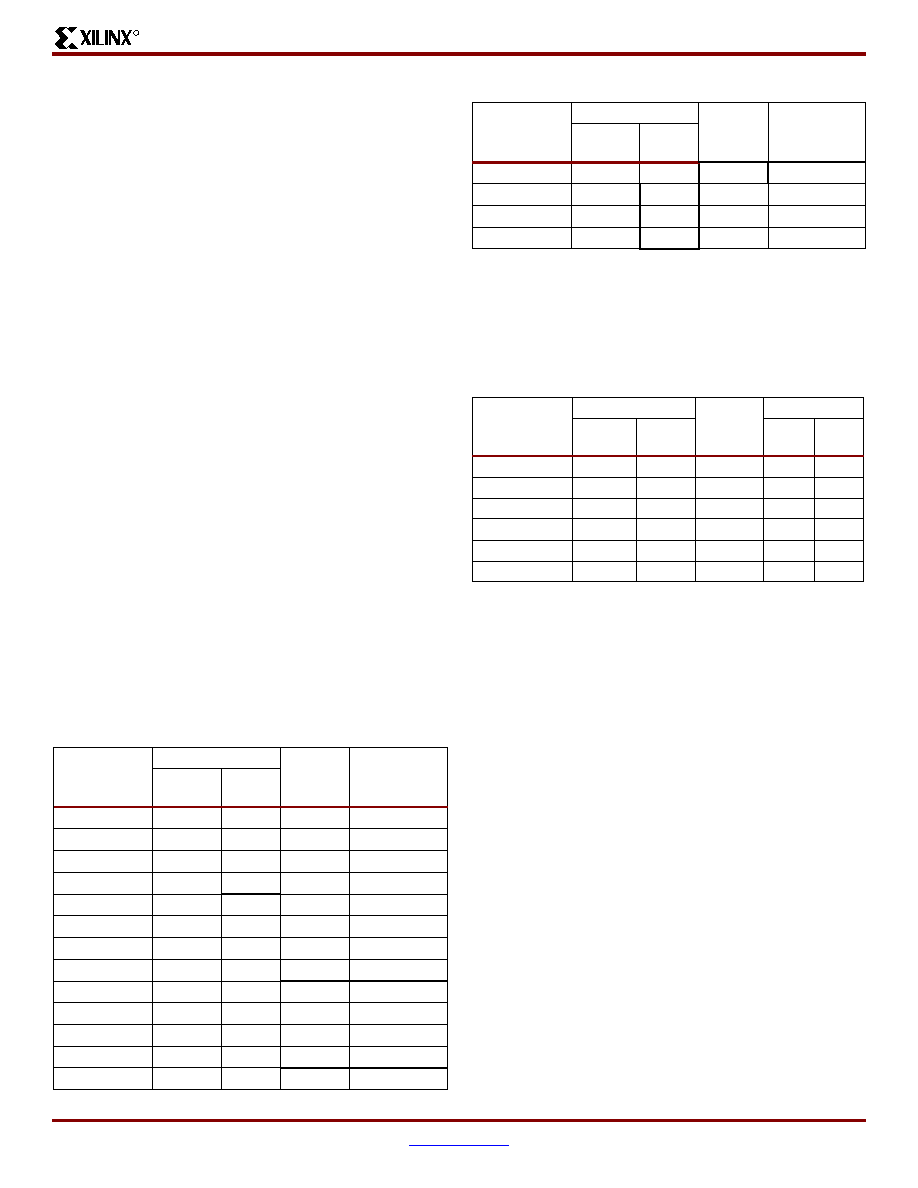

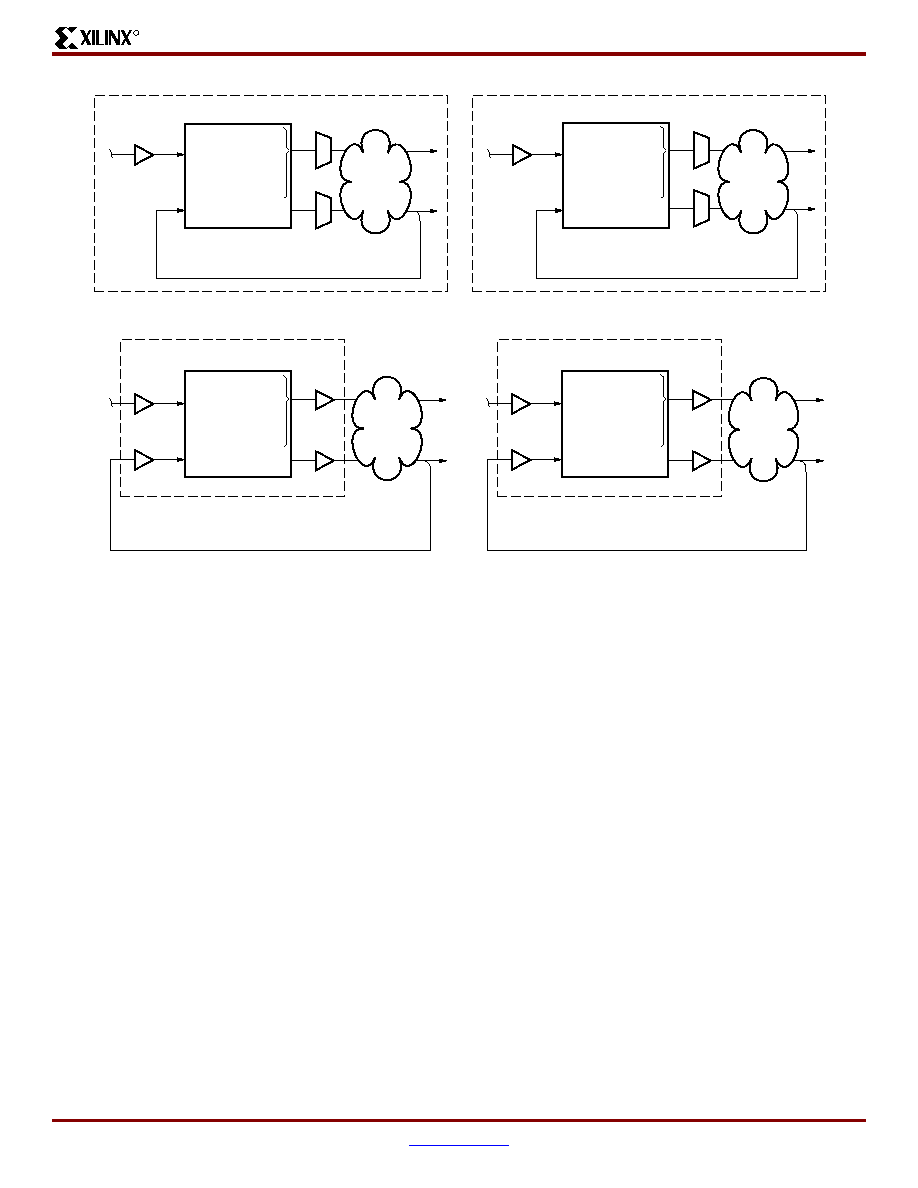

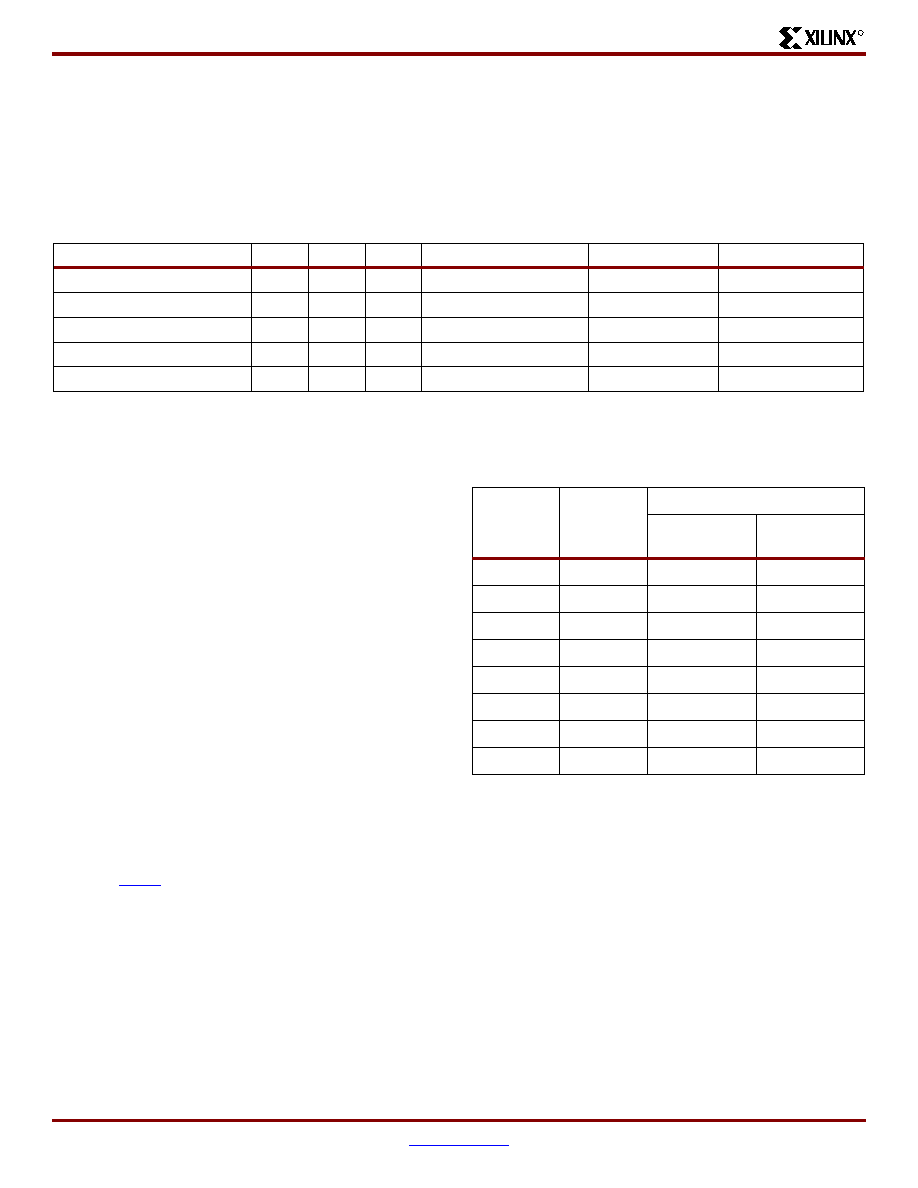

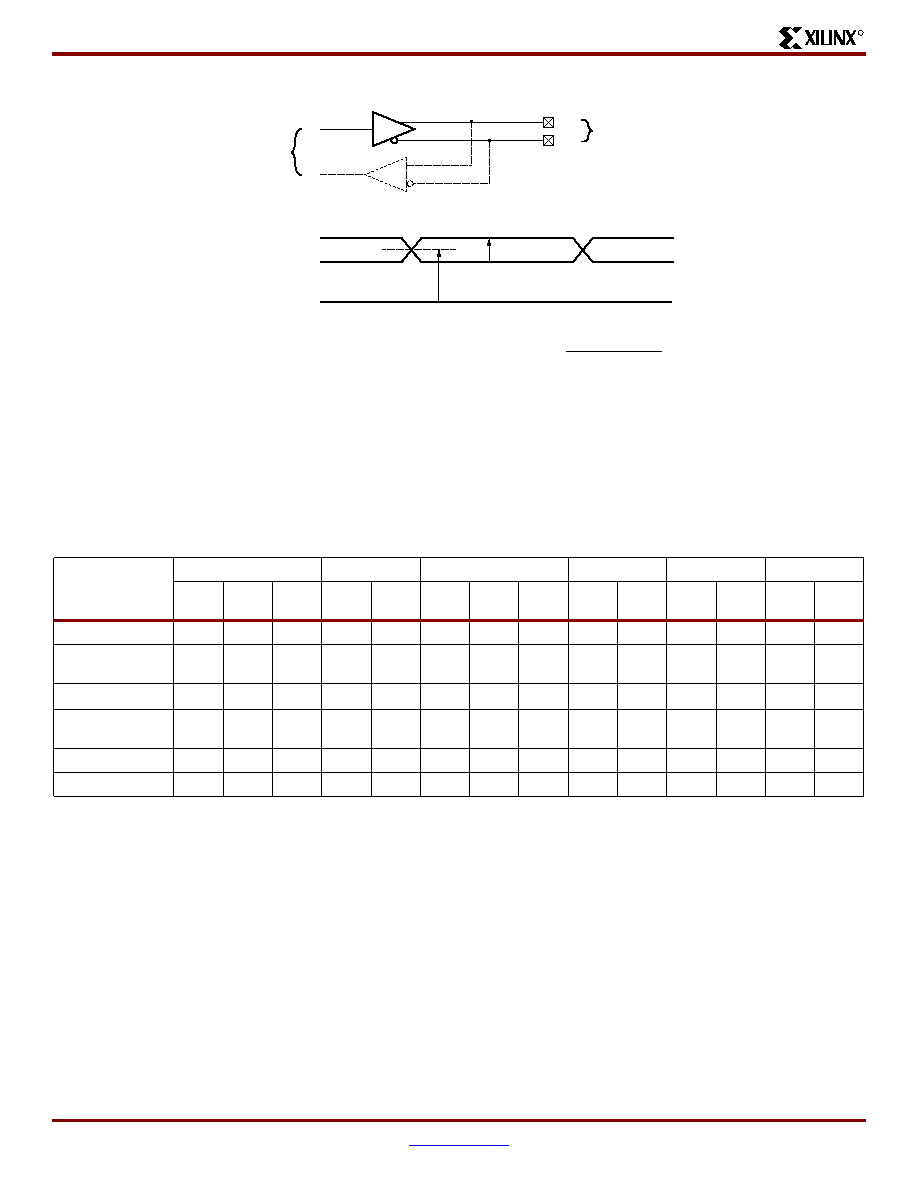

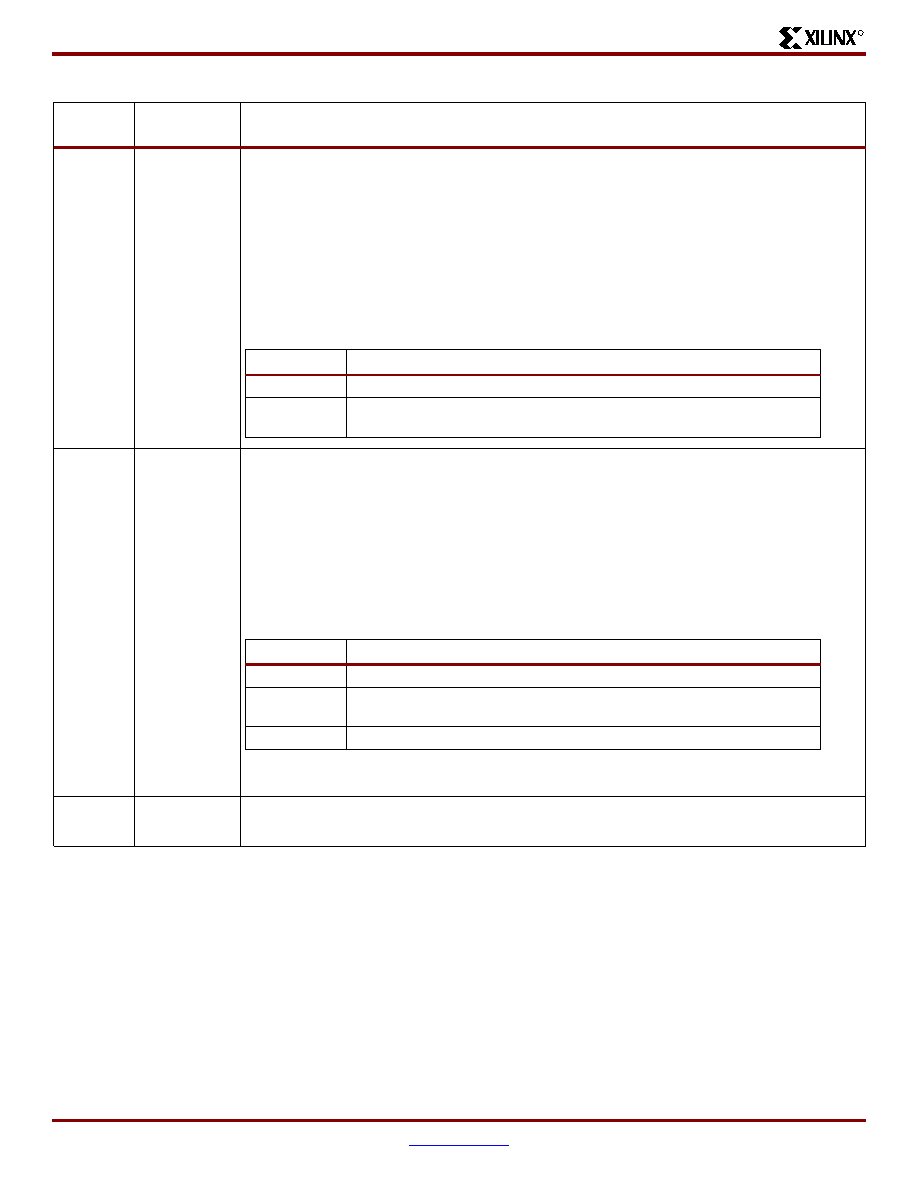

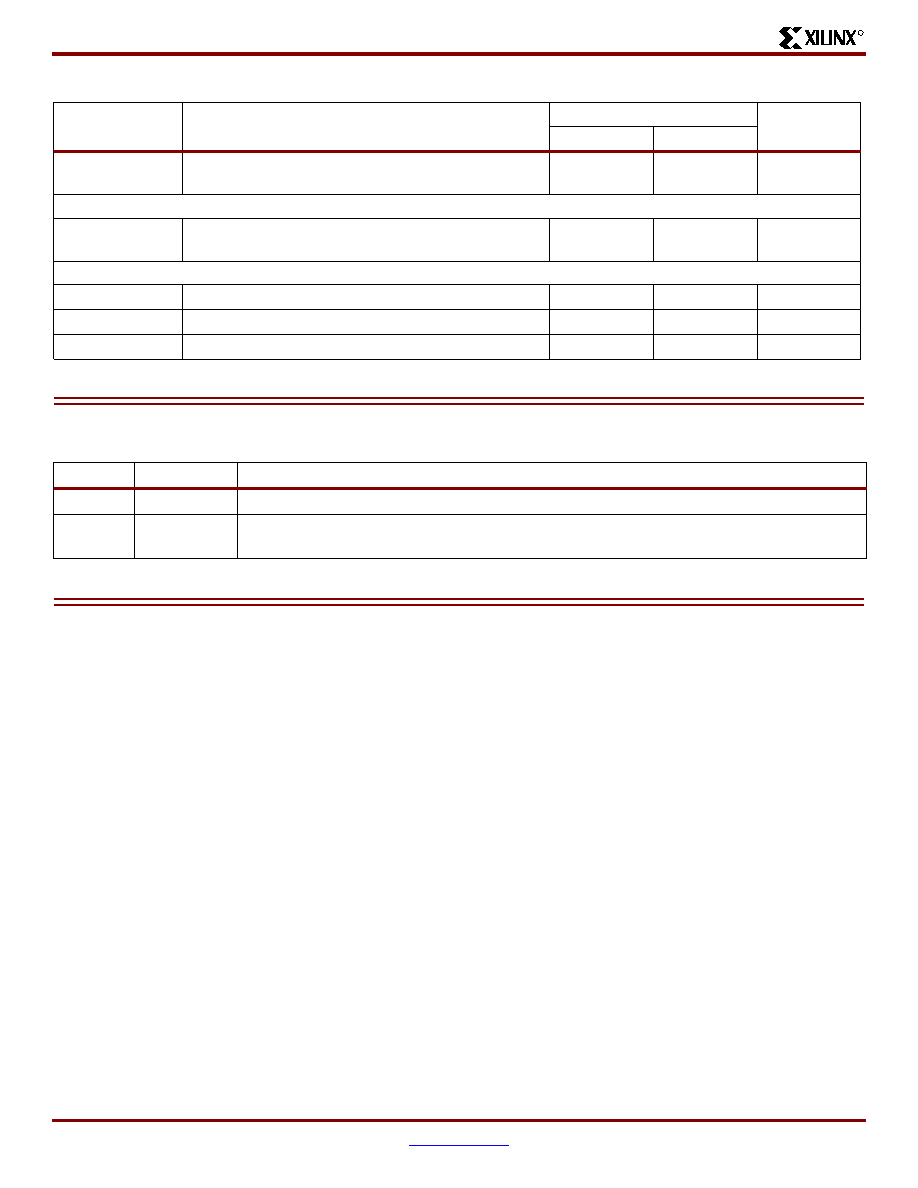

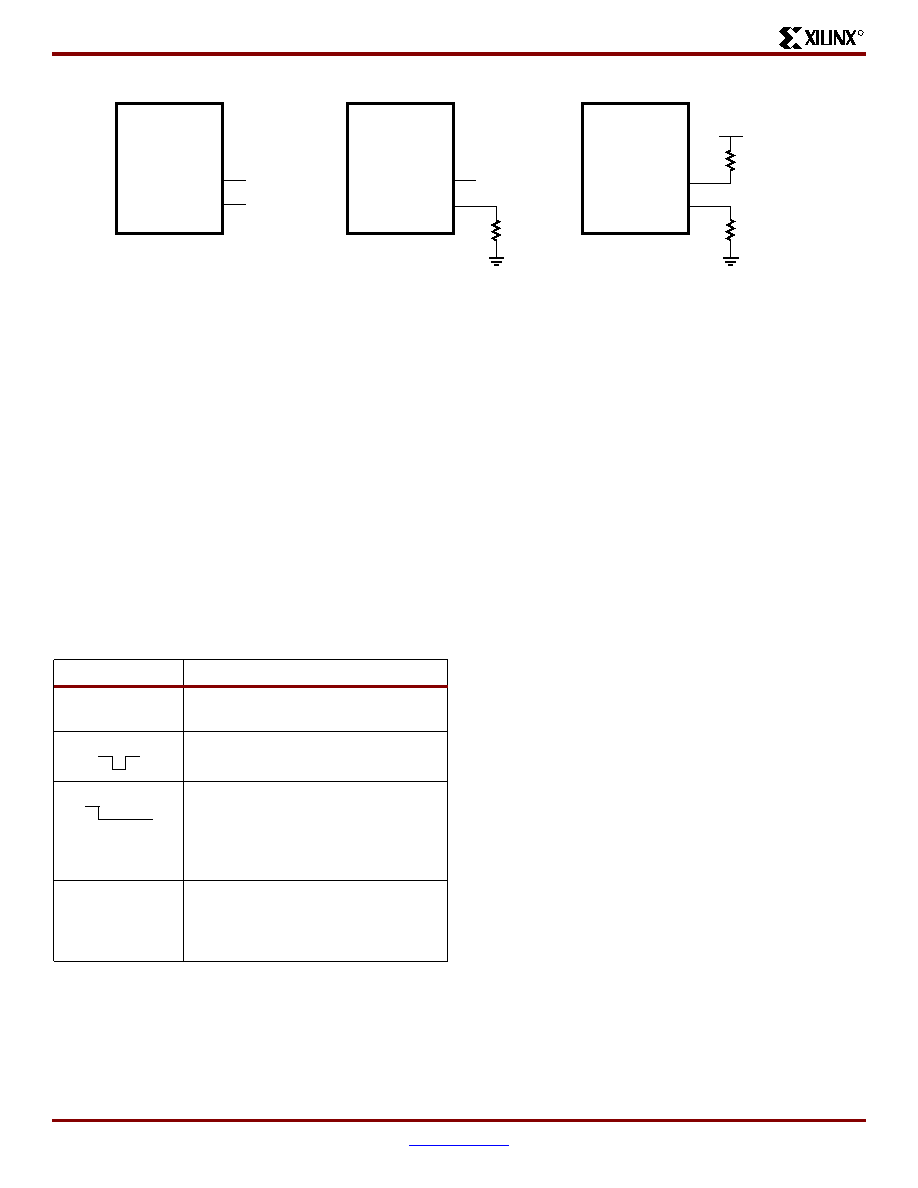

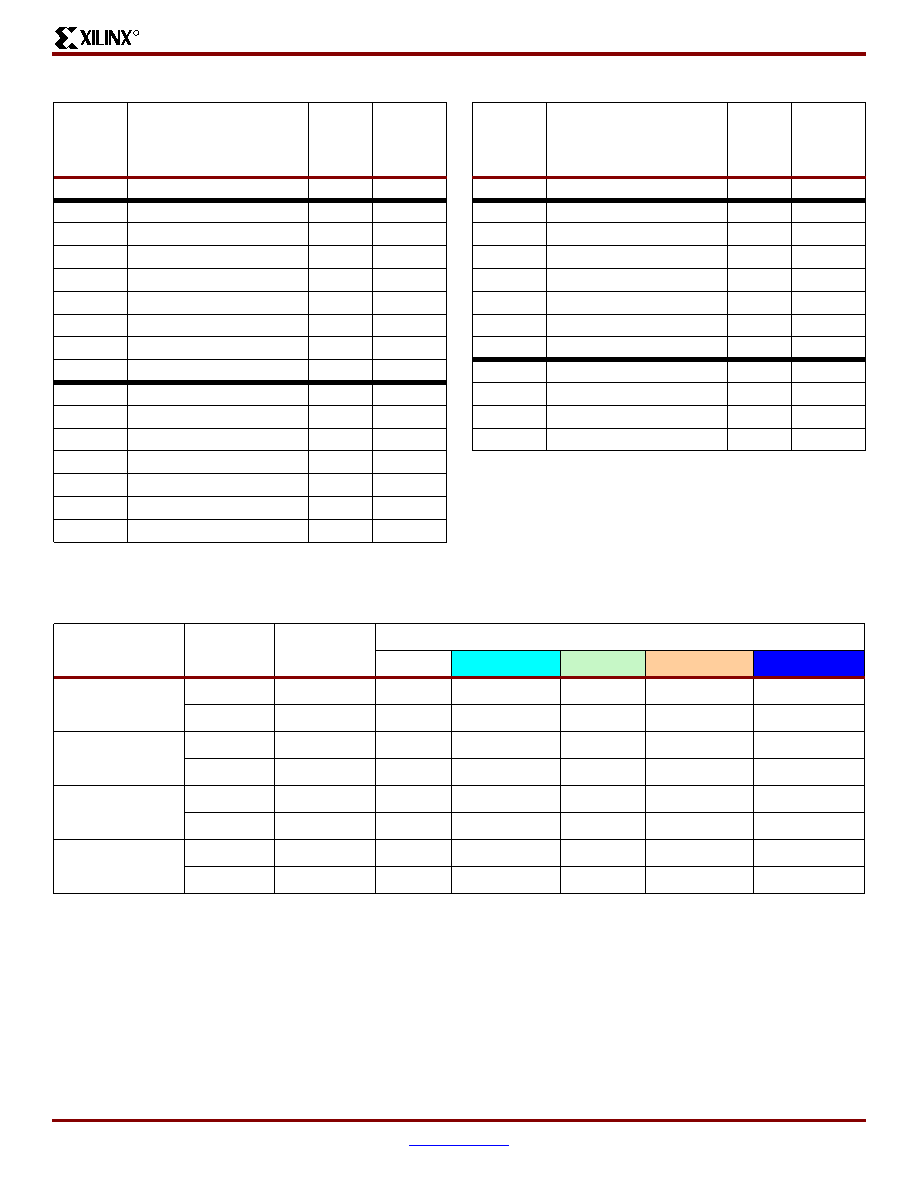

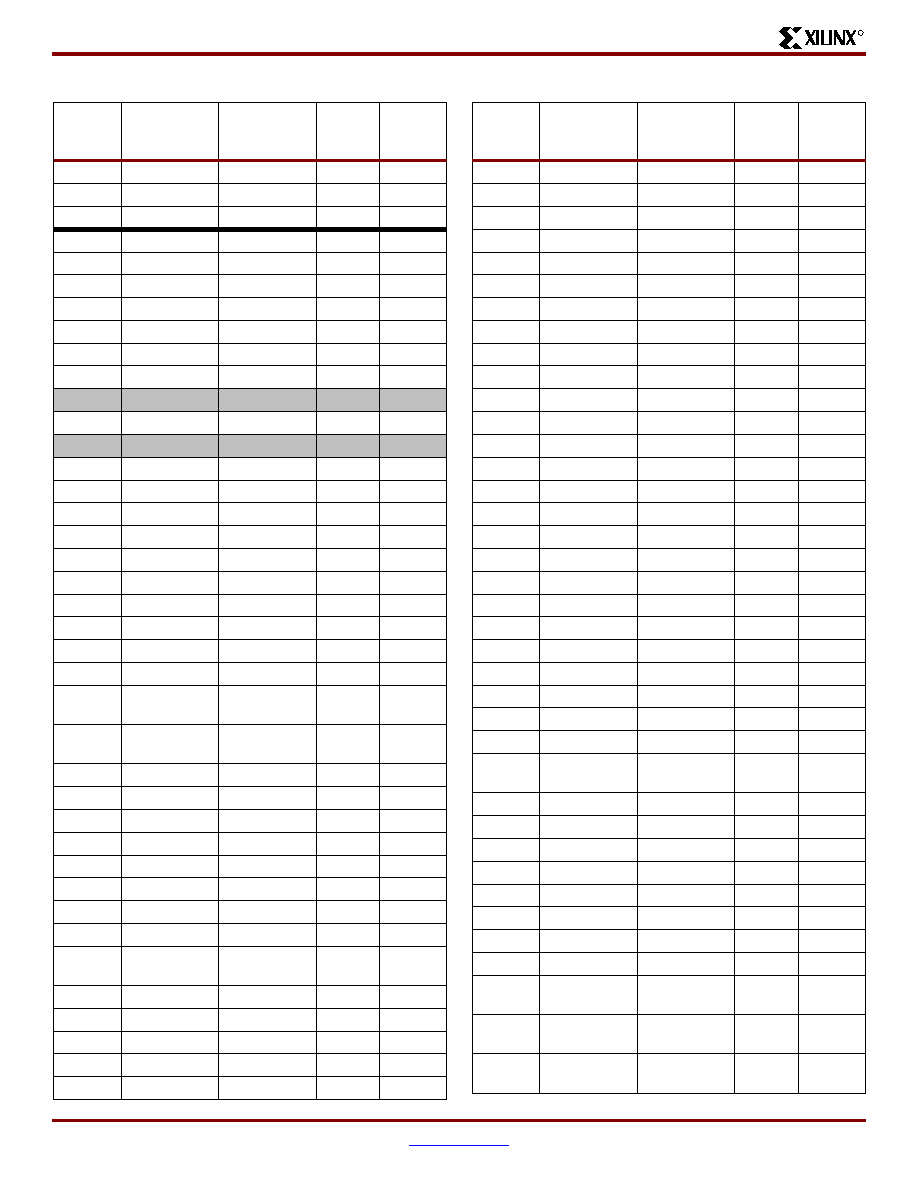

Table 7: DCI Terminations

Termination

Schematic

(1)

I/O Standards

Controlled impedance output driver

LVDCI_15

LVDCI_18

LVDCI_25

LVDCI_33

Controlled output driver with half impedance

LVDCI_DV2_15

LVDCI_DV2_18

LVDCI_DV2_25

LVDCI_DV2_33

Single resistor

GTL_DCI

GTLP_DCI

HSTL_III_DCI

(2)

HSTL_III_DCI_18

(2)

Split resistors

HSTL_I_DCI

(2)

HSTL_I_DCI_18

(2)

HSTL_II_DCI_18

LVDS_25_DCI

LVDSEXT_25_DCI

Split resistors with output driver impedance

fixed to 25

SSTL18_I_DCI

(3)

SSTL2_I_DCI

(3)

SSTL2_II_DCI

Notes:

1.

The value of R is equivalent to the characteristic impedance of the line connected to the I/O. It is also equal to half the value of R

REF

for the DV2 standards and R

REF

for all other DCI standards.

2.

For DCI using HSTL Classes I and III, terminations only go into effect at inputs (not at outputs).

3.

For DCI using SSTL Class I, the split termination only goes into effect at inputs (not at outputs).

Z

0

IOB

R

Z

0

IOB

R/2

R

Z

0

V

CCO

IOB

2R

2R

Z

0

V

CCO

IOB

25

2R

2R

Z

0

V

CCO

IOB

Spartan-3 1.2V FPGA Family: Functional Description

8

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

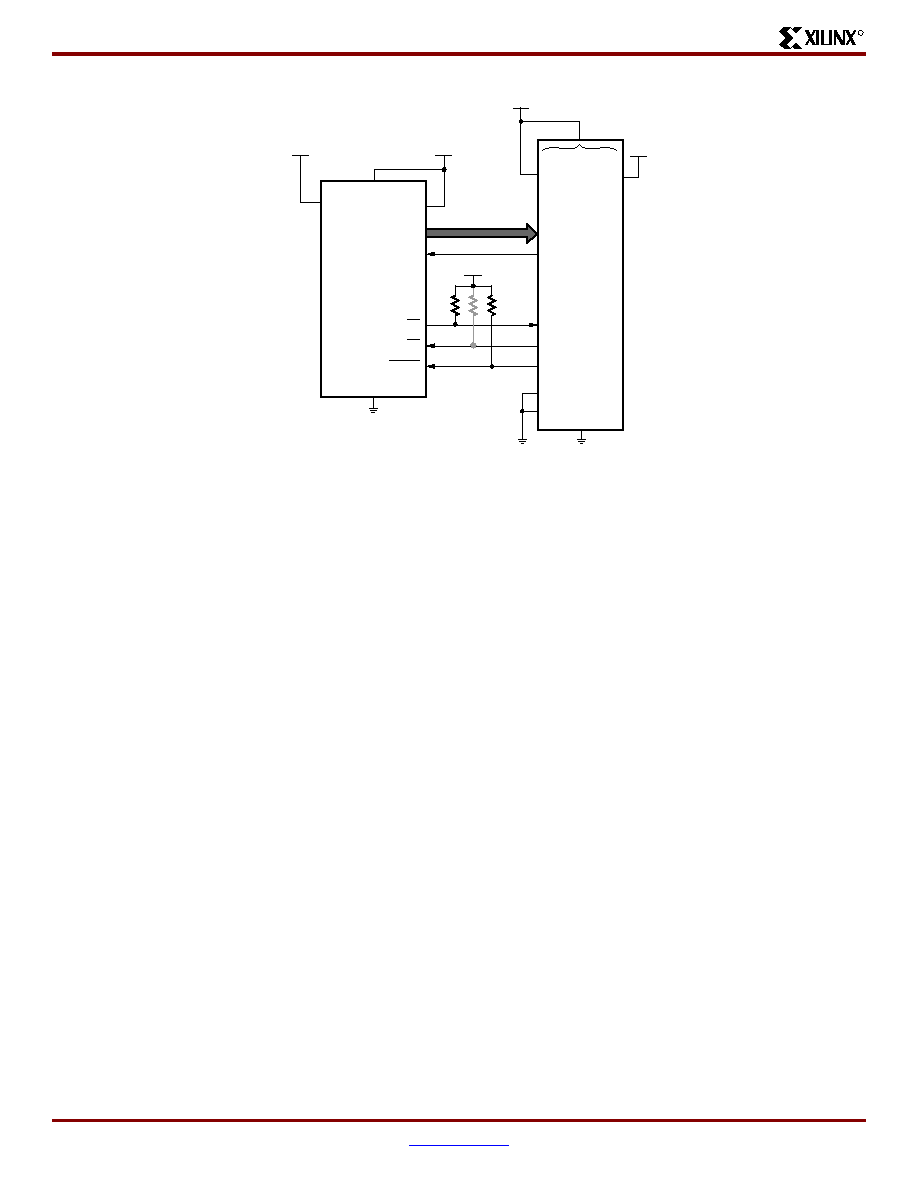

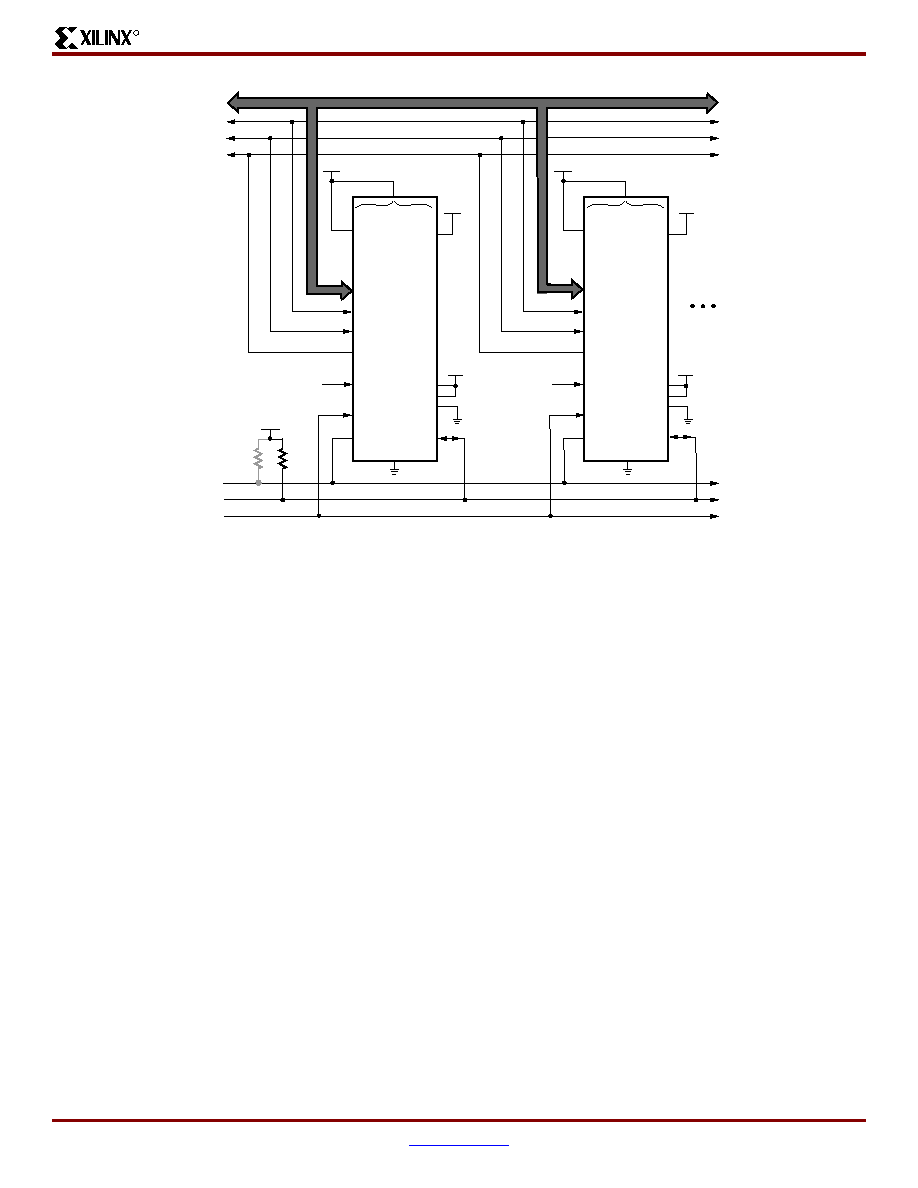

The DCI feature operates independently for each of the

device's eight banks. Each bank has an "N" reference pin

(VRN) and a "P" reference pin, (VRP), to calibrate driver

and termination resistance. Only when using a DCI stan-

dard on a given bank do these two pins function as VRN

and VRP. When not using a DCI standard, the two pins func-

tion as user I/Os. As shown in

Figure 3

, add an external ref-

erence resistor to pull the VRN pin up to V

CCO

and

another

reference resistor to pull the VRP pin down to GND. Both

resistors have the same value -- commonly 50 Ohms --

with one-percent tolerance, which is either the characteristic

impedance of the line or twice that, depending on the DCI

standard in use. Standards having a symbol name that con-

tains the letters "DV2" use a reference resistor value that is

twice the line impedance. DCI adjusts the output driver

impedance to match the reference resistors' value or half

that, according to the standard. DCI always adjusts the

on-chip termination resistors to directly match the reference

resistors' value.

The rules guiding the use of DCI standards on banks are as

follows:

1.

No more than one DCI I/O standard with a Single

Termination is allowed per bank.

2.

No more than one DCI I/O standard with a Split

Termination is allowed per bank.

3.

Single Termination, Split Termination, Controlled-

Impedance Driver, and Controlled-Impedance Driver

with Half Impedance can co-exist in the same bank.

See also

The Organization of IOBs into Banks, page 8

.

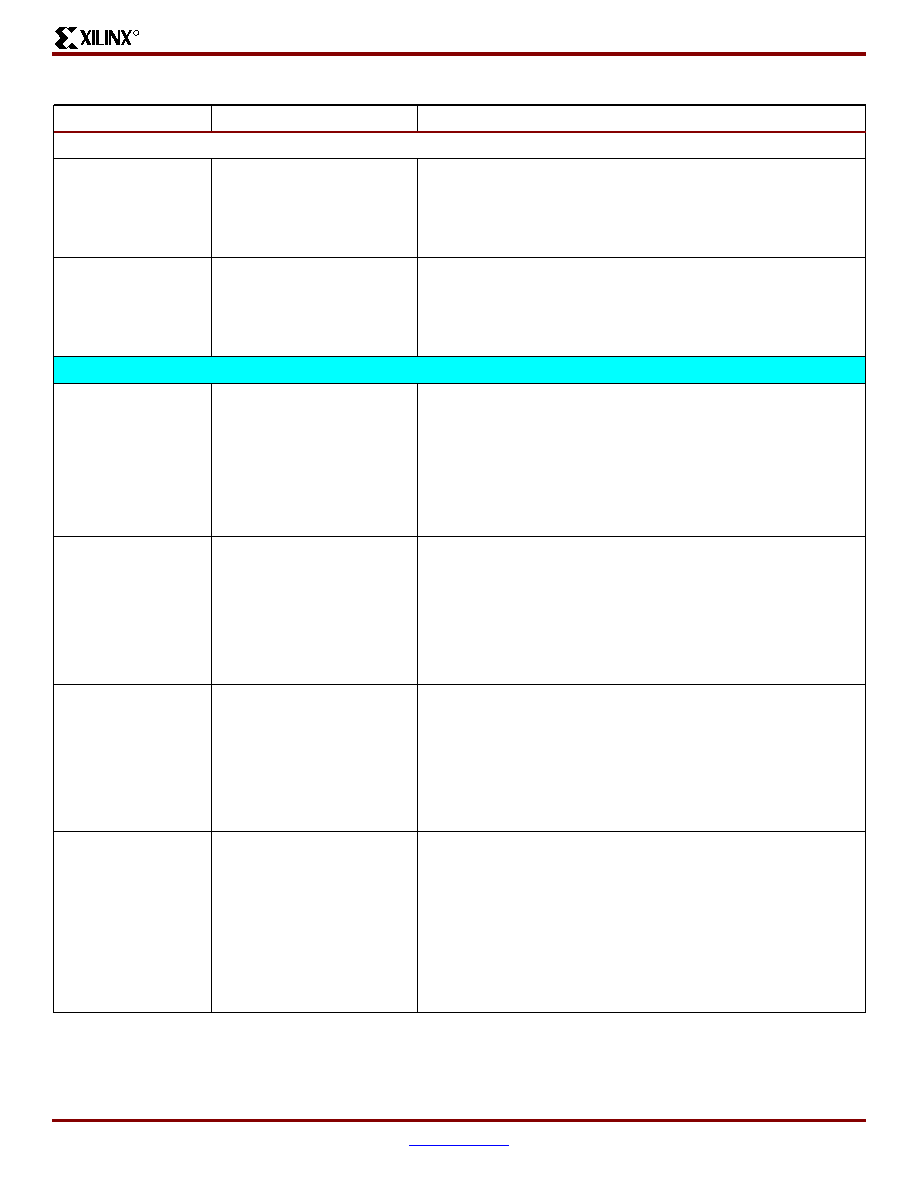

The Organization of IOBs into Banks

IOBs are allocated among eight banks, so that each side of

the device has two banks, as shown in

Figure 4

. For all

packages, each bank has independent V

REF

lines. For

example, V

REF

Bank 3 lines are separate from the V

REF

lines going to all other banks.

For the Very Thin Quad Flat Pack (VQ), Plastic Quad Flat

Pack (PQ), Fine Pitch Thin Ball Grid Array (FT), and Fine

Pitch Ball Grid Array (FG) packages, each bank has dedi-

cated V

CCO

lines. For example, the V

CCO

Bank 7 lines are

separate from the V

CCO

lines going to all other banks. Thus,

Spartan-3 devices in these packages support eight inde-

pendent V

CCO

supplies.

In contrast, the 144-pin Thin Quad Flat Pack (TQ144) pack-

age ties V

CCO

together internally for the pair of banks on

each side of the device. For example, the V

CCO

Bank 0 and

the V

CCO

Bank 1 lines are tied together. The interconnected

bank-pairs are 0/1, 2/3, 4/5, and 6/7. As a result, Spartan-3

devices in the TQ144 package support four independent

V

CCO

supplies.

Spartan-3 Compatibility

Within the Spartan-3 family, all devices are pin-compatible

by package. When the need for future logic resources out-

grows the capacity of the Spartan-3 device in current use, a

larger device in the same package can serve as a direct

replacement. Larger devices may add extra V

REF

and V

CCO

lines to support a greater number of I/Os. In the larger

device, more pins can convert from user I/Os to V

REF

lines.

Also, additional V

CCO

lines are bonded out to pins that were

"not connected" in the smaller device. Thus, it is important

to plan for future upgrades at the time of the board's initial

design by laying out connections to the extra pins.

The Spartan-3 family is not pin-compatible with any previ-

ous Xilinx FPGA family.

Rules Concerning Banks

When assigning I/Os to banks, it is important to follow the

following V

CCO

rules:

1.

Leave no V

CCO

pins unconnected on the FPGA.

2.

Set all V

CCO

lines associated with the (interconnected)

bank to the same voltage level.

3.

The V

CCO

levels used by all standards assigned to the

I/Os of the (interconnected) bank(s) must agree. The

Xilinx development software checks for this. Tables

4

,

5

,

and

6

describe how different standards use the V

CCO

supply.

Figure 3: Connection of Reference Resistors (R

REF

)

DS099-2_04_091602

VCCO

VRN

VRP

One of eight

I/O Banks

R

REF

(1%)

R

REF

(1%)

Figure 4: Spartan-3 I/O Banks (top view)

DS099-2_03_060102

Bank 0

Bank 1

Bank 5

Bank 4

Bank 7

Bank 6

Bank 2

Bank 3

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

9

Advance Product Specification

1-800-255-7778

R

4.

If none of the standards assigned to the I/Os of the

(interconnected) bank(s) use V

CCO

, tie all associated

V

CCO

lines to 2.5V.

5.

In general, apply 2.5V to V

CCO

Bank 4 from power-on to

the end of configuration. Apply the same voltage to

V

CCO

Bank 5 during parallel configuration or a

Readback operation. For information on how to

program the FPGA using 3.3V signals and power, see

the

3.3V-Tolerant Configuration Interface

section.

If any of the standards assigned to the Inputs of the bank

use V

REF

, then observe the following additional rules:

1.

Leave no V

REF

pins unconnected on any bank.

2.

Set all V

REF

lines associated with the bank to the same

voltage level.

3.

The V

REF

levels used by all standards assigned to the

Inputs of the bank must agree. The Xilinx development

software checks for this. Tables

4

and

6

describe how

different standards use the V

REF

supply.

If none of the standards assigned to the Inputs of a bank

use V

REF

for biasing input switching thresholds, all associ-

ated V

REF

pins function as User I/Os.

Exceptions to Banks Supporting I/O

Standards

Bank 5 of any Spartan-3 device in a VQ100 or TQ144 pack-

age does not support DCI signal standards. In this case,

bank 5 has neither VRN nor VRP pins.

Furthermore, banks 4 and 5 of any Spartan-3 device in a

VQ100 package do not support signal standards using

V

REF

(see

Table 4

). In this case, the two banks do not have

any V

REF

pins.

Supply Voltages for the IOBs

Three different supplies power the IOBs:

1.

The V

CCO

supplies, one for each of the FPGA's I/O

banks, power the output drivers, except when using the

GTL and GTLP signal standards. The voltage on the

V

CCO

pins determines the voltage swing of the output

signal.

2.

V

CCINT

is the main power supply for the FPGA's internal

logic.

3.

The V

CCAUX

is an auxiliary source of power, primarily to

optimize the performance of various FPGA functions

such as I/O switching.

The I/Os During Power-On, Configuration, and

User Mode

With no power applied to the FPGA, all I/Os are in a

high-impedance state. The V

CCINT

(1.2V), V

CCAUX

(2.5V),

and V

CCO

supplies may be applied in any order. Before

power-on can finish, V

CCINT

, V

CCO

Bank 4, and V

CCAUX

must have reached their respective minimum recom-

mended operating levels (see

Table 2

in Module 3:

DC and

Switching Characteristics

). At this time, all I/O drivers

also will be in a high-impedance state. V

CCO

Bank 4,

V

CCINT

, and V

CCAUX

serve as inputs to the internal

Power-On Reset circuit (POR).

A Low level applied to HSWAP_EN input enables weak

pull-up resistors on User I/Os from power-on throughout

configuration. A High level on HSWAP_EN disables the

pull-up resistors, allowing the I/Os to float. As soon as

power is applied, the FPGA begins initializing its configura-

tion memory. At the same time, the FPGA internally asserts

the Global Set-Reset (GSR), which asynchronously resets

all IOB storage elements to a Low state.

Upon the completion of initialization, INIT_B goes High,

sampling the M0, M1, and M2 inputs to determine the con-

figuration mode. At this point, the configuration data is

loaded into the FPGA. The I/O drivers remain in a

high-impedance state (with or without pull-up resistors, as

determined by the HSWAP_EN input) throughout configura-

tion.

The Global Three State (GTS) net is released during

Start-Up, marking the end of configuration and the begin-

ning of design operation in the User mode. At this point,

those I/Os to which signals have been assigned go active

while all unused I/Os remain in a high-impedance state. The

release of the GSR net, also part of Start-up, leaves the IOB

registers in a Low state by default, unless the loaded design

reverses the polarity of their respective RS inputs.

In User mode, all weak, internal pull-up resistors on the I/Os

are disabled and HSWAP_EN becomes a "don't care" input.

If it is desirable to have weak pull-up or pull-down resistors

on I/Os carrying signals, the appropriate symbol -- e.g.,

PULLUP, PULLDOWN -- must be placed at the appropriate

pads in the design. The Bitstream Generator (Bitgen) option

UnusedPin available in the Xilinx development software

determines whether unused I/Os collectively have pull-up

resistors, pull-down resistors, or no resistors in User mode.

Spartan-3 1.2V FPGA Family: Functional Description

10

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

.

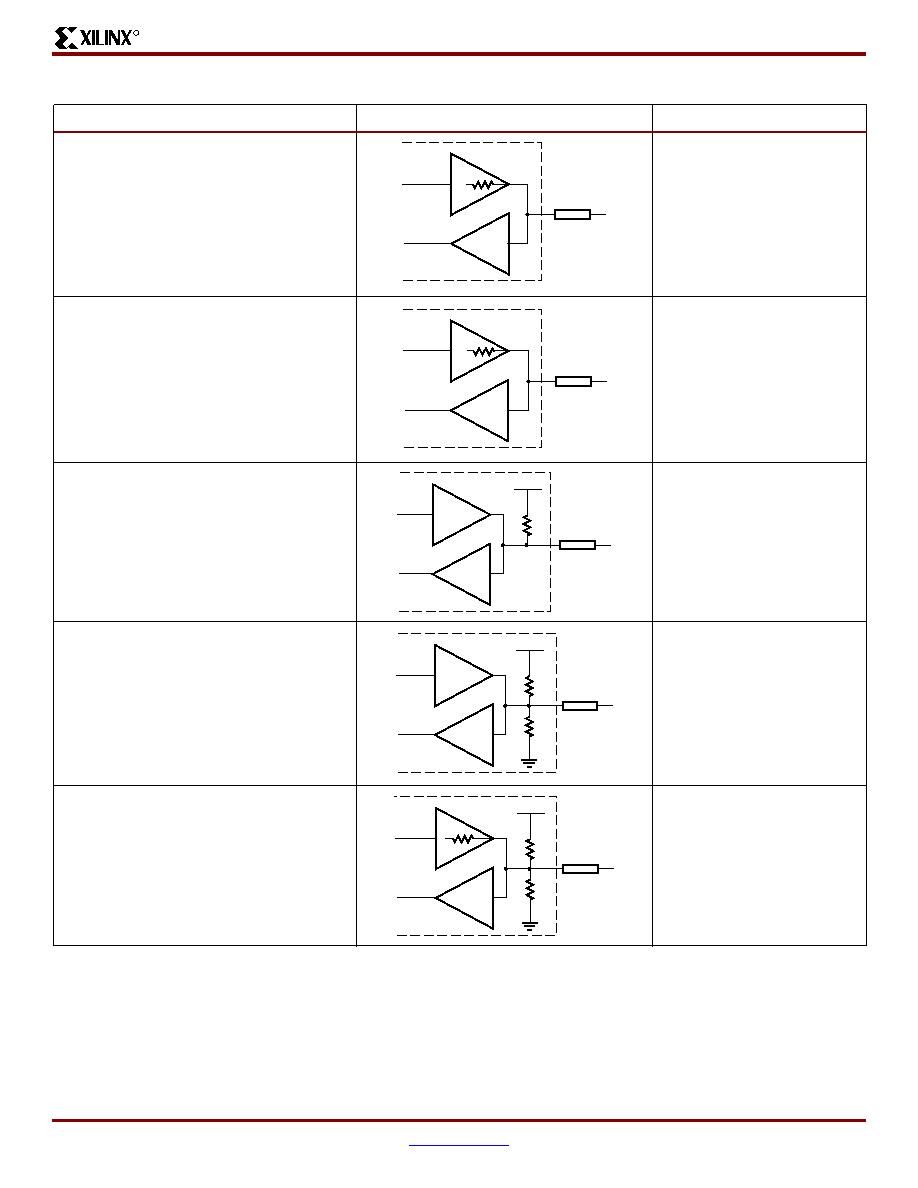

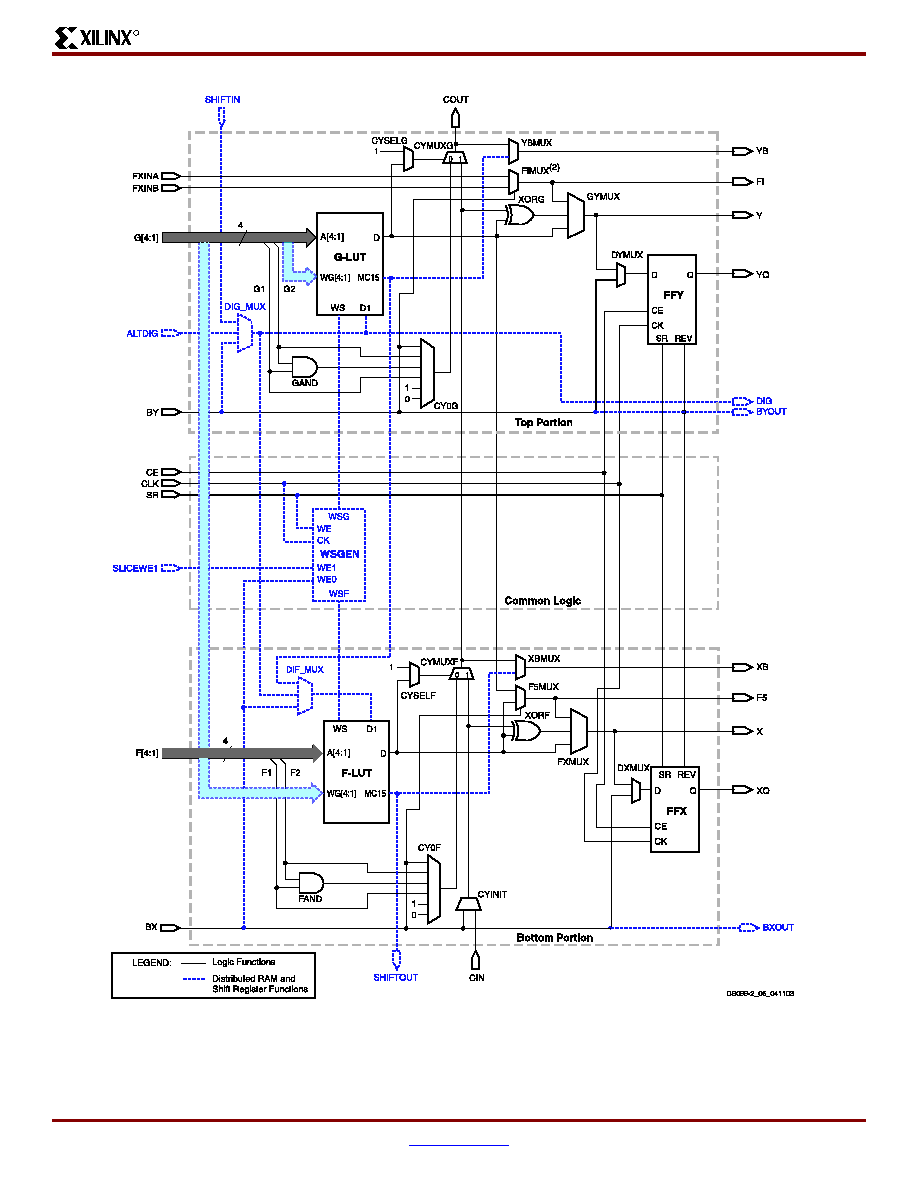

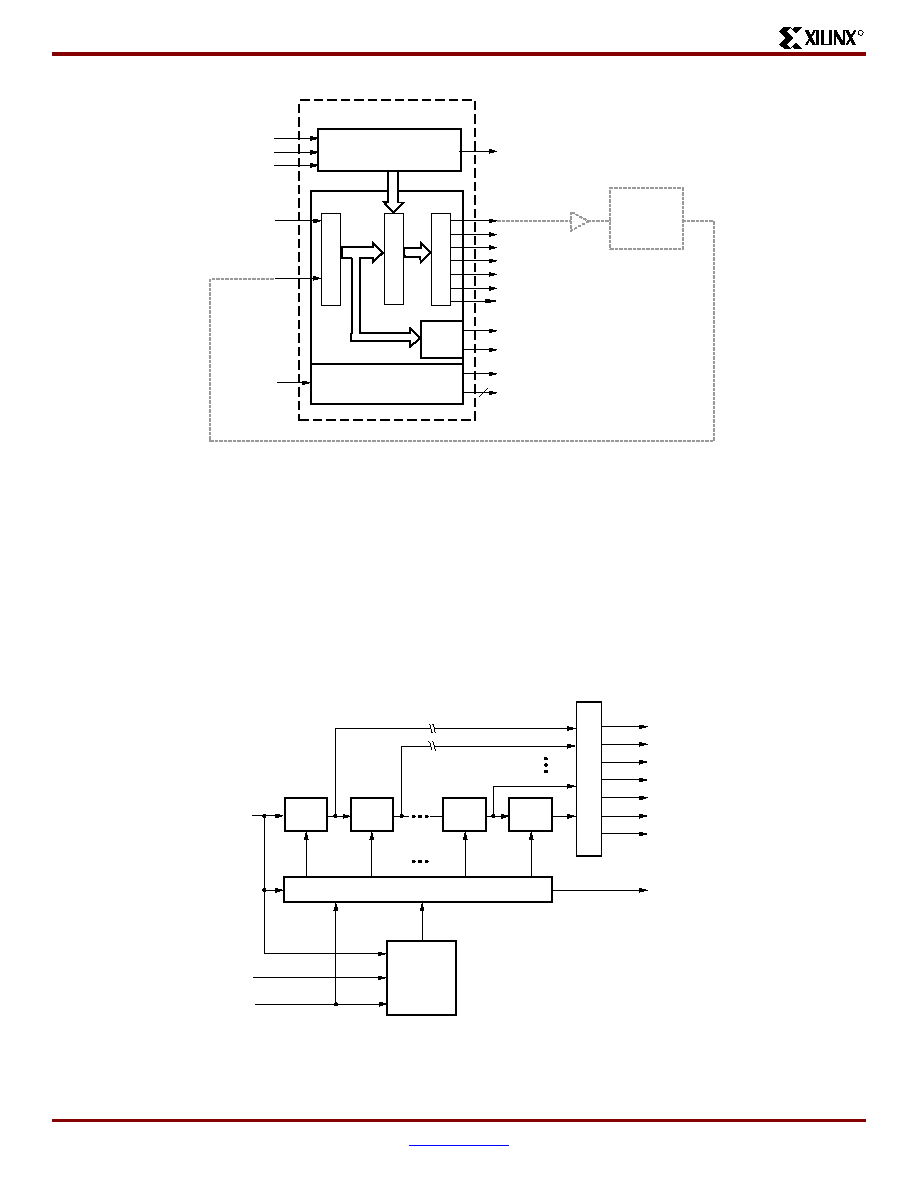

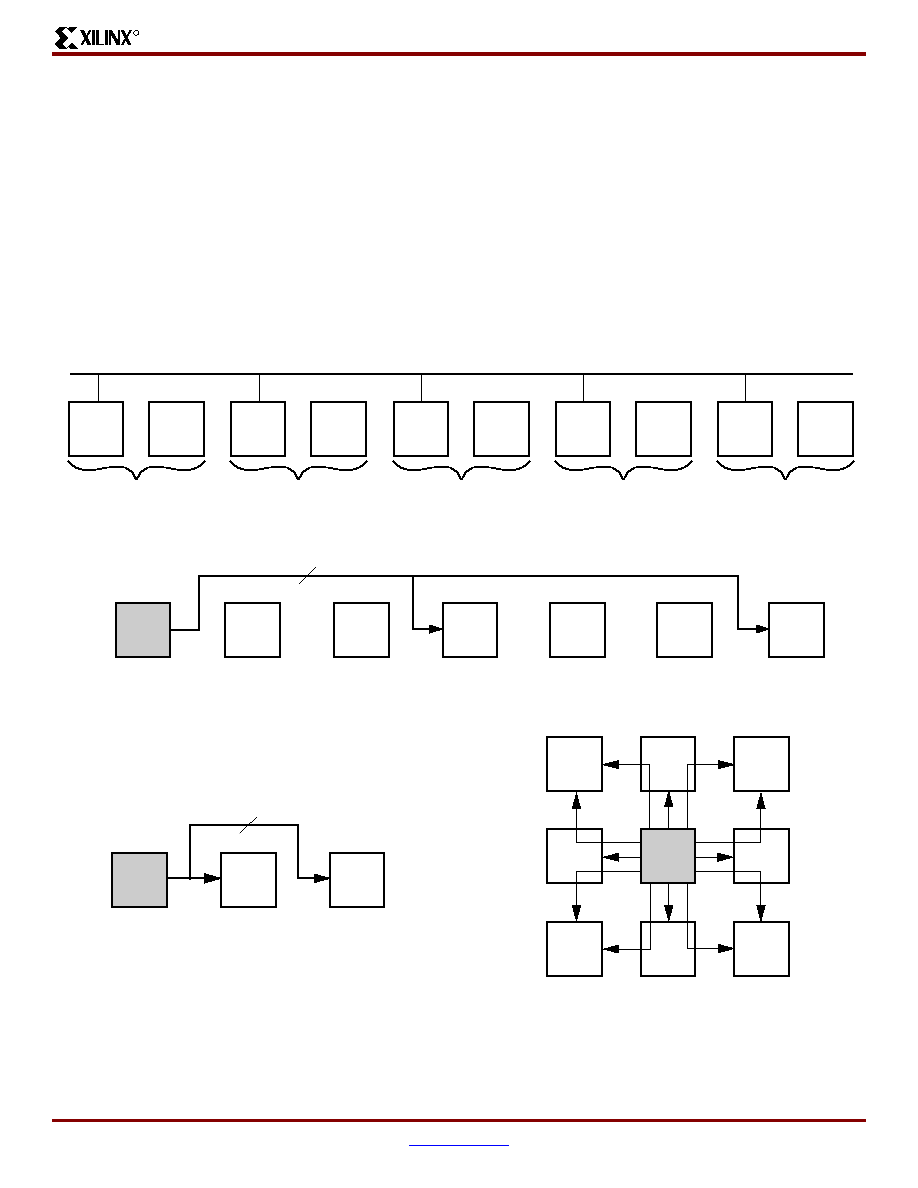

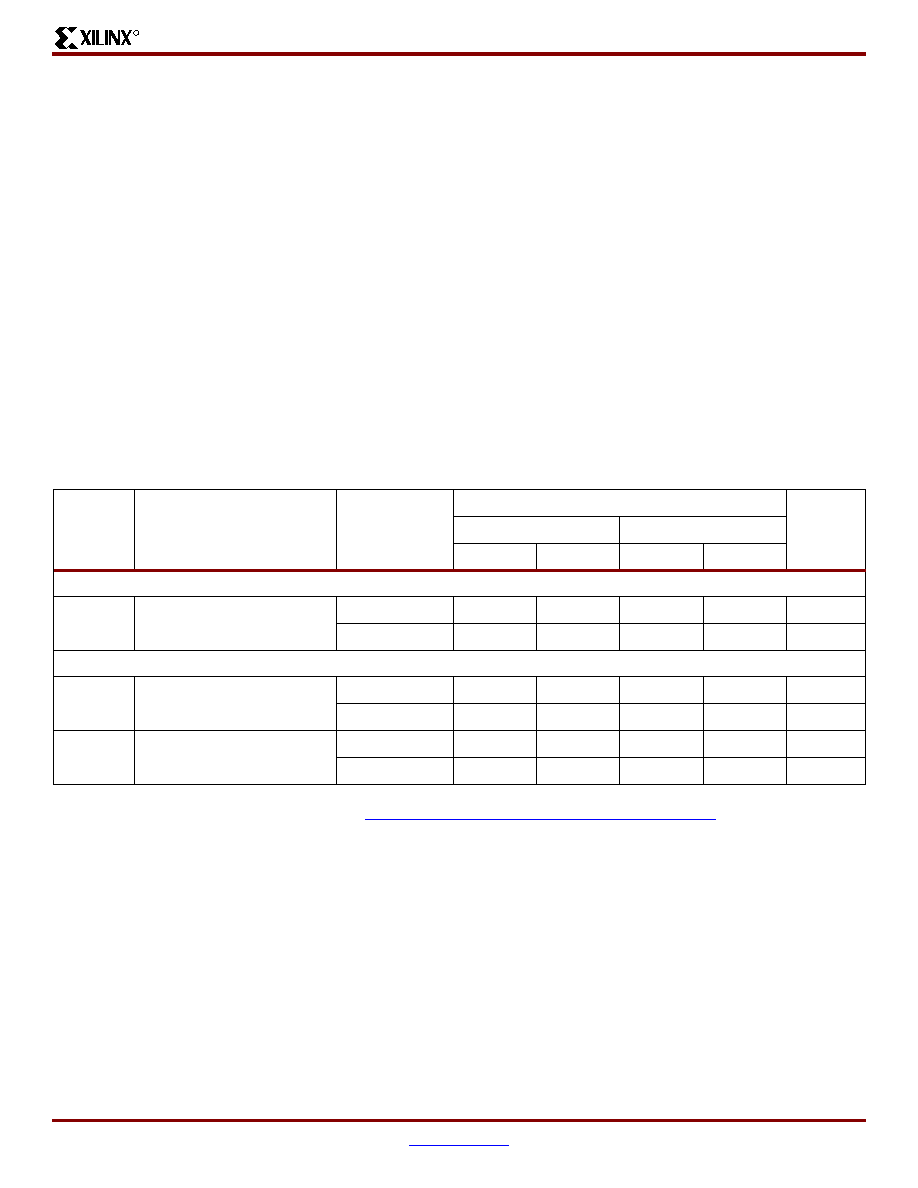

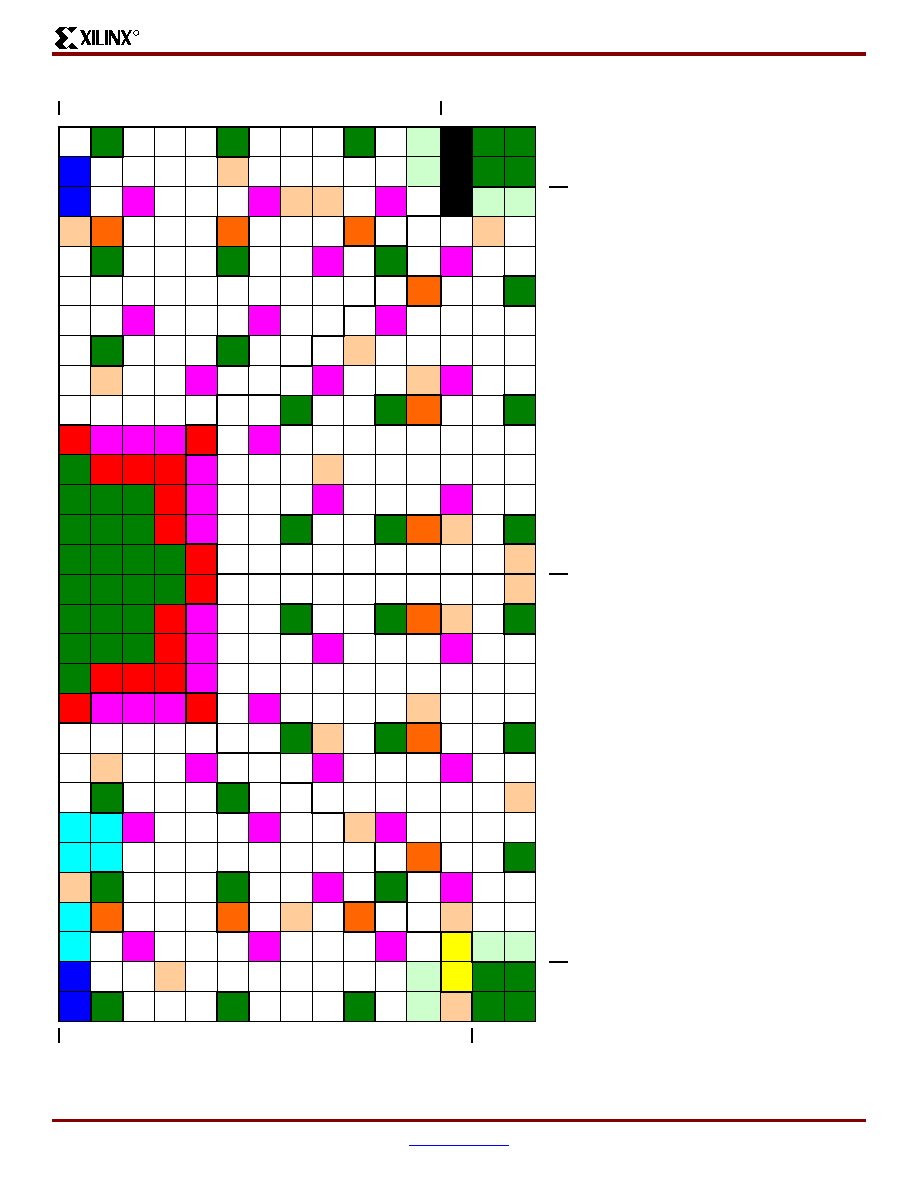

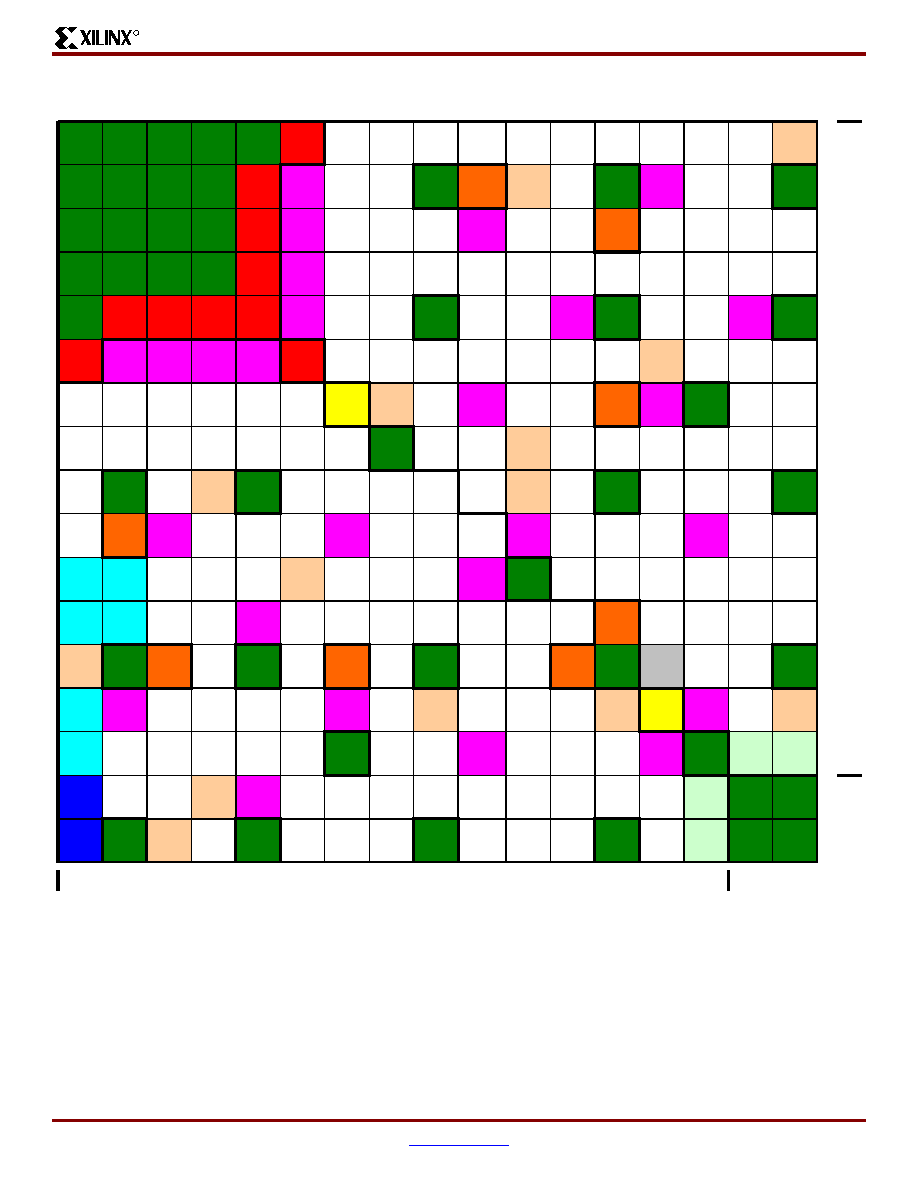

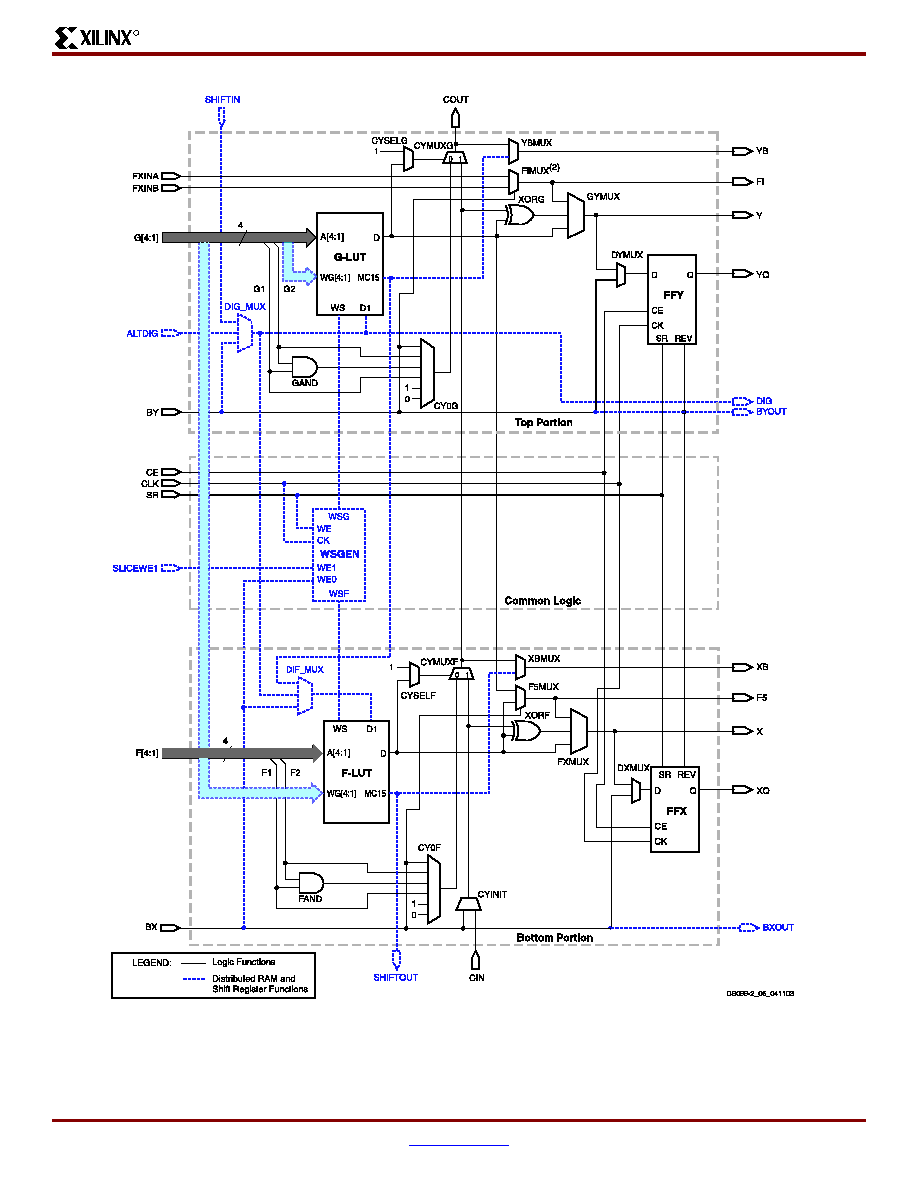

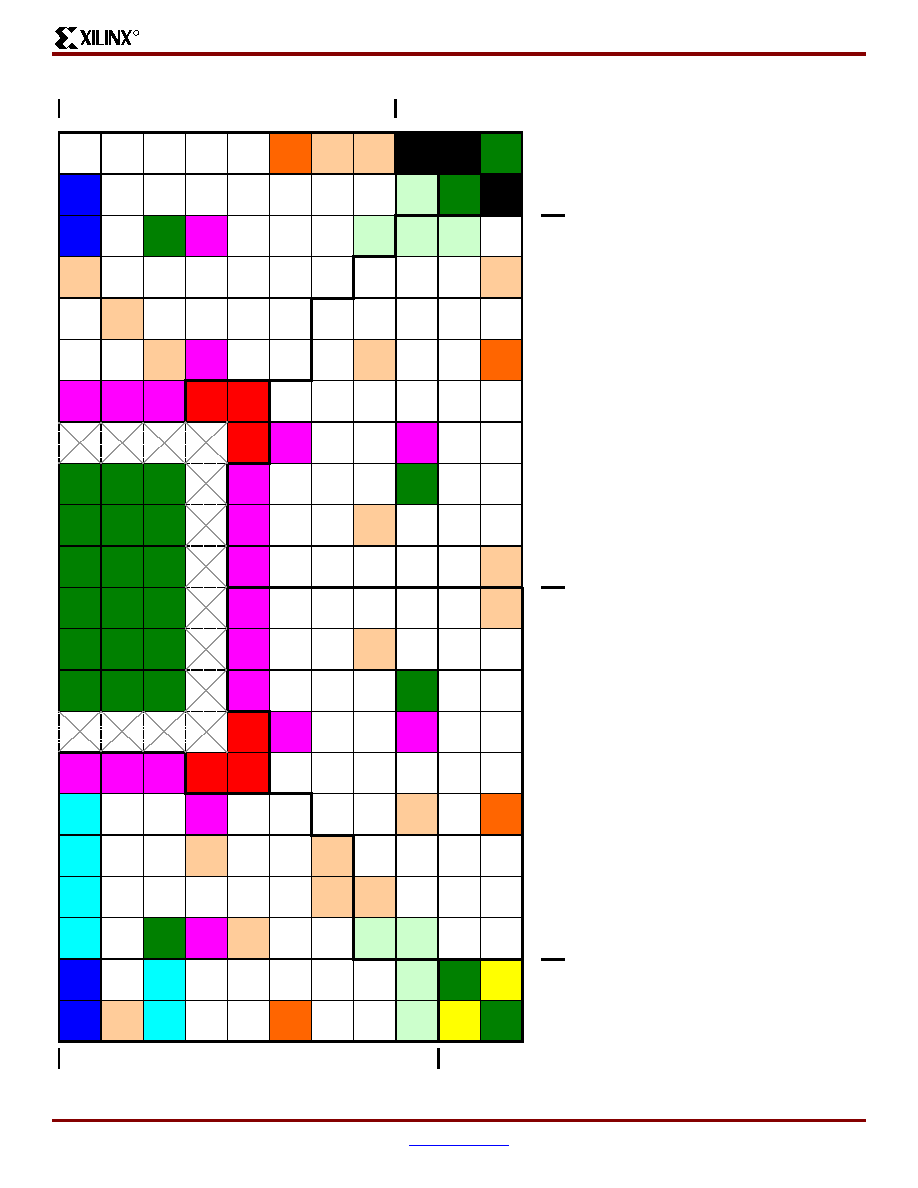

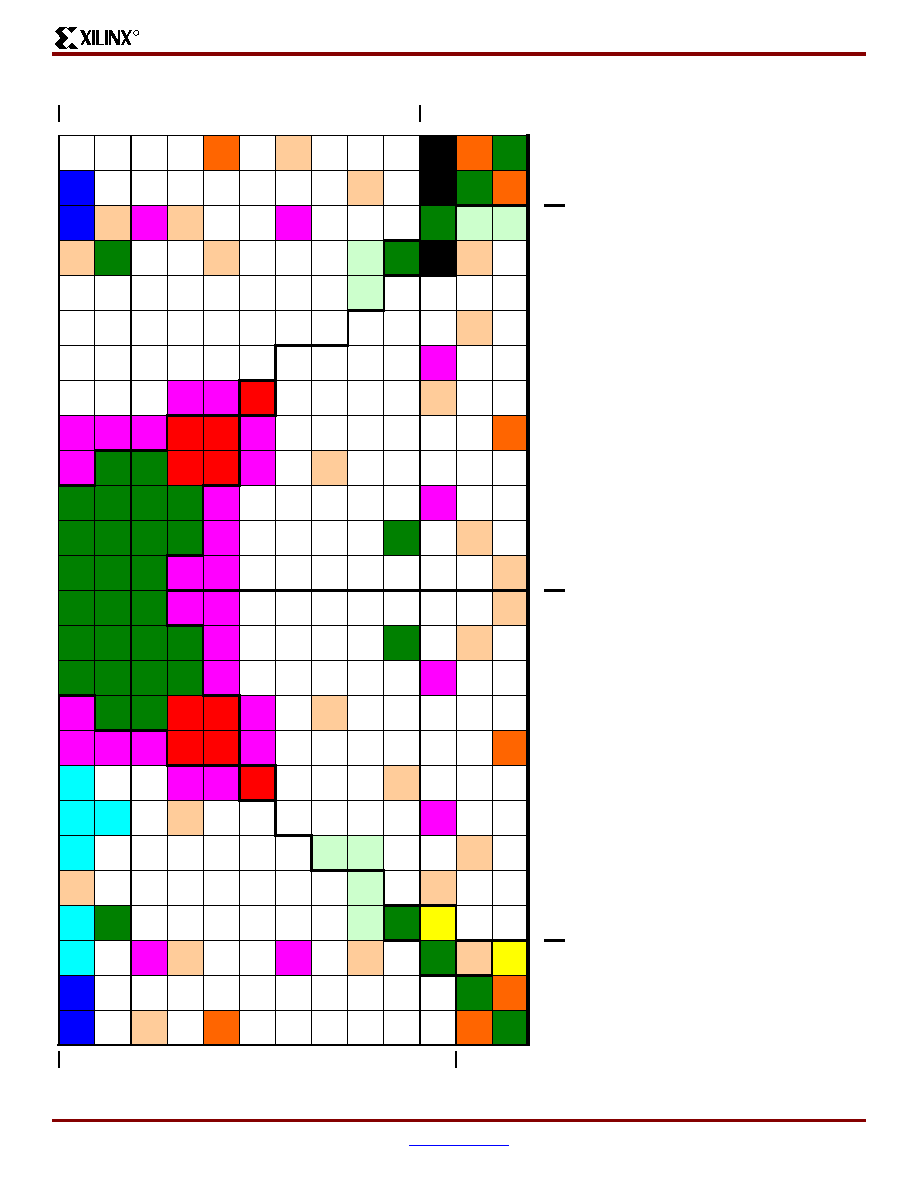

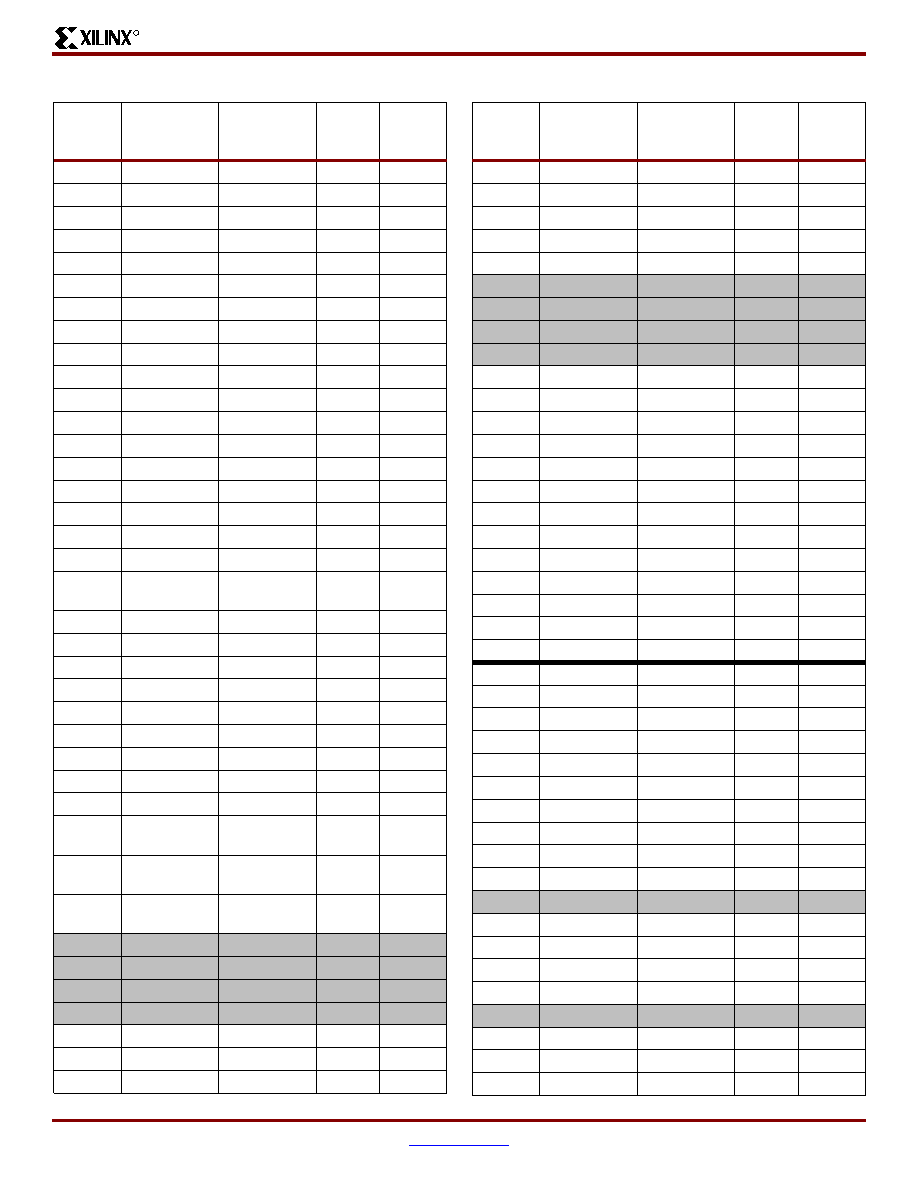

CLB Overview

The Configurable Logic Blocks (CLBs) constitute the main

logic resource for implementing synchronous as well as

combinatorial circuits. Each CLB comprises four intercon-

nected slices, as shown in

Figure 5

. These slices are

grouped in pairs. Each pair is organized as a column with an

independent carry chain.

The nomenclature that the FPGA Editor -- part of the Xilinx

development software -- uses to designate slices is as fol-

lows: The letter "X" followed by a number identifies columns

of slices. The "X" number counts up in sequence from the

left side of the die to the right. The letter "Y" followed by a

number identifies the position of each slice in a pair as well

as indicating the CLB row. The "Y" number counts slices

starting from the bottom of the die according to the

sequence: 0, 1, 0, 1 (the first CLB row); 2, 3, 2, 3 (the sec-

ond CLB row); etc.

Figure 5

shows the CLB located in the

lower left-hand corner of the die. Slices X0Y0 and X0Y1

make up the column-pair on the left where as slices X1Y0

and X1Y1 make up the column-pair on the right. For each

CLB, the term "left-hand" (or SLICEM) is used to indicated

the pair of slices labeled with an even "X" number, such as

X0, and the term "right-hand" (or SLICEL) designates the

pair of slices with an odd "X" number, e.g., X1.

Elements Within a Slice

All four slices have the following elements in common: two

logic function generators, two storage elements, wide-func-

tion multiplexers, carry logic, and arithmetic gates, as

shown in

Figure 6

. Both the left-hand and right-hand slice

pairs use these elements to provide logic, arithmetic, and

ROM functions. Besides these, the left-hand pair supports

two additional functions: storing data using Distributed RAM

and shifting data with 16-bit registers.

Figure 6

is a diagram

of the left-hand slice; therefore, it represents a superset of

the elements and connections to be found in all slices. See

Function Generator, page 12

for more information.

The RAM-based function generator -- also known as a

Look-Up Table or LUT -- is the main resource for imple-

menting logic functions. Furthermore, the LUTs in each

left-hand slice pair can be configured as Distributed RAM or

a 16-bit shift register. For information on the former, see

XAPP464

: Using Look-Up Tables as Distributed RAM in

Spartan-3 FPGAs; for information on the latter, refer to

XAPP465

: Using Look-Up Tables as Shift Registers (SRL16)

in Spartan-3 FPGAs. The function generators located in the

upper and lower portions of the slice are referred to as the

"G" and "F", respectively.

The storage element, which is programmable as either a

D-type flip-flop or a level-sensitive latch, provides a means

for synchronizing data to a clock signal, among other uses.

The storage elements in the upper and lower portions of the

slice are called FFY and FFX, respectively.

Wide-function multiplexers effectively combine LUTs in

order to permit more complex logic operations. Each slice

has two of these multiplexers with F5MUX in the lower por-

tion of the slice and FXMUX in the upper portion. Depend-

ing on the slice, FXMUX takes on the name F6MUX,

F7MUX, or F8MUX. For more details on the multiplexers,

see

XAPP466

: Using Dedicated Multiplexers in Spartan-3

FPGAs.

Figure 5: Arrangement of Slices within the CLB

DS099-2_05_040703

Interconnect

to Neighbors

Left-Hand SLICEM

(Logic or Distributed RAM

or Shift Register)

Right-Hand SLICEL

(Logic Only)

CIN

SLICE

X0Y1

SLICE

X0Y0

Switch

Matrix

COUT

CLB

COUT

SHIFTOUT

SHIFTIN

CIN

SLICE

X1Y1

SLICE

X1Y0

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

11

Advance Product Specification

1-800-255-7778

R

Figure 6: Simplified Diagram of the Left-Hand SLICEM

Notes:

1.

Options to invert signal polarity as well as other options that enable lines for various functions are not shown.

2.

The index i can be 6, 7, or 8, depending on the slice. In this position, the upper right-hand slice has an F8MUX,

and the upper left-hand slice has an F7MUX. The lower right-hand and left-hand slices both have an F6MUX.

Spartan-3 1.2V FPGA Family: Functional Description

12

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

The carry chain, together with various dedicated arithmetic

logic gates, support fast and efficient implementations of

math operations. The carry chain enters the slice as CIN

and exits as COUT. Five multiplexers control the chain:

CYINIT, CY0F, and CYMUXF in the lower portion as well as

CY0G and CYMUXG in the upper portion. The dedicated

arithmetic logic includes the exclusive-OR gates XORF and

XORG (upper and lower portions of the slice, respectively)

as well as the AND gates GAND and FAND (upper and

lower portions, respectively).

Main Logic Paths

Central to the operation of each slice are two nearly identi-

cal data paths, distinguished using the terms top and bot-

tom. The description that follows uses names associated

with the bottom path. (The top path names appear in paren-

theses.) The basic path originates at an interconnect-switch

matrix outside the CLB. Four lines, F1 through F4 (or G1

through G4 on the upper path), enter the slice and connect

directly to the LUT. Once inside the slice, the lower 4-bit

path passes through a function generator "F" (or "G") that

performs logic operations. The function generator's Data

output, "D", offers five possible paths:

1.

Exit the slice via line "X" (or "Y") and return to

interconnect.

2.

Inside the slice, "X" (or "Y") serves as an input to the

DXMUX (DYMUX) which feeds the data input, "D", of

the FFY (FFX) storage element. The "Q" output of the

storage element drives the line XQ (or YQ) which exits

the slice.

3.

Control the CYMUXF (or CYMUXG) multiplexer on the

carry chain.

4.

With the carry chain, serve as an input to the XORF (or

XORG) exclusive-OR gate that performs arithmetic

operations, producing a result on "X" (or "Y").

5.

Drive the multiplexer F5MUX to implement logic

functions wider than four bits. The "D" outputs of both

the F-LUT and G-LUT serve as data inputs to this

multiplexer.

In addition to the main logic paths described above, there

are two bypass paths that enter the slice as BX and BY.

Once inside the FPGA, BX in the bottom half of the slice (or

BY in the top half) can take any of several possible

branches:

1.

Bypass both the LUT and the storage element, then exit

the slice as BXOUT (or BYOUT) and return to

interconnect.

2.

Bypass the LUT, then pass through a storage element

via the D input before exiting as XQ (or YQ).

3.

Control the wide function multiplexer F5MUX (or

F6MUX).

4.

Via multiplexers, serve as an input to the carry chain.

5.

Drives the DI input of the LUT. See Distributed RAM

section.

6.

BY can control the REV inputs of both the FFY and FFX

storage elements. See Storage Element Section.

7.

Finally, the DIG_MUX multiplexer can switch BY onto to

the DIG line, which exits the slice.

Other slice signals shown in

Figure 6, page 11

are dis-

cussed in the sections that follow.

Function Generator

Each of the two LUTs (F and G) in a slice have four logic

inputs (A1-A4) and a single output (D). This permits any

four-variable Boolean logic operation to be programmed

into them. Furthermore, wide function multiplexers can be

used to effectively combine LUTs within the same CLB or

across different CLBs, making logic functions with still more

input variables possible.

The LUTs in both the right-hand and left-hand slice-pairs

not only support the logic functions described above, but

also can function as ROM that is initialized with data at the

time of configuration.

The LUTs in the left-hand slice-pair (even-numbered col-

umns such as X0 in

Figure 5

) of each CLB support two

additional functions that the right-hand slice-pair (odd-num-

bered columns such as X1) do not.

First, it is possible to program the "left-hand LUTs" as dis-

tributed RAM. This type of memory affords moderate

amounts of data buffering anywhere along a data path. One

left-hand LUT stores 16 bits. Multiple left-hand LUTs can be

combined in various ways to store larger amounts of data. A

dual port option combines two LUTs so that memory access

is possible from two independent data lines. A Distributed

ROM option permits pre-loading the memory with data dur-

ing FPGA configuration For more information, see the Dis-

tributed RAM section.

Second, it is possible to program each left-hand LUT as a

16-bit shift register. Used in this way, each LUT can delay

serial data anywhere from one to 16 clock cycles. The four

left-hand LUTs of a single CLB can be combined to produce

delays up to 64 clock cycles. The SHIFTIN and SHIFTOUT

lines cascade LUTs to form larger shift registers. It is also

possible to combine shift registers across more than one

CLB. The resulting programmable delays can be used to

balance the timing of data pipelines.

Block RAM Overview

All Spartan-3 devices support block RAM, which is orga-

nized as configurable, synchronous 18Kbit blocks. Block

RAM stores relatively large amounts of data more efficiently

than the distributed RAM feature described earlier. (The lat-

ter is better suited for buffering small amounts of data any-

where along signal paths.) This section describes basic

Block RAM functions. For more information, see

XAPP463

:

Using Block RAM in Spartan-3 FPGAs.

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

13

Advance Product Specification

1-800-255-7778

R

The aspect ratio -- i.e., width vs. depth -- of each block

RAM is configurable. Furthermore, multiple blocks can be

cascaded to create still wider and/or deeper memories.

A choice among primitives determines whether the block

RAM functions as dual- or single-port memory. A name of

the form RAM16_S[w

A

]_S[w

B

] calls out the dual-port primi-

tive, where the integers w

A

and w

B

specify the total data

path width at ports w

A

and w

B

, respectively. Thus, a

RAM16_S9_S18 is a dual-port RAM with a 9-bit-wide Port A

and an 18-bit-wide Port B. A name of the form RAM16_S[w]

identifies the single-port primitive, where the integer w

specifies the total data path width of the lone port. A

RAM16_S18 is a single-port RAM with an 18-bit-wide port.

Other memory functions -- e.g., FIFOs, data path width

conversion, ROM, etc. -- are readily available using the

CORE GeneratorTM system, part of the Xilinx development

software.

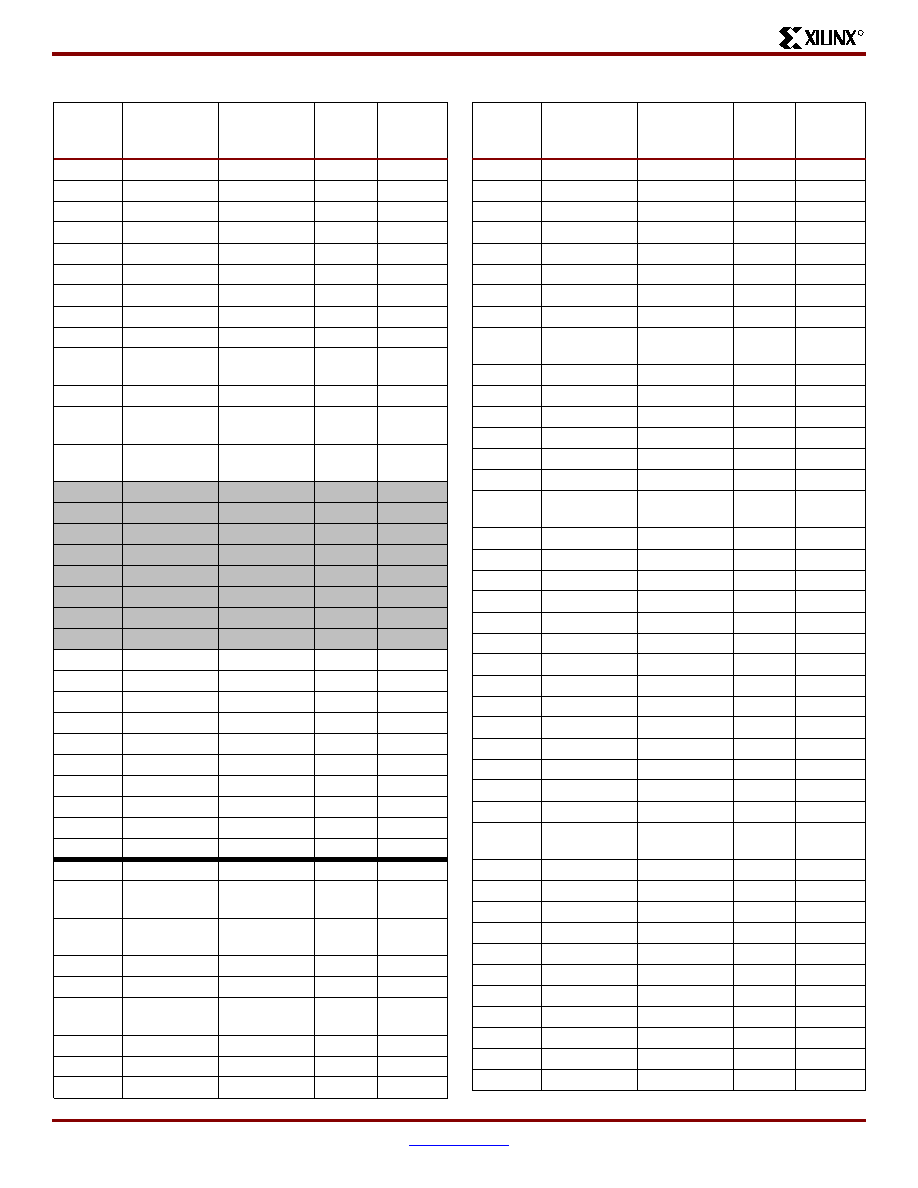

Arrangement of RAM Blocks on Die

The XC3S50 has one column of block RAM. The Spartan-3

devices ranging from the XC3S200 to XC3S2000 have two

columns of block RAM. The XC3S4000 and XC3S5000

have four columns. The position of the columns on the die is

shown in

Figure 1

in Module 1:

Introduction and Ordering

Information

. For a given device, the total available RAM

blocks are distributed equally among the columns.

Table 8

shows the number of RAM blocks, the data storage capac-

ity, and the number of columns for each device.

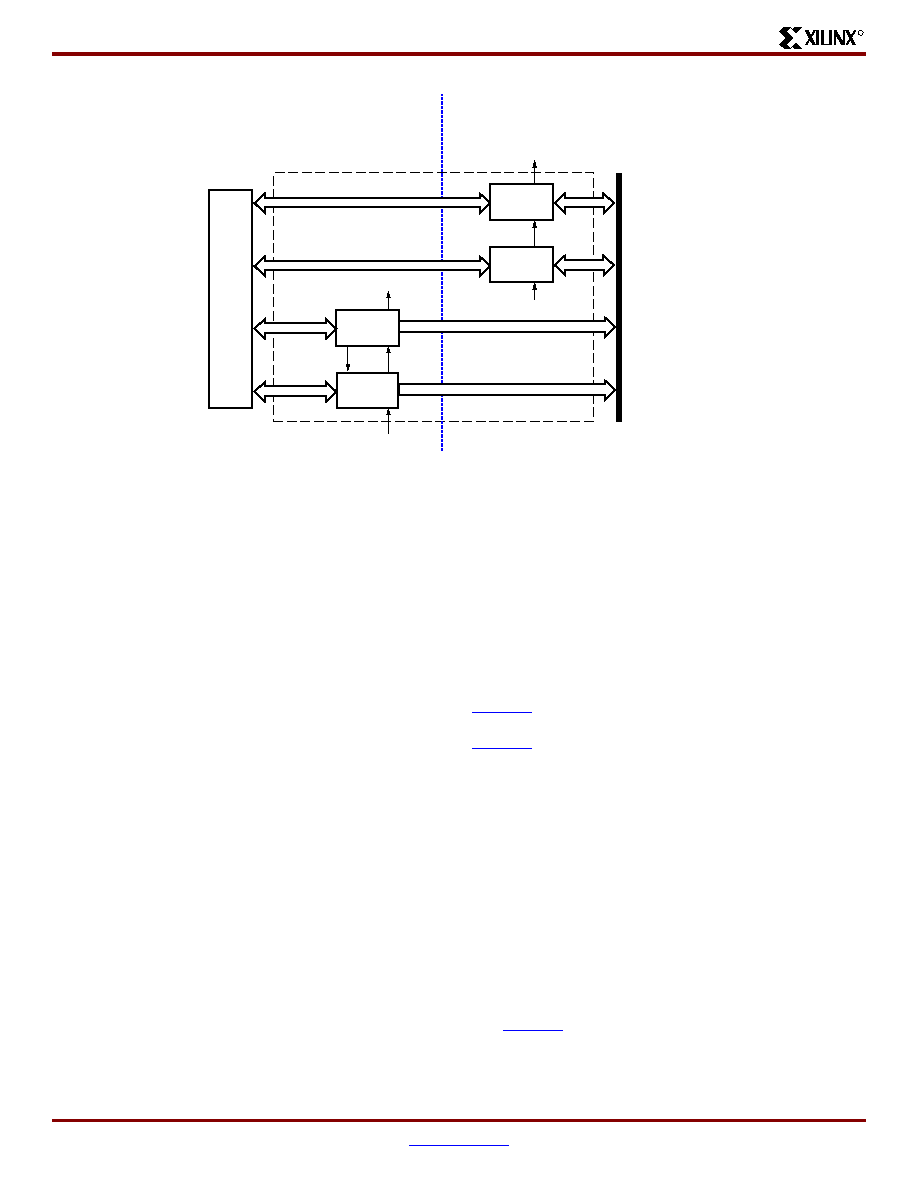

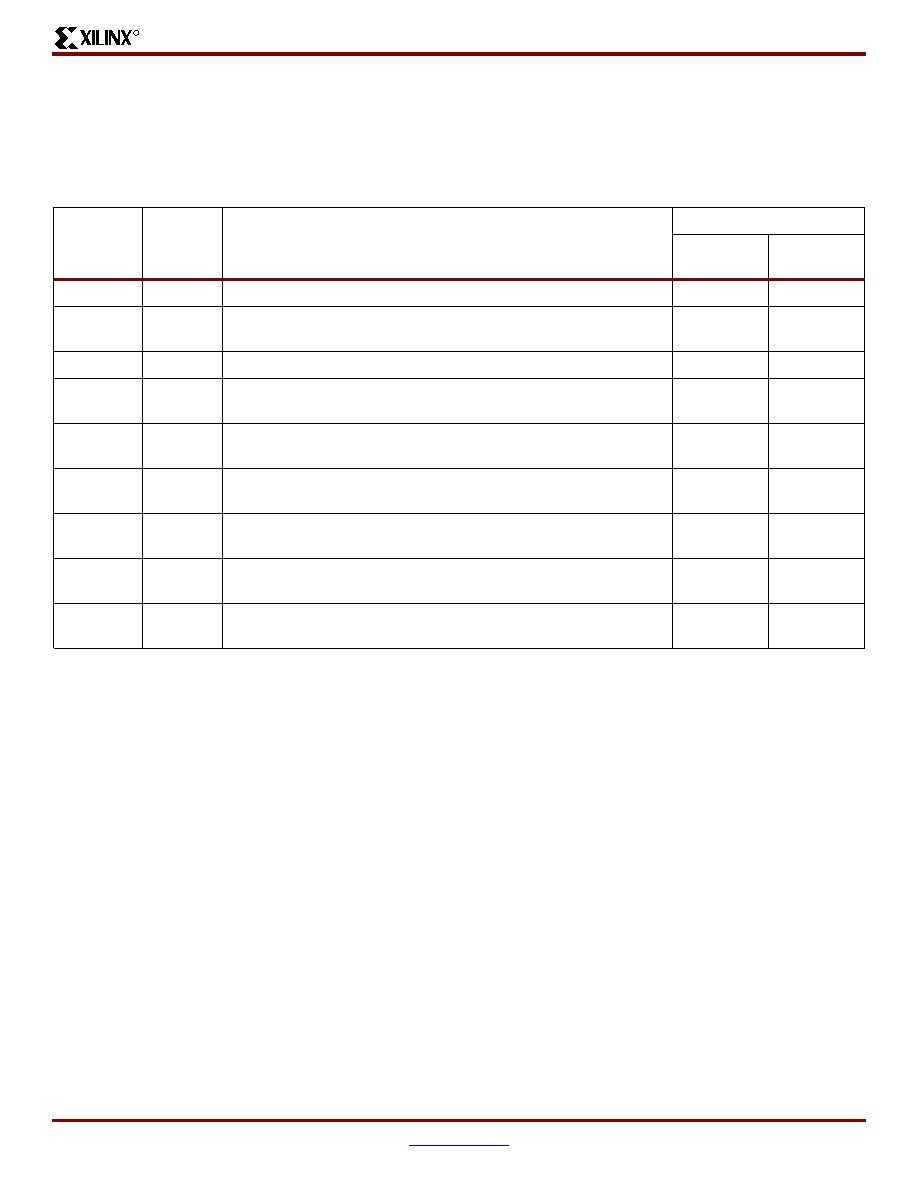

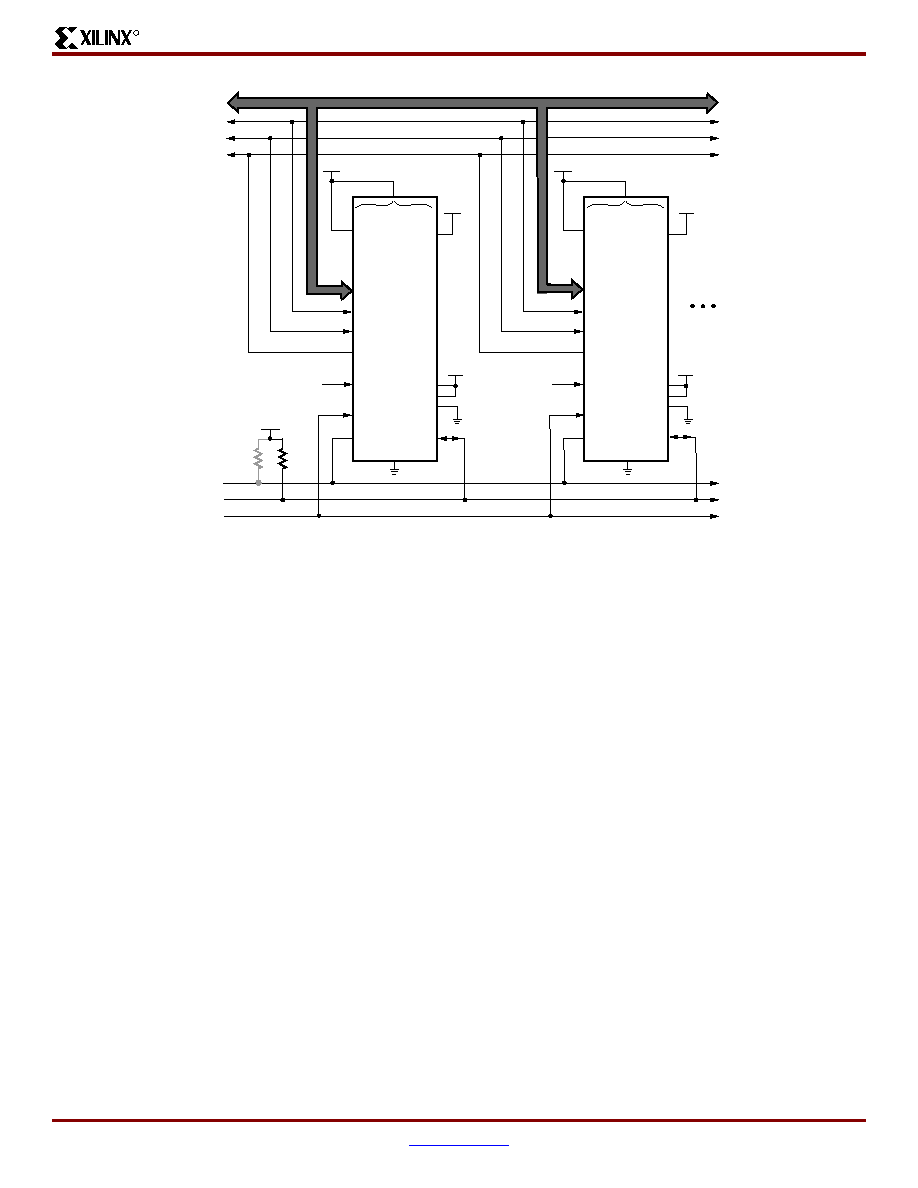

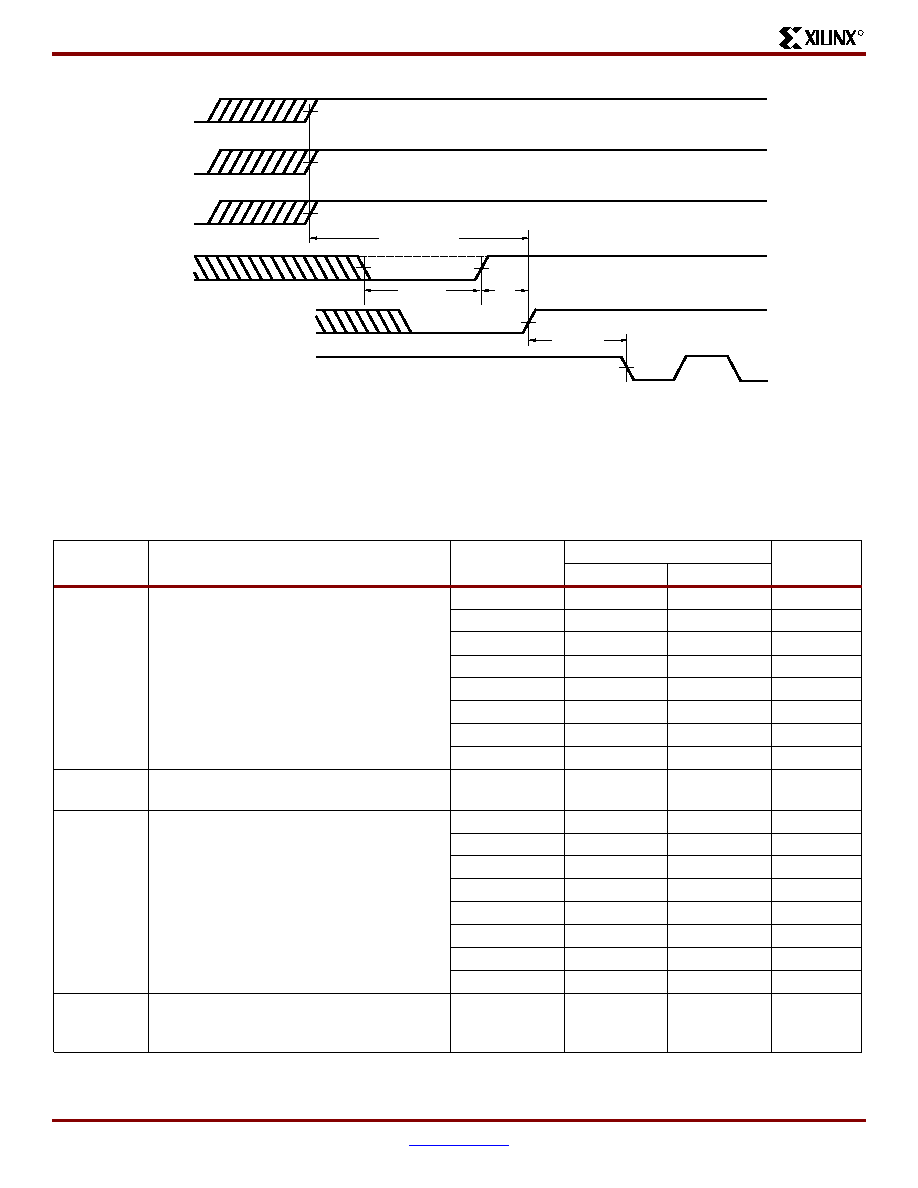

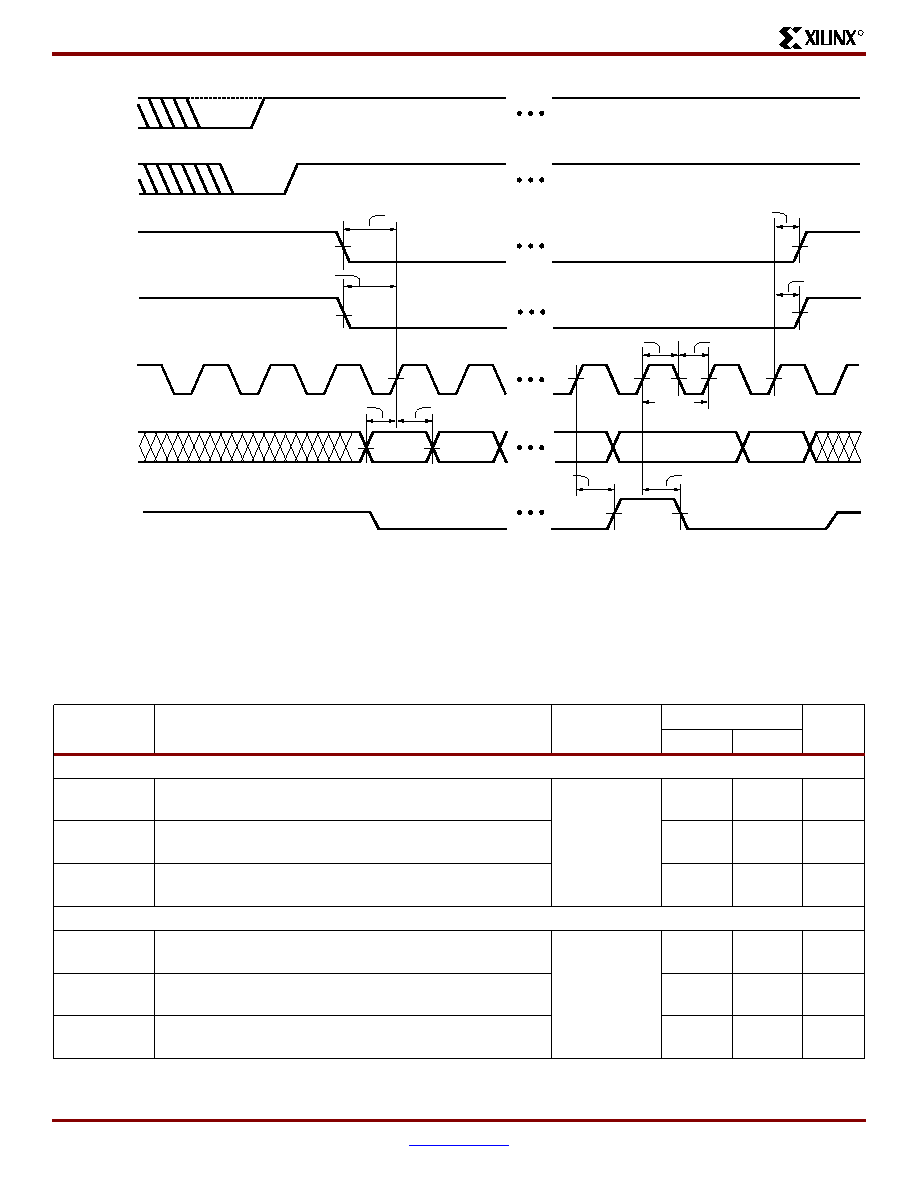

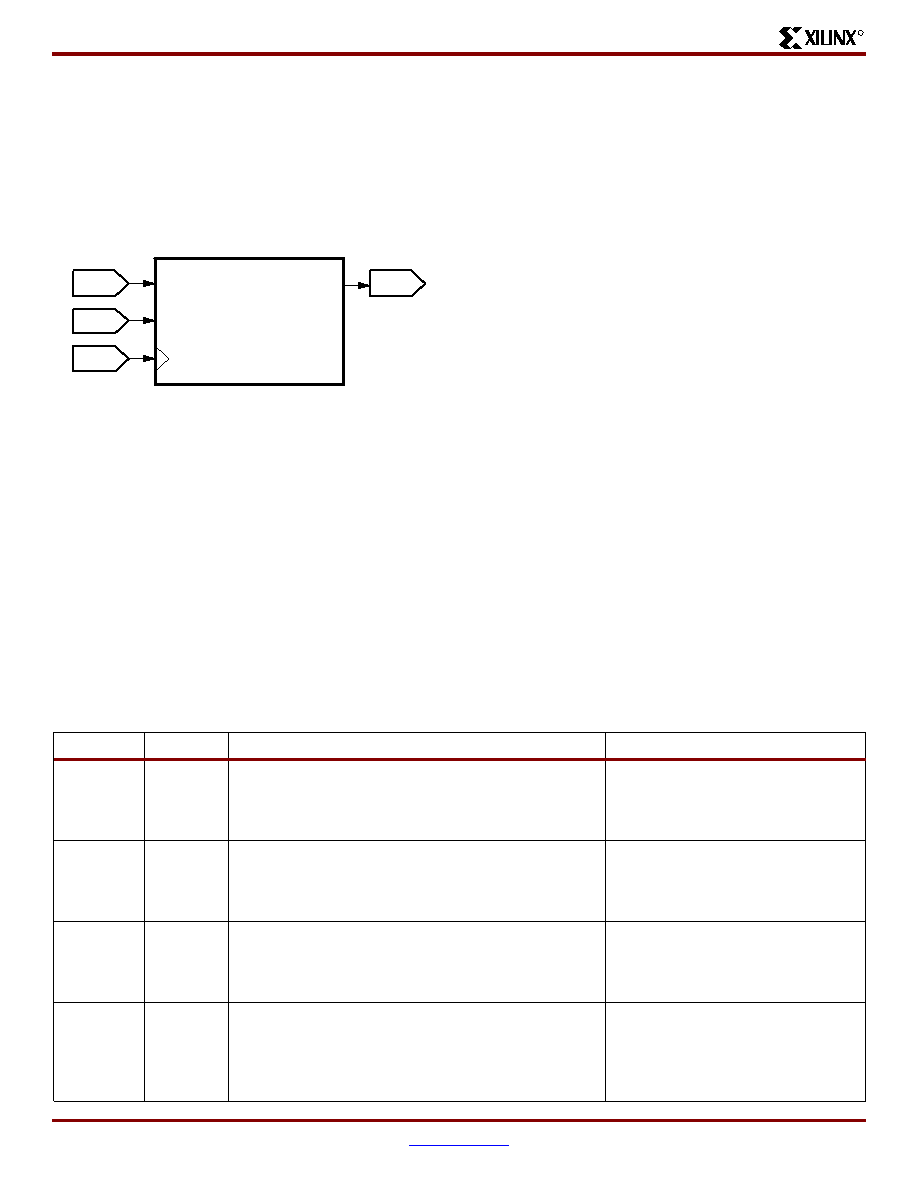

The Internal Structure of the Block RAM

The block RAM has a dual port structure. The two identical

data ports called A and B permit independent access to the

common RAM block, which has a maximum capacity of

18,432 bits -- or 16,384 bits when no parity lines are used.

Each port has its own dedicated set of data, control and

clock lines for synchronous read and write operations.

There are four basic data paths, as shown in

Figure 7

: (1)

write to and read from Port A, (2) write to and read from Port

B, (3) data transfer from Port A to Port B, and (4) data trans-

fer from Port B to Port A.

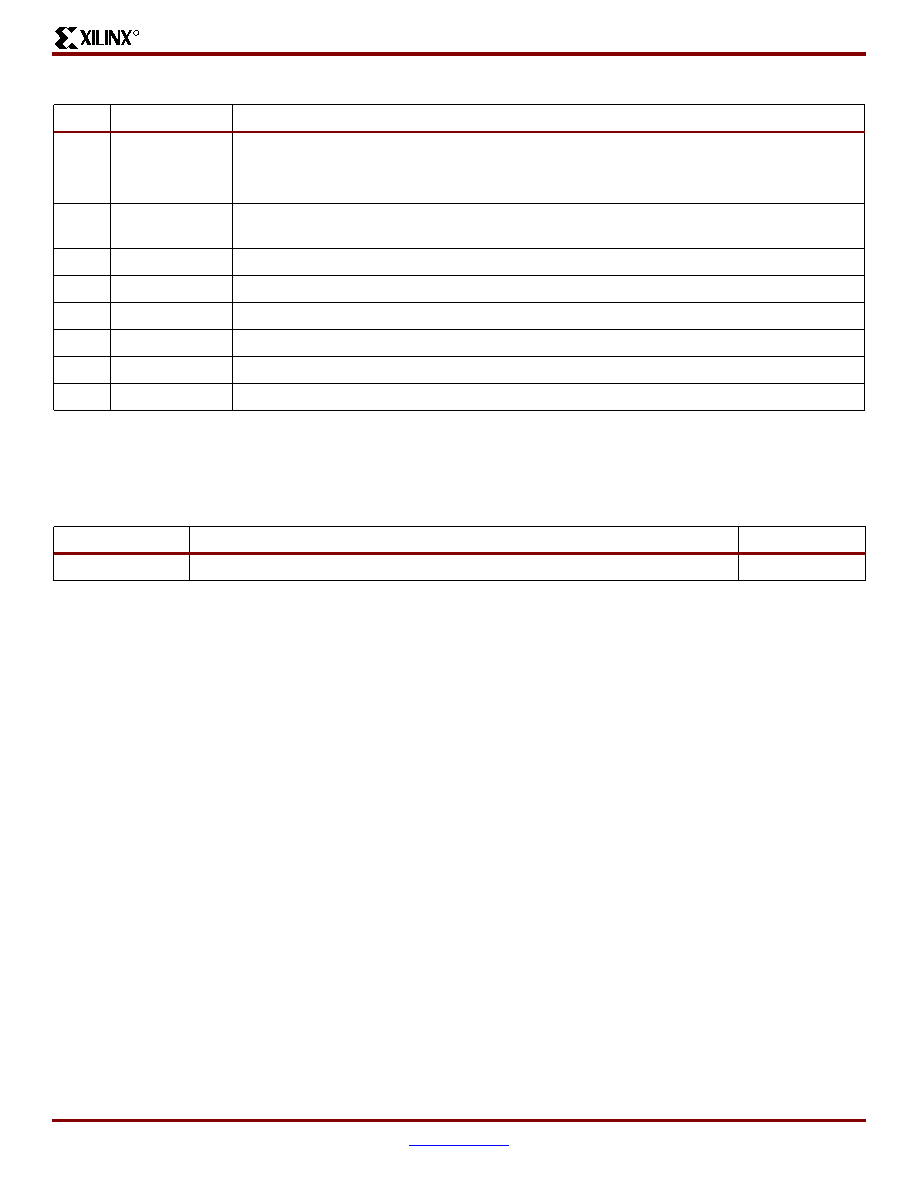

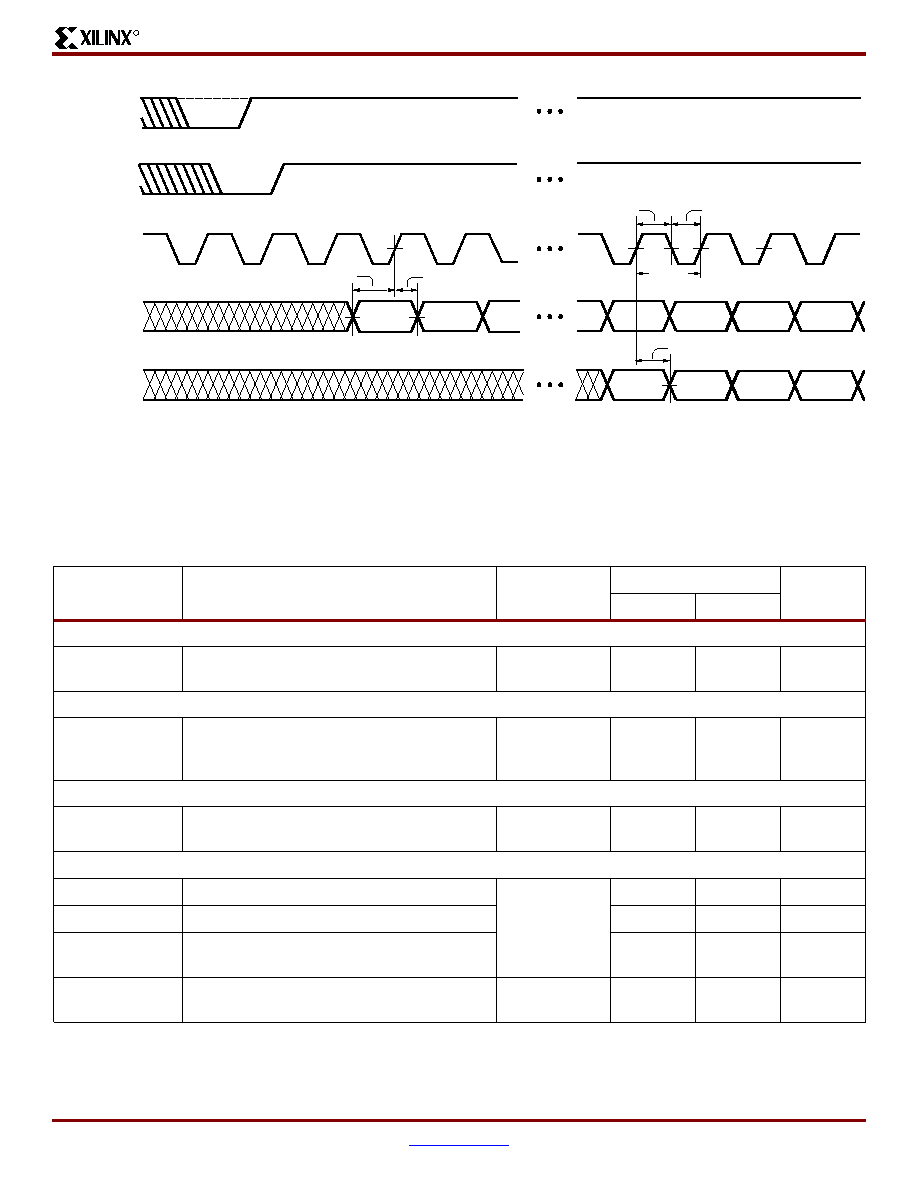

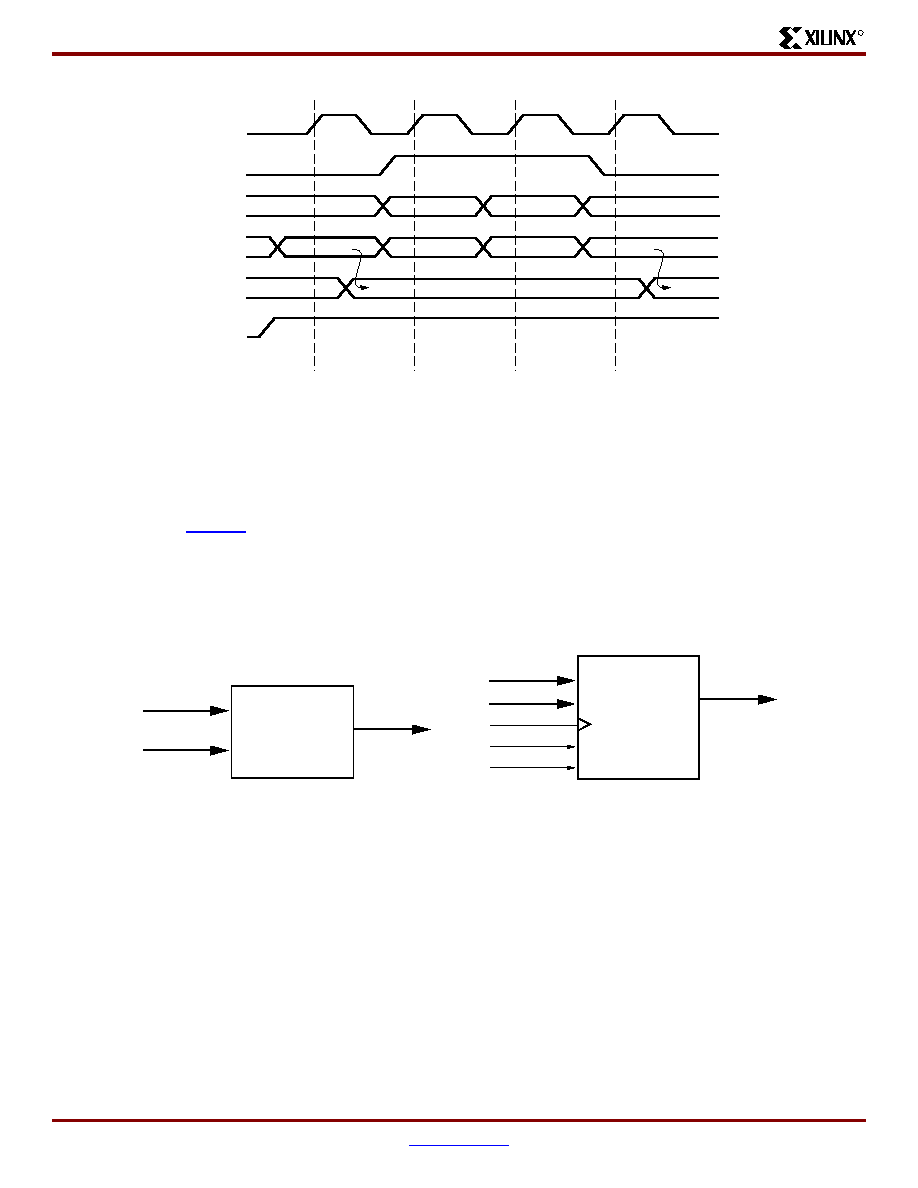

Block RAM Port Signal Definitions

Representations of the dual-port primitive

RAM16_S[w

A

]_S[w

B

] and the single-port primitive

RAM16_S[w] with their associated signals are shown in

Figure 8a

and

Figure 8b

, respectively. These signals are

defined in

Table 9

.

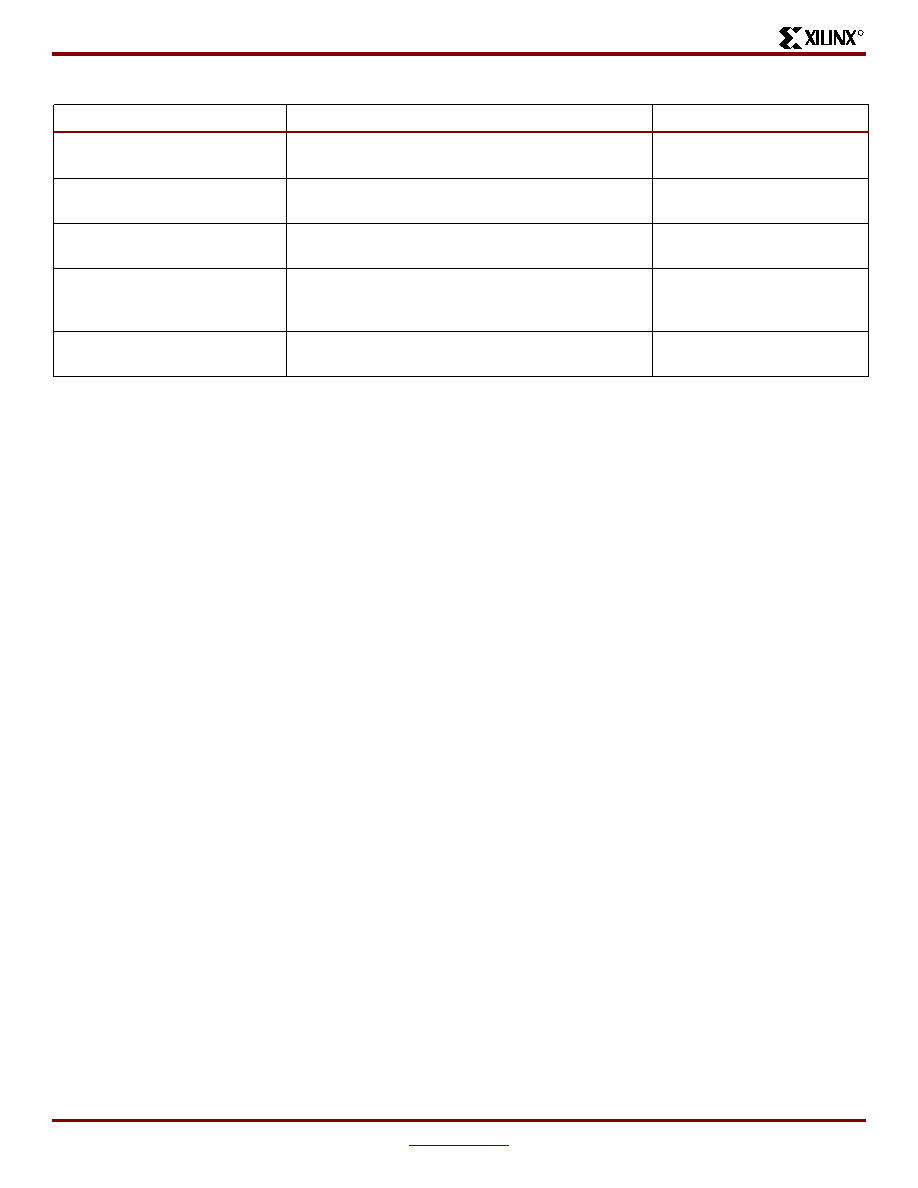

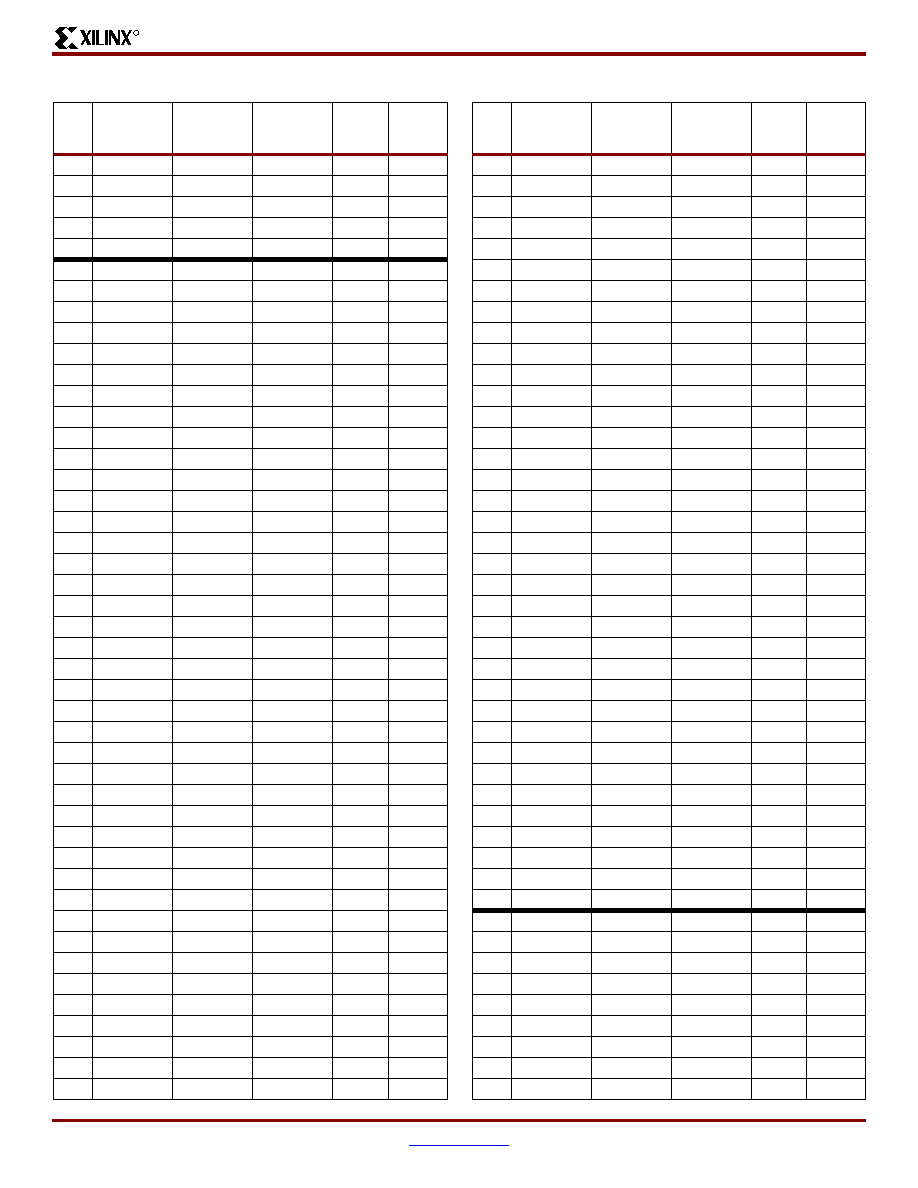

Table 8: Number of RAM Blocks by Device

Device

Total Number

of RAM Blocks

Total

Addressable

Locations (bits)

Number

of

Columns

XC3S50

4

73,728

1

XC3S200

12

221,184

2

XC3S400

16

294,912

2

XC3S1000

24

442,368

2

XC3S1500

32

589,824

2

XC3S2000

40

737,280

2

XC3S4000

96

1,769,472

4

XC3S5000

104

1,916,928

4

Figure 7: Block RAM Data Paths

DS099-2_12_030703

Spartan-3

Dual Port

Block RAM

Read 3

Read

Write

Write

Read

Write

Write

Read

Port A

Port B

2

1

4

Spartan-3 1.2V FPGA Family: Functional Description

14

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

Figure 8: Block RAM Primitives

DS099-2_13_091302

WEA

ENA

SSRA

CLKA

ADDRA[r

A

1:0]

DIA[w

A

1:0]

DIPA[3:0]

DOPA[p

A

1:0]

DOA[w

A

1:0]

RAM16_w

A

_w

B

(a) Dual-Port

(b) Single-Port

DOPB[p

B

1:0]

DOB[w

B

1:0]

WEB

ENB

SSRB

CLKB

ADDRB[r

B

1:0]

DIB[w

B

1:0]

DIPB[3:0]

WE

EN

SSR

CLK

ADDR[r 1:0]

DI[w 1:0]

DIP[p 1:0]

DOP[p 1:0]

DO[w 1:0]

RAM16_Sw

Notes:

1.

w

A

and w

B

are integers representing the total data path width (i.e., data bits plus parity bits) at ports A and B, respectively.

2.

p

A

and p

B

are integers that indicate the number of data path lines serving as parity bits.

3.

r

A

and r

B

are integers representing the address bus width at ports A and B, respectively.

4.

The control signals CLK, WE, EN, and SSR on both ports have the option of inverted polarity.

Table 9: Block RAM Port Signals

Signal

Description

Port A

Signal

Name

Port B

Signal

Name

Direction

Function

Address Bus

ADDRA

ADDRB

Input

The Address Bus selects a memory location for read or write

operations. The width (w) of the port's associated data path

determines the number of available address lines (r).

Data Input Bus

DIA

DIB

Input

Data at the DI input bus is written to the addressed memory

location addressed on an enabled active CLK edge.

It is possible to configure a port's total data path width (w) to be

1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and

DO paths of a given port. Each port is independent. For a port

assigned a width (w), the number of addressable locations will

be 16,384/(w-p) where "p" is the number of parity bits. Each

memory location will have a width of "w" (including parity bits).

See the DIP signal description for more information of parity.

Parity Data

Input(s)

DIPA

DIPB

Input

Parity inputs represent additional bits included in the data input

path to support error detection. The number of parity bits "p"

included in the DI (same as for the DO bus) depends on a port's

total data path width (w). See

Table 10

.

Spartan-3 1.2V FPGA Family: Functional Description

DS099-2 (v1.2) July 11, 2003

www.xilinx.com

15

Advance Product Specification

1-800-255-7778

R

Port Aspect Ratios

On a given port, it is possible to select a number of different

possible widths (w � p) for the DI/DO buses as shown in

Table 10

. These two buses always have the same width.

This data bus width selection is independent for each port. If

the data bus width of Port A differs from that of Port B, the

Block RAM automatically performs a bus-matching function.

When data are written to a port with a narrow bus, then read

from a port with a wide bus, the latter port will effectively

combine "narrow" words to form "wide" words. Similarly,

when data are written into a port with a wide bus, then read

from a port with a narrow bus, the latter port will divide

Data Output

Bus

DOA

DOB

Output

Basic data access occurs whenever WE is inactive. The DO

outputs mirror the data stored in the addressed memory

location.

Data access with WE asserted is also possible if one of the

following two attributes is chosen: WRITE_FIRST accesses

data before the write takes place. READ_FIRST accesses data

after the write occurs.

A third attribute, NO_CHANGE, latches the DO outputs upon

the assertion of WE.

It is possible to configure a port's total data path width (w) to be

1, 2, 4, 9, 18, or 36 bits. This selection applies to both the DI and

DO paths. See the DI signal description.

Parity Data

Output(s)

DOPA

DOPB

Output

Parity inputs represent additional bits included in the data input

path to support error detection. The number of parity bits "p"

included in the DI (same as for the DO bus) depends on a port's

total data path width (w). See

Table 10

.

Write Enable

WEA

WEB

Input

When asserted together with EN, this input enables the writing

of data to the RAM. In this case, the data access attributes

WRITE_FIRST, READ_FIRST or NO_CHANGE determines if

and how data is updated on the DO outputs. See the DO signal

description.

When WE is inactive with EN asserted, read operations are still

possible. In this case, a transparent latch passes data from the

addressed memory location to the DO outputs.

Clock Enable

ENA

ENB

Input

When asserted, this input enables the CLK signal to

synchronize Block RAM functions as follows: the writing of data

to the DI inputs (when WE is also asserted), the updating of data

at the DO outputs as well as the setting/resetting of the DO

output latches.

When de-asserted, the above functions are disabled.

Set/Reset

SSRA

SSRB

Input

When asserted, this pin forces the DO output latch to the value

that the SRVAL attribute is set to. A Set/Reset operation on one

port has no effect on the other ports functioning, nor does it

disturb the memory's data contents. It is synchronized to the

CLK signal.

Clock

CLKA

CLKB

Input

This input accepts the clock signal to which read and write

operations are synchronized. All associated port inputs are

required to meet setup times with respect to the clock signal's

active edge. The data output bus responds after a clock-to-out

delay referenced to the clock signal's active edge.

Table 9: Block RAM Port Signals (Continued)

Signal

Description

Port A

Signal

Name

Port B

Signal

Name

Direction

Function

Spartan-3 1.2V FPGA Family: Functional Description

16

www.xilinx.com

DS099-2 (v1.2) July 11, 2003

1-800-255-7778

Advance Product Specification

40

R

"wide" words to form "narrow" words. When the data bus

width is eight bits or greater, extra parity bits become avail-

able. The width of the total data path (w) is the sum of the

DI/DO bus width and any parity bits (p).

The width selection made for the DI/DO bus determines the

number of address lines according to the relationship

expressed below:

r = 14 � [log(w�p)/log(2)]

(1)

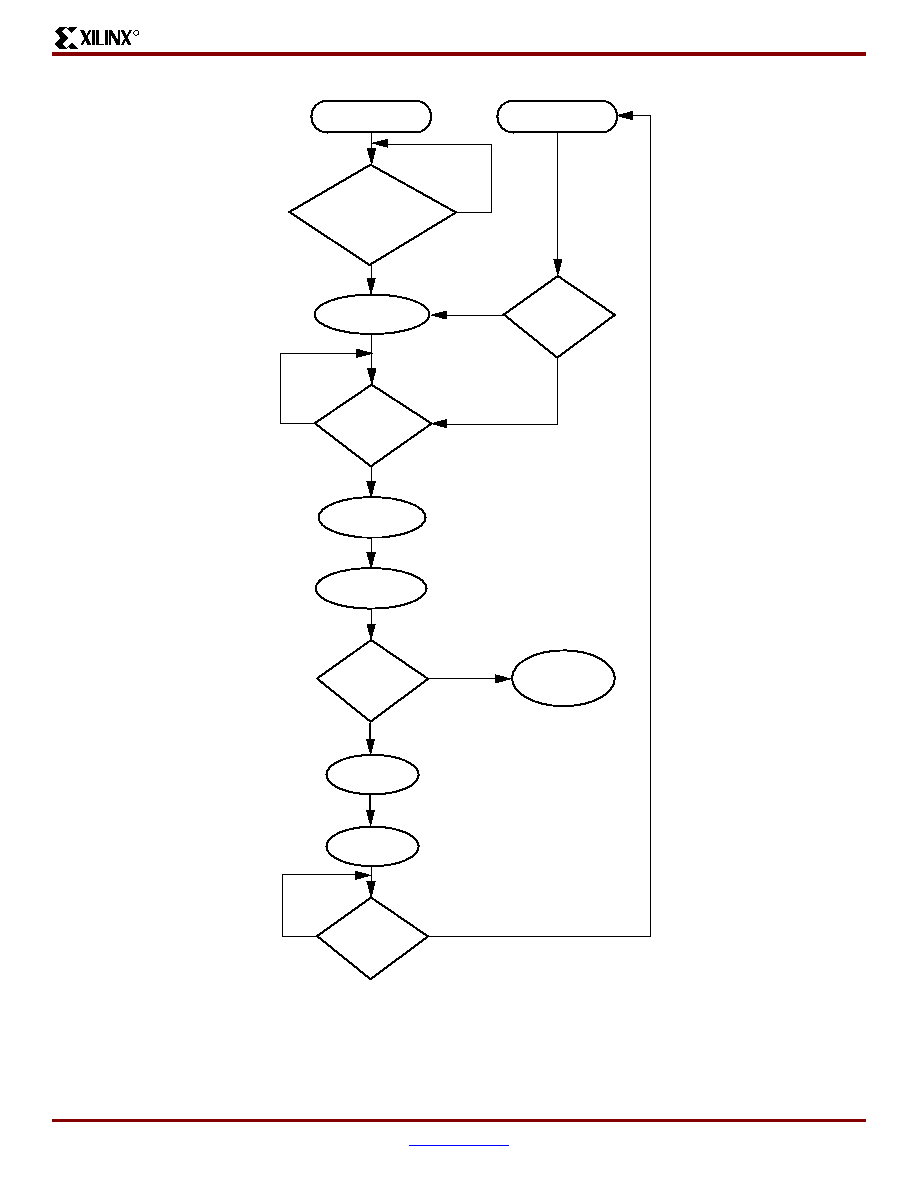

In turn, the number of address lines delimits the total num-