Ordering Information

GP4020/IG/GQ1N (trays)

GP4020/IG/GQ1Q (tape and reel, 1000 units per reel)

The GP4020 is available in a 100 pin PQFP package in

Industrial (-40

∞

C to +85

∞

C) grade. The ordering code is

standard for screened devices

Description

The GP4020 is a complete digital baseband processor

for a Global Positioning System (GPS) receiver. It

combines the 12-channel correlator function of the

GP2021 with an advanced ARM7TDMI (Thumb)

microprocessor to achieve a higher level of integration,

reduced system cost, reduced power consumption and

added functionality. The GP4020 complements the

GP2015 and GP2010 C/A code RF downconverters

available from Zarlink Semiconductor.

The correlator section contains 12 identical tracking

module blocks, one for each channel. Each channel

contains all the components necessary for acquiring

and tracking the received signal, and also contains

other functional blocks, which are used to produce part

of the measurement data set. Individual channels may

be deactivated for systems not requiring full 12-channel

operation and thus allowing for reduced power

consumption and processor loading.

The microprocessor section contains the Firefly MF1

microcontroller core, which includes an ARM7TDMI

with a Thumb instruction de-compressor plus the Firefly

B

µ

ILD module. Also included are a second UART,

B

µ

ILD Serial I/O, General I/O and Watchdog functions.

GP4020

GPS Receiver Baseband Processor

DS5134 ISSUE 4.4 May 2002

Features

∑ Complete GPS correlator and Firefly MF1

microcontroller core

∑ ARM 7TDMI

TM

(Thumb

Æ

) Microprocessor, with JTAG

ICEBreaker

TM

Debug Interface

∑ Fully Configurable External Data Bus

∑ 12 Fully Independent Correlation Channels

∑ Low Voltage Operation: 3∑3V

∑ Low Current Power≠Down Mode

∑ 1PPS UTC Aligned Timing Output

∑ Dual UART

∑ 3-wire B

µ

ILD Serial Input/Output (BSIO) Interface

∑ 8 General Purpose Input/Output (GPIO) Lines

∑ Boot ROM, allowing Software Upload via UART

∑ 8K Bytes Internal SRAM

∑ Compatible with GP2015 and GP2010 RF Front Ends

Applications

∑

GPS Navigation Systems

∑

GPS Geodetic Receivers

∑

Time Transfer Receivers

∑

Automatic Vehicle Location (AVL)

∑

E911 Emergency Positioning

GP2015

GP2010

DS4374

DS4056

GPS Receiver RF Front End

(TQFP 48 package)

GPS Receiver RF Front End

(PQFP 44 package)

Part

Description

Data sheet

Related Products

Absolute Maximum Ratings

-0∑5V to +5∑0V

+7∑0V max.

GND-0∑5V to V

DD

+0∑5V

GND-0∑5V to V

DD

+0∑5V

-55

∞

C to +150

∞

C

2kV

Supply voltage (V

DD

) from ground (GND)

Bias for 5V inputs

Input voltage (any input pin)

Output voltage (any output pin)

Storage temperature

Static discharge (HBM)*

*Mil Std 883 Human Body Model = discharge from 100pF through

1500

between any 2 pins

Manufactured under licence from ARM Ltd

ARM and the ARM logo are trademarks of Advanced RISC Machines Ltd

2

GP4020

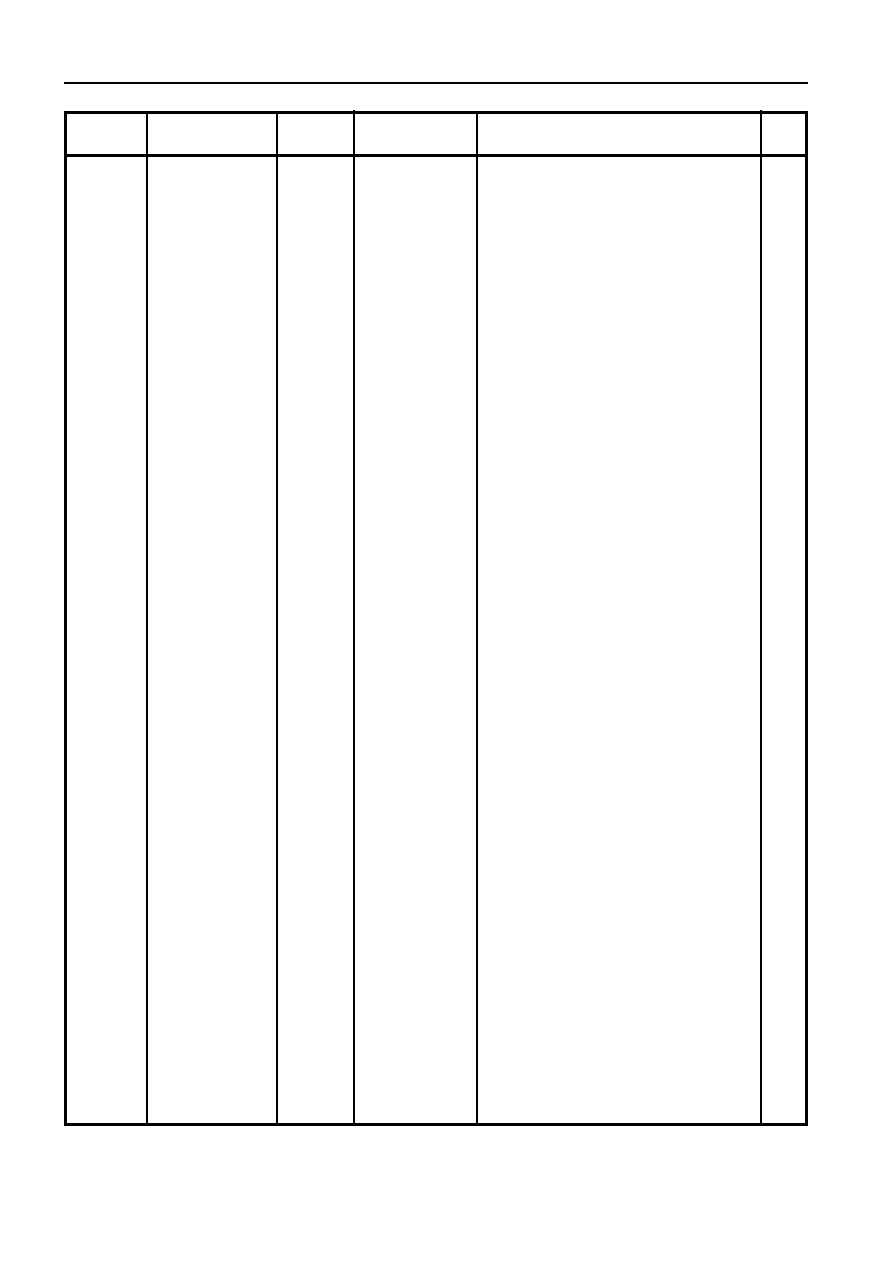

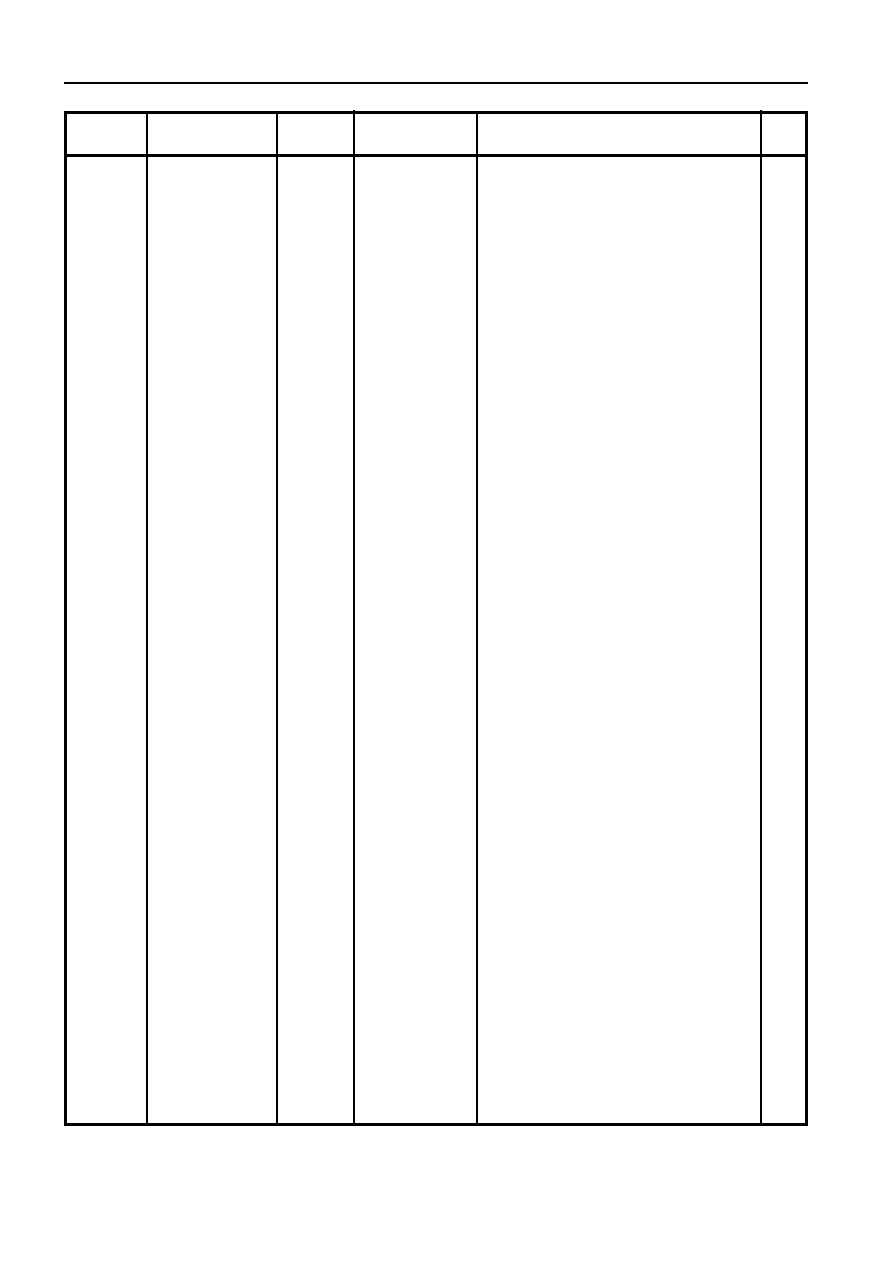

Figure 1 - Block diagram

PLLAT1

PR_XIN

PR_XOUT

CLK_I

CLK_T

SAMPCLK

MAG0

SIGN0

RF_PLL_LOCK

IEXTINT2

TIMEMARK/TIC

PERIPHERAL

CONTROL

LOGIC

GPIO

GPIO

BSIO

BSIO

GPIO

[ 7:0

]

POWER_GOOD

NRESET

GPIO[7:0]

DISCIO

MUL

TI_FNIO

B

µ

ILD_CLK

NRESET

REAL

TIME

CLOCK

PLL

SYSTEM

CLOCK

GENERATOR

RTC_CLK

UART_CLK

NPOR_RESET

NRESET

12-CHANNEL

GPS

CORRELATOR

M_CLK

RA

W

TIMEMARK

M_CLK

TIC

WDOG

ARM7

TDMI

MICRO

UART2

UART_CLK

DMAC

U2RXD

U2TXD

UART1

TIC

INTC

PER_INT

MEAS_INT

ACCUM_INT

1PPS

TIMEMARK

GENERATOR

SSM

JTAG

JT

AG

JTAG

INTERFACE

SSM BDIAG/XPIN IO

B

µ

ILD BUS

S

D

ATA

[ 15:0

]

SADD

[ 19:0

]

FIREFLY

MF1 CORE

MPC

UIM

BOOT

ROM

512

3

16

SRAM

2K

3

32

(6ns)

UIM BUS

UIM BUS

UIM BUS

U1RXD

U1TXD

NICE

NTRST

TMS

TDO

TDI

TCK

SW

AIT

NOSE

NSUB

NSWE[1:0]

NCSC[2:0]

SDA

T

A[15:0]

SADD[19:0]

GP4020

RTC_XIN

RTC_XOUT

NPOR_

RESET

3

GP4020

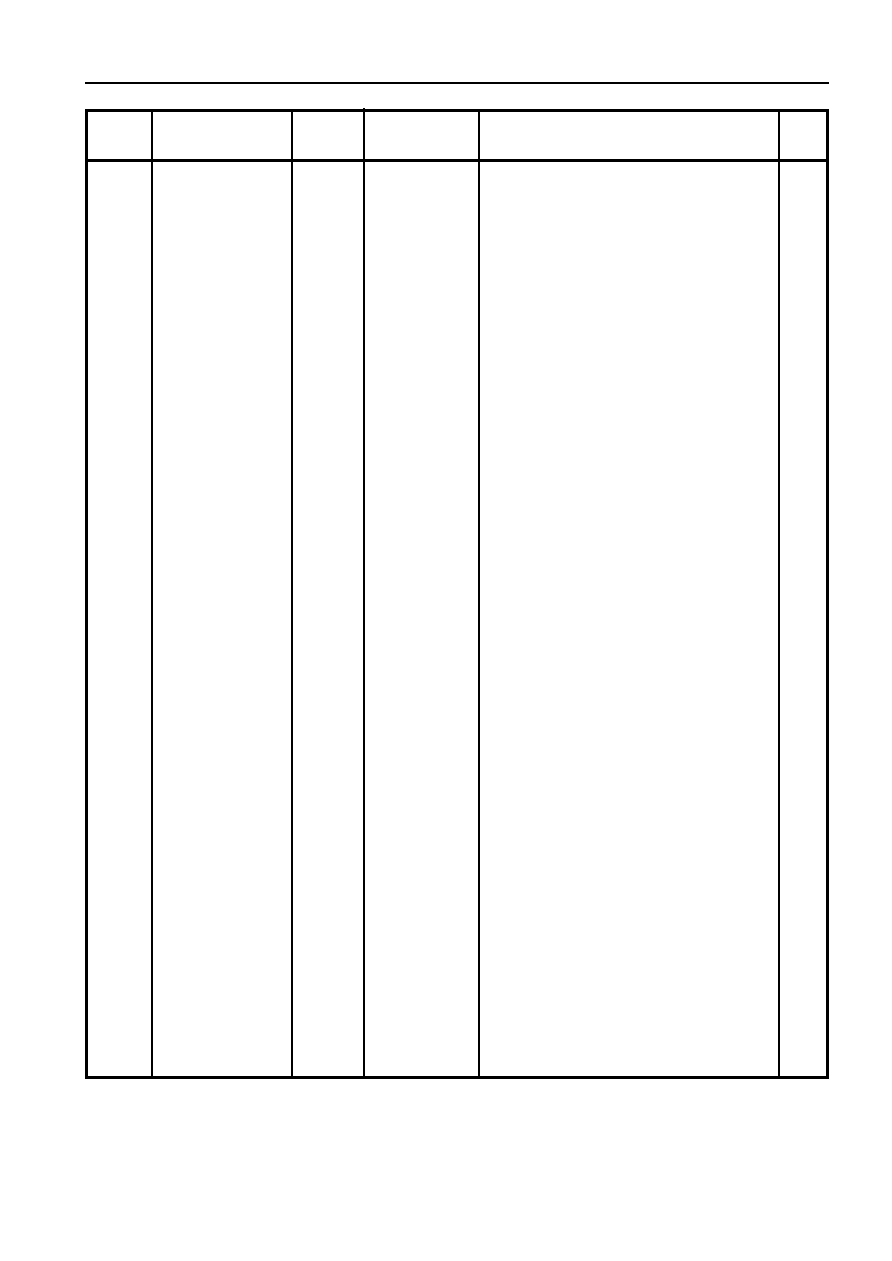

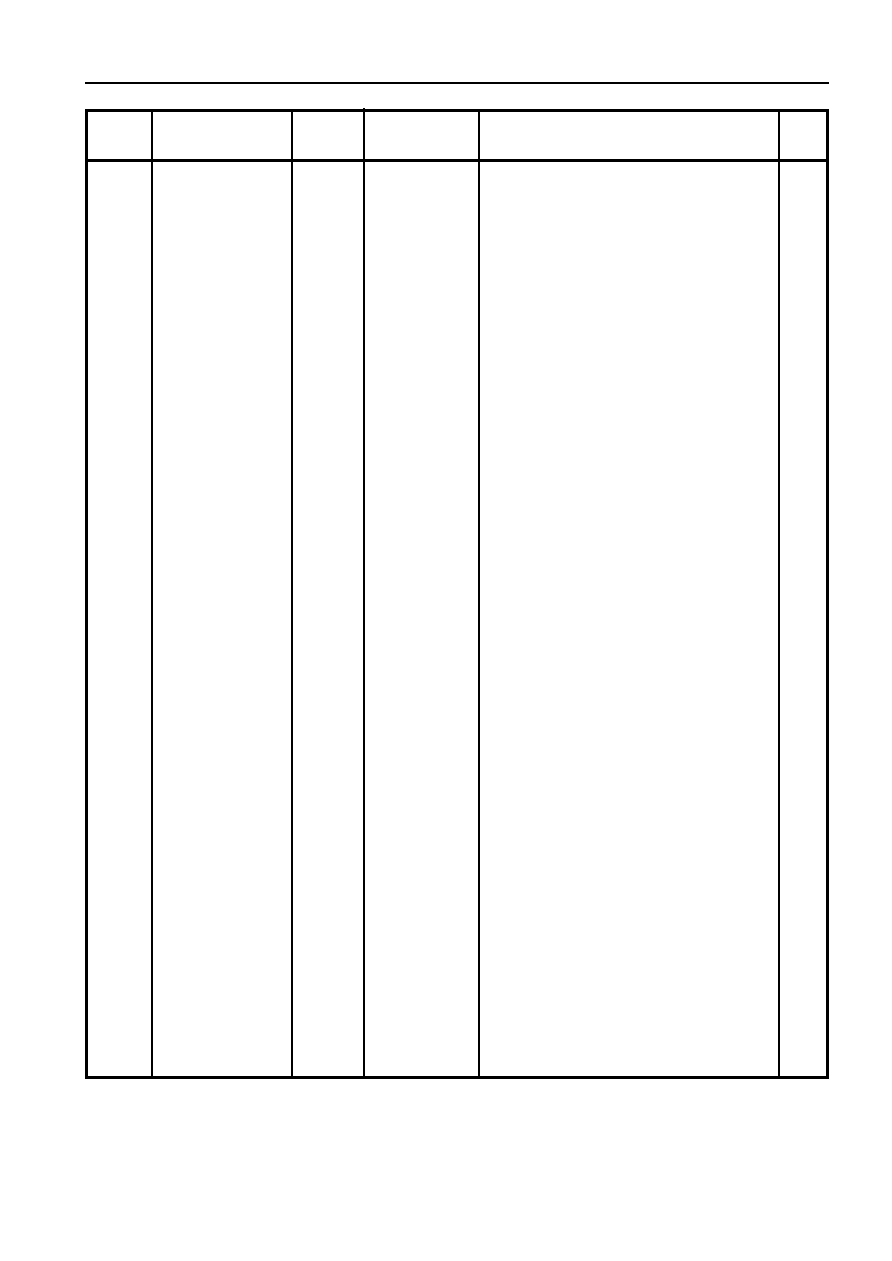

Figure 2 - Pin connections (top view)

1

25

50

76

100

QPA100

Pin No.

Signal Name

Type

Associated

Description

Notes

circuit block

1

SADD[0]

I/O

MPC

System Address bit 0

2

SADD[1]

I/O

MPC

System Address bit 1

3

SADD[2]

I/O

MPC

System Address bit 2

4

SADD[3]

I/O

MPC

System Address bit 3

5

SADD[4]

I/O

MPC

System Address bit 4

6

SADD[5]

I/O

MPC

System Address bit 5

7

GNDPWR

8

SADD[6]

I/O

MPC

System Address bit 6

9

SADD[7]

I/O

MPC

System Address bit 7

10

V

DD

PWR

11

NSCS[0]

I/O

MPC

System Chip Select 0 - Active Low

1

12

NSCS[1]

O

MPC

System Chip Select 1 - Active Low

1

13

NSCS[2A]

O

MPC

System Chip Select 2A - Active Low

1

14

SADD[19]

O

MPC

System Address bit 19

15

SDATA[0]

I/O

MPC

System Data bit 01

16

SDATA[1]

I/O

MPC

System Data bit 11

17

SDATA[2]

I/O

MPC

System Data bit 21

18

SDATA[3]

I/O

MPC

System Data bit 31

19

GNDPWR

20

SDATA[4]

I/O

MPC

System Data bit 41

21

SDATA[5]

I/O

MPC

System Data bit 51

22

V

DD

PWR

23

SDATA[6]

I/O

MPC

System Data bit 61

Cont

...

Table 1 - Pin descriptions

All V

DD

and GND pins must be connected to ensure reliable operation. Any unused input pins must be tied either

high or low; no inputs should be left unconnected.

4

GP4020

Pin No.

Signal Name

Type

Associated

Description

Notes

circuit block

24

SDATA[7]

I/O

MPC

System Data bit 7

1

25

NSOE

I/O

MPC

System Output Enable, active low

1

26

NSWE[1]

I/O

MPC

System Write Enable bit 1, active low

1

27

NSWE[0]

I/O

MPC

System Write Enable bit 0, active low

1

28

SDATA[8]

I/O

MPC

System Data bit 8

1

29

SDATA[9]

I/O

MPC

System Data bit 9

1

30

V

DD

PWR

31

SDATA[10]

I/O

MPC

System Data bit 10

1

32

SDATA[11]

I/O

MPC

System Data bit 11

1

33

GND

PWR

34

SDATA[12]

I/O

MPC

System Data bit 12

1

35

SDATA[13]

I/O

MPC

System Data bit 13

1

36

SDATA[14]

I/O

MPC

System Data bit 14

1

37

SDATA[15]

I/O

MPC

System Data bit 15

1

38

SADD[18]

I/O

MPC

System Address bit 18

39

SADD[17]

I/O

MPC

System Address bit 17

40

SADD[16]

I/O

MPC

System Address bit 16

41

GND

PWR

42

SADD[15]

I/O

MPC

System Address bit 15

43

SADD[14]

I/O

MPC

System Address bit 14

44

V

DD

PWR

45

SADD[13]

I/O

MPC

System Address bit 13

46

SADD[12]

I/O

MPC

System Address bit 12

47

SADD[11]

I/O

MPC

System Address bit 11

48

SADD[10]

I/O

MPC

System Address bit 10

49

SADD[9]

I/O

MPC

System Address bit 9

50

SADD[8]

I/O

MPC

System Address bit 8

51

SWAIT

I

MPC

System Wait input - allows

wait-states to be inserted into the

current Firefly clock cycle.

52

NSUB

O

MPC

System Upper Byte, active low.

1,2

53

IEXTINT2

I

INTC

Interrupt source 2 input

(for external interrupts).

54

MULTI_FNIO

I/O

PCL

Multi-function Input / Output. Used to set

Boot Up ROM area, and source either

100kHz square wave or System Clock.

55

DISCIO

I/O

PCL

Discrete Input / Output.

3

Used either as input or to source

RF_Power_Down control signal or TIC.

56

RF_PLL_LOCK

I

INTC /PCL

PLL Lock Indicator input from RF section.

When high this signal indicates that the

PLL within the RF section is in lock and

the master-clock inputs have stabilised.

57

A1V

DD

PWR

SCG

V

DD

Supply for CLK_T & CLK_I input

block in the System Clock Generator. This

pin should be well decoupled to pin 60

(GND) to ensure optimum noise immunity

58

CLK_T

I

SCG

Master Clock Input from RF front end

4

40MHz 100mV rms.

59

CLK_I

I

SCG

Inverted Master Clock Input from RF

4

front end: 40MHz 100mV rms.

Cont

...

Table 1 - Pin descriptions (continued)

5

GP4020

Sampled Sign (polarity) data from RF front end.

Sampled Mag (amplitude) data from RF front

end.

Sample Clock output to the RF front end. Provides

a 5∑714MHz clock with a 4:3 mark to space ratio.

Power Monitor input, high for normal operation;

low forces the GP4020 into Power Down mode.

System Clock Oscillator - crystal output for 10 to

16MHz crystal.

System Clock Oscillator - crystal inputfor 10 to

16MHz crystal.

TEST select pin,used with TESTMODE (pin 74).

Used for test purposes only and should be

connected to GND in normal operation.

Timemark output. This pin can be used to produce

a UTC-aligned 1 PPS output, or TIC output.

TEST select pin,used with TESTMODE (pin 74).

Used for test purposes only and should be

connected to GND in normal operation.

Real-time Clock Oscillator input for 32kHz crystal.

Real-time Clock Oscillator output for 32kHz crystal.

TEST select pin,used with TEST (pin 67). Used

for test purposes only and should be connected

to GND in normal operation.

System Reset input.

UART 2 Transmit data output.

UART 2 Receive data input.

UART 1 Transmit data output.

UART 1 Receive data input.

GND connection for PLL Block.

V

DD

connection for PLL Block.

System Clock Generator PLL Analog Test I/O.

Reserved for TEST purposes only and should

NOT be connected in normal operation.

ARM7 operating mode and JTAG / SSM Signal

Multiplex (pins 86, 87, 88, 89).

JTAG Test Clock/SSM Diagnostic broadcast

debug output bdiag[0]/System test control input

XReq.

JTAG Test Data In/SSM Diagnostic broadcast

debug output bdiag[1]/System Test control input

X/Write.

JTAG Test Data Out/SSM Diagnostic broadcast

debug output bdiag[2]/System test control input

XBurst.

Pin No.

Signal name

Associated

circuit block

Description

Type

Notes

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

GND

SIGN0

MAG0

SAMPCLK

POWER_GOOD

PR_XOUT

PR_XIN

TEST

V

DD

TIMEMARK / TIC

IDDQTEST

GND

RTC_XIN

RTC_XOUT

TESTMODE

NSRESET

U2TXD

U2RXD

U1TXD

U1RXD

PLLGND

PLLVDD

GND

PLLAT1

NICE

V

DD

TCK/bdiag[0]/XReq

TDI/bdiag[1]/XWrite

TDO/bdiag[2]/XBurst

Table 1 - Pin descriptions (continued)

Cont...

PWR

I

I

O

I

O

I

I

PWR

O

I

PWR

I

O

I

I

O

I

O

I

PWR

PWR

PWR

O

I

PWR

I/O

I/O

I/O

CORR

CORR

CORR

PCL

SCG

SCG

1PPS

RTC

RTC

PCL

UART2

UART2

UART1

UART1

SCGPLL

SCGPLL

SCGPLL

JTAG/SSM

MUTIPLEX

JTAG/SSM

JTAG/SSM

JTAG/SSM

5

5

3

3

6

6

6

6