The KESRX04 is a single chip ASK (Amplitude Shift Key)

Receiver IC. It is designed to operate in a variety of low power

radio applications including keyless entry, general domestic

and industrial remote control, RF tagging and local paging

systems.

The receiver offers an exceptionally high level of integration

and performance to meet the local oscillator radiation require-

ments of regulatory authorities world-wide. Functionally the

device works in the same way as the KESRX01 with the added

features of low supply voltage, in-band interference rejection

(anti-jamming detector), a 2 stage power down to enable

receiver systems to be implemented with less than 1mA supply,

and a wide IF bandwidth and drive stage to interface to an

external ceramic IF band pass filter at intermediate frequencies

from 0.2MHz to 15MHz.

The KESRX04 is an ideal receiver for difficult reception

areas where high level interferers would jam the wanted signal.

The anti-jamming circuit allows operation to be possible with

interfering signals which are more than 14dB stronger than the

wanted signal, without the cost penalties of increased IF

selectivity and frequency accuracy.

QP28

Figure 1 Pin Connections (top view)

Figure 2 Typical system application

FEATURES

s

In-band interference rejection (typ. 14dB)

s

-103dBm Sensitivity (IF BW = 470kHz)

s

AGC around LNA and Mixer

s

Low supply voltage (3 to 6V)

s

2 stage power-down for low current applications

s

Interface for ceramic IF filters up to 15MHz

ORDERING INFORMATION

KESRX04/IG/QP1S (anti-static tubes)

KESRX04/IG/QP1T (tape and reel)

APPLICATIONS

s

Remote Keyless Entry

s

Security, tagging

s

Remote Controlled equipment

KESRX04

260 to 470MHz. ASK Receiver with Power Down

Preliminary Information

DS4997 - 1.5 August 1998

PIN 1

REF

. SPOT

P

(9.80/10.01)

IFFLT1

IFDC1

IFIN

IFDC2

VCC

IFOUT

VCCRF

MIXIP

RFOP

VEERF

RFIN

AGC

PEAK

DATOP

IFFLT2

RSSI

DETB

PD

XTAL1

XTAL2

DF0

DF1

DF2

VCO1

VCO2

VEE

LF

DSN

ABSOLUTE MAXIMUM RATINGS

Supply Voltage Vcc

-0.5V to +7V

Storage temperature,Tstg

-55 to 150

∞

C

Junction Temperature, Tj

-55 to 150

∞

C

RF Input power

+20dBm from 50

Ref

RF Input

SAW

Filter

LNA

agc

mixer

Local

Oscillator

Ceramic

IF Filter

RSSI detector

Noise

reduction

Filter

Anti-jam data filter

Slicer

Sliced

data

2

KESRX04

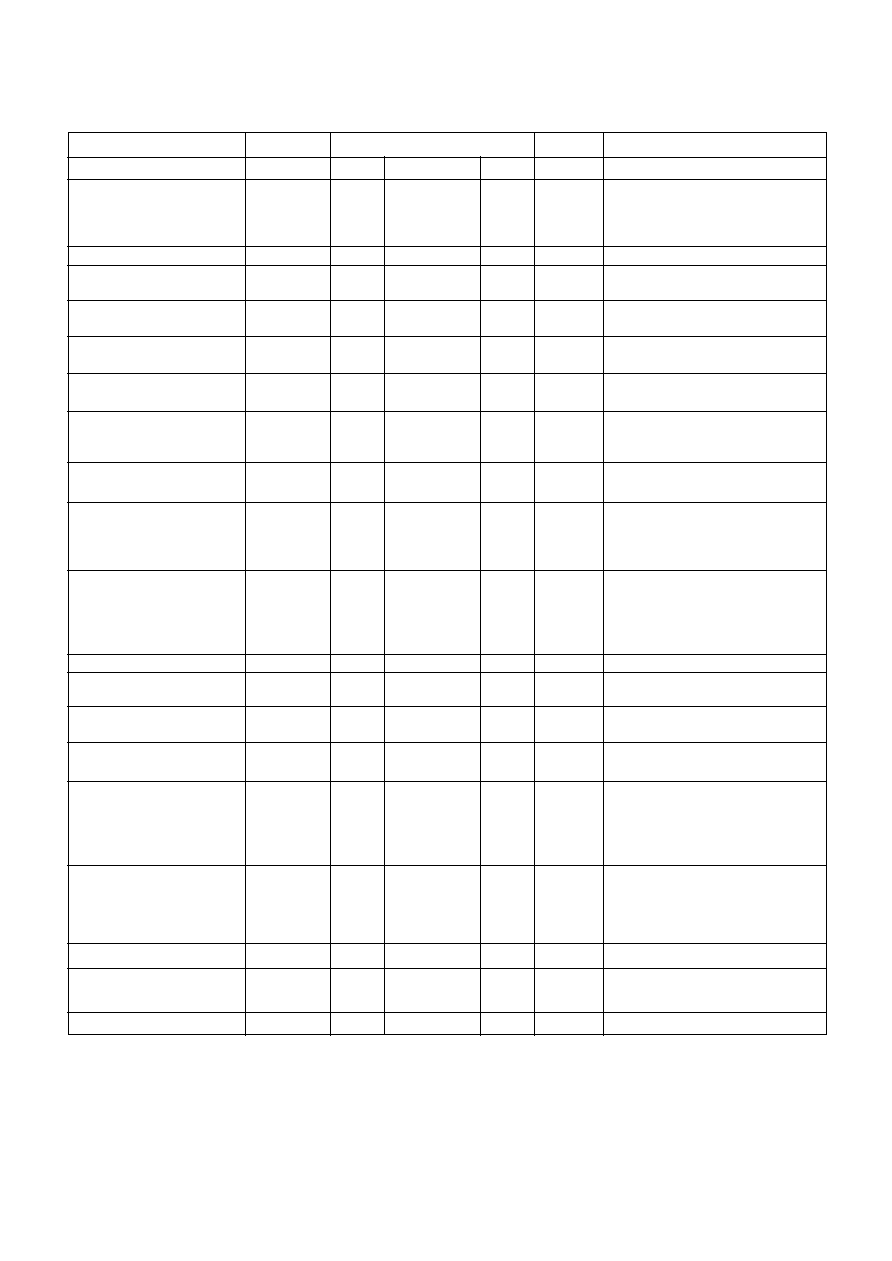

Pin

Symbol

Function

1

IFFLT1

Noise reducing IF filter

2

IFDC1

Log amp dc stability capacitor

3

IFIN

Log amp input

4

IFDC2

Log amp dc stability capacitor

5

VCC

Positive supply

6

IFOUT

IF output to external IF filter

7

VCCRF

Positive supply for RF circuits

8

MIXIP

Mixer input

9

RFOP

Output from LNA

10

VEERF

Negative supply for RF circuits

11

RFIN

Input to LNA

12

AGC

RF AGC time constant

13

PEAK

Data signal peak detect

14

DATOP

Sliced data output

15

DSN

Data slice level

16

LF

PLL loop filter

17

VEE

Negative supply

18

VCO2

Voltage controlled oscillator

19

VCO1

Voltage controlled oscillator

20

DF2

Data filter

21

DF1

Data filter

22

DF0

Data filter

23

XTAL2

Crystal oscillator

24

XTAL1

Crystal oscillator

25

PD

Power down

26

DETB

Anti-jam detector input

27

RSSI

RSSI output

28

IFFLT2

Noise reducing IF filter

PIN DESCRIPTION

DESCRIPTION

The single-conversion super-heterodyne receiver approach

is now generally considered the way forward for ISM band type

applications because of lower cost, superior selectivity, lower

radiation, and flexibility over other techniques. For power-

conscious, hand-held applications KESRX04 provides im-

proved performance and flexibility on a lower 3.0V supply and

a power-down feature allows faster switch-on times for use in

a pulsed power saving mode.

Although this is a relatively simple receiver, the flexibility of

using an external IF filter allows the designer to choose both

the selectivity and the IF in order to optimise the performance

for a wide range of applications and locations world wide.

The KESRX04, with its Anti-jamming detector circuit, is an

ideal ASK / OOK receiver for difficult reception areas caused

by interference such as "Amateur Radio Repeater Stations"

and Wireless Stereo Head-Phones". Operation is possible

with interfering signals which are more than 14dB stronger that

the wanted signal (IF bandwidth = 470kHz.), without the cost

penalities of increased IF selectivity and frequency accuracy.

Figure 2 is the system block diagram for the device with an

external ceramic IF filter, SAW fillter and noise reduction filter.

3

KESRX04

ELECTRICAL CHARACTERISTICS Test conditions

T amb = ≠40

∞

C to + 85

∞

C, V

CC

= 3.0V to 6.0V. These characteristics are guaranteed by either device characterisation, production

test and or design. They apply within the specified ambient temperature and supply voltage ranges unless otherwise stated using

test circuit Figure 12.

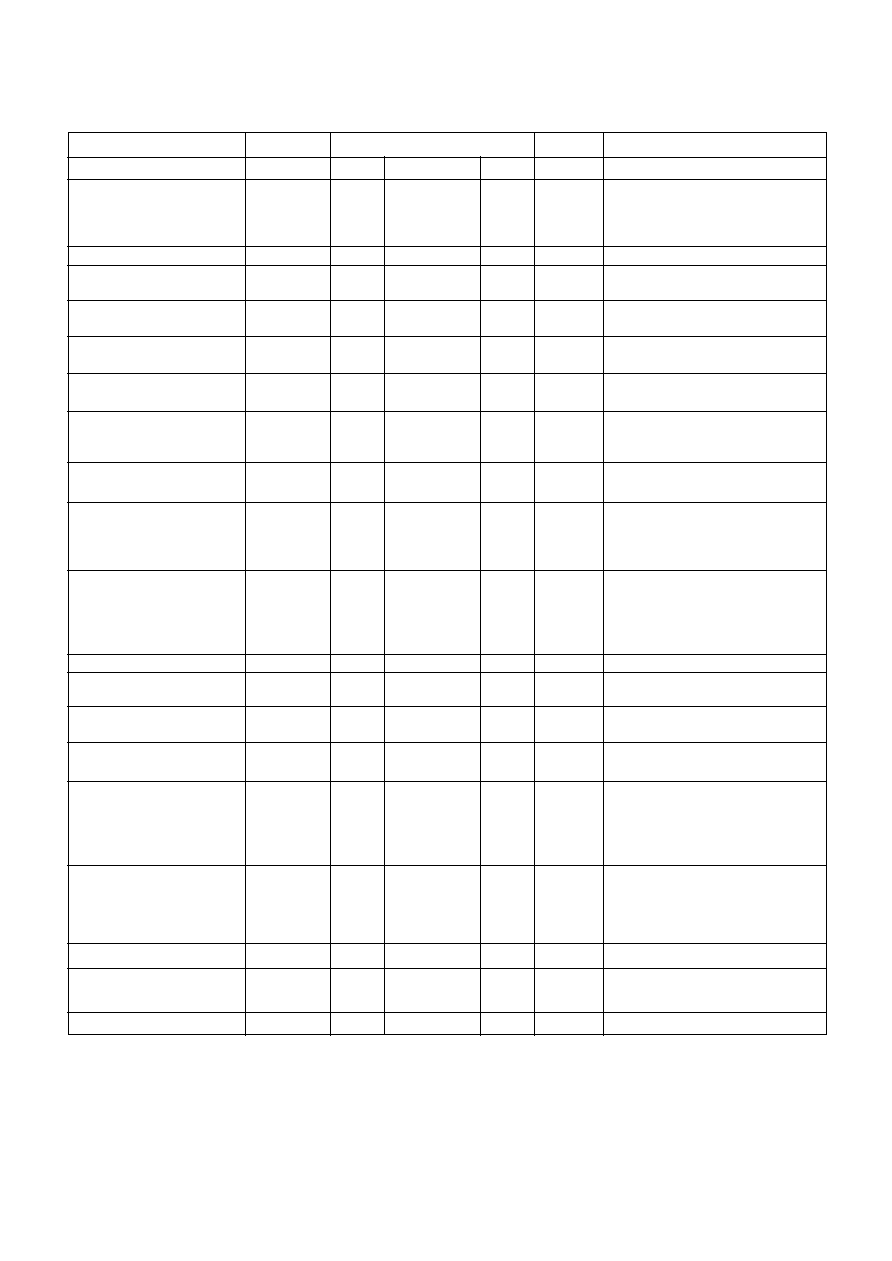

Characteristic

Symbol

Value

Units

Conditions

Min

Typ

Max

Supply voltage

V

CC

3.0

6.0

V

Ambient temperature

Ta

≠40

+85

∞

C

Test Frequency

470

MHz

local Oscillator

480.7

MHz

local oscillator frequency

configured for high side injection,

except where otherwise specified

ELECTRICAL CHARACTERISTICS D.C.

T amb = ≠40

∞

C to + 85

∞

C, V

CC

= 3.0V to 6.0V. These characteristics are guaranteed by either device characterisation production

test and or design. They apply within the specified ambient temperature and supply voltage ranges unless otherwise stated.

Parameter

Symbol

Value

Units

Condition

Min

Typ

Max

Supply Current

Receive mode (PD2)

Icc

3.7

4.5

mA

All. PD=High. RF input <-50dBm.

Power down (PD1)

Icc1

0.33

0.5

mA

All. PD=Vcc/2 or

high impedance source.

Vcc = 3 to 6.0V (4)

Power down (PD0)

Icc2

33

50

µ

A

All. PD=low

ELECTRICAL CHARACTERISTICS A.C

Parameter

Symbol

Value

Units

Condition

Min

Typ

Max

Input frequency range

fs

260

470

MHz

All

Intermediate Frequency

IF

0.2

15.0

MHz.

All. (8)

Sensitivity (test fixture)

Vin(min)

8.0

23.0

µ

Vrms

20kB/s data rate at 470MHz. (1)

Sensitivity (application)

Vin(min)

1.5

µ

Vrms

Circuit as Figure 11 with SAW filter

removed1kB/s data rate at

433.92MHz. (3)

Overload Performance

Vin(max)

0.5

2.23

Vrms

20kB/s data rate at 470MHz. (2)

PLL control line (pin 16)

ts2

2.0

4.0

mS

All. Circuit as Figure 11 (5)

To achieve 90% of final

Local Oscillator low side

value PD0 to PD2

Injection 423.33 MHz.

PLL control line (pin 16)

ts3

1.0

3.0

mS

All. Circuit as Figure 11 (5)

To achieve 90% of final

Local Oscillator low side

value PD1 to PD2

Injection 423.33 MHz.

Data output Voltage High

Voh

Vcc-0.7V

Volt

Ioh=+10

µ

A

Data output Voltage Low

Vol

0.7

Volt

Iol=-10

µ

A

Conducted emissions

Antenna

5.6

100

µ

Vrms

All Figure 11 (6), local Osc. low

(LO)

side injection = 423.3MHz

.

ESD Protection:

All pins meet 2kV Human Body Model requirement. Except pins 9 and 11, which are limited to 700V

and pins 18 and 19 which are limited to 1.00kV.

4

KESRX04

ELECTRICAL CHARACTERISTICS A.C.

(continued)

These characteristics are typical values measured for a limited sample size. They are not guaranteed by production test.

They are only given as a design guide to assist during the design-in phase of KESRX04.

Parameter

Symbol

Value

Units

Condition

Min

Typ

Max

Anti-jam rejection

+14

dB

Unmodulated interfering signal

= -76dBm 433.82MHz. OOK

modulated wanted signal =

-90dBm 433.92MHz Figure 5 (7)

Internal RF Amplifier

Parallel input impedance

Rfin

1.0 // 1.8

K

// pF Fs=434MHz, Vcc= 5V,

Tamb =25

∞

C

Parallel input impedance

Rfin

1.6 // 1.9

K

// pF Fs=315MHz, Vcc= 5V,

Tamb =25

∞

C

Parallel output impedance

Rfout

8.8 // 1.7

K

// pF Fs=434MHz, Vcc= 5V,

Tamb =25

∞

C

Parallel output impedance

Rfout

18 // 1.8

K

// pF Fs=315MHz, Vcc= 5V,

Tamb =25

∞

C

Noise Figure

NF

4.5

dB

Fs=434MHz; Vcc= 5V,

Tamb =25

∞

C matched 50ohm

environment input and output

Noise matching Impedance

Rfin

1.0 // 4.6

K

// nH Fs=434MHz, Vcc= 5V,

Tamb =25

∞

C

1dB compression point

(input referred)

Rfin

-20

dBm

Fs=434MHz, Vcc= 5V,

Tamb =25

∞

C matched 50ohm

environment input and output

Amplifier gain

RFamp

13

dB

Fs=434MHz., Vcc= 5V,

Tamb =25

∞

C O/P matched to

Mixer input impedance

RF Amplifier is conditionally

stable

MIXER

Parallel input impedance

MIXIP

1.6 // 1.8

K

// pF Fs=434MHz, Vcc= 5V,

Tamb =25

∞

C

Parallel input impedance

MIXIP

1.6 // 1.8

K

// pF Fs=315MHz, Vcc= 5V,

Tamb =25

∞

C

Output impedance

IF1

300

Fs=10.7MHz, Vcc= 5V,

Tamb =25

∞

C

Noise Figure

(Double side band

NF

10

dB

Fs=434MHz; Vcc= 5V,

measurement)

Tamb =25

∞

C

matched 50ohm environment

input and output

Mixer conversion gain

Amix

9

dB

Fs=434MHz., Vcc= 5V,

Tamb =25

∞

C Measured at

input to ceramic filter. Includes

6dB matching loss

IF Strip (RSSI)

IF2 input impedance

4.0

K

IF=10.7MHz, Vcc= 5V,

Tamb =25

∞

C

IF gain of log amp

Alog

80

dB

All, Vcc= 5V, Tamb =25

∞

C

5

KESRX04

Notes:

1.

The Sensitivity of the test fixture Figure 12 is degraded by loading the input to RF amplifier with 50 ohms, lack of image

rejection and increasing the data filter bandwidth to 50kHz. Sensitivity is defined as the average signal level measured

at the input necessary to achieve a bit error ratio of 0.01 where the input signal is a return to zero pulse at 470MHz.,with

an average duty cycle of 50%, 20kB/s data rate with the receiver bandwidth set to 470kHz.

2.

Peak RF input level, pin RFIN, to overload the demodulator with the AGC operating. Equivalent to +7dBm for 50 ohm

input impedance. Where the input signal is a return to zero pulse at 470MHz. with an average duty cycle of 50%.

20kB/s data rate with the receiver bandwidth set to 470kHz.

3.

Sensitivity is defined as the average signal level measured at the input necessary to achieve a bit error ratio of 0.01 where

the input signal is a return to zero pulse with an average duty cycle of 50%, 1kB/s data rate. Equivalent to -103dBm for

50ohm input impedance. Does not include insertion loss of SAW filter at RF input but does include IF filter of 470kHz

3dB bandwidth and a data filter bandwidth of 5kHz. This equates closely to a measurement of tangential sensitivity.

4.

The performance of the power down option PD1 to PD2 cannot be guaranteed below 3V for temperatures less than 0

∞

C

5.

Time taken for PLL lock voltage to achieve 90% transition point of the control signal and the VCO frequency to achieve

within 470kHz of the final frequency. The time taken to acquire PLL acquisition is governed by the PLL loop filter (C12,

C1 and R2) and the crystal oscillator components (XTAL1, C13 and C14). The dominant term for PLL aquistion is the start-

up time of the crystal oscillator circuit, provided the PLL loop filter settling time is much less than the crystal oscillator start-

up time. Figure 6 illustrates a suitable test setup for measuring the acquisition time of the PLL. The electrical

characterisation parameters are based on the following set of conditions:

Crystal Oscillator circuit

C13 = C14

=

15pF

XTAL 1

Freq.

6.6128 MHz.

ESR

15.3

L

85.36 mH

C0

1.83 pF

C1

6.8 fF

PLL loop filter

C12 = 1.5 nF,

C1 = 180pF

R1 = 10K

6.

Local oscillator power fed back into 50ohm source at antenna input (RF input). Measured with RF input matching network

shown in Figure 11.

7.

In-band interference rejection for an unmodulated interfering signal at 100kHz. low side from the wanted modulated signal

at 433.92MHz. to achieve a Bit Error Rate =0.01. Figure 5 illustrates a suitable test set-up for measuring the interference

rejection and selectivity of the receiver.

Wanted signal =

-90dBm at 433.92MHz.

(1kB/s. 50% duty cycle)

Interfering signal =

-76dBm at 433.82MHz.

(unmodulated)

Interference rejection typically equals +14dBm.

i.e. in-band interfering signal is 14dBm above the wanted signal level at ≠90dBm.

8.

Actual intermediate frequency determined by choice of crystal and external ceramic filter.