Obsolescence Notice

This product is obsolete.

This information is available for your

convenience only.

For more information on

Zarlink's obsolete products and

replacement product lists, please visit

http://products.zarlink.com/obsolete_products/

FEATURES

s

Low supply Current

s

Power down feature

s

Adjustable output power level

s

Low external part count

s

Fully integrated VCO, PLL and Power Amplifier

Figure.2 block diagram

ORDERING INFORMATION

KESTX01/IG/MPAD (Tape and Reel)

KESTX01/IG/MPAS (Tubes)

The KESTX01 is a single chip ASK (Amplitude Shift Key)

transmitter IC. It is designed to operate in a variety of low

power radio applications including keyless entry, general

domestic and industrial remote control, RF tagging and local

paging systems.

The transmitter offers a high level of integration and per-

formance, which enables the harmonic rejection and funda-

mental power requirements of the ESTI 300 220, and

other governing bodies, to be met.

The basic architecture utilises a crystal reference oscilla-

tor, an integrated frequency multiplying PLL and a power

output stage. The design is centred around the popular

433.92MHz operating frequency and particular emphasis has

been placed on low current drain, including a power≠down

feature which greatly increases battery life.

ABSOLUTE MAXIMUM RATINGS

Junction temperature

-55 to +150

∞

C

Storage temperature

-55 to +150

∞

C

Supply voltage

V

EE

-0.5 to +8.0V

Voltage on any pin

V

EE

-0.5 to V

CC

+0.5V

Notes:

1. The voltage on pin OUT and OUTB (open collector outputs)

can support a higher voltage than this (+14V)

MP14

Figure.1 Pin connections - top view

TXEN

XTAL

OSCILLATOR

XTAL1 XTAL2

LF

VCC

PLL POWER SUPPLY

1

64

PHASE

DETECTOR

VCO

VCC

PWRC

DATA

OUT

OUT B

VEE

VEE

2

1

LF1

VCOTST

VCCPA

KESTX01

400MHz - 460MHz ASK Transmitter

Preliminary Information

Supersedes September 1996 version, DS4548 - 2.0

DS3969 - 3.8 August 1998

XTAL2

PWRC

DATA

OUTB

OUT

VCCPA

VEE2

1

1

4

KESTX01

8

7

XTAL1

VCOTST

VEE1

LF

LF1

TXEN

VCC

.

KESTX01

2

KESTX01

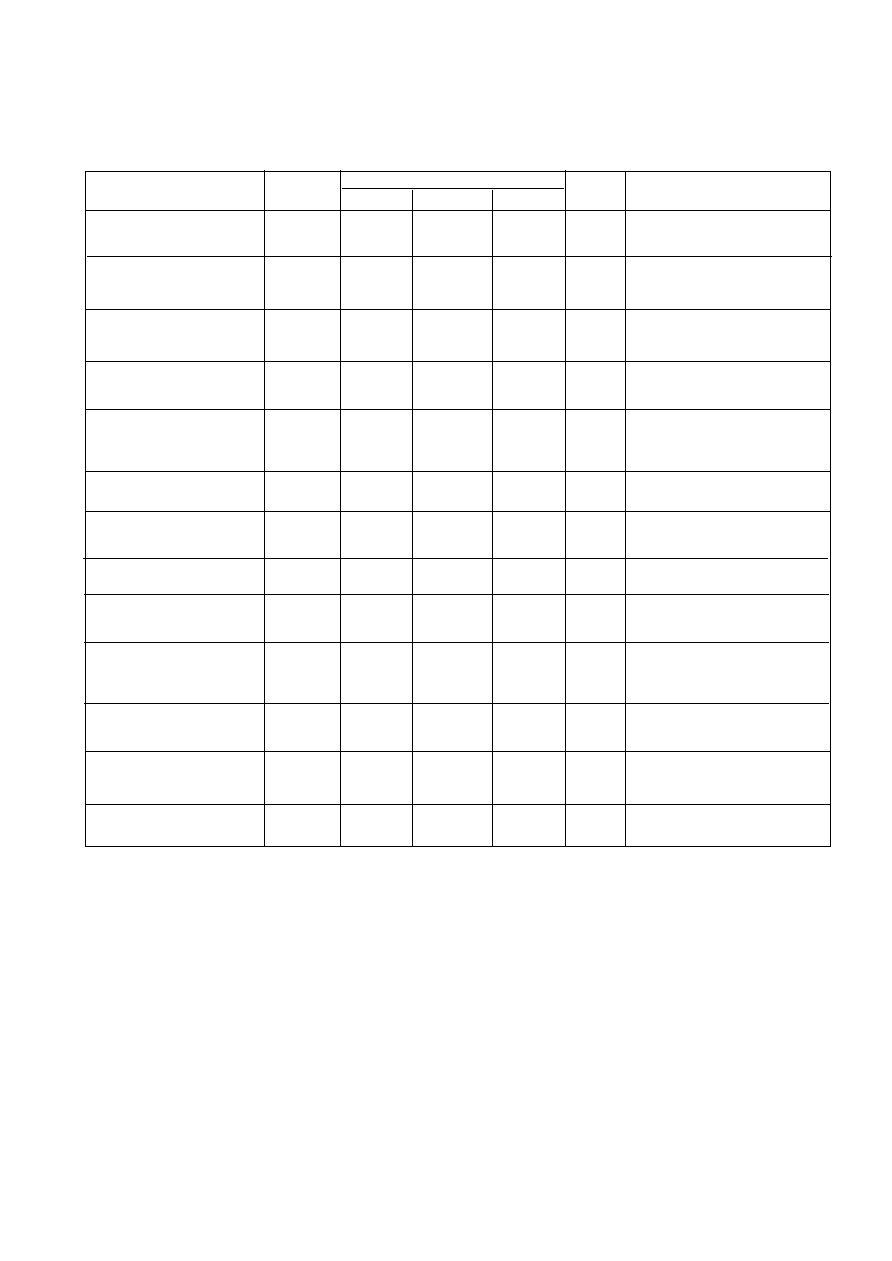

ELECTRICAL CHARACTERISTICS Operating conditions

T amb = ≠40

∞

C to + 85

∞

C, V

CC

= 3.5V to 6.5V. These characteristics are guaranteed by either production test or design.

They apply within the specified ambient temperature and supply voltage ranges unless otherwise stated.

Parameter

Symbol

Value

Units

Conditions

Min

Typ

Max

Power supply voltage

V

CC

3.5

6.5

V

Ambient temperature

Ta

≠40

+85

∞

C

Electro static discharge 2kV all pins ≠ human body model

ELECTRICAL CHARACTERISTICS D.C.

T amb = ≠40

∞

C to + 85

∞

C, V

CC

= 3.5V to 6.5V. These characteristics are guaranteed by either production test or design.

They apply within the specified ambient temperature and supply voltage ranges unless otherwise stated.

Parameter

Symbol

Value

Units

Condition

Min

Typ

Max

Supply current

I

CC

1

0.7

µ

A

V

TXEN

=0V; V

DATA

=0V;Ta=25

∞

C

stand by mode

V

CC

= 7V

Supply current

I

CC

2

1.6

2.8

4

mA

I

mod

=0

µ

A; V

CC

=V

TXEN

3.5V

PLL enable/transmit space

V

DATA

=LOW; 434MHz

Supply current

I

CC

3

6.4

8.5

10.1

mA

I

mod

=150

µ

A; V

CC

=V

TXEN

=3.5V

PLL enable/transmit mark

V

DATA

=HIGH; 434MHz

Supply current

I

CC

4

1.6

3.17

5.0

mA

I

mod

=0

µ

A; V

CC

=V

TXEN

=6.5V

PLL enable/transmit space

V

DATA

=LOW; 434MHz

Supply current

I

CC

5

6.4

9.8

12.5

mA

I

mod

=150

µ

A; V

CC

=V

T

XEN

=6.5V

PLL enable/transmit mark

V

DATA

=HIGH; 434MHz

see note 1

TXEN ≠ transmit enable

Ven

3.5

V

CC

+0.2

V

TXEN ≠ transmit

V

dis

V

EE

≠0.2

0.5

V

disable/stand by

Input bias current TXEN

I

txen

150

µ

A

TXEN = V

CC

transmit enable

Bias voltage pin PWRC

1.0

1.20

1.5

V

I

mod

=150 A V

CC

= 3.5V

Data pin input logic high

V

ih

0.7V

CC

V

CC

+0.5

V

Data pin input logic low

V

il

V

EE

≠0.5

0.3V

CC

V

Data pin input current ≠

I

inl

≠100

µ

A

V

CC

= 7V

logic low

V

DATA

= 2.1V

Data pin input current ≠

I

inh

+100

µ

A

V

CC

= 7V

logic high

V

DATA

= 4.9V

Notes:≠ 1. The maximum supply current is directly related to Imod and hence the output power level. (Figure 4)

3

KESTX01

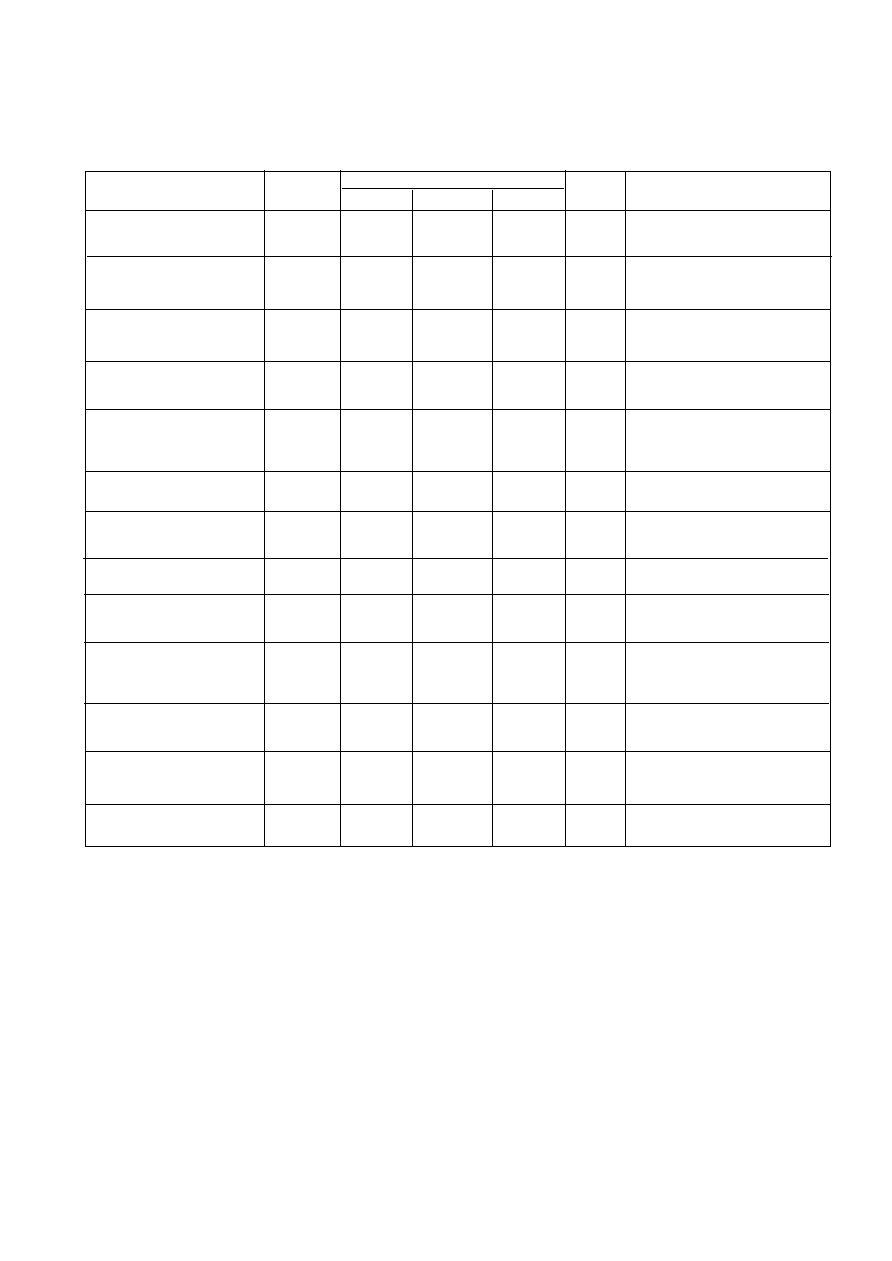

ELECTRICAL CHARACTERISTICS A.C.

T amb = ≠40

∞

C to + 85

∞

C, V

CC

= 3.5V to 6.5V. These characteristics are guaranteed by either production test, characterisation

or design. They apply within the specified ambient temperature and supply voltage ranges unless otherwise stated.

Parameter

Symbol

Value

Units

Conditions

Min

Typ

Max

Output current at

IF75

1.4

2.1

2.8

pk≠pk

I

mod

=75

µ

A, F

o

=434MHz

fundamental, V

CC

=3.5V

mA

Output current at

IF150

2.4

3.8

4.9

pk-pk

I

mod

=150

µ

A, F

o

=434MHz

Fundamental, V

CC

= 3.5V

mA

Output current

IF150(6V5)

3.0

4.6

5.6

pk≠pk

I

mod

=150

µ

A, F

o

=434MHz

fundamental V

CC

= 6.5V

mA

Output level at 2 x

≠32

dBc

I

mod

=150

µ

A, F

o

=434MHz

fundamental see note 1

(1)

Output level at 3 x

≠11

dBc

I

mod

=150

µ

A, F

o

=434MHz (1)

fundamental and all other

spurii see note 1

Phase detector gain

PDG

4.7

8

9.5

µ

A/rad

V

CC

= 3.5V

Extinction ratio

ER

40

dB

see note 2

VCO gain

G

VCO

110

MHz/V

TXEN settling time

Txe

5.0

ms

see note 3

Output sidebands due to

SB

≠40

dBc

I

mod

=150

µ

A, F

o

=434MHz

reference frequency

see note 4

(1, 4)

30dB rise timeRF envelope

T30R

380

ns

of Data pulse

30dB fall timeRF envelope

T30F

430

ns

of Data pulse

VCO operating frequency

400

434

460

MHz

V

CC

= 3.5

Notes:

1. The spurii are specified relative to the fundamental, measured in a 300KHz resolution bandwidth.

2. Extinction ratio is defined as the ratio of the output power SPACE to output power MARK measured at the output

operating fequency.

3. Regulatory issues demand that transmission does not take place until the PLL has acquired lock and the VCO is

operating at its final output frequency. This requirement demands that pin TXEN is set high at least Txe ms prior to the

transmission of any data. This value is dependent on the PLL loop bandwidth and hence on the value of the external

loop filter component values. The specification value above is for the loop filter components shown in the applications

diagram (Figure. 6)

4. Sidebands on the output due to the PLL reference are a function of the PLL loop bandwidth and the application.

Reducing the closed loop bandwidth of the PLL loop will aid in reducing the level of the PLL reference spurii.

4

KESTX01

PIN LISTING

Signal

Description

XTAL1

Crystal oscillator

XTAL2

Crystal oscillator

DATA

Input data

TXEN

Transmit enable/stand by

OUT

Power amplifier output/antenna interface

OUTB

Power amplifier output/antenna interface

(complementary output)

LF

Phase detector output

FUNCTION

When the IC is enabled (TXEN high) a phase locked loop

locks the output of the VCO to a multiple of a crystal defined

reference input. The output of the VCO operates at the final

output frequency and is the input to a power amplifier stage.

The power amplifier directly drives the antenna.

Signal

Description

LF1

VCO control input

PWRC

Output power control

VCCPA

Power amplifier positive supply

VEE2

Power amplifier ground

VEE1

PLL ground

VCC

Positive supply

VCOTST

VCO test control input

Phase locked loop

Dividers

A divide by 64 prescaler is present in the PLL feedback

loop. The final output frequency is then Fo = 64xFref.

Phase detector

The phase detector used is a phase frequency detector

(PFD) with a current (charge pump) output. This phase

detector has a triangular characteristic for an input phase error

in the range ≠2

<

e < 2

. The charge pump provides an

output current in the range

±

50

µ

A and hence gives a phase

detector gain of (50/2

)

µ

A/rad

(

8

µ

A/rad).

The advantage of the PFD over a pure phase detector is

that it is also a frequency discriminator and will always lock the

loop irrespective of the initial frequency offset. The PLL loop

characteristics such as lock≠up time, capture range, loop

bandwidth and VCO reference sideband suppression are

controlled by the external loop filter.

For certain applications spurious sidebands at the

reference frequency must be adequately suppressed and a

3rd order loop is recommended.

VCO

To minimize external component cost,s the VCO is fully

integrated. The frequency of the VCO is controlled by the

voltage on pin LF.

Reference crystal oscillator

A single transistor Collpits crystal oscillator provides a

reference clock for the PLL. The oscillator is configured for

parallel resonant operation in the fundamental mode (typical

operating frequency of 3≠7MHz). The crystal is connected

between pins XTAL2 and VEE1 with external components as

shown in Figure 6.

Alternatively, a reference clock can be provided by an

external source connected to pin XTAL2 Figure 7.

Output stage (PA)

The input signal at pin DATA produces amplitude shift key

(ASK) modulation of the VCO output. This is achieved by

on≠off keying of the bias current in the output power amplifier

stage. The output of the PA is a balanced output (pin OUT and

OUTB) and is current source driven (open collector outputs).

The outputs of which should be D.C. referenced to a positive

supply voltage (anticipated to be V

CC

in most applications).

The current source outputs can drive a PCB antenna directly

(Figure 6) or if a higher output power is required on limited

supply headroom via a simple impedance transforming net-

work. A balanced output stage is used as it automatically

suppresses the even order harmonics of the fundamental. In

order to obtain the benefits of this output stage it is essential

to use a balanced antenna.

Power up

In the intended application, it is expected that the

transmitter will spend a large proportion of time in ``stand by"

not transmitting data. To maximise battery life it is important

that very little quiescent current is taken in this mode.

The ``stand by mode" is selected by setting pin TXEN low

and similarly the transmitter is enabled by setting TXEN high.

To minimize stand≠by current TXEN is used to bias an on≠

chip npn transistor connected in a common collector

configuration (Figure 3 below). This transistor is used to

provide the supply to large portions of the IC. Collapsing the

supply when TXEN is set low results in a very low stand by

current. The voltage on TXEN should not exceed V

CC

by more

than 0.2Volts.

From an application standpoint the TXEN pin must be able

to source the bias current for the input transistor and should

also be decoupled if possible to prevent high frequency noise

directly coupling into the IC power supply. The value of the

decoupling capacitors and the drive capability of the TXEN

source will affect power up delay. Since TXEN enables the

PLL it is therefore essential that it is set high prior to any data

transmission and that it remains high during the

transmission.Therefore three different power drain modes are

possible

(i) Stand by (TXEN low, DATA low)

(ii) PLL Mode/Transmit SPACE (TXEN high, DATA low)

(iii) Transmit MARK (TXEN high, DATA high)