1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

Features

∑ 4 10/100 Mbps auto-negotiating RMII ports

∑ 1 10/100 Mbps auto-negotiating MII/serial port

(Port 4) that can be used as a WAN uplink or as a

5th port

∑ External I

2

C EEPROM for power-up configuration

- Default mode allows operation without external

EEPROM

∑ Up to 4 port-based VLANs

∑ Full wire-speed layer 2 switching on all ports (up

to 1.448 M packets per second)

∑ Internal 1 k MAC address table

- Auto address learning

- Auto address aging

∑ Leading edge QoS capabilities provided based on

802.1p and IP TOS/DS field

- 2 queues per output port

- Packet scheduling based on Weighted Round-

Robin (WRR) and Weighted Random Early

Detection/Drop (WRED)

- Without flow control can drop packets during

congestion using WRED

- 2 levels of packet drop provided

∑ Supports both Full/Half duplex ports

∑ Supports external parallel port for configuration

updates

∑ Port 3 can be used to mirror traffic from the other

3 ports (0-2)

∑ Provides port-based prioritization of packets on up

to 2 ports (0-1)

- Input ports are defined to be high or low priority

- Allows explicit identification of IP Phone ports

∑ Ports 0 & 1 can be trunked to provide a 200 Mbps

link to another switch or server

∑ Utilizes a single low-cost external Pipelined,

SyncBurst SRAM (SBRAM) for buffer memory

- 256 k bytes or 512 k bytes (1 chip)

∑ Flow Control capabilities

- Provides back pressure for half duplex

- 802.3x flow control for full duplex

∑ Special power-saving mode for inactive ports

∑ Ability to support WinSock2.0 and Windows2000

smart applications

∑ Transmit delay control capabilities

- Provides maximum delay guarantee (<1 ms)

- Supports mixed voice-data networks

∑ Optimized pin-out for easy board layout

November 2003

Ordering Information

MDS105AL

208 Pin PQFP

-40

∞C to +85∞C

MDS105

Unmanaged 5-Port 10/100 Mbps

Ethernet Switch

Data Sheet

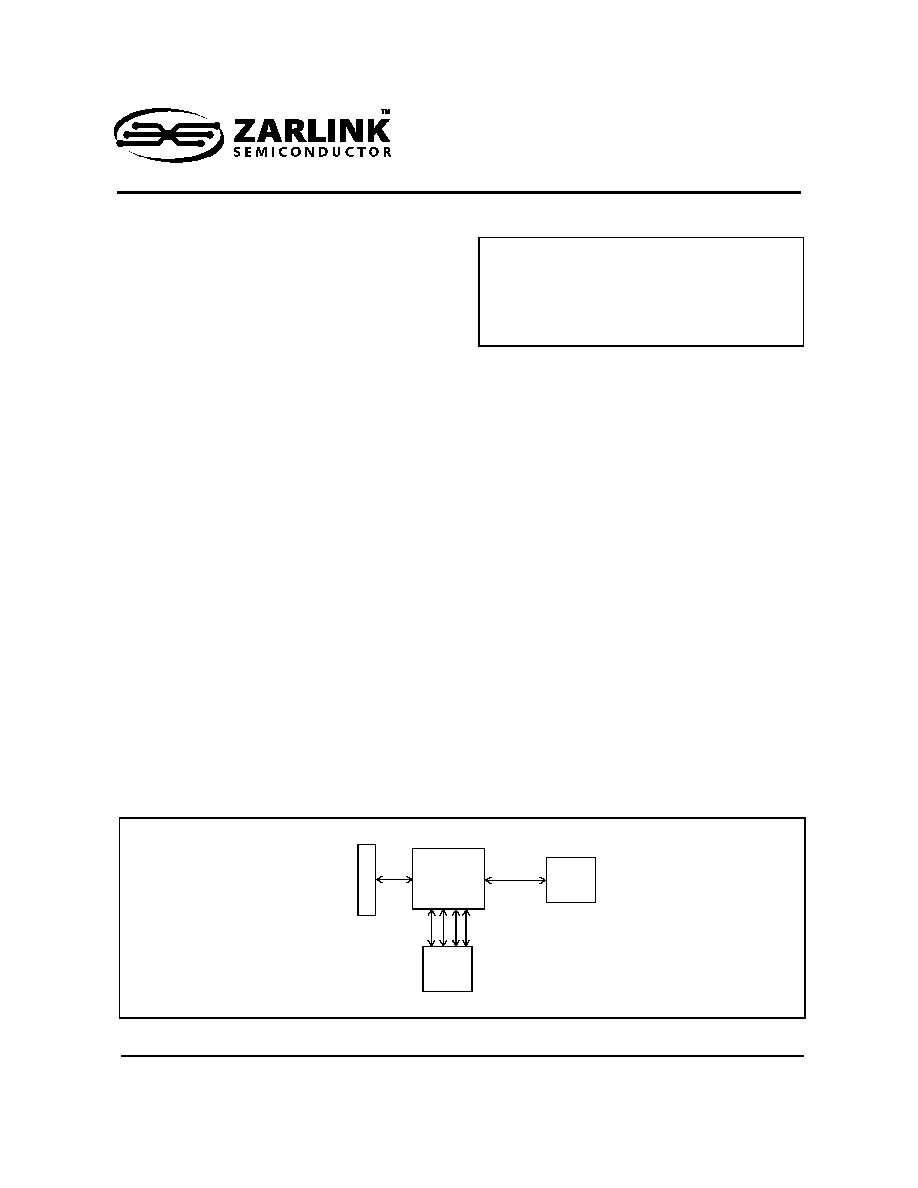

Figure 1 - System Block Diagram

MDS105

5-Port

Switch

Chip

S

S

R

A

M

10/100

Phy

10/100

Phy

Quad

RMII

MII

MDS105

Data Sheet

2

Zarlink Semiconductor Inc.

Description

The MDS105 is a fully integrated 5 port Ethernet switch designed to support the low-cost requirements of

unmanaged switch applications. The MDS105 provides features that are normally not associated with plug-and-

play technology, while not requiring an external processor to facilitate their utilization.

The MDS105 begins operating immediately at power-up, learning addresses automatically and forwarding packets

at full wire-speed to any of its four output ports or the uplink expansion port. The default configuration allows

operation without using an external EEPROM.

With an EEPROM to configure the device at power-up, however, the MDS105 provides flexible features: port

trunking, port mirroring, port-based VLANs, and Quality of Service (QoS) capabilities that are usually associated

only with managed switches.

The built-in intelligence of the MDS105 allows it to recognize and offer packet prioritization using Zarlink's QoS

scheme. Packets are prioritized based upon their layer 2 VLAN priority tag or the layer 3 Type-Of-

Service/Differentiated Services (TOS/DS) field. This priority can be defined as transmit and/or drop priority.

The MDS105 can be used to create a 4 port unmanaged switch with one WAN router port by connecting a CPU

(ARM or MPC 850) to the additional MII port (Port 4). The only external components needed are the physical layer

transceivers and a single SBRAM, resulting in a low total system cost.

Designed to support the requirements of converging networks, the MDS105 utilizes a power conserving

architecture. To further enhance this power management, the chip automatically detects when a switch port is not

being utilized, and turns off the logic associated with that port, thereby saving power and reducing the current load

on the switch power supply.

Operating at 66 MHz internally, and with a 66 MHz interface to the external SBRAM, the MDS105 sustains full wire-

speed switching on all 5 ports.

The chip is packaged in a small 208 pin Plastic Quad Flat-Pak (PQFP) package.