THIS DOCUMENT IS FOR MAINTENANCE

PURPOSES ONLY AND IS NOT

RECOMMENDED FOR NEW DESIGNS

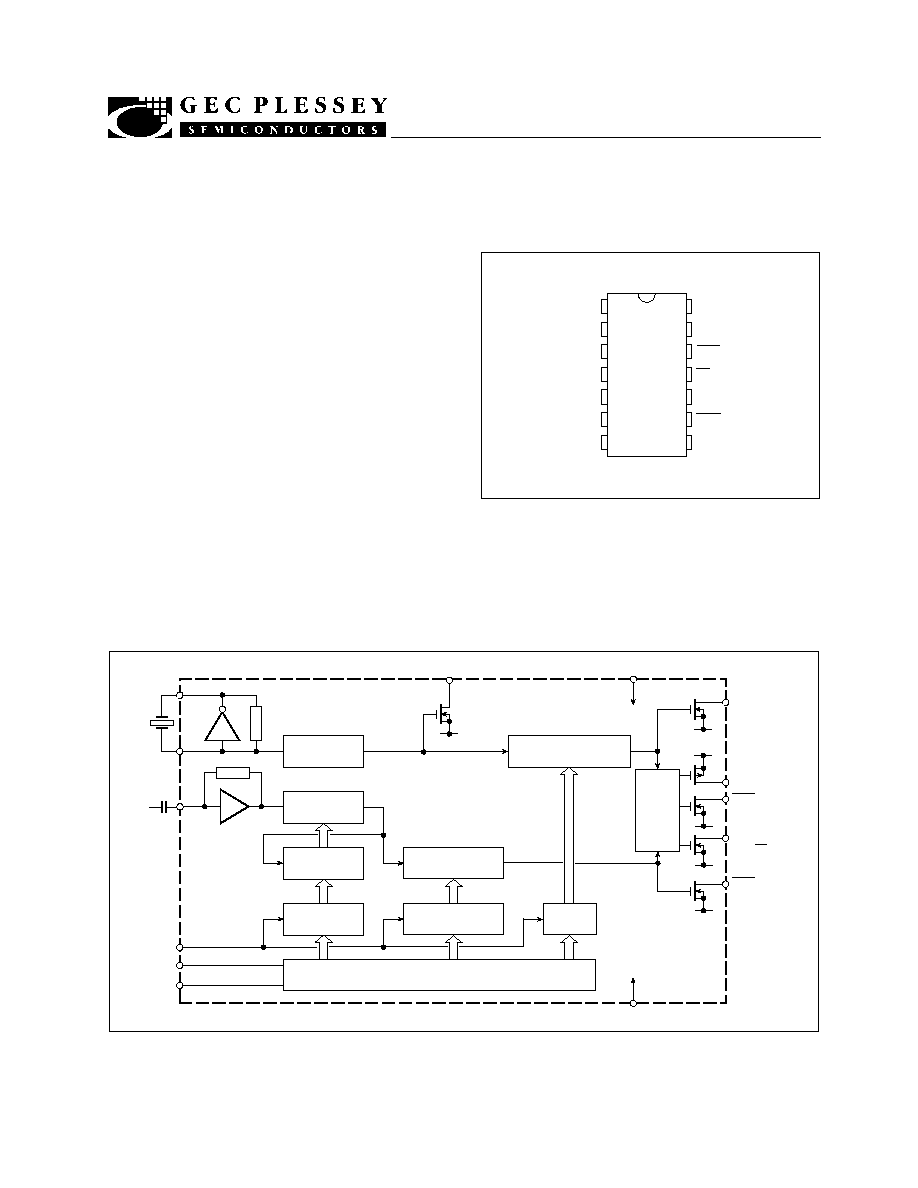

NJ88C30

Fig.1 Pin connections - top view

The NJ88C30 contains all the logic needed for a VHF PLL

synthesiser and is fabricated on the GPS high performance, small

geometry CMOS process. The circuit contains a reference oscillator

and divider, a two-modulus prescaler and 4-bit control register, a

12-bit programmable divider, a phase comparator and the

necessary data input and control logic.

COMP FREQ

f

UP

f

DN

LD

VCO

P DIV OUT

V

DD

GROUND

DATA TRANSFER

CLOCK

DATA

CRYSTAL MON

CRYSTAL IN

CRYSTAL OUT

1

2

3

4

5

6

7

14

13

12

11

10

9

8

NJ88C30

ORDERING INFORMATION

NJ88C30 KA DP Plastic DIL Package

NJ88C30 KA MP Miniature Plastic DIL Package

FEATURES

s

Low Power CMOS

s

Easy to Use

s

Low Cost

s

Single Chip Synthesiser to VHF

s

Lock Detect Output

APPLICATIONS

s

Mobile Radios

s

Hand Held Portable Radios

s

Sonobuoys

ABSOLUTE MAXIMUM RATINGS

Supply voltage, V

DD

Voltage on any pin

Operating temperature

Storage temperature

20�3V to 6V

20�3V to V

DD

10�3V

230

�

C to

170

�

C

255

�

C to 1125

�

C

DP14, MP14

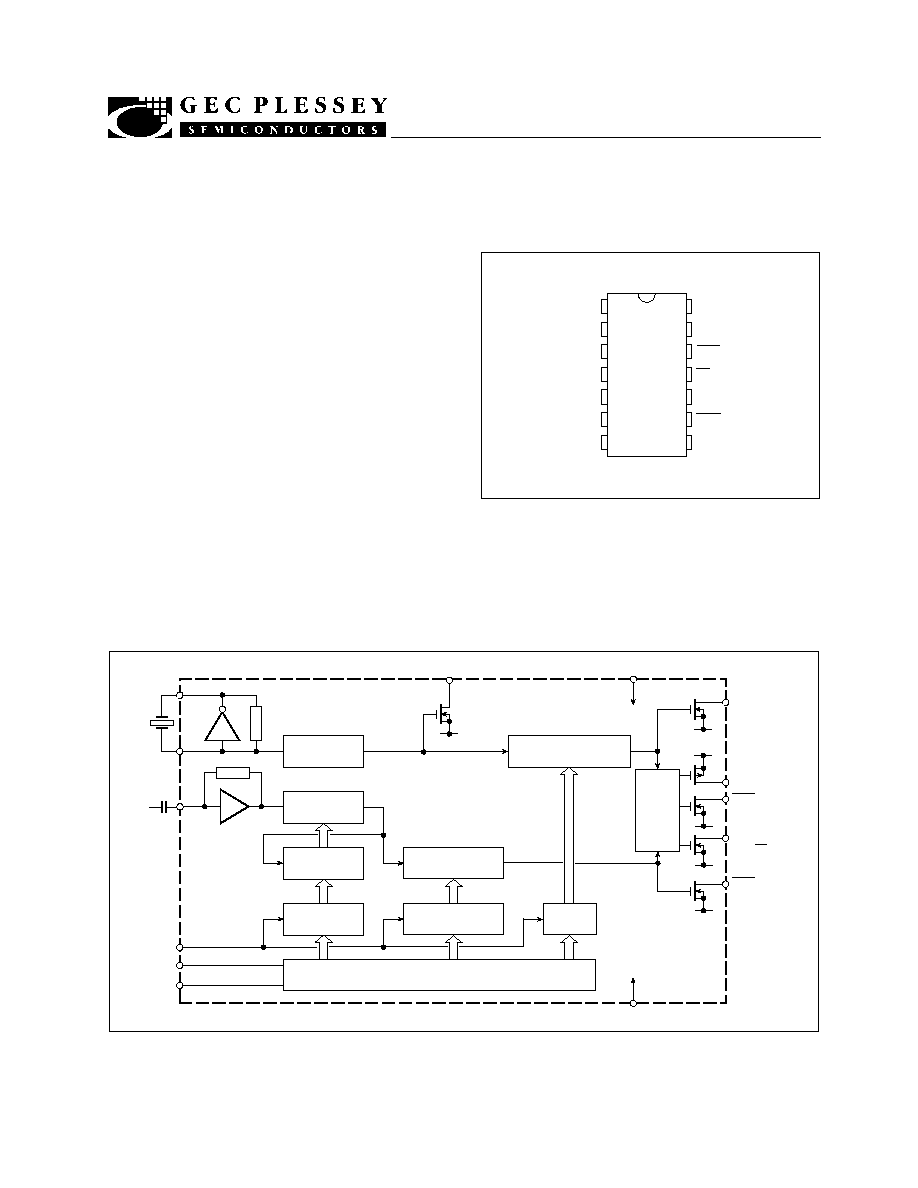

NJ88C30

VHF SYNTHESISER

Fig.2 Block diagram

12-BIT PROG DIVIDER

V

DD

4-BIT COUNTER

4-BIT REGISTER

12-BIT REGISTER

3-BIT

REGISTER

19-BIT SHIFT REGISTER

4

15/16

4

100

REFERENCE DIVIDER

4

1, 5, 10, 20, 2, 4, 8 OR 16

0V

0V

PHASE

COMP

CRYSTAL MON

V

DD

0V

0V

0V

GROUND

1

5

8

CRYSTAL

OUT

CRYSTAL

IN

VCO

f

UP

f

DN

LOCK DETECT

(LD)

P DIV OUT

13

12

11

9

DATA

TRANSFER

DATA

CLOCK

2

4

3

10

6

7

REF

SELECT

(DR2-DR0)

COMP FREQ

14

DS3281-1.1

NJ88C30 IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

NJ88C30

2

ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated):

T

AMB

= �30

�

C to +70

�

C, V

DD

= 5V

�

0�5V

8

6, 7

6

6

6

10

10

10

2, 3, 4

2. 3, 4

2, 3

3, 4

3

2

5

9, 11, 14

12

13

1VRMS VCO input at 200MHz

and f

XTAL

= 10MHz

Parallel resonant,

fundamental crystal

AC coupled

DC coupled

DC coupled

At 200MHz, see Fig. 3

See Fig. 4

V

OUT

= 0�5V

V

OUT

= 0�5V

V

OUT

= 0�5V

V

OUT

= V

DD

20�5V

mA

MHz

Vrms

V

V

Vrms

V/

�

s

V

V

ns

ns

MHz

ns

mA

mA

mA

mA

7

15

1

1

200

2

Supply current

Crystal Oscillator

Frequency

External input level

High level

Low level

VCO Input

Input sensitivity

Slew rate

Input impedance

DATA, DATA TRANSFER and

CLOCK Inputs

High level

Low level

Rise, fall time

Data set-up time

Clock frequency

Transfer pulse width

CRYSTAL MONITOR Output

Current sink

COMP FREQ, LD, P DIV

Current sink

f UP / f DN

Current sink

Current source

1

V

DD

21

1

4

V

DD

21

200

500

0�8

1�6

0�8

0�8

Value

Typ.

Max.

Characteristic

Min.

4

10

5pF//

10k

Units

Conditions

Pin

Fig. 3 Input sensitivity

FREQUENCY (MHz)

0 50 100 150 200

VCO INPUT AMPLITUDE (V RMS)

1�6

1�4

1�2

1�0

0�8

0�6

0�4

0�2

0

GUARANTEED OPERATING AREA

*

TYPICAL

*

Tested as

specified in

Table of

Electrical

Characteristics

NJ88C30

CIRCUIT DESCRIPTION

Crystal Oscillator and Reference Divider

The Reference oscillator consists of a Pierce type oscillator

intended for use with a parallel resonant fundamental crystal.

Typical gain and phase characteristics for the oscillator inverter

are shown in Fig 5. An external reference oscillator may be

used by either capacitively coupling a 1V RMS sinewave into

CRYSTAL IN (pin 6) or, if CMOS levels are available, by direct

connection to CRYSTAL IN.

The reference oscillator drives a 4100 prescaler followed

by a reference divider to provide a range of comparison

frequencies which are selected by decoding the first three bits

(DR2, DR1, DR0) of the input data. The possible division ratios

and the comparison frequencies (channel spacing) if a 10MHz

crystal is used are shown in Table 1.

Fig. 4 Input data timing diagram

FREQUENCY (Hz)

100k 1M 10M

PHASE (DEGREES)

180

120

60

0

FREQUENCY (Hz)

100k 1M 10M

GAIN (dB)

20

10

0

210

Fig. 5 Gain and phase characteristics of reference oscillator inverter

To assist in trimming the crystal, an open drain output at one

hundredth of the reference oscillator frequency is provided on

CRYSTAL MONITOR pin 5

Programmable Divider

The programmable divider consists of a 415/16 two modulus

prescaler with a 4-bit control register, followed by a 12-bit

programmable divider. A 1V RMS sinewave should be

capacitively coupled from the VCO to the divider input VCO pin

(pin 10).

The overall division ratio is selected by a single 16-bit word

(DF15 to DF0), loaded through the serial data bus. A lower limit

of 240 ensures correct prescaler operation; the upper limit is

65535. The VCO frequency in a locked system will be this

division ratio multiplied by the comparison frequency.

Phase Comparator

The phase comparator consists of a digital type phase

comparator with open drain f UP and f DN outputs and an

open drain LOCK DETECT (LD) output. Open drain outputs

from the reference divider and programmable divider are

provided for monitoring purposes or for use with an external

phase comparator. Waveforms for all these outputs are shown

in Fig.6. The duty cycle of f UP and f DN versus phase

difference are shown in Fig. 7. The phase comparator is linear

over a

�

2

range and if the phase gains or slips by more than

2

, the phase comparator outputs repeat with a 2

period.

CLOCK

DATA

DATA SET-UP TIME

TRANSFER PULSE WIDTH

DR2

DR1

DR0

DF15

DF1

DF0

DATA

TRANSFER

3

Total

division

ratio

1600

800

400

200

2000

1000

500

100

Table 1 Reference divider division ratios

DR2

0

0

0

0

1

1

1

1

DR1

0

0

1

1

0

0

1

1

DR0

0

1

0

1

0

1

0

1

Comparison frequency

for 10MHz Ref. Osc.

6�25kHz

12�5kHz

25kHz

50kHz

5kHz

10kHz

20kHz

100kHz

NJ88C30

4

COMP FREQ

P DIV

f

UP

f

DN

LD

COMP FREQ

P DIV

f

UP

f

DN

LD

(a) Phase P DIV output leads

phase COMP FREQ output

(b) Phase P DIV output lags

phase COMP FREQ output

DUTY CYCLE

f

UP

DUTY CYCLE

f

DN

100%

100%

0%

0%

2

2

2

2

2

2

0

0

PHASE DIFFERENCE

PHASE DIFFERENCE

Fig. 6 Phase comparator waveforms

Fig. 7 Phase comparator output characteristics

NJ88C30

PROGRAMMING EXAMPLE

1.Maximum Frequency

For a channel spacing (comparison frequency, f

comp

) of

5kHz when using a 10MHz crystal oscillator, the reference

divider ratio will need to be 2000 (seeTable 1) This is

programmed as binary 100 (= 4

HEX

) in the most significant

three of the 19 bits (MSB programmed first).

2. Minimum Frequency

Using the same crystal frequency and channel spacing

(10MHz, 5kHz), the lower limit of programmable divider ratio of

To obtain the maximum VCO frequency of 200MHz the

programmable divider ratio would be:

= 40310

3

which is 9C40

HEX

The program word would then be as shown in Table 2.

240 = F0

HEX

gives a minimum programmable VCO frequency

of 24035310

3

= 1�2MHz. The program word for this frequency

is therefore as shown in Table 3.

5

Once the phase difference exceeds 2

, the comparator will

gain or slip one cycle and then try to lock on to the new zero

phase difference. Note that very narrow pulses may be seen on

the inactive phase comparator output at the end of the pulse on

the active output, as shown in Fig. 6.

Data Input and Control Register

To control the synthesiser a simple three-line serial input is

used with DATA, CLOCK and DATA TRANSFER signals. The

data consists of 19 bits; the first three, DR2, DR1 and DR0,

control the reference divider while the following sixteen, DF15

to DF0, control the prescaler and programmable divider. Until

the synthesiser receives the DATA TRANSFER pulse, it will

use the previously loaded data; on receiving the pulse it will

switch rapidly to the new data.

APPLICATIONS

A simplified circuit for a synthesiser intended for VHF

broadcast receiver applications is shown in Fig. 8. When the

varicap line drive voltage necessary to tune the required band

is greater than 5V, some form of level shifter such as the

operational amplifier shown in Fig. 8 is required.

14

13

12

11

10

9

8

NJ88C30

1

2

3

4

5

6

7

DATA TRANSFER

CLOCK

DATA

R1 18k

R1' 18k

R2

10k

C1

47n

22k

10n

5 - 65p

4�5MHz

LOCK DETECT (LD)

SL562

1

2

22k

10k

22k

10n

VCO

VARICAP DRIVE

1 -10V

1

12V

1

5V

1

12V

Fig.8. Typical application

200310

6

5310

3

DR

DF

2

1

0

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Binary

1

0

0

1

0

0

1

1

1

0

0

0

1

0

0

0

0

0

0

Hex

4

9

C

4

0

Table 2 Maximum VCO frequency programming (f

XTAL

= 10MHz, f

comp

= 5kHz)

DR

DF

2

1

0

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Binary

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

Hex

4

0

0

F

0

Table 3 MinimumVCO frequency programming (f

XTAL

= 10MHz, f

comp

= 5kHz)

NJ88C30

HEADQUARTERS OPERATIONS

GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon,

Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000

Fax: (0793) 518411

GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017

1500 Green Hills Road,

Scotts Valley, California 95067-0017,

United States of America.

Tel: (408) 438 2900

Fax: (408) 438 5576

CUSTOMER SERVICE CENTRES

� FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Tx: 602858F

Fax : (1) 64 46 06 07

� GERMANY Munich Tel: (089) 3609 06-0 Tx: 523980 Fax : (089) 3609 06-55

� ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

� JAPAN Tokyo Tel: (03) 3296-0281 Fax: (03) 3296-0228

� NORTH AMERICA Integrated Circuits and Microwave Products Scotts Valley, USA

Tel (408) 438 2900 Fax: (408) 438 7023.

Hybrid Products, Farmingdale, USA Tel (516) 293 8686

Fax: (516) 293 0061.

� SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

� SWEDEN Stockholm, Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

� UNITED KINGDOM & SCANDINAVIA

Swindon Tel: (0793) 518510 Tx: 444410 Fax : (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

�

GEC Plessey Semiconductors 1992 Publication No. DS3281 Issue No. 1.1 May 1992

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded

as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company

reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute

any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information

and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury

or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable.

However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such

information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or

use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual

property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in

certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part

of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other

information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the

capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute

any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and

suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does

not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in

significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I

2

C components conveys a licence under the Philips I

2

C Patent rights to use these components in and I

2

C System, provided that the system

conforms to the I

2

C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

For more information about all Zarlink products

visit our Web Site at