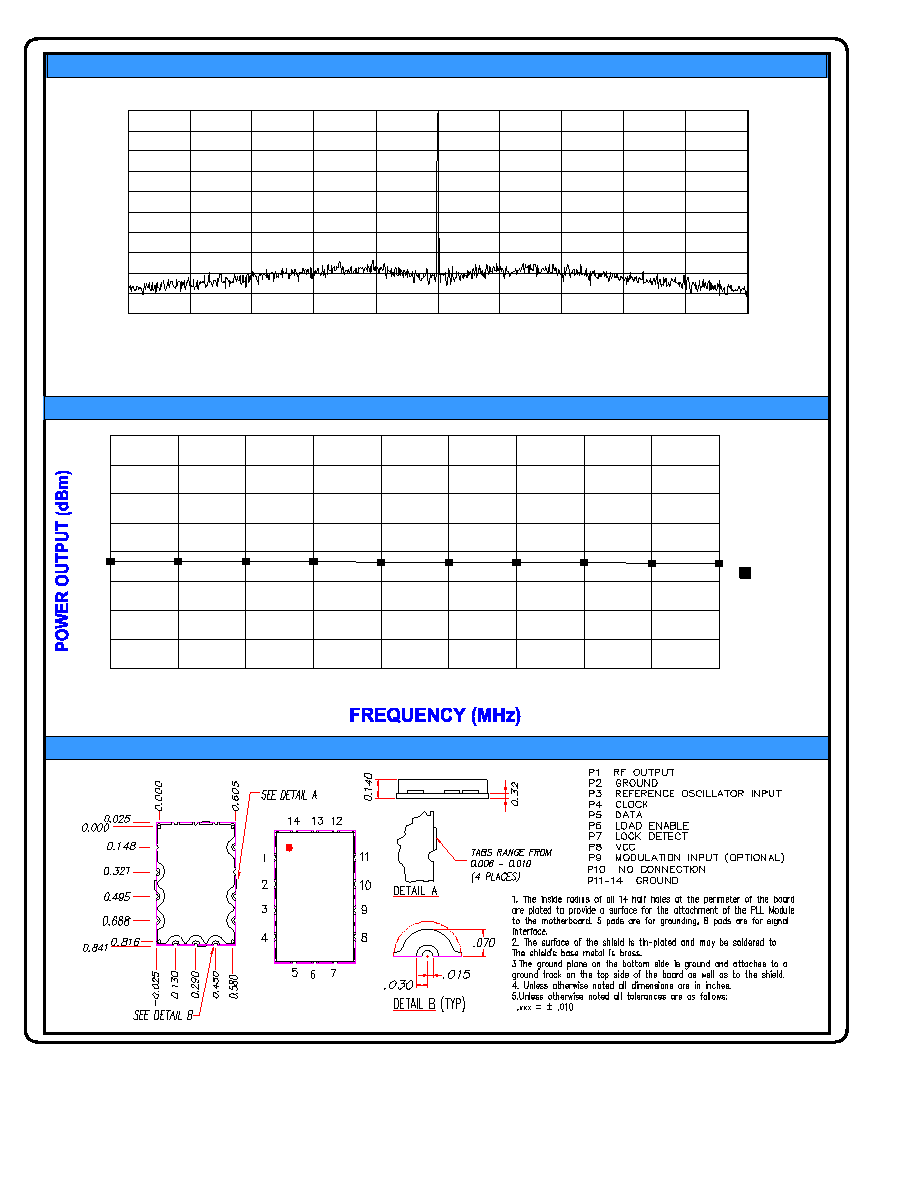

100 Hz

1 kHz

10 kHz

100 kHz

-60

-140

-180

-200

-20

-100

PSN0800A

Basestations

Mobile Radios

Satellite Communications

5

17

787

-70

2.0

-10

8

4

-40 to 85

Frequency Range

RMS Phase Error (100 Hz - 100 KHz)

Harmonic Suppression (2nd, typ.)

Sideband Spurs (typ.)

Switching Speed (typ., adjacent channel)

Startup Lock Time (typ.)

Operating Temperature Range

Package Style

PLL

MHz

∞

dBc

dBc

mSec

mSec

∞C

Vdc

mA

Supply Voltage (Vcc, nom.)

Supply Current (Icc, typ.)

All specifications are typical unless otherwise noted and subject to change without notice.

PHASE NOISE (1 Hz BW, typical)

LOW COST - HIGH PERFORMANCE

© Z-Communications, Inc.

All rights reserved

Page 1

PHASE LOCKED LOOP

FEATURES

APPLICATIONS

PERFORMANCE SPECIFICATIONS

VALUE

UNITS

POWER SUPPLY REQUIREMENTS

APPLICATION NOTES

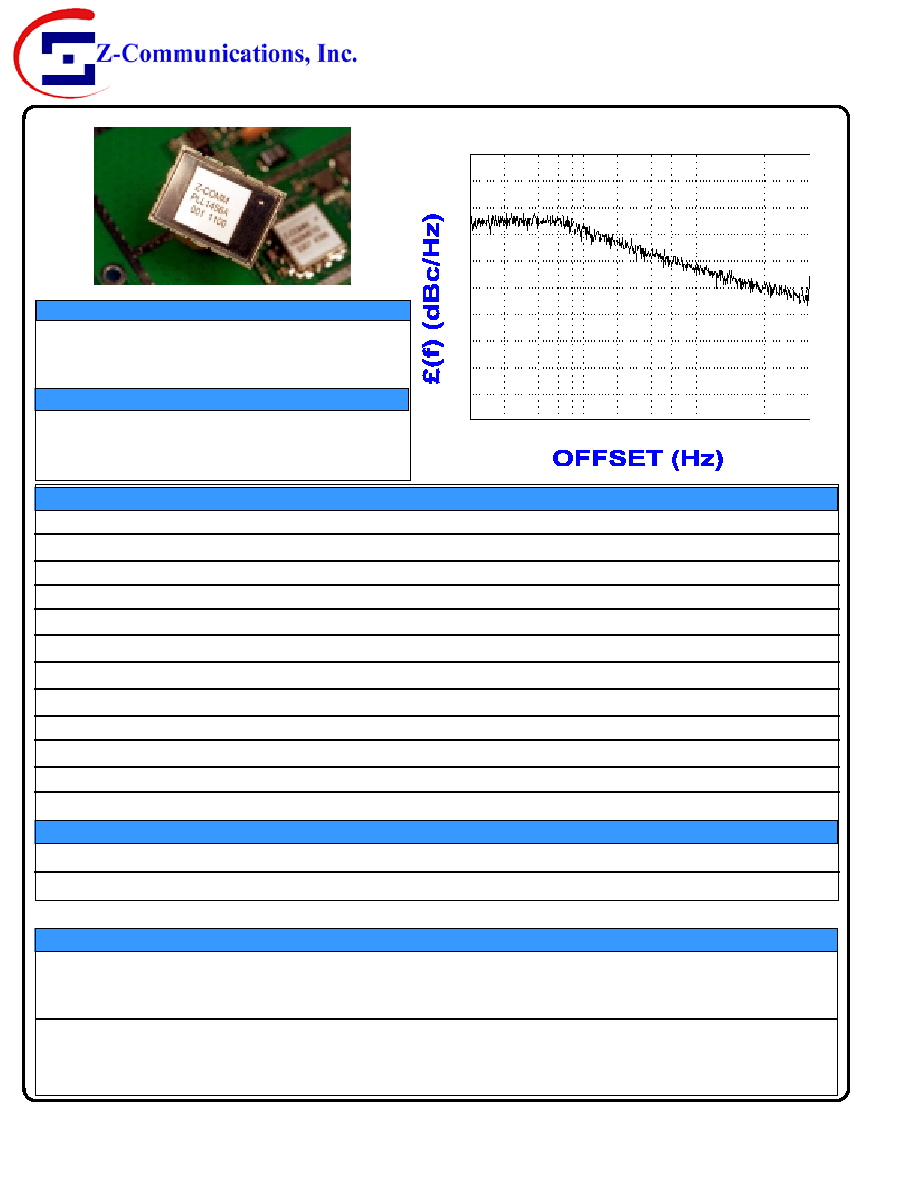

787

MHz

∑

Step Size:

50 KHz

- Style Package

PLL

∑

∑

∑

∑

A1

Rev

∑

AN-107 : How to Solder Z-COMM VCOs / PLLs

∑

AN-200 : Mounting and Grounding of Z-COMM PLLs

∑

AN-201 : PLL Fundamentals AN-202 : PLL Functional Description

NOTES:

Reference Oscillator Signal: 5 MHz<

f

osc

<40 MHz

Frequency Synthesizer: National Semiconductor - LMX2316

9939 Via Pasar ∑ San Diego, CA 92126

TEL (858) 621-2700 FAX (858) 621-2722

Power Output

3±2

dBm

Load Impedance

50

Step Size

50

KHz

1000

821

-

∑ Frequency Range:

-

821

Charge Pump Output Current

µ