eZ8 CPU

UM012811-0904

ZiLOG Worldwide Headquarters � 532 Race Street � San Jose, CA 95126-3432

Telephone: 408.558.8500 � Fax: 408.558.8300 �

www.ZiLOG.com

User Manual

UM012811-0904

Discliamer

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or

to request copies of publications, contact:

ZiLOG Worldwide Headquarters

532 Race Street

San Jose, CA 95126-3432

Telephone: 408.558.8500

Fax: 408.558.8300

www.ZiLOG.com

Document Disclaimer

ZiLOG is a registered trademark of ZiLOG Inc. in the United States and in other countries. All other products and/or service

names mentioned herein may be trademarks of the companies with which they are associated.

�2004 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology

described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR

PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED

IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGE-

MENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN

OR OTHERWISE. Devices sold by ZiLOG, Inc. are covered by warranty and limitation of liability provisions appearing in the

ZiLOG, Inc. Terms and Conditions of Sale. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose Except

with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support sys-

tems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

eZ8 CPU

User Manual

UM012811-0904

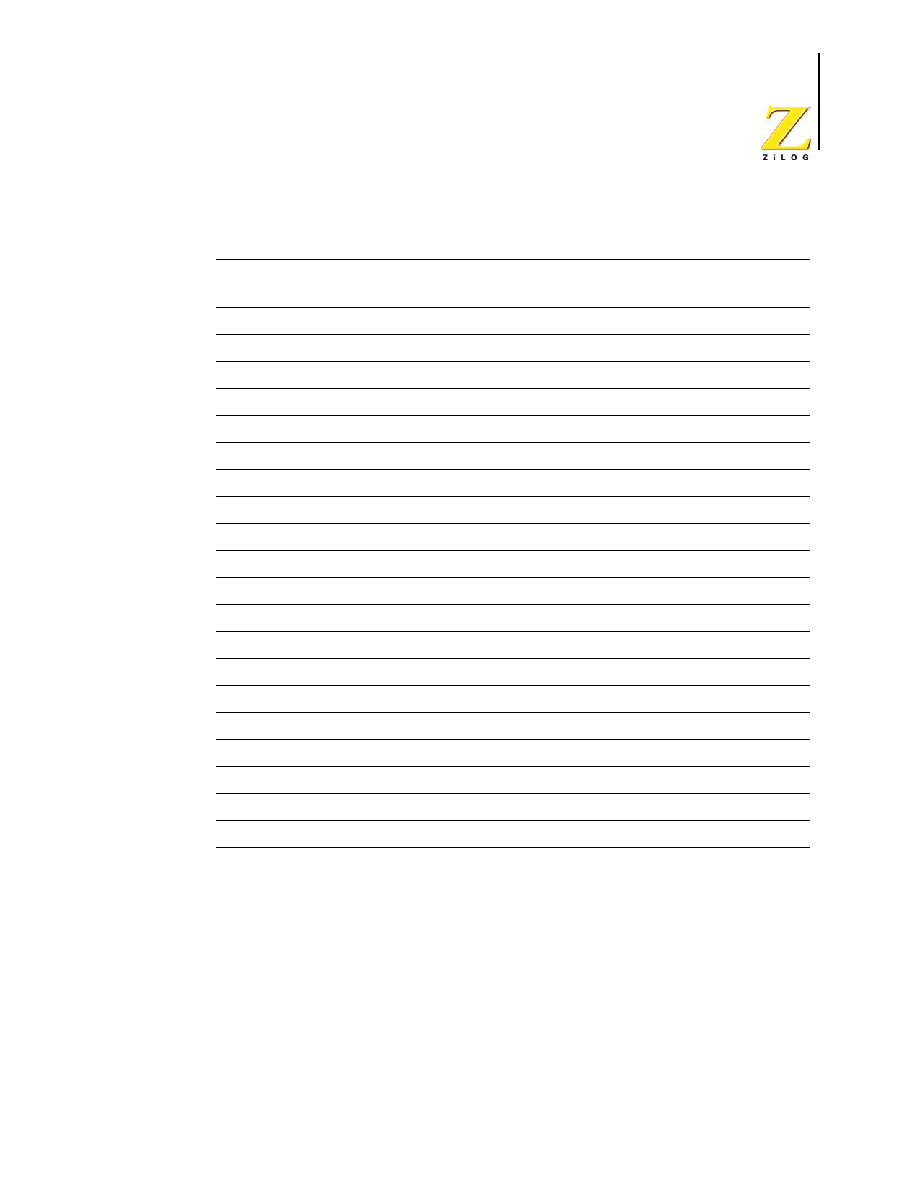

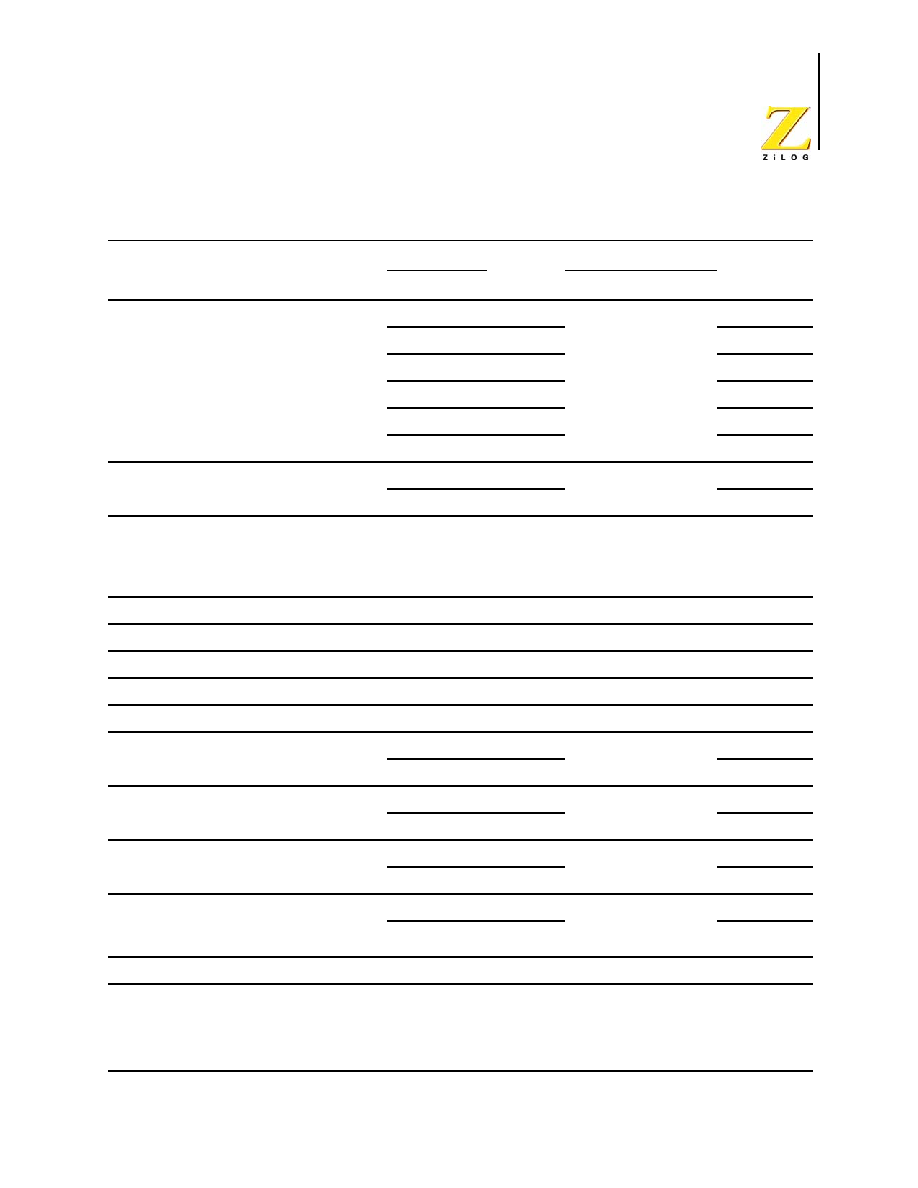

Table of Contents

iii

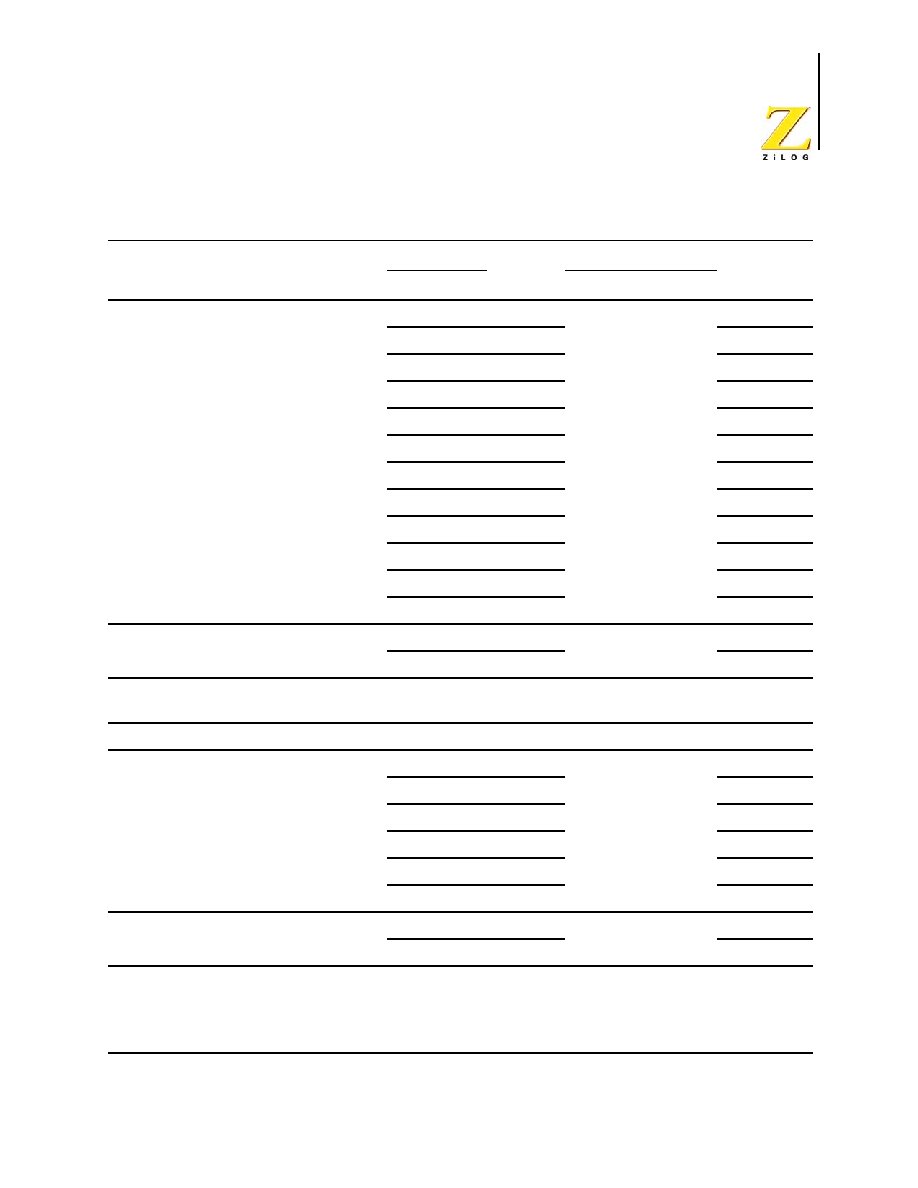

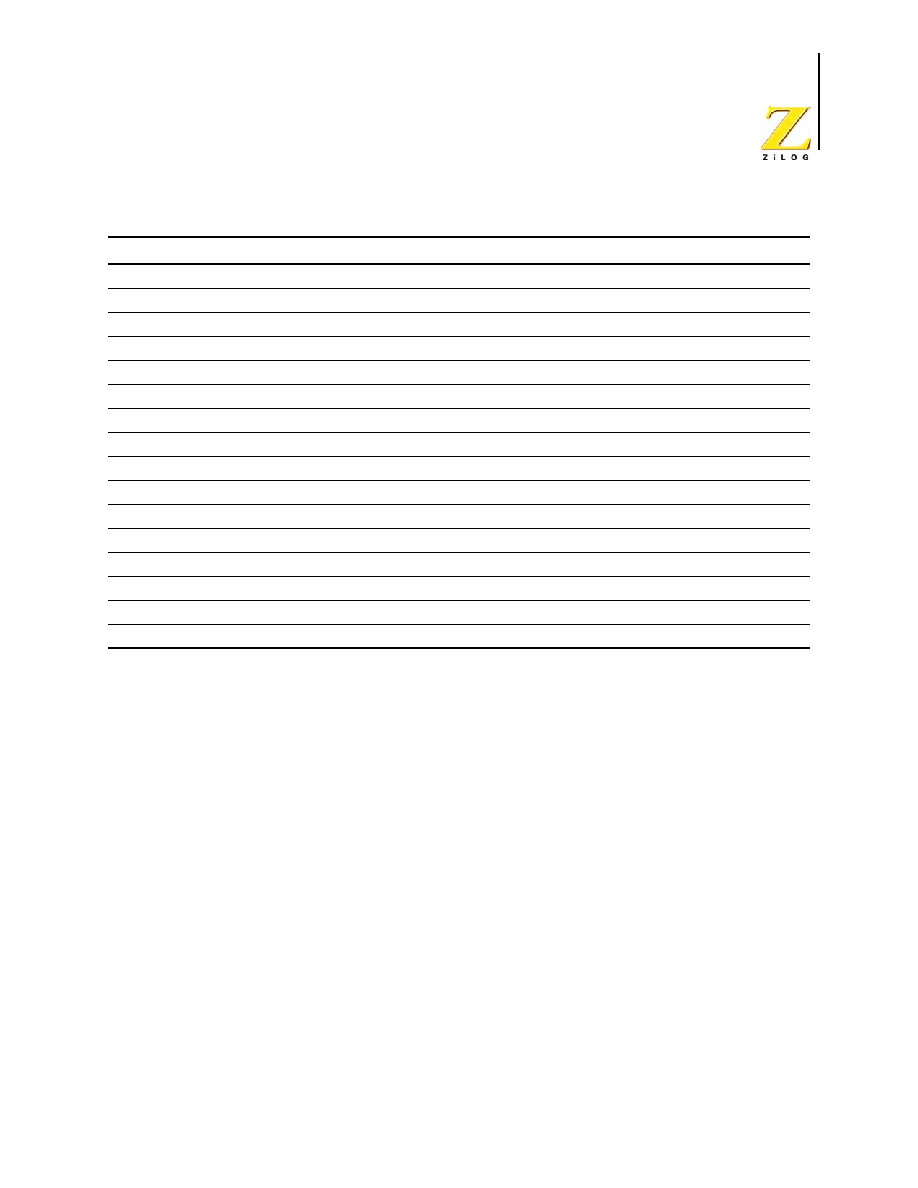

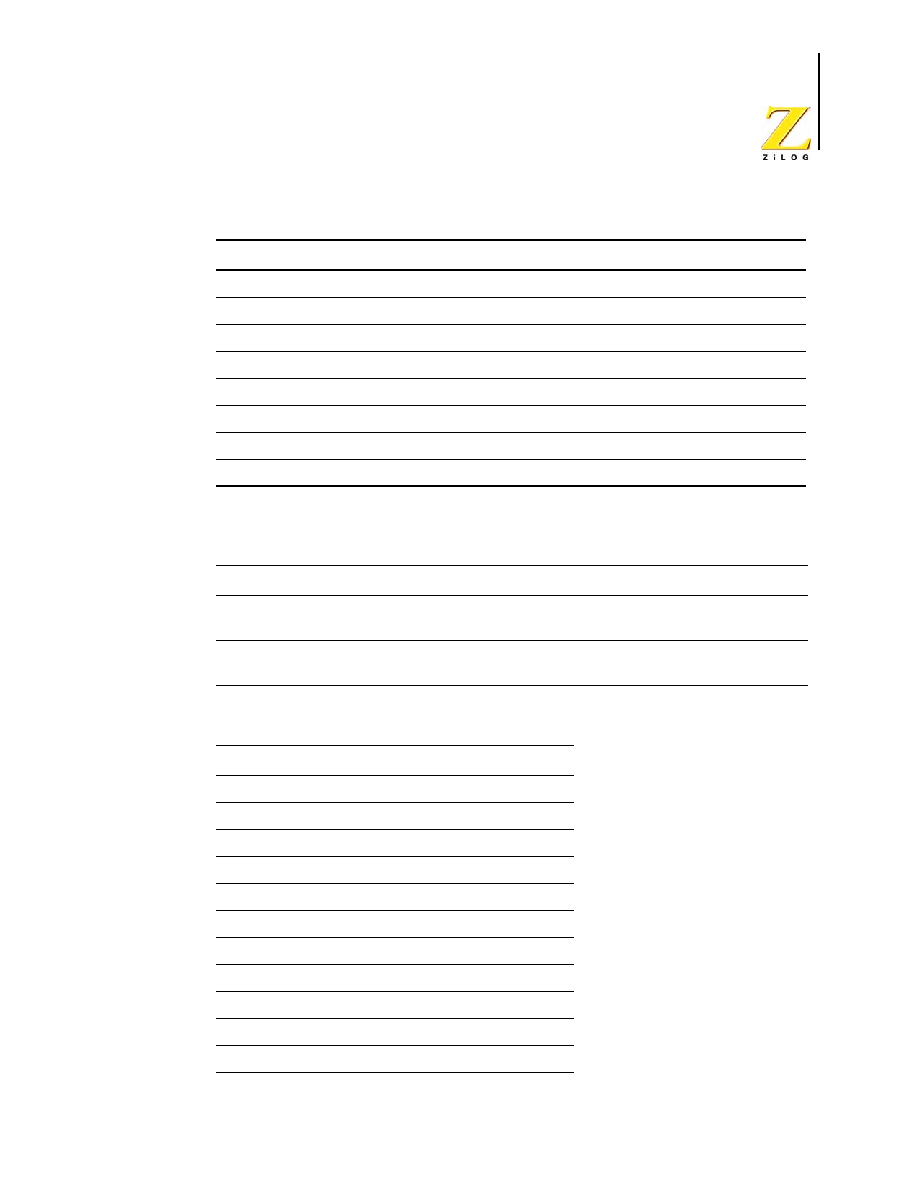

Table of Contents

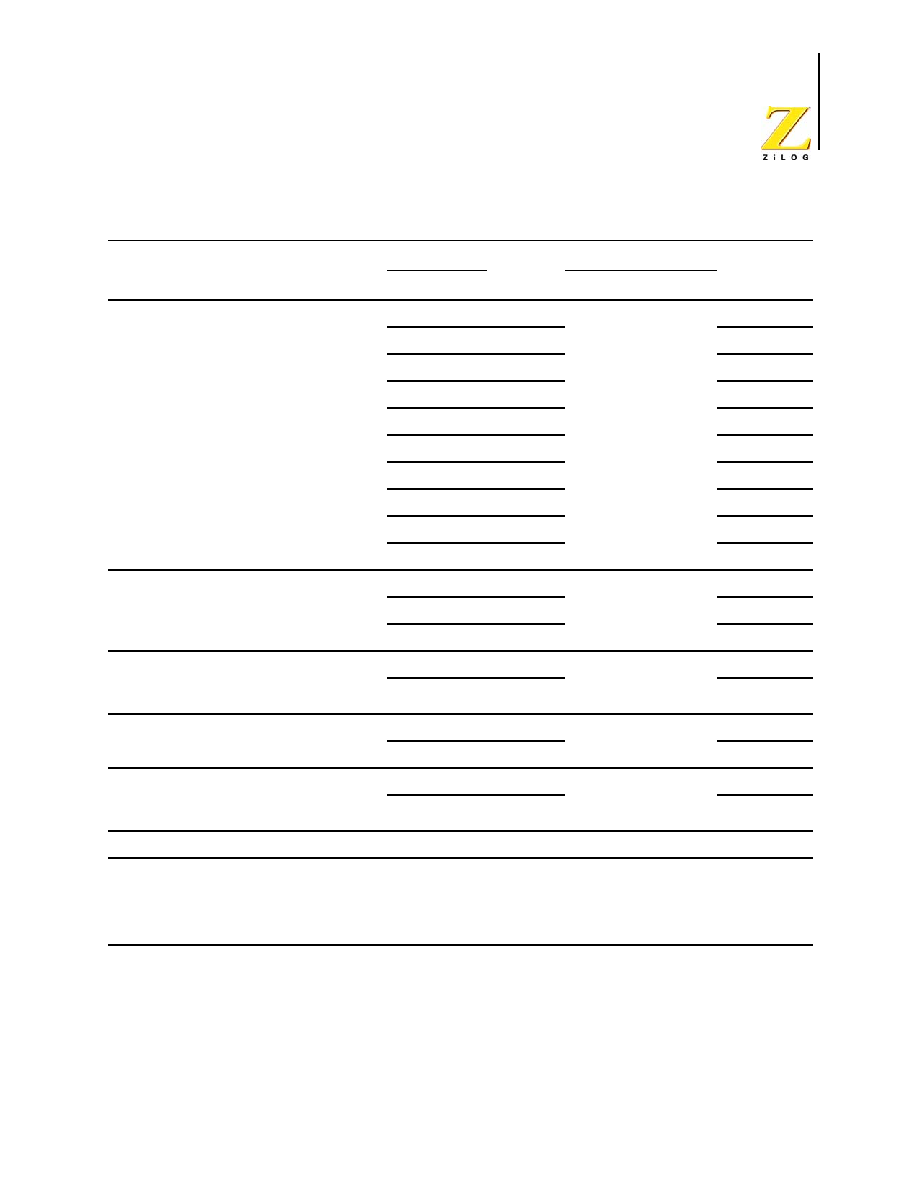

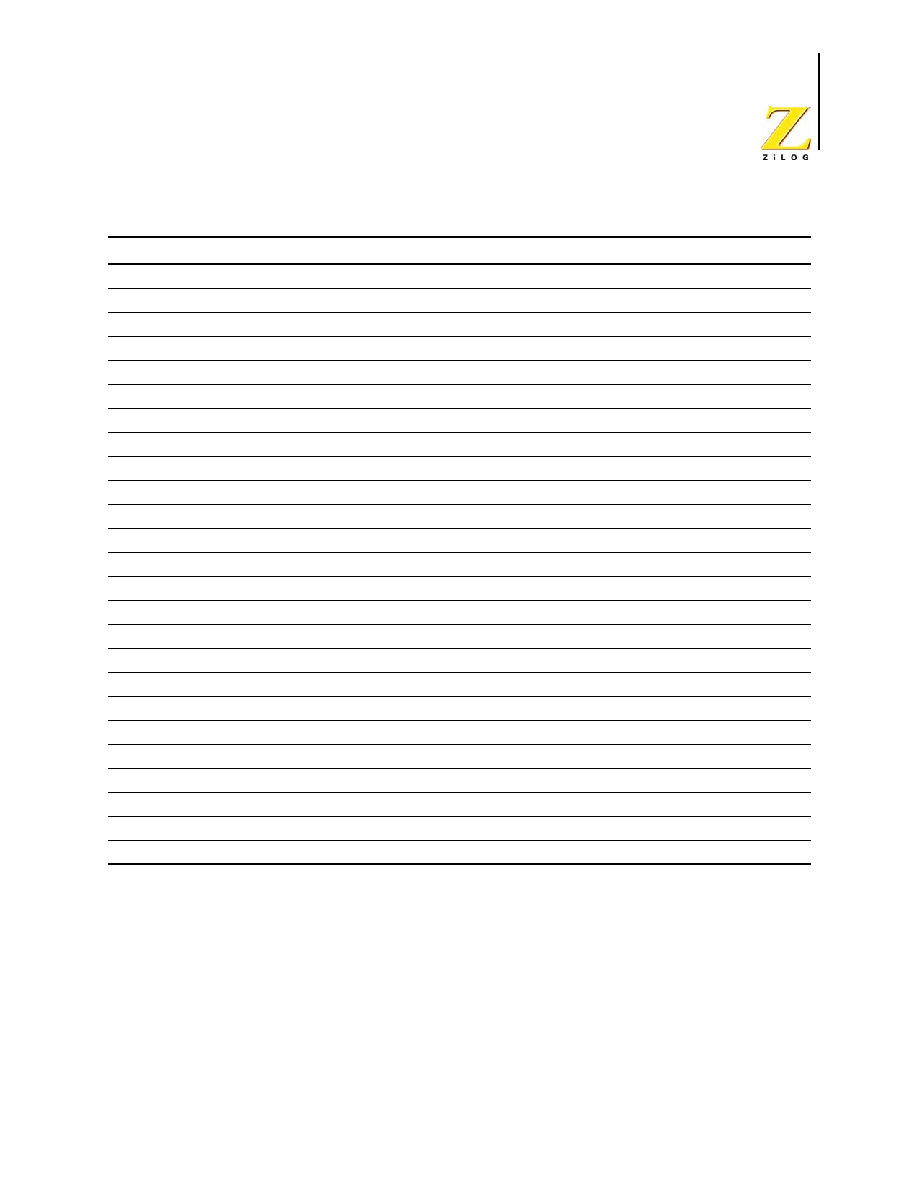

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . v

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .vi

Manual Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Processor Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Fetch Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Instruction State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Program Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

eZ8 CPU CONTROL REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Z8 Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Assembly Language Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

New Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Relocation of the eZ8 CPU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Stack Pointer Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Reset Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Interrupt Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Address Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Register File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Stacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Register Addressing (R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Indirect Register Addressing (IR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Indexed Addressing (X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Direct Addressing (DA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Relative Addressing (RA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Immediate Data Addressing (IM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

UM012811-0904

Table of Contents

eZ8 CPU

User Manual

iv

Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Interrupt Enable and Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Vectored Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Nesting of Vectored Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Polled Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Software Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Illegal Instruction Traps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

eZ8 CPU Instruction Set Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Assembly Language Programming Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Assembly Language Syntax . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

eZ8 CPU Instruction Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

eZ8 CPU Instruction Classes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

eZ8 CPU Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

eZ8 CPU Instruction Set Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Opcode Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Opcodes Listed Numerically . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Assembly and Object Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

eZ8 CPU

User Manual

UM012811-0904

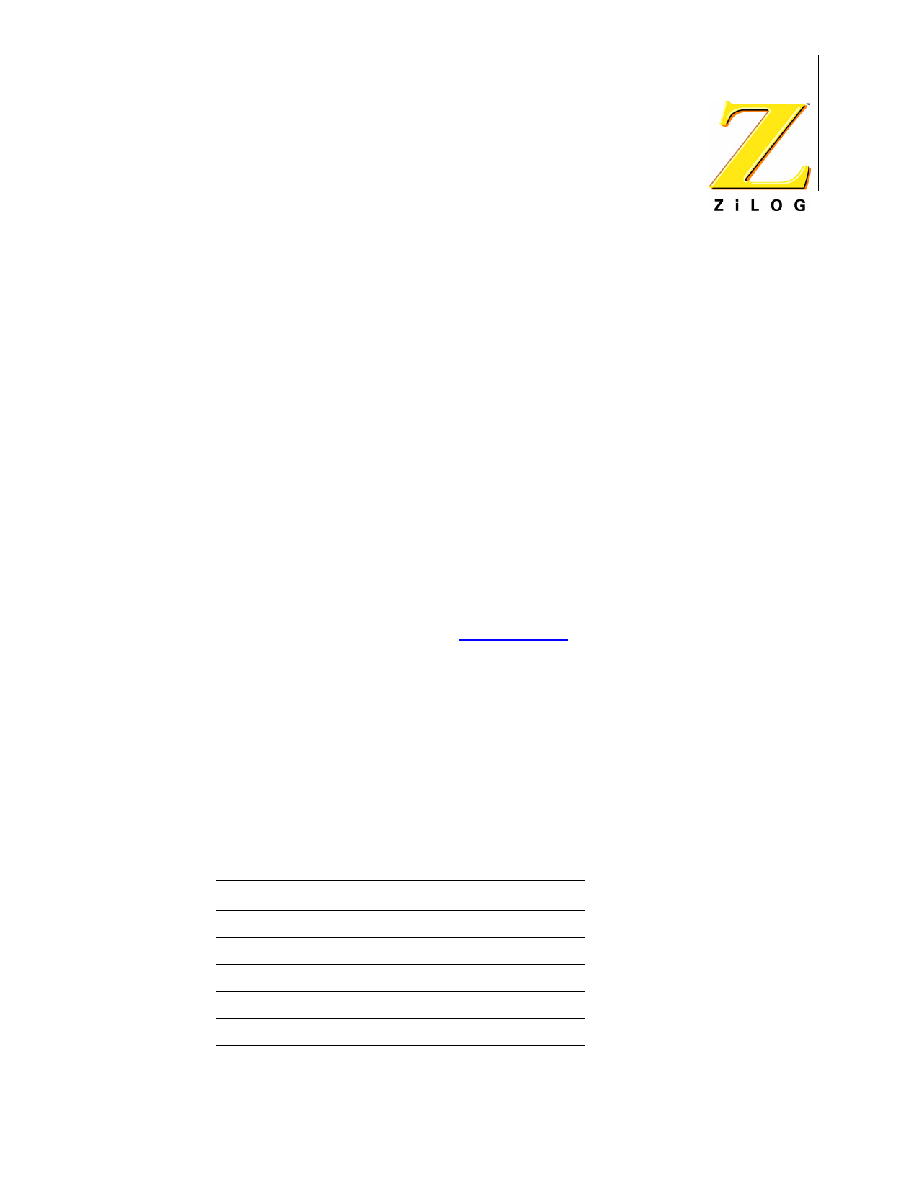

List

of

Figures

v

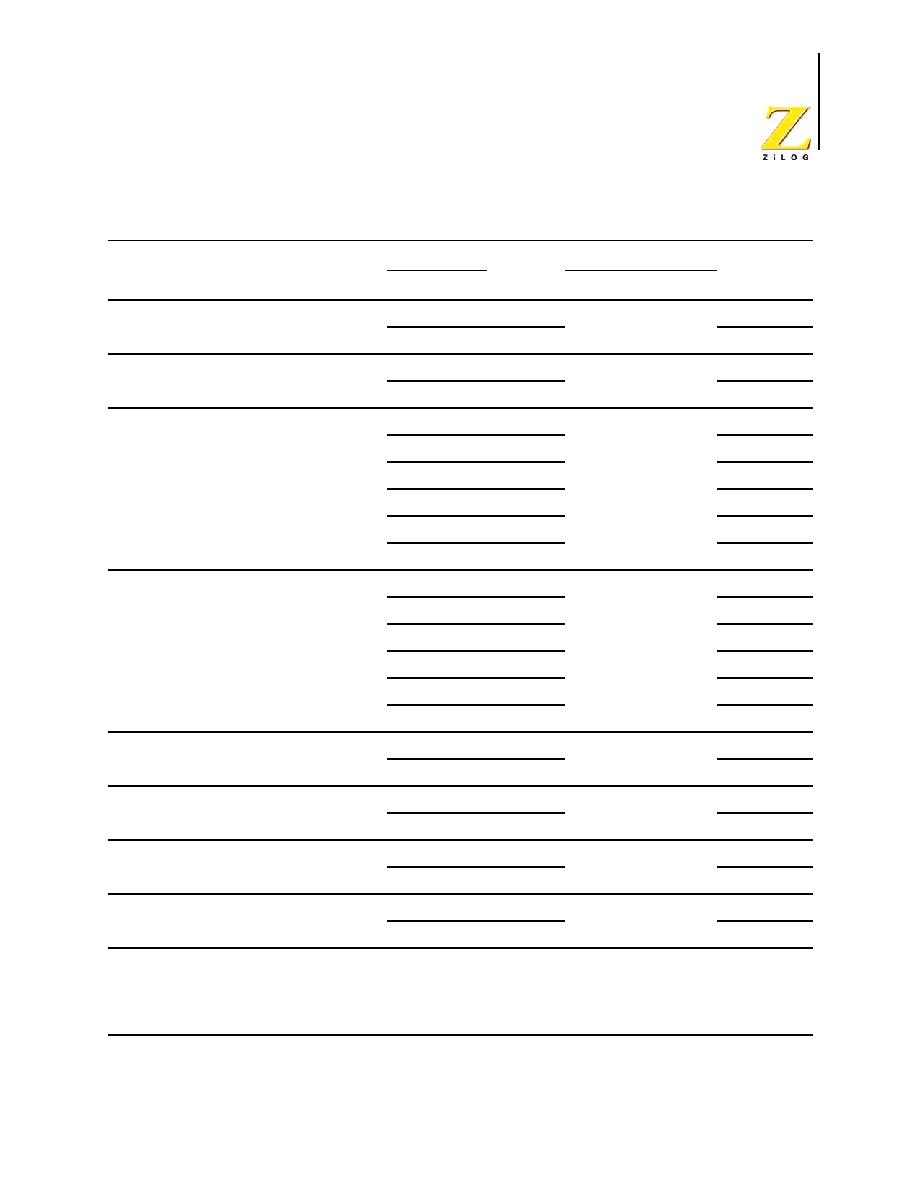

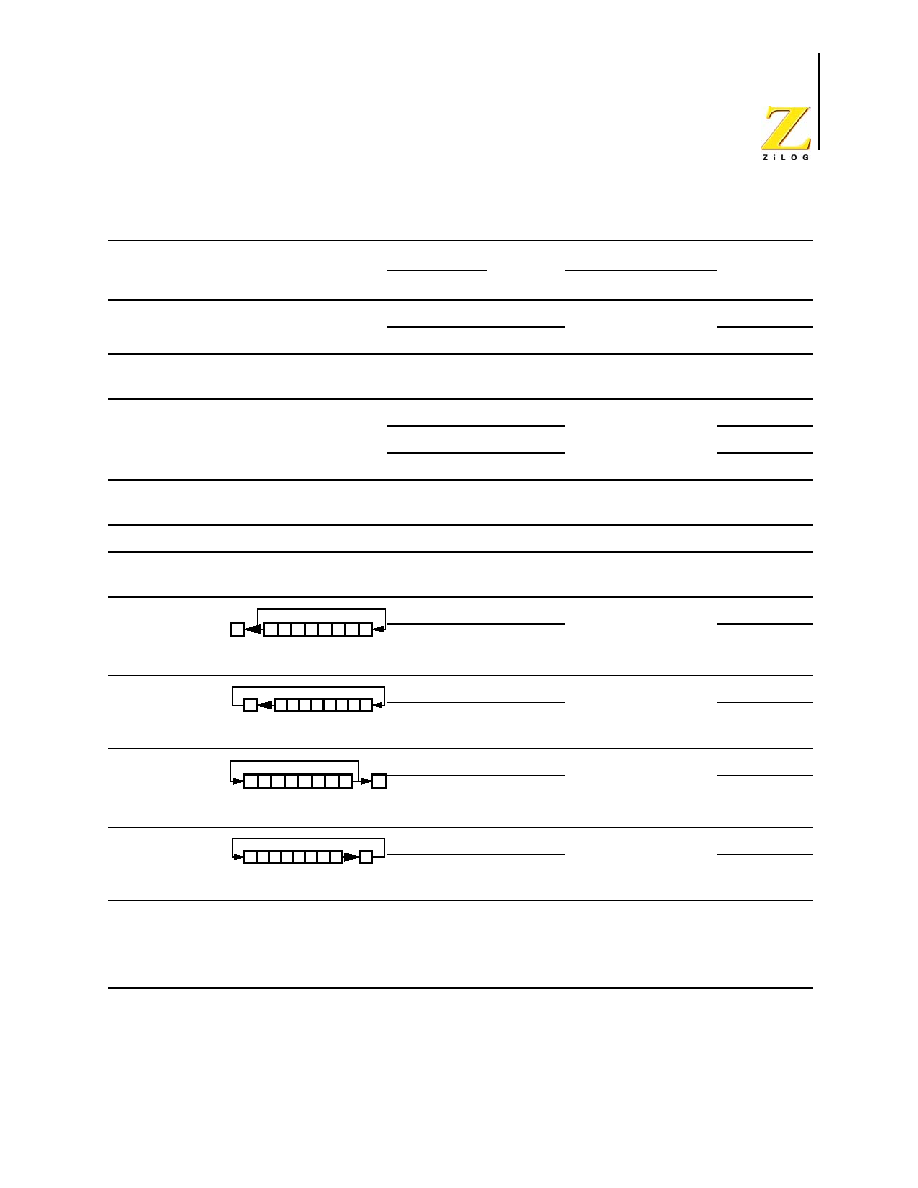

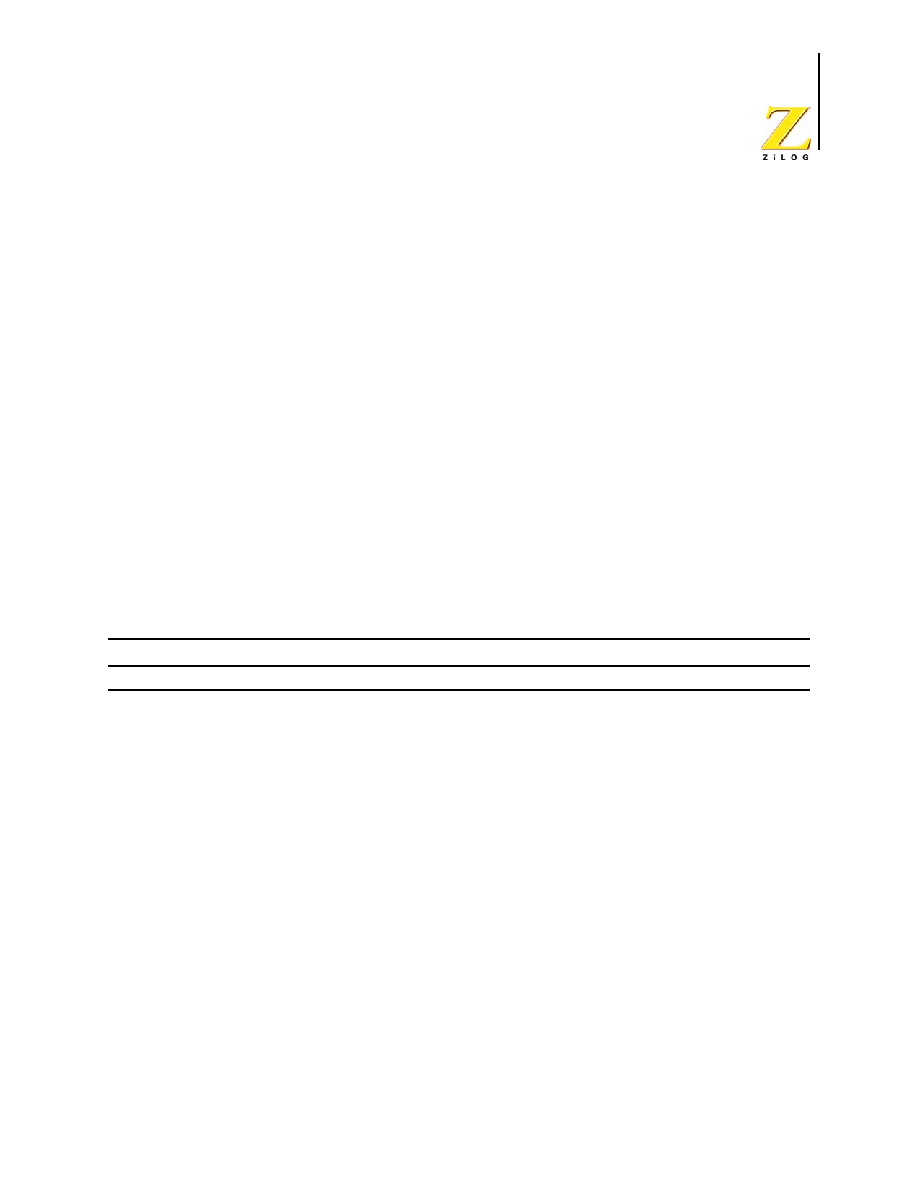

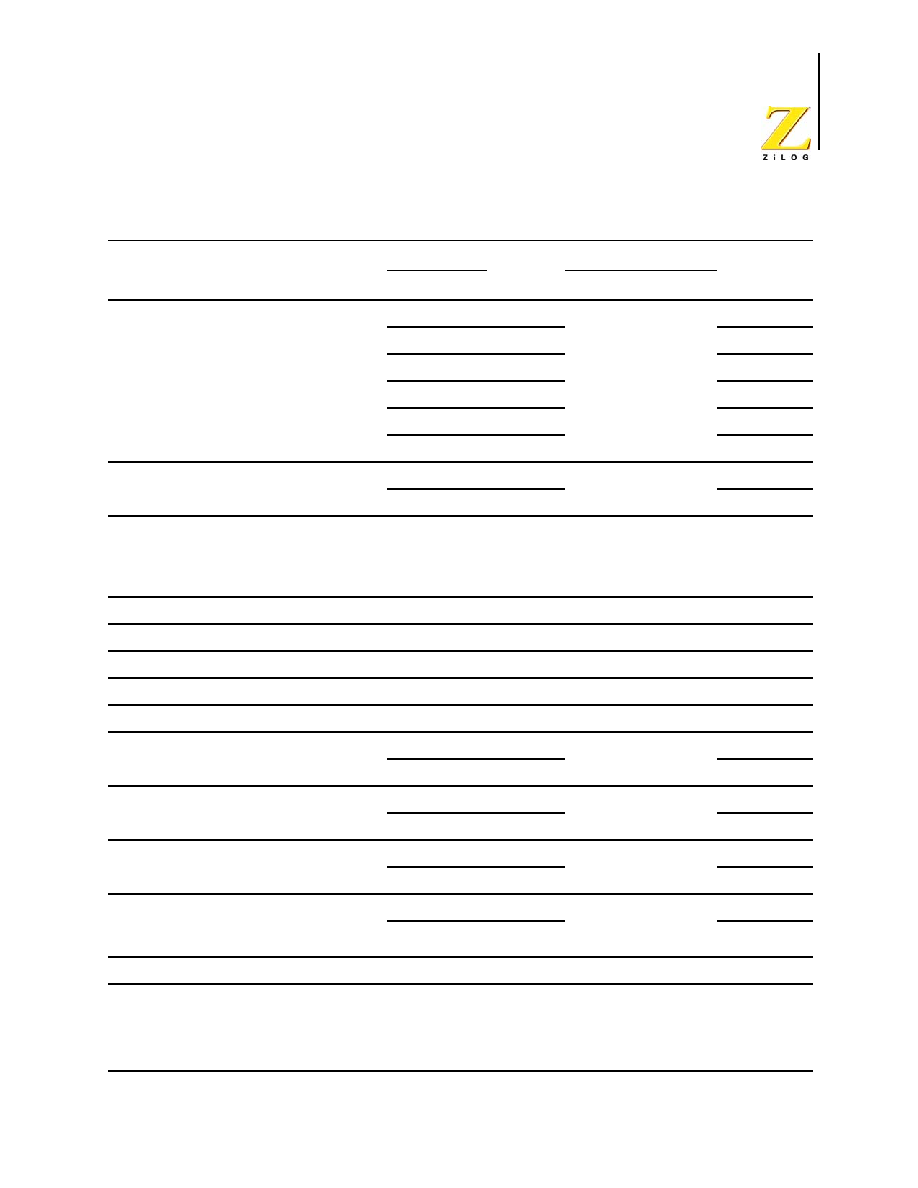

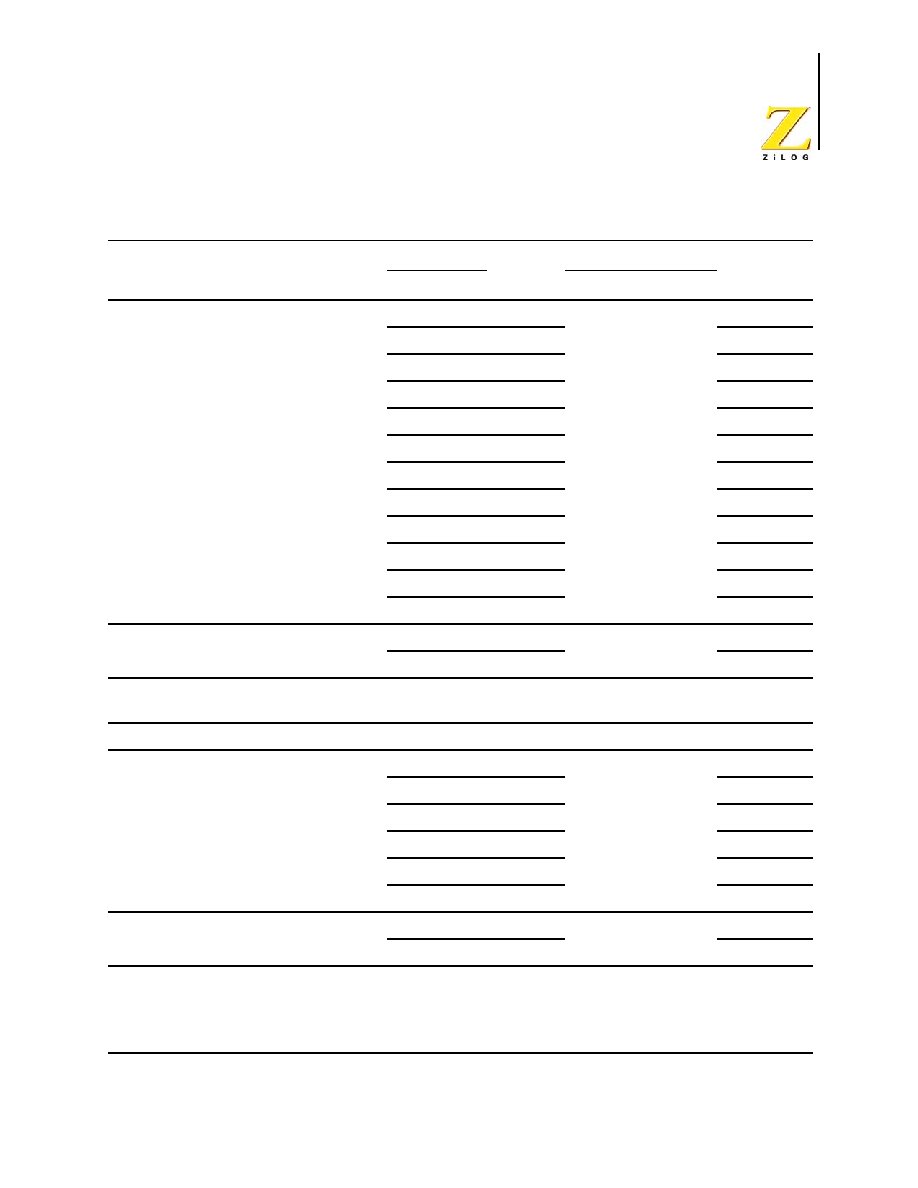

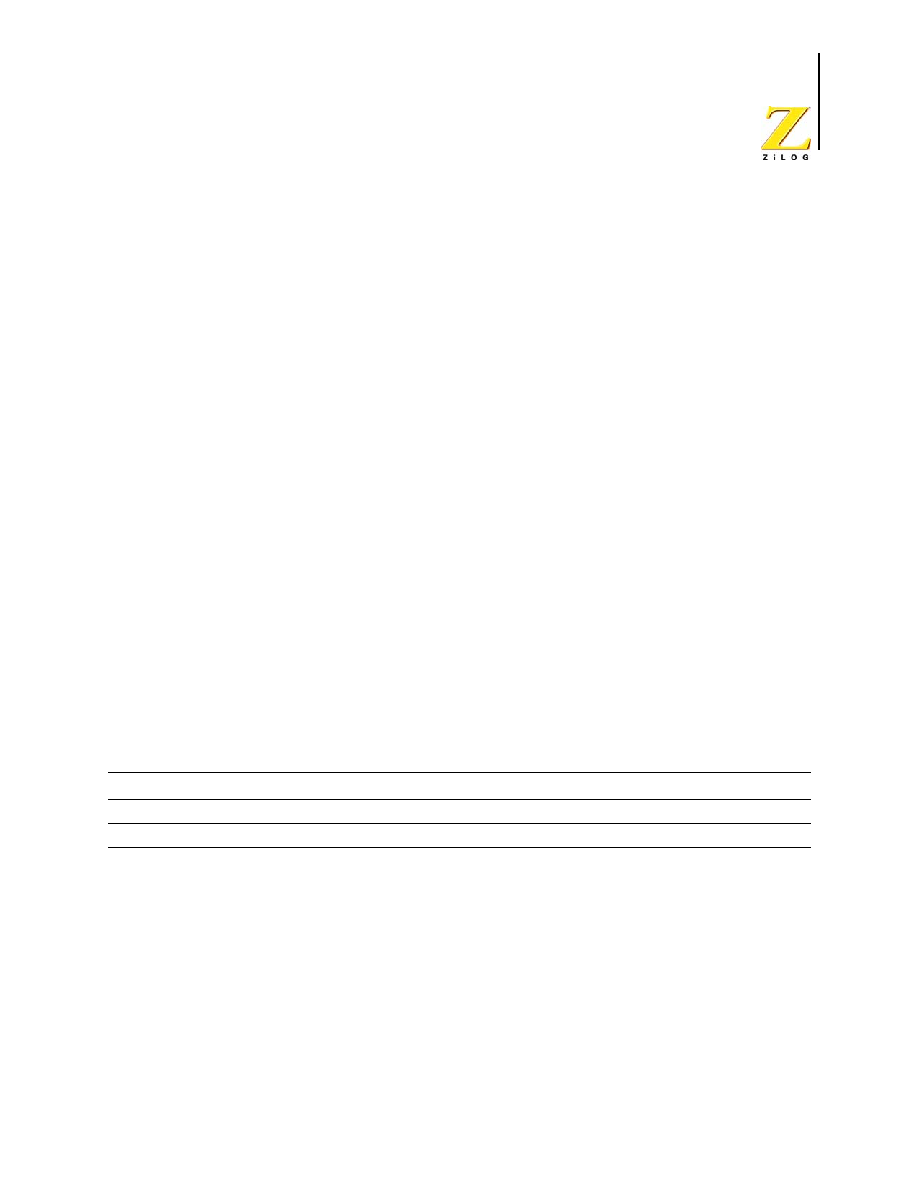

List of Figures

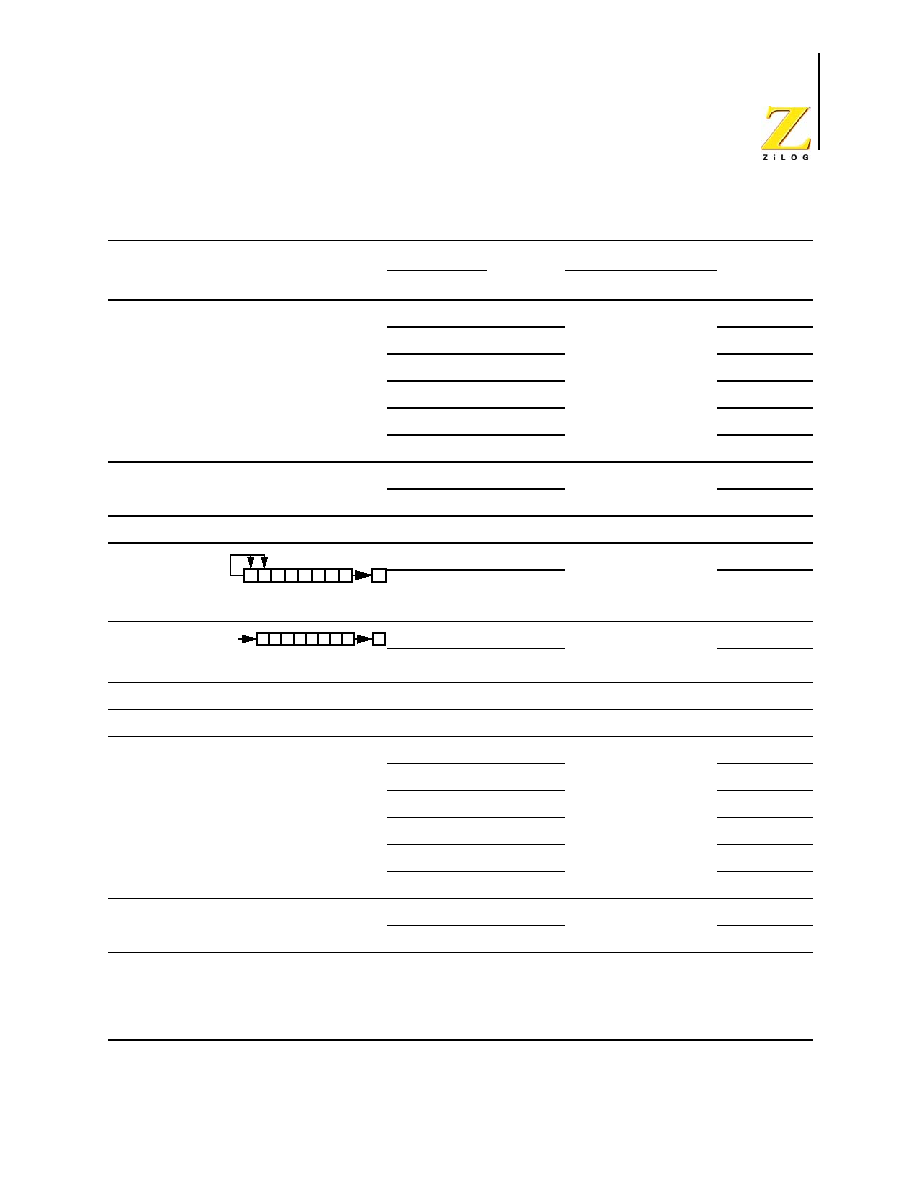

Figure 1.

eZ8 CPU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

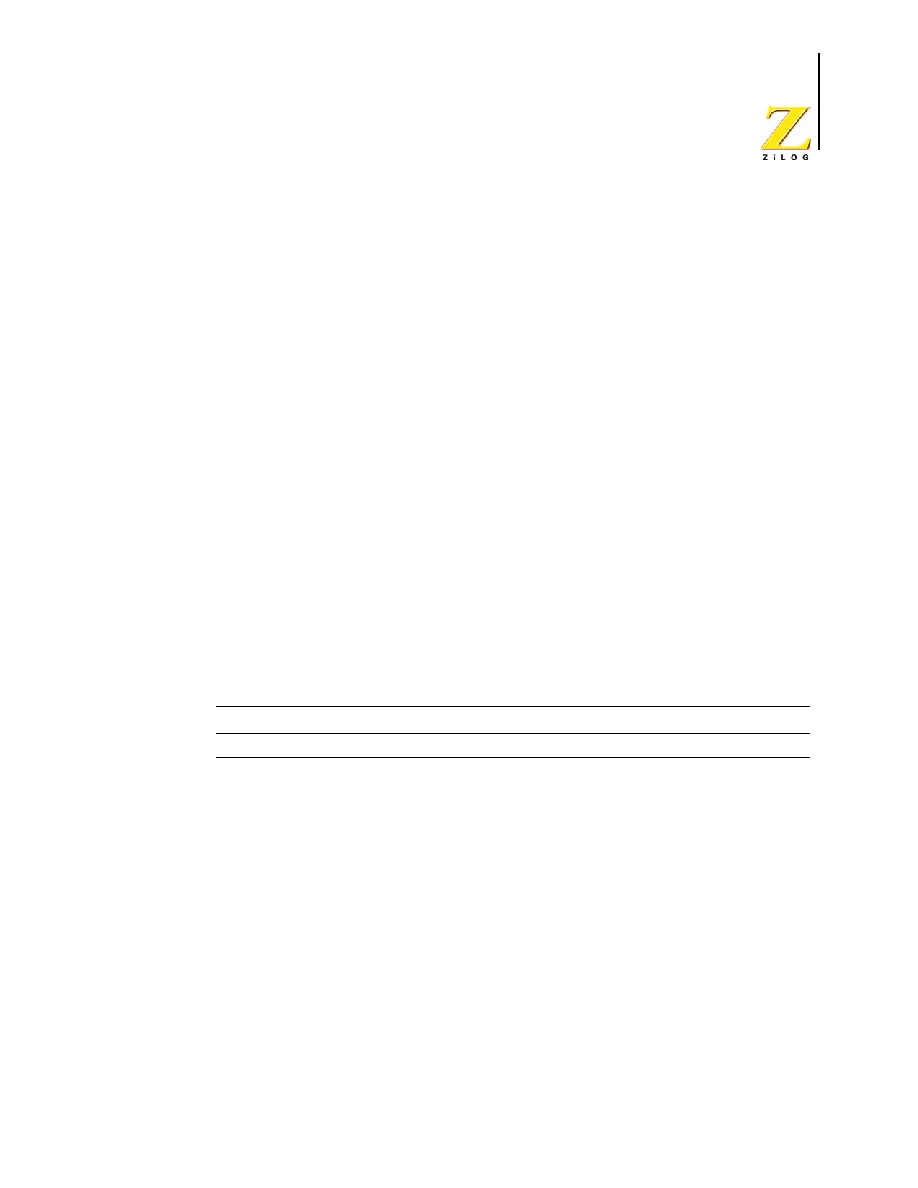

Figure 2.

Flags Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

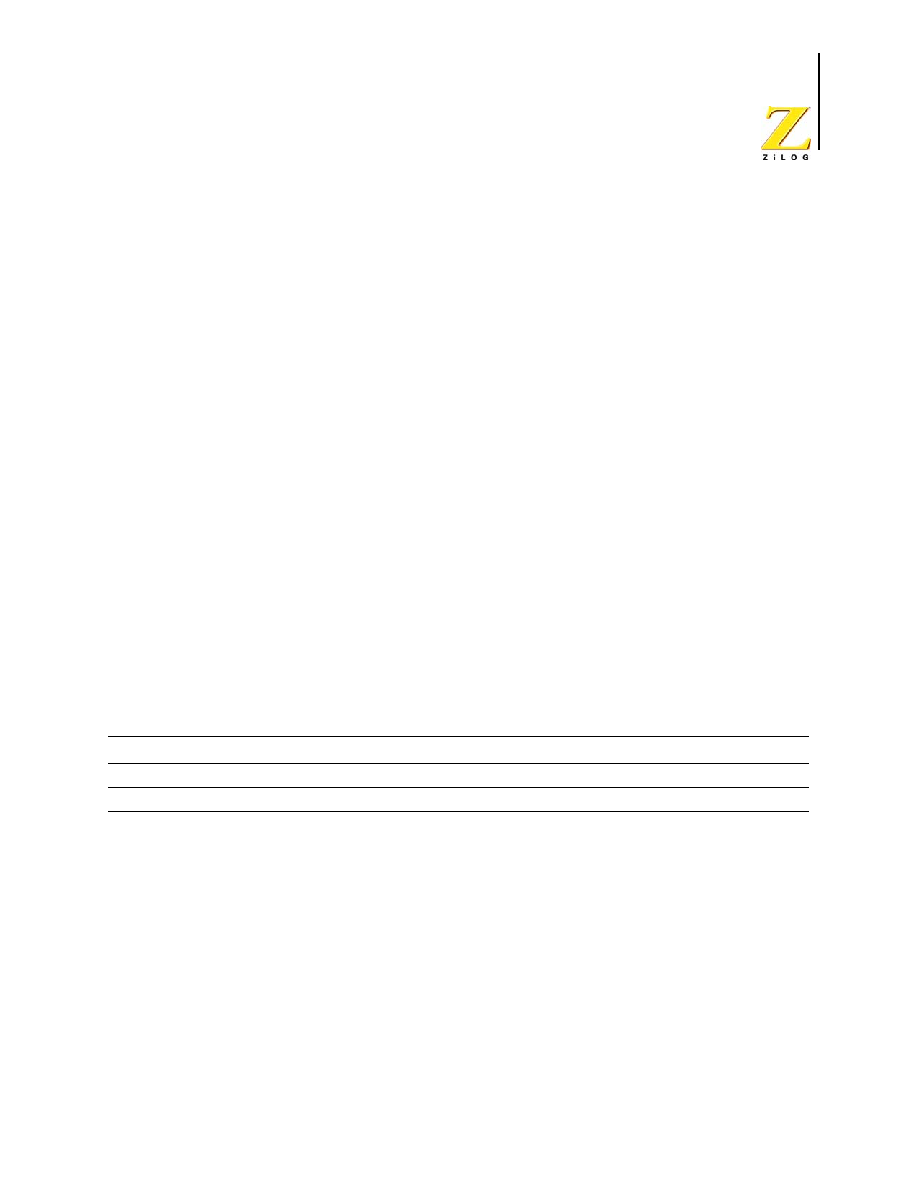

Figure 3.

Register File Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

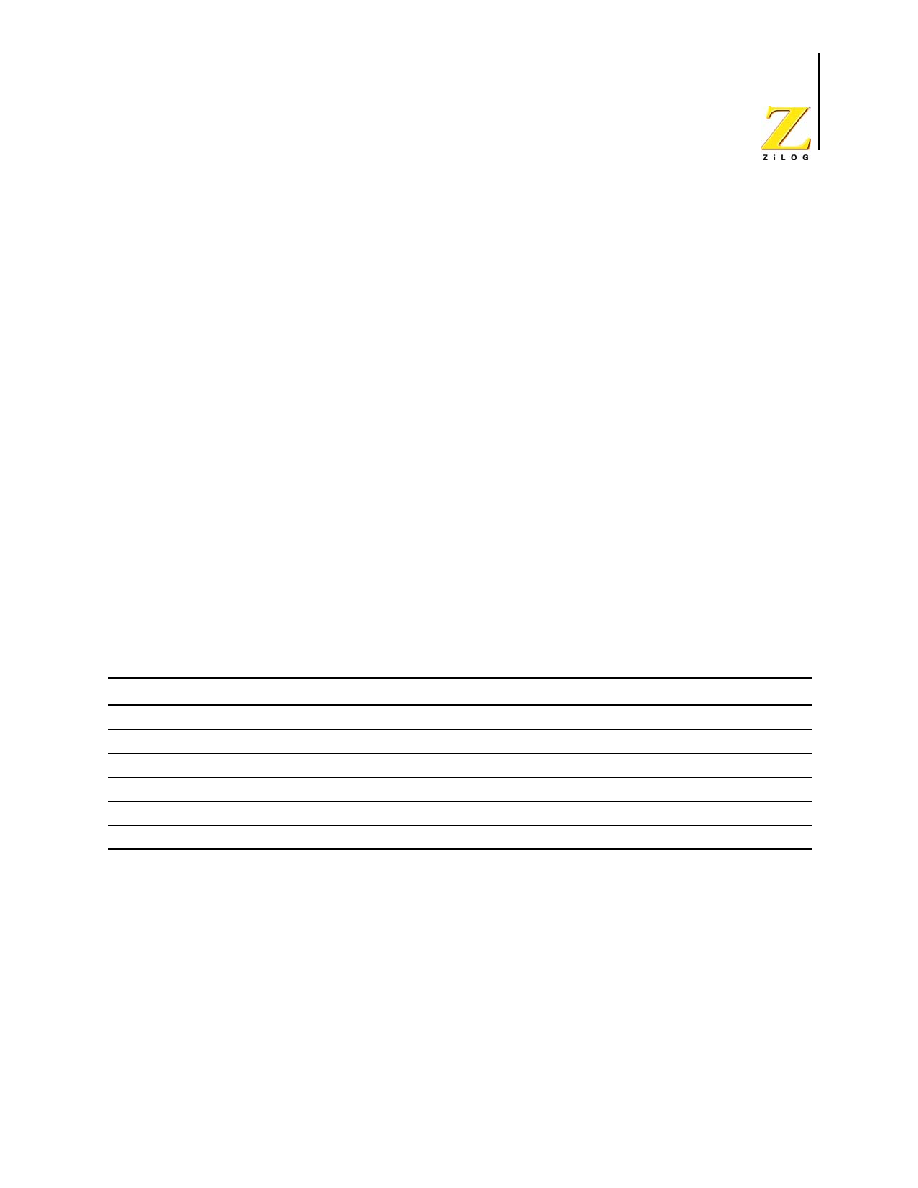

Figure 4.

Working Register Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 5.

16-Bit Register Pair Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 6.

Bit Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 7.

Stack Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 8.

Register Addressing Using 12-Bit Addresses . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 9.

Register Addressing Using 8-Bit Addresses . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 10. Register Addressing Using 4-Bit Addresses . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 11. Indirect Register Addressing to Register File . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 12. Indirect Register Addressing to Program or Data Memory . . . . . . . . . . . . . 25

Figure 13. Indexed Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 14. Direct Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 15. Relative Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 16. Immediate Data Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 17. Effects of an Interrupt on the Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 18. Interrupt Vectoring in Program Memory Example . . . . . . . . . . . . . . . . . . . 32

Figure 19. Example Instruction Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 20. BTJ Operand Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 21. BTJNZ Operand Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 22. BTJZ Operand Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 23. Opcode Map Cell Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

eZ8 CPU

User Manual

UM012811-0904

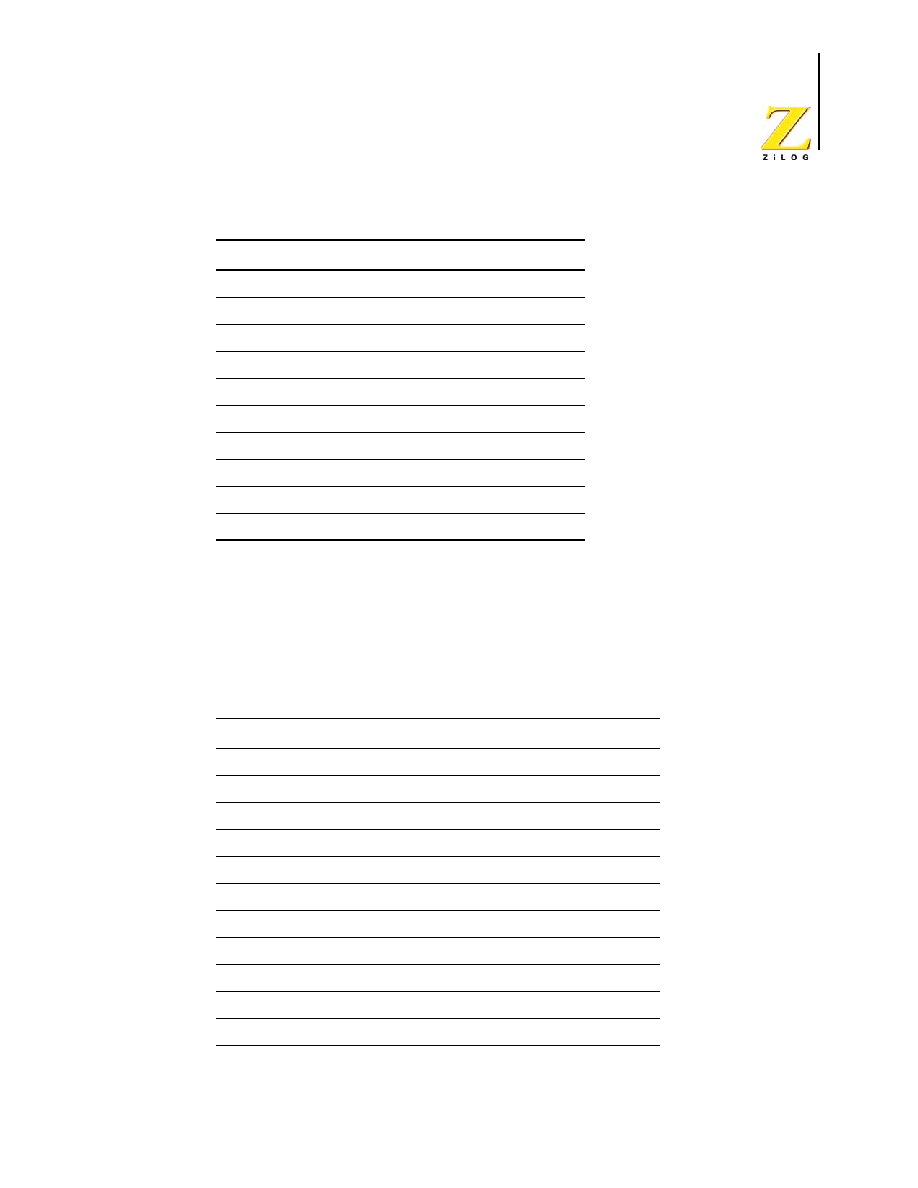

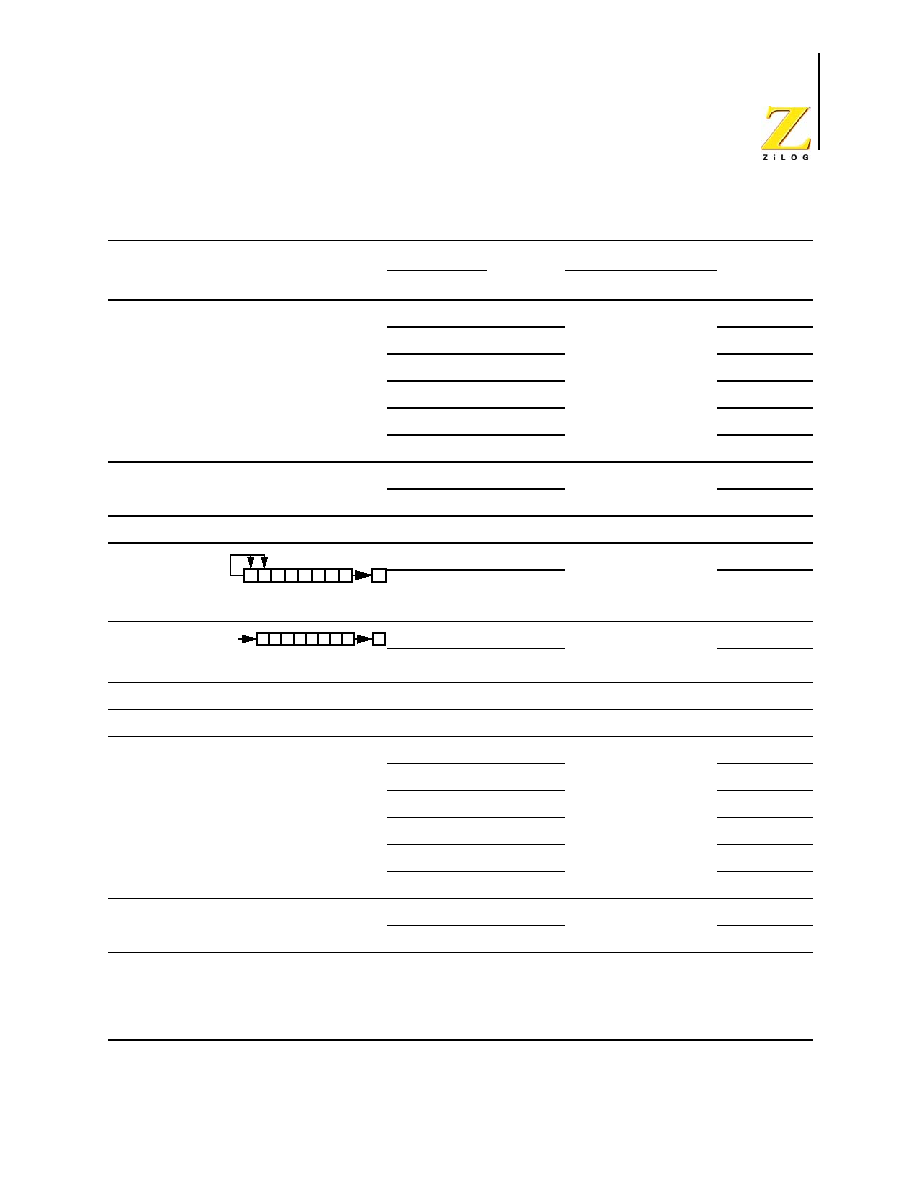

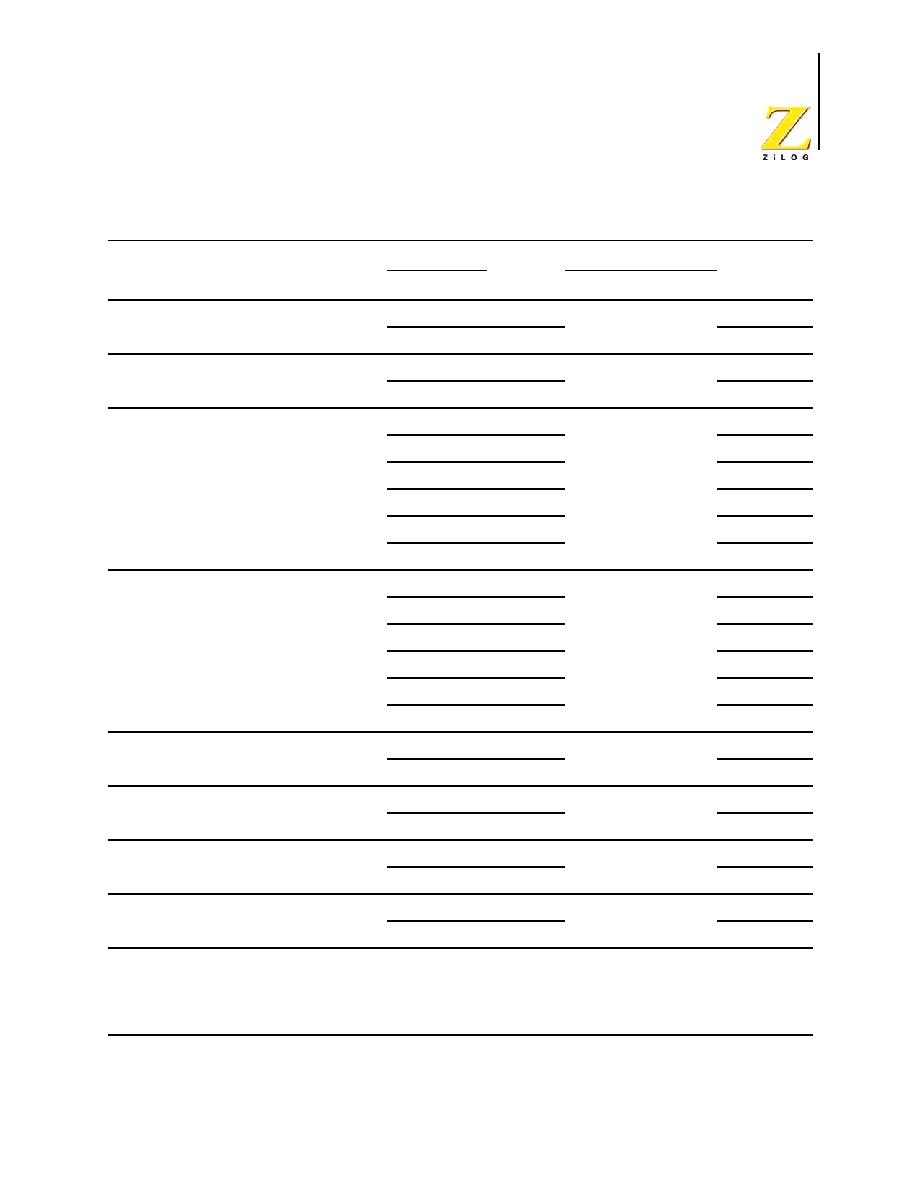

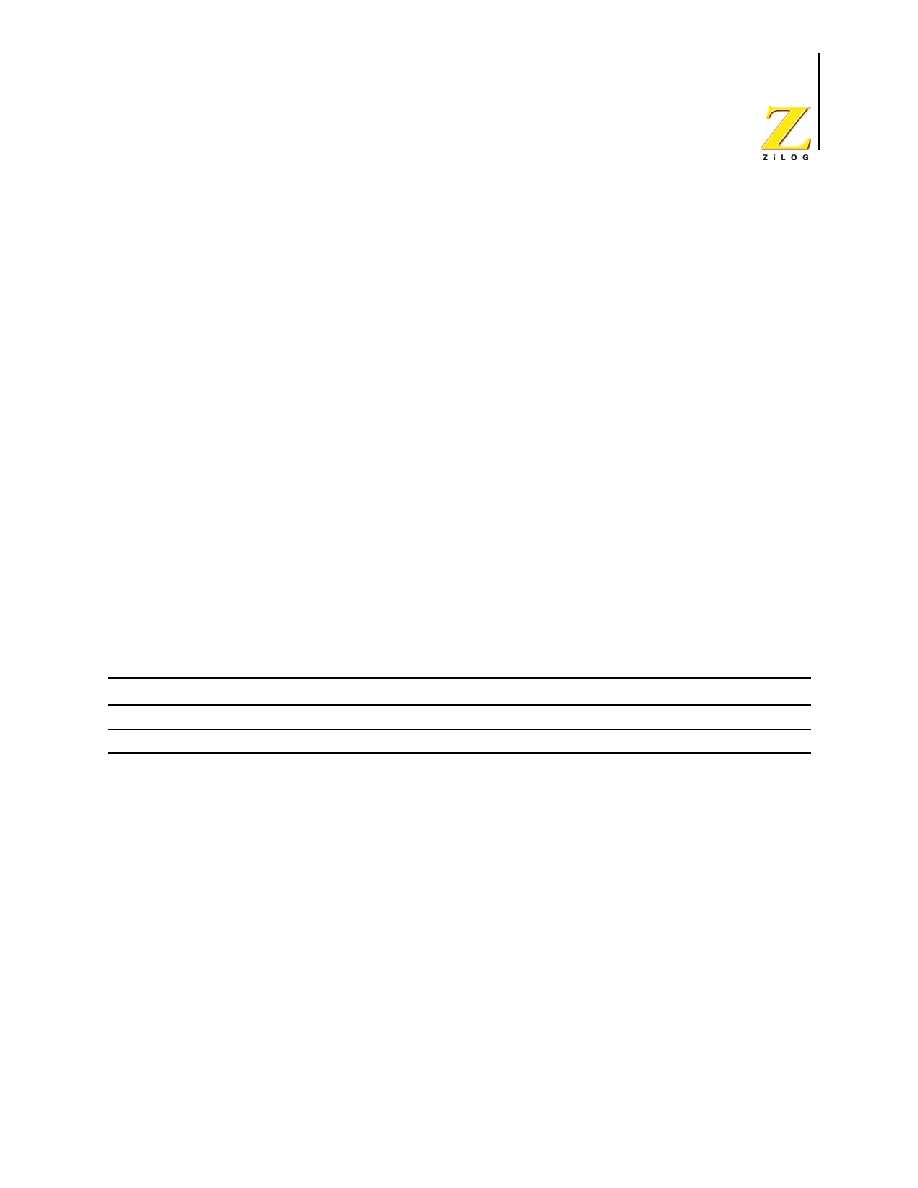

List of Tables

vi

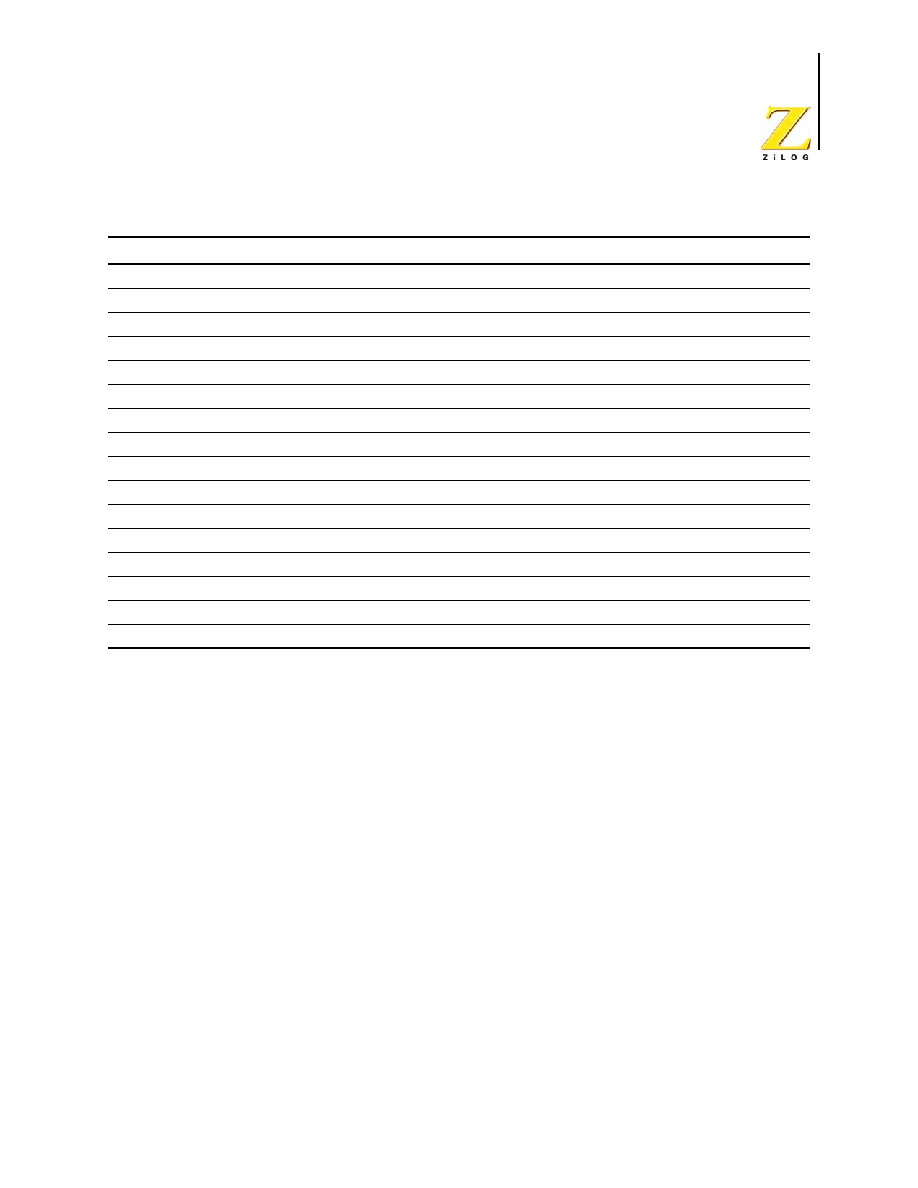

List of Tables

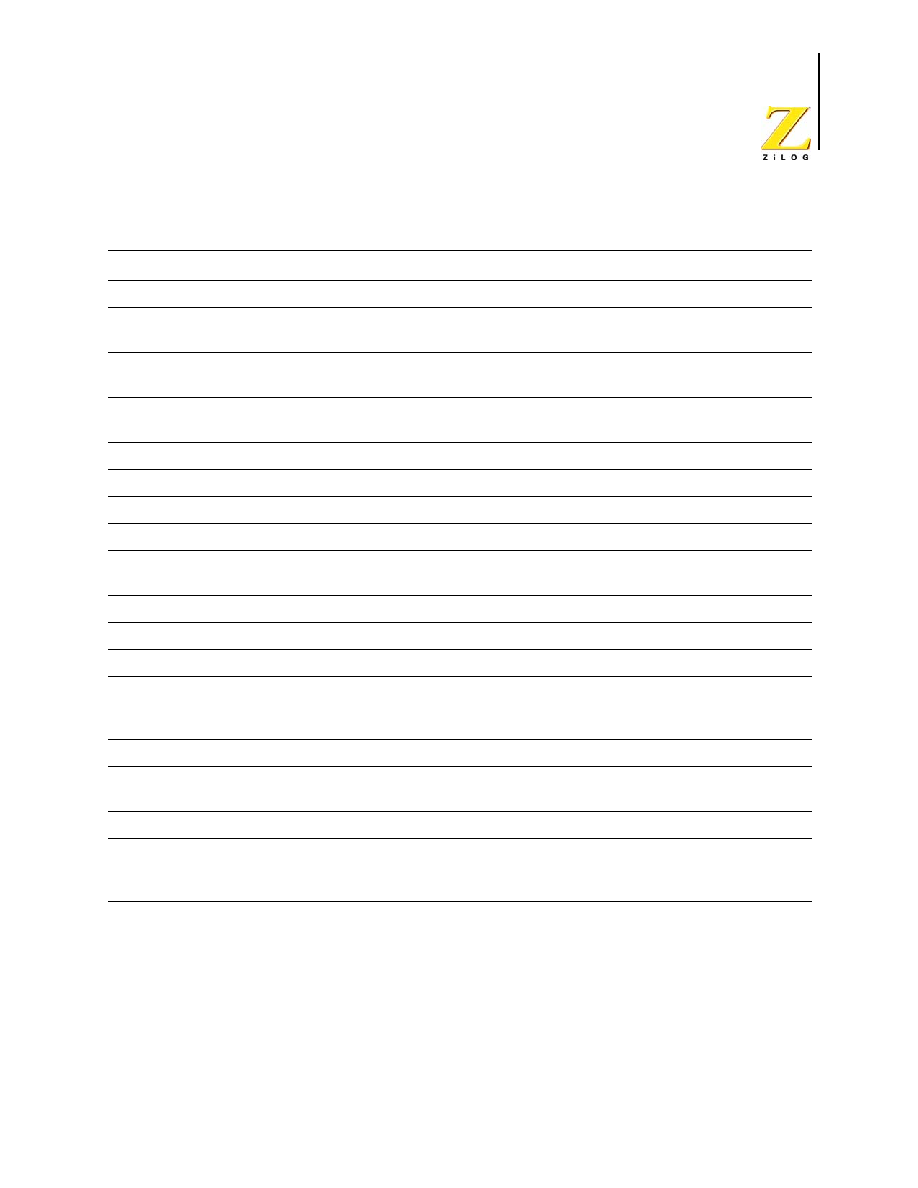

Table 1. eZ8 CPU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 2. Condition Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 3. New Function Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 4. New Extended Addressing Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5. Instructions with New Opcodes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 6. eZ8 CPU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 7. Program Memory Map Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Assembly Language Syntax Example 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 9. Assembly Language Syntax Example 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 10. Notational Shorthand . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 11. Additional Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 12. Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 13. Bit Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 14. Block Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 15. CPU Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 16. Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 17. Load Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 18. Program Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 19. Rotate and Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 20. eZ8 CPU Instruction Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 21. Operation of the DAA Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 22. Opcode Map Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Table 23. eZ8 CPU Instructions Sorted by Opcode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 24. Assembly and Object Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

eZ8 CPU

User Manual

UM012811-0904

Manual

Objectives

vii

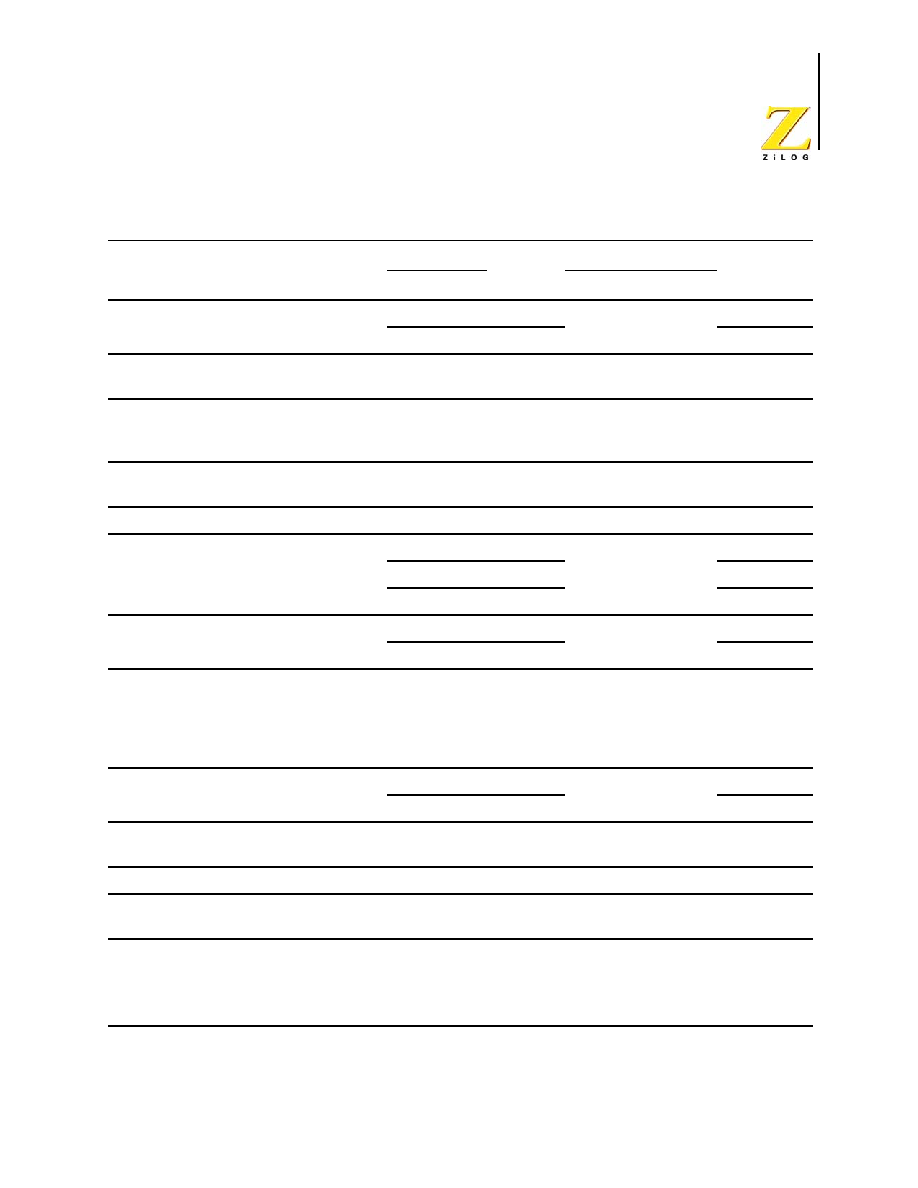

Manual Objectives

This user manual describes the architecture and instruction set of the eZ8 CPU.

About This Manual

ZiLOG recommends that the user read and understand everything in this manual before

setting up and using the product. However, we recognize that there are different styles of

learning. Therefore, we have designed this manual to be used either as a how to procedural

manual or a reference guide to important data.

Intended Audience

This document is written for ZiLOG customers who are experienced at working with

microprocessors or in writing assembly code or compilers.

Manual Organization

The User Manual is divided into ten sections; each section details a specific topic about

the product.

Architectural Overview

Presents an overview of the eZ8 CPU's features and benefits, and a description of its

architecture.

Z8 Compatibility

Provides information for users who are familiar with programming ZiLOG's classic Z8

�

CPU or who are planning to use existing Z8

�

code with the eZ8 CPU.

Address Space

Describes the three address spaces accessible by the eZ8 CPU - Register File, Program

Memory, and Data Memory.

UM012811-0904

Manual

Objectives

eZ8 CPU

User Manual

viii

Addressing Modes

Details the eZ8 CPU's six addressing modes:

�

Register (R)

�

Indirect Register (IR)

�

Indexed (X)

�

Direct (DA)

�

Relative (RA)

�

Immediate Data (IM)

�

Extended Register (ER)

Interrupts

Describes eZ8 CPU operation in response to interrupt requests from either internal periph-

erals or external devices.

Illegal Instruction Traps

Describes the consequences of executing undefined opcodes.

eZ8 CPU Instruction Set Summary

Lists assembly language instructions, including mnemonic definitions and a summary of

the User Manual instruction set.

Opcode Maps

Presents a detailed diagram of each opcode table.

Opcodes Listed Numerically

Provides an easy reference for locating instructions by their opcode.

Sample Program Listing

A sample program shows how the instructions, using many of the available memory

modes, will translate into object code after assembly.

Manual Conventions

The following assumptions and conventions are adopted to provide clarity and ease of use:

Courier Typeface

Commands, code lines and fragments, bits, equations, hexadecimal addresses, and various

executable items are distinguished from general text by the use of the

Courier

typeface.

UM012811-0904

Manual

Objectives

eZ8 CPU

User Manual

ix

Where the use of the font is not indicated, as in the Index, the name of the entity is pre-

sented in upper case.

�

Example: FLAGS[1] is

smrf

.

Hexadecimal Values

Hexadecimal values are designated by uppercase

H

and appear in the

Courier

typeface.

�

Example: R1 is set to

F8H.

Brackets

The square brackets, [ ], indicate a register or bus.

�

Example: for the register R1[7:0], R1 is an 8-bit register, R1[7] is the most significant

bit, and R1[0] is the least significant bit.

Braces

The curly braces, { }, indicate a single register or bus created by concatenating some com-

bination of smaller registers, buses, or individual bits.

�

Example: the 12-bit register address {

0H

, RP[7:4], R1[3:0]} is composed of a 4-bit

hexadecimal value (

0H

) and two 4-bit register values taken from the Register Pointer

(RP) and Working Register R1.

0H

is the most significant nibble (4-bit value) of the

12-bit register, and R1[3:0] is the least significant nibble of the 12-bit register.

Parentheses

The parentheses, ( ), indicate an indirect register address lookup.

�

Example: (R1) is the memory location referenced by the address contained in the

Working Register R1.

Parentheses/Bracket Combinations

The parentheses, ( ), indicate an indirect register address lookup and the square brackets,

[ ], indicate a register or bus.

�

Example: assume PC[15:0] contains the value

1234h

. (PC[15:0]) then refers to the

contents of the memory location at address

1234h

.

Use of the Words Set, Reset and Clear

The word set implies that a register bit or a condition contains a logical 1. The word reset

or clear implies that a register bit or a condition contains a logical 0. When either of these

terms is followed by a number, the word logical may not be included; however, it is

implied.

UM012811-0904

Manual

Objectives

eZ8 CPU

User Manual

x

Notation for Bits and Similar Registers

A field of bits within a register is designated as: Register[n:n].

�

Example: ADDR[15:0] refers to bits 15 through bit 0 of the Address.

Use of the Terms LSB, MSB, lsb, and msb

In this document, the terms LSB and MSB, when appearing in upper case, mean least sig-

nificant byte and most significant byte, respectively. The lowercase forms, lsb and msb,

mean least significant bit and most significant bit, respectively.

Use of Initial Uppercase Letters

Initial uppercase letters designate settings, modes, and conditions in general text.

�

Example 1: Stop mode.

�

Example 2: The receiver forces the SCL line to Low.

�

The Master can generate a Stop condition to abort the transfer.

Use of All Uppercase Letters

The use of all uppercase letters designates the names of states and commands.

�

Example 1: The bus is considered BUSY after the Start condition.

�

Example 2: A START command triggers the processing of the initialization sequence.

Bit Numbering

Bits are numbered from 0 to n�1 where n indicates the total number of bits. For example,

the 8 bits of a register are numbered from 0 to 7.

Safeguards

It is important that all users understand the following safety terms, which are defined here.

Indicates a procedure or file may become corrupted if the

user does not follow directions.

Trademarks

eZ8 and Z8

�

are trademarks of

ZiLOG, Inc

.

Caution:

eZ8 CPU

User Manual

UM012811-0904

Architectural

Overview

1

Architectural Overview

FEATURES

The eZ8 is ZiLOG's latest 8-bit central processing unit (CPU) designed to meet the con-

tinuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU exe-

cutes a superset of the original Z8

�

instruction set. The features of the eZ8 CPU include:

�

Direct register-to-register architecture allows each register to function as an

accumulator. This improves execution time and decreases the required program

memory.

�

Software stack allows much greater depth in subroutine calls and interrupts than

hardware stacks.

�

Compatible with Z8

�

assembly instruction set.

�

Expanded internal Register File allows access of up to 4KB.

�

New instructions improve execution efficiency for code developed using higher-level

programming languages including C.

�

Pipelined instruction fetch and execution

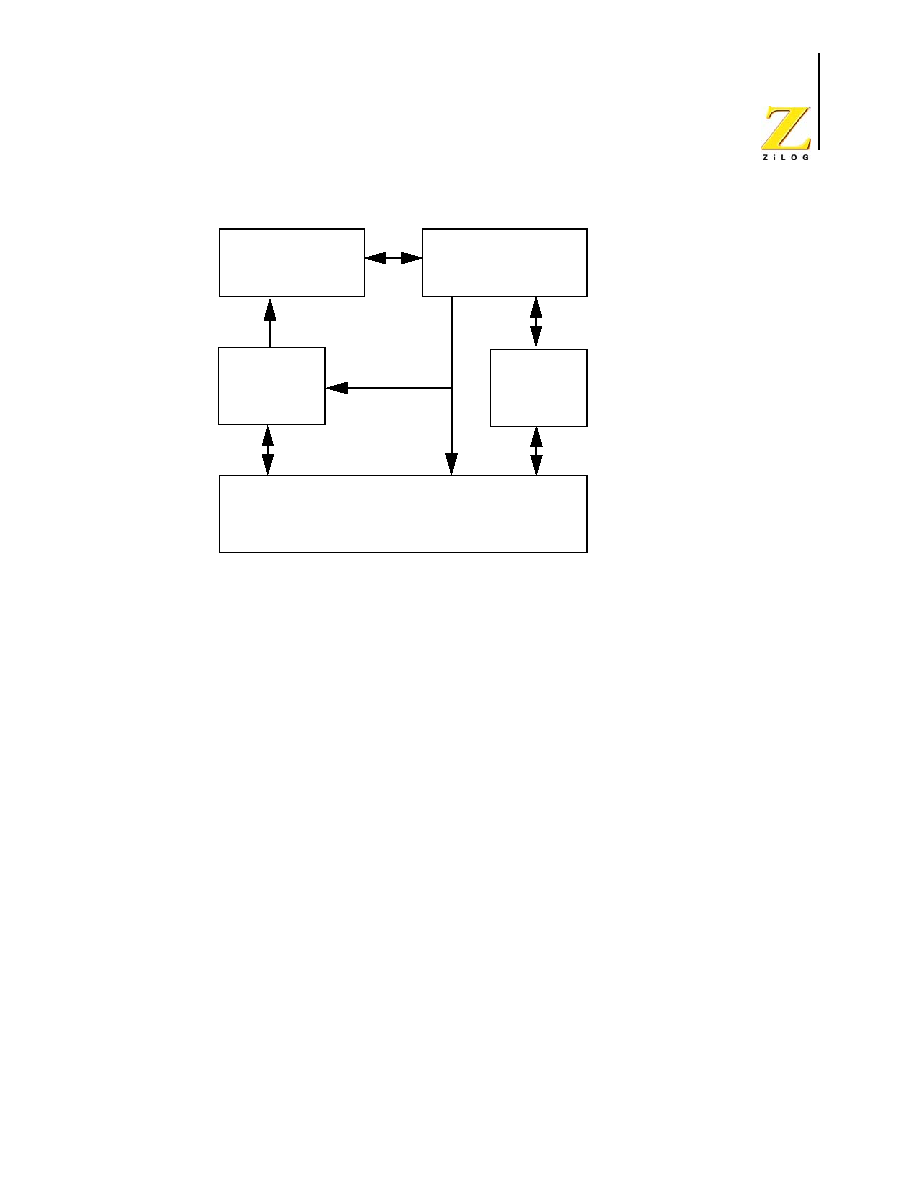

PROCESSOR DESCRIPTION

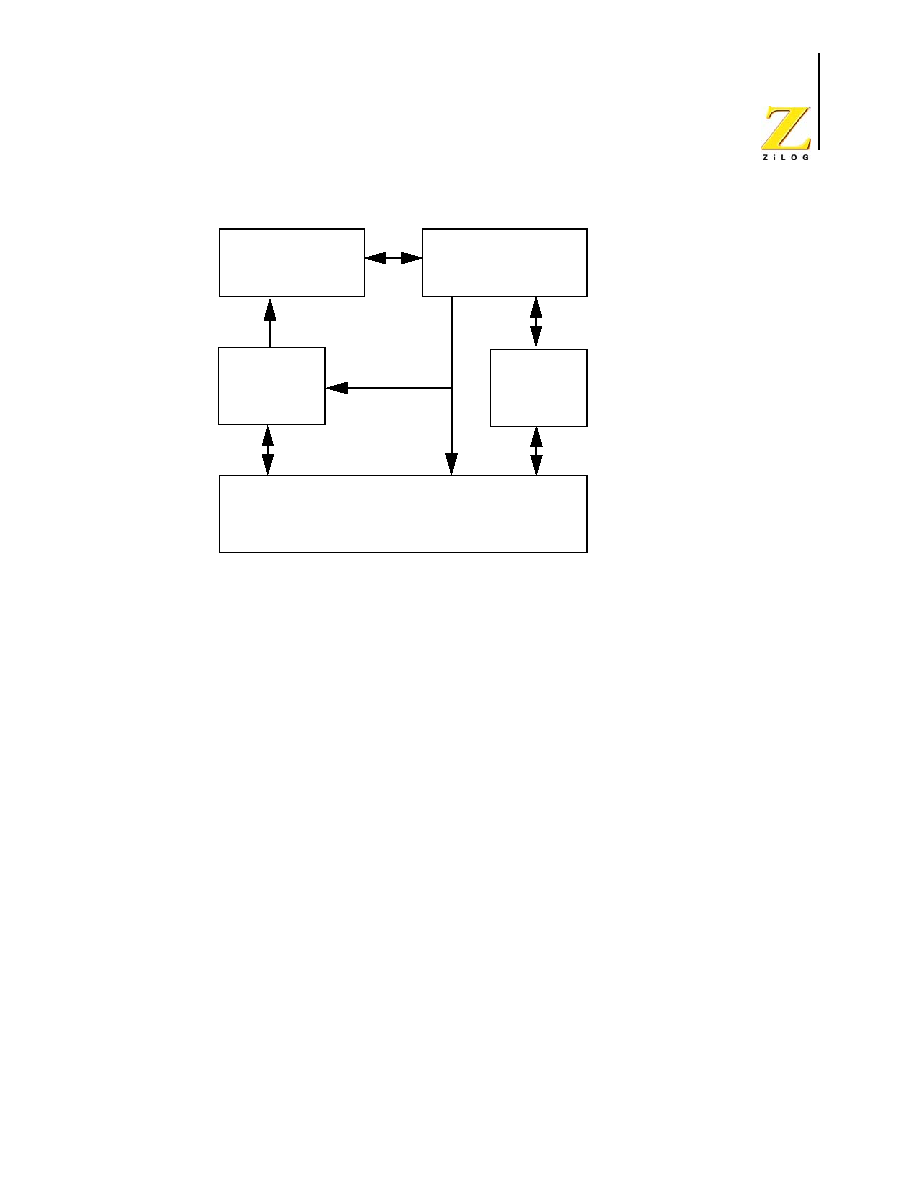

The eZ8 CPU contains two major functional blocks - the Fetch Unit and the Execution

Unit. The Execution Unit is further subdivided into the Instruction State Machine, Pro-

gram Counter, CPU Control Registers, and Arithmetic Logic Unit (ALU). Figure 1 illus-

trates the eZ8 CPU architecture.

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

2

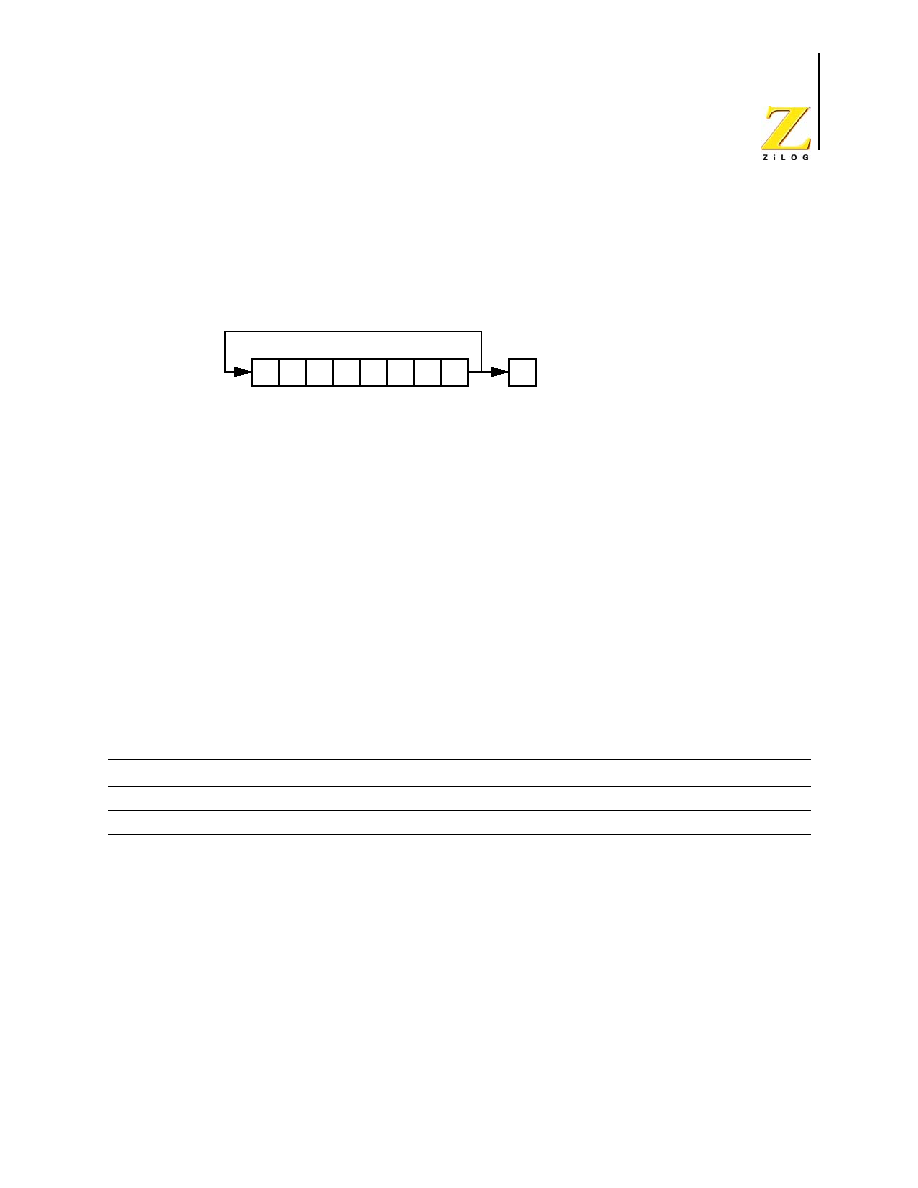

Figure 1. eZ8 CPU Block Diagram

FETCH UNIT

The Fetch Unit controls the memory interface. Its primary function is to fetch opcodes and

operands from memory. The Fetch Unit also fetches interrupt vectors or reads and writes

memory in the Program or Data Memory.

The Fetch Unit performs a partial decoding of the opcode to determine the number of

bytes to fetch for the operation. The Fetch Unit operation sequence follows:

1. Fetch the opcode

2. Determine the operand size (number of bytes)

3. Fetch the operands

4. Present the opcode and operands to the Instruction State Machine.

The Fetch Unit is pipelined and operates semi-independently from the rest of the eZ8

CPU.

INSTRUCTION STATE MACHINE

The Instruction State Machine is the controller for the eZ8 CPU Execution Unit. After the

initial operation decode by the Fetch Unit, the Instruction State Machine takes over and

completes the instruction. The Instruction State Machine performs register read and write

operations and generates addresses.

Fetch Unit

Instruction

State Machine

CPU Control

Registers

Program

Counter

Arithmetic Logic Unit

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

3

Instruction Cycle Time

The instruction cycle times vary from instruction to instruction, allowing higher perfor-

mance given a specific clock speed. Minimum instruction execution time for standard

CPU instructions is two clock cycles (only the BRK instruction executes in a single cycle).

Because of the variation in the number of bytes required for different instructions, delay

cycles can occur between instructions. Delay cycles are added any time the number of

bytes in the next instruction exceeds the number of clock cycles the current instruction

takes to execute. For example, if the eZ8 CPU executes a 2-cycle instruction while fetch-

ing a 3-byte instruction, a delay cycle occurs because the Fetch Unit has only two cycles to

fetch the three bytes. The Execution Unit is idle during a delay cycle.

PROGRAM COUNTER

The Program Counter contains a 16-bit counter and a 16-bit adder. The Program Counter

monitors the address of the current memory address and calculates the next memory

address. The Program Counter increments automatically according to the number of bytes

fetched by the Fetch Unit. The 16-bit adder increments and handles Program Counter

jumps for relative addressing.

eZ8 CPU CONTROL REGISTERS

The eZ8 CPU contains four CPU control registers that are mapped into the Register File

address space. These four eZ8 CPU control registers are:

�

Stack Pointer High Byte

�

Stack Pointer Low Byte

�

Register Pointer

�

Flags

The eZ8 CPU register bus can access up to 4K (4096) bytes of register space. In all eZ8

CPU products, the upper 256 bytes are reserved for control of the eZ8 CPU, the on-chip

peripherals, and the I/O ports. The eZ8 CPU control registers are always located at

addresses from

FFCH

to

FFFH

as listed in Table 1 on page 4.

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

4

Stack Pointer Registers

The eZ8 CPU allows the user to relocate the stack within the Register File. The stack can

be located at addresses from

000H

to

EFFH

. The 12-bit Stack Pointer value is given by

{SPH[3:0], SPL[7:0]}. The Stack Pointer has a 12-bit increment/decrement capability for

stack operations, allowing the Stack Pointer to operate over more than one page (256-byte

boundary) of the Register File. The Stack Pointer register values are undefined after Reset.

Register Pointer

The Register Pointer contains address information for the current Working Register Group

and the Register File Page. The Page Pointer is the lower 4-bits of the Register Pointer,

RP[3:0], and points to the current Page. There are sixteen 256-byte Pages available. The

Working Register Group Pointer is the upper 4 bits of the Register Pointer, RP[7:4], and

points to one of sixteen 16-byte Working Register Groups. There are 16 Working Register

Groups per page. For more information on the Register File, please refer to the sec-

tion`'Address Space" on page 13.

Flags Register

The Flags Register contains the status information regarding the most recent arithmetic,

logical, bit manipulation or rotate and shift operation. The Flags Register contains six bits

of status information that are set or cleared by CPU operations. Four of the bits (C, V, Z

and S) can be tested with conditional jump instructions. Two flags (H and D) cannot be

tested and are used for Binary-Coded Decimal (BCD) arithmetic.

The two remaining bits, User Flags (F1 and F2), are available as general-purpose status

bits. User Flags are unaffected by arithmetic operations and must be set or cleared by

instructions. The User Flags cannot be used with conditional Jumps. They are undefined at

initial power-up and are unaffected by Reset. Figure 2 illustrates the flags and their bit

positions in the Flags Register.

Table 1. eZ8 CPU Control Registers

Register

Mnemonic

Register Description

Address

(Hex)

FLAGS

Flags

FFC

RP

Register Pointer

FFD

SPH

Stack Pointer High Byte

FFE

SPL

Stack Pointer Low Byte

FFF

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

5

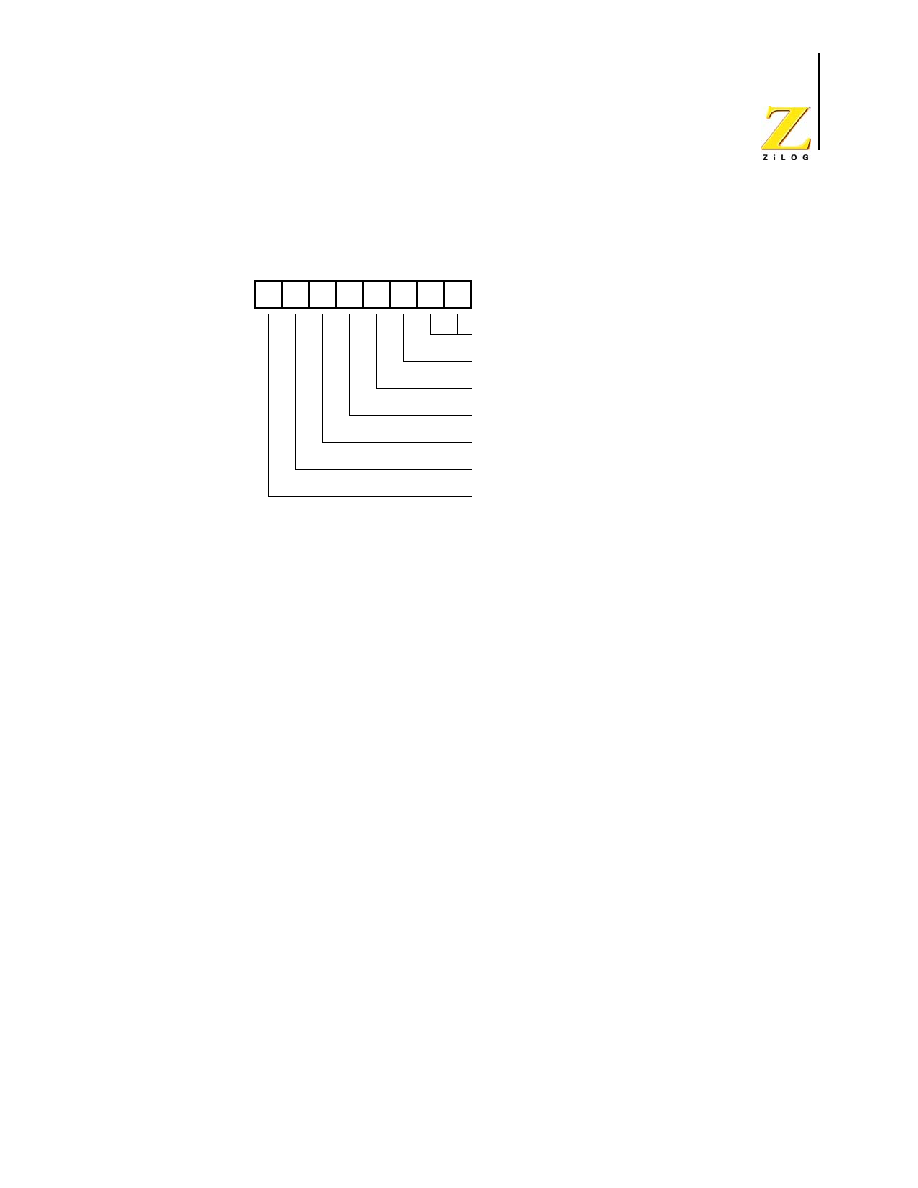

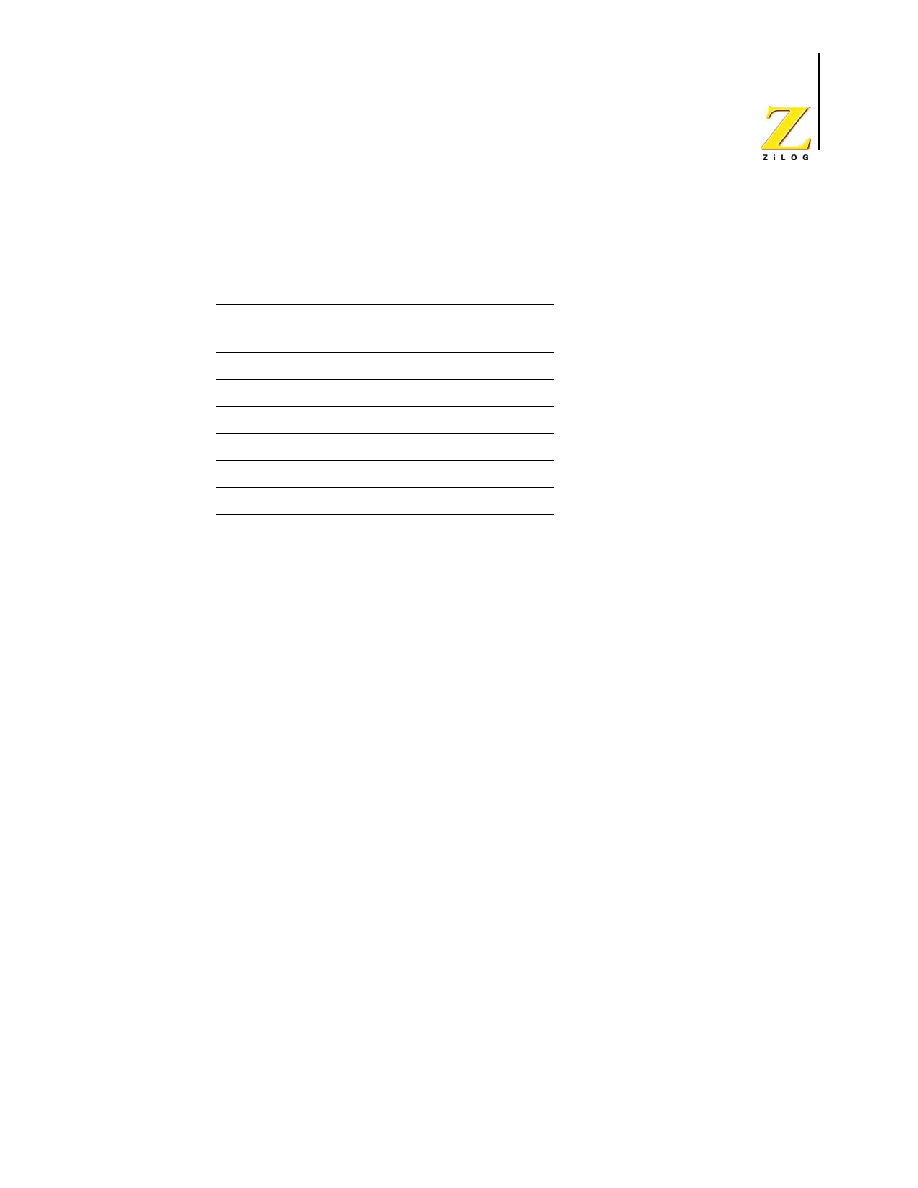

Figure 2. Flags Register

Interrupts, the Software Trap (TRAP) instruction, and Illegal Instruction Traps all write

the value of the Flags Register to the stack. Executing an Interrupt Return (IRET) instruc-

tion restores the value saved on the stack into the Flags Register.

Carry Flag

The Carry flag (C) is 1 when the result of an arithmetic operation generates a carry out of

or a borrow into the most significant bit (Bit 7) of the data. Otherwise, the Carry flag is 0.

Some bit rotate or shift instructions also affect the Carry flag. There are three instructions

available for directly changing the value of the Carry Flag:

�

Complement Carry Flag (CCF)

�

Reset Carry Flag (RCF)

�

Set Carry Flag (SCF)

Zero Flag

For arithmetic and logical operations, the Zero (Z) flag is 1 if the result is 0. Otherwise, the

Zero flag is 0. If the result of testing bits in a register is

00H

, the Zero flag is 1; otherwise,

the Zero flag is 0. Also, if the result of a rotate or shift operation is

00H

, the Zero flag is 1;

otherwise, the Zero flag is 0.

Sign Flag

The Sign (S) flag stores the value of the most-significant bit of a result following an arith-

metic, logical, rotate or shift operation. For signed numbers, the eZ8 CPU uses binary

two's complement to represent the data and perform the arithmetic operations. A 0 in the

C Z S V D H F2 F1 Flags Register

Bit

0

Bit

7

Half Carry Flag

Decimal Adjust Flag

Overflow Flag

Sign Flag

Zero Flag

Carry Flag

User Flags

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

6

most significant bit position (Bit 7) identifies a positive number; therefore, the Sign flag is

also 0. A 1 in the most significant position (Bit 7) identifies a negative number; therefore,

the Sign flag is also 1.

Overflow Flag

For signed arithmetic, rotate or shift operations, the Overflow (V) flag is 1 when the result

is greater than the maximum possible number (>127) or less than the minimum possible

number (<�128) that can be represented with 8-bits in two's complement form. The Over-

flow flag is 0 if no overflow occurs. Following logical operations, the Overflow flag is 0.

Following addition operations, the Overflow flag is 1 when the operands have the same

sign, but the result has the opposite sign. Following subtraction operations, the Overflow

flag is 1 if the two operands are of opposite sign and the sign of the result is same as the

sign of the source. Following rotation operations, the Overflow flag is 1 if the sign bit of

the destination operand changed during rotation.

Decimal Adjust Flag

The Decimal Adjust (D) flag is used for Binary-Coded Decimal (BCD) arithmetic opera-

tions. Because the algorithm for correcting BCD operations is different for addition and

subtraction, this flag specifies the type of instruction that was last executed, enabling the

subsequent decimal adjust (DA) operation. Normally, the Decimal Adjust flag cannot be

used as a test condition. After a subtraction, the Decimal Adjust flag is 1. Following an

addition, it is 0.

Half Carry Flag

The Half Carry (H) flag is 1 when an addition generates a carry from Bit 3 or a subtraction

generates a borrow from Bit 4. The DA instruction converts the binary result of a previous

addition or subtraction into the correct BCD result using the Half Carry flag. As in the

case of the Decimal Adjust flag, the user does not normally access this flag directly.

Condition Codes

The C, Z, S and V flags control the operation of the conditional jump (JP cc and JR cc)

instructions. Sixteen frequently useful functions of the flag settings are encoded in a 4-bit

field called the condition code (cc), which forms Bits 7:4 of the first opcode of conditional

jump instructions. Table 2 summarizes the condition codes. Some binary condition codes

can be created using more than one assembly code mnemonic. The result of the flag test

operation determines if the conditional jump executes.

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

7

Arithmetic Logic Unit

The Arithmetic Logic Unit (ALU) performs arithmetic and logical operations on the data.

The arithmetic operations include addition, subtraction, and multiplication. The logical

functions include binary logic operations, bit shifting, and bit rotation.

Byte Ordering

For multi-byte data, the eZ8 CPU stores the most significant byte in the lowest memory

address. For example, the value 1 can be stored as a 2-byte (16-bit) number in Register

Table 2. Condition Codes

Binary

Hex

Assembly

Mnemonic Definition

Flag Test Operation

0000

0

F

Always False

�

0001

1

LT

Less Than

(S XOR V) = 1

0010

2

LE

Less Than or Equal

(Z OR (S XOR V)) = 1

0011

3

ULE

Unsigned Less Than or Equal

(C OR Z) = 1

0100

4

OV

Overflow

V = 1

0101

5

Ml

Minus

S = 1

0110

6

Z

Zero

Z = 1

0110

6

EQ

Equal

Z = 1

0111

7

C

Carry

C = 1

0111

7

ULT

Unsigned Less Than

C = 1

1000

8

T (or blank) Always True

�

1001

9

GE

Greater Than or Equal

(S XOR V) = 0

1010

A

GT

Greater Than

(Z OR (S XOR V)) = 0

1011

B

UGT

Unsigned Greater Than

(C = 0 AND Z = 0)

1100

C

NOV

No Overflow

V = 0

1101

D

PL

Plus

S = 0

1110

E

NZ

Non-Zero

Z = 0

1110

E

NE

Not Equal

Z = 0

1111

F

NC

No Carry

C = 0

1111

F

UGE

Unsigned Greater Than or Equal C = 0

UM012811-0904

Architectural

Overview

eZ8 CPU

User Manual

8

Pair

122H

and

123H

. The value is stored as

0001H

. The most-significant byte (

00H

) is

stored in the lowest memory address at

122H

. The least-significant byte (

01H

) is stored in

the higher memory address at

123H

. This ordering of multi-byte data is often referred to as

"big endian".

eZ8 CPU

User Manual

UM012811-0904

Z8 Compatibility

9

Z8 Compatibility

OVERVIEW

The eZ8 CPU is an extension and improvement of ZiLOG's popular, easy-to-use, and

powerful Z8

�

CPU architecture. Users who have experience programming the Z8

�

CPU

will have no difficulty adapting to the eZ8 CPU. All users will appreciate the new instruc-

tions that improve execution for programs developed in high-level programming lan-

guages such as C.

ASSEMBLY LANGUAGE COMPATIBILITY

The eZ8 CPU executes all Z8

�

assembly language instructions other than WDH (Watch-

Dog Timer Enable During HALT Mode at opcode 4FH). Users with existing Z8

�

assem-

bly code can easily compile their code to use the eZ8 CPU. The assembler for the eZ8

CPU is available for download from

www.zilog.com.

NEW INSTRUCTIONS

The eZ8 CPU features many new instructions to increase processor efficiency and allow

access to the expanded 4KB Register File. There are two classes of new instructions avail-

able in the eZ8 CPU - New Function instructions and Extended Addressing instructions.

New Function Instructions

Table 3 lists the instructions that provide new functionality.

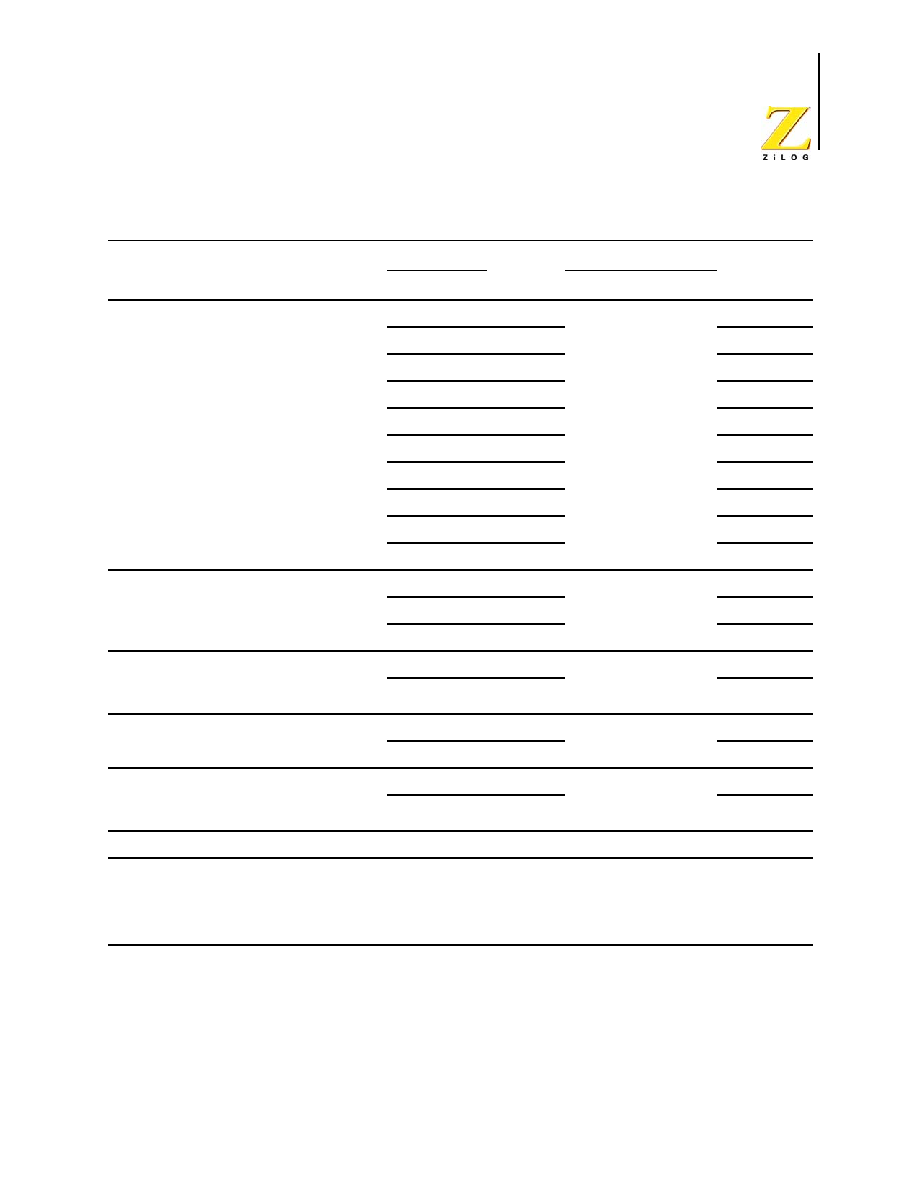

Table 3. New Function Instructions

Mnemonic Instruction Description

ATM

Atomic Execution

BCLR

Bit Clear

BIT

Bit Set or Clear

BRK

Break

BSET

Bit Set

BSWAP

Bit Swap

UM012811-0904

Z8 Compatibility

eZ8 CPU

User Manual

10

Extended Addressing Instructions

New Extended Addressing instructions allow data movement between Register File pages.

These instructions allow the generation of a 12-bit address and direct access to any register

value in the 4KB Register File address space. Table 4. lists the new Extended Addressing

instructions

BTJ

Bit Test and Jump

BTJNZ

Bit Test and Jump if Non-Zero

BTJZ

Bit Test and Jump if Zero

CPC

Compare with Carry

LDC

Load Constant

LDCI

Load Constant and Auto-Increment Addresses

LEA

Load Effective Address

MULT

8-bit X 8-bit multiply with 16-bit result

SRL

Shift Right Logical

TRAP

Software Trap

Table 4. New Extended Addressing Instructions

Mnemonic Instruction Description

ADCX

Add with Carry using Extended Addressing

ADDX

Add using Extended Addressing

ANDX

Logical AND using Extended Addressing

CPCX

Compare with Carry using Extended Addressing

CPX

Compare using Extended Addressing

LDWX

Load Word using Extended Addressing

LDX

Load using Extended Addressing

ORX

Logical OR using Extended Addressing

POPX

Pop using Extended Addressing

PUSHX

Push using Extended Addressing

SBCX

Subtract with Carry using Extended Addressing

SUBX

Subtract using Extended Addressing

Table 3. New Function Instructions (Continued)

Mnemonic Instruction Description

UM012811-0904

Z8 Compatibility

eZ8 CPU

User Manual

11

Alternate Function Opcode

To accommodate the new instructions, the opcode

1FH

refers to a new second opcode

map. The

1FH

is pre-pended to an opcode to select the alternate functions available on the

second opcode map. The CPC, CPCX, SRL, LDWX and PUSH (immediate) instructions

use this second opcode map. Users writing assembly language code can employ the CPC,

CPCX, SRL, LDWX and PUSH (immediate) instructions directly. The eZ8 CPU assem-

bler automatically inserts the

1FH

opcode as necessary.

Moved Instructions

Some of the existing Z8

�

CPU instructions have been moved to new opcodes in the eZ8

CPU. Table 5 lists these moved instruction.

Removed Instructions

The instruction types LD r1, R2 and LD R1, r2 have been removed from the opcode map

as they are now subsets of the LD instruction (opcode E4) using Escaped mode address-

ing. In the Z8

�

CPU, these instructions used opcodes

08H

through

F8H

and

09H

through

F9H

. The assembler for the eZ8 CPU continues to support these instructions. Refer to the

Address Modes chapter and the LD instruction description for more information.

The WDH (Watch-Dog Timer Enable During HALT Mode) instruction has also been

removed. For information regarding the Watch-Dog Timer, refer to the Product Specifica-

tion for the specific device.

TCMX

Test Complement Under Mask using Extended Addressing

TMX

Test Under Mask using Extended Addressing

XORX

Logical XOR using Extended Addressing

Table 5. Instructions with New Opcodes

Instruction

eZ8 CPU Opcode (Hex) Z8

�

CPU Opcode (Hex)

SRP

01

31

DEC R1

30

00

DEC IR1

31

01

JP IRR1

C4

30

NOP

0F

FF

Table 4. New Extended Addressing Instructions (Continued)

Mnemonic Instruction Description

UM012811-0904

Z8 Compatibility

eZ8 CPU

User Manual

12

RELOCATION OF THE EZ8 CPU CONTROL REGISTERS

The four control registers within the eZ8 CPU have new addresses to take advantage of the

larger Register File.

Stack Pointer High and Low Byte Registers

The Stack Pointer Low Byte (SPL) now resides at address

FFFH

in the Register File. The

Stack Pointer High Byte (SPH) now resides at address

FFEH

.

Register Pointer

The Register Pointer (RP) now resides at address

FFDH

in the Register File.

Flags Register

The Flags Register (FLAGS) now resides at address

FFCH

in the Register File.

STACK POINTER COMPATIBILITY

The stack pointer is now 12-bits in length and given by {SPH[3:0], SPL[7:0]}. This

change allows the origin of the stack to be placed at any address from

000H

to

EFFH

where

general-purpose registers are available. Refer to the device-specific Product Specification

for available Register File addresses. All stack pointer operations occur within the Regis-

ter File address space.

RESET COMPATIBILITY

Unlike the Z8

�

CPU which uses a fixed reset address of

00CH

, the eZ8 CPU uses a vec-

tored reset. Program Memory stores the RESET vector at addresses

0002H

and

0003H

(most significant byte at

0002H

and least significant byte at

0003H

). When the eZ8 CPU

is reset it fetches the RESET vector at addresses

0002H

and

0003H.

The eZ8 CPU writes

the RESET factor to the Program Counter. The eZ8 CPU executes code at the new Pro-

gram Counter address.

INTERRUPT COMPATIBILITY

The interrupt table now resides at starting address

0008H

in Program Memory to accom-

modate the increased number of interrupts available with the eZ8 CPU.

eZ8 CPU

User Manual

UM012811-0904

Address

Space

13

Address Space

INTRODUCTION

The eZ8 CPU can access three distinct address spaces:

�

The Register File contains addresses for the general-purpose registers and the eZ8

CPU, peripheral, and I/O port control registers.

�

The Program Memory contains addresses for all memory locations having executable

code and/or data.

�

The Data Memory contains addresses for all memory locations that hold data only.

REGISTER FILE

The eZ8 CPU supports a maximum of 4096 consecutive bytes (registers) in the Register

File. The Register File is composed of two sections - control registers and general-purpose

registers. The upper 256 bytes are reserved for control of the eZ8 CPU, the on-chip periph-

erals, and the I/O ports. These 256 registers are always located at addresses from

F00H

to

FFFH

.

When instructions execute, registers are read from when defined as sources and written to

when defined as destinations. The architecture of the eZ8 CPU allows all general-purpose

registers to function as accumulators, address pointers, index registers, stack areas, or

scratch pad memory.

Some eZ8 CPU products contain a Register File that is less than the maximum of 4096

bytes. For eZ8 CPU products with less than 4096B in the Register File, reading from an

unavailable Register File addresses returns an undefined value. Writing to an unavailable

Register File addresses produces no effect. Refer to the device-specific Product Specifica-

tion to determine the number of registers available in the Register File as well as descrip-

tions of the peripheral and I/O control registers.

CPU Control Registers

Within the 256 registers reserved for control, there are four eZ8 CPU control registers that

are always at the same register addresses. These four eZ8 CPU control registers (see

Table 6) are the Stack Pointer High Byte, Stack Pointer Low Byte, Register Pointer and

Flags registers. For more information on the operation of the eZ8 CPU control registers,

please refer to the Architectural Overview chapter.

UM012811-0904

Address

Space

eZ8 CPU

User Manual

14

General-Purpose Registers

Other than the upper 256 registers reserved for control functions, all other available

addresses within the Register File are available for general-purpose use. Refer to the

device-specific Product Specification to determine the addresses available.

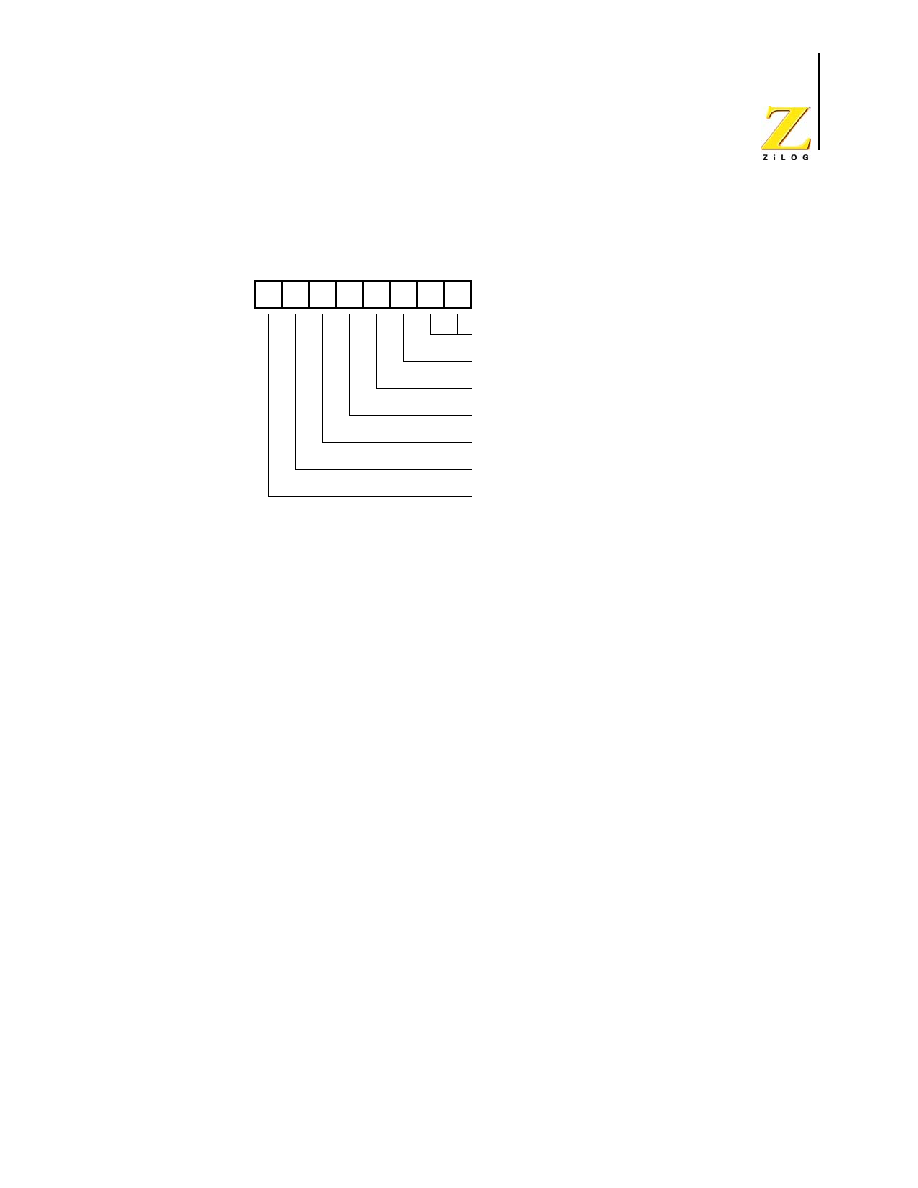

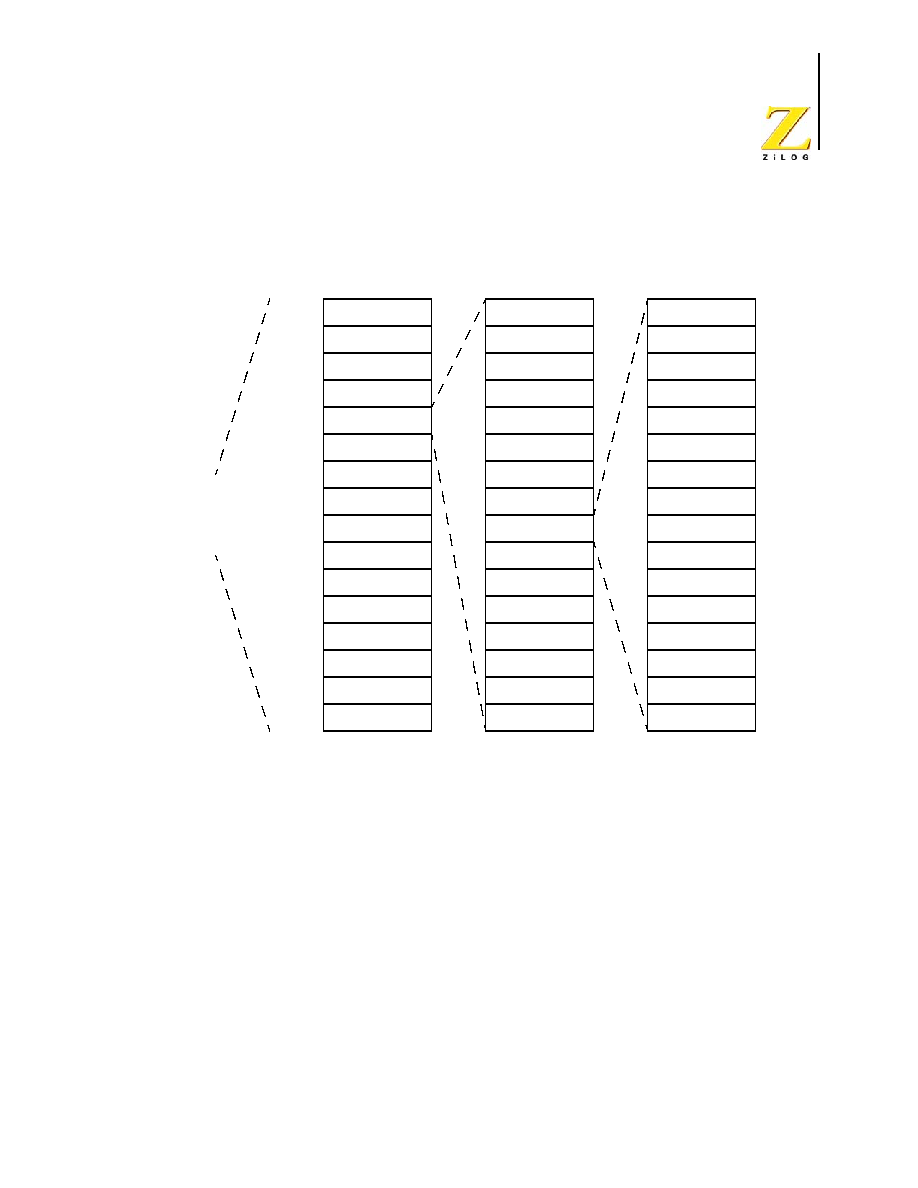

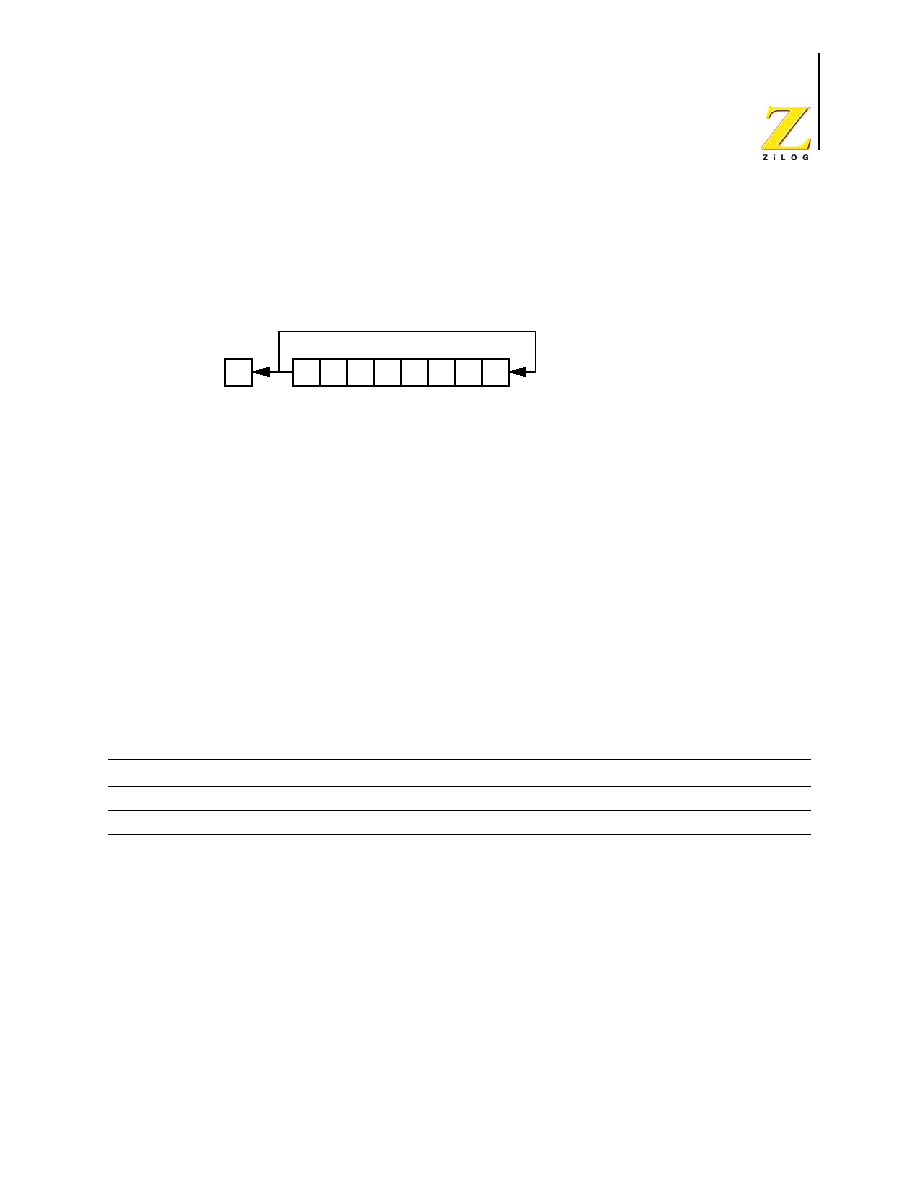

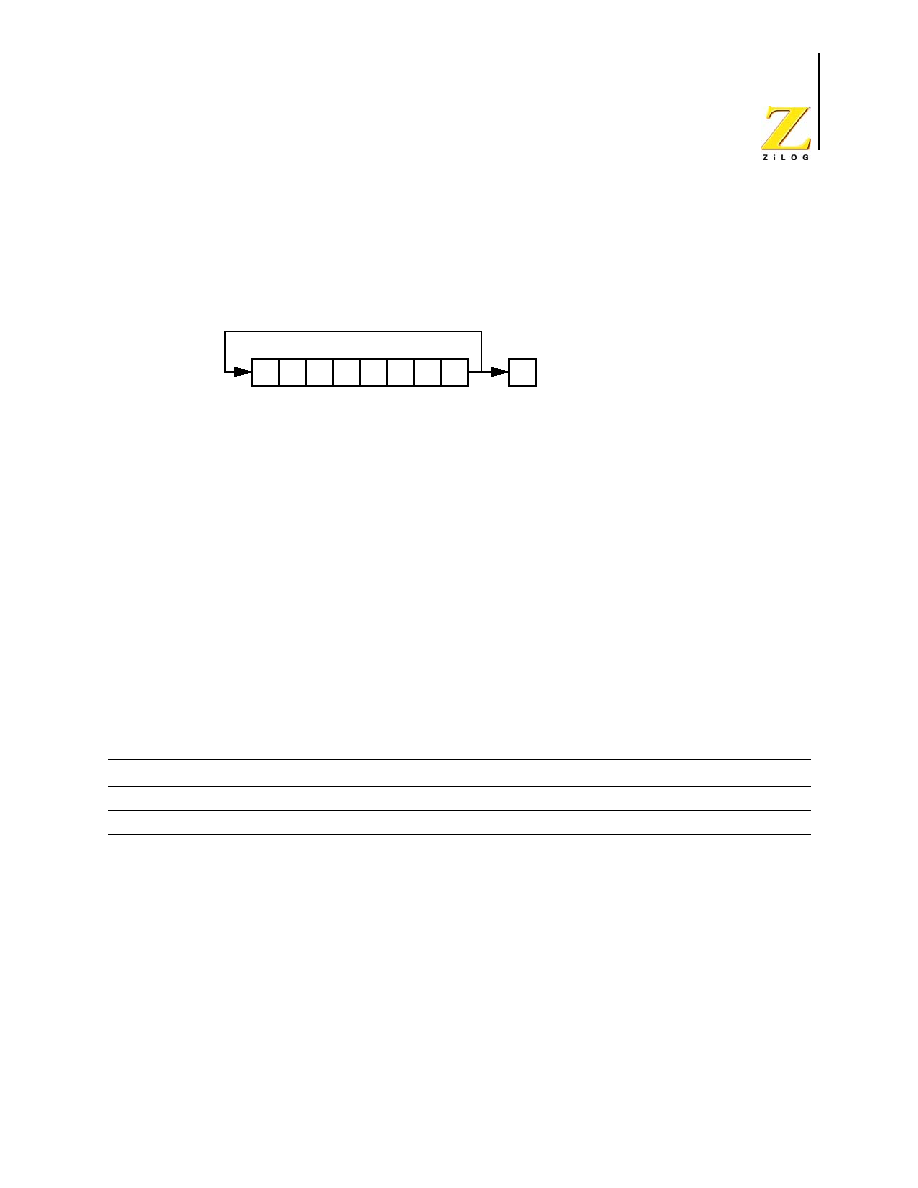

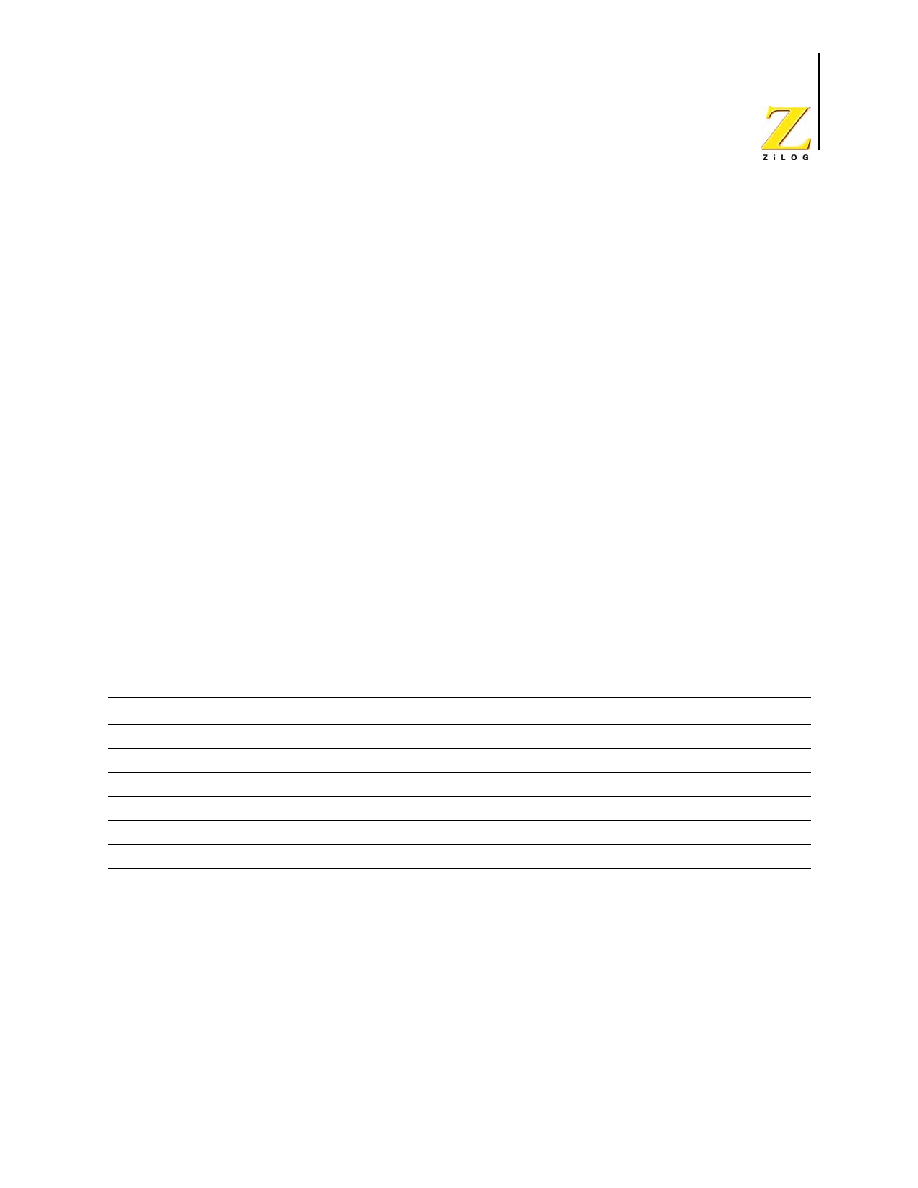

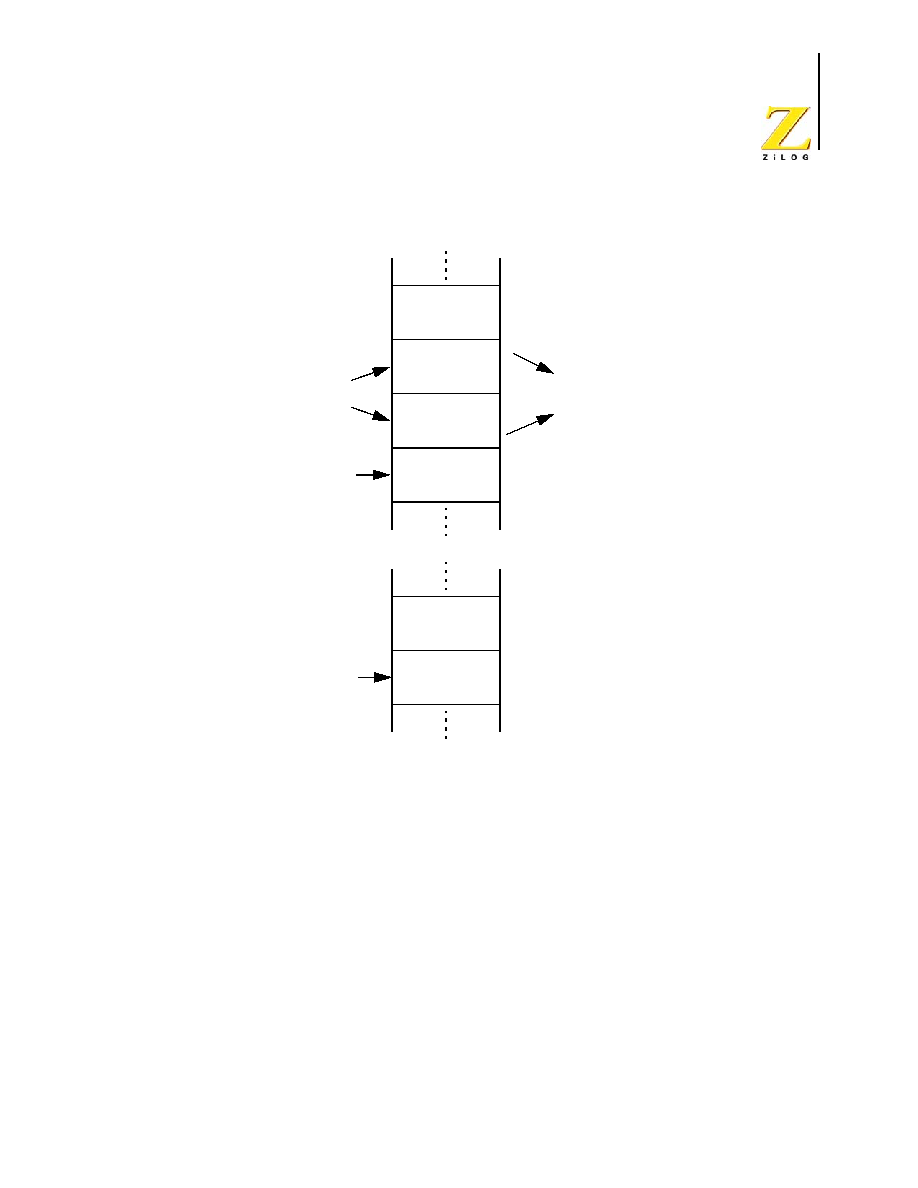

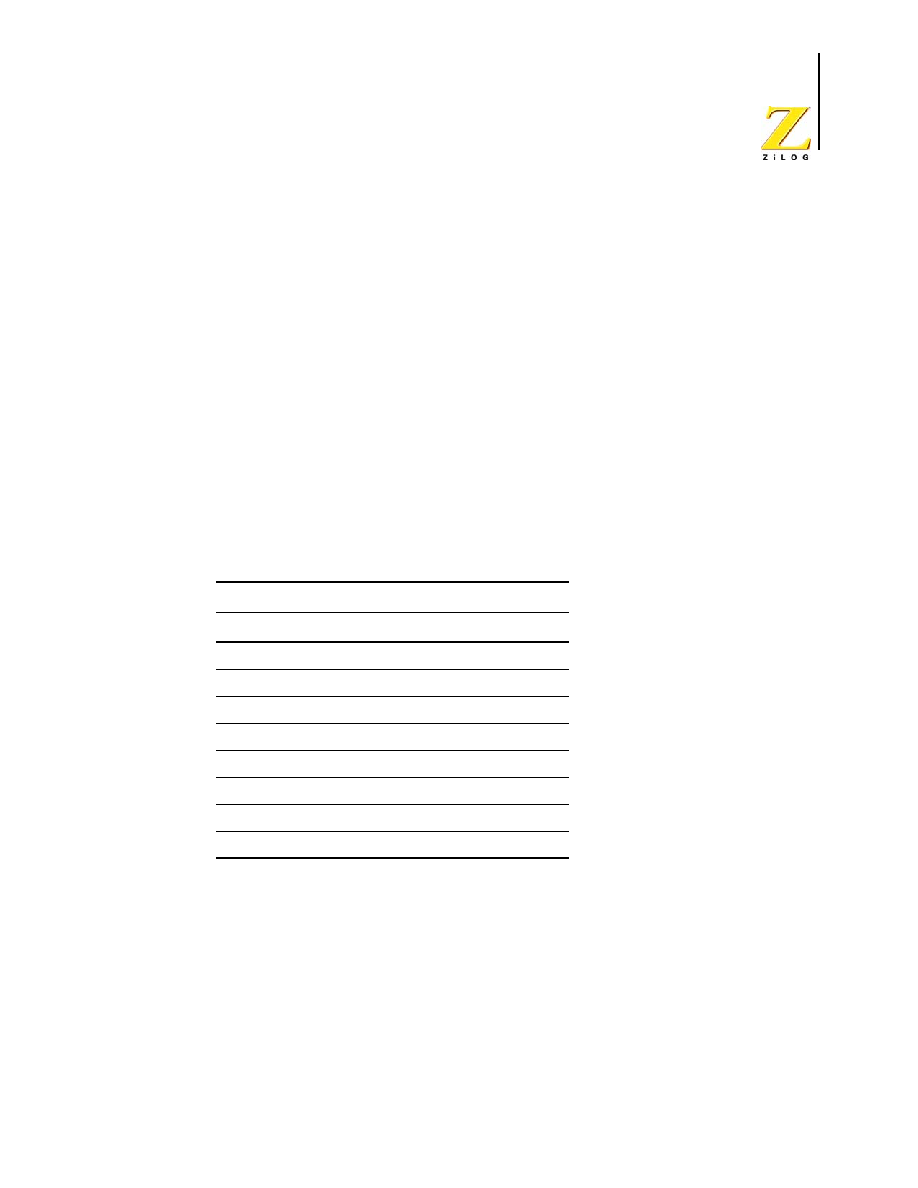

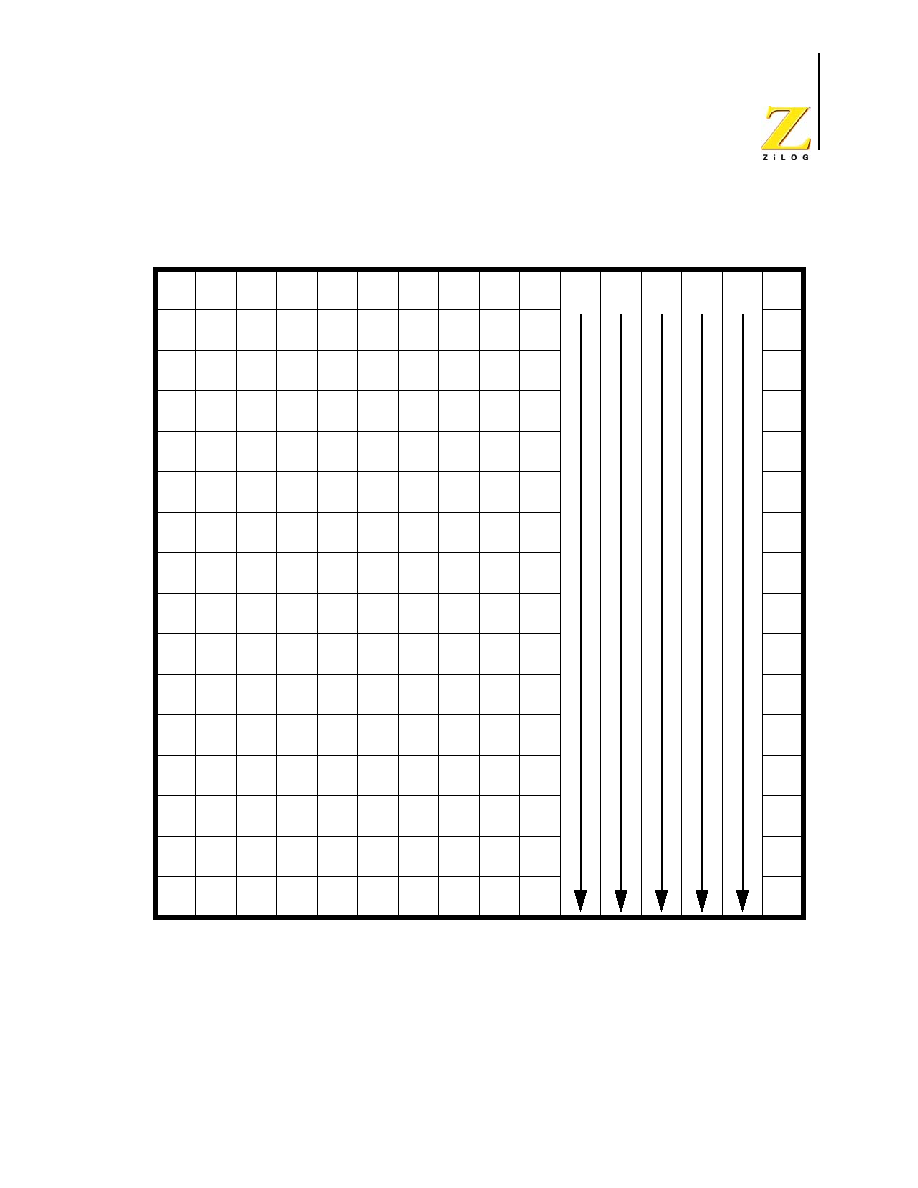

Register File Organization

The Register File can be accessed as a 4096 byte linear address space using 12-bit address-

ing mode, as sixteen 256-byte Register Pages using 8-bit addressing mode, or as sixteen

16-byte Working Register Groups per Register Page using 4-bit addressing mode. Figure 3

illustrates the organization of the Register File. Attempts to read unavailable Register File

addresses return an undefined value. Attempts to write to unavailable Register File

addresses produce no effect.

Table 6. eZ8 CPU Control Registers

Register

Mnemonic

Register Description

Address

(Hex)

FLAGS

Flags

FFC

RP

Register Pointer

FFD

SPH

Stack Pointer High Byte

FFE

SPL

Stack Pointer Low Byte

FFF

UM012811-0904

Address

Space

eZ8 CPU

User Manual

15

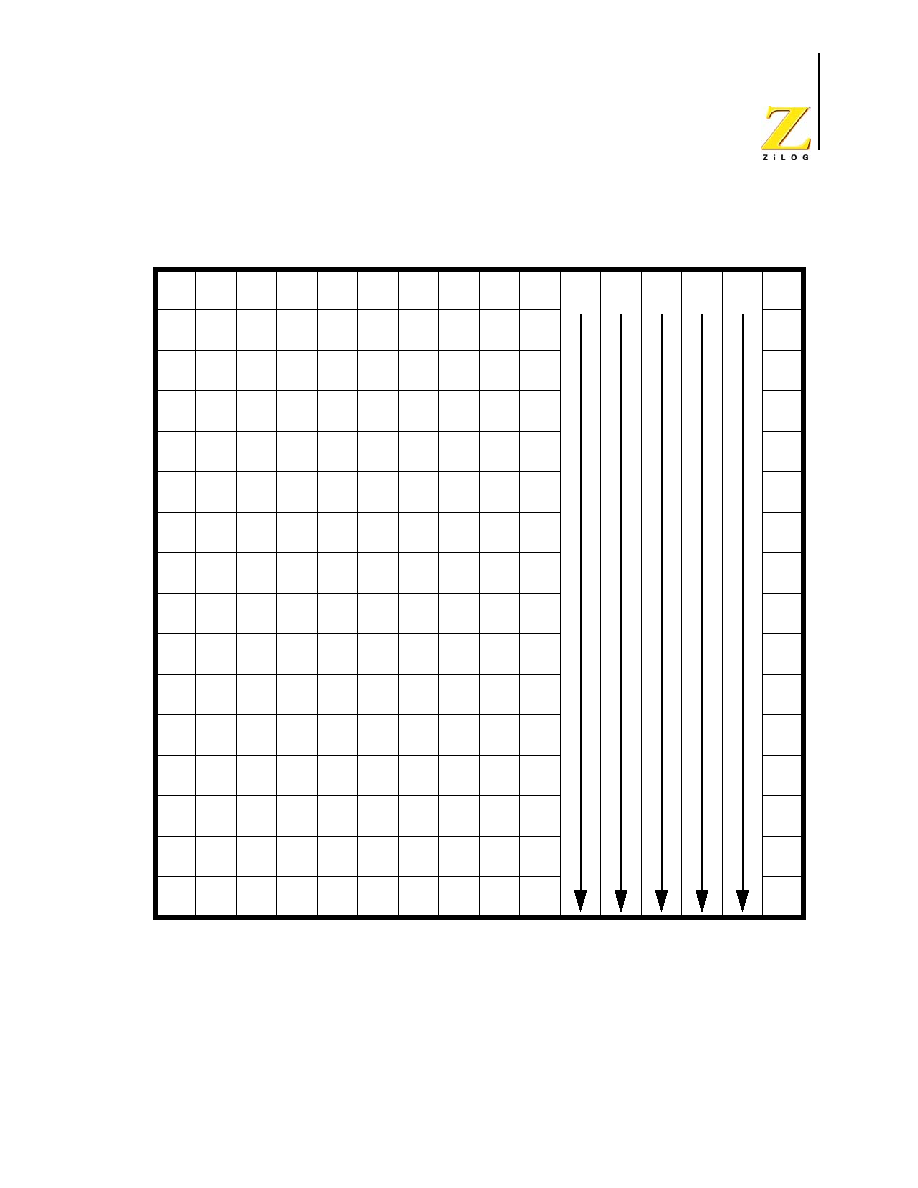

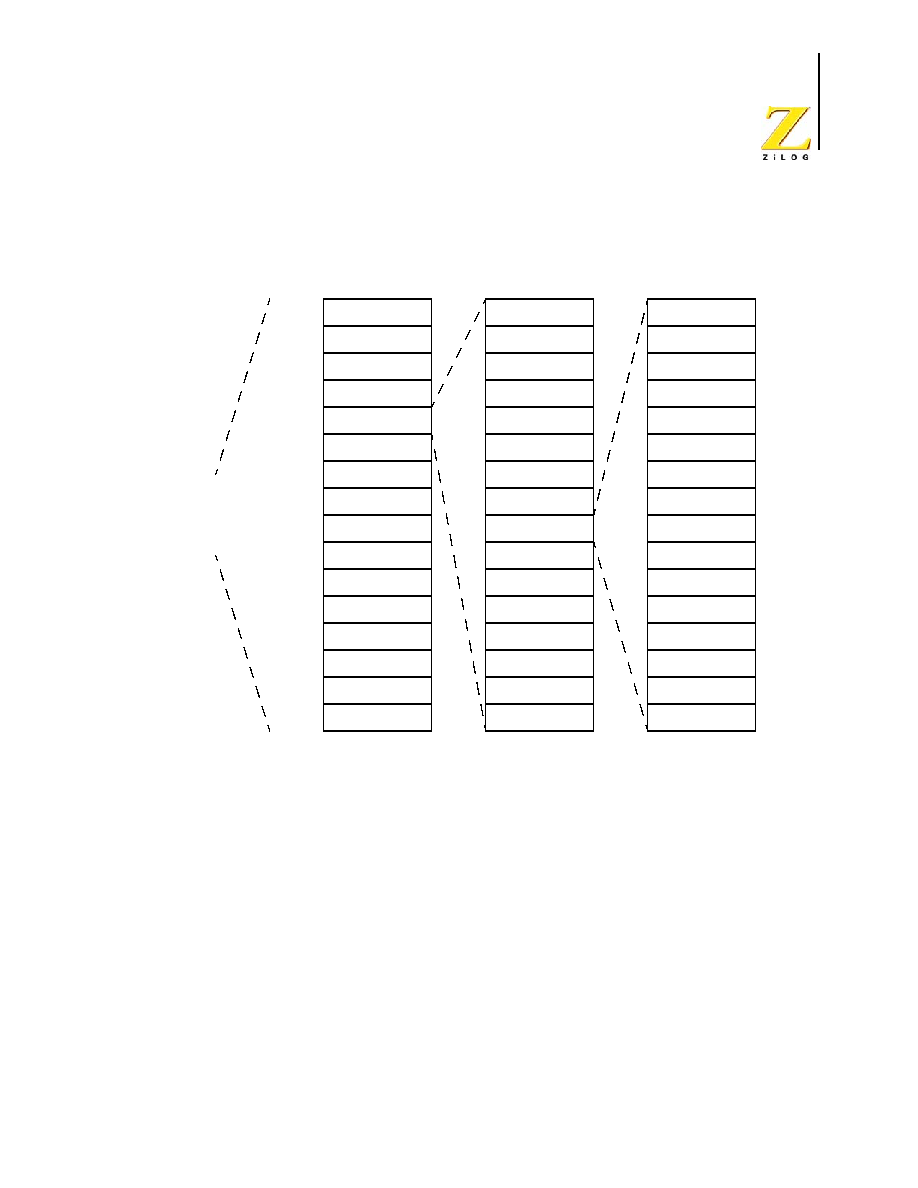

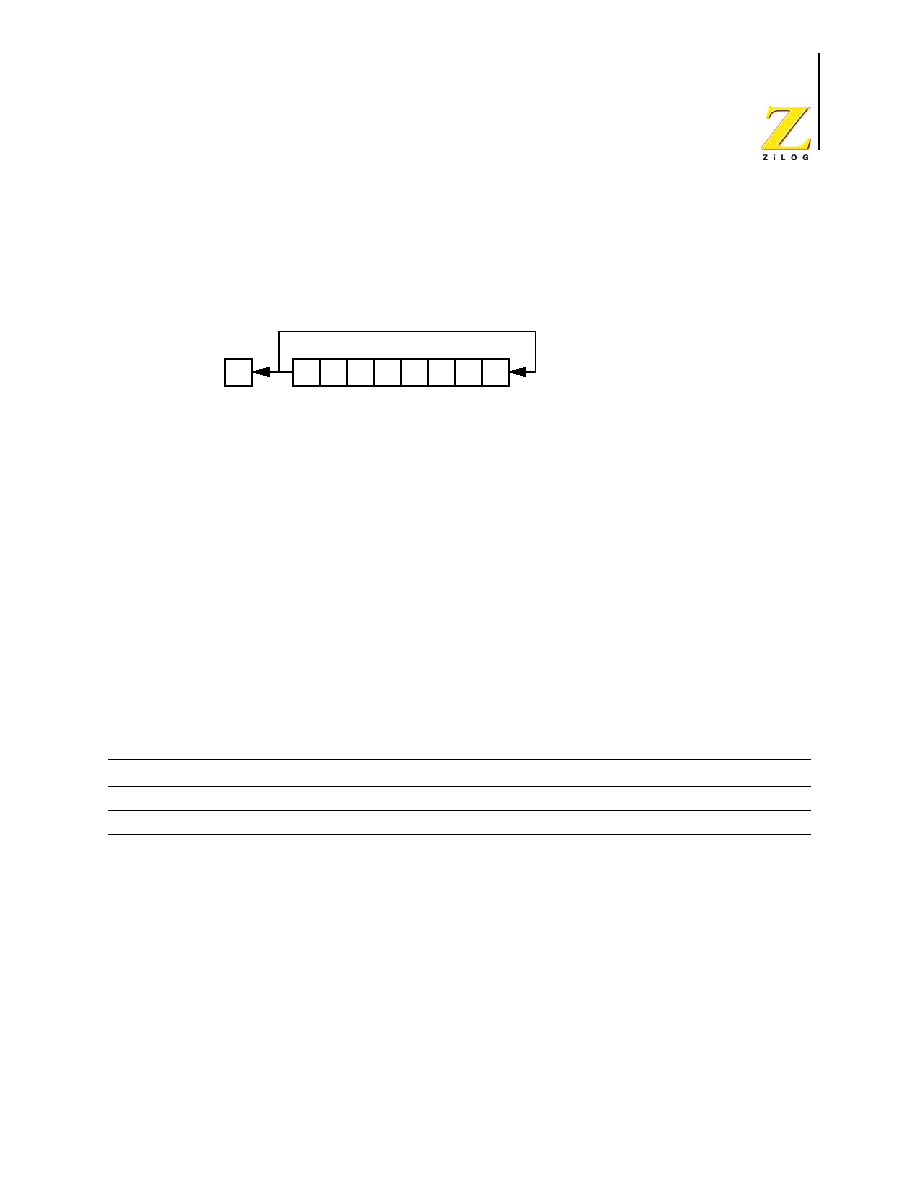

Figure 3. Register File Organization

Linear Addressing of the Register File

Using 12-bit linear addressing, the eZ8 CPU can directly access any 8-bit registers or 16-

bit register pairs within the 4096B Register File. The instructions that support 12-bit

addressing allow direct register access to most registers without requiring a change to the

value of the Register Pointer (RP). To accommodate the increase in the register address

space relative to the Z8

�

architecture, new Extended Addressing instructions have been

added to allow easier register access across page boundaries.

Page Mode Addressing of the Register File

In Page mode, the Register File is divided into sixteen 256-Byte register Pages. The cur-

rent page is determined by the Page Pointer value, RP[3:0]. Registers can be accessed by

Direct, Indirect, or Indexed Addressing using 8-bit addresses. The full 12-bit address is

given by {RP[3:0], Address[7:0]}. All 256 registers on the current page can be referenced

0

16

256B Pages

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

16

16B Working Register

Groups Per Page

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

000H

FFFH

4096B

Linear Addressable

Register File

16

Working Registers

Per Group

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

UM012811-0904

Address

Space

eZ8 CPU

User Manual

16

or modified by any instruction that uses 8-bit addressing. To change to a different page,

use the Set Register Pointer (SRP) instruction to change the value of the Register Pointer.

(Load instructions, LD or LDX, can also be used but require more bytes of code space).

Working Register Addressing of the Register File

Each Register File page is logically divided into 16 Working Register Groups of 16 regis-

ters each. The Working Registers within each Working Register Group are accessible

using 4-bit addressing. The high nibble of the eZ8 CPU Register Pointer (RP) contains the

base address of the active Working Register Group, referred to as the Working Group

Pointer. When accessing one of the Working Registers, the 4-bit address of the Working

Register is combined within the Page Pointer and the Working Group Pointer to form the

full 12-bit address {RP[3:0], RP[7:4], Address[3:0]}. Figure 4 illustrates this operation.

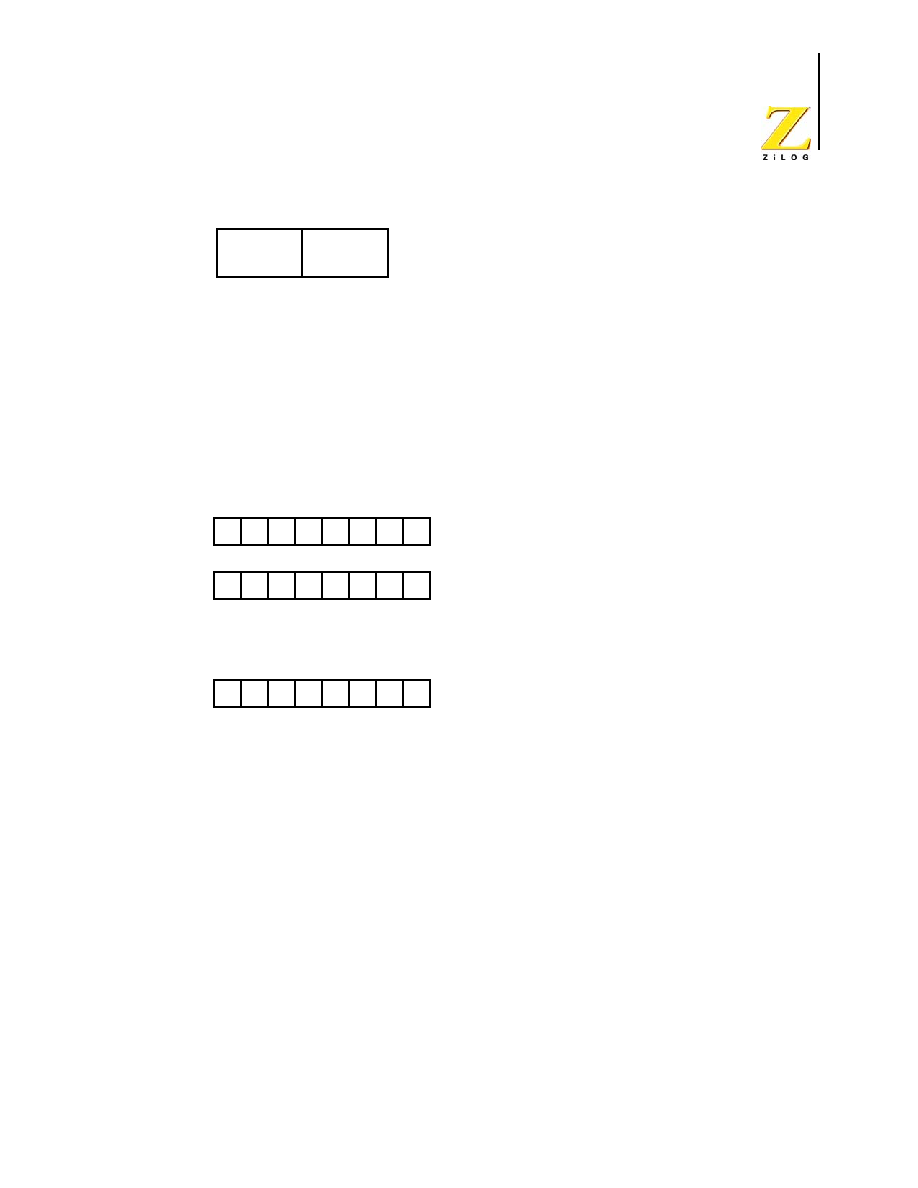

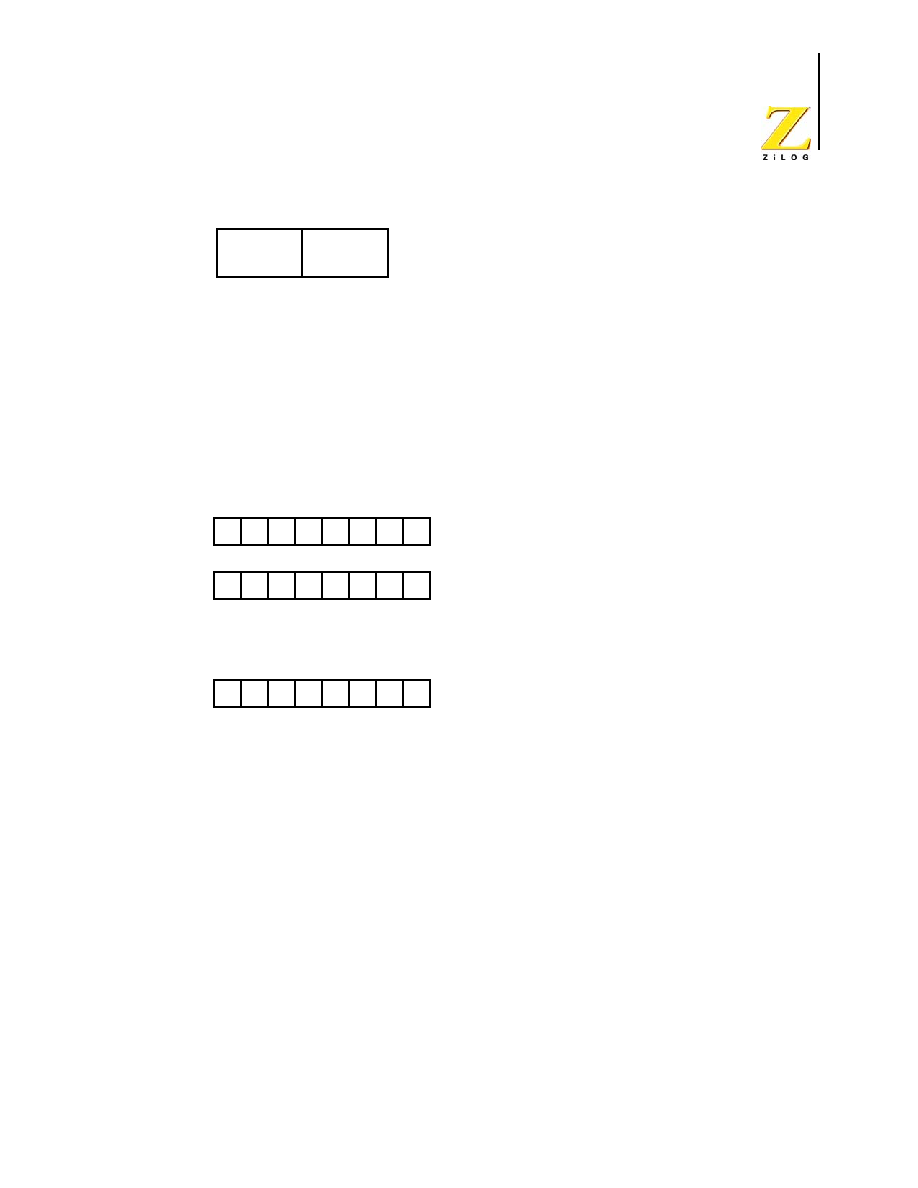

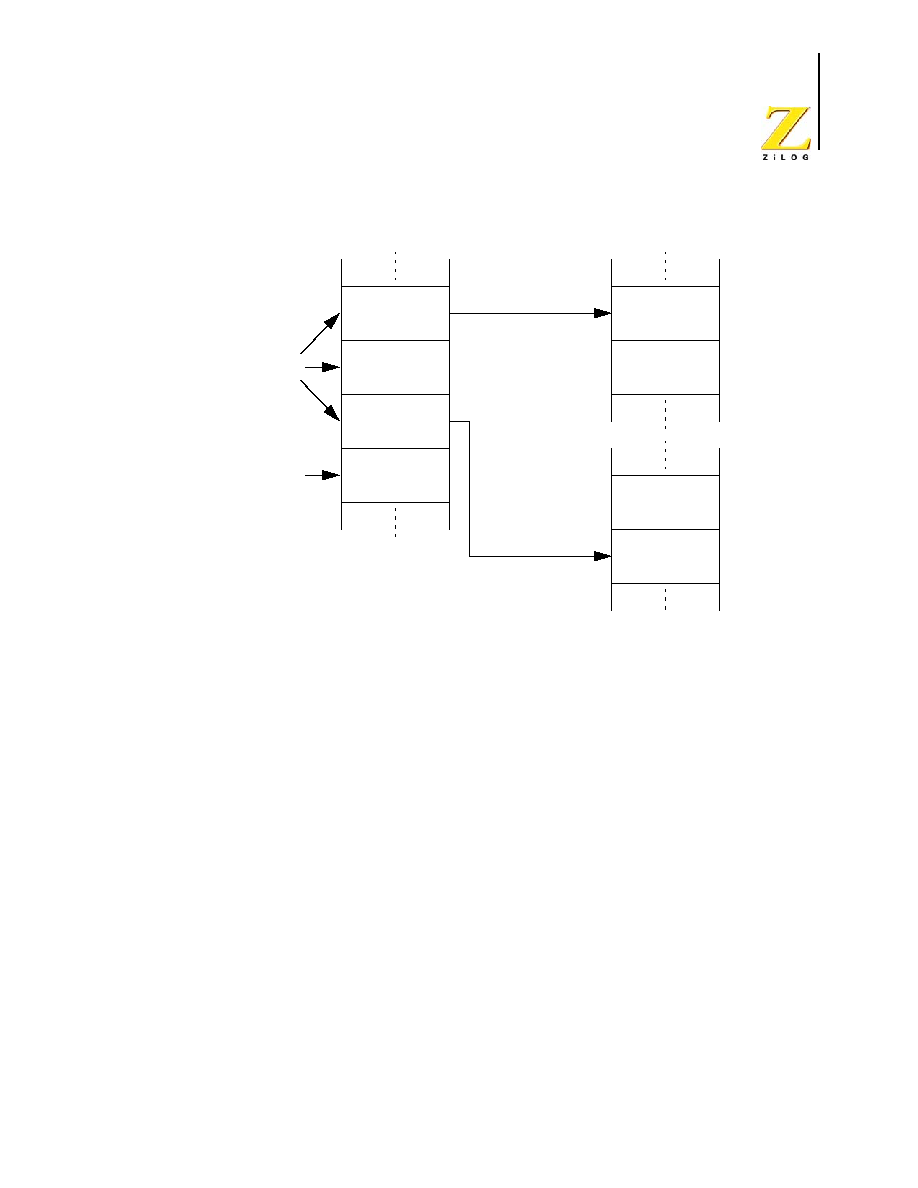

Figure 4. Working Register Addressing Example

Because Working Registers can typically be specified using fewer operand bytes, there are

fewer bytes of code needed, which reduces execution time. In addition, when processing

interrupts or changing tasks, the Register Pointer speeds context switching. The Set Regis-

ter Pointer (SRP) instruction sets the contents of the Register Pointer.

16-bit Register Pairs

Register data may be accessed as a 16-bit word using Register Pairs. In this case, the most

significant byte (MSB) of the data is stored in the even numbered register, while the least

significant byte (LSB) is stored in the next higher odd numbered register (see Figure 5).

Address the register pair using the address of the MSB.

0

1

1

1

0

0

1

1

Register Pointer

0

1

1

0

1

1

1

0

INC R6

0

1

1

1

0

1

1

0

Bit

0

Bit

7

0

0

1

1

Full 12-bit Register Address (376H)

Bit

11

Bit

0

Working Group

Page

Working Register

4-bit Address

UM012811-0904

Address

Space

eZ8 CPU

User Manual

17

Figure 5. 16-Bit Register Pair Addressing

Bit Addressing

Many eZ8 CPU instructions allow access to individual bits within registers. Figure 6 illus-

trates how the instruction AND R15, MASK can clear an individual bit.

Figure 6. Bit Addressing Example

Register File Precautions

Some control registers within the Register File provide Read-Only or Write-Only access.

When accessing these Read-Only or Write-Only registers, insure that the instructions do

not attempt to read from a Write-Only register or, conversely, write to a Read-Only regis-

ter. To determine which control registers allow either Read-Only or Write-Only access,

refer to the device-specific Product Specification.

PROGRAM MEMORY

The eZ8 CPU can access 64KB (65,536 bytes) of Program Memory. The Program Mem-

ory provides storage for both executable program code and data. For each product within

the eZ8 CPU family, a block of Program Memory beginning at address

0000H

is reserved

for option bits, the Reset vector, the Watch-Dog Timer time-out vector, the Illegal Instruc-

tion Trap vector, and the Interrupt vectors. The rest of the Program Memory stores code

MSB

LSB

Rn Rn+1

n = Even Address

0

1

1

1

0

0

0

0

R15

1

1

0

1

1

1

1

1

MASK = DFH

0

1

0

1

0

0

0

0

R15

Bit

0

Bit

7

AND R15, DFH

; Clear Bit 5 of Working Register 15

UM012811-0904

Address

Space

eZ8 CPU

User Manual

18

and data. Program Memory is accessed using opcode fetches, operand fetches, and LDC/

LDCI instructions. Table 7 provides an example of a Program Memory map for a eZ8

CPU product with 64KB of Program Memory and 16 interrupt vectors.

Individual products containing the eZ8 CPU support varying amounts of Program Mem-

ory. Refer to the device-specific Product Specification for your product to determine the

amount of Program Memory available. Attempts to read or execute from unavailable Pro-

gram Memory addresses return

FFH

. Attempts to write to unavailable Program Memory

addresses produce no effect.

DATA MEMORY

In addition to the Register File and the Program Memory, the eZ8 CPU also accesses a

maximum of 64KB (65,536 bytes) of Data Memory. The Data Memory space provides

data storage only. Opcode and operand fetches cannot be executed out of this space.

Access is obtained by the use of the LDE and LDEI instructions. Valid addresses for the

Data Memory are from

0000H

to

FFFFH

.

Individual products containing the eZ8 CPU support varying amounts of Data Memory.

Refer to the device-specific Product Specification for your product to determine the

amount of Data Memory available. Attempts to read unavailable Data Memory addresses

returns

FFH

. Attempts to write to unavailable Data Memory addresses produce no effect.

STACKS

Stack operations occur in the general-purpose registers of the Register File. The Register

Pair

FFEH

and

FFFH

form the 16-bit Stack Pointer (SP) used for all stack operations. The

Stack Pointer holds the current stack address. The Stack Pointer must be always be set to

point to a section of the Register File that does not cause user program data to be over-

written. Even for linear program code that may not employ the stack for Call and/or Inter-

Table 7. Program Memory Map Example

Program Memory

Address (Hex)

Description

0000-0001

Option Bits

0002-0003

RESET Vector

0004-0005

Watch-Dog Timer Vector

0006-0007

Illegal Instruction Trap Vector

0008-0027

Interrupt Vectors

0028-FFFF

Program code and data

UM012811-0904

Address

Space

eZ8 CPU

User Manual

19

rupt routines, the Stack Pointer must be set to prepare for possible Illegal Instruction

Traps.

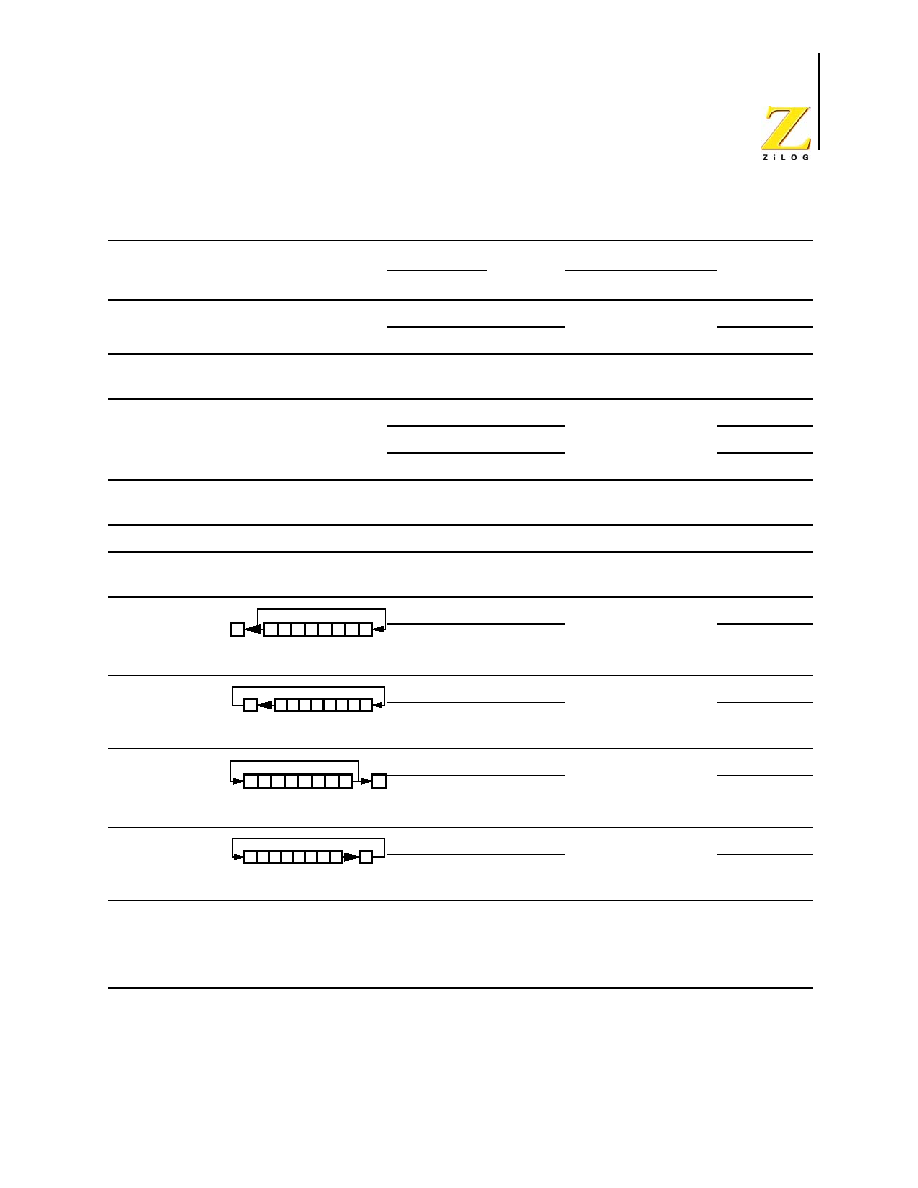

The stack address decrements prior to a PUSH operation and increments after a POP oper-

ation. The stack address always points to the data stored at the top of the stack. The stack

is a return stack for interrupts and CALL and TRAP instructions. It can also be employed

as a data stack.

During a CALL instruction, the contents of the Program Counter are saved on the stack.

The Program Counter is restored during execution of a Return (RET). Interrupts and Traps

(either the TRAP instruction or an Illegal Instruction Trap) save the contents of the Pro-

gram Counter and the Flags Register on the stack. The Interrupt Return (IRET) instruction

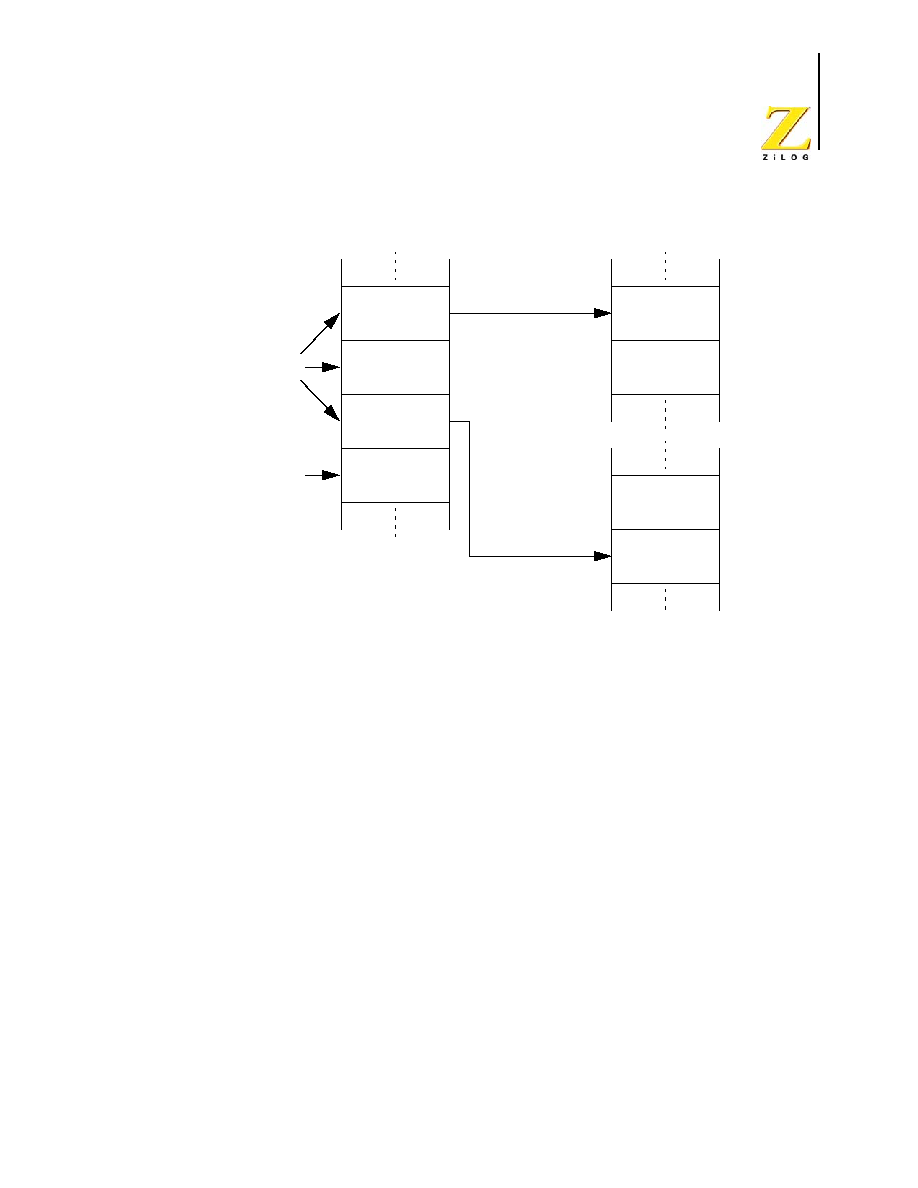

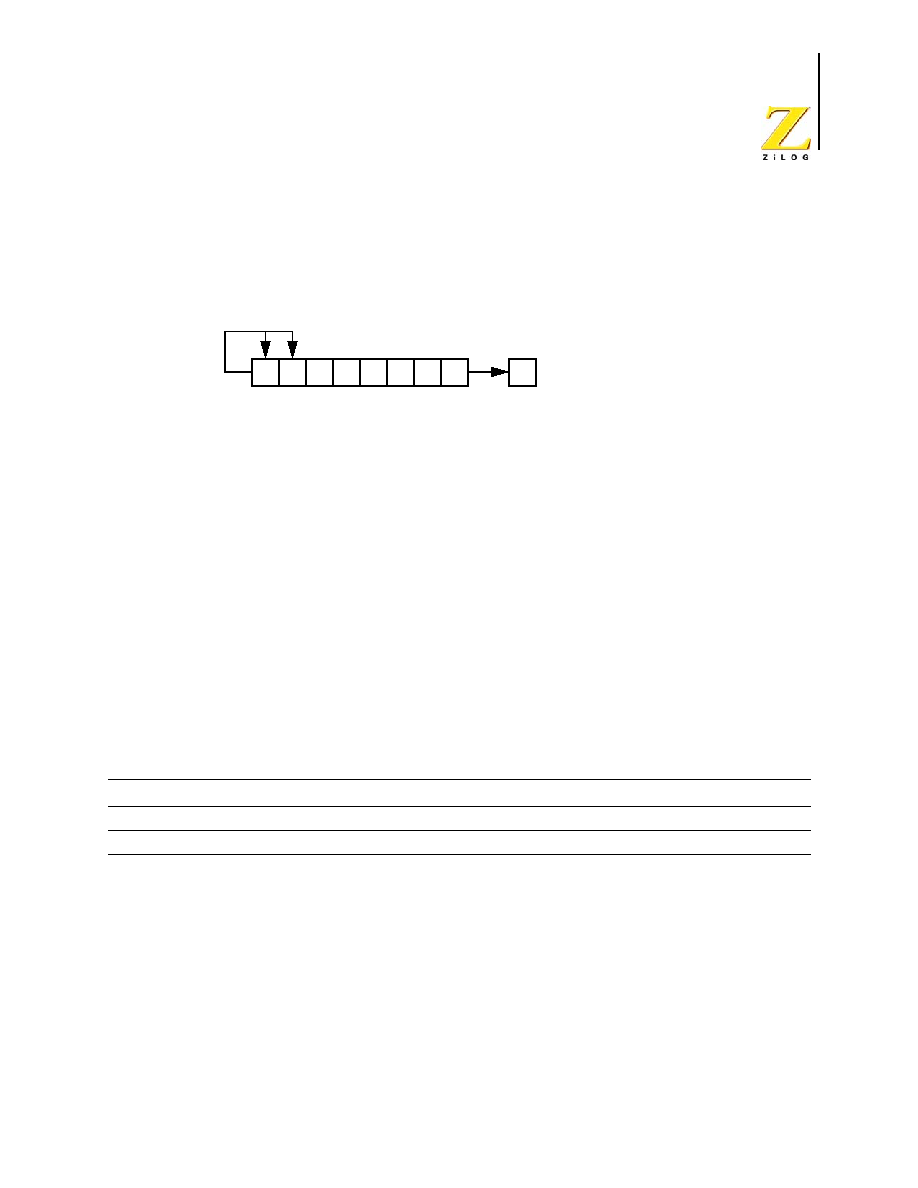

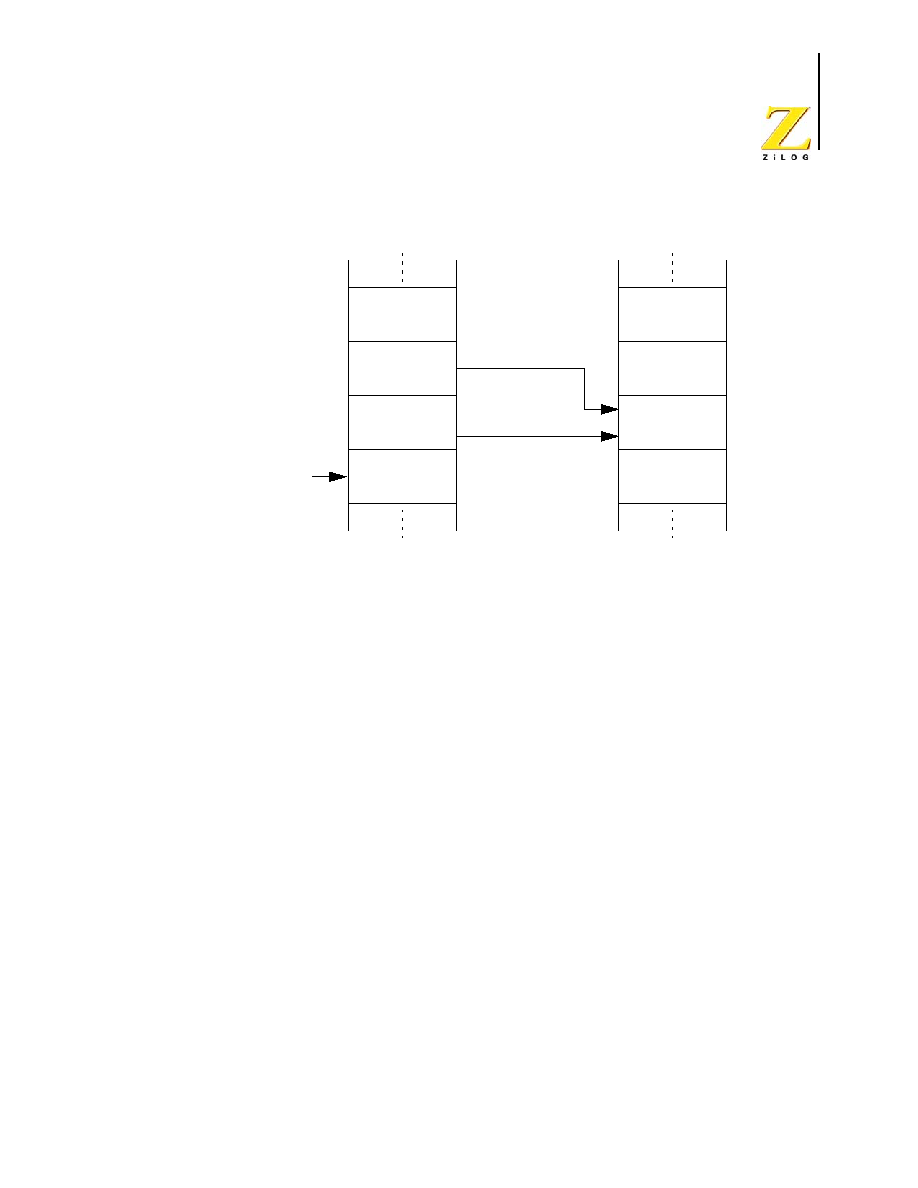

restores them. Figure 7 illustrates the contents of the Stack and the location of the Stack

Pointer following Call, Interrupt and Trap operations.

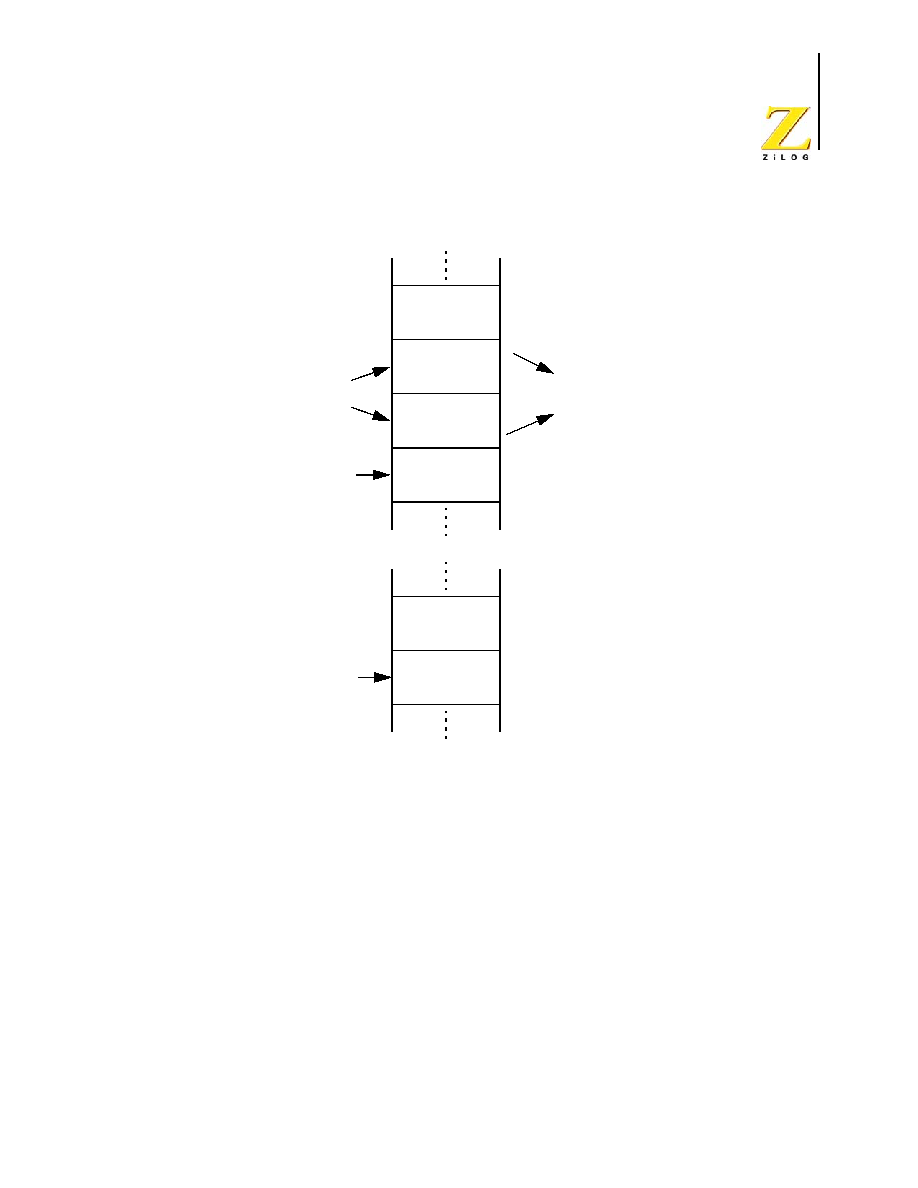

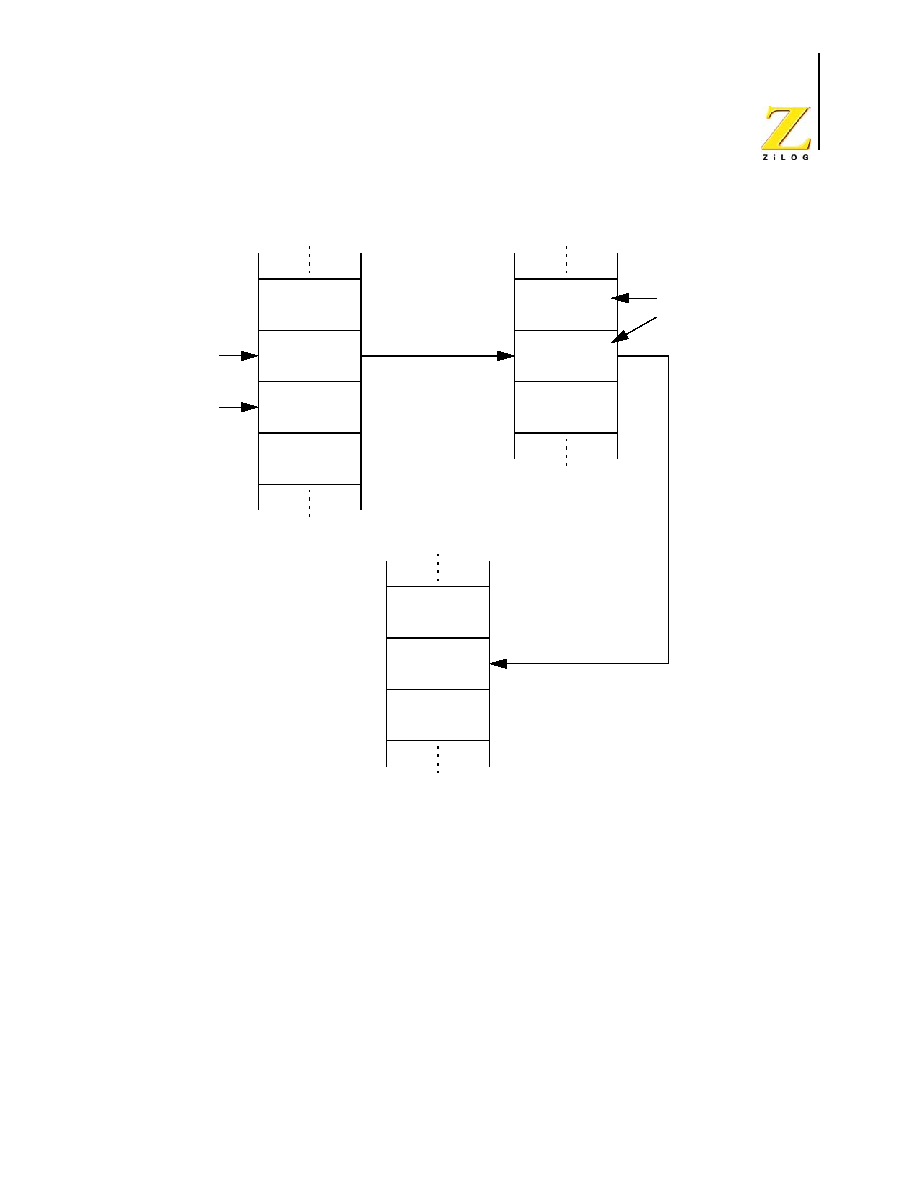

Figure 7. Stack Operations

An overflow or underflow can occur when the stack address is incremented or decre-

mented beyond the available address space. The programmer must prevent this occurrence

or unpredictable operation will result.

PC[15:8]

PC[7:0]

Top of Stack

Flags

PC[15:8]

PC[7:0]

Top of Stack

Stack Contents

After an

Interrupt or Trap

Stack Contents

After a

Call Instruction

eZ8 CPU

User Manual

UM012811-0904

Addressing

Modes

20

Addressing Modes

INTRODUCTION

The eZ8 CPU provides six addressing modes:

�

Register (R)

�

Indirect Register (IR)

�

Indexed (X)

�

Direct (DA)

�

Relative (RA)

�

Immediate Data (IM)

With the exception of immediate data and condition codes, all operands are expressed as

either Register File, Program Memory, or Data Memory addresses. Registers use 12-bit

addresses in the range of

000H

-

FFFH

. Program Memory and Data Memory use 16-bit

addresses (register pairs) in the range of

0000H

-

FFFFH

.

Register pairs can designate 16-bit values or memory addresses. Working Register Pairs

use 4-bit addresses and must be specified as an even-numbered address in the range of 0,

2, ..., 14. Register Pairs use 8-bit addresses and must be specified as an even-numbered

address in the range of 0, 2, ..., 254.

In the following definitions of Addressing Modes, the use of 'register' can imply a Regis-

ter, a Register Pair, a Working Register, or a Working Register pair, depending on the con-

text.

Refer to the device-specific Product Specification for details of the Program, Data, and

Register File memory types and address ranges available.

REGISTER ADDRESSING (R)

Register Addressing Using 12-Bit Addresses

Extended register addressing is used to directly access any register in the Register File.

The 12-bit address is supplied in the operands. There are two types of extended mode

instructions: Register to Register operations and Immediate to Register operations.

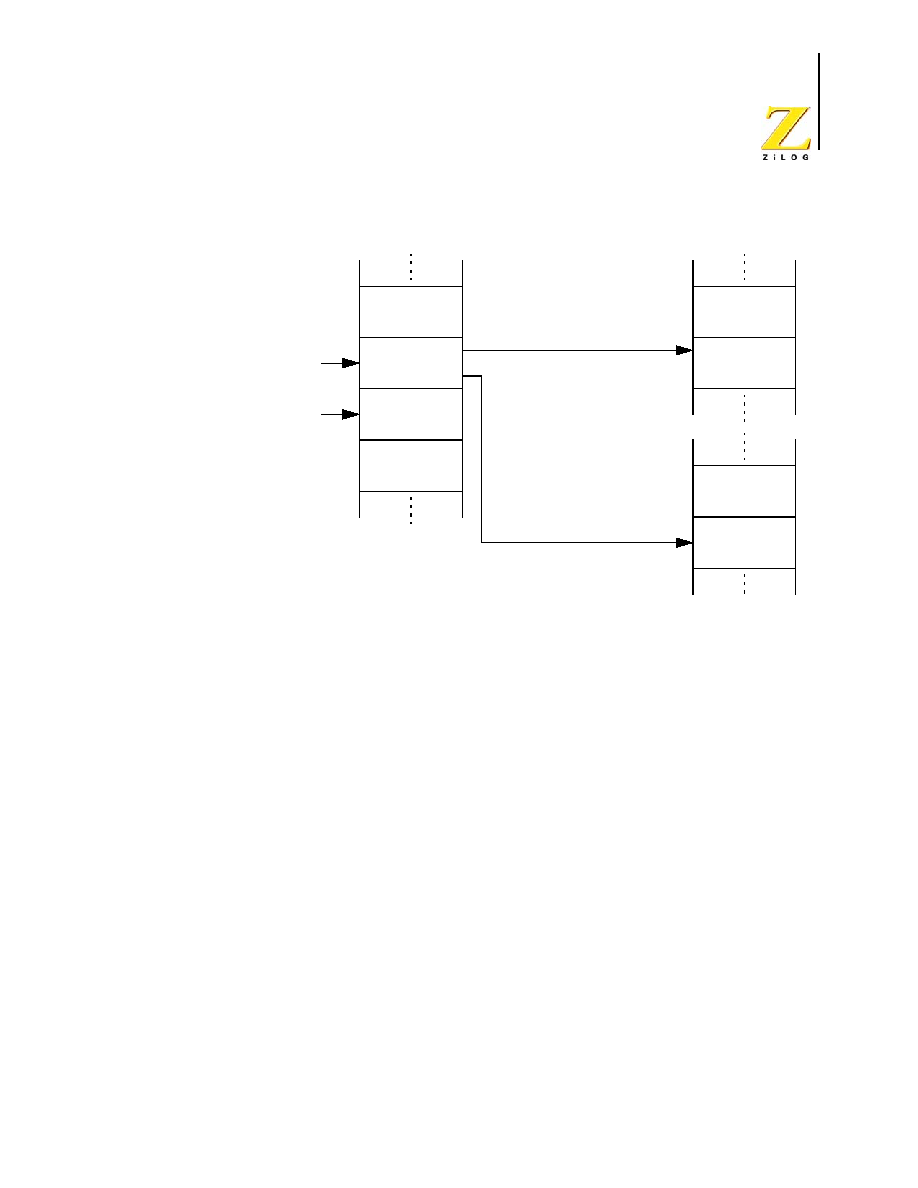

Figure 8 illustrates Register addressing using 12-bit addresses.

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

21

Figure 8. Register Addressing Using 12-Bit Addresses

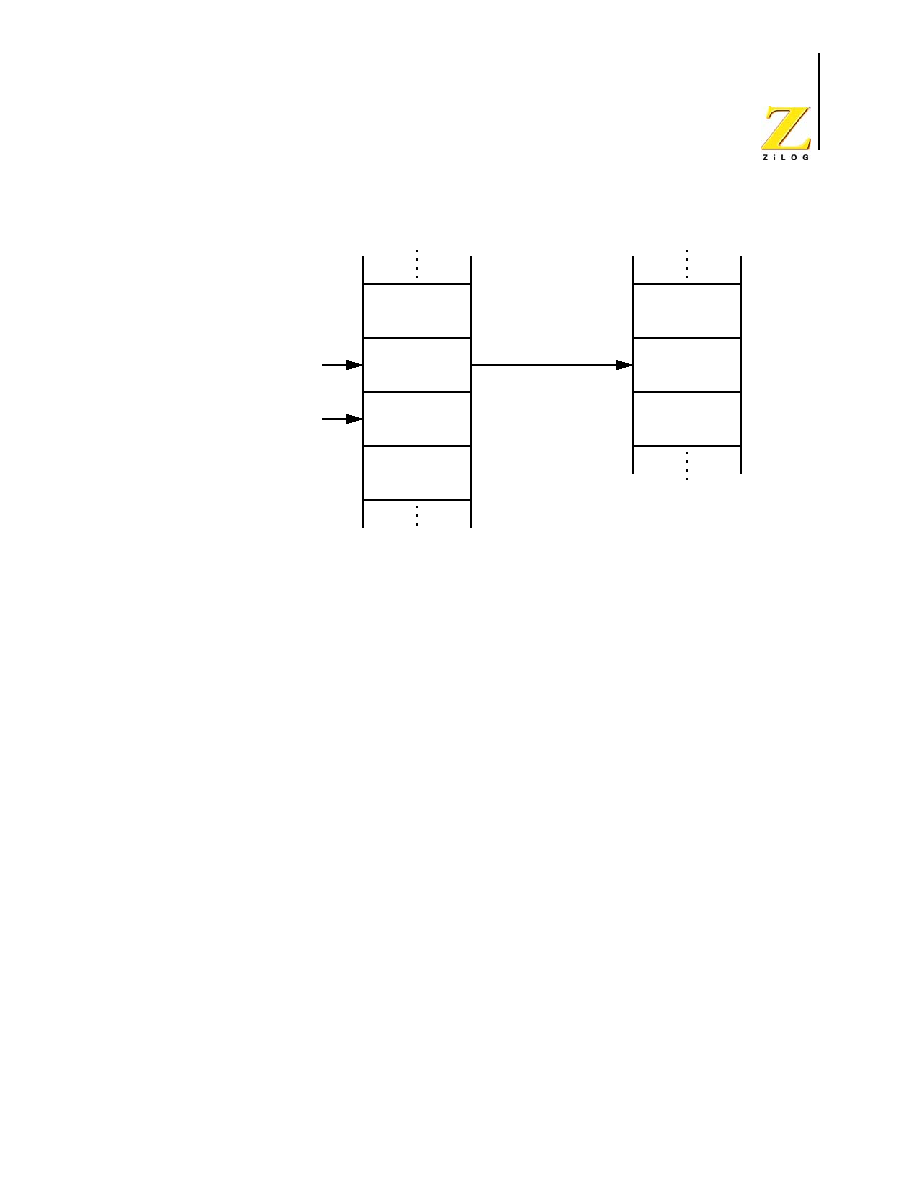

Register Addressing Using 8-Bit Addresses

Registers or Register Pairs may be accessed using 8-bit addresses supplied in the oper-

ands. Any of the 256 registers on the current Register File Page can be accessed using 8-

bit addressing. The upper 4-bits of the 12-bit address is provided by the Page Pointer,

RP[3:0]. The full 12-bit address is given by {RP[3:0], Address[7:0]}.

Figure 9 illustrates using 8-bit addressing, the destination and/or source address specified

corresponds to the a register in the Register File.

Two 12-bit

Program Memory

Addresses

(dst, src)

Three Operand

Instruction

(Example)

Opcode

src[11:4]

{src[3:0},

dst[11:8]}

dst[7:0]

Source

Destination

Register File

Register

Register

12-bit address is

dst[11:0]

12-bit address is

src[11:0]

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

22

Figure 9. Register Addressing Using 8-Bit Addresses

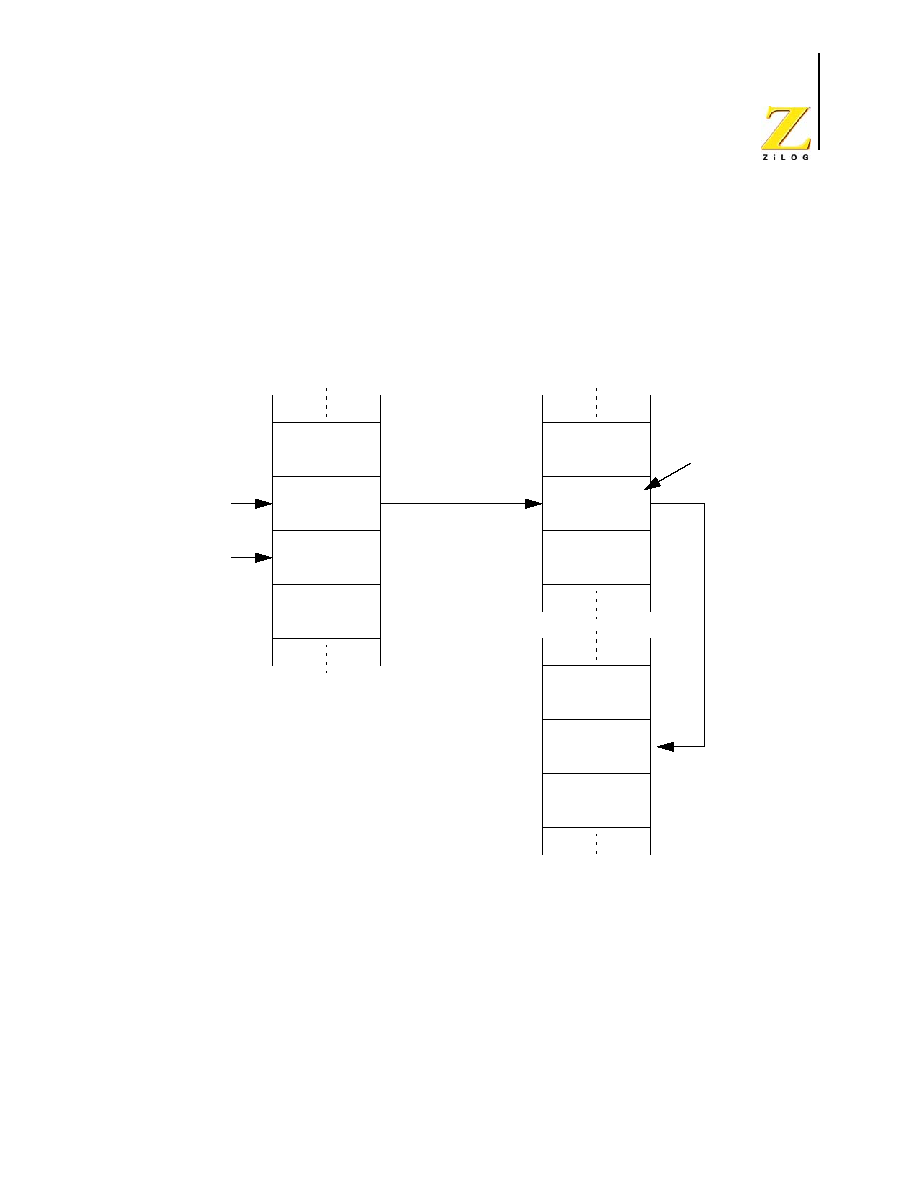

Register Addressing Using 4-Bit Addresses

Working Registers or Working Register Pairs may be accessed using 4-bit addresses sup-

plied in the operands. With 4-bit Addressing, the destination and/or source addresses point

to one of the 16 possible Working Registers within the current Working Register Group.

This 4-bit address is combined with the Page Pointer, RP[3:0], and the Working Group

Pointer, RP[7:4], to form the actual 12-bit address in the Register File. The full 12-bit

address is given by {RP[3:0], RP[7:4], Address[3:0]}. Figure 10 illustrates 4-bit address-

ing of the Register File.

One 8-bit

Program Memory

Address

(dst)

One Operand

Instruction

(Example)

Opcode

dst[7:0]

Destination

Register File

Register

12-bit address is

{RP[3:0], dst[7:0]}

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

23

Figure 10. Register Addressing Using 4-Bit Addresses

Escaped Mode Addressing

Escaped Mode Addressing with 8-bit Addresses

Using Escaped Mode Addressing 12-bit addresses can specify a Working Register. If the

high nibble of the 8-bit address is

EH

(1110b), a Working Register is inferred. For exam-

ple, if Working Register R12 (

CH

) is the desired destination operand, use

ECH

as the 8-bit

address operand in the opcode. To access Registers with addresses

E0H

to

EFH

, either set

the Working Group Pointer, RP[7:4], to

EH

or use indirect addressing.

Escaped Mode Addressing with 12-bit Addresses

Using Escaped Mode Addressing, address mode ER for the source or destination can spec-

ify a Working Register with 4-bit addressing.

If the high byte of the source or destination address is EEH (11101110B), a Working Reg-

ister is inferred. For example, the operand EE3H selects Working Register R3. The full 12-

bit address is given by {RP[3:0], RP[7:4], 3H}.

To access Registers on Page EH (addresses E00H to EFFH), set the Page Pointer, RP[3:0],

to EH and set the Working Group Pointer, RP[7:4], to the desired Working Group.

Two 4-bit

Program Memory

Addresses

(dst, src)

One Operand

Instruction

(Example)

Opcode

{dst[3:0],

12-bit address is

{RP[3:0], RP[7:4], dst[3:0]}

src[3:0]}

Source

Destination

Register

Register

Register File

12-bit address is

{RP[3:0], RP[7:4], src[3:0]}

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

24

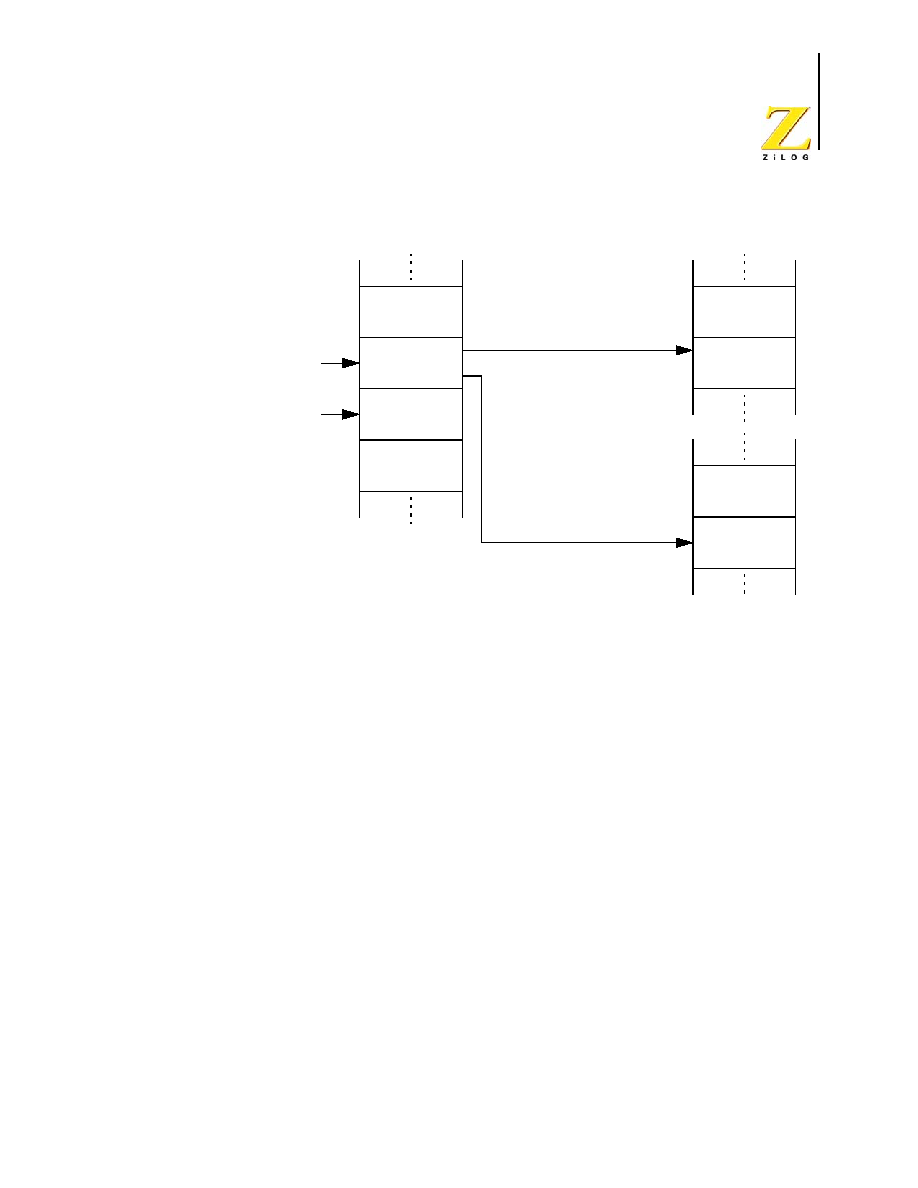

INDIRECT REGISTER ADDRESSING (IR)

In Indirect Register Addressing Mode, the contents of the specified Register provide an

address as illustrated in Figures 11 and 12. Depending upon the instruction selected, the

specified Register contents point to a Register File, Program Memory, or an Data Memory

location. When accessing Program Memory or Data Memory, Register Pairs or Working

Register Pairs hold the 16-bit addresses.

Figure 11. Indirect Register Addressing to Register File

One 8-bit

Program Memory

Address

(dst)

One Operand

Instruction

(Example)

Opcode

dst[7:0]

Destination

Register File

Register

12-bit address is

{RP[3:0], dst[7:0]}

Value used

in execution

Register

contains 8-bit

address (addr[7:0])

12-bit address is

{RP[3:0], ad

dr[7

:0

]}

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

25

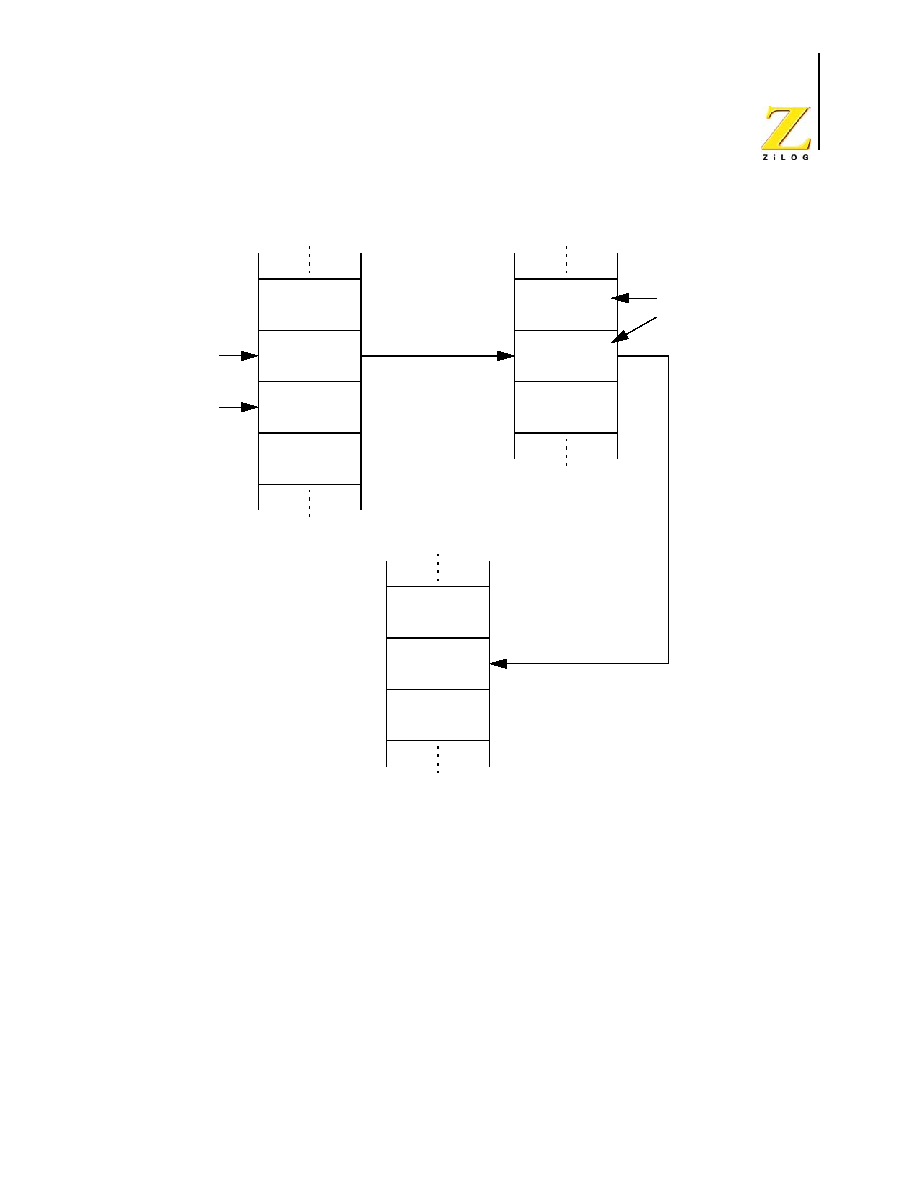

Figure 12. Indirect Register Addressing to Program or Data Memory

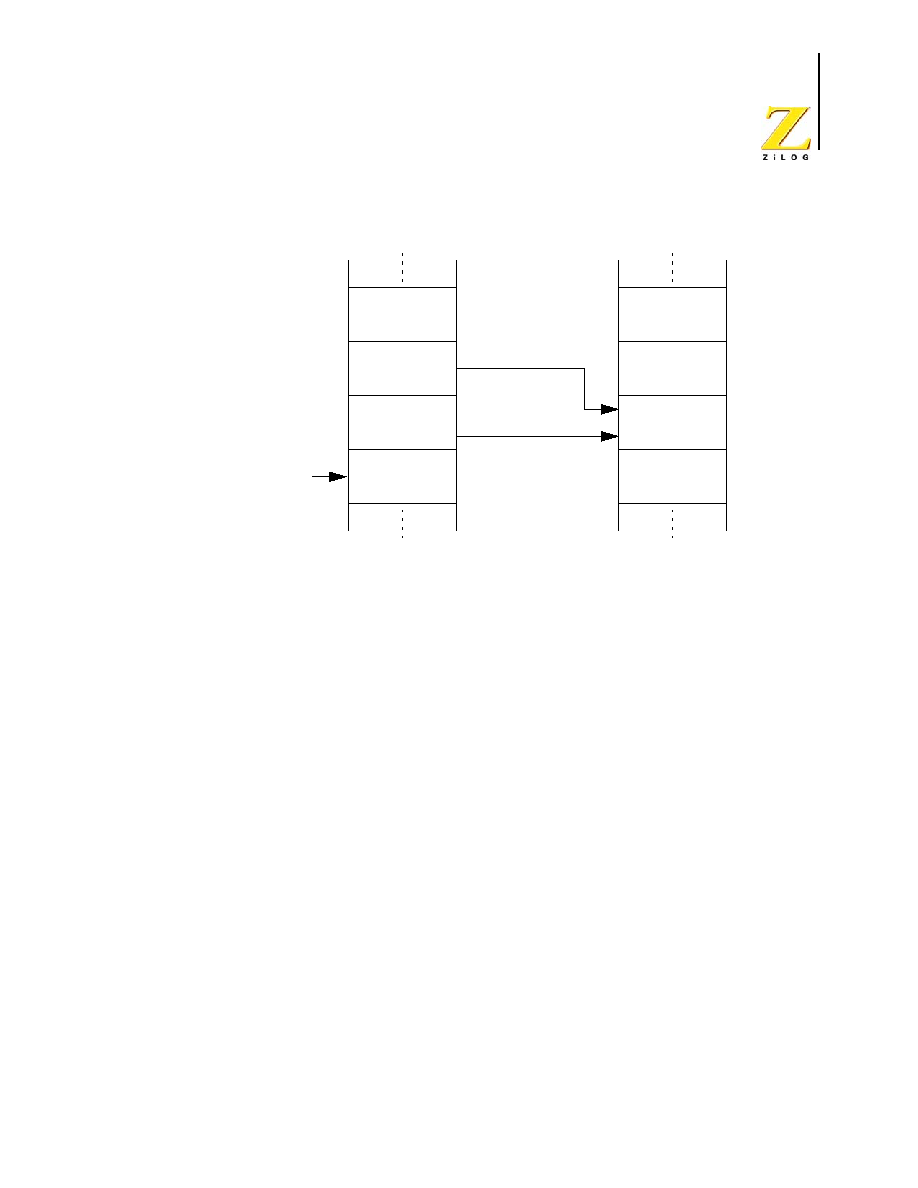

INDEXED ADDRESSING (X)

An Indexed Address consists of an 8-bit address contained in a Working Register offset by

an 8-bit Signed Index value. Figure 13 illustrates Indexed Addressing.

One 8-bit

Program Memory

Address

(dst)

One Operand

Instruction

(Example)

Opcode

dst[7:0]

Destination

Register File

Register MSB

12-bit address is

{RP[3:0], dst[7:0]}

Value used

in execution

Register Pair

contains two

8-bit address

16

-b

it ad

dress is

{a

ddr[15:8

]

, add

r[7:0]}

Program or Data Memory

Destination

Register LSB

{addr[15:8], addr[7:0]}

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

26

Figure 13. Indexed Register Addressing

DIRECT ADDRESSING (DA)

Figure 14 depicts the Direct Addressing mode.This instruction specifies the address of the

next instruction to be executed. Only the Jump (JP and JP cc) and Call (CALL) instruc-

tions use Direct Addressing. The 16-bit Direct Address is written to the Program Counter.

Two 4-bit

Program Memory

Address

(dst, src)

Two Operand

Instruction

(Example)

Opcode

{dst[3:0],

Destination

Register File

Register

12-bit address is

{RP[3:0], RP[7:4], dst[3:0]}

Value used

in execution

8-

bi

t

va

l

u

e

w

r

i

t

t

e

n

to

De

si

t

n

a

t

i

o

n

Re

gi

st

er

src[3:0]}

Index

+

Source

Register

Source

Value

12-bit address is

{RP[3:0], Source Value + Index}

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

27

Figure 14. Direct Addressing

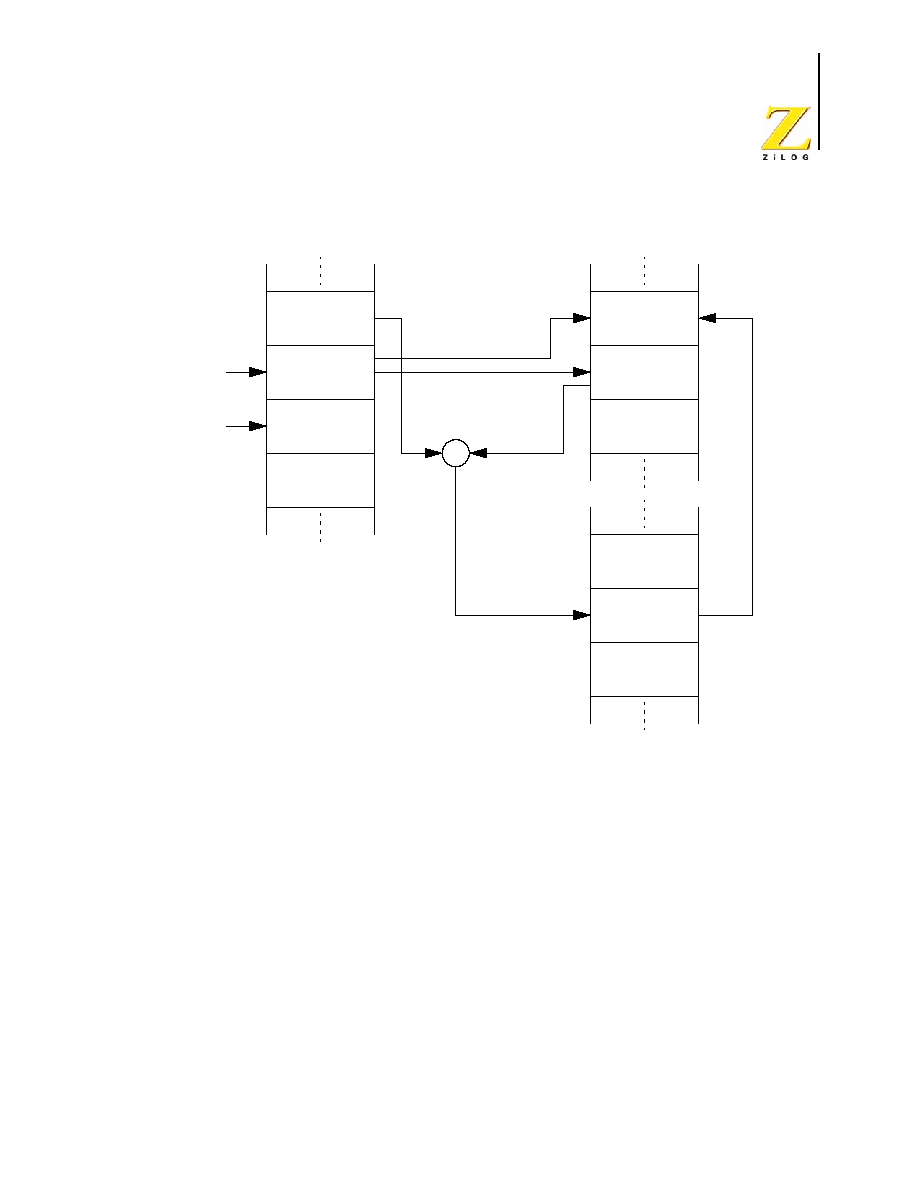

RELATIVE ADDRESSING (RA)

Figure 15 illustrates the Relative Addressing mode. The instruction specifies a two's com-

plement signed displacement in the range of �128 to +127. This instruction, added to the

contents of the Program Counter, obtains the address of the next instruction to be exe-

cuted. Prior to the addition operation, the Program Counter contains the address of the

instruction immediately following the current relative addressing instruction. The JR and

DJNZ instructions are the only instructions that use this mode.

16-bit Direct

Program Memory

Address

Two Operand

Instruction

(Example)

Opcode

DA[15:8]

DA[7:0]

Next

Opcode

16-bit Program

Memory address

is DA[15:0]

DA[15:0] written to

Program Counter

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

28

Figure 15. Relative Addressing

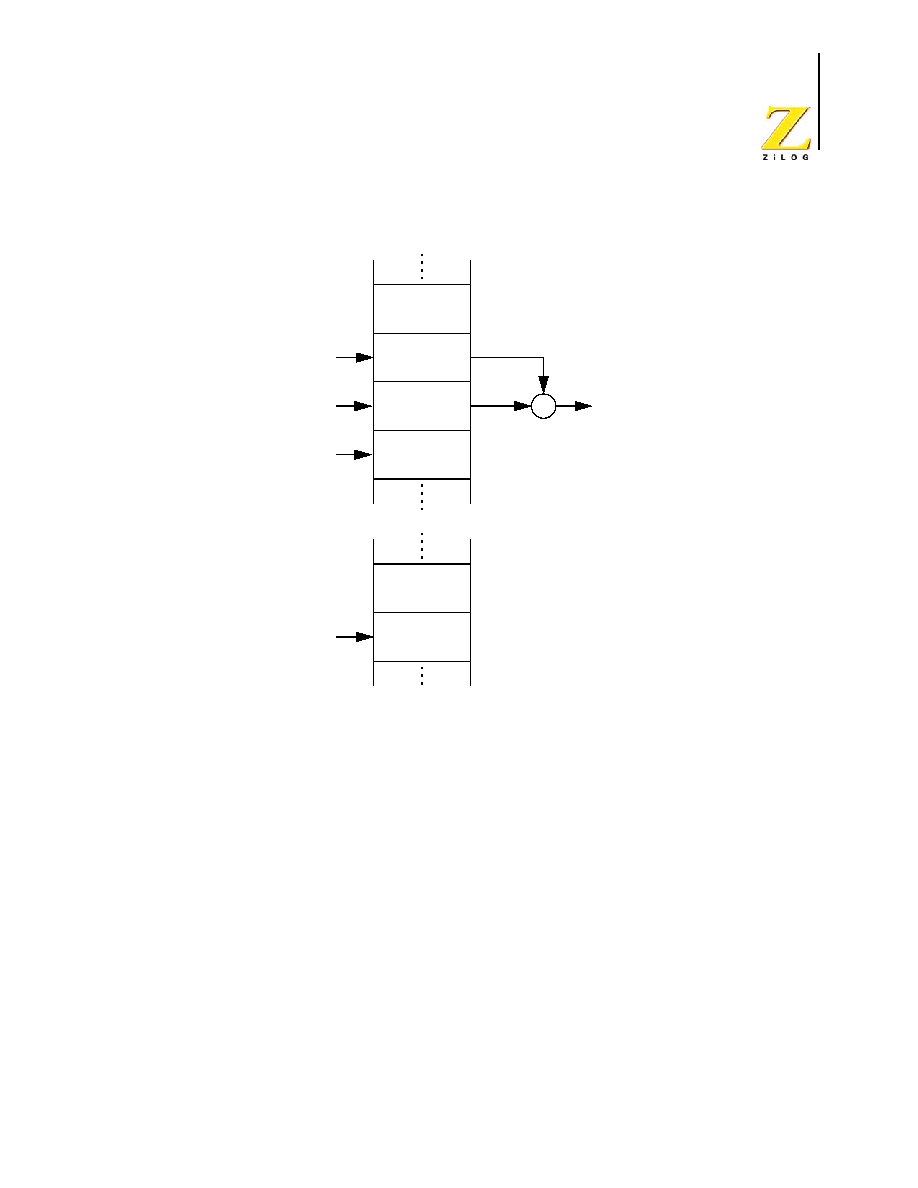

IMMEDIATE DATA ADDRESSING (IM)

Immediate data is considered an "addressing mode" for this discussion. It is the only

addressing mode that does not indicate a register or memory address as the operand. The

operand value used by the instruction is the value supplied in the operand field itself.

Because an immediate operand is part of the instruction, it is always located in the Pro-

gram Memory address space (see Figure 16).

8-bit Value

Program Memory

-128 to +127

One Operand

Instruction

(Example)

Opcode

Displacement

Next Opcode

Next Opcode

if Jump

16-bit Program

Memory address

is PC[15:0] + d[7:0]

if no Jump

+

PC[15:0]

d

If Jump taken,

PC[15:0] = PC[15:0] + d[7:0]

16-bit Program

Memory address

is PC[15:0]

UM012811-0904

Addressing

Modes

eZ8 CPU

User Manual

29

Figure 16. Immediate Data Addressing

Program Memory

Two Operand

Instruction

(Example)

Opcode

dst

Immediate

Data

Register File

12-bit address is

{RP[3:0], dst[7:0]}

Destination

Register

8-bit data written

to Destination

eZ8 CPU

User Manual

UM012811-0904

Interrupts

30

Interrupts

INTRODUCTION

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation and force the

CPU to start an interrupt service routine (ISR). The interrupt service routine exchanges

data, status information, or control information between the CPU and the interrupting

peripheral. When the service routine finishes, the CPU returns to the previous operation.

The eZ8 CPU supports both vectored-and polled-interrupt handling. Interrupts are gener-

ated from internal peripherals, external devices through the port pins, or software. The

Interrupt Controller prioritizes and handles individual interrupt requests before passing

them on to the eZ8 CPU.

The interrupt sources and trigger conditions are device dependent. Refer to the device-spe-

cific Product Specification to determine available interrupt sources (internal and external),

triggering edge options, and exact programming details.

INTERRUPT ENABLE AND DISABLE

Interrupts are globally enabled and disabled by executing the Enable Interrupts (EI) and

Disable Interrupts (DI) instructions, respectively. These instructions affect the global

interrupt enable control bit in the Interrupt Controller. Enable or disable the individual

interrupts using control registers in the Interrupt Controller. Refer to the device-specific

Product Specification for information on the Interrupt Controller.

INTERRUPT PRIORITY

The Interrupt Controller prioritizes all interrupts. Refer to the device-specific Product

Specification for information on the Interrupt Controller.

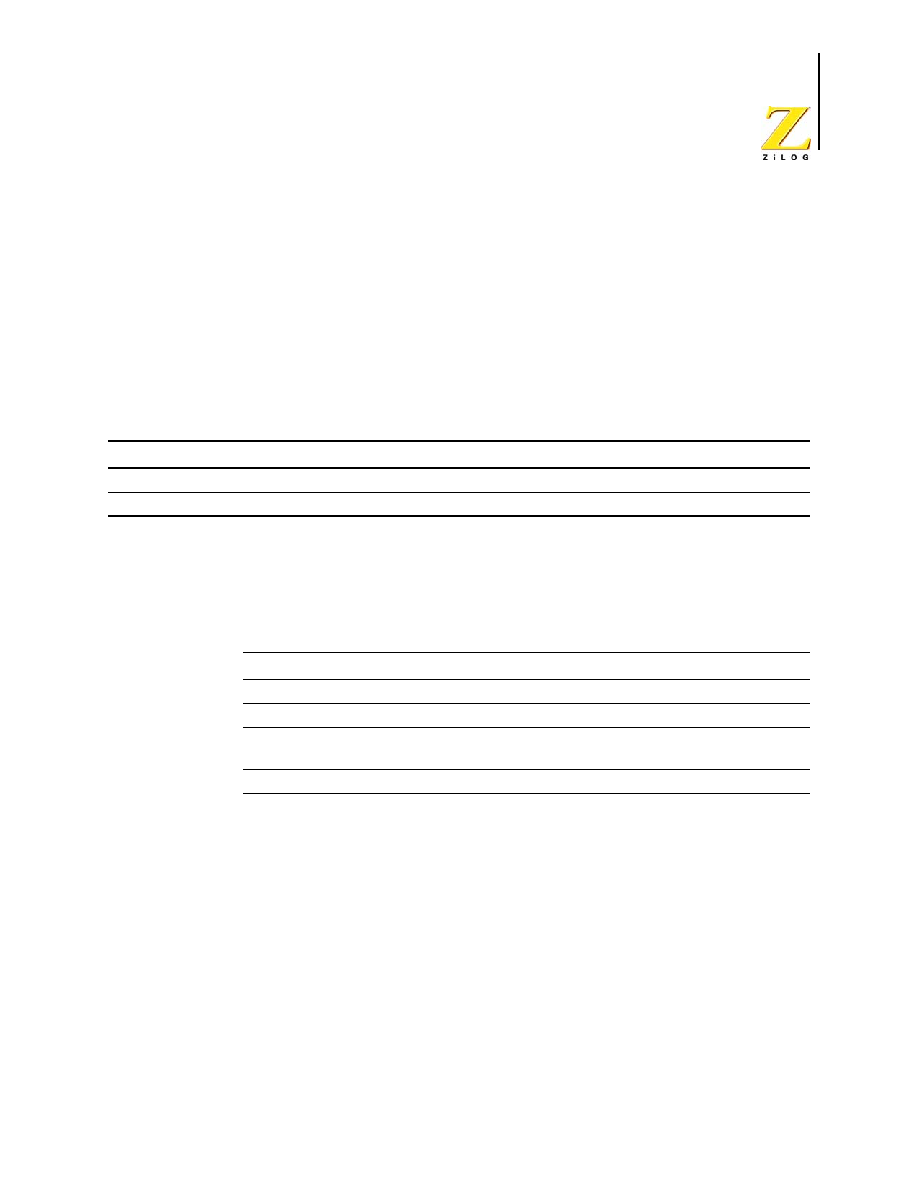

VECTORED INTERRUPT PROCESSING

Each eZ8 CPU interrupt is assigned its own vector. When an interrupt occurs, control

passes to the interrupt service routine pointed to by the interrupt's vector location in Pro-

gram Memory. The sequence of events for a vectored interrupt is as follows:

UM012811-0904

Interrupts

eZ8 CPU

User Manual

31

1. Push the low byte of the Program Counter, PC[7:0], on the stack.

2. Push the high byte of the Program Counter, PC[15:8], on the stack.

3. Push the Flags Register on the stack.

4. Fetch the High Byte of the Interrupt Vector

5. Fetch the Low Byte of the Interrupt Vector

6. Branch to the Interrupt Service Routine specified by the Interrupt Vector

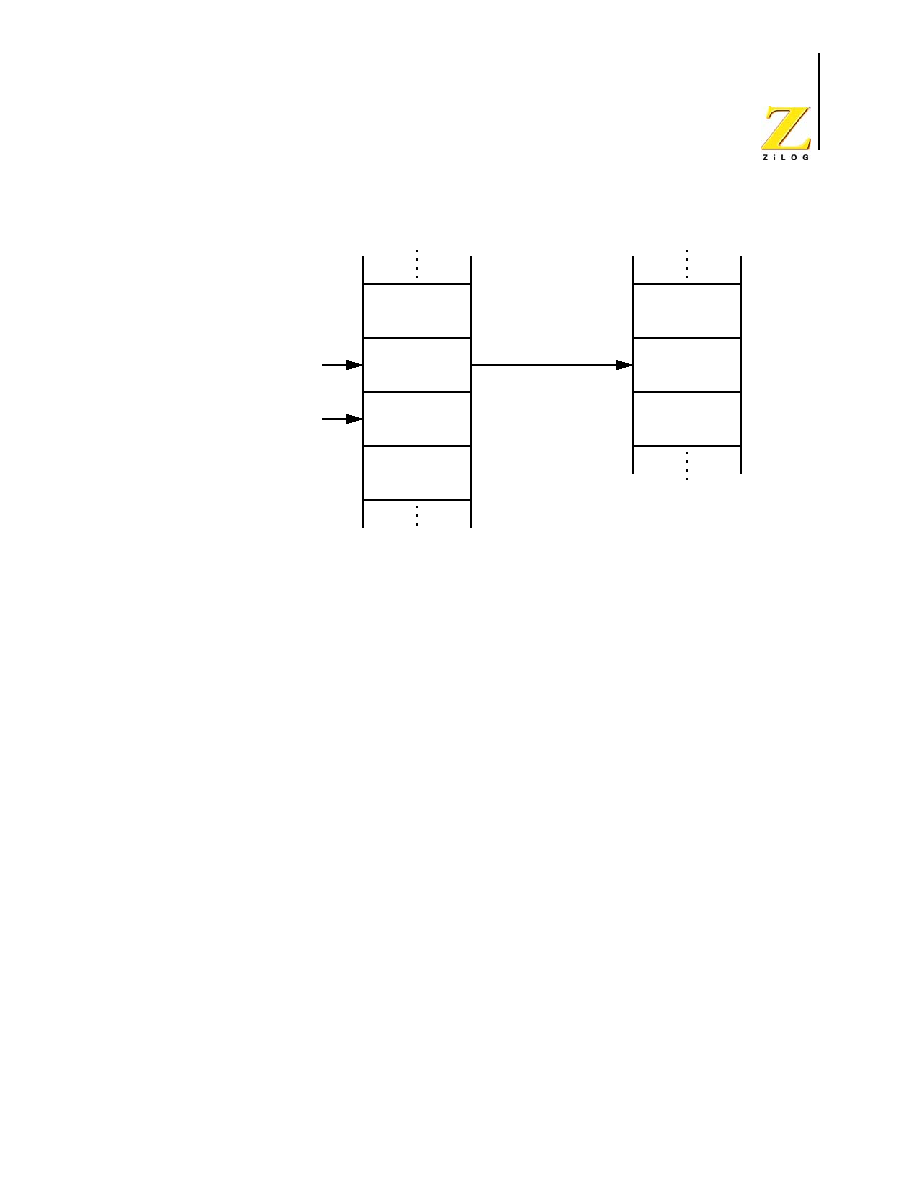

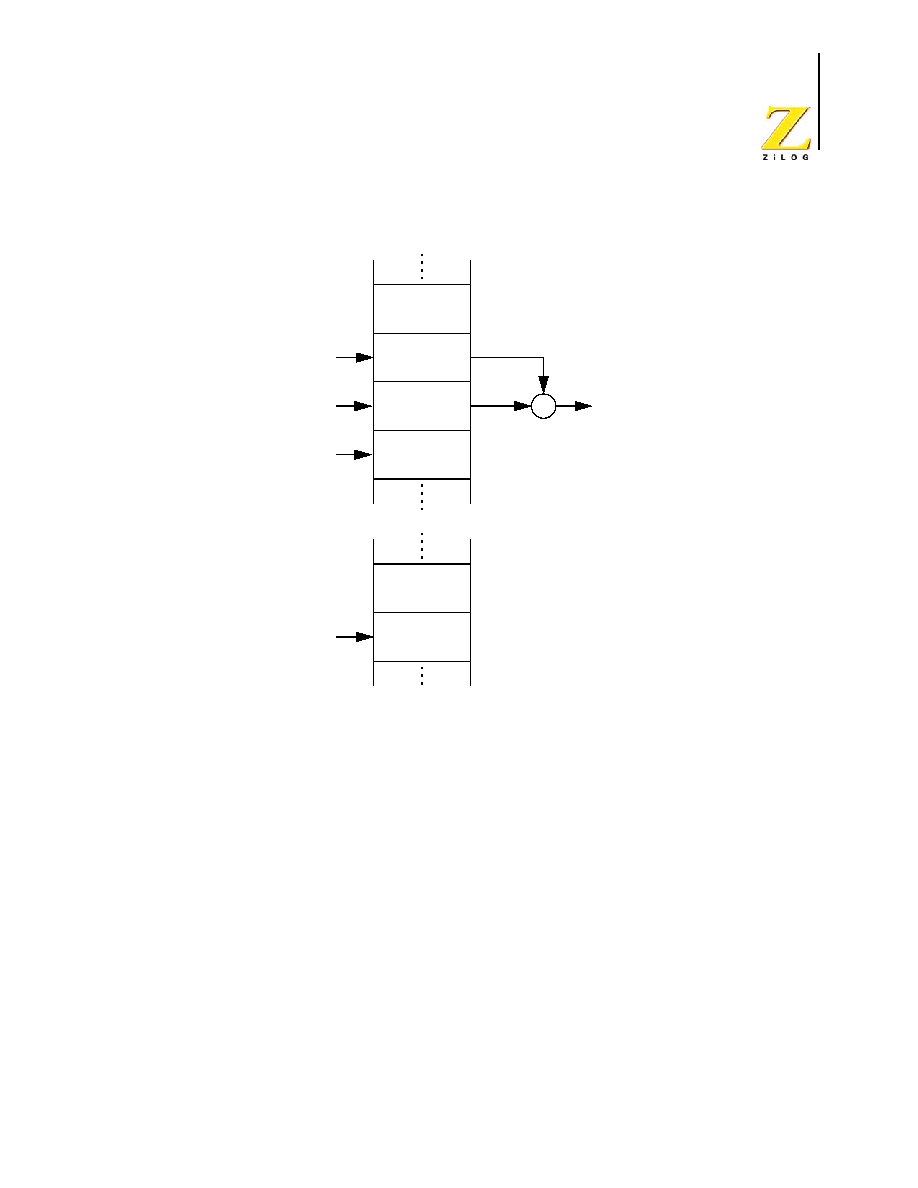

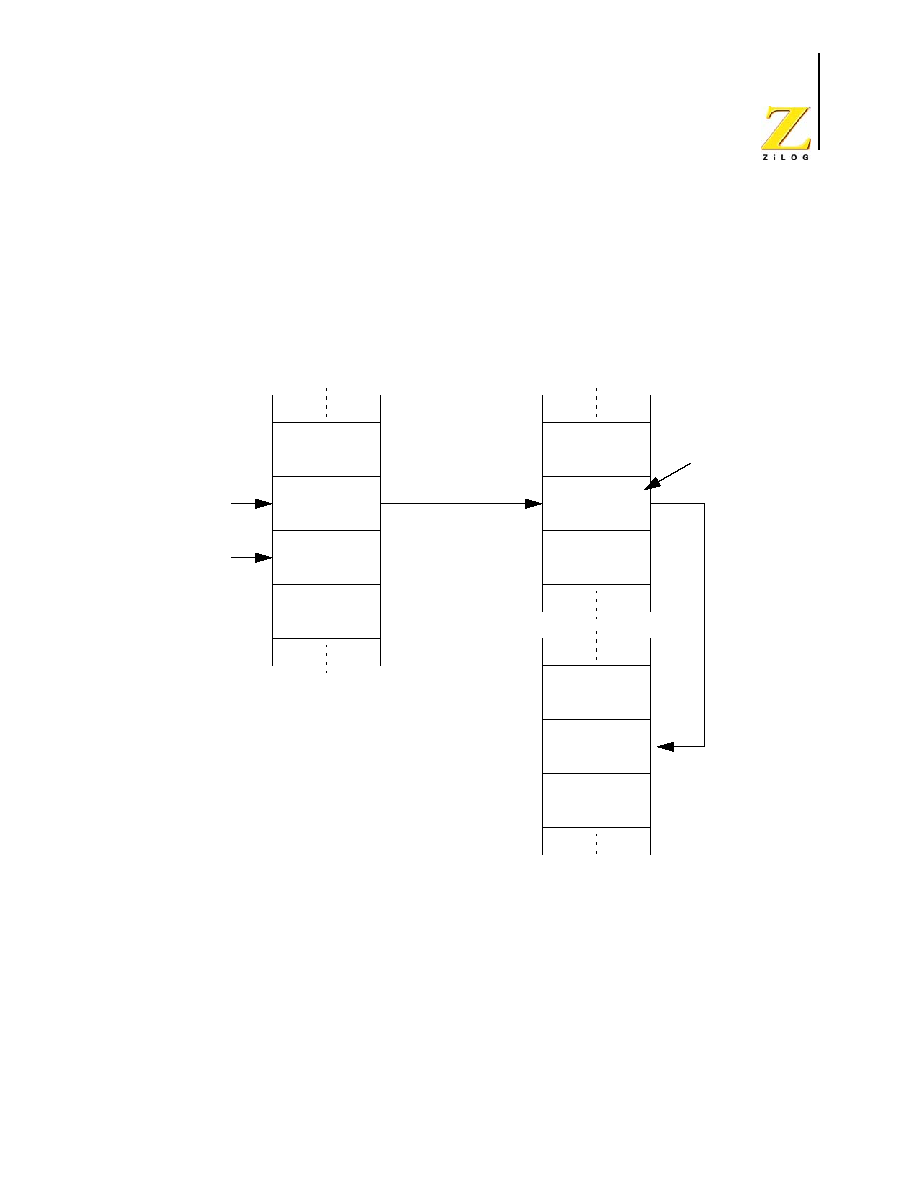

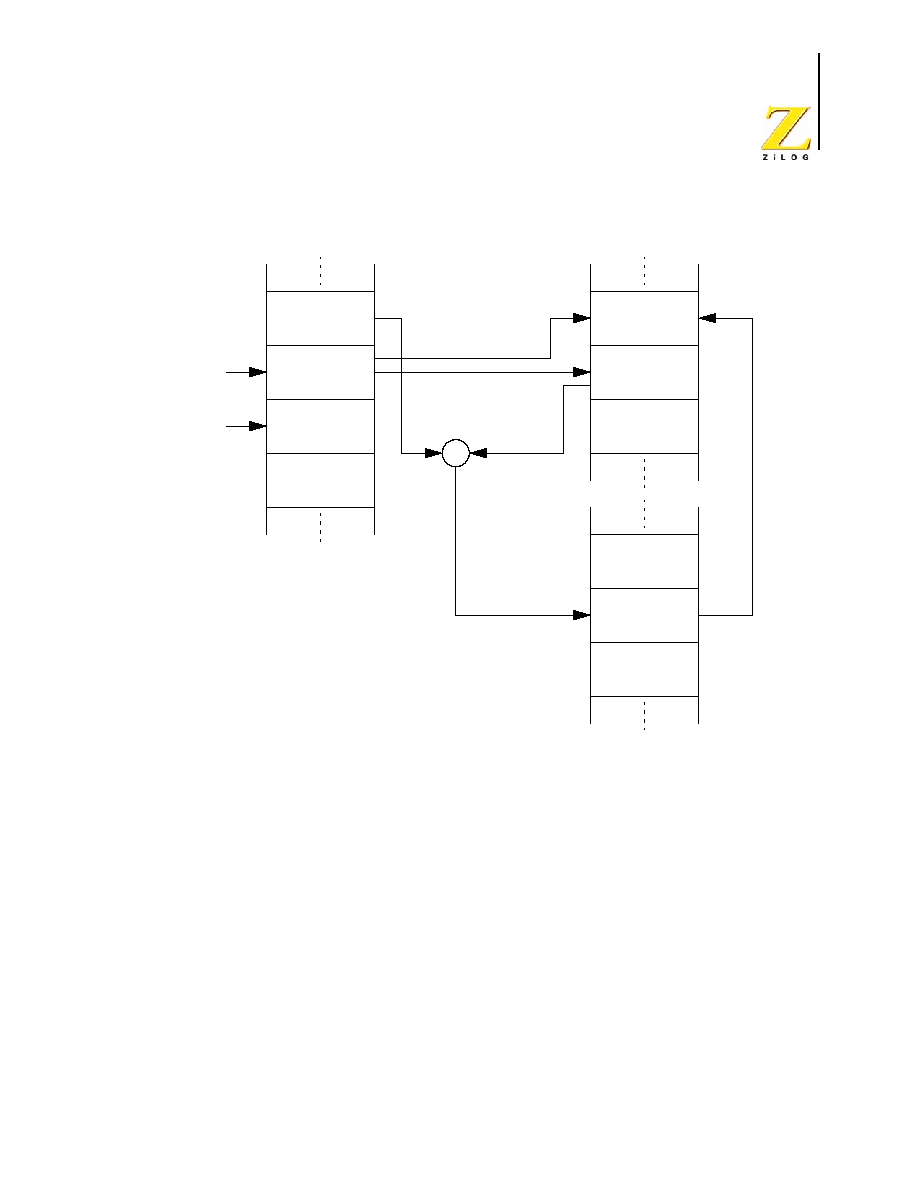

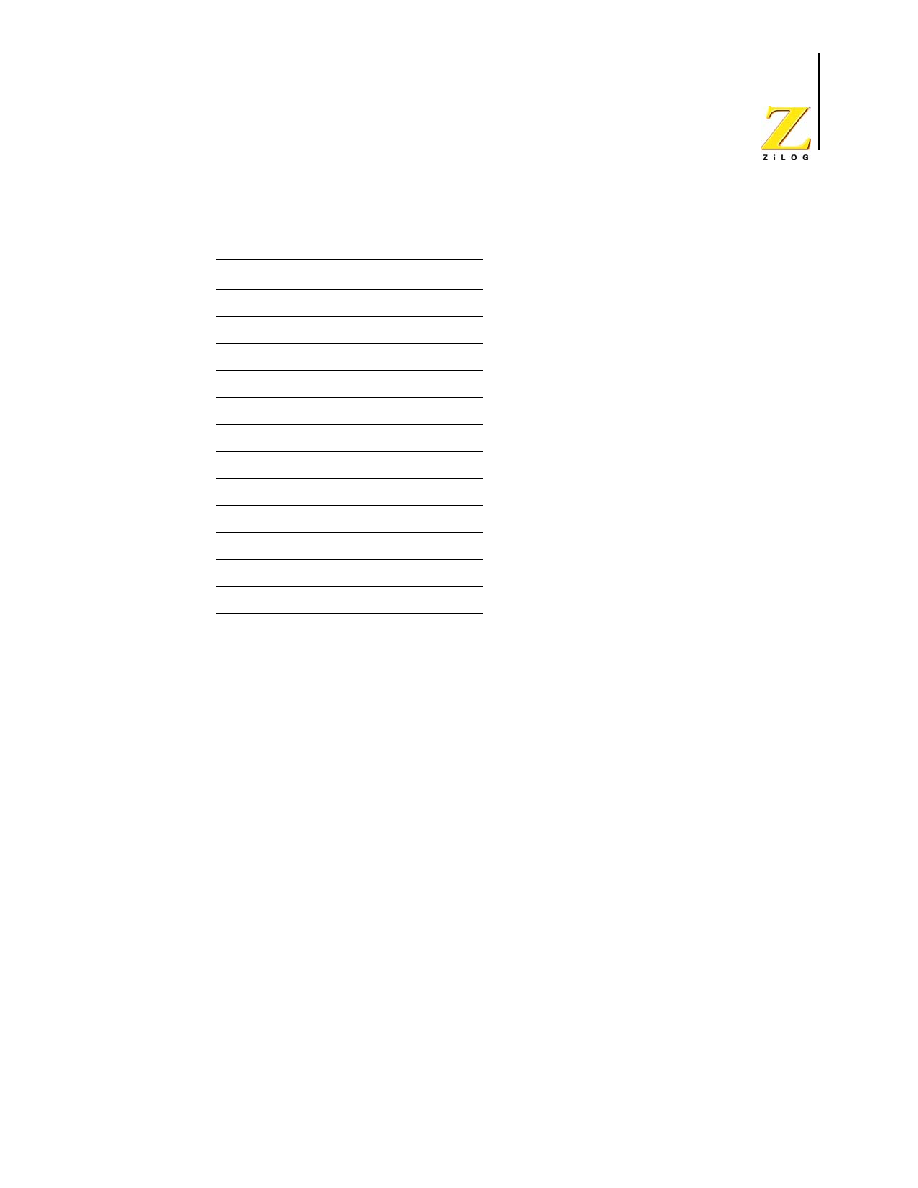

Figure 17 illustrates the effect of vectored interrupts on the Stack Pointer and the contents

of the stack. Figure 18 provides an example of the Program Memory during interrupt oper-

ation. In the example of Figure 18, the Interrupt Vector is located at address

0014H

in Pro-

gram Memory. The 2-byte Interrupt Vector, stored at Program Memory addresses

0014H

and

0015H

, is loaded into the Program Counter. Execution of the Interrupt Service Rou-

tine begins at Program Memory address

4567H

, as is stored in the Interrupt Vector.

Figure 17. Effects of an Interrupt on the Stack

Top of Stack

Stack Pointer

Flags[7:0]

PC[15:8]

PC[7:0]

Stack Pointer

Stack Pointer and Stack

Before an Interrupt

Stack Pointer and Stack

After an Interrupt

UM012811-0904

Interrupts

eZ8 CPU

User Manual

32

Figure 18. Interrupt Vectoring in Program Memory Example

NESTING OF VECTORED INTERRUPTS

Vectored interrupt nesting allows higher priority requests to interrupt a lower priority

request. To initiate vectored interrupt nesting, perform the following steps during the inter-

rupt service routine:

1. Push the old Interrupt Control and Interrupt Enable Register information on the stack.

2. Load the Interrupt Enable Register information with new masks to disable lower

priority interrupts.

3. Execute an EI instruction to enable the interrupts.

4. Proceed with the interrupt service routine processing.

5. After processing is complete, execute a DI instruction to disable the interrupts.

6. Restore the Interrupt Control and Interrupt Enable Register information from the

stack.

7. Execute an IRET instruction to return from the interrupt service routine.

Program Memory

Vector Selected by

Interrupt Controller

Interrupt

Vector

Table

Interrupt Service

Routine Origin

Vector[15:8] = 45H

Vector[7:0] = 67H

4567H

Program Memory

Address

0014H

0015H

UM012811-0904

Interrupts

eZ8 CPU

User Manual

33

POLLED INTERRUPT PROCESSING

Polled interrupt processing is supported by individually disabling the interrupts to be

polled. To initiate polled processing, check the interrupt bits of interest in the Interrupt

Request Register(s) using the Test Under Mask (TM) or similar bit test instruction. If the

bit is 1, perform a software call or branch to the interrupt service routine. Write the service

routine to service the request, reset the Interrupt Request Bit in the Interrupt Request Reg-

ister, and return or branch back to the main program. An example of a polling routine fol-

lows:

TM

IRQ1, #0010000B

; Test for interrupt request in Bit 5 of IRQ1

JR

Z, NEXT

; If no interrupt request, go to NEXT

CALL SERVICE

; If interrupt request, go to the interrupt service

; routine.

NEXT:

Other program code here

SERVICE:

; Process interrupt request

Service routine code here

AND IRQ1, #1101111B

; Clear the interrupt request in Bit 5 of IRQ1

RET

; Return to address following the CALL

Refer to the device-specific Product Specification for information on the Interrupt Request

Registers.

SOFTWARE INTERRUPT GENERATION

The eZ8 CPU generates Software Interrupts by writing to the Interrupt Request Registers

in the Register File. The Interrupt Controller and eZ8 CPU handle these software inter-

rupts in the same manner as hardware-generated interrupt requests. To generate a Software

Interrupt, write a 1 to the desired interrupt request bit in the selected Interrupt Request

Register. As an example, the following instruction

OR IRQ1, #0010000B

writes a 1 to Bit 5 of Interrupt Request Register 1. If this interrupt at Bit 5 is enabled and

there are no higher priority pending interrupt requests, program control transfers to the

interrupt service routine specified by the corresponding Interrupt Vector.

For more information on the Interrupt Controller and Interrupt Request Registers, refer to

the device-specific Product Specification.

eZ8 CPU

User Manual

UM012811-0904

Illegal

Instruction

Traps

34

Illegal Instruction Traps

Description

The instruction set of the eZ8 CPU does not cover all possible sequences of binary values.

Binary values and sequences for which no operation is defined are illegal instructions.

When the eZ8 CPU fetches one of these illegal instructions, it performs an Illegal Instruc-

tion Trap operation.

The Illegal Instruction Trap functions similarly to a TRAP #%3 instruction (object code

F2H

03H

). The Flags and Program Counter are pushed on the stack. When the Program

Counter detects an illegal instruction it does not increment. The Program Counter value

that is pushed onto the stack points to the illegal instruction.

The most significant byte (MSB) of the Illegal Instruction Trap Vector is stored at Pro-

gram Memory address

0006H

. The least significant byte (LSB) of the Illegal Instruction

Trap Vector is stored at Program Memory address

0007H

. The 16-bit Illegal Instruction

Trap Vector replaces the value in the Program Counter (PC). Program execution resumes

from the new value in the Program Counter.

An IRET instruction must not be performed following an Illegal Instruction Trap

service routine. Because the stack contains the Program Counter value of the il-

legal instruction, the IRET instruction returns the code execution to this illegal

instruction.

Symbolic Operation of an Illegal Instruction Trap

SP

SP - 2

@SP

PC

SP

SP - 1

@SP

Flags

PC

Vector

Linear Programs that do not Employ the Stack

The Stack Pointer must point to a section of the Register File that does not overwrite user

program data. Even for linear program code that may not employ the stack for Call and/or

Interrupt routines, set the Stack Pointer to prepare for possible Illegal Instruction Traps.

Caution:

eZ8 CPU

User Manual

UM012811-0904

eZ8 CPU Instruction Set Summary

35

eZ8 CPU Instruction Set Summary

ASSEMBLY LANGUAGE PROGRAMMING INTRODUCTION

The eZ8 CPU assembly language enables writing to an application program without con-

cern about actual memory addresses or machine instruction formats. A program written in

assembly language is called a source program. Assembly language uses symbolic

addresses to identify memory locations. It also allows mnemonic codes (opcodes and

operands) to represent the instructions themselves. The opcodes identify the instruction

while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands, called state-

ments. Each statement contains labels, operations, operands and comments.

Labels are assigned to a particular instruction step in a source program. The label identi-

fies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine

instruction. The assembler directives, or pseudo-ops, are not translated into a machine

instruction. The pseudo-ops are interpreted as directives that control or assist the assembly

process.

The assembler processes the source program to obtain a machine language program called

the object code. The eZ8 CPU executes the object code. An example segment of an assem-

bly language program is detailed in the following example.

Assembly Language Source Program Example

JP START

; Everything after the semicolon is a comment.

START:

; A label called "START". The first instruction (

JP START

) in this

; example causes program execution to jump to the point within the

; program where the

START

label occurs.

LD R4, R7