December 12, 1997

Maintenance only UD61256

1

Features

F

Dynamic random access memory

262144 x 1 bit manufactured

using a CMOS technology

F

RAS access times 70 ns, 80 ns

F

TTL-compatible

F

Three-state output

F

256 refresh cycles

4 ms refresh cycle time

F

FAST PAGE MODE

F

Operating modes: Read, Write,

Read - Write,

RAS only Refresh,

Hidden Refresh with address

transfer

F

Power Supply Voltage 5 V

F

Packages

PDIP16 (300 mil)

SOJ20/26 (300 mil)

F

Operating temperature range

0 to 70 �C

F

Quality assessment according to

CECC 90000, CECC 90100 and

CECC 90112

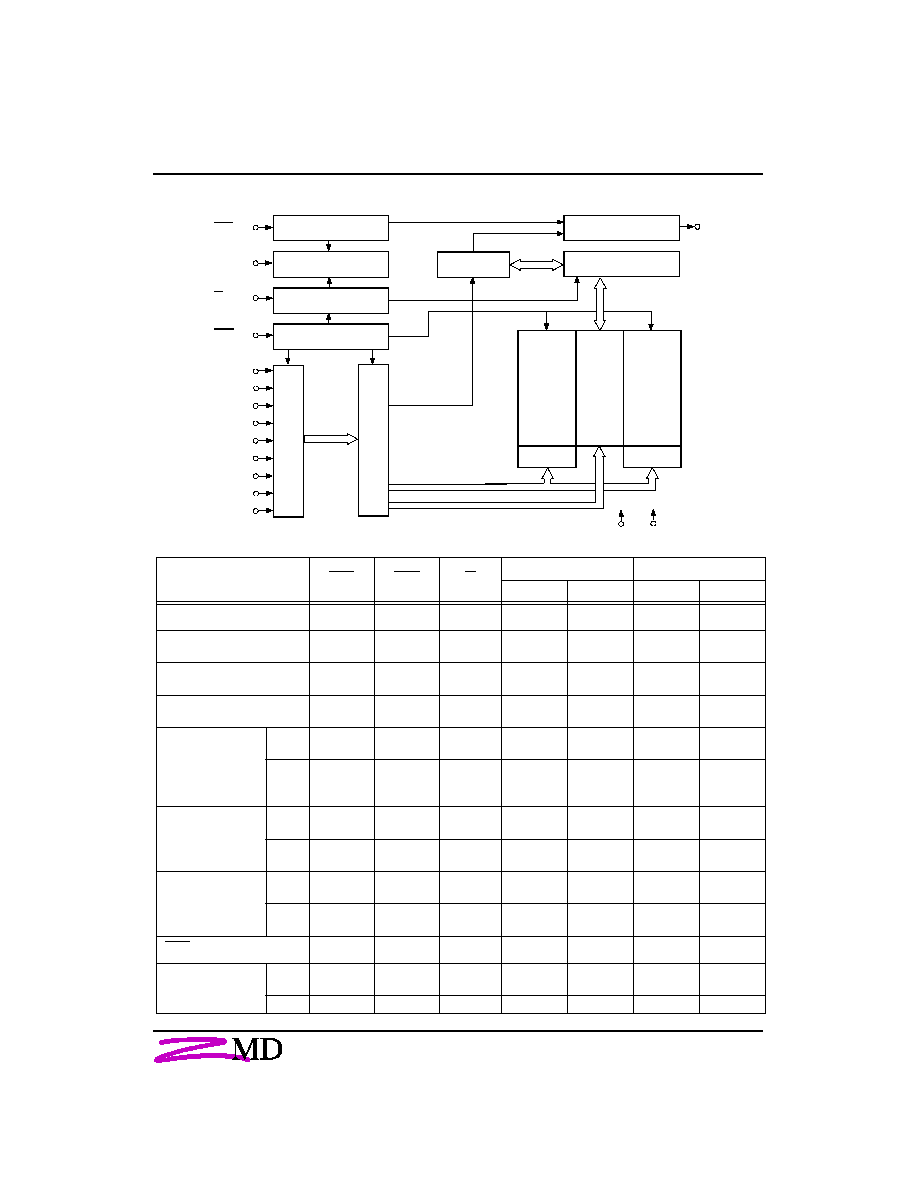

Description

Addressing

The UD61256 is a dynamic Write-

Read-memory with random access.

FPM facilitates faster data operation

with predefined row address. Via 9

address inputs the 18 address bits

are transmitted into the internal

address memories in a time-multi-

plex operation. The falling RAS-

edge takes over the row address.

During RAS Low, the column

address together with the CAS

signal are taken over. The selection

of one or more memory circuits can

be made by activation of the RAS

input.

Read-Write-Control

The choice between Read or Write

cycle is made at the W input. HIGH

at the W input causes a Read cycle,

meanwhile LO W leads to a Write

cycle.

Both CAS-controlled and W-control-

led Write cycles are possible with

activated RAS signal.

Data Output Control

The usual state of the data output is

the High-Z state. Whenever CAS is

inactive (HIGH), Q will float (High-Z).

Thus, CAS functions as data output

control.

After access time, in case of a Read

cycle, the output is activated, and it

contains the logic ,,0" or ,,1".

Q is then valid until CAS returns into

to inactive state (HIGH).

The memory cycle being a Read,

Read-Write or a Write cycle (W-con-

trolled), Q changes from High-Z

state to the active state (,,0" or ,,1").

After the access time the contents of

the selected cell is available, except

for the Write cycle.

The output remains active until CAS

becomes inactive, irrespective of

RAS becoming inactive or not. The

memory cycle being a Write cycle

(CAS-controlled), the data output

keeps its High-Z state throughout

the whole cycle. This configuration

makes Q fully controllable by the

user merely through the timing of W.

The output storaging the data, they

remain valid from the end of access

time until the start of another cycle.

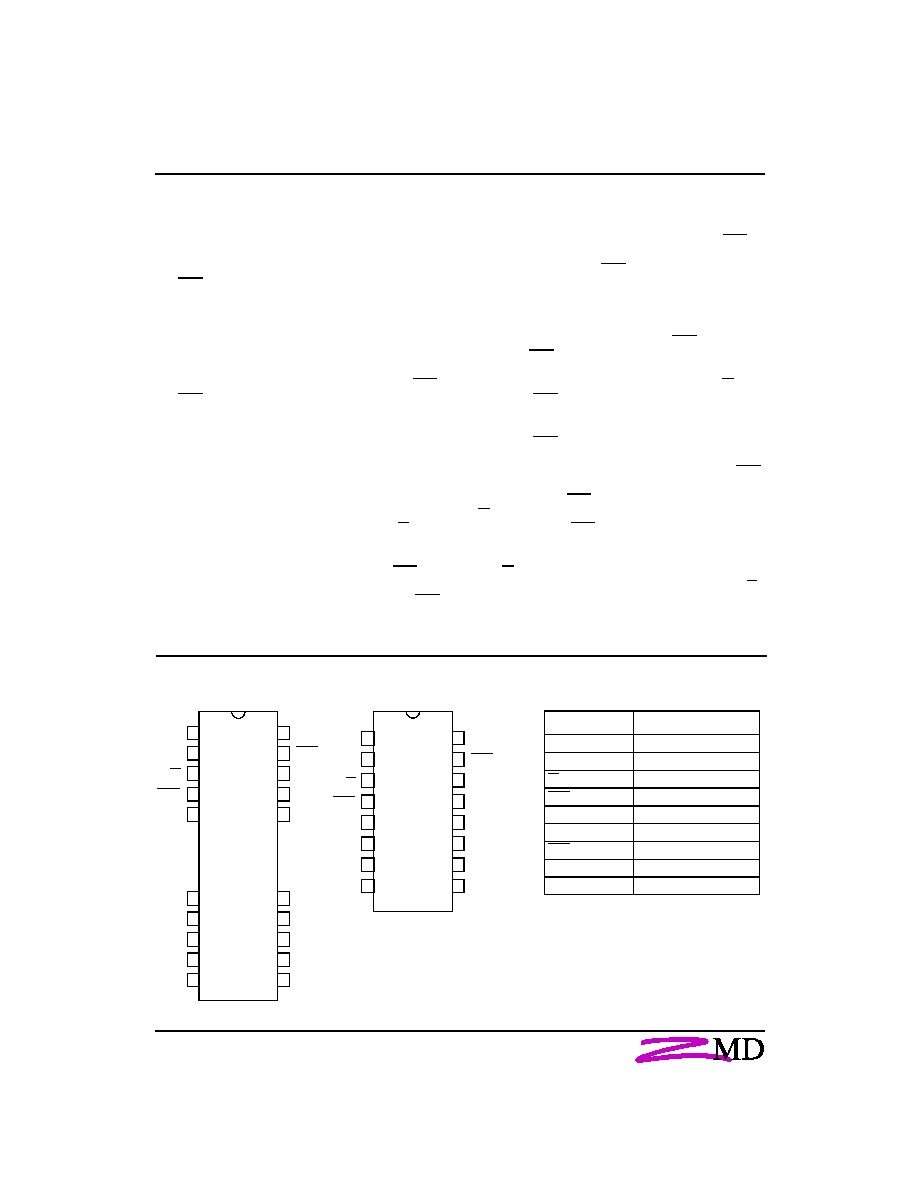

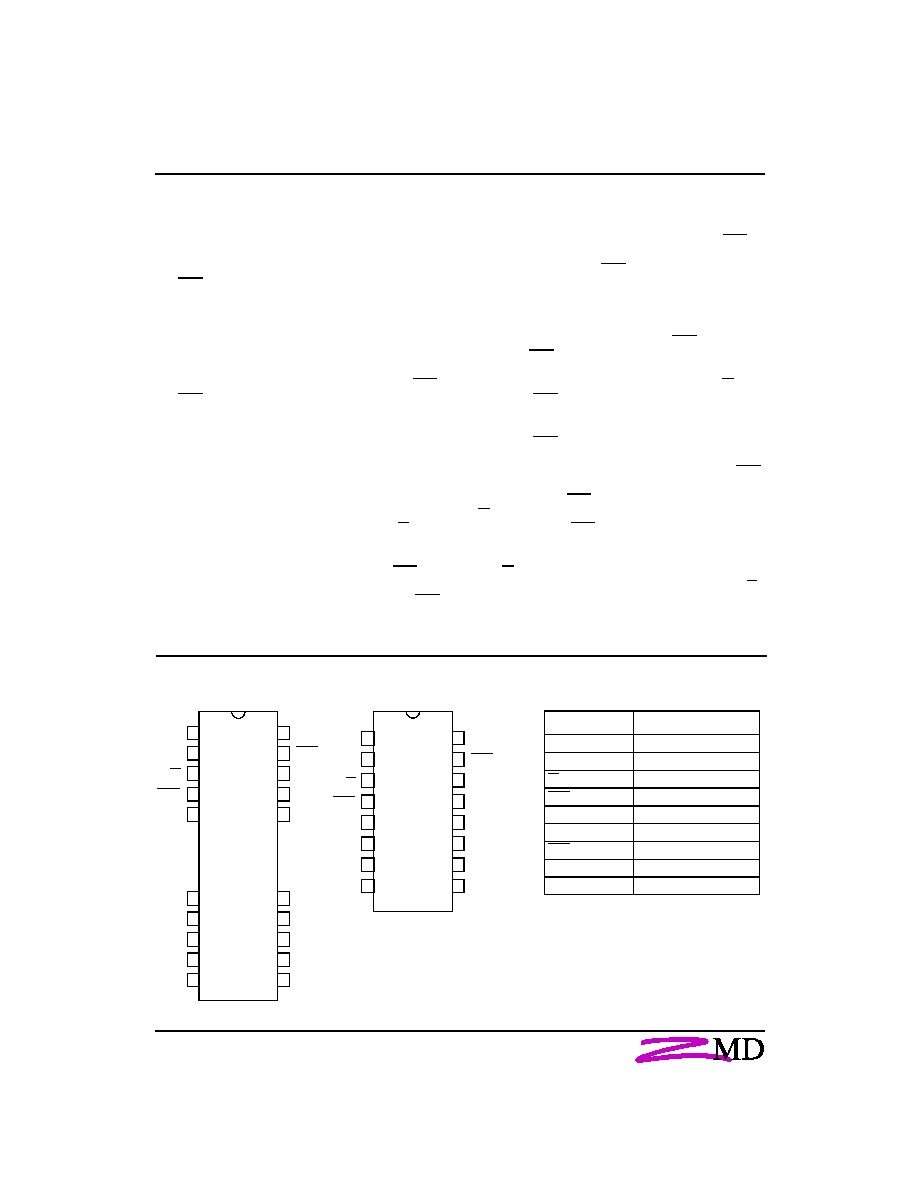

Pin Configuration

1

A8

VSS

16

2

D

CAS

15

4

RAS

A6

13

5

A0

A3

12

3

Q

14

6

A2

A4

11

7

A1

A5

10

8

VCC

A7

9

W

1

A8

V

26

2

D

CAS

25

4

RAS

A6

23

10

A0

A3

17

3

Q

24

11

A2

A4

16

12

A1

A5

15

13

VCC

A7

14

W

5

n.c.

n.c.

22

9

n.c.

n.c.

18

Pin Description

Signal Name Signal Description

A0 - A8 Address Inputs

D Data Input

W

Read, Write Control

RAS

Row Address Strobe

UCC Power Supply Voltage

USS Ground

CAS

Column Address Strobe

Q Data Output

n.c. no connected

Top View

Top View

256K x 1 DRAM

SOJ

PDIP

December 12, 1997

UD61256

3

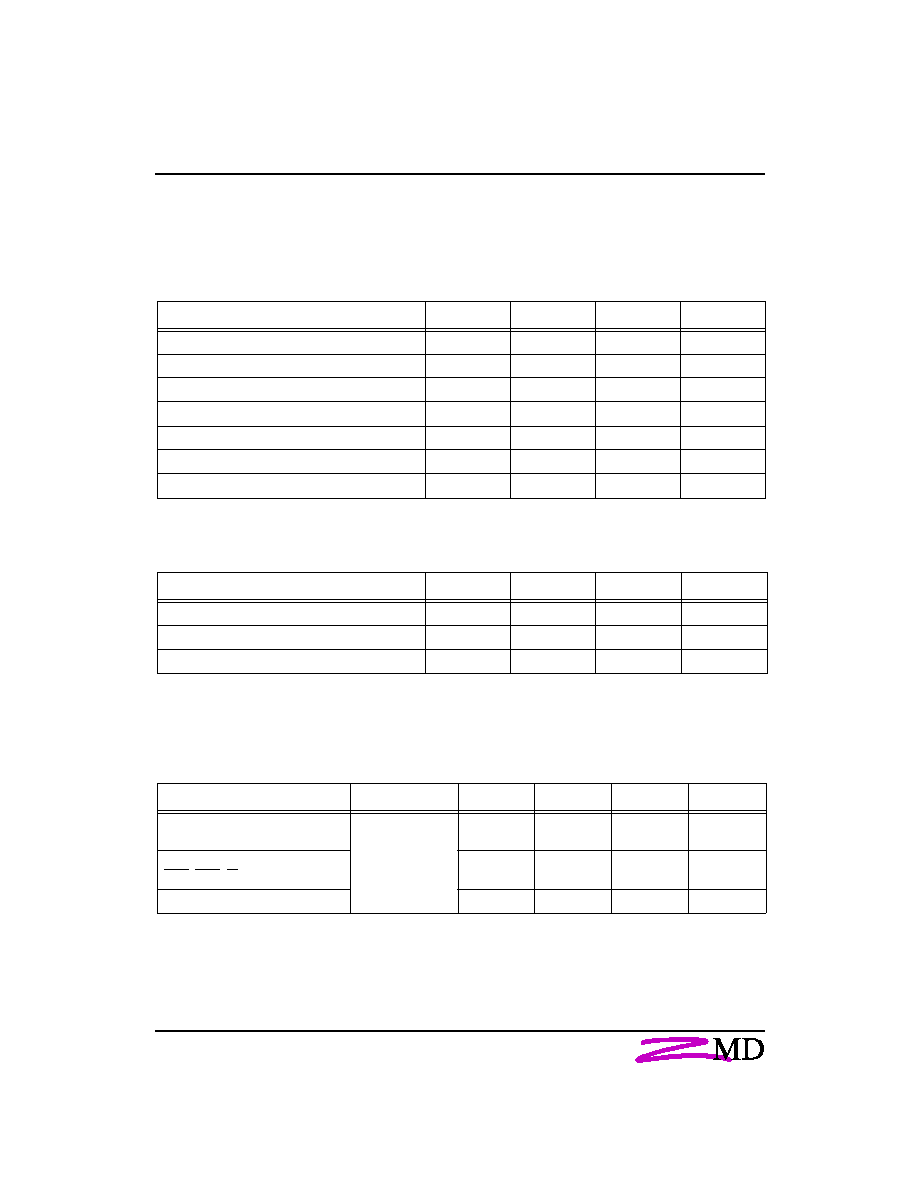

Characteristics

All voltages are referenced to V

SS

= 0 V (ground).

All characteristics are valid in the power supply voltage range and operating temperature range indicated below.

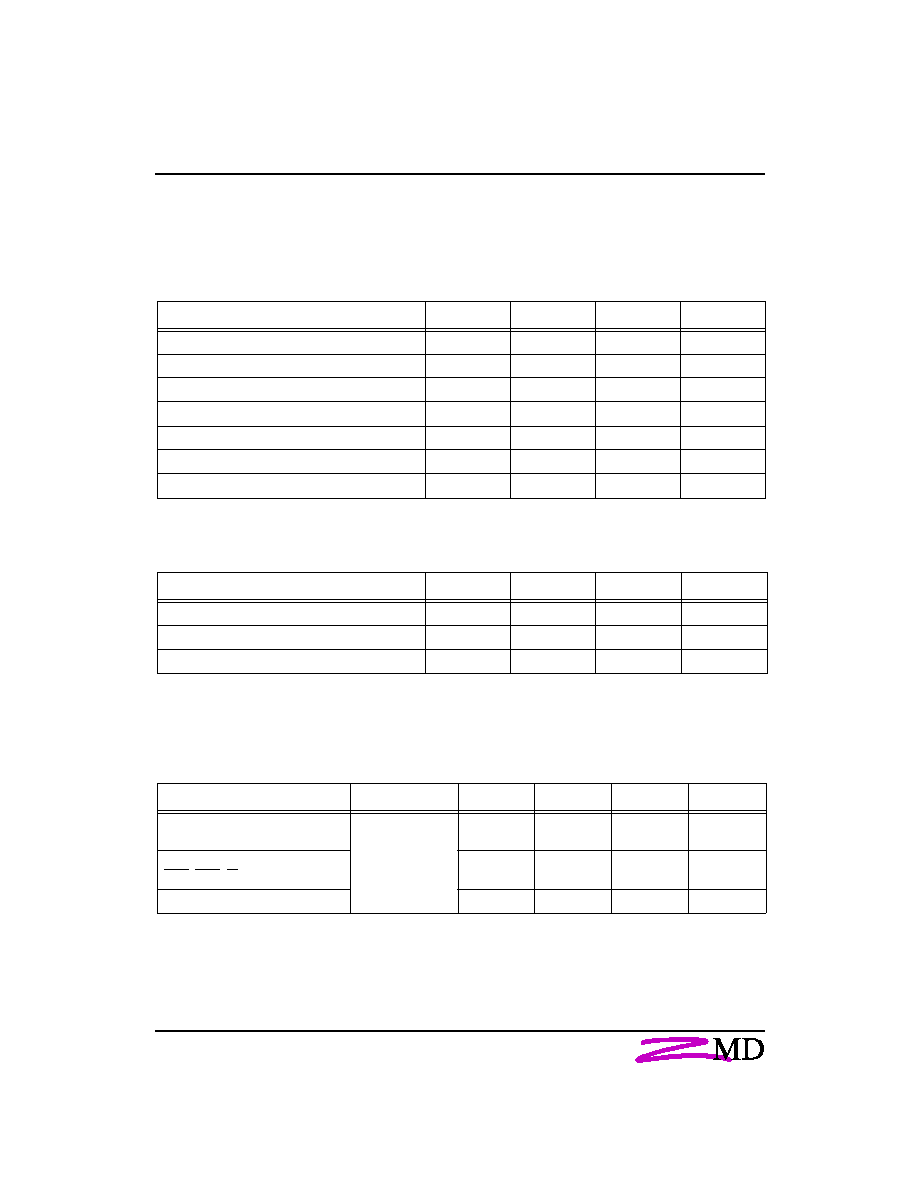

Absolute Maximum Ratings

Symbol

Min.

Max.

Unit

Power Supply Voltage

V

CC

-0.5

7.0

V

Input Voltage

1)

V

I

-1.0

7.0

V

Output Voltage

1)

V

O

-1.0

7.0

V

Output Current

I

O

-50

50

mA

Power Dissipation

P

D

1

W

Operating Temperature

T

a

0

70

�

C

Storage Temperature

T

stg

-55

125

�

C

Remarks: see page 7

Recommended Operating Conditions

Symbol

Min.

Max.

Unit

Power Supply Voltage

V

CC

4.5

5.5

V

Input Low Voltage

1)

V

IL

-1.0

0.8

V

Input High Voltage

V

IH

2.4

5.5

V

Remark: see page 7

Capacitances

Conditions

Symbol

Min.

Max.

Unit

Input Capacitance

A0 to A8, D

V

CC

= 5.0 V

V

I

=

V

SS

f

= 1 MHz

T

a

=

25

�

C

C

I1

6

pF

Input Capacitance

RAS, CAS, W

C

I2

7

pF

Output Capacitance

C

O

7

pF

All pins not under test must be connected with ground by capacitors.

December 12, 1997

UD61256

4

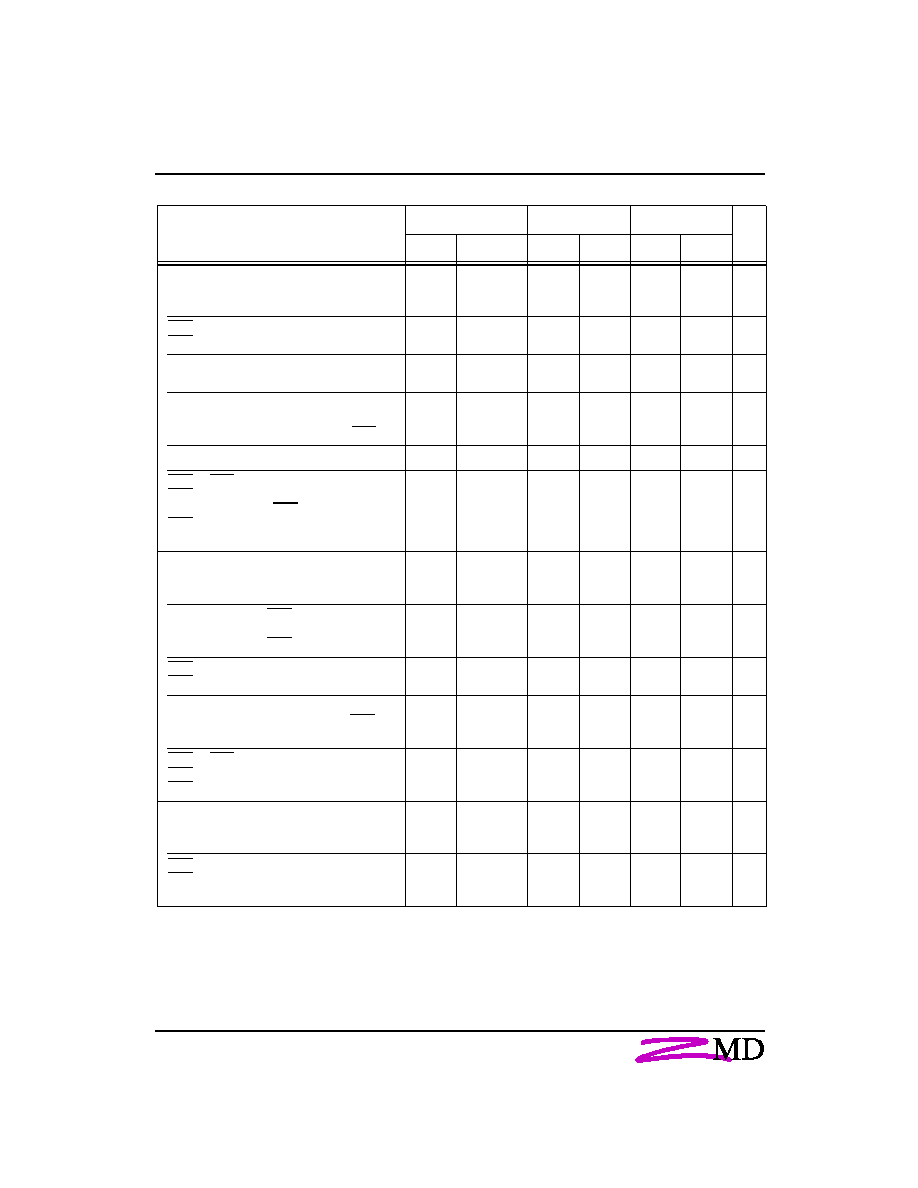

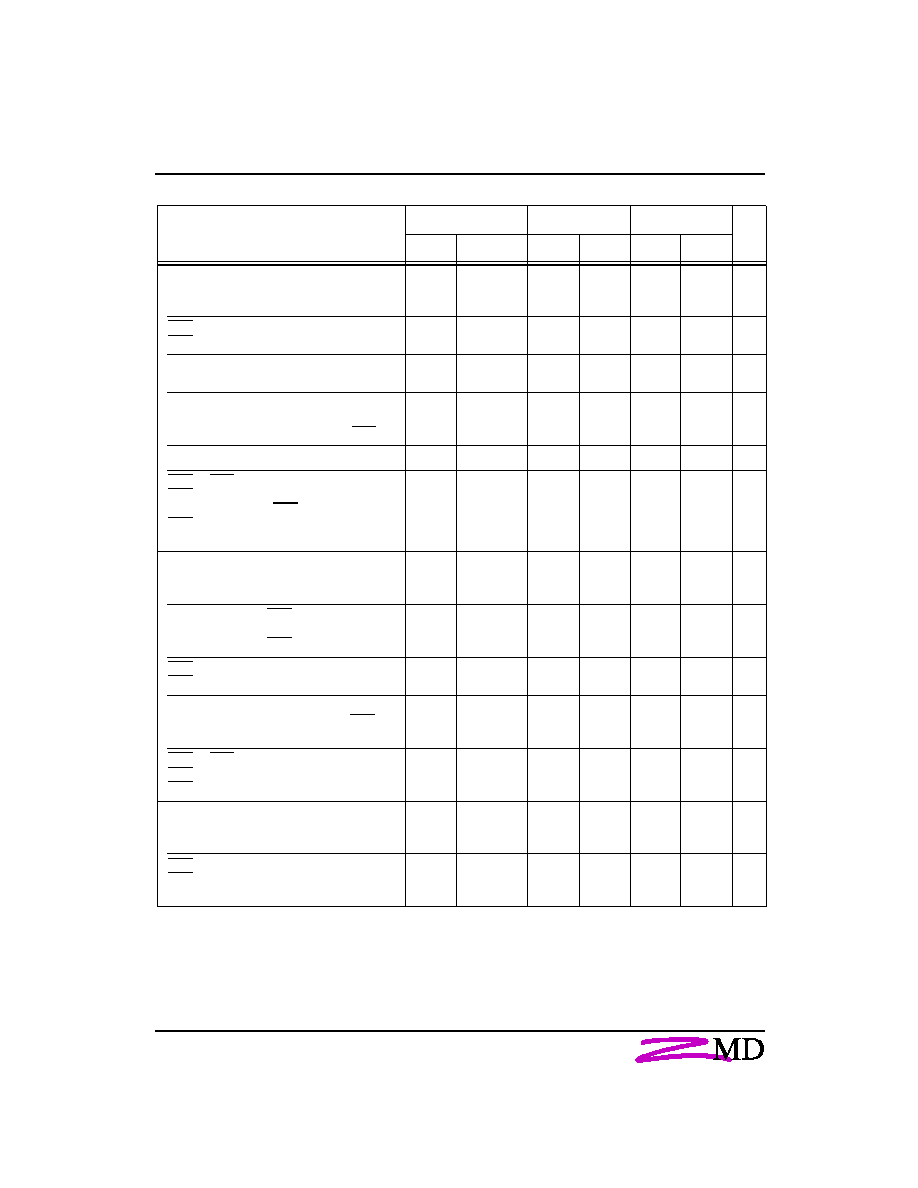

Static Characteristics

Conditions

Symbol

Min.

Max.

Unit

07

08

07

08

Power Supply Current

(average value of RAS-CAS cycles)

2)

t

cW

= t

cWmin

t

cR

= t

cRmin

I

CC1

70

60

mA

Refresh Current

(average value of RAS cycles)

2)

t

cW

= t

cWmin

t

cR

= t

cRmin

CAS = V

IH

I

CC2

70

60

mA

FPM Current

(average value of FPM cycles)

2)

t

cPG

= t

cPGmin

RAS = V

IL

I

CC3

50

40

mA

Stand-by Current (TTL Level)

RAS = CAS

= V

IH

I

CC4

2

2

mA

Stand-by Current (CMOS Level)

RAS = CAS

= V

CC

- 0.2 V

I

CC5

1

1

mA

Output High Voltage

I

OH

= -5 mA

V

OH

2.4

2.4

V

Output Low Voltage

I

OL

= 4.2 mA

V

OL

0.4

0.4

V

Input Leakage Current

at any input,

all other pins = 0 V

V

I

= 0 V to

5.5 V

I

I

-10

-10

10

10

�

A

Output Leakage Current

Q = High-Z

V

O

= 0 V to

5.5 V

RAS = CAS

= V

IH

I

O

-10

-10

10

10

�

A

Remarks: see page 7

December 12, 1997

UD61256

5

Dynamic Characteristics

3)

Symbol

Min.

Max.

Unit

Alt.

IEC

07

08

07

08

F

ALL CYCLES

Transition Time (Rise and Fall)

4)

t

T

t

t

3

3

50

50

ns

RAS Precharge Time

CAS Precharge Time

t

RP

t

CP

t

w(RASH)

t

w(CASH)

50

10

60

10

ns

ns

Row Address Set-up Time

Column Address Set-up Time

t

ASR

t

ASC

t

su(RA-RAS)

t

su(CA-CAS)

0

0

0

0

ns

ns

Row Address Hold Time

Column Address Hold Time

Column Address Hold Time ref. to RAS

t

RAH

t

CAH

t

AR

t

h(RAS-RA)

t

h(CAS-CA)

t

h(RAS-CA)

10

15

55

10

15

60

ns

ns

ns

Output Buffer Turn-off Delay

5)

t

OFF

t

v(CAS)

0

0

20

20

ns

CAS to RAS Precharge Time

RAS to Column Address Delay Time

Column Address to RAS Lead Time

CAS to Output in Low-Z

Refresh Period

6)

t

CRP

t

RAD

t

RAL

t

CLZ

t

REF

t

CASH-RASL

t

RAS-CA

t

CA-RASH

t

CASL-QX

t

rf

5

15

35

0

5

15

40

0

35

4

40

4

ns

ns

ns

ns

ms

F

READ

Random Read Cycle Time

12)

t

RC

t

cR

130

150

ns

Access Time from RAS

Access Time from Column Address

Access Time from CAS

8)

8)

8)

t

RAC

t

AA

t

CAC

t

a(RAS)

t

a(CA)

t

a(CAS)

70

35

20

80

40

20

ns

ns

ns

RAS Pulse Width

CAS Pulse Width

t

RAS

t

CAS

t

w(RASL)

t

w(CASL)

70

20

80

20

10000

10000

10000

10000

ns

ns

Read Command Set-up Time

Read Command Hold Time ref. to RAS

Read Command Hold Time

9)

9)

t

RCS

t

RRH

t

RCH

t

su(R-CAS)

t

h(RAS-R)

t

h(CAS-R)

0

0

0

0

0

0

ns

ns

ns

RAS to CAS Delay Time

CAS Hold Time

RAS Hold Time

6)

t

RCD

t

CSH

t

RSH

t

RASL-CASL

t

RASL-CASH

t

CASL-RASH

20

70

20

20

80

20

50

60

ns

ns

ns

F

WRITE

Random Write Cycle Time

12)

t

RC

t

cW

130

150

ns

RAS Pulse Width

CAS Pulse Width

Write Command Pulse Width

t

RAS

t

CAS

t

WP

t

w(RASL)

t

w(CASL)

t

w(W)

70

20

15

80

20

15

10000

10000

10000

10000

ns

ns

ns

Remarks: see page 7

7),

7),

7),