1

November 07, 2003

UL62H1616B

Preliminary

!

65536 x 16 bit static CMOS RAM

!

15, 20 and 35 ns Access Time

!

Common data inputs and

data outputs

!

Three-state outputs

!

Standby current < 100 µA

at 125∞C

!

Power supply voltage 2.5 V

!

Operating temperature range

K-Type:-40 ∞C to 85 ∞C

A-Type:-40 ∞C to 125 ∞C

!

QS 9000 Quality Standard

!

ESD protection > 2000 V

(MIL STD 883C M3015.7)

!

Latch-up immunity >100 mA

!

Package: TSOP II 44 (400 mil)

The UL62H1616B is a static RAM

manufactured using a CMOS pro-

cess technology with the following

operating modes:

- Lower / Upper Byte Read

- Word Read

- Lower / Upper Byte Write

- Word Write

- Standby

- Data Retention

The memory array is based on a

6-Transistor cell.

The circuit is activated by the fal-

ling edge of E. The address and

control inputs open simultaneously.

According to the information of W

and G, the data inputs, or outputs,

are active. During the active state

E = L and W = H each address

change leads to a new Read cycle.

In a Read cycle, the data outputs

are activated by the falling edge of

G. If LB = L the data lower byte will

be available at the outputs DQ0-

DQ7, on UB = L the data upper

byte appear at the outputs DQ8-

DQ15. After the address change,

the data outputs go High-Z until the

new information is available. The

data outputs have no preferred

state. The Read cycle is finished by

the falling edge of W, or by the

rising edge of E, respectively.

Data retention is guaranteed down

to 2 V. With the exception of E, all

inputs consist of NOR gates, so

that no pull-up/pull-down resistors

are required.

Low Voltage Automotive Fast 64K x 16 SRAM

Features

Description

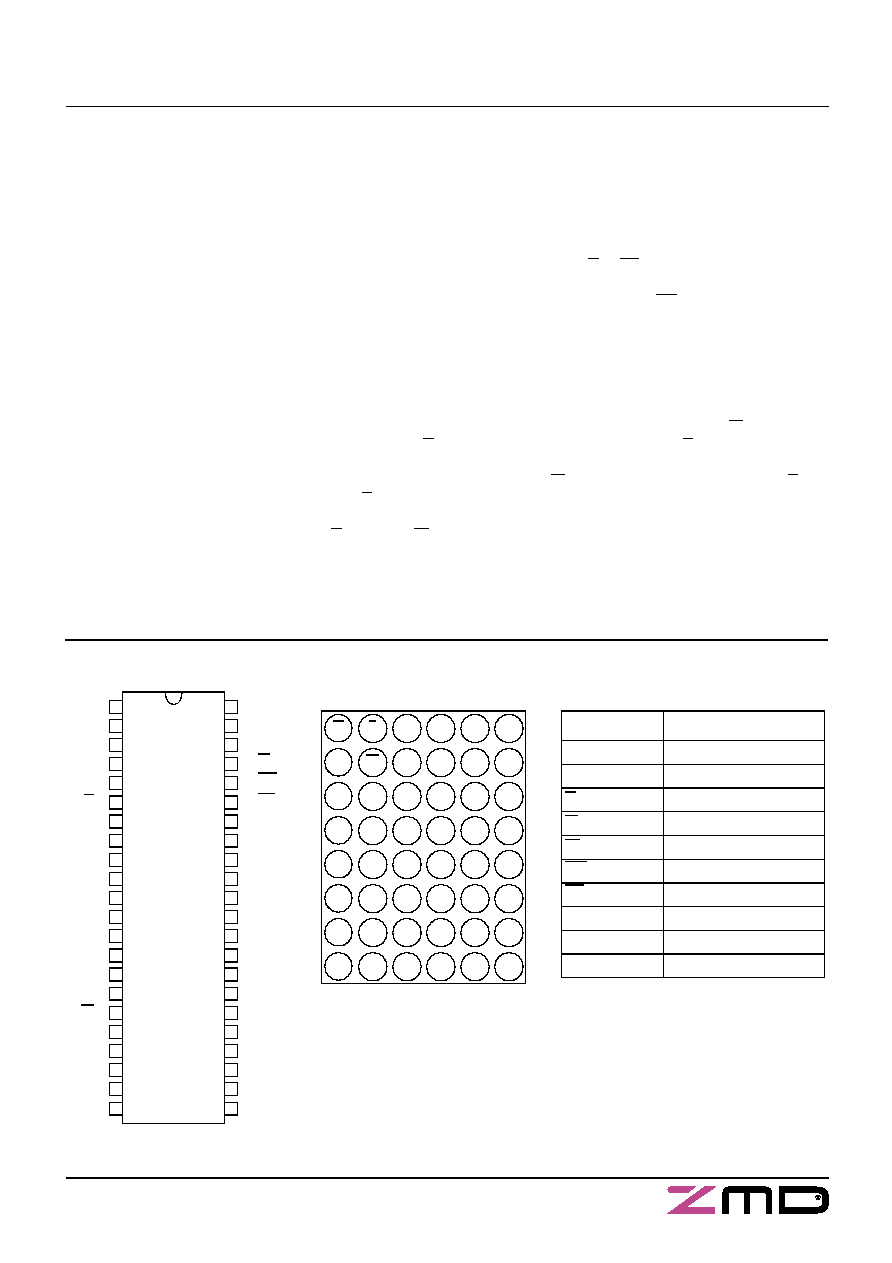

LB

G

A0

A1

A2

n.c.

DQ8

UB

A3

A4

E

DQ0

DQ9 DQ10

A5

A6

DQ1

DQ2

VSS DQ11

n.c.

A7

DQ3

VCC

VCC DQ12

n.c.

n.c.

DQ4

VSS

DQ14 DQ13

A14

A15

DQ5

DQ6

DQ15

n.c.

A12

A13

W

DQ7

n.c.

A8

A9

A10

A11

n.c.

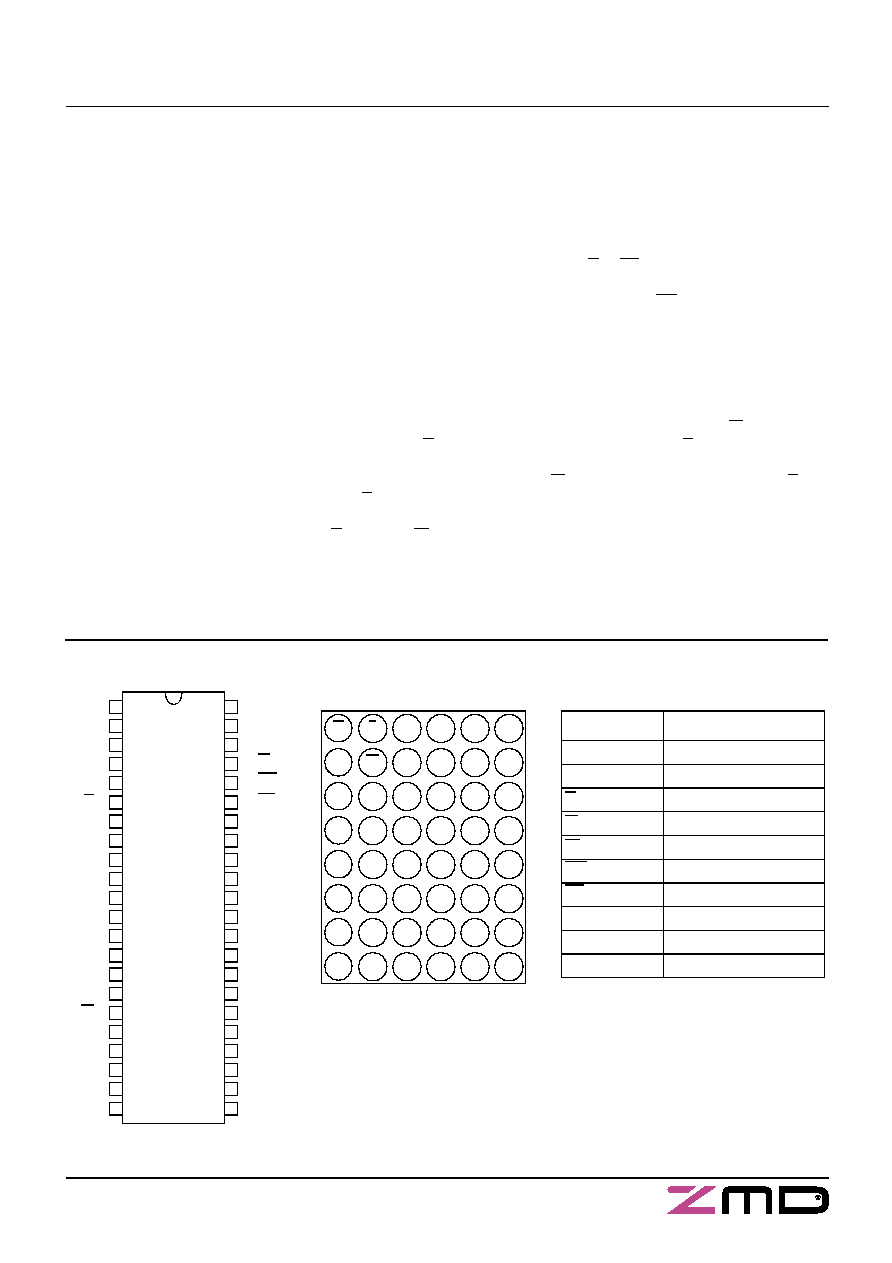

Pin Configuration

Top View

Signal Name Signal Description

A0 - A15

Address Inputs

DQ0 - DQ15

Data In/Out

E

Chip Enable

G

Output Enable

W

Write Enable

UB

Upper Byte Enable

LB

Lower Byte Enable

VCC

Power Supply Voltage

VSS

Ground

n.c.

not connected

Pin Description

1

A4

VCC

35

2

A3

A6

34

4

A1

G

32

5

A0

UB

31

3

A2

A7

33

6

E

A5

30

7

DQ0

LB

29

8

DQ1

DQ15

28

12

VSS

A8

24

9

DQ2

DQ9

27

10

DQ3

DQ8

26

11

VCC

n.c.

25

13

DQ4

A9

23

14

DQ5

A10

38

SOJ

15

16

17

18

19

20

22

21

36

37

39

40

41

42

43

44

DQ7

W

A15

A14

A13

A12

n.c.

DQ6

DQ14

DQ13

DQ12

VSS

DQ11

DQ10

n.c.

A11

TSOPII

Top View

BGA

2

November 07, 2003

UL62H1616B

Preliminary

* H or L

Operating Mode

E

W

G

LB

UB

DQ0-DQ7

DQ8-DQ15

Standby/not selected

H

*

*

*

*

High-Z

High-Z

Internal Read

L

H

H

*

*

High-Z

High-Z

L

*

*

H

H

High-Z

High-Z

Lower Byte Read

L

H

L

L

H

Data Outputs Low-Z

High-Z

Upper Byte Read

L

H

L

H

L

High-Z

Data Outputs Low-Z

Word Read

L

H

L

L

L

Data Outputs Low-Z

Data Outputs Low-Z

Lower Byte Write

L

L

*

L

H

Data Inputs High-Z

High-Z

Upper Byte Write

L

L

*

H

L

High-Z

Data Inputs High-Z

Word Write

L

L

*

L

L

Data Inputs High-Z

Data Inputs High-Z

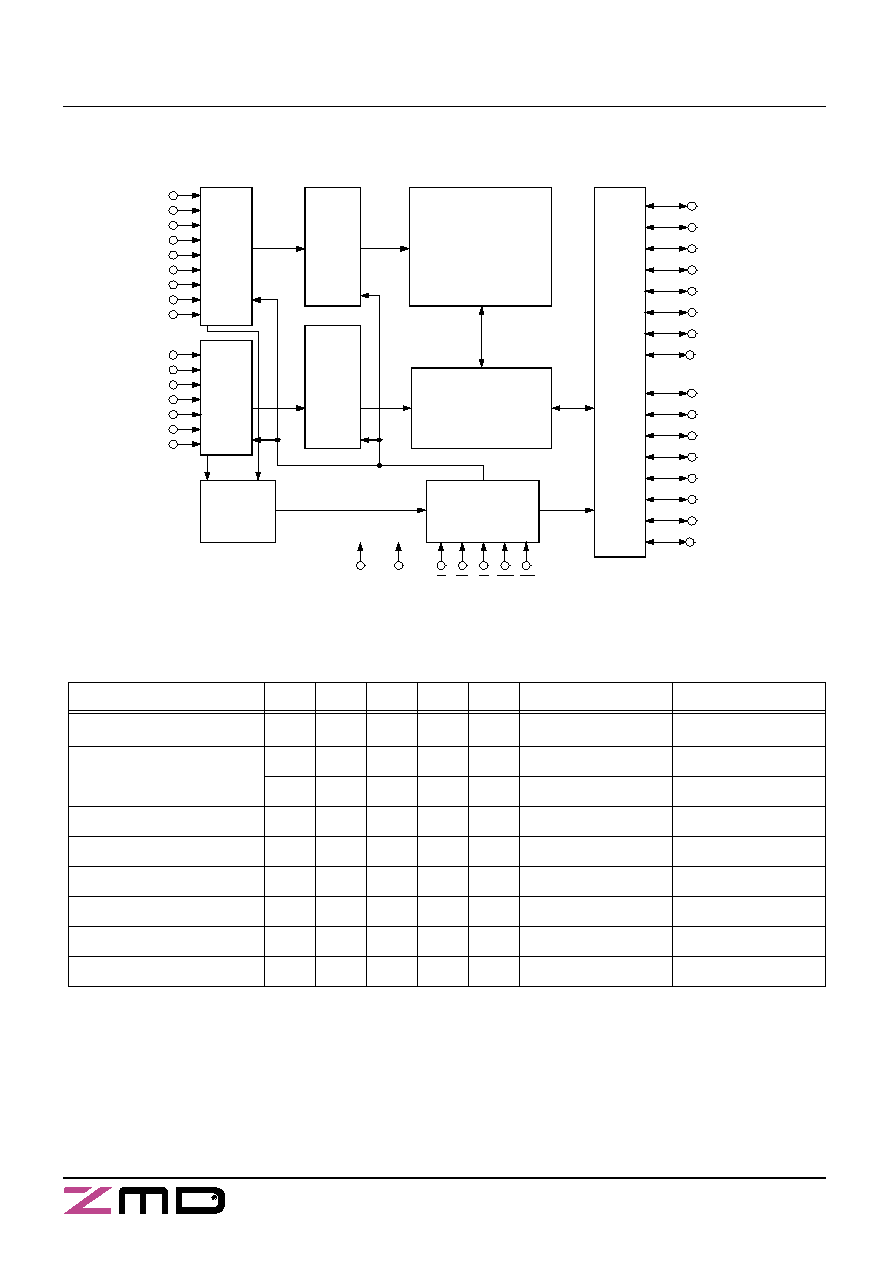

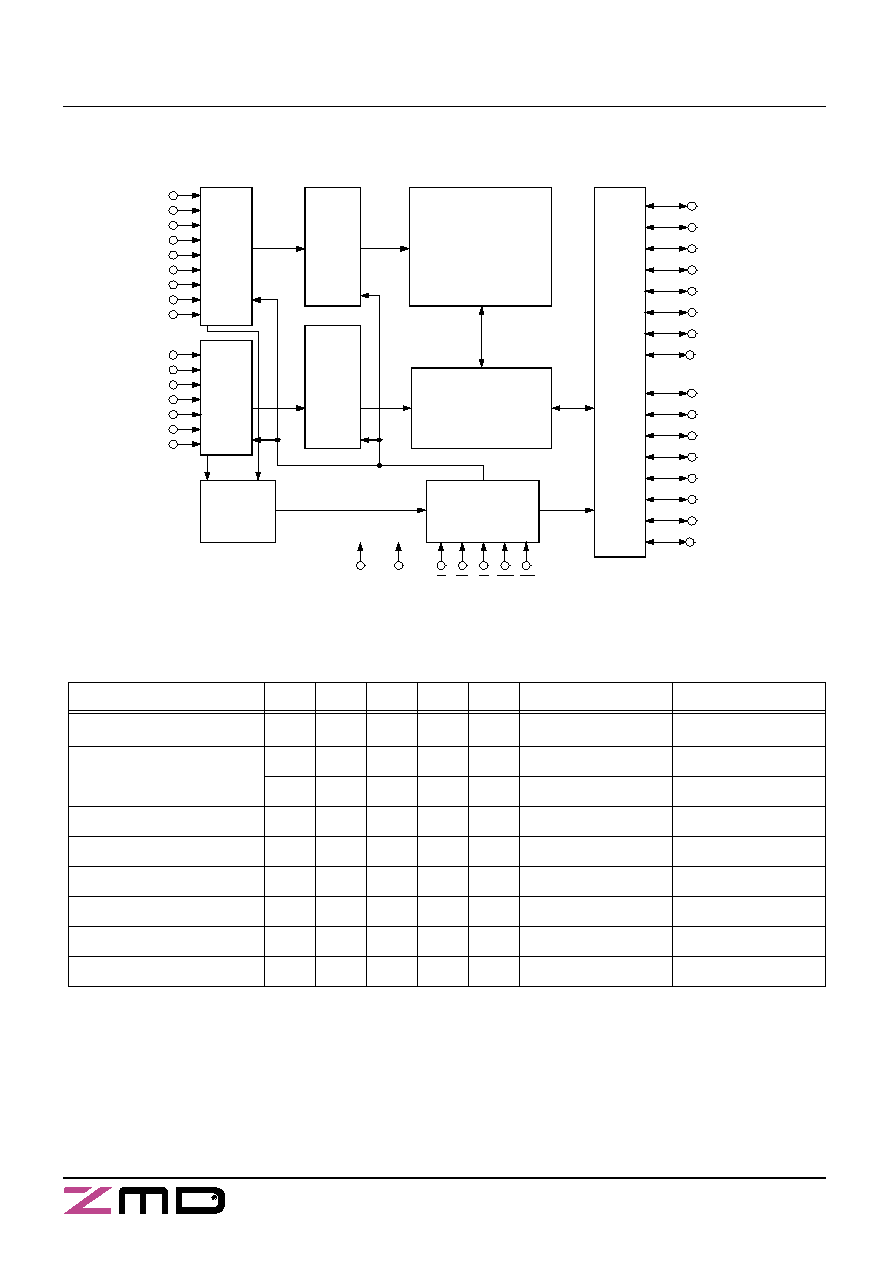

Block Diagram

Truth Table

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

V

CC

V

SS

W G

E

Ro

w

A

d

d

r

e

s

s

In

p

u

t

s

Co

l

u

m

n

A

d

d

r

e

s

s

In

p

u

t

s

Address

Change

Detector

Co

l

u

m

n

De

c

o

d

e

r

Ro

w De

c

o

d

e

r

Sense Amplifier/

Write Control Logic

Clock

Generator

C

o

m

m

o

n

D

a

ta

I/O

Memory Cell

Array

512 Rows x

128 x 16 Columns

A10

A11

A12

A13

A14

A9

A15

A0

A1

A2

A3

A4

A5

A6

A7

A8

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

UB LB

3

November 07, 2003

UL62H1616B

Preliminary

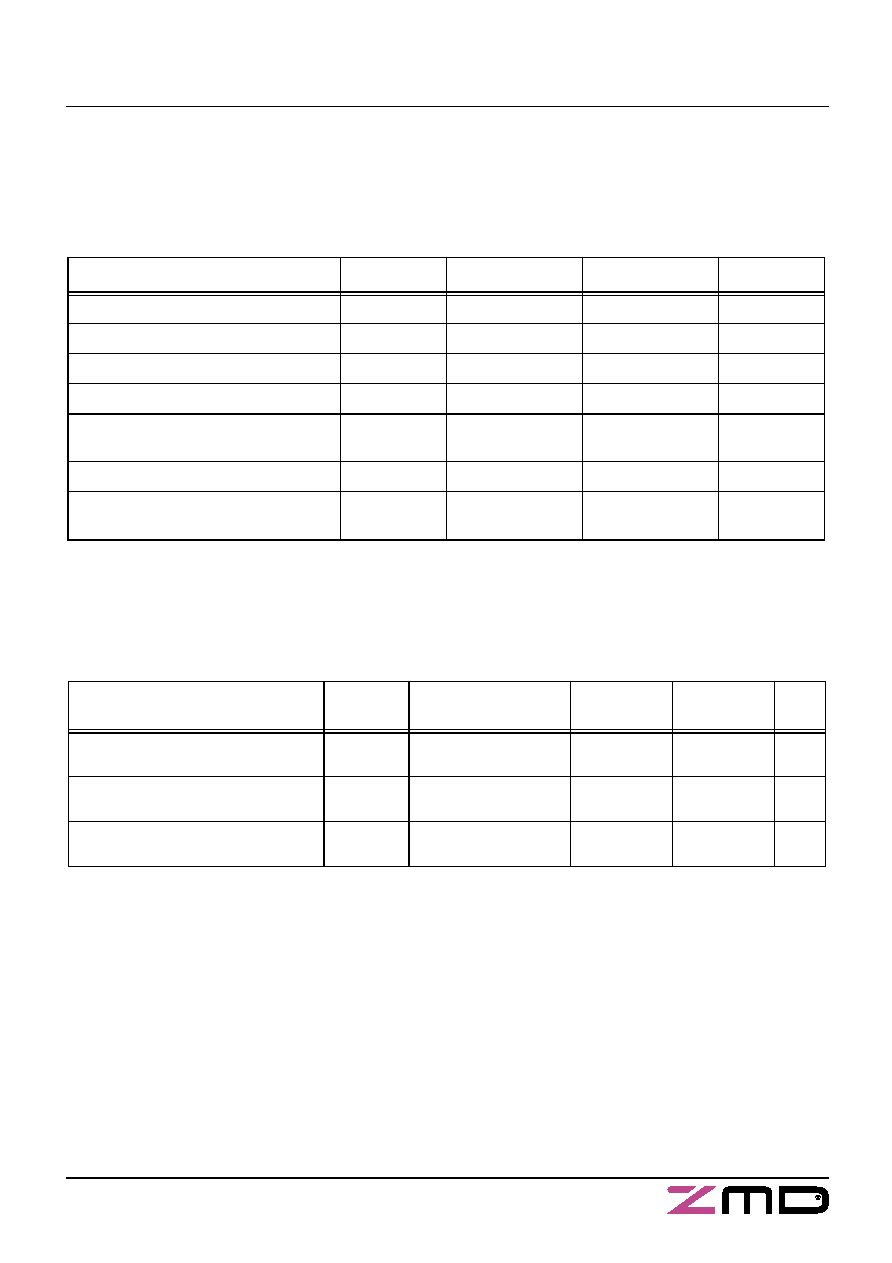

a

Stresses greater than those listed under ,,Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating

only, and functional operation of the device at condition above those indicated in the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect reliability

b

Maximum voltage is 3.6 V

c

Not more than 1 output should be shorted at the same time. Duration of the short circuit should not exceed 30 s.

Absolute Maximum Ratings

a

Symbol

Min.

Max.

Unit

Power Supply Voltage

V

CC

-0.3

3.6

V

Input Voltage

V

I

-0.3

V

CC

+ 0.3

b

V

Output Voltage

V

O

-0.3

V

CC

+ 0.3

b

V

Power Dissipation

P

D

-

1

W

Operating Temperature

K-Type

A-Type

T

a

-40

-40

85

125

∞C

Storage Temperature

T

stg

-65

150

∞C

Output Short-Circuit Current

at V

CC

= 2.5 V and V

O

= 0 V

c

| I

OS

|

100

mA

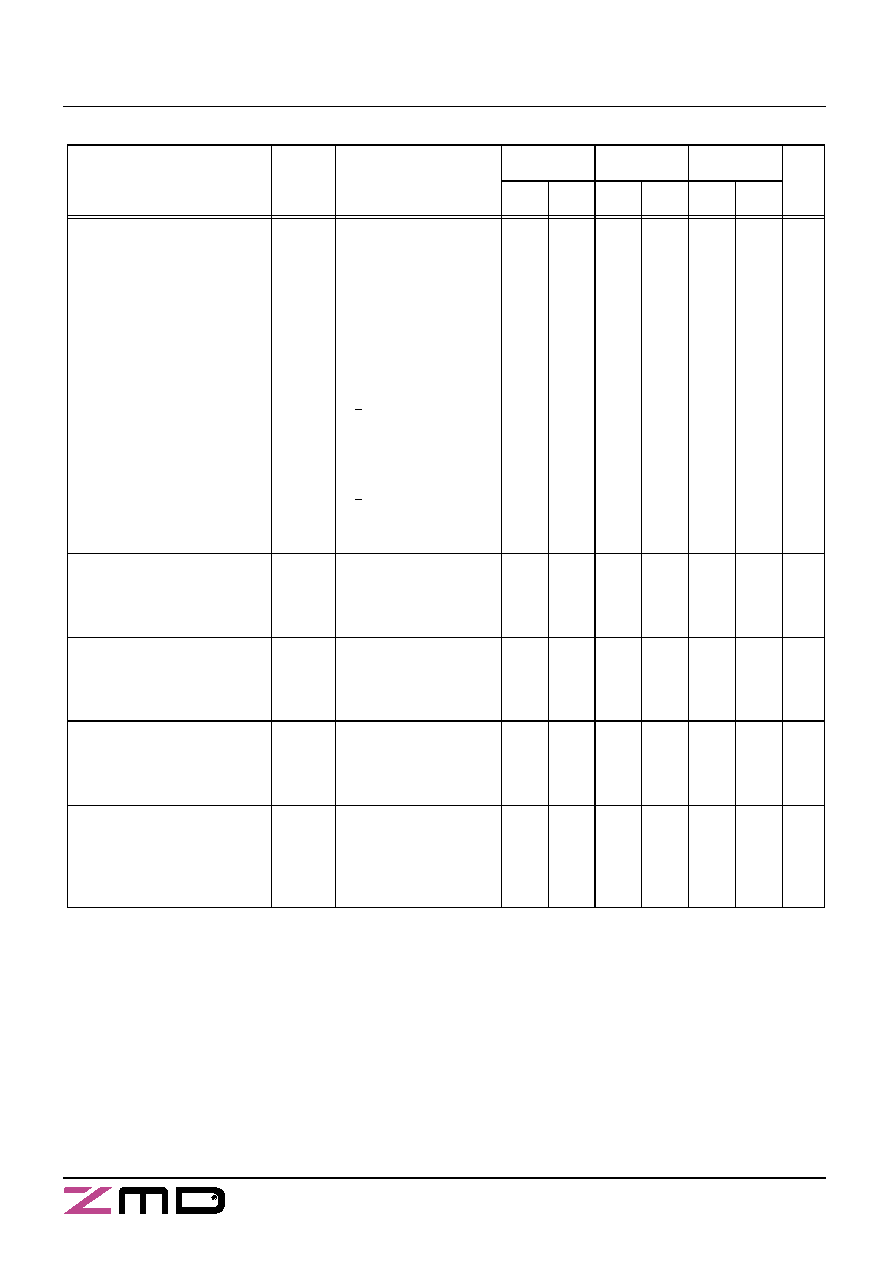

Characteristics

All voltages are referenced to V

SS

= 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified.

Dynamic measurements are based on a rise and fall time of

5 ns, measured between 10 % and 90 % of V

I

, as well as

input levels of V

IL

= 0 V and V

IH

= 2.5 V. The timing reference level of all input and output signals is 1.2 V,

with the exception of the t

dis

-times and t

en

-times, in which cases transition is measured ±200 mV from steady-state voltage.

d

-2 V at Pulse Width 10 ns

Recommended

Operating Conditions

Symbol

Conditions

Min.

Max.

Unit

Power Supply Voltage

V

CC

2.3

2.7

V

Input Low Voltage

d

V

IL

-0.2

0.6

V

Input High Voltage

V

IH

2.0

V

CC

+ 0.2

V

4

November 07, 2003

UL62H1616B

Preliminary

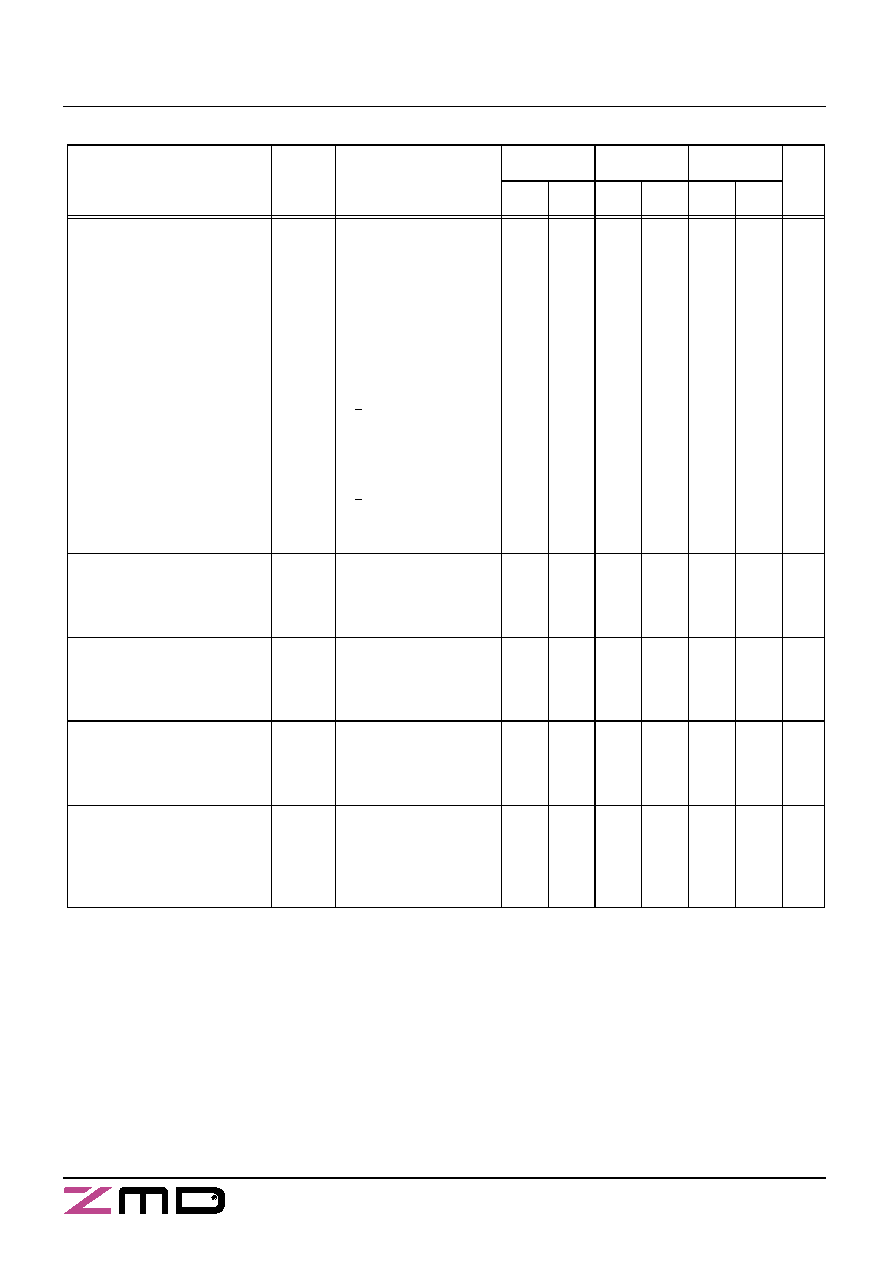

e

This parameter is guaranteed, but not tested.

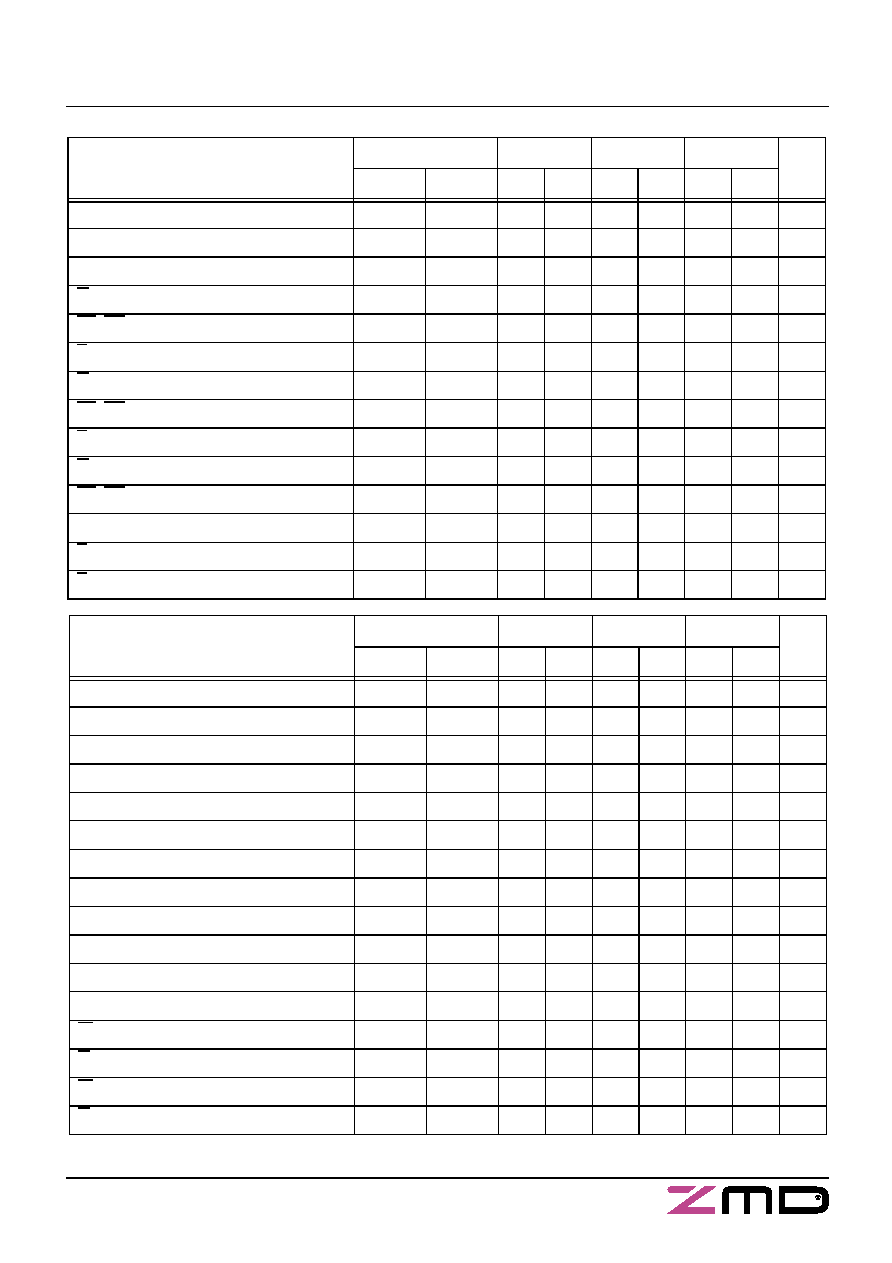

Electrical Characteristics

Symbol

Conditions

15

20

35

Unit

Min. Max. Min. Max. Min. Max.

Supply Current -

Operating Mode

Supply Current -

Standby Mode

(CMOS level)

Supply Current -

Standby Mode

(LVTTL level)

I

CC(OP)

I

CC(SB)

I

CC(SB)1

V

CC

V

IL

V

IH

t

cW

t

cW

t

cW

t

cW

t

cW

V

CC

V

E

K-Type

A-Type

V

CC

V

E

K-Type

A-Type

= 2.7 V

= 0.6 V

= 2.0 V

= 15 ns

= 20 ns

= 35 ns

= 55 ns

= 70 ns

= 2.7 V

= V

CC

- 0.2 V

= 2.7 V

= 2.0 V

50

40

e

25

e

15

e

12

e

1000

1000

1

2

-

40

25

e

15

e

12

e

1000

1000

1

2

-

-

25

15

e

12

e

70

100

0.5

1

mA

mA

mA

µA

µA

mA

mA

Output High Voltage

Output Low Voltage

V

OH

V

OL

V

CC

I

OH

V

CC

I

OL

= 2.3 V

= -0.5 mA

= 2.3 V

= 0.5 mA

2.0

0.4

2.0

0.4

2.0

0.4

V

V

Input High Leakage Current

Input Low Leakage Current

I

IH

I

IL

V

CC

V

IH

V

CC

V

IL

= 2.7 V

= 2.7 V

= 2.7 V

= 0 V

-2

2

-2

2

-2

2

µA

µA

Output High Current

Output Low Current

I

OH

I

OL

V

CC

V

OH

V

CC

V

OL

= 2.3 V

= 2.0 V

= 2.3 V

= 0.4 V

0.5

-0.5

0.5

-0.5

0.5

-0.5

mA

mA

Output Leakage Current

High at Three-State Outputs

Low at Three-State Outputs

I

OHZ

I

OLZ

V

CC

V

OH

V

CC

V

OL

= 2.7 V

= 2.7 V

= 2.7 V

=

0 V

-2

2

-2

2

-2

2

µA

µA

5

November 07, 2003

UL62H1616B

Preliminary

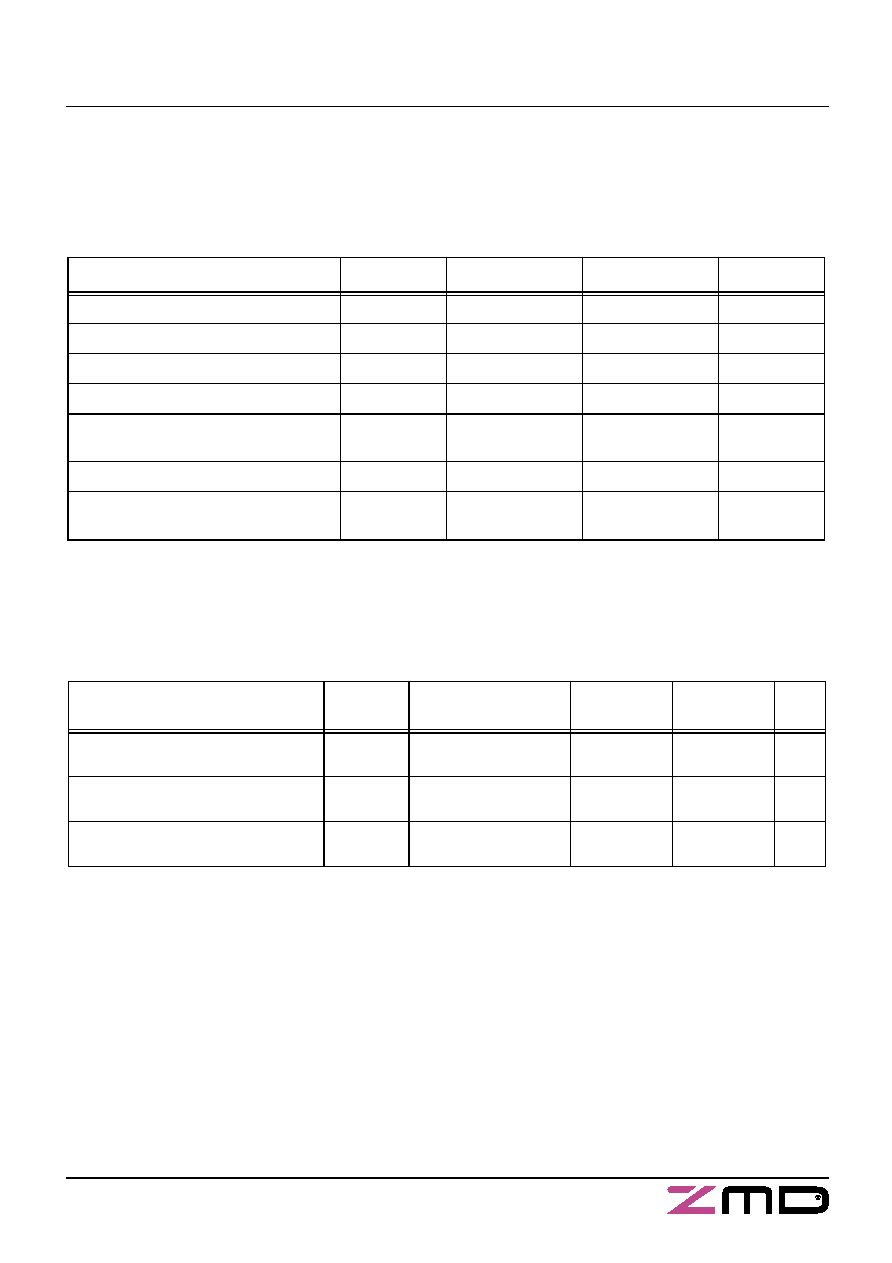

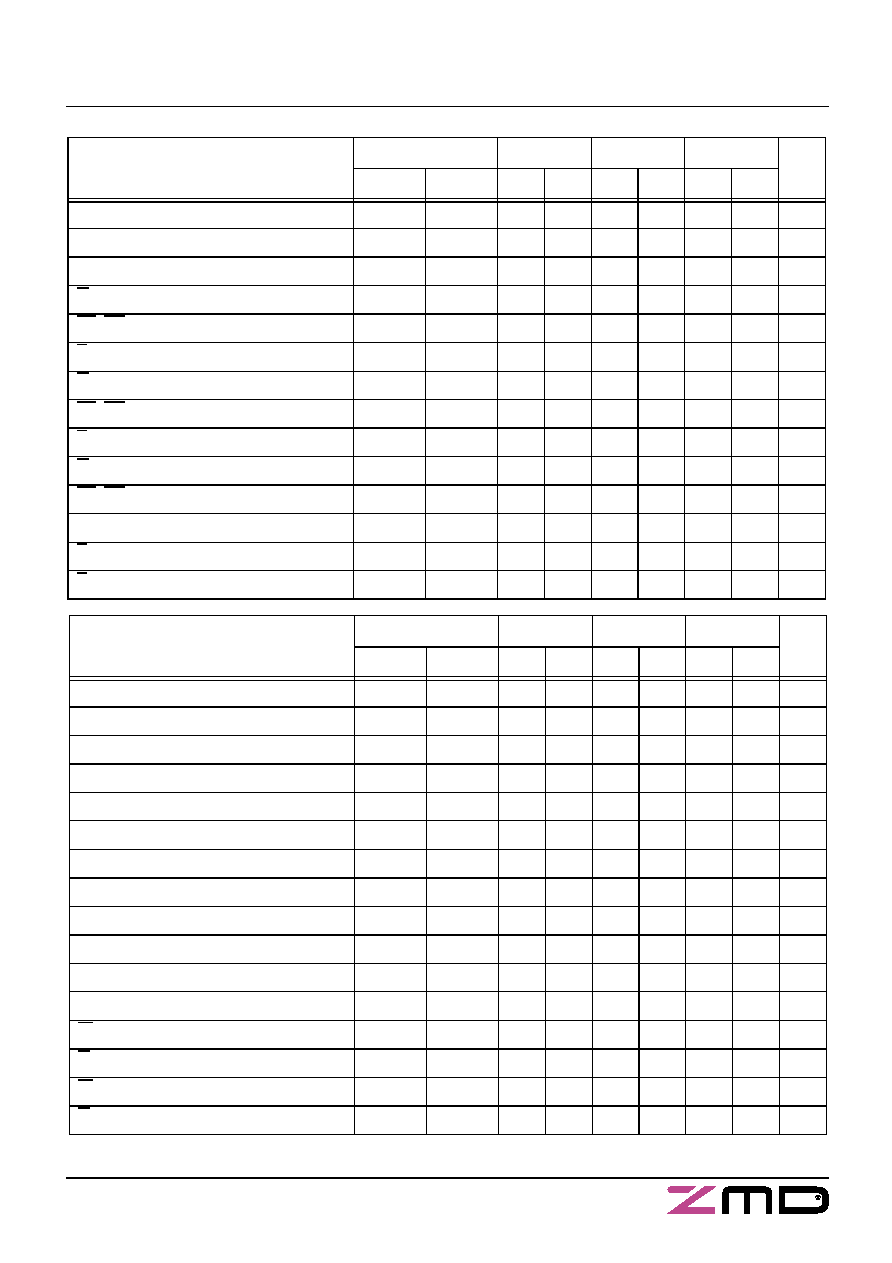

Switching Characteristics

Read Cycle

Symbol

15

20

35

Unit

Alt.

IEC

Min.

Max.

Min.

Max.

Min.

Max.

Read Cycle Time

t

RC

t

cR

15

20

35

ns

Address Access Time to Data Valid

t

AA

t

a(A)

15

20

35

ns

Chip Enable Access Time to Data Valid

t

ACE

t

a(E)

15

20

35

ns

G LOW to Data Valid

t

OE

t

a(G)

7

9

15

ns

LB, UB LOW to Data Valid

t

B

t

a(B)

7

9

15

ns

E HIGH to Output in High-Z

t

HZCE

t

dis(E)

7

8

12

ns

G HIGH to Output in High-Z

t

HZOE

t

dis(G)

7

8

12

ns

LB, UB HIGH to Output in High-Z

t

HZB

t

dis(B)

7

8

12

ns

E LOW to Output in Low-Z

t

LZCE

t

en(E)

4

4

5

ns

G LOW to Output in Low-Z

t

LZOE

t

en(G)

0

0

0

ns

LB, UB LOW to Output in Low-Z

t

LZB

t

en(B)

0

0

0

ns

Output Hold Time from Address Change

t

OH

t

v(A)

3

3

3

ns

E LOW to Power-Up Time

t

PU

0

0

0

ns

E HIGH to Power-Down Time

t

PD

15

20

35

ns

Switching Characteristics

Write Cycle

Symbol

15

20

35

Unit

Alt.

IEC

Min.

Max.

Min.

Max.

Min.

Max.

Write Cycle Time

t

WC

t

cW

15

20

35

ns

Write Pulse Width

t

WP

t

w(W)

10

12

20

ns

Write Setup Time

t

WP

t

su(W)

10

12

20

ns

Address Setup Time

t

AS

t

su(A)

0

0

0

ns

Address Valid to End of Write

t

AW

t

su(A-WH)

10

12

20

ns

Chip Enable Setup Time

t

CW

t

su(E)

10

12

25

ns

Byte Enable Setup Time

t

BW

t

su(B)

10

12

25

ns

Pulse Width Chip Enable to End of Write

t

CW

t

w(E)

10

12

25

ns

Pulse Width Byte Enable to End of Write

t

BW

t

w(B)

10

12

25

ns

Data Setup Time

t

DS

t

su(D)

7

9

15

ns

Data Hold Time

t

DH

t

h(D)

0

0

0

ns

Address Hold from End of Write

t

AH

t

h(A)

0

0

0

ns

W LOW to Output in High-Z

t

HZWE

t

dis(W)

7

8

15

ns

G HIGH to Output in High-Z

t

HZOE

t

dis(G)

7

8

12

ns

W HIGH to Output in Low-Z

t

LZWE

t

en(W)

3

3

3

ns

G LOW to Output in Low-Z

t

LZOE

t

en(G)

0

0

0

ns